Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2 results about "Schematic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A schematic, or schematic diagram, is a representation of the elements of a system using abstract, graphic symbols rather than realistic pictures. A schematic usually omits all details that are not relevant to the key information the schematic is intended to convey, and may include oversimplified elements in order to make this essential meaning easier to grasp. For example, a subway map intended for passengers may represent a subway station with a dot. The dot is not intended to resemble the actual station at all; instead, it aims to give the viewer information without unnecessary visual clutter. A schematic diagram of a chemical process uses symbols in place of detailed representations of the vessels, piping, valves, pumps, and other equipment that compose the system; in so doing, it emphasizes the functions of these individual elements--and the interconnections among them--and suppresses their particular physical details. In an electronic circuit diagram, the layout of the symbols may not look anything like the circuit as it appears in the physical world: instead of representing the way the circuit looks, the schematic aims to capture, on a more general level, the way it works.

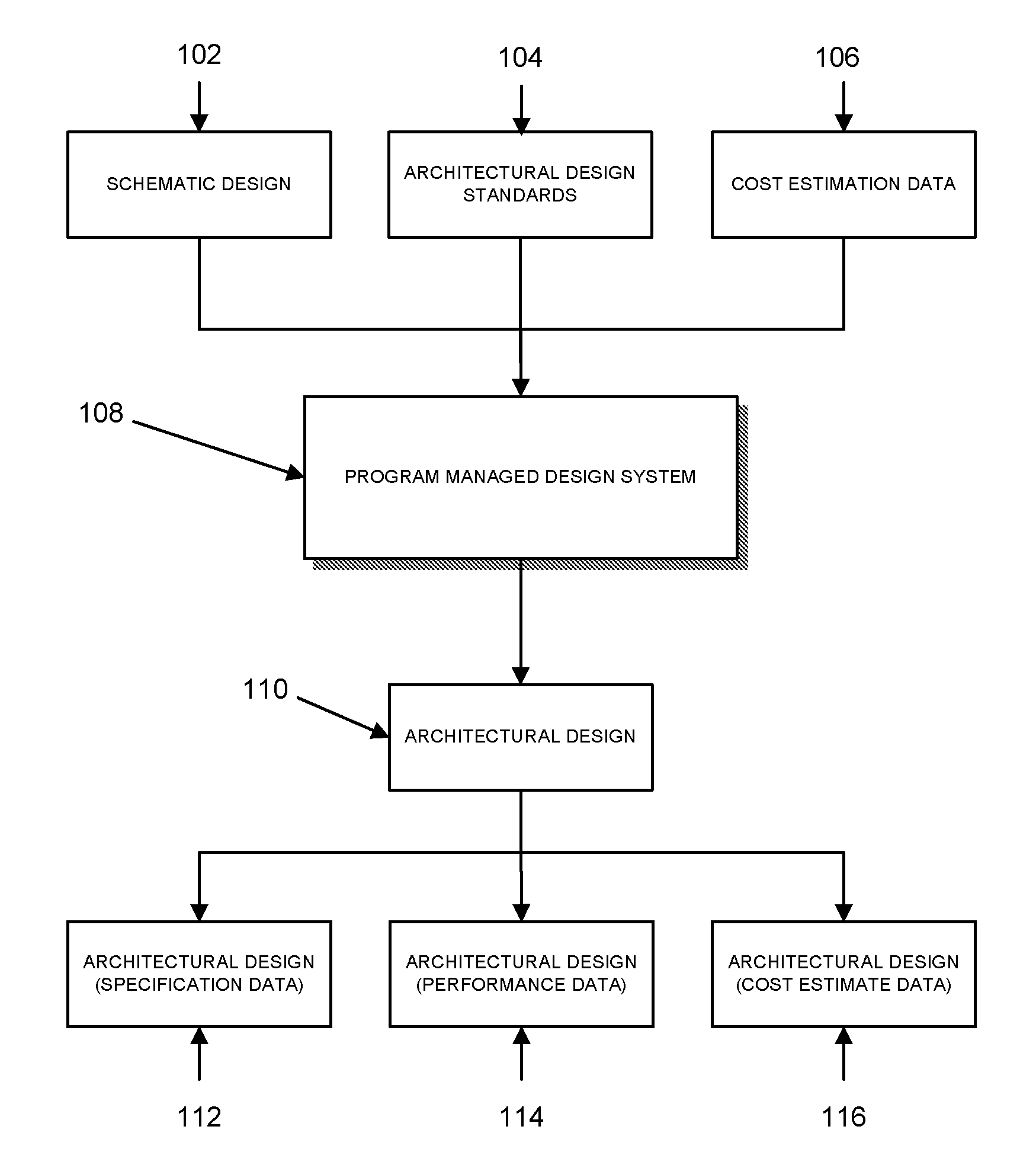

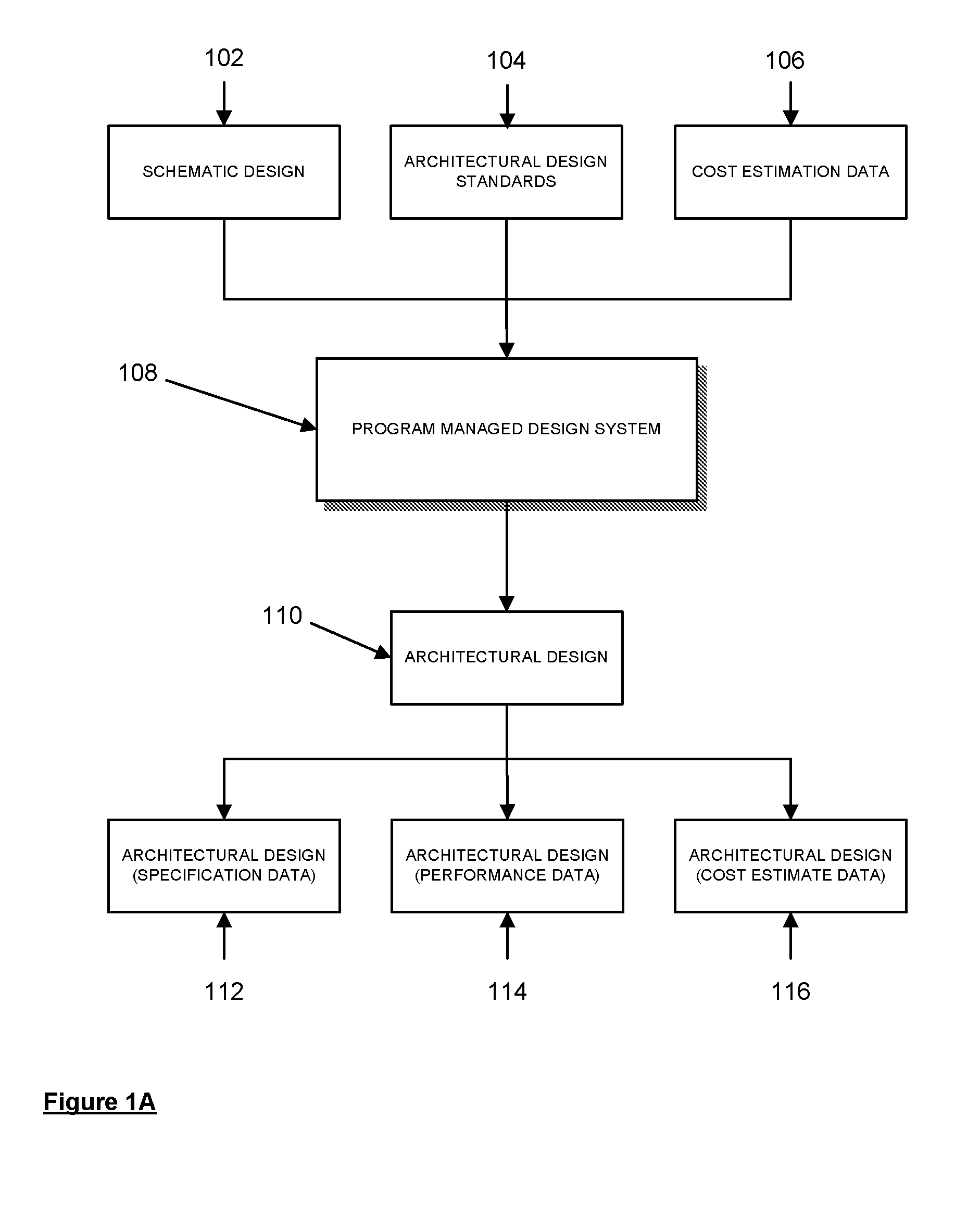

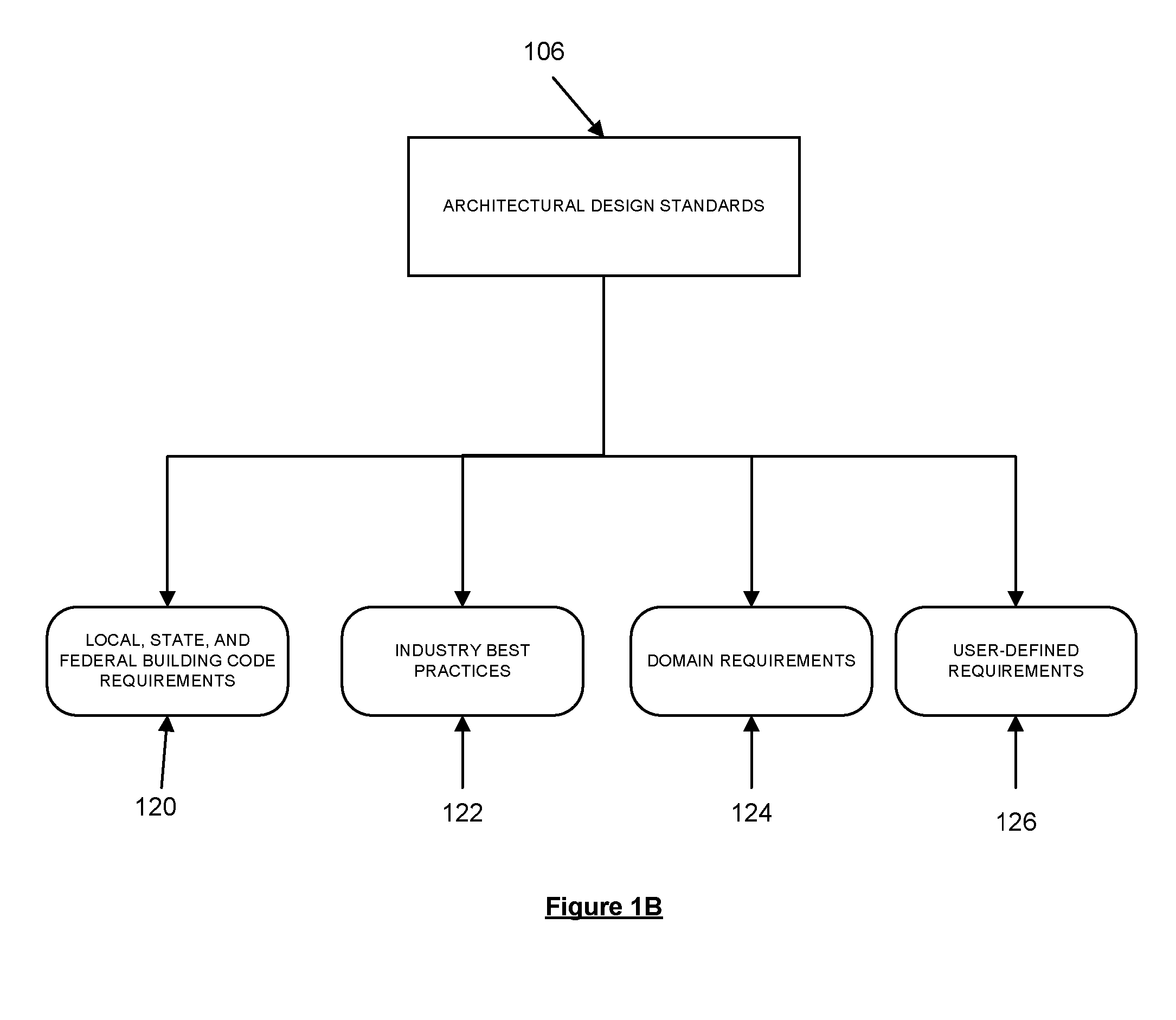

Program managed design for complex construction projects

Owner:GANNON TECH GROUP

Apparatus and method for collaborative adaptation of hierarchically-designed schematics to variant design requirements

ActiveUS9760666B1Efficient sharingEfficient mergeCAD circuit designComputer designed circuitsElectronic systemsHierarchical design

A planned schematic for an electronic system is hierarchically divided into base-level schematic blocks which may be designed individually. In accordance with a plurality of sets of design requirements, variant overlays are designed for each base-level schematic block, each overlay including variant parameter values which may replace corresponding parameter values of the schematic blocks. The schematic blocks are integrated to generate a system-level schematic, and the variant overlays for a given set of design requirements are merged to generate a system variant overlay. Parameter values of the system variant overlay may then replace corresponding parameter values of the system-level schematic to generate a variant schematic for the given set of design requirements. Using this system and methodology, variant designs may be collaboratively generated by multiple designers each with expertise in particular schematic blocks and / or variant requirements, and may be shared either at the system level or at lower levels.

Owner:CADENCE DESIGN SYST INC

Popular searches

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap