Demultiplexer circuit

a multi-channel circuit and multi-channel technology, applied in the direction of code conversion, data switching network, synchronisation signal speed/phase control, etc., can solve the problems of increasing power consumption, reducing data transfer rate, and not considering the bit deviation of the comma code in the received serial data. achieve the effect of improving the data transfer ra

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

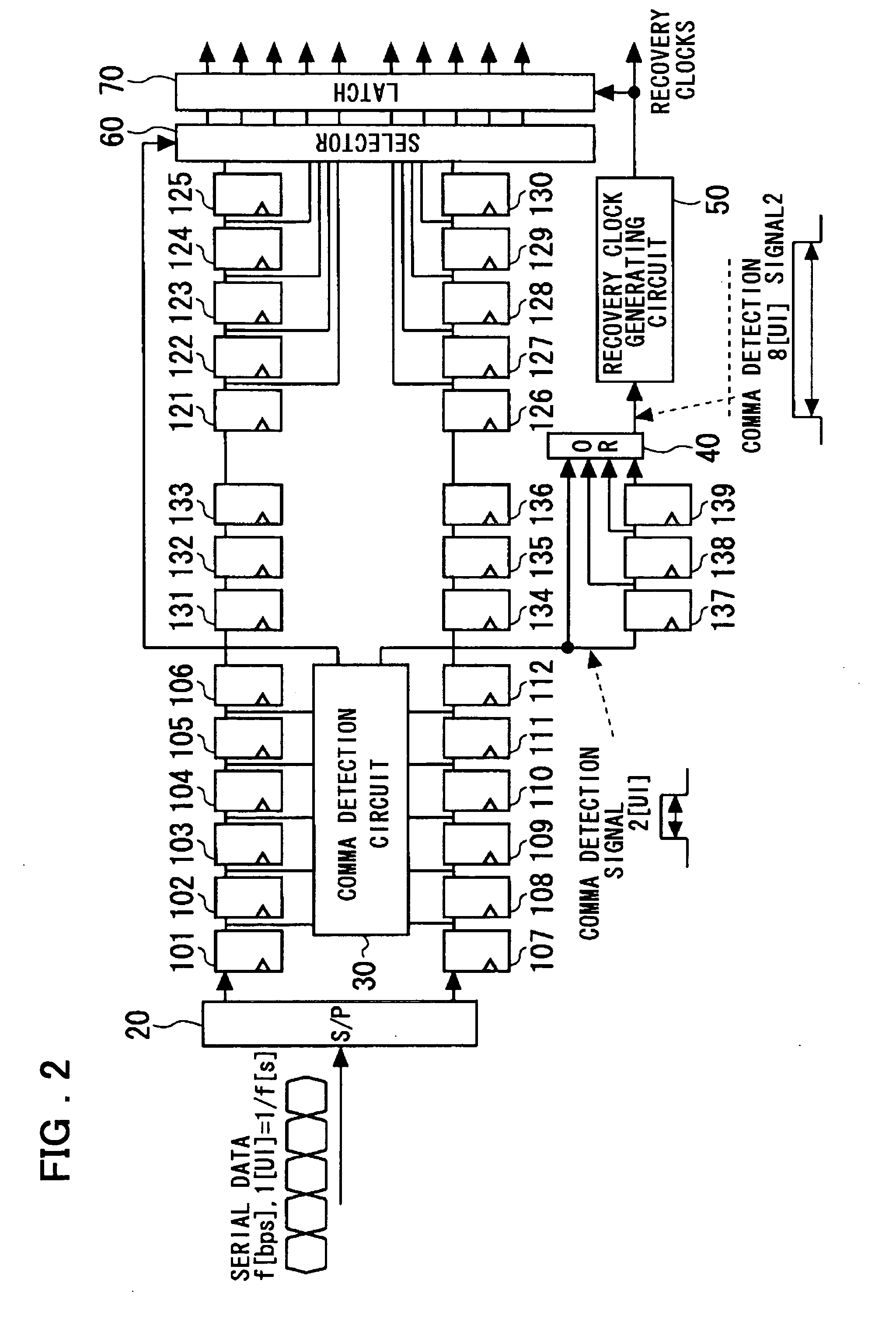

[0032] Referring to the drawings, preferred embodiments of the present invention are explained in detail.

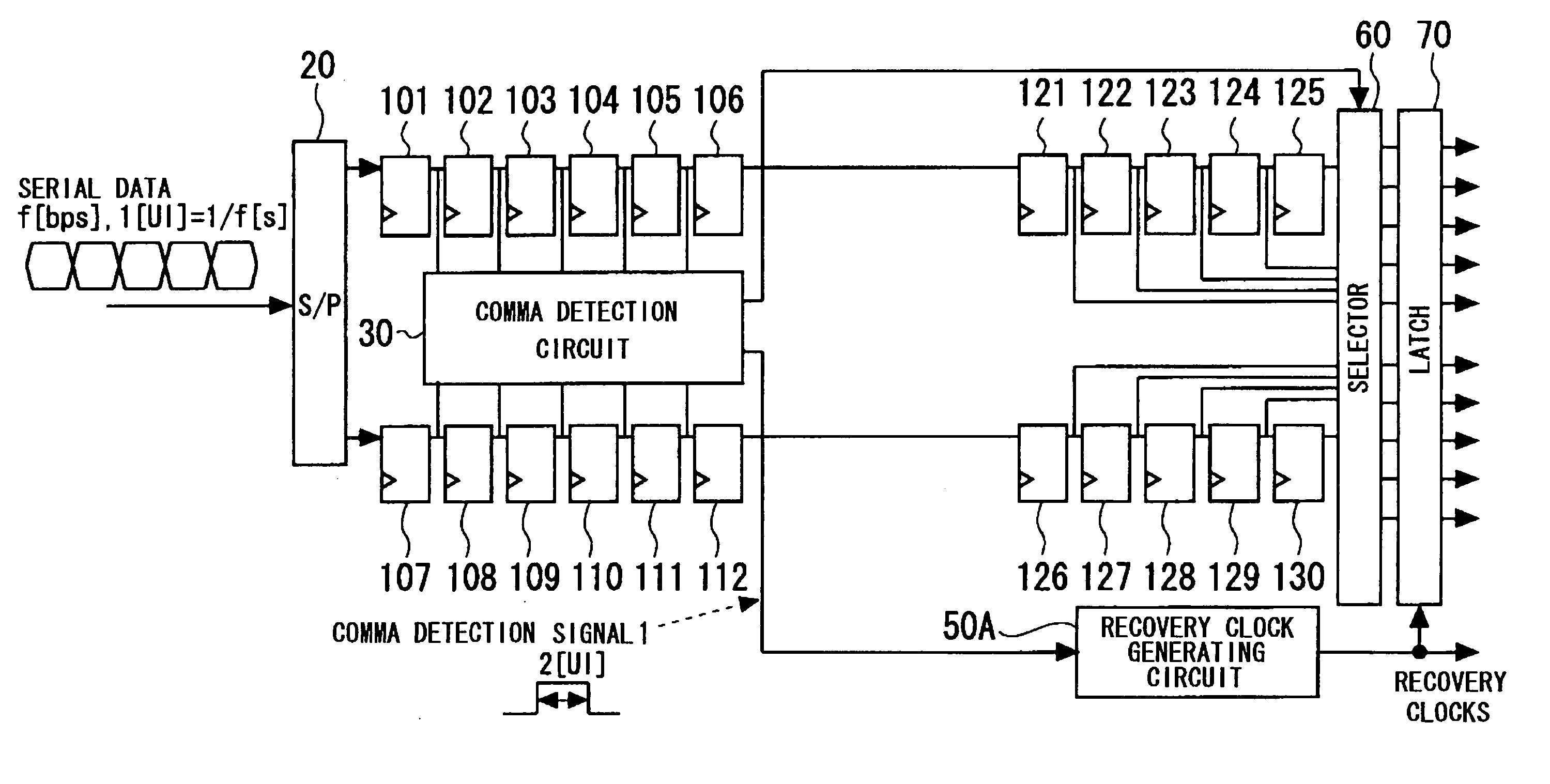

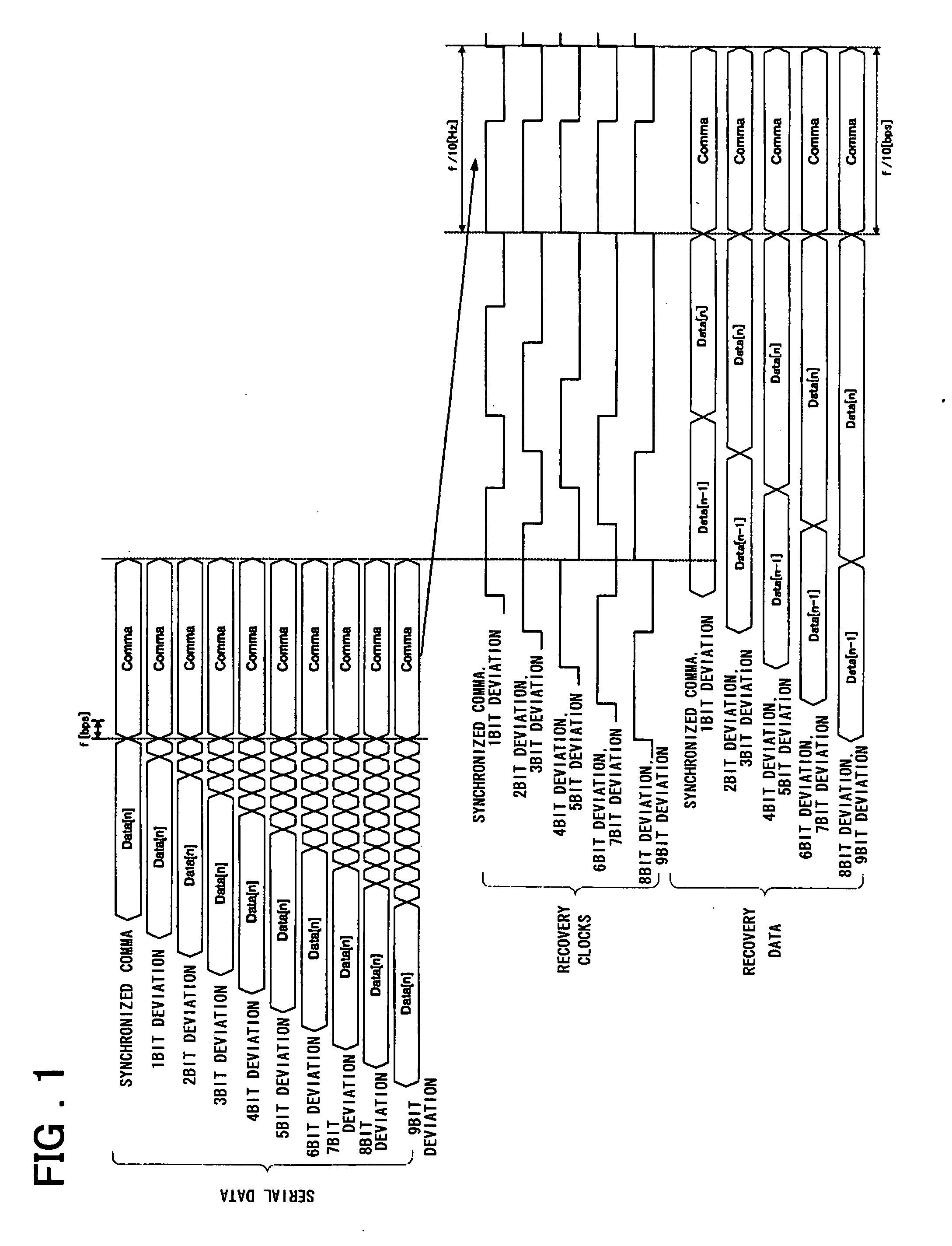

[0033]FIG. 1 illustrates the operating principle of an embodiment of the present invention. Specifically, FIG. 1 illustrates the timing operation of a demultiplexer (macro-cell) at a high-speed serial interface adapted for effecting 1:10 serial-to-parallel conversion and byte alignment. Referring to FIG. 1, recovery data of f / 10 bps ( . . . , Data[n−1], Data[n], Comma) and recovery clocks of f / 10 Hz are generated against serial data input with a transfer rate of f bps. It is noted that the received serial data is 8 B-10 B converted data. The received serial data is processed with byte alignment every symbol (every ten bits), responsive to rising edges of the recovery clocks, to issue 10-bit output parallel data. Moreover, when the 10-bit command code (Comma), made up by preset logical bits, as mentioned previously, is detected, the period of the recovery clocks is adjusted. In

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap