Lateral semiconductor device and vertical semiconductor device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Example

First Embodiment

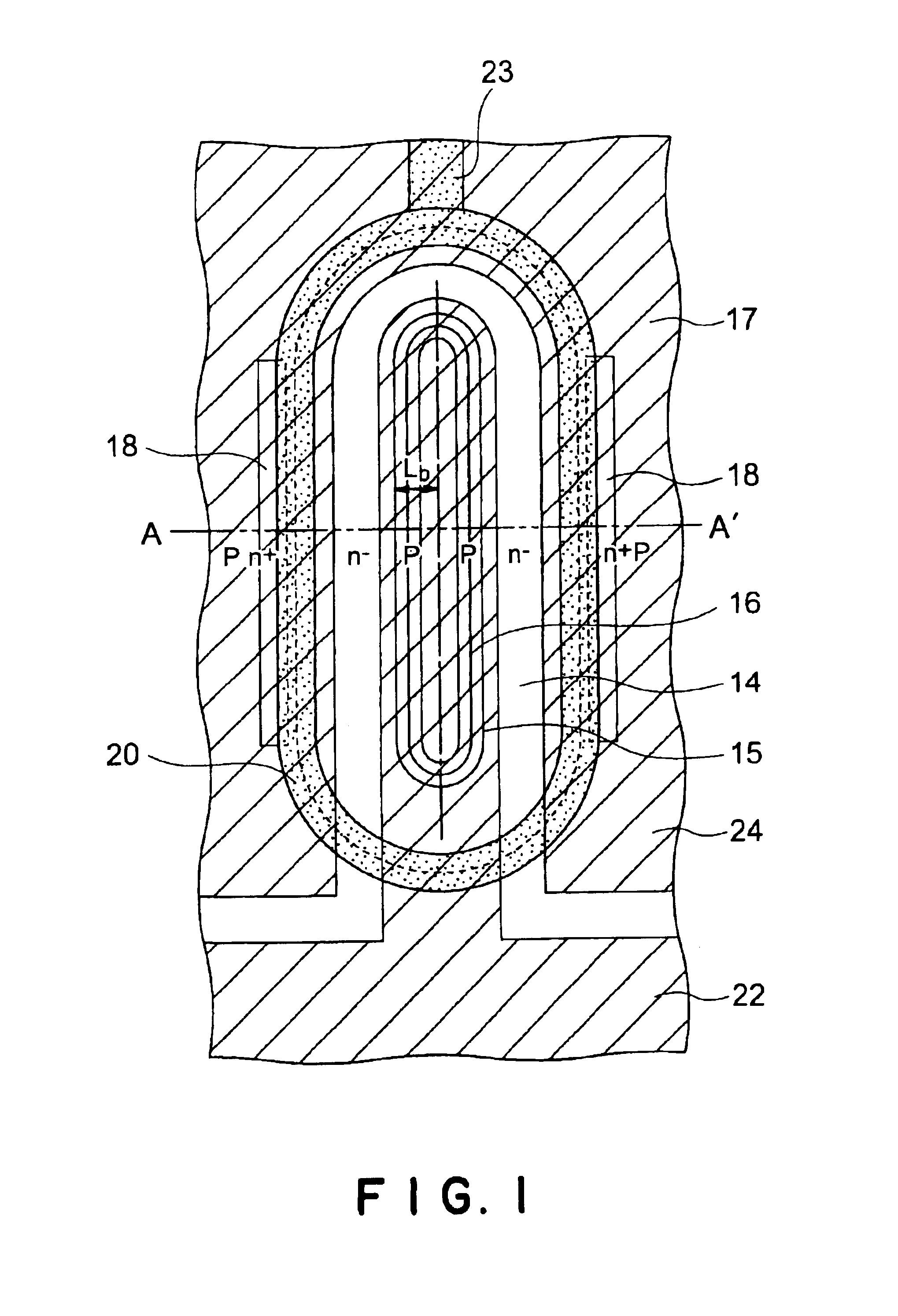

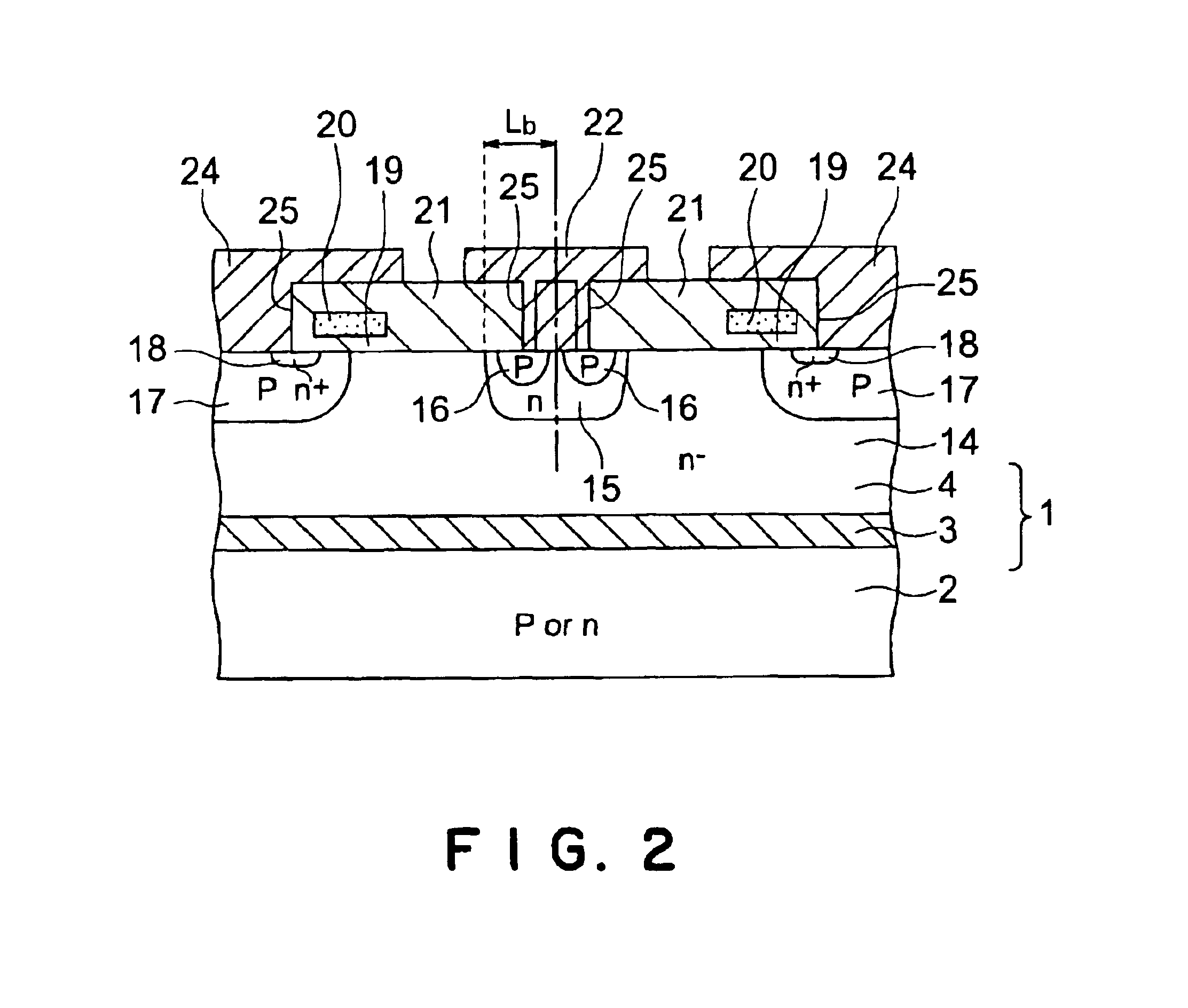

[0060]FIG. 1 is a plan view schematically showing a lateral IGBT according to the first embodiment of the present invention. FIG. 2 is a sectional view taken along a line A-A′ in FIG. 1.

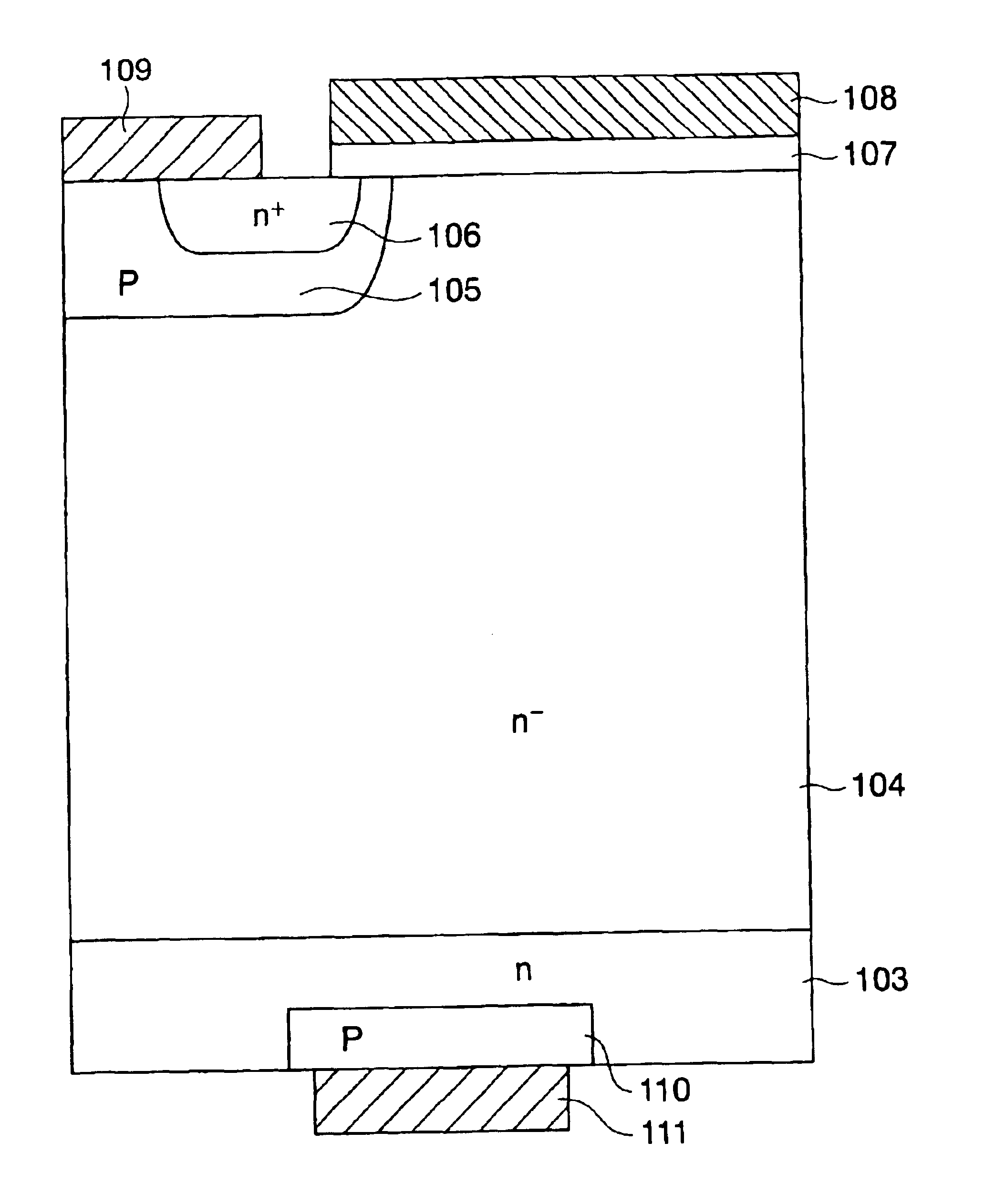

[0061]An SOI substrate 1 has a silicon support substrate 2, a buried oxide film 3, and a high-resistance, n−-type silicon active layer 4. In the IGBT of this embodiment, the n−-type silicon active layer 4 is used as an n−-type base layer 14. An n-type buffer layer 15 is formed in the surface of the n−-type base layer 14 by selective diffusion. This n-type buffer layer 15 has a stripe shape whose two, upper and lower end portions protrude outward into the shape of an arc having a curvature R. A p-type drain layer 16 is formed in the surface of the n-type buffer layer 15 by selective diffusion.

[0062]In this embodiment, the p-type drain layer 16 has the same shape as the n-type buffer layer 15 and has an annular structure.

[0063]In the surface of the n−-type base layer 14, a p-type base laye

Example

Second Embodiment

[0070]FIG. 3 is a plan view of a lateral IGBT according to the second embodiment of the present invention. A sectional view taken along a line A-A′ in FIG. 3 is the same as FIG. 2, so this sectional view will be omitted.

[0071]A difference of this embodiment from the above first embodiment is that in the first embodiment the p-type drain layer 16 has an annular structure, but in this embodiment a p-type drain layer 36 has a horseshoe-shaped or inverse U-shaped structure formed by cutting away in the horizontal direction (a lateral direction on the paper surface) one of the upper and lower end portions, e.g., the lower end portion of the p-type drain layer 16 having the annular structure in the first embodiment. The rest of the arrangement is the same as the first embodiment.

[0072]In the lateral IGBT of this embodiment, the area of the p-type drain layer 36 is smaller than the aforementioned IGBT related to the present invention. As in the first embodiment described abov

Example

Third Embodiment

[0076]FIG. 6 is a plan view of a lateral IGBT according to the third embodiment of the present invention. A sectional view taken along a line A-A′ in FIG. 6 is the same as FIG. 2, so this sectional view will be omitted.

[0077]A difference of this embodiment from the above first embodiment is that in the first embodiment the p-type drain layer 16 has an annular structure, but in this embodiment p-type drain layers 46 are two striped structures formed by cutting away in the horizontal direction the upper and lower end portions of the p-type drain layer 16 having the annular structure in the first embodiment. The rest of the arrangement is the same as the first embodiment.

[0078]In the lateral IGBT of this embodiment, the area of the p-type drain layers 46 is smaller than that in the aforementioned IGBT related to the present invention. As in the first embodiment described above, therefore, the breakdown voltage can be raised without raising the ON voltage.

[0079]Also, the p-

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap