Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1 results about "Physical verification" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Physical verification is a process whereby an integrated circuit layout (IC layout) design is verified via EDA software tools to ensure correct electrical and logical functionality and manufacturability. Verification involves design rule check (DRC), layout versus schematic (LVS), XOR (exclusive OR), antenna checks and electrical rule check (ERC).

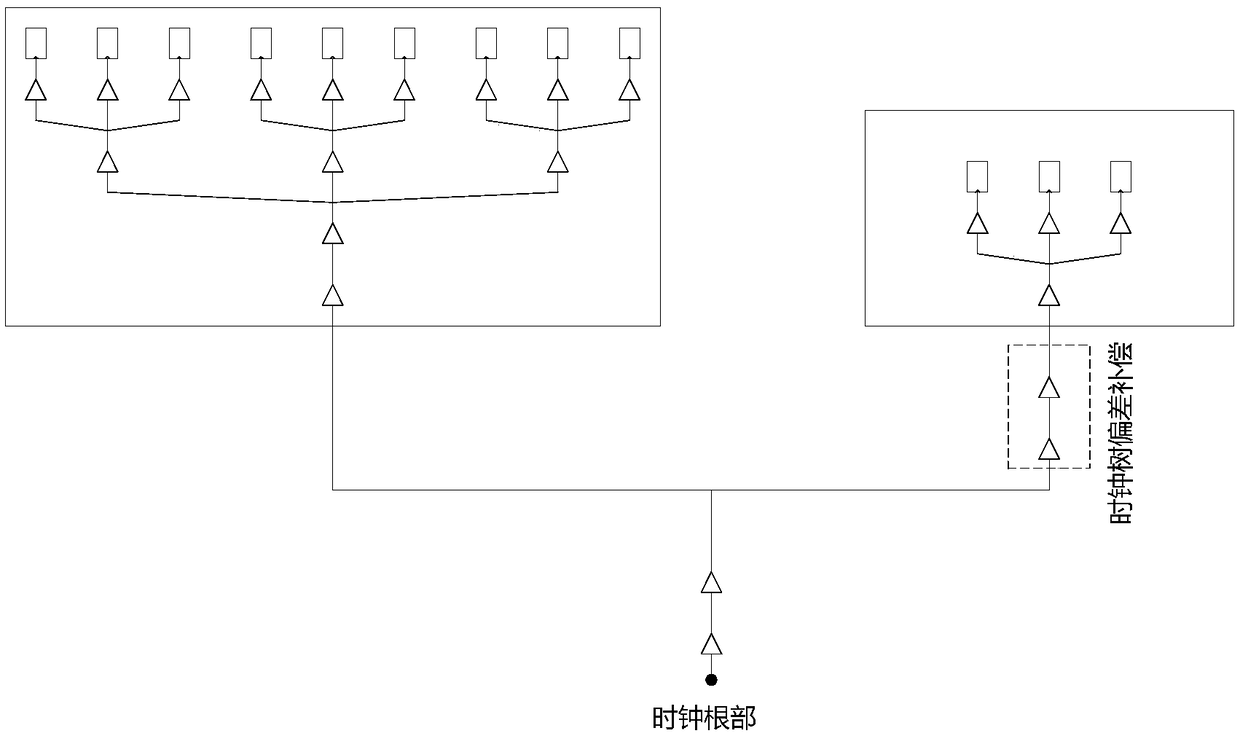

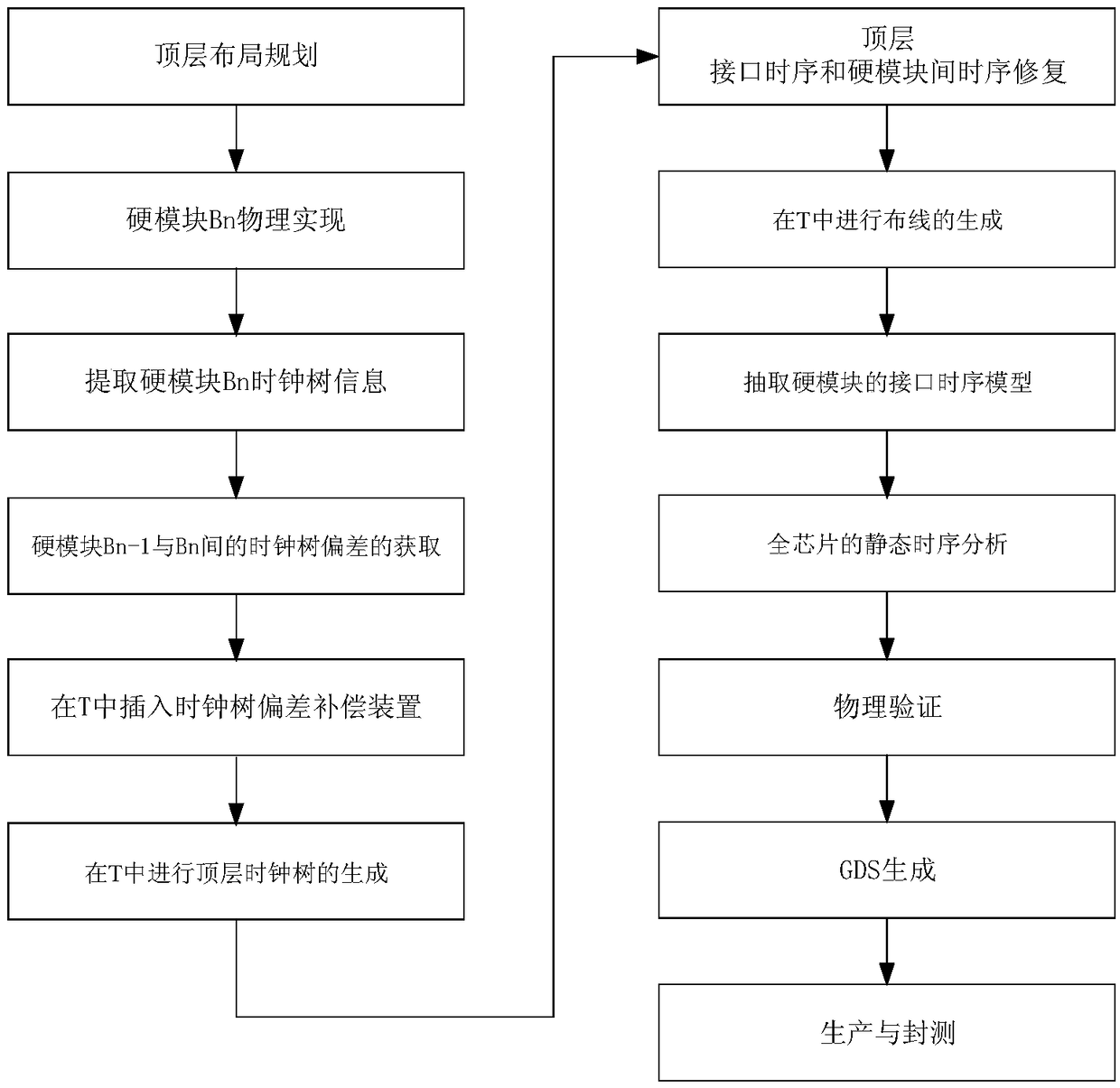

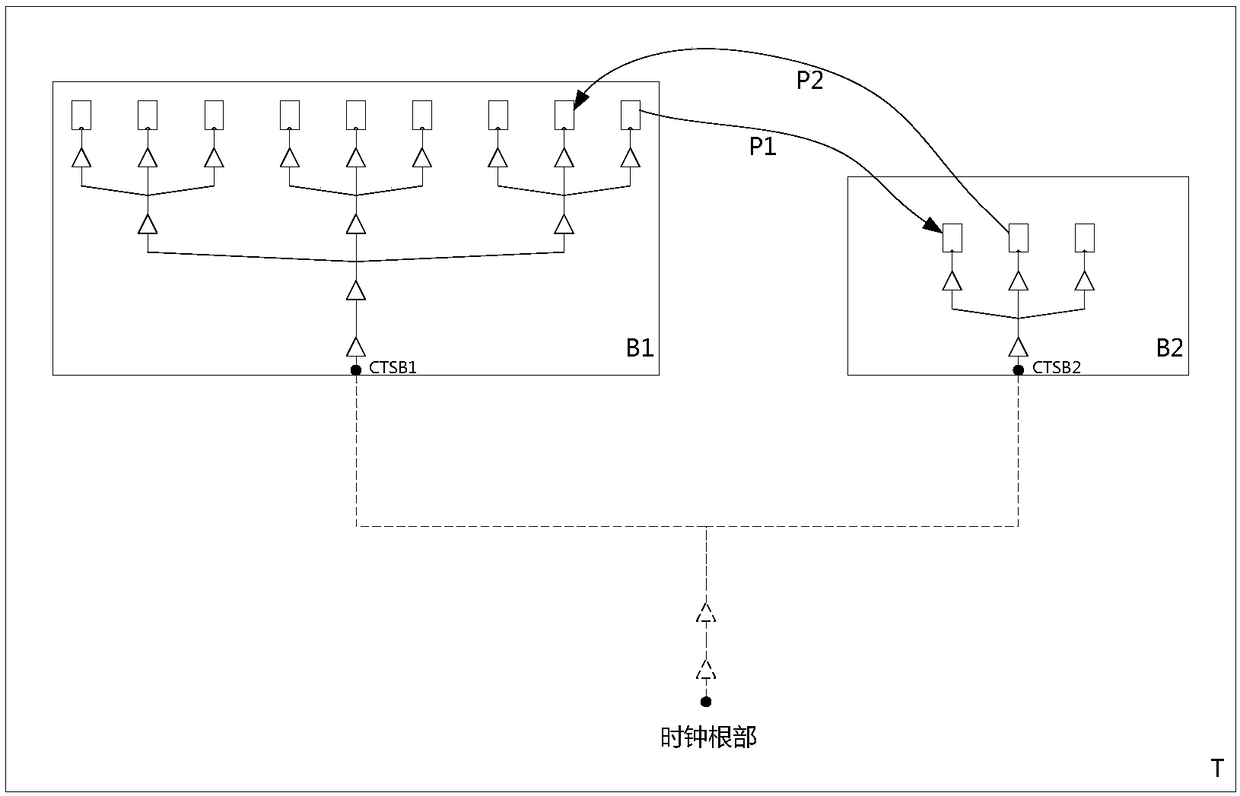

Clock-tree layout flow method and clock-tree deviation compensation device in integrate circuit

ActiveCN109376467AReduce hierarchyReduce difficultySpecial data processing applicationsStatic timing analysisPhysical verification

Owner:WUHAN INSTITUTE OF TECHNOLOGY

Popular searches

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap