Forming method of semiconductor structure, and semiconductor structure

A technology of semiconductor and isolation structure, applied in the field of semiconductor structure formation method and semiconductor structure, can solve the problems of occupying a large chip area and the shallow trench isolation structure cannot continue to shrink, and achieves the reduction of occupied area, size, and size. Effect of Trigger Voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

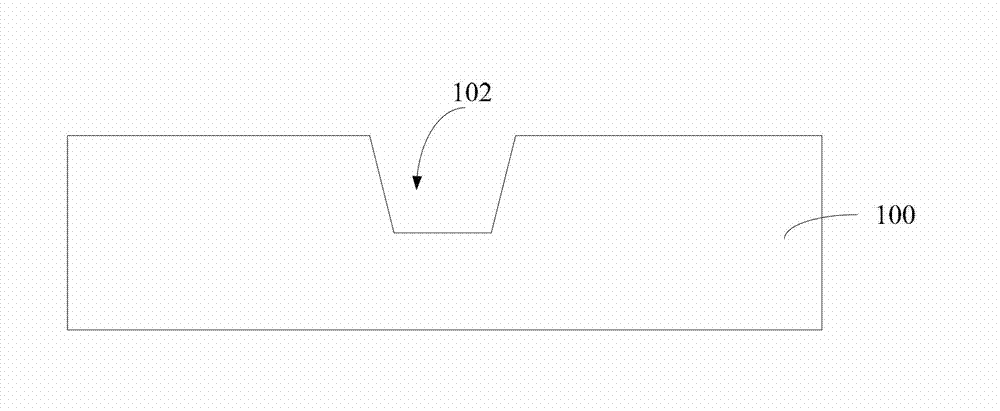

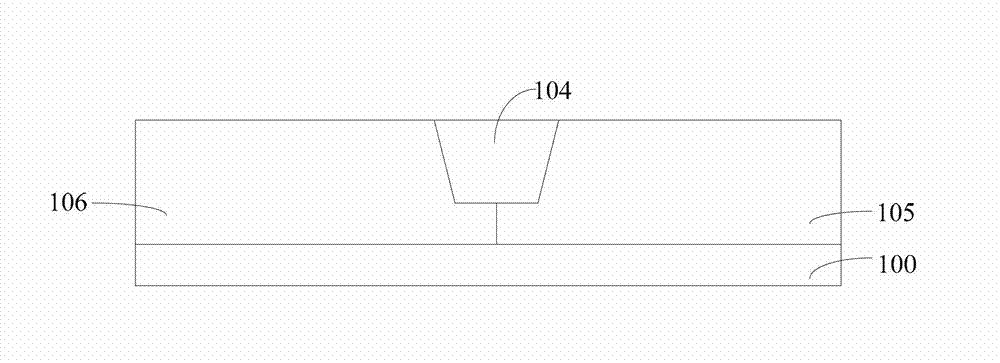

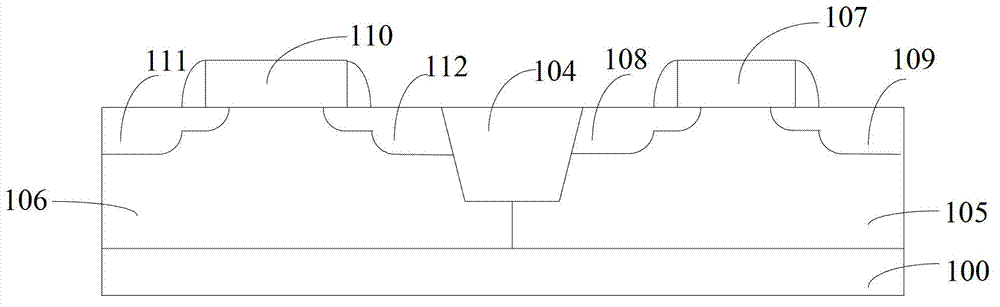

[0046] The inventors have found and analyzed that the reason why the shallow trench isolation structure in the prior art cannot continue to shrink and occupy a large area of the chip is as follows:

[0047] refer to image 3 , in the prior art, the holes in the P well region 106 will diffuse to the N well region 105, and the electrons in the N well region 105 will diffuse to the P well region 106. Therefore, the holes diffused to the N well region 105 and diffused to the P The electrons in the well region 106 will recombine at the bottom of the shallow trench isolation structure 104 to form a depletion region. When the device works, it is necessary to apply a voltage to the source and drain of the PMOS transistor and the NMOS transistor, and the width of the depletion region will increase under the effect of the applied voltage. If the size of the shallow trench isolation structure 104 is reduced at this time, it is equivalent to Narrowing the distance between the drain 112 of

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap