Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

64 results about "Dielectric layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In an embodiment, a dielectric layer is graded with respect to a crystalline structure profile across the dielectric layer. In an embodiment, a dielectric layer is formed by atomic layer deposition incorporating sequencing techniques to generate a doped dielectric material.

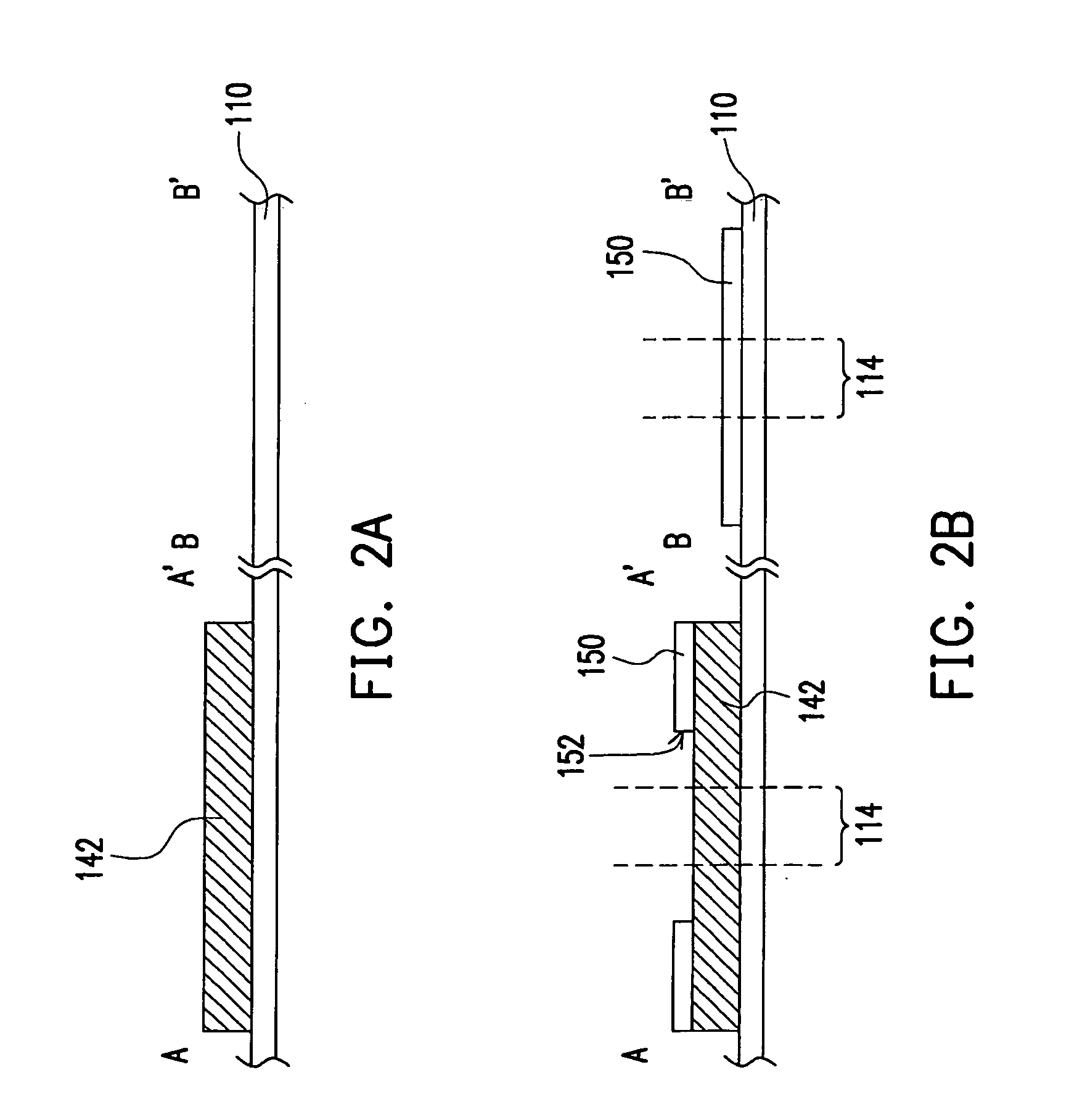

Flexure including a heat sink and a dielectric layer under trace termination pads

ActiveUS7567410B1Electrical connection between head and armRecord information storageEngineeringHeat sink

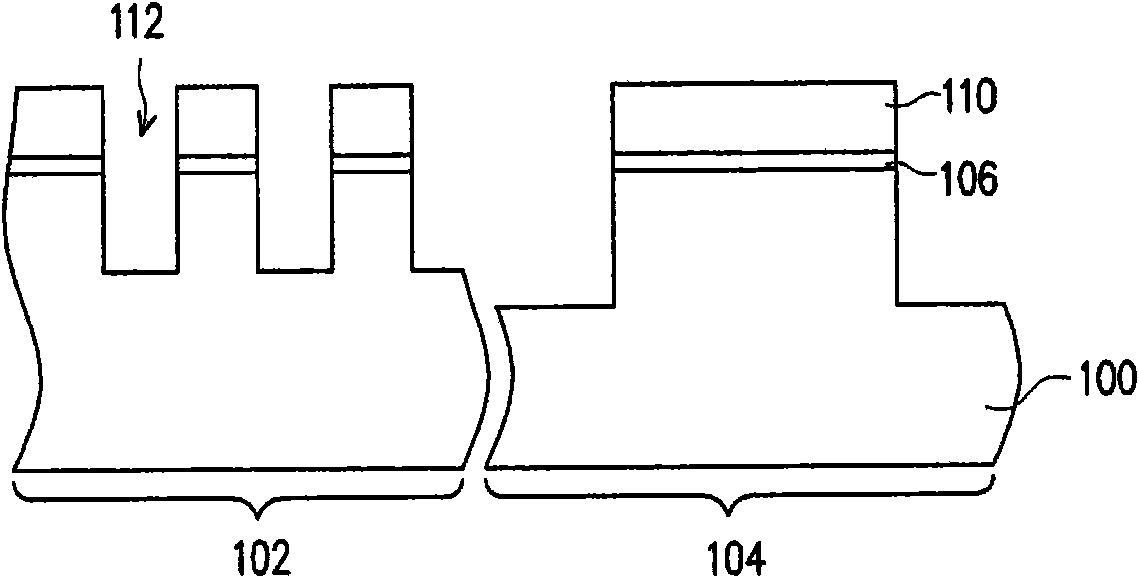

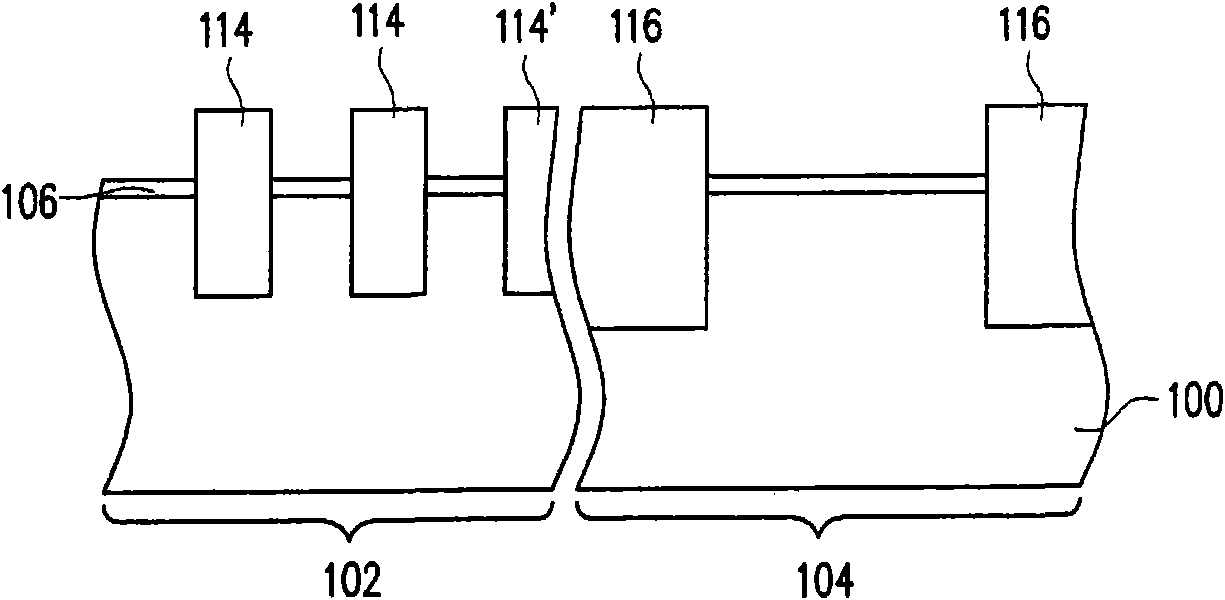

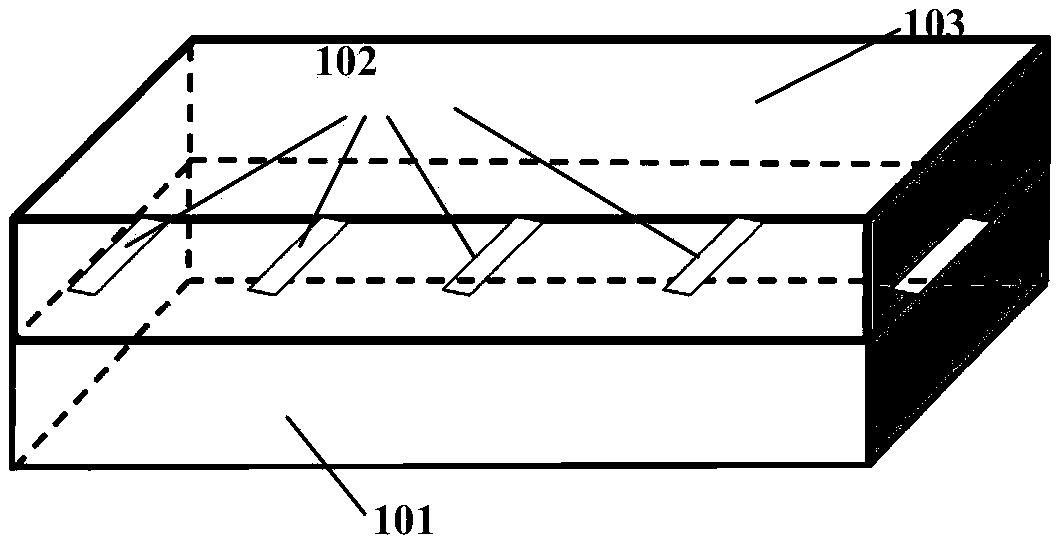

A flexure is provided for a HGA suspension. The flexure includes a metal base layer, a trace layer, and a dielectric layer disposed between the trace and base layers. The metal base layer includes a heat sink portion. The trace layer includes a plurality of conductive traces, each conductive trace having a curved section that terminates in a trace termination pad. The dielectric layer includes a portion that underlies the trace termination pads and overlies the heat sink portion. The base layer and the dielectric layer each also include a window. The curved section of each conductive trace extends over the window of the base layer. The curved section of each conductive trace may at least partially extend over the window of the dielectric layer.

Owner:WESTERN DIGITAL TECH INC

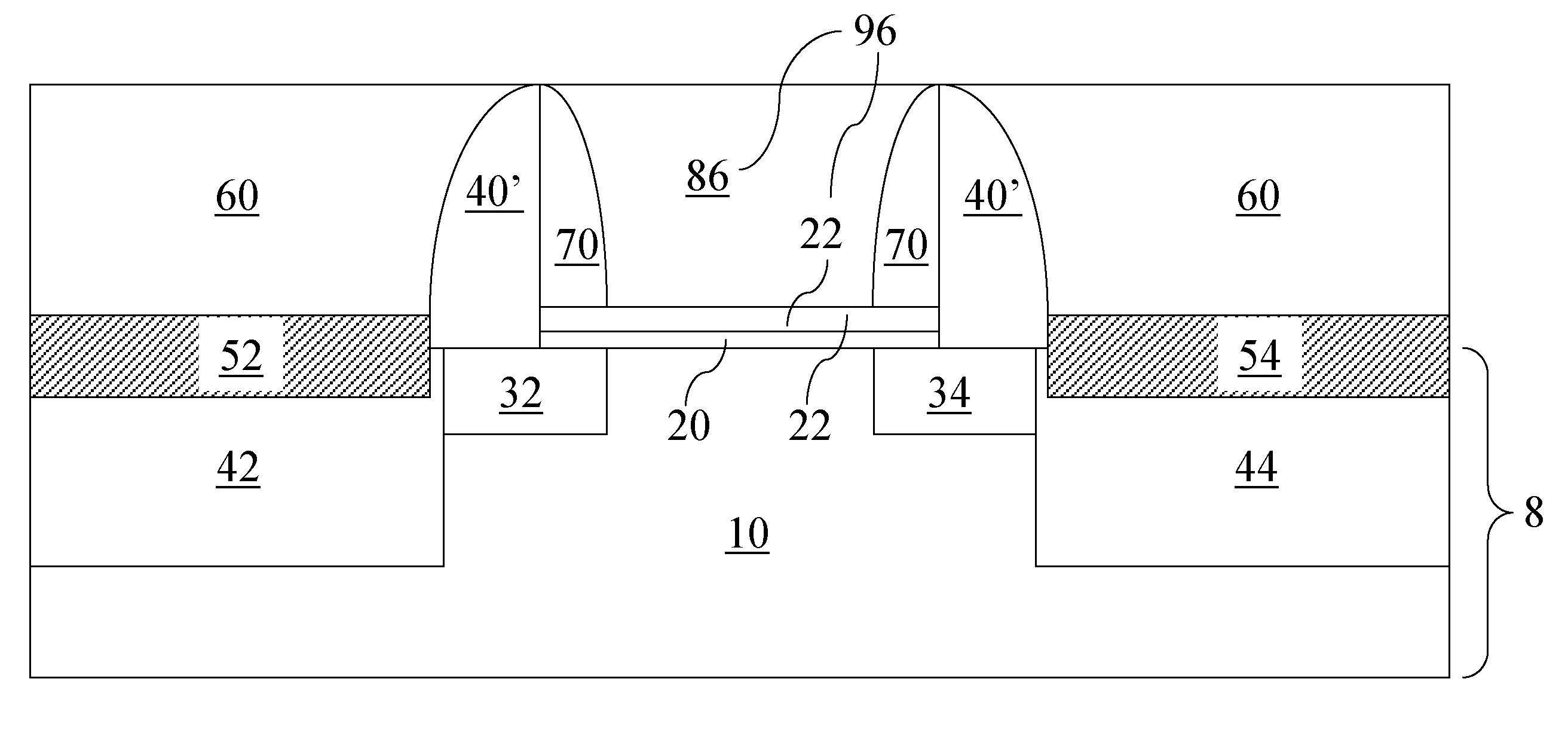

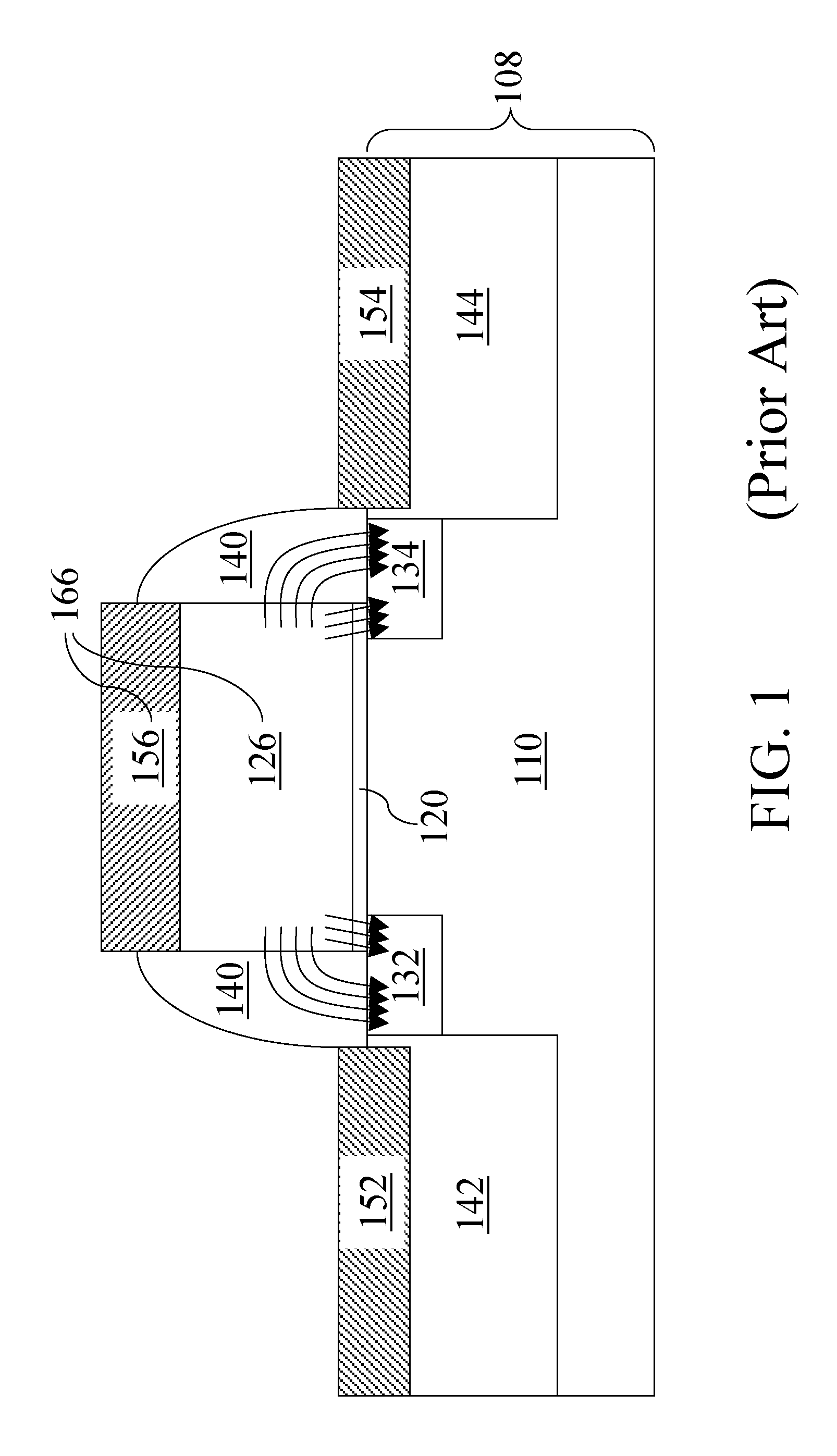

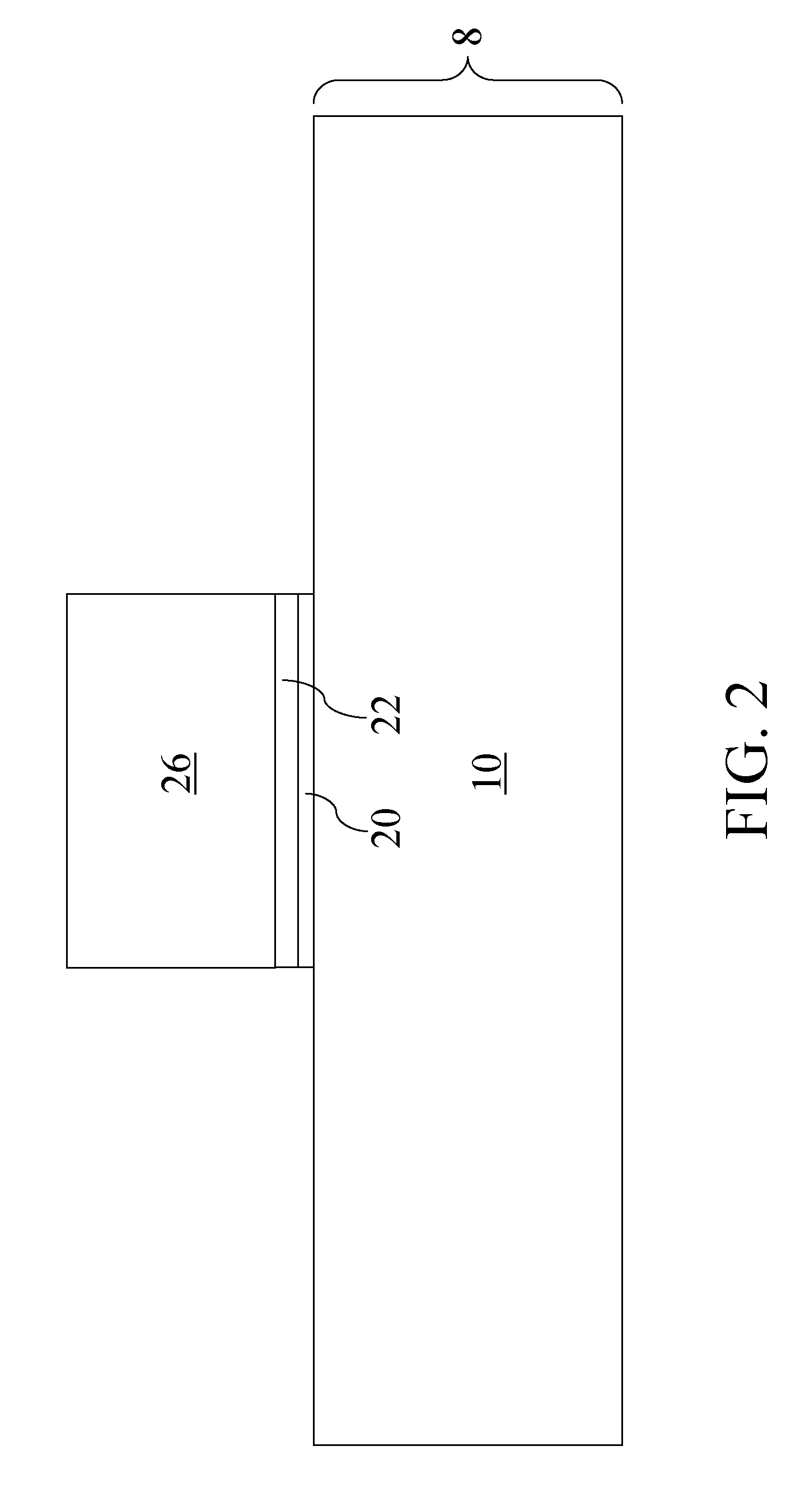

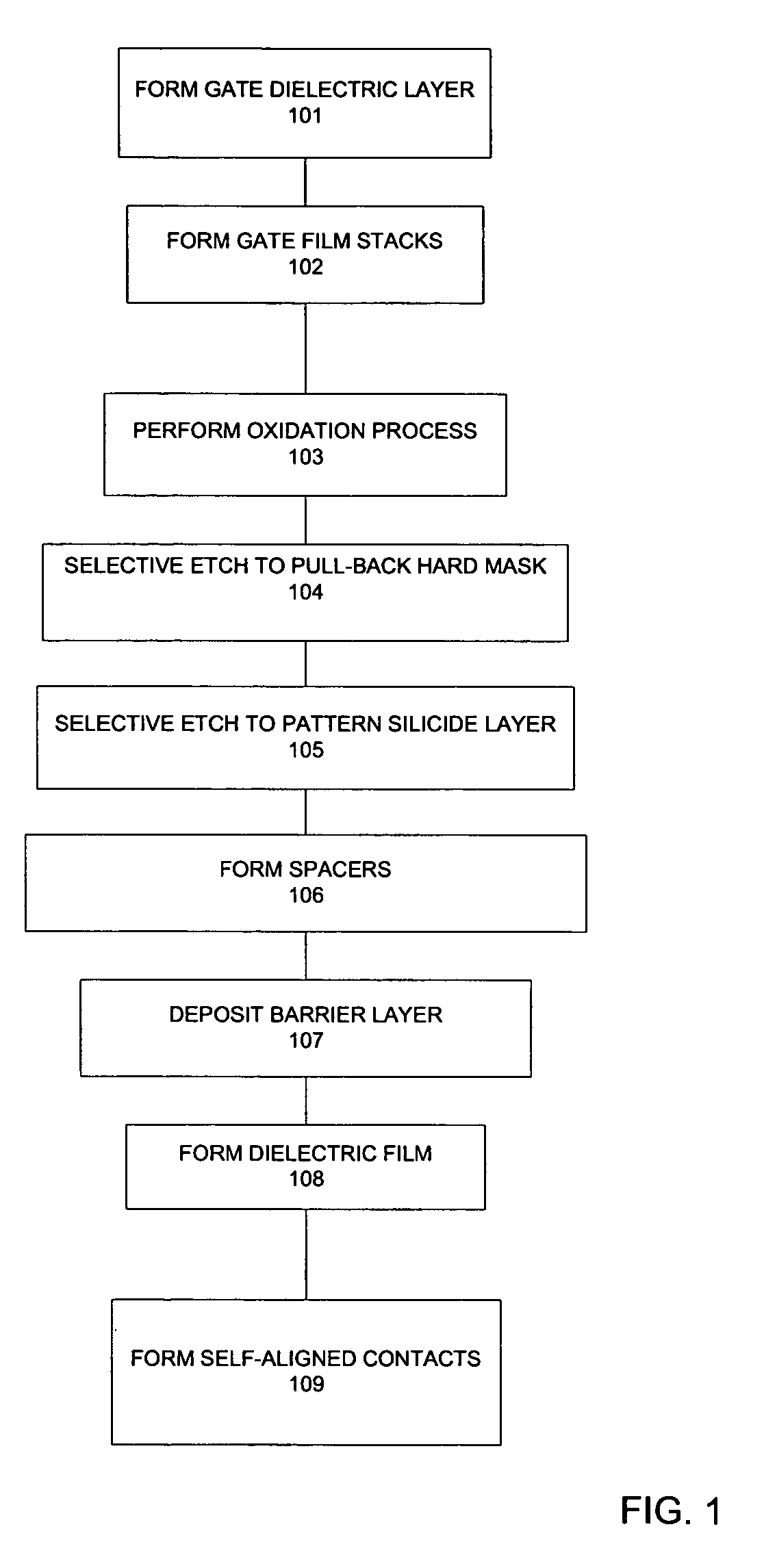

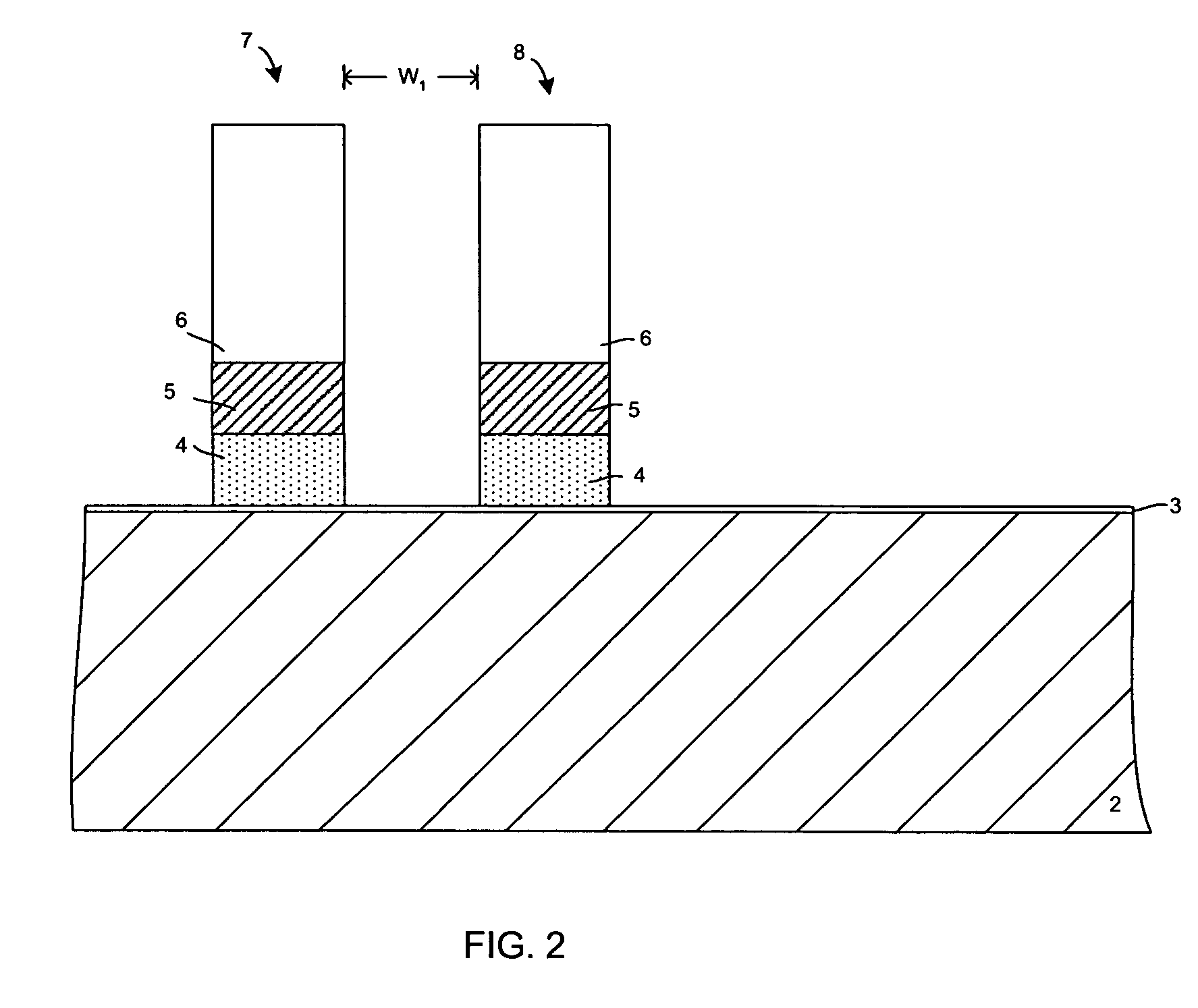

Field effect transistor with reduced overlap capacitance

InactiveUS20090212332A1Reduce Overlap CapacitanceTransistorSemiconductor/solid-state device manufacturingCapacitanceElectrical conductor

Owner:GLOBALFOUNDRIES INC

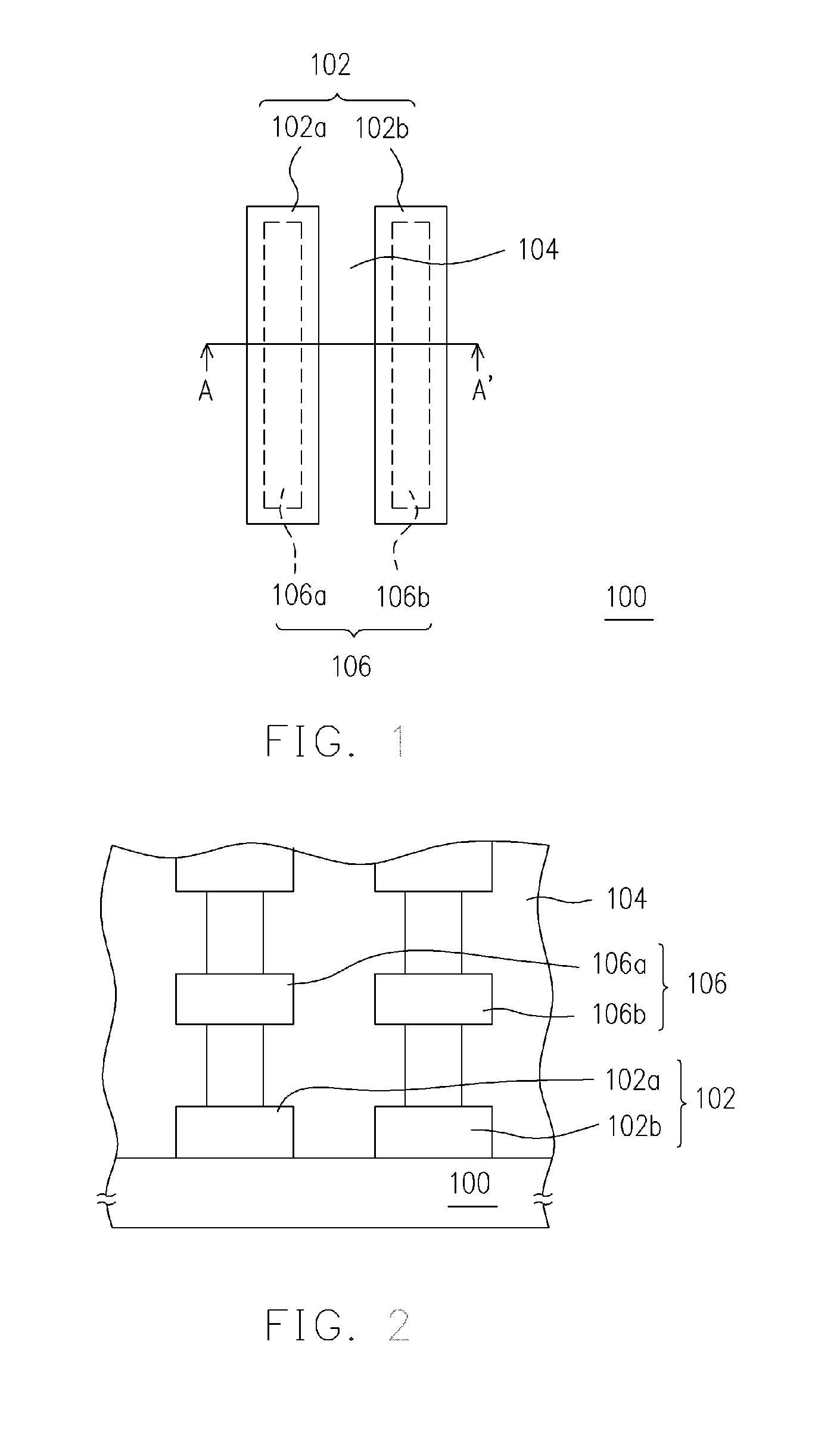

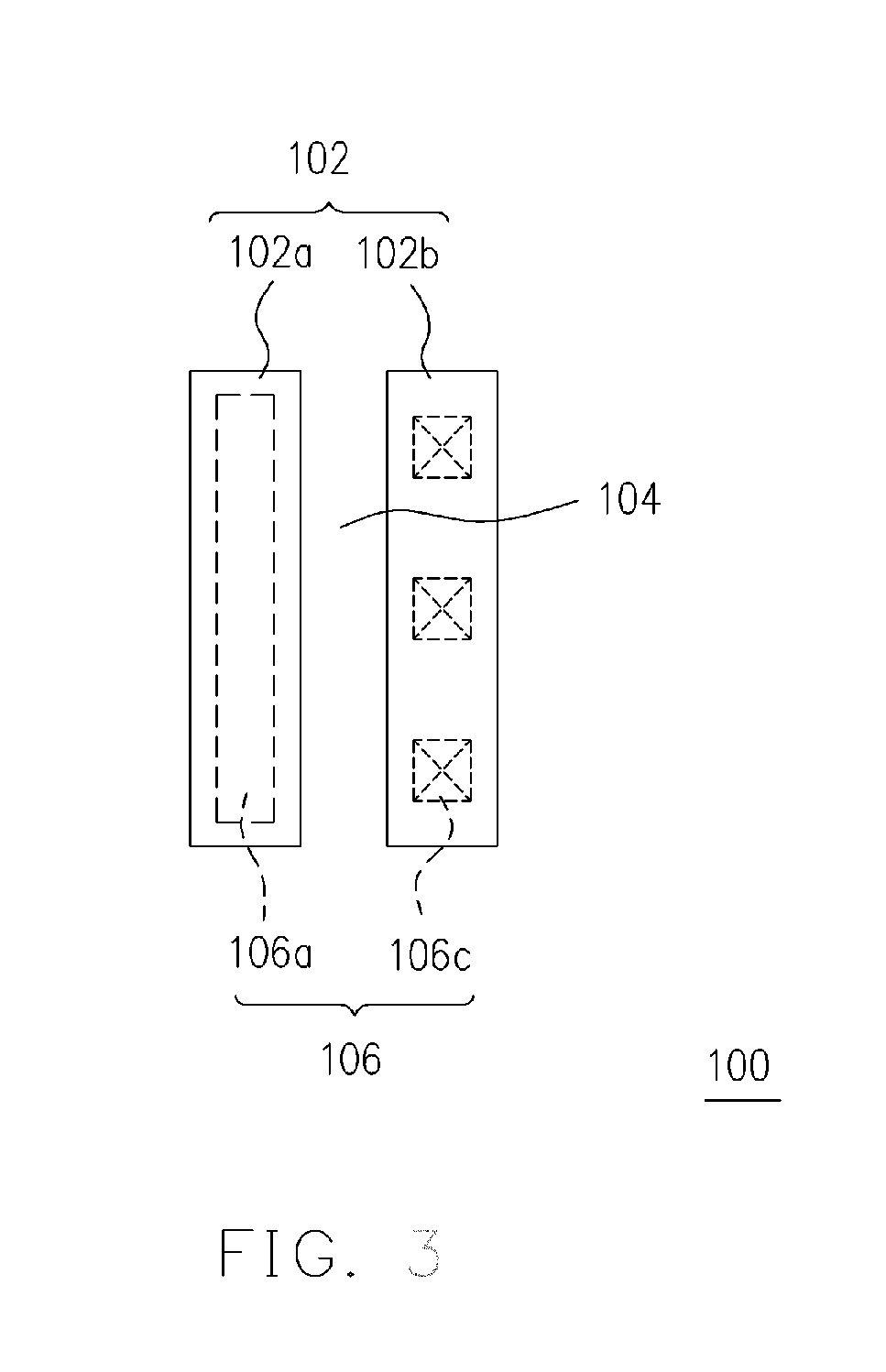

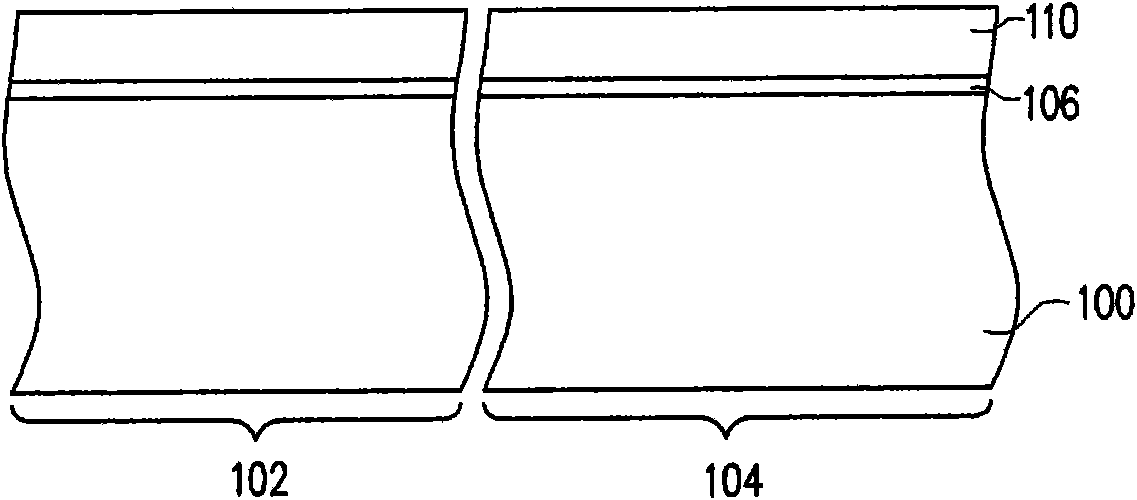

Antenna and method of making the same

ActiveUS20050264452A1Improve balanceSimultaneous aerial operationsAntenna supports/mountingsElectrical conductorLength wave

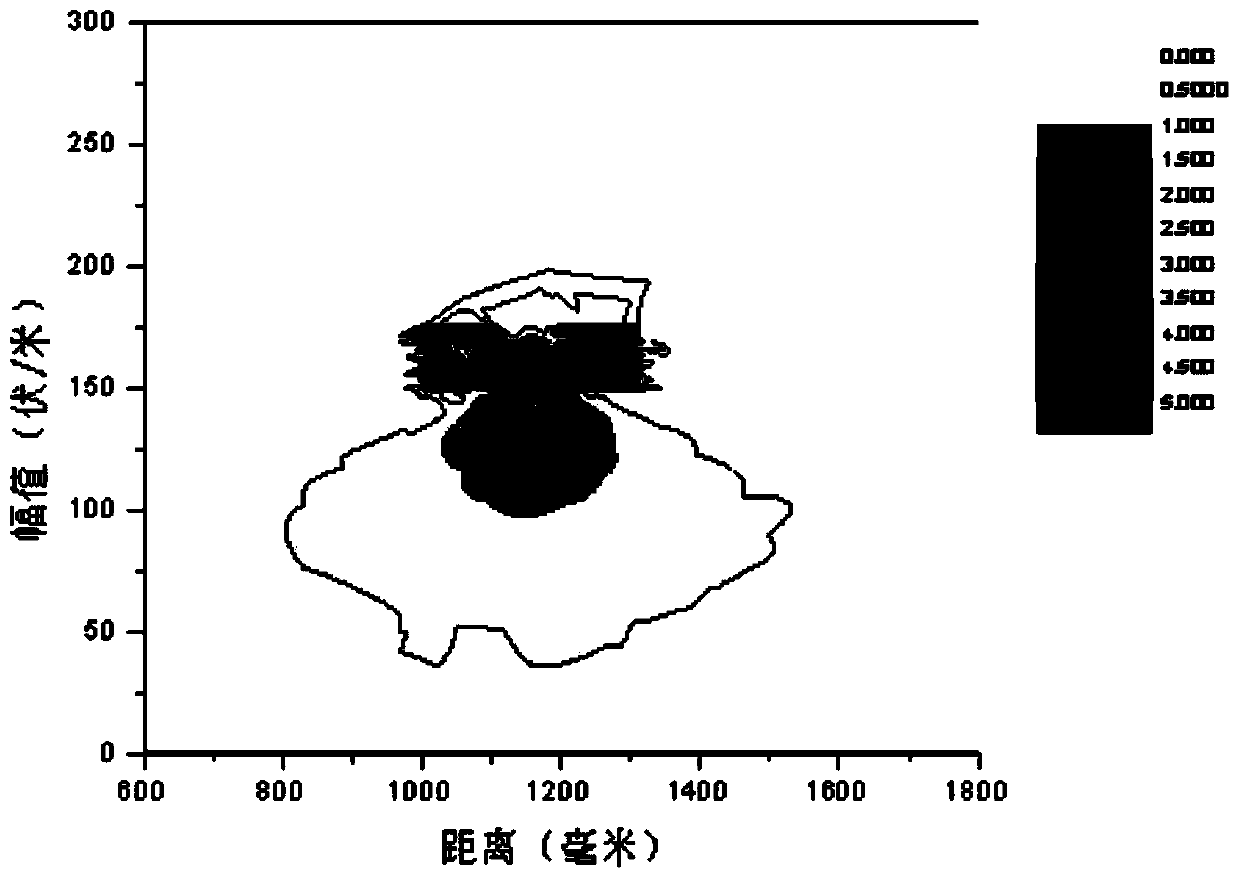

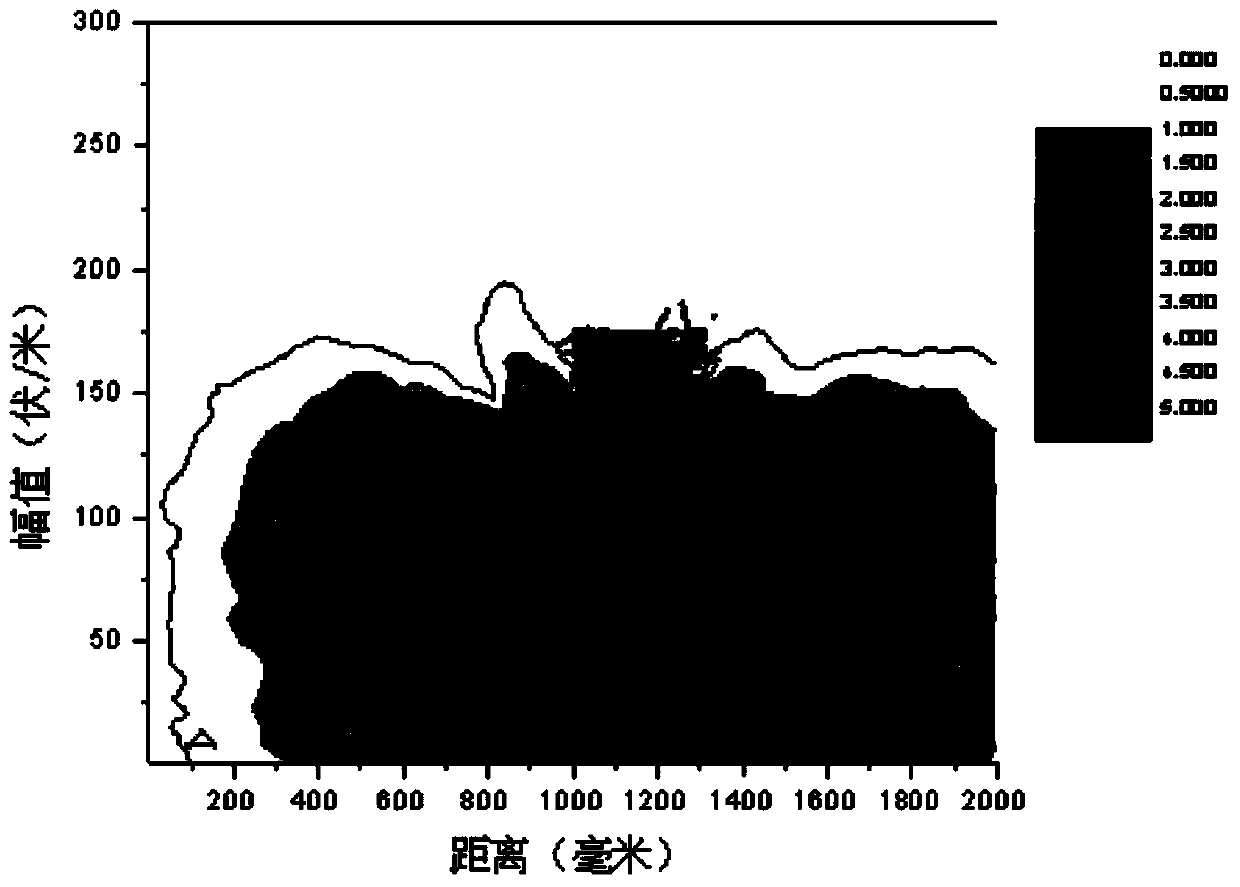

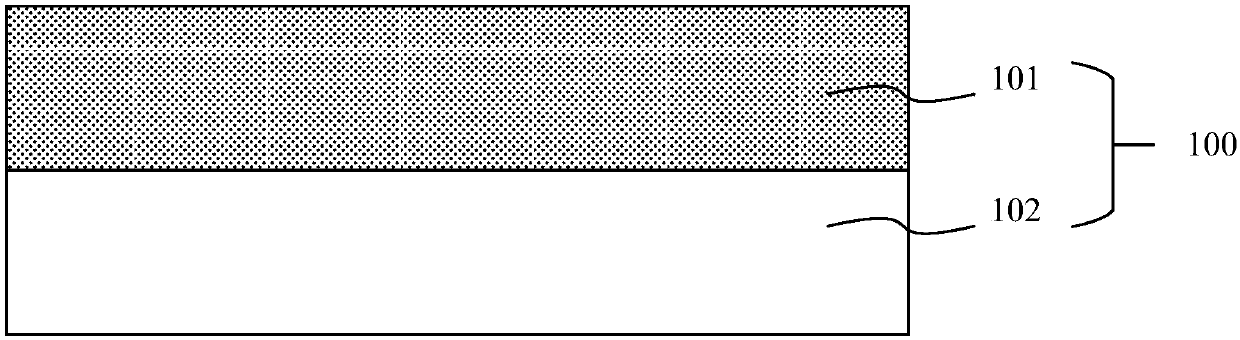

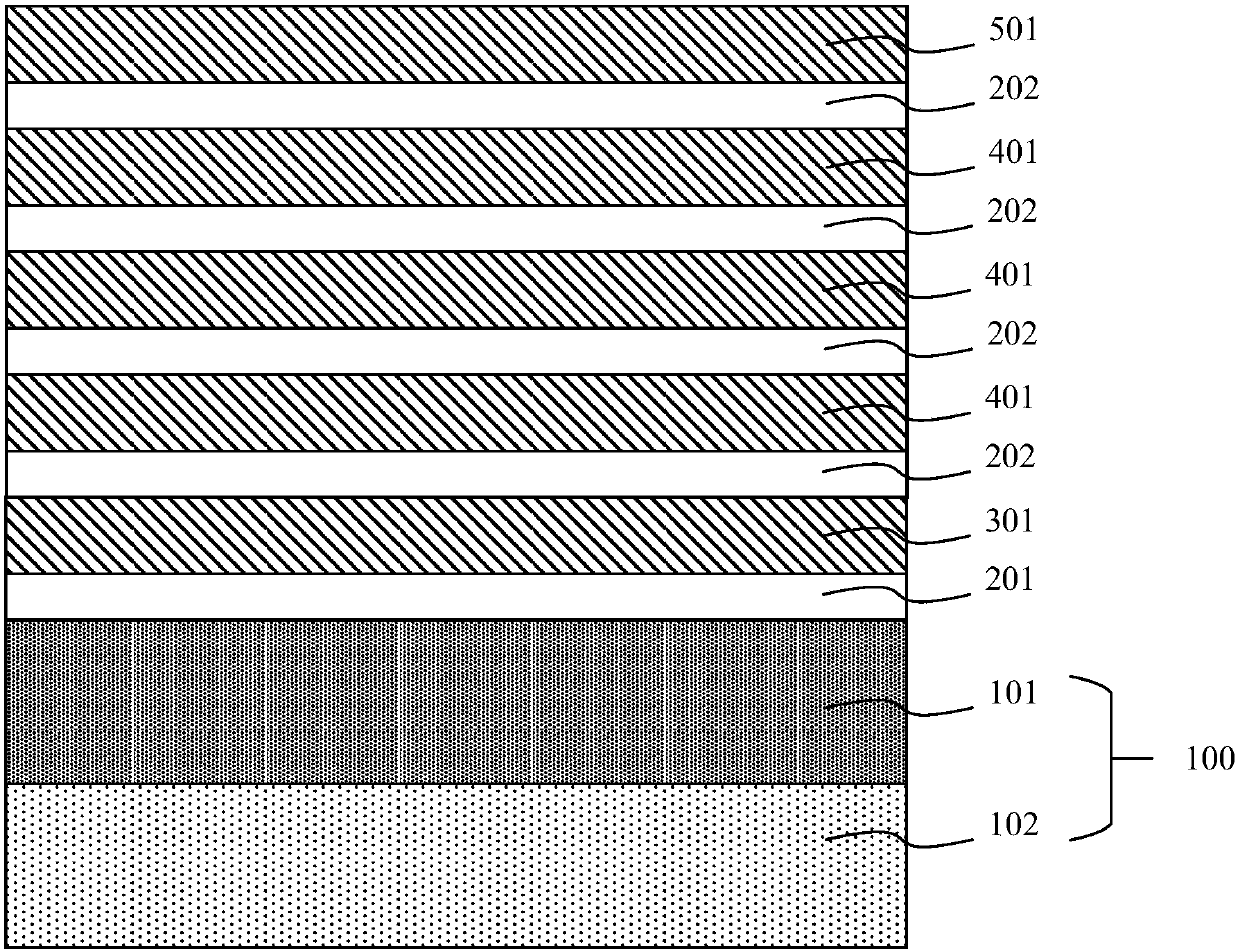

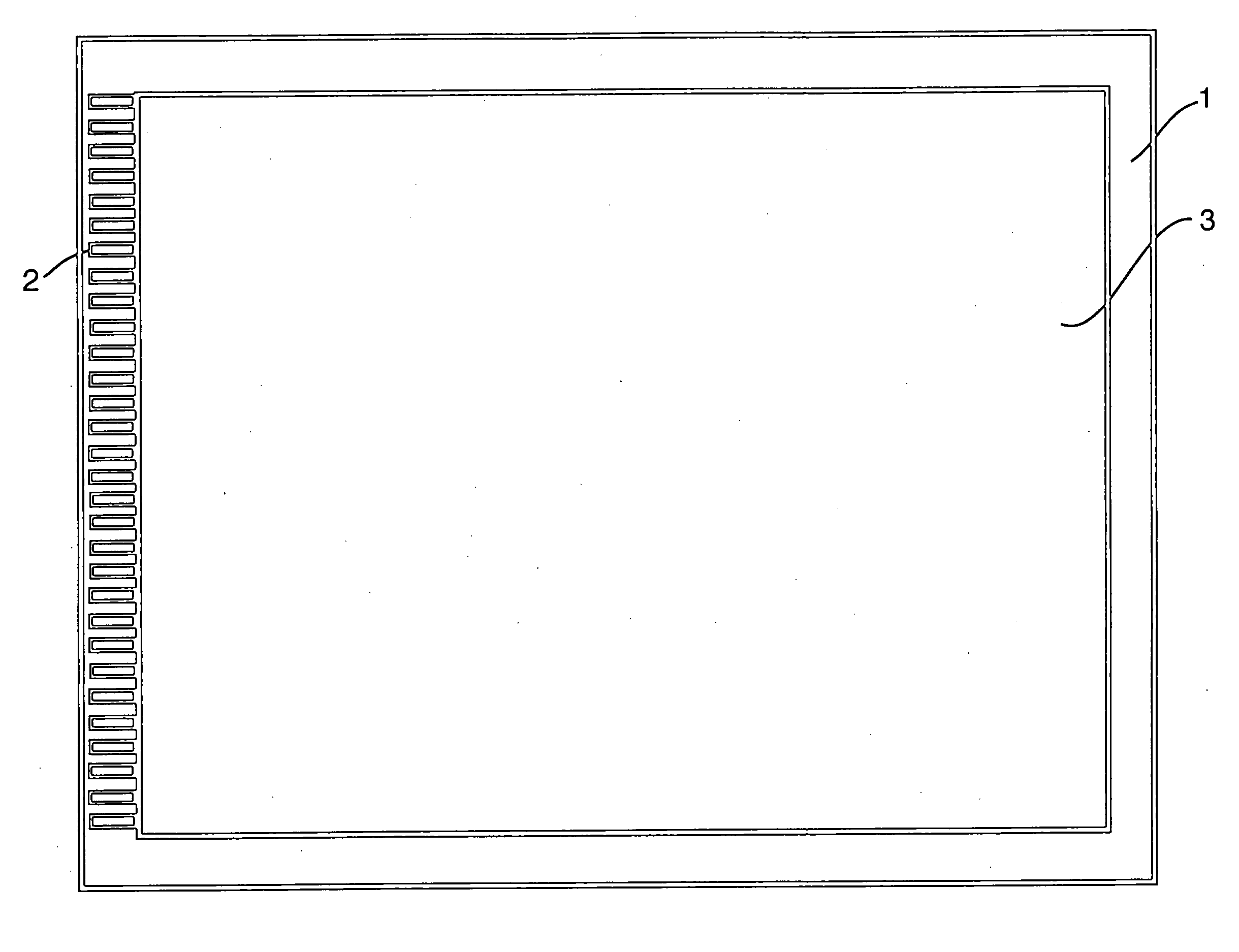

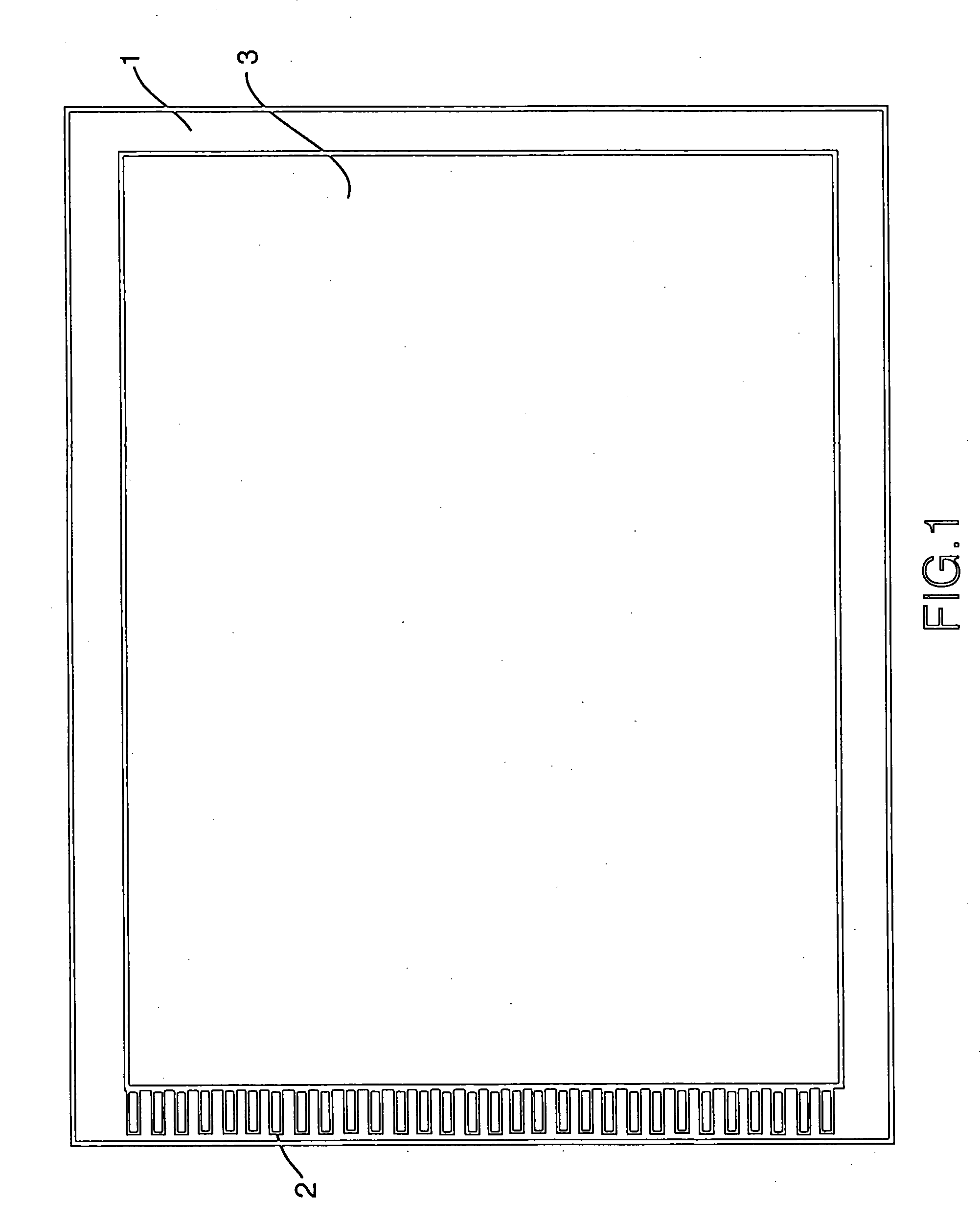

An antenna according to the present invention includes a dielectric layer 102 with an upper surface and a lower surface, a signal line strip 101 provided on the upper surface of the dielectric layer 102, and a grounding conductor portion 104 provided on the lower surface of the dielectric layer 102. The surface of the grounding conductor portion 104 includes a plurality of planar areas, each of which has a size that is shorter than the wavelength of an electromagnetic wave to transmit or receive. A distance from a virtual reference plane to each planar area is adjusted on an area-by-area basis. Thus, an antenna, which can change various antenna parameters such as radiation directivity, gain and efficiency dynamically and adaptively according to incessantly changing propagation environment of radio wave, is provided.

Owner:PANASONIC CORP

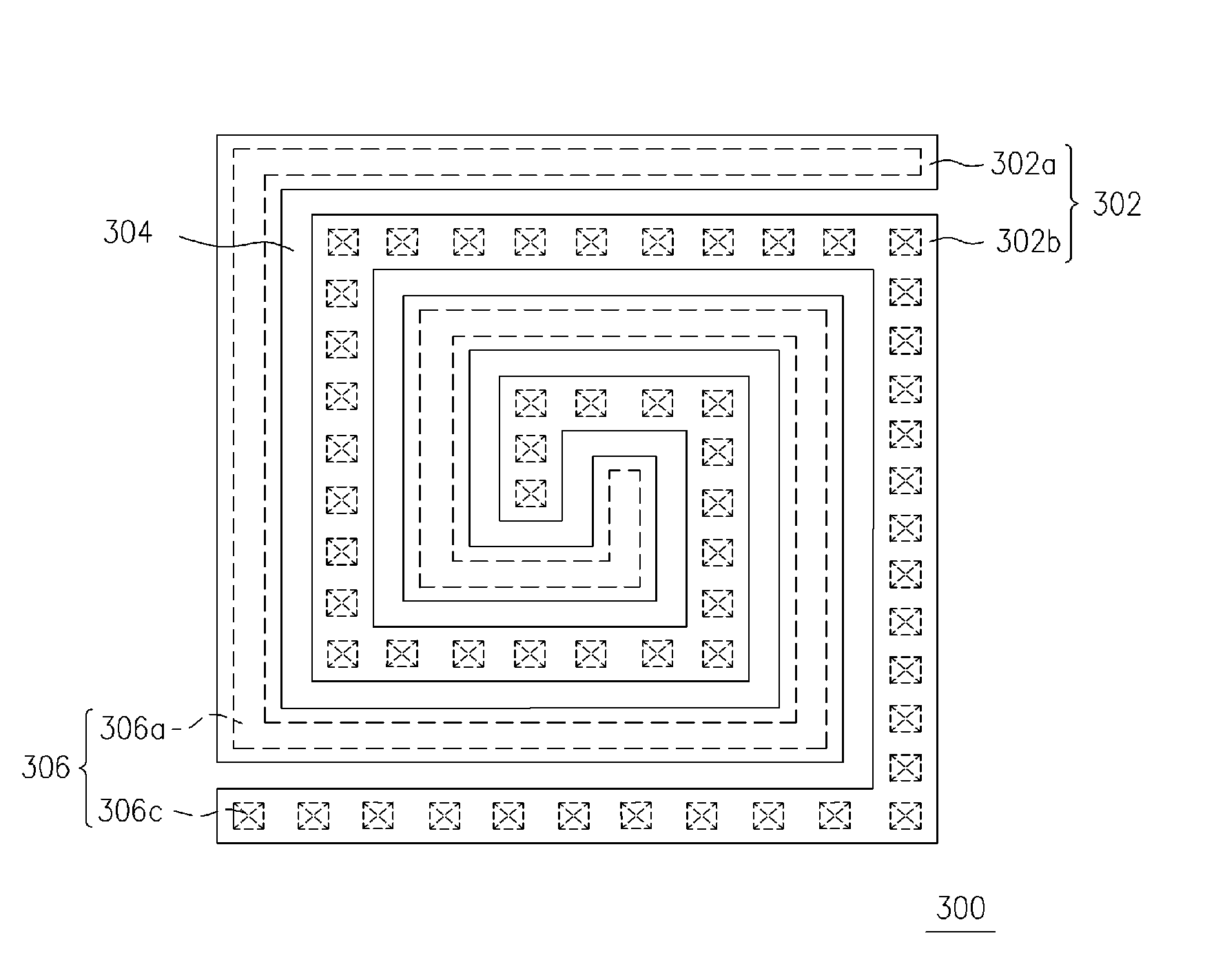

Capacitor structure

InactiveUS20070181973A1Semiconductor/solid-state device detailsSolid-state devicesElectrical and Electronics engineeringDielectric layer

Owner:UNITED MICROELECTRONICS CORP

Amorphous silicon image sensor with storage capacitor structure

ActiveCN102157533AIncreased charge storage capacityImprove signal dynamic rangeRadiation controlled devicesCapacitanceDynamic range

Owner:CARERAY DIGITAL MEDICAL TECH CO LTD

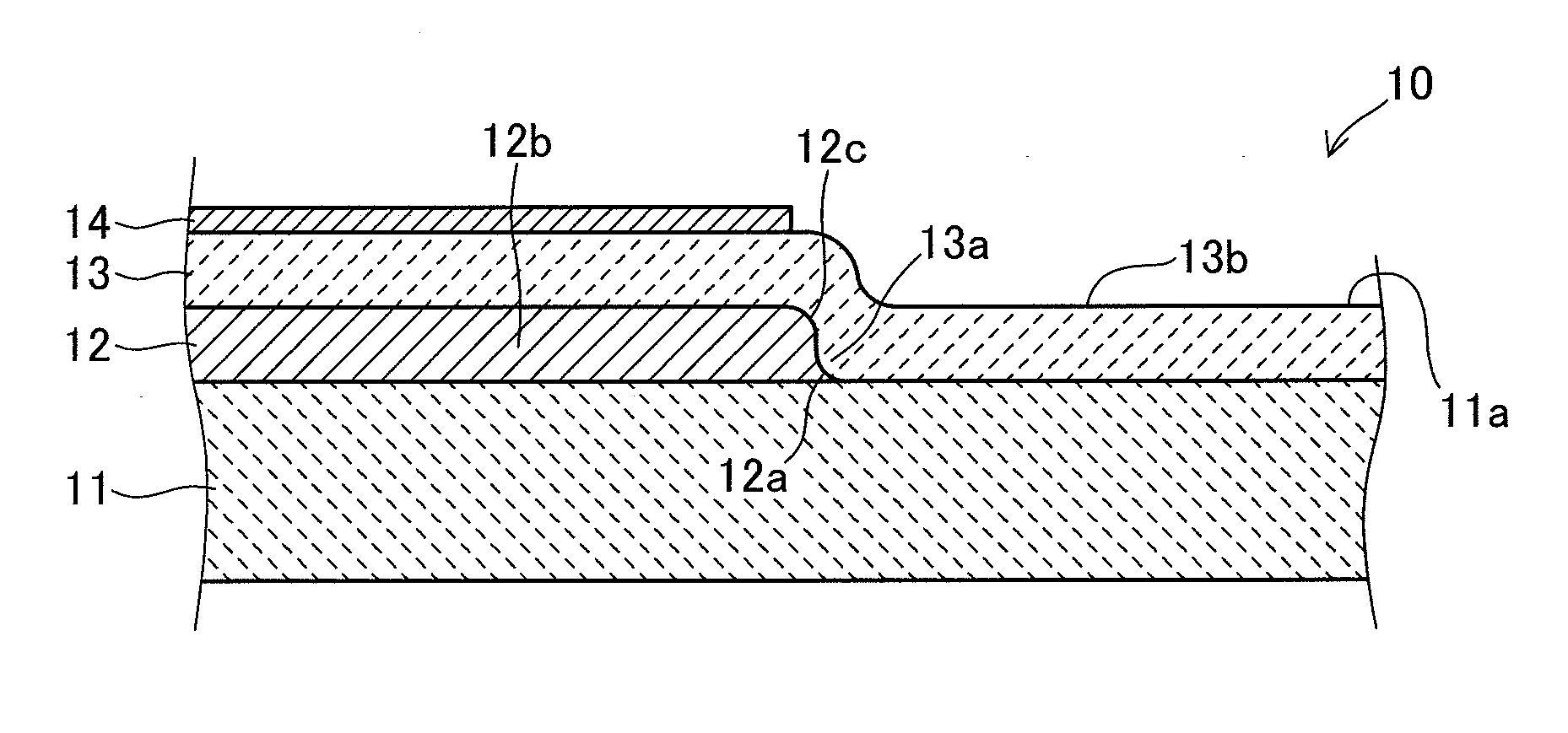

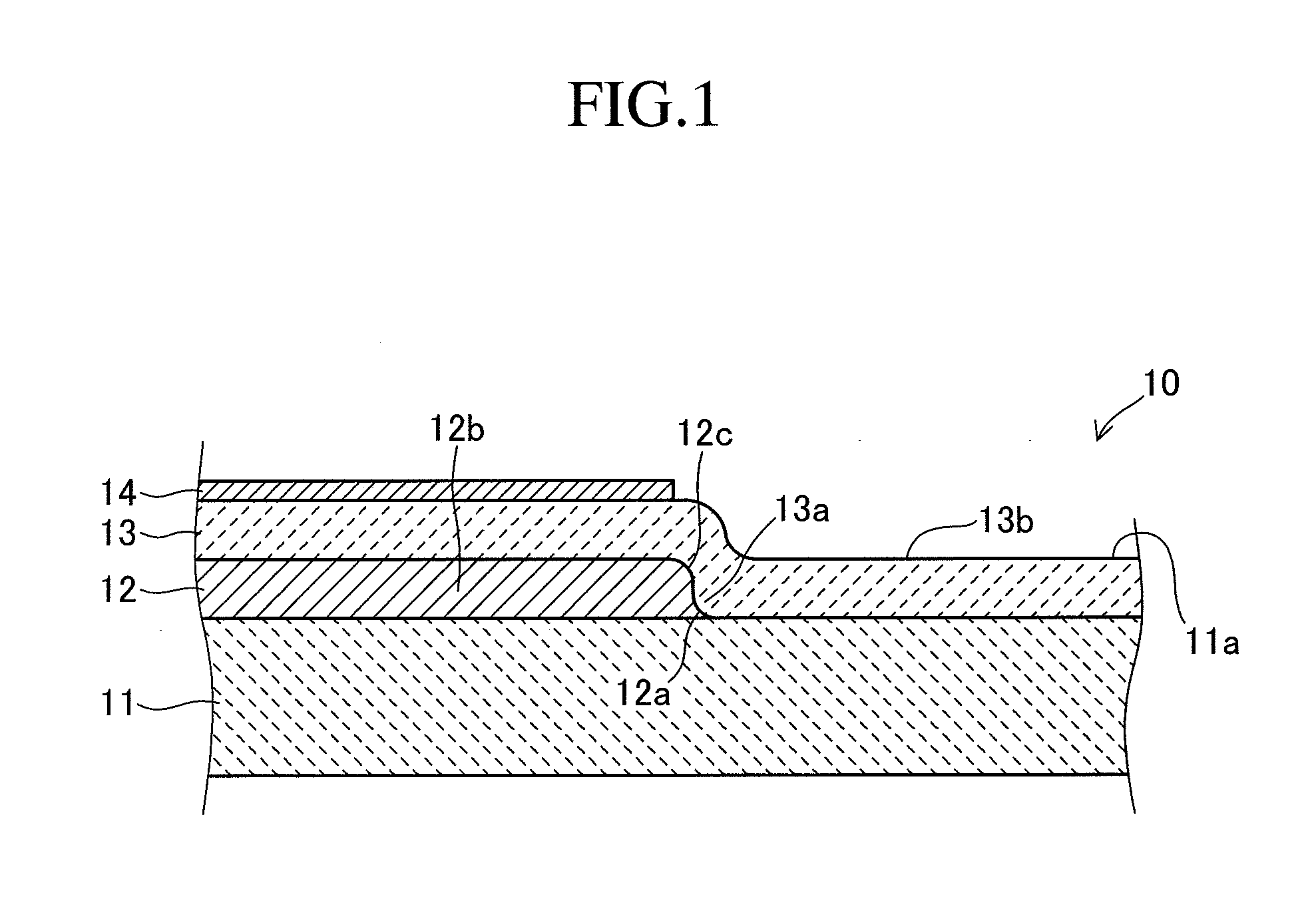

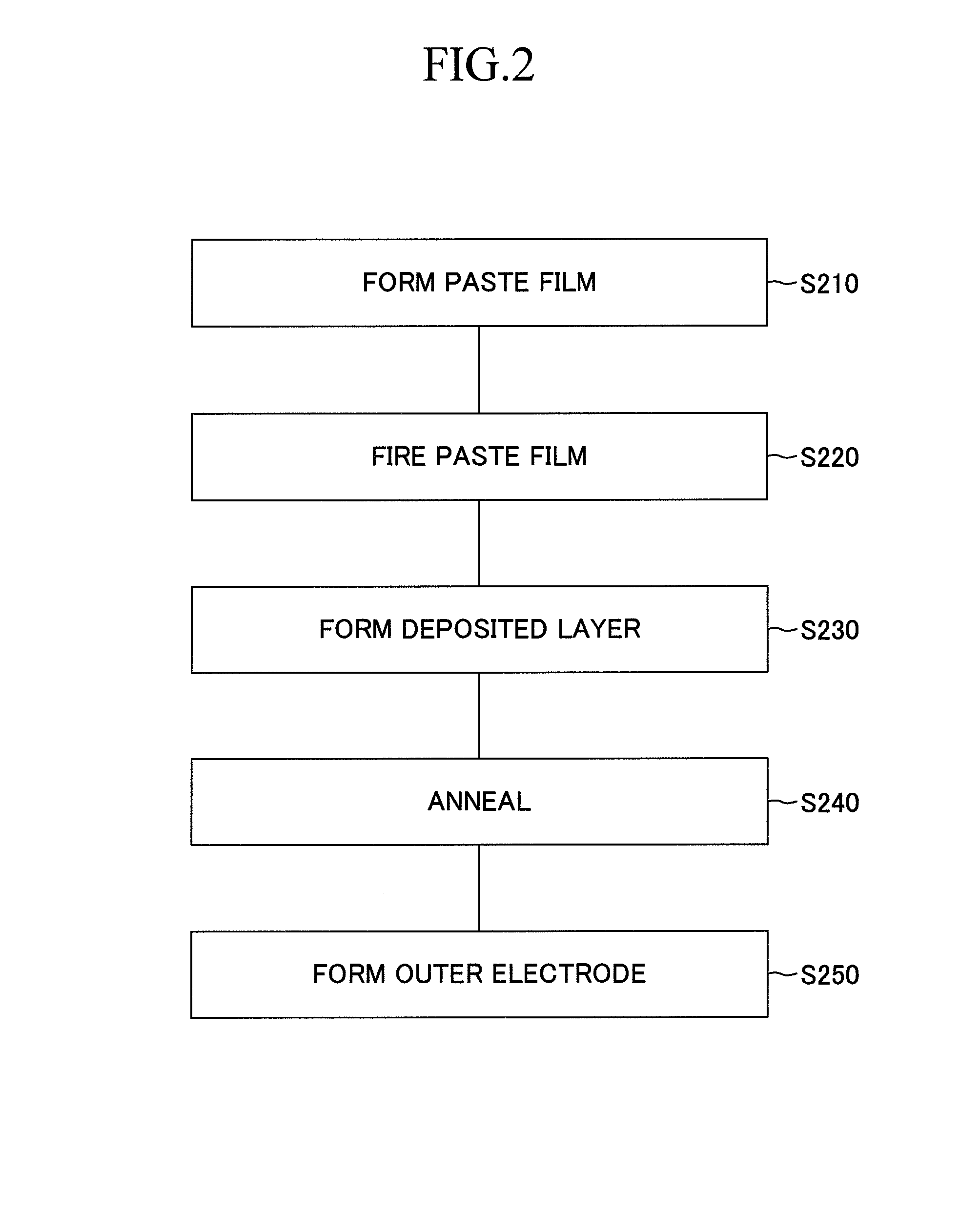

Variable capacitance element and tunable filter

ActiveUS20130342285A1Reduce size and thicknessSmall sizeImpedence networksCapacitor with voltage varied dielectricCapacitanceDielectric layer

A variable capacitance element includes a piezoelectric substrate, a buffer layer located on the piezoelectric substrate with an orientation, a dielectric layer located on the buffer layer and having a relative dielectric constant that varies in accordance with an applied voltage, and a first electrode and a second electrode arranged to apply an electric field to the dielectric layer.

Owner:MURATA MFG CO LTD

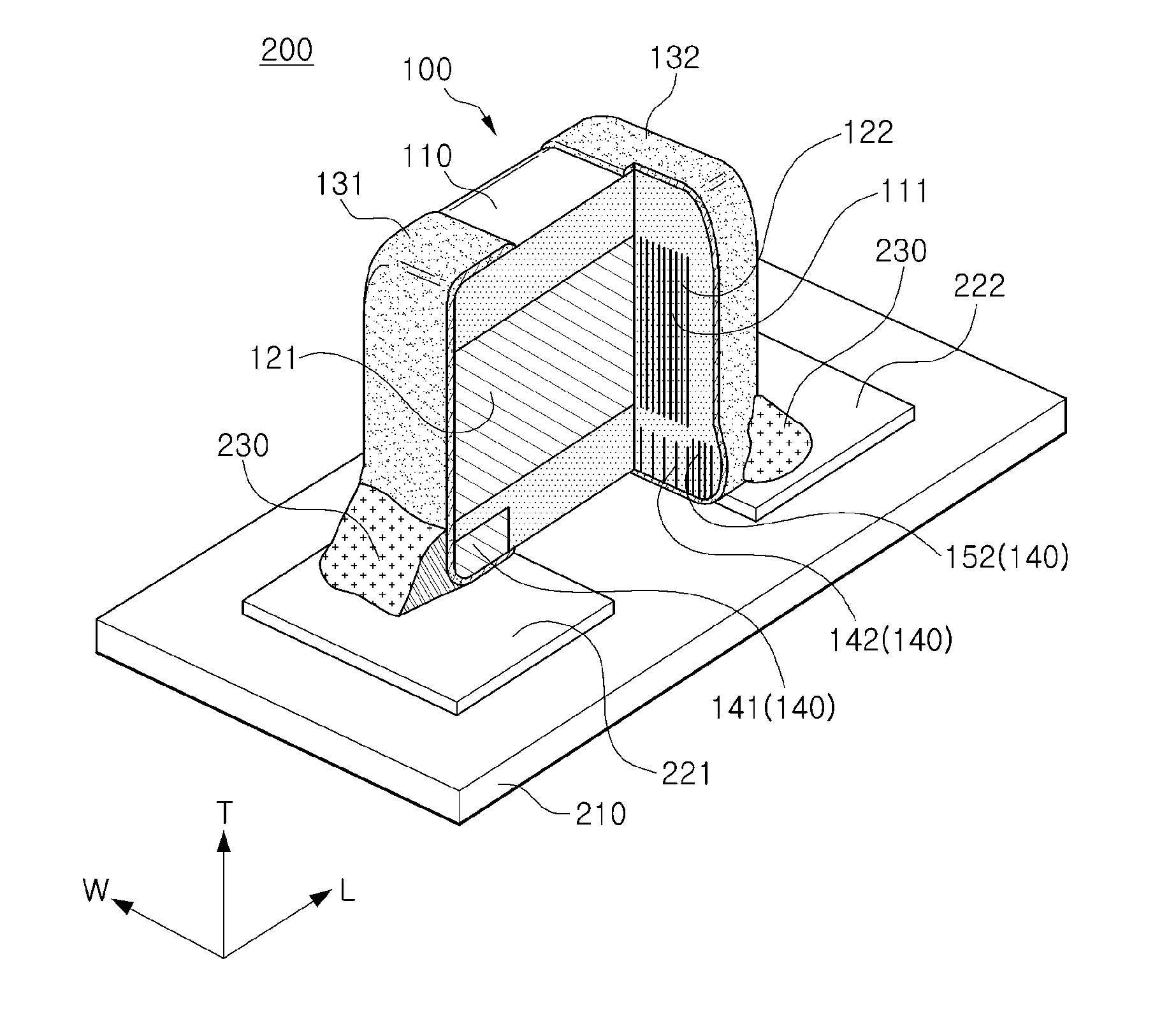

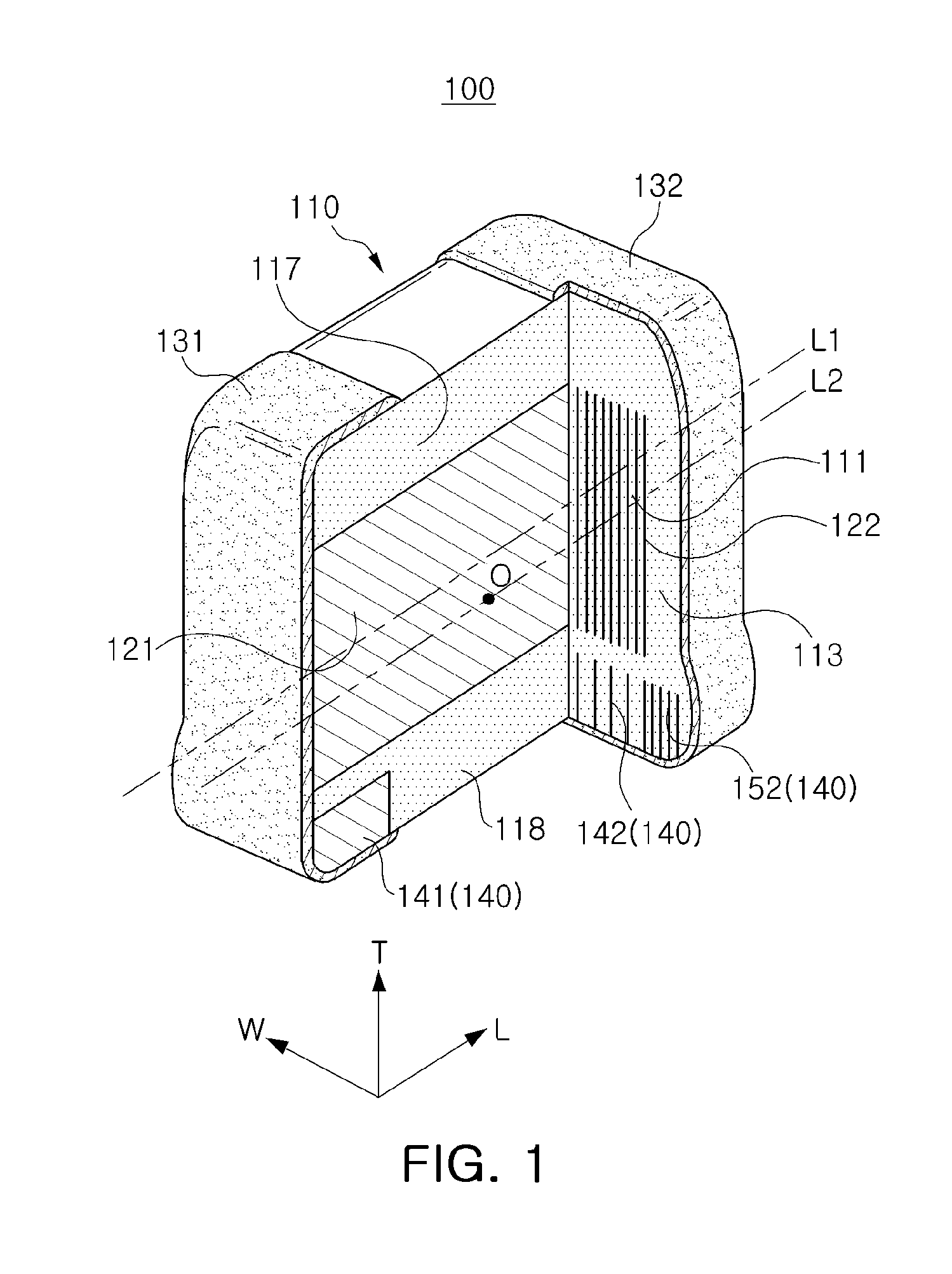

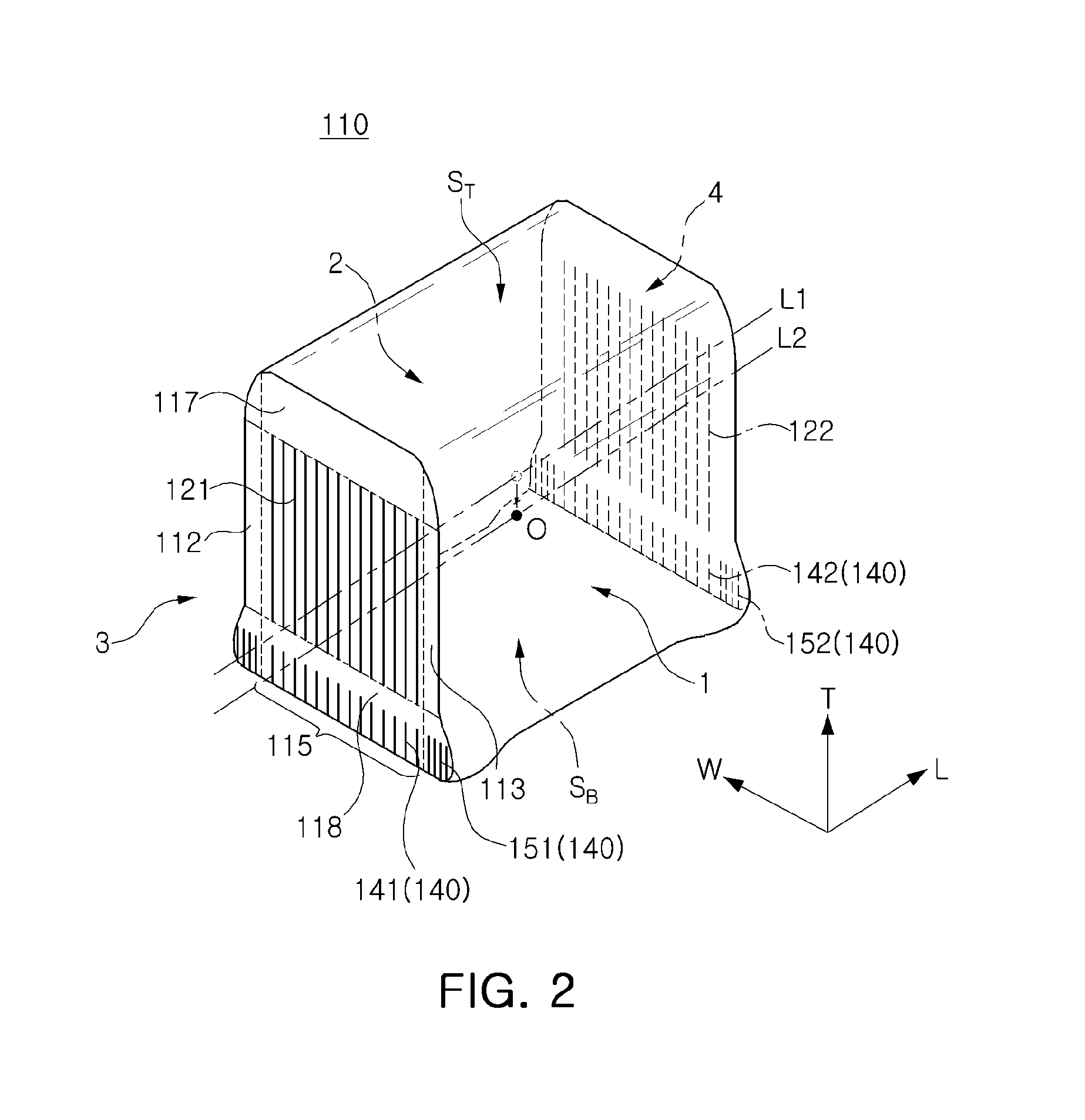

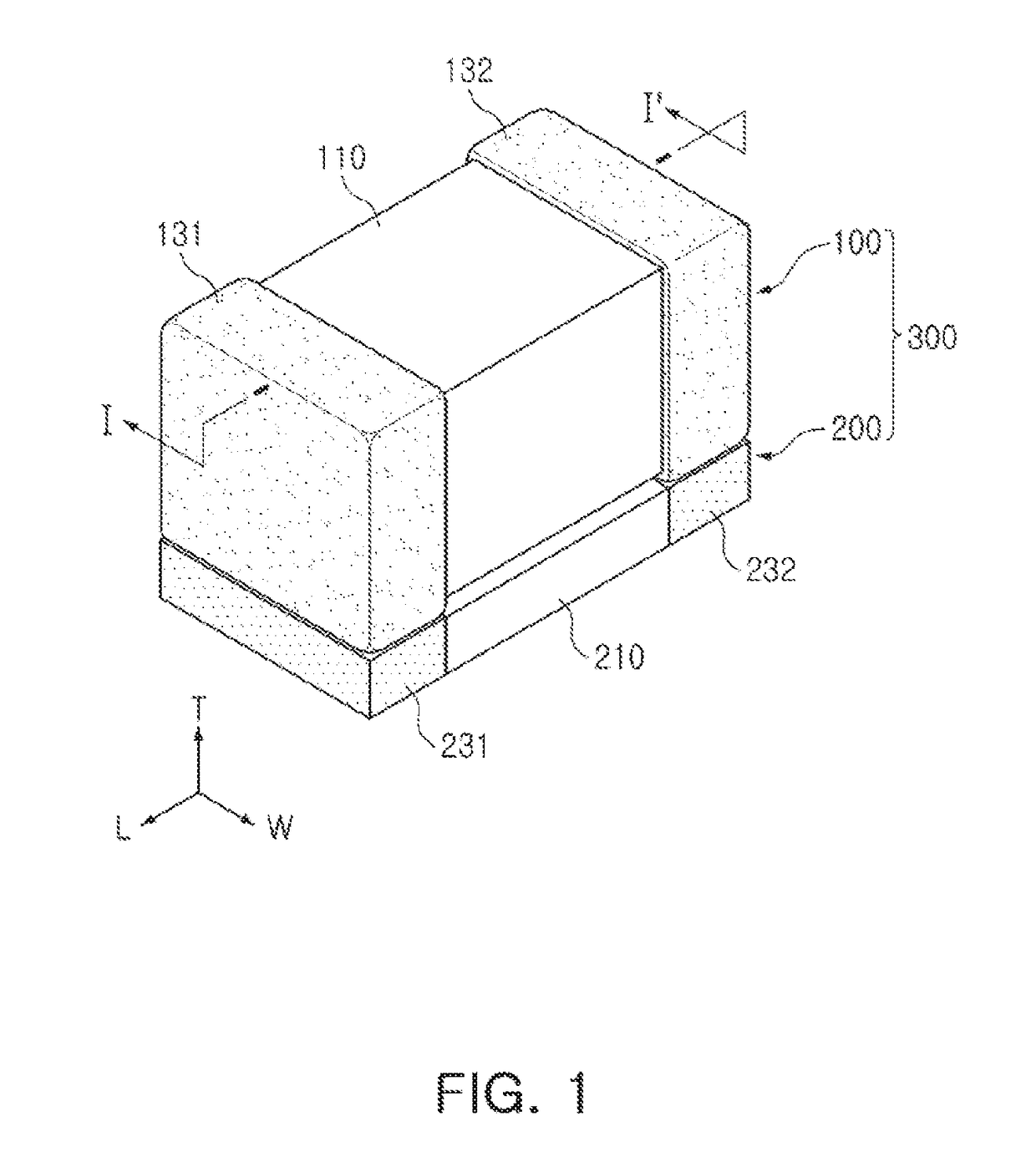

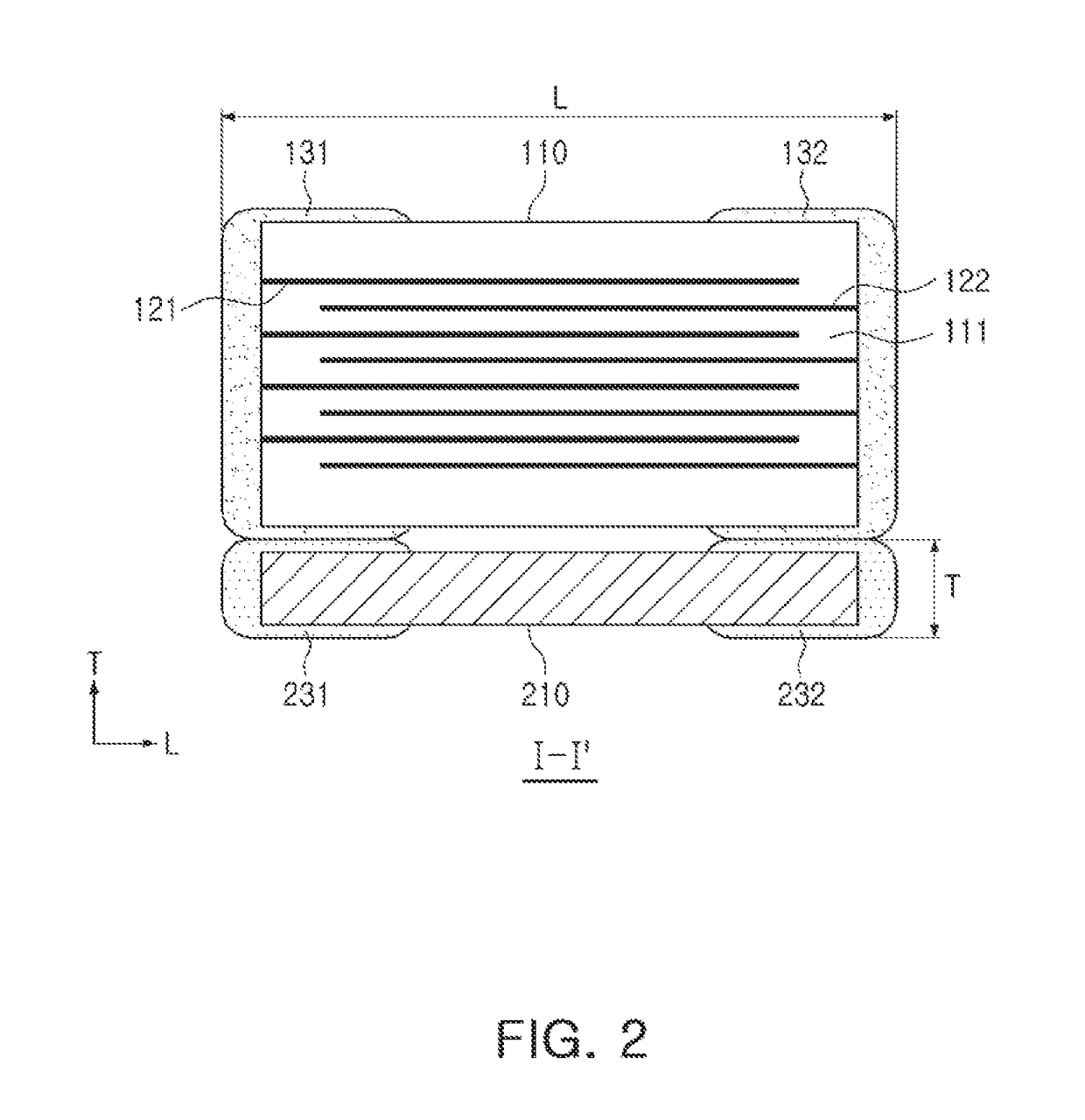

Multilayer ceramic electronic component and assembly board having the same

ActiveUS20150255213A1Fixed capacitor electrodesFixed capacitor dielectricDielectric layerElectronic component

The present application describes a multilayer ceramic electronic component including a ceramic body having a thickness greater than a width and includes a dielectric layers, and has upper and lower surfaces opposing each other in a thickness direction. First and second side surfaces oppose each other in a width direction, and first and second end surfaces oppose each other in a length direction. First and second internal electrodes are stacked with at least one of the dielectric layers interposed therebetween within the ceramic body in the width direction. A volume increasing part is disposed in a lower portion of the ceramic body in the thickness direction to allow a volume of a lower margin portion of the ceramic body to be greater than that of an upper margin portion thereof.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Multi-layer multi-chip fan-out structure and manufacturing method

ActiveCN103594451ALow costPackage Size OptimizationSemiconductor/solid-state device detailsSolid-state devicesSolder maskInterconnection

The invention provides a multi-layer multi-chip fan-out structure. The multi-layer multi-chip fan-out structure comprises a bearing plate, and a plurality of packaging sub bodies which are stacked are arranged on the bearing plate; at least one die is packaged into each packaging sub body; in each packaging sub body, the die is coated by a dielectric material of a dielectric layer, and the die is attached to a metal cushion block with the front face faces upwards; an RDL layer is arranged on the dielectric layer of each packaging sub body; a bonding pad of the front face of each die is electrically connected with the RDL layer of the corresponding packaging sub body where the die exists; insulating layers are arranged between adjacent packaging sub bodies, and the RDL layers of the adjacent packaging sub bodies are electrically connected through second interconnection holes between the layers. The metal cushion blocks in the bottom packaging sub bodies are pressed on the surface of the bearing plate, and the metal cushion blocks in the middle or top packaging sub bodies are pressed on the insulating layers of the packaging sub bodies; the surface of each top packaging sub body is provided with a solder mask layer in a distributed mode. According to the multi-layer multi-chip fan-out structure, three-dimensional multi-chip stacking can be easily achieved.

Owner:JIANGSU CAS MICROELECTRONICS INTEGRATION TECH CO LTD

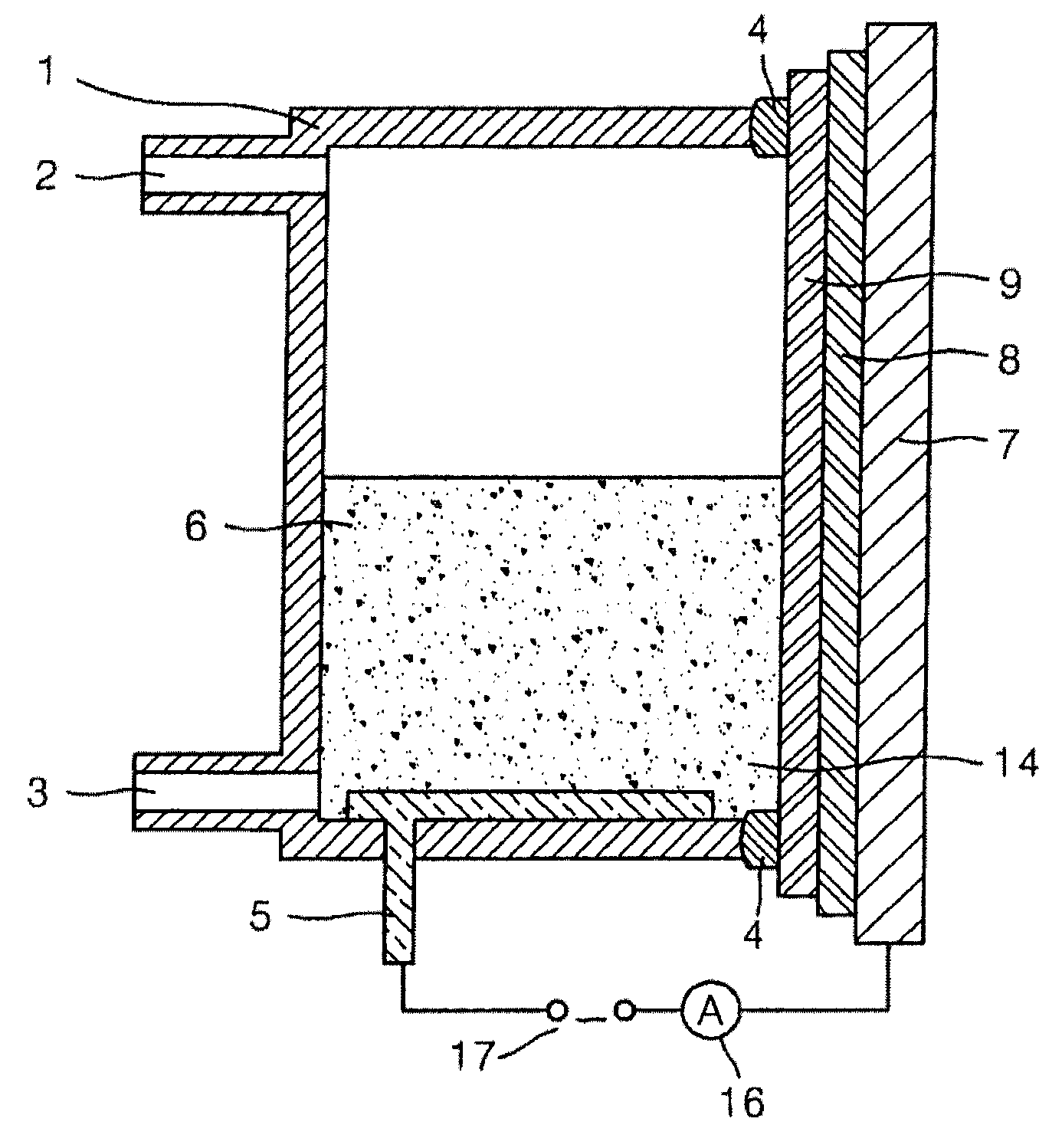

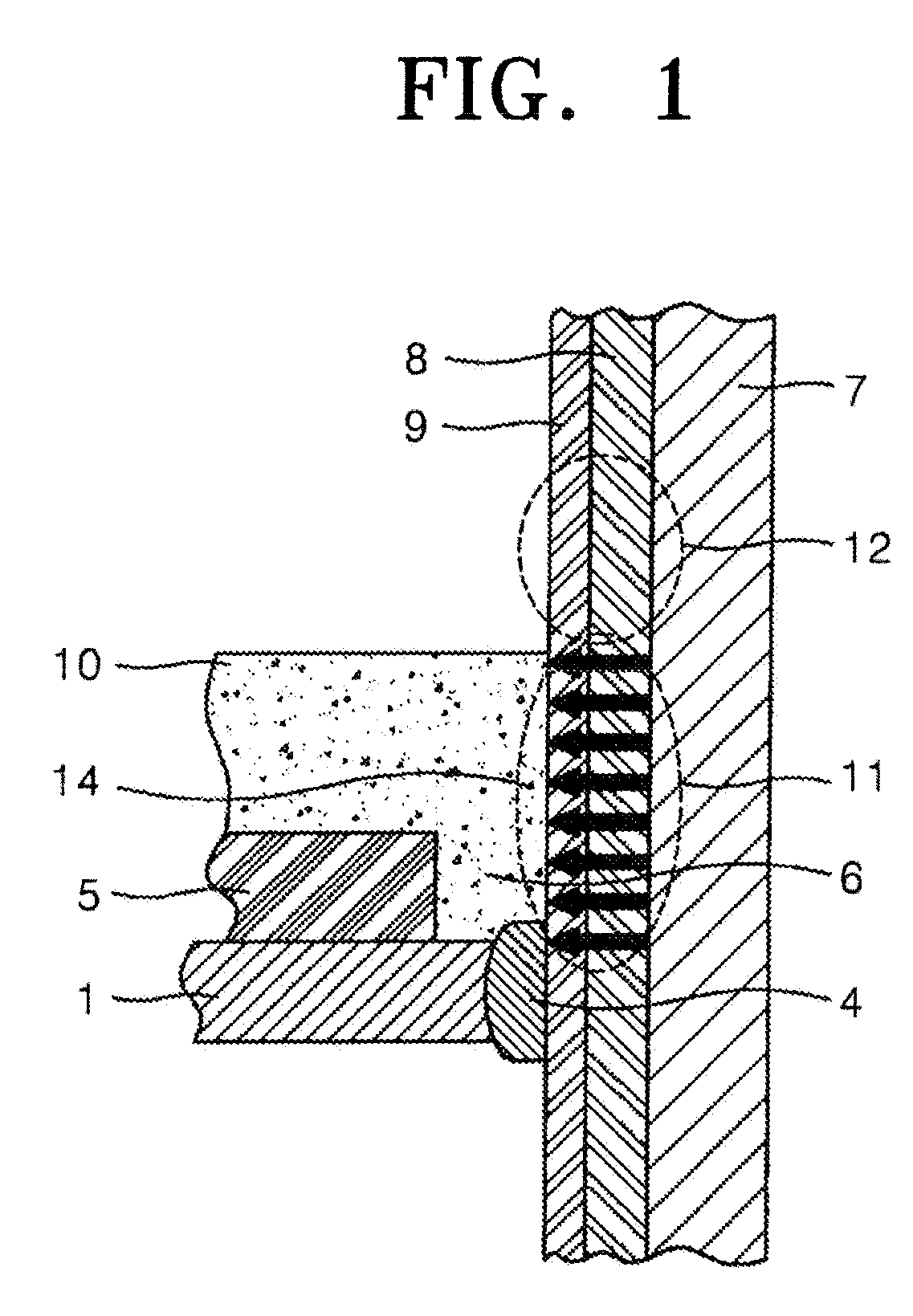

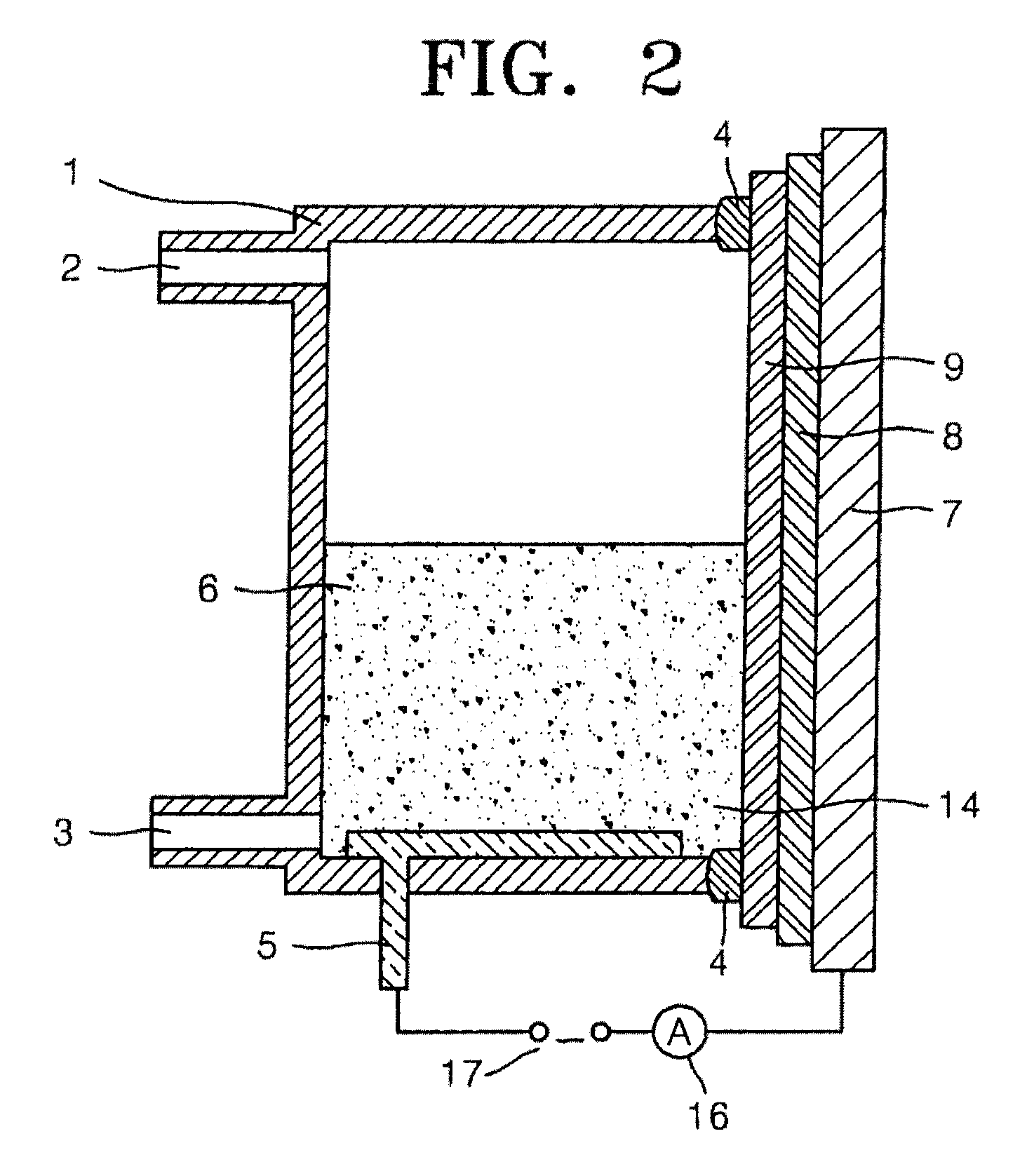

Capacitive liquid level detector for direct methanol fuel cell systems

InactiveUS20080282795A1Improve accuracyHigh precision measurementReactant parameters controlMachines/enginesFuel cellsDielectric layer

Owner:SAMSUNG SDI CO LTD

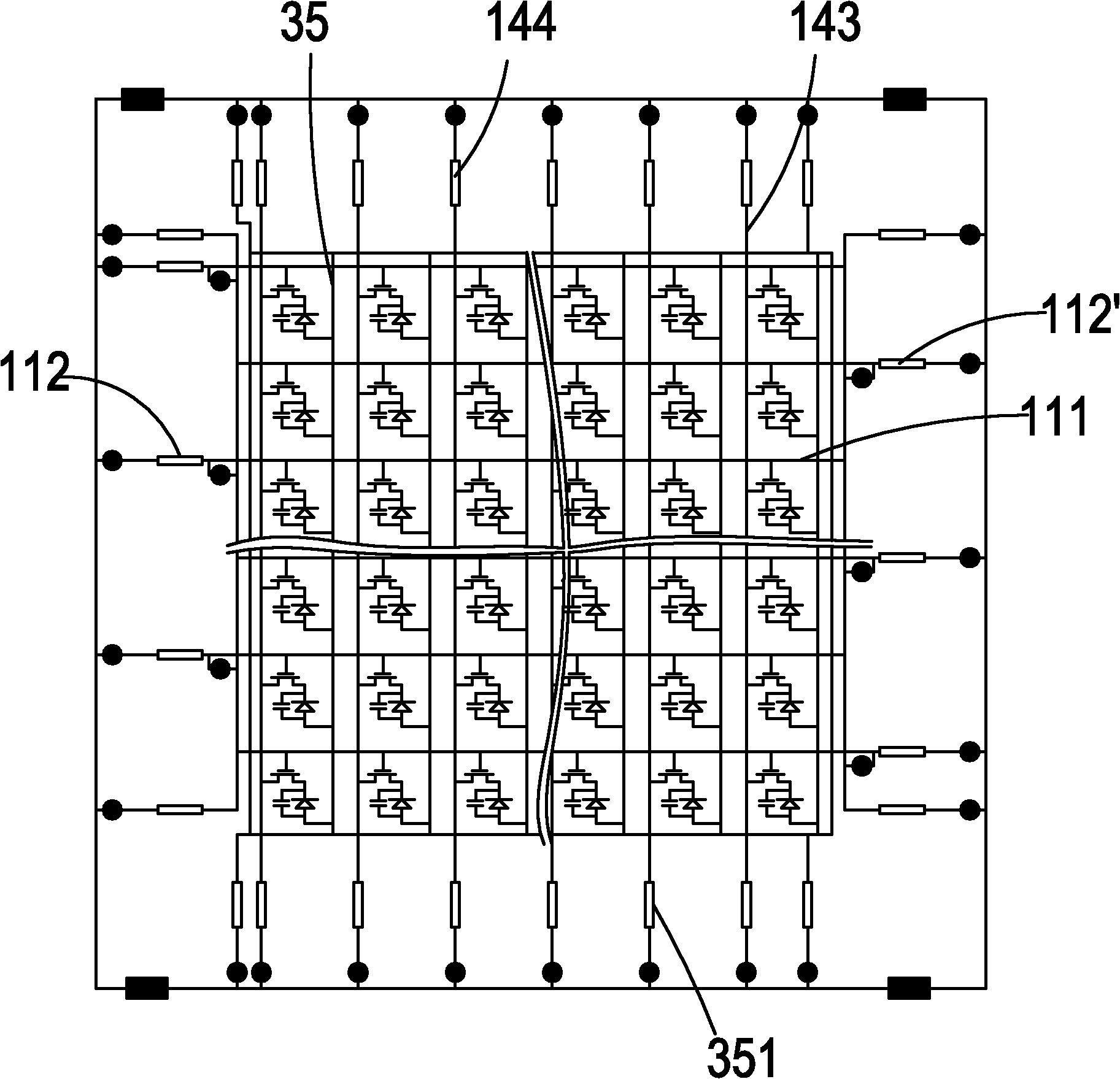

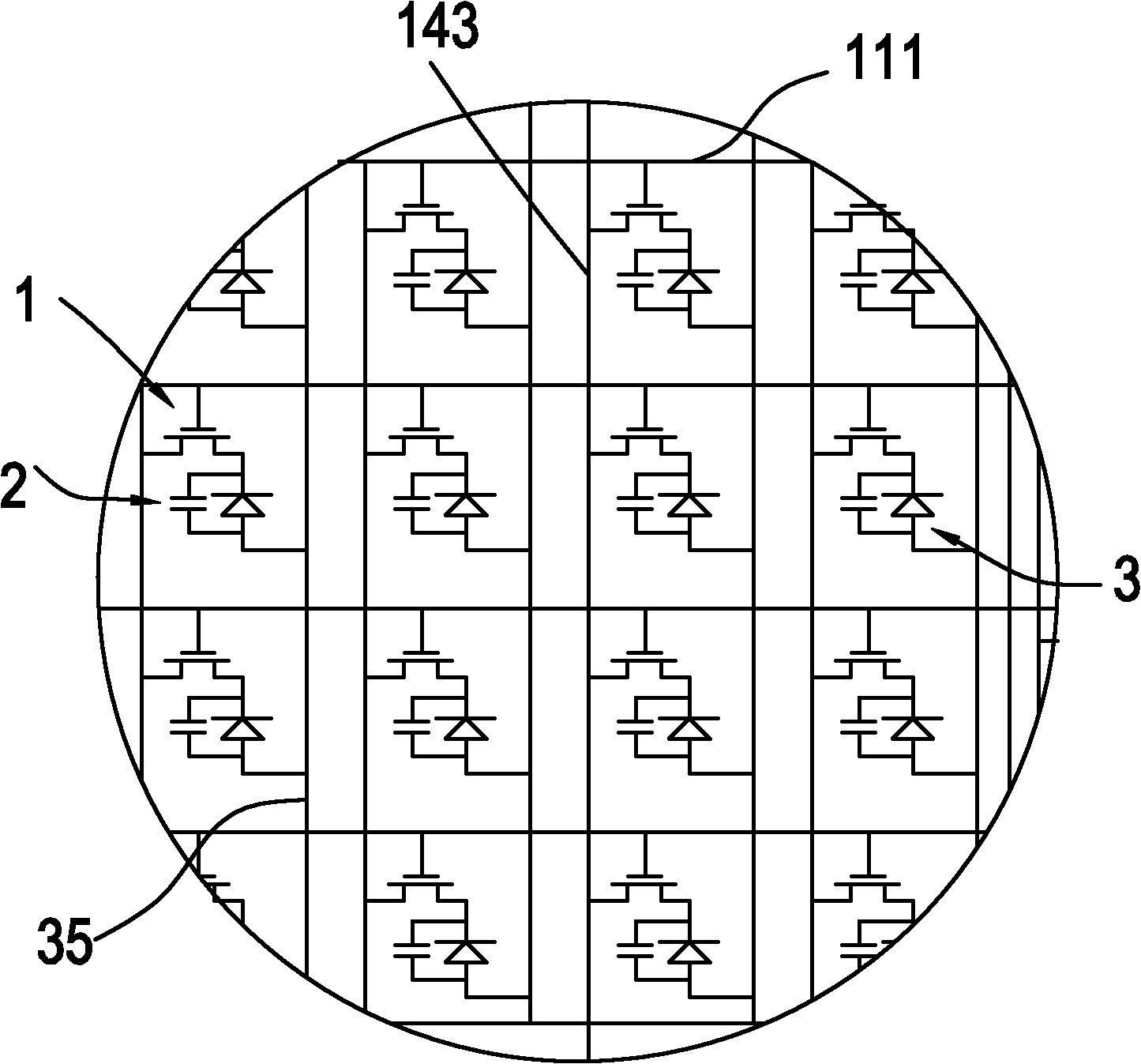

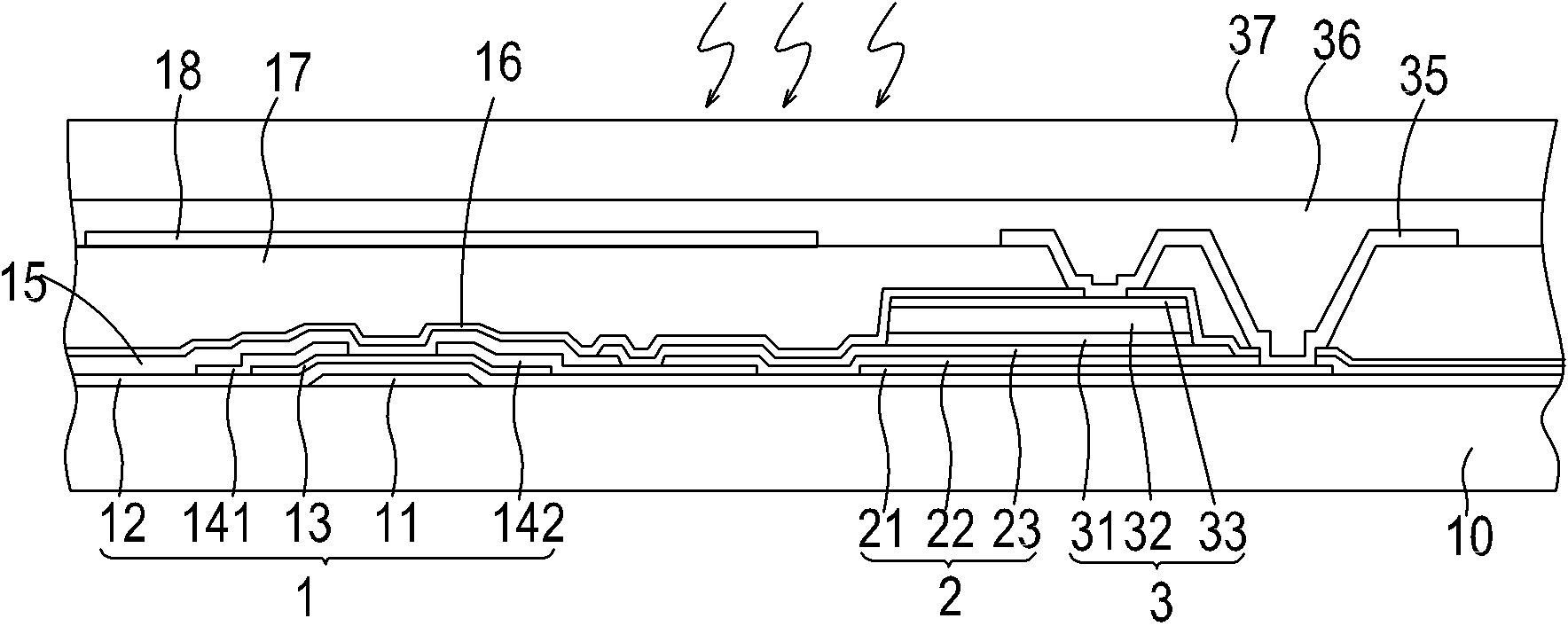

Master, pixel array substrate, electro-optical device and methods of manufacturing the same

ActiveUS20090108270A1Improve display qualityQuality improvementSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

Owner:AU OPTRONICS CORP

Dielectric device

InactiveUS20070247782A1High yieldSimple structureTransistorPiezoelectric/electrostrictive microphonesTriple pointDielectric layer

Owner:NGK INSULATORS LTD

Substrate for liquid crystal display and liquid crystal display having the same

InactiveUS20050248700A1Improve display qualitySimple processTransistorNon-linear opticsCapacitanceLiquid-crystal display

The invention relates to a liquid crystal display used in a display section of an electronic apparatus and a liquid crystal display substrate used for the same and provides a liquid crystal display that can be manufactured through simplified manufacturing processes and that can provide high display quality and a liquid crystal display substrate used for the same. A configuration is employed which includes gate bus lines and drain bus lines formed on a substrate such that they intersect each other with an insulation film interposed therebetween and pixel electrodes provided so as to cover at least one of the gate bus lines and the drain bus lines with a dielectric layer interposed therebetween and forming parasitic capacities between the gate bus lines or drain bus lines and themselves.

Owner:SHARP KK

Method for manufacturing flash memory

ActiveCN101924078AImprove gate coupling ratioImprove electrical performanceSemiconductor/solid-state device manufacturingElectrical conductorGate dielectric

Owner:WINBOND ELECTRONICS CORP

Organic electroluminescence display device with top luminous

ActiveCN101257035AImproving impedanceImprove luminous efficiencySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOrganic electroluminescence

A top luminous organic electroluminescent luminous display unit includes: a substrate including a display zone; a conductive layer situated above the substrate, and is electrically connected with the substrate; a reflection layer situated at the display zone of the substrate; a dielectric layer situated above the conductive layer, the reflection layer and the substrate, wherein the dielectric layer has a contact window out from the conductive layer; a transparent electrode layer situated above the dielectric layer and electrically connected along the contact window and the conductive layer; and a organic electroluminescent luminous layer situated above the transparent electrode layer, and corresponding to the display zone.

Owner:INNOLUX CORP

Method of fabricating a flash memory device

InactiveUS20080268608A1Good step coverageReduce interferenceSolid-state devicesSemiconductor/solid-state device manufacturingInterference phenomenonEngineering

In a method of fabricating a flash memory device, after an isolation trench is formed, a bottom surface and sidewalls of the trench are gap-filled with a HARP film having a favorable step coverage. A wet etch process is performed such that the HARP film remains on the sidewalls of a tunnel dielectric layer, thereby forming a wing spacer. Accordingly, the tunnel dielectric layer can be protected and an interference phenomenon can be reduced because a control gate to be formed subsequently is located between floating gates.

Owner:SK HYNIX INC

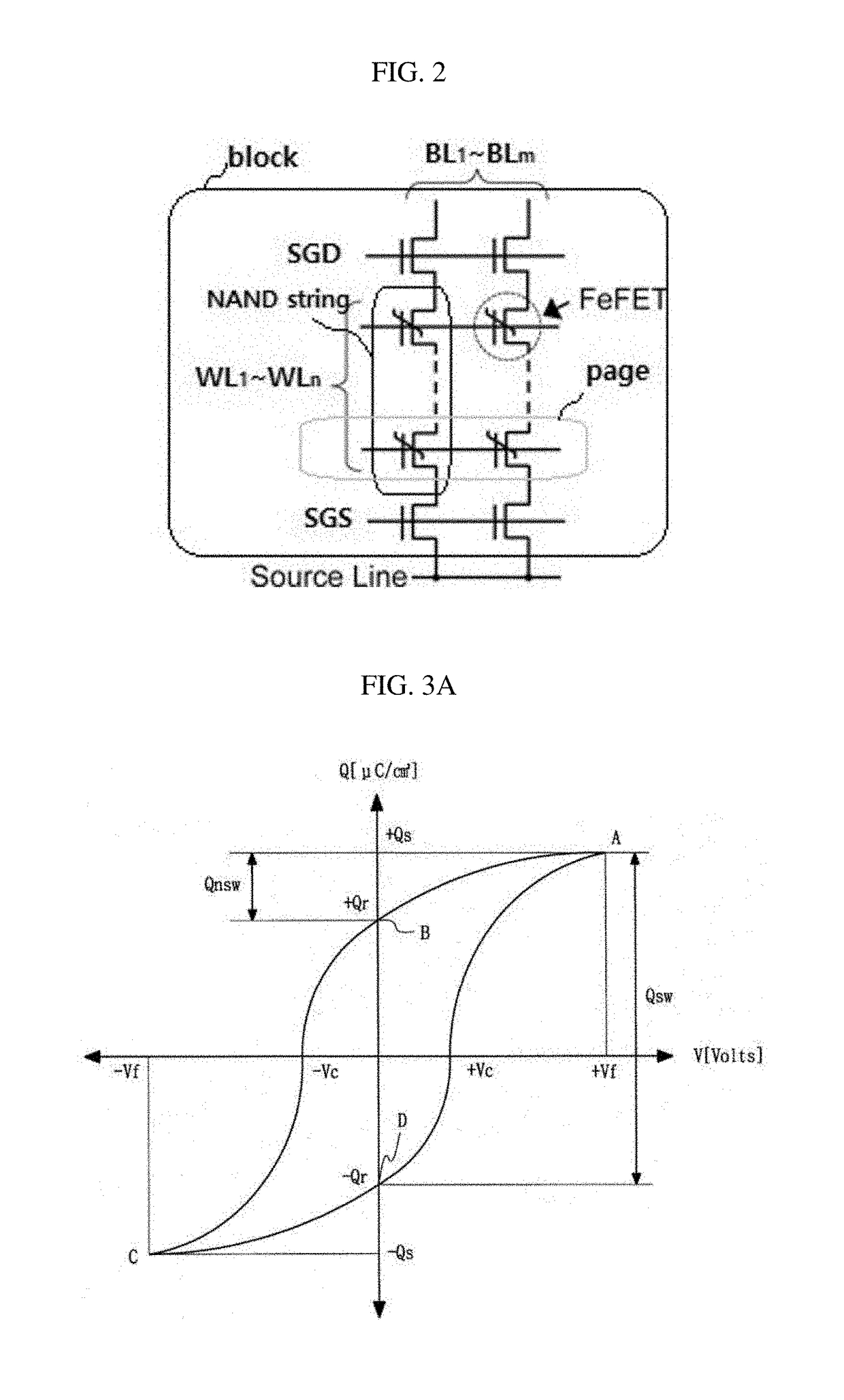

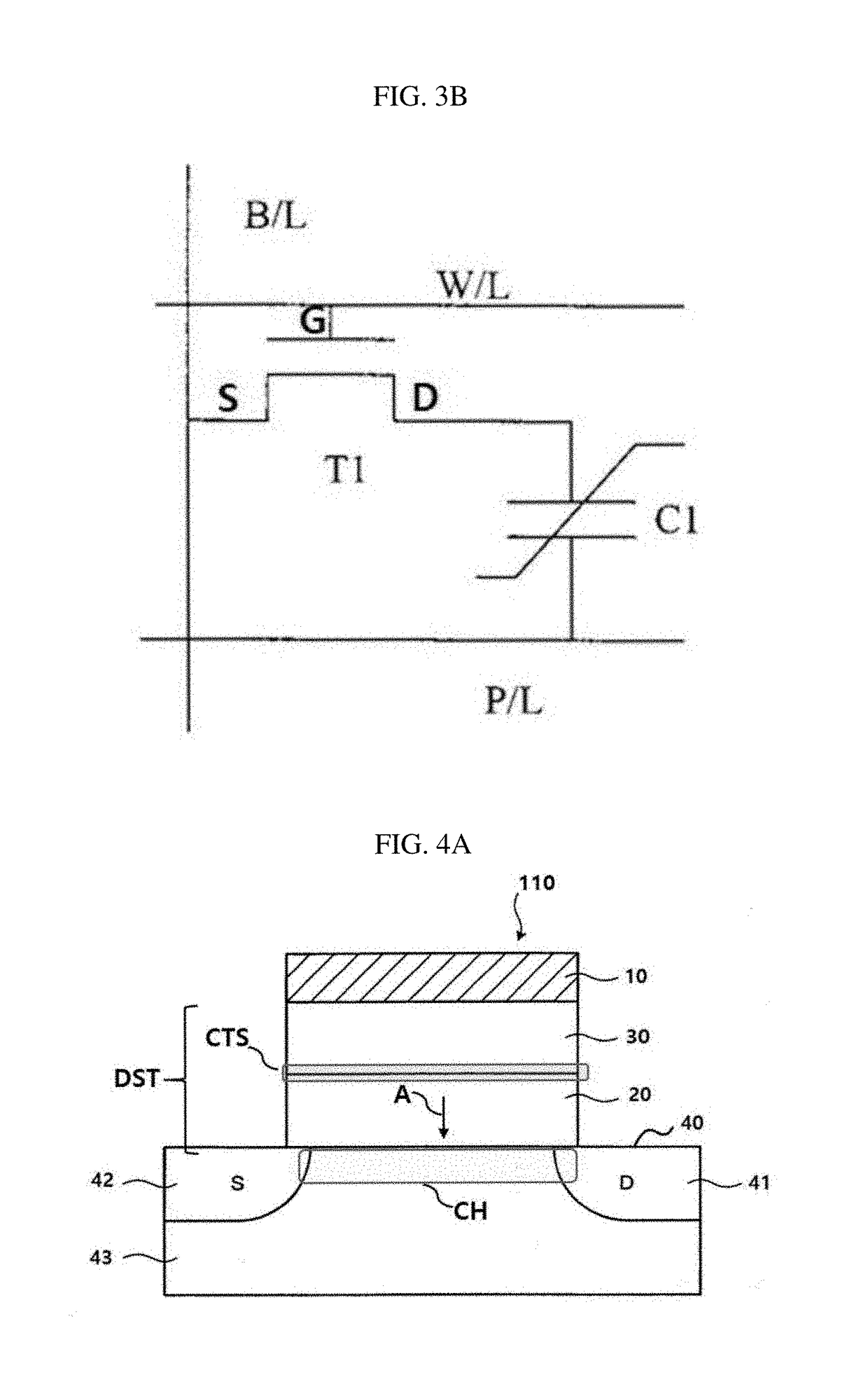

Non-volatile ferroelectric memory device and method of driving the same

ActiveUS10210921B1Negative capacitance effectImprove failureSolid-state devicesDigital storageCapacitanceEngineering

Owner:SAMSUNG ELECTRONICS CO LTD

Method for manufacturing self-aligned thin-film transistor and structure thereof

InactiveUS20110001135A1Made preciselyImprove featuresTransistorSemiconductor/solid-state device manufacturingUltraviolet lightsOptoelectronics

A method for manufacturing a self-aligned thin-film transistor (TFT) is described. Firstly, an oxide gate, a dielectric layer, and a photoresist layer are deposited on a first surface of a transparent substrate in sequence. Then, an ultraviolet light is irradiated on a second surface of the substrate opposite to the first surface to expose the photoresist layer, in which a gate manufactured by the oxide gate serves as a mask, and absorbs the ultraviolet light irradiated on the photoresist layer corresponding to the oxide gate. Then, the exposed photoresist layer is removed, and a transparent conductive layer is deposited on the unexposed photoresist layer and the dielectric layer. Then, a patterning process is executed on the transparent conductive layer to form a source and a drain, and an active layer is formed to cover the source, the drain, and the dielectric layer, so as to finish a self-aligned TFT structure.

Owner:NAT CHIAO TUNG UNIV

Method of fabricating a dual-damascene copper structure

ActiveUS20060252250A1Good step coveragePreferable ability to block copper atomsSemiconductor/solid-state device manufacturingTantalum nitrideCopper

A method for fabricating a dual-damascene copper structure includes providing a semiconductor substrate having a dielectric layer thereon and a dual-damascene hole positioned in the dielectric layer, wherein a portion of the semiconductor substrate is exposed in the dual-damascene hole. A PVD process and an atomic CVD process are sequentially performed to form a substrate-protecting layer and a tantalum nitride layer in the dual-damascene hole. And then a copper layer is formed in the dual-damascene hole.

Owner:UNITED MICROELECTRONICS CORP

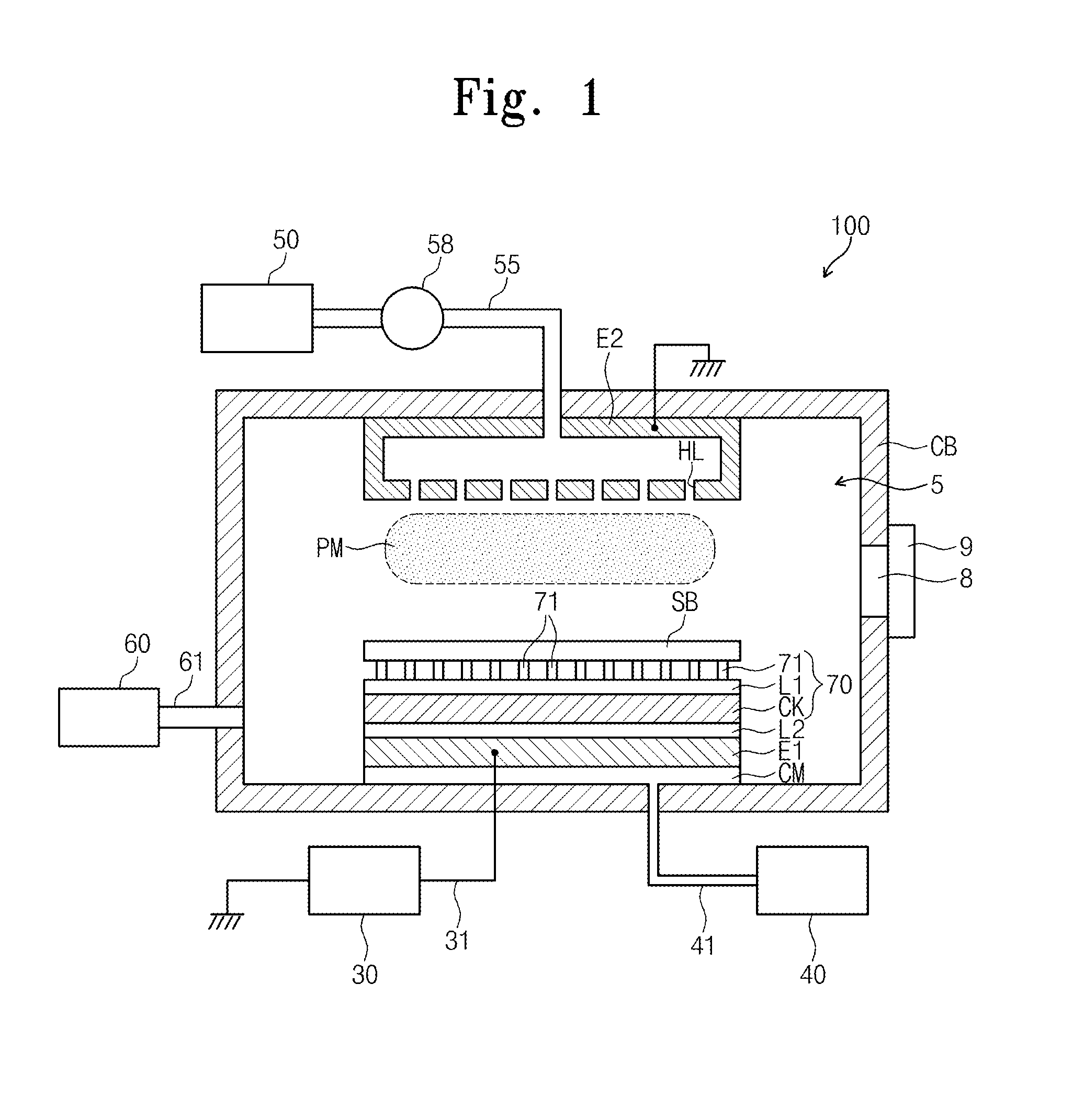

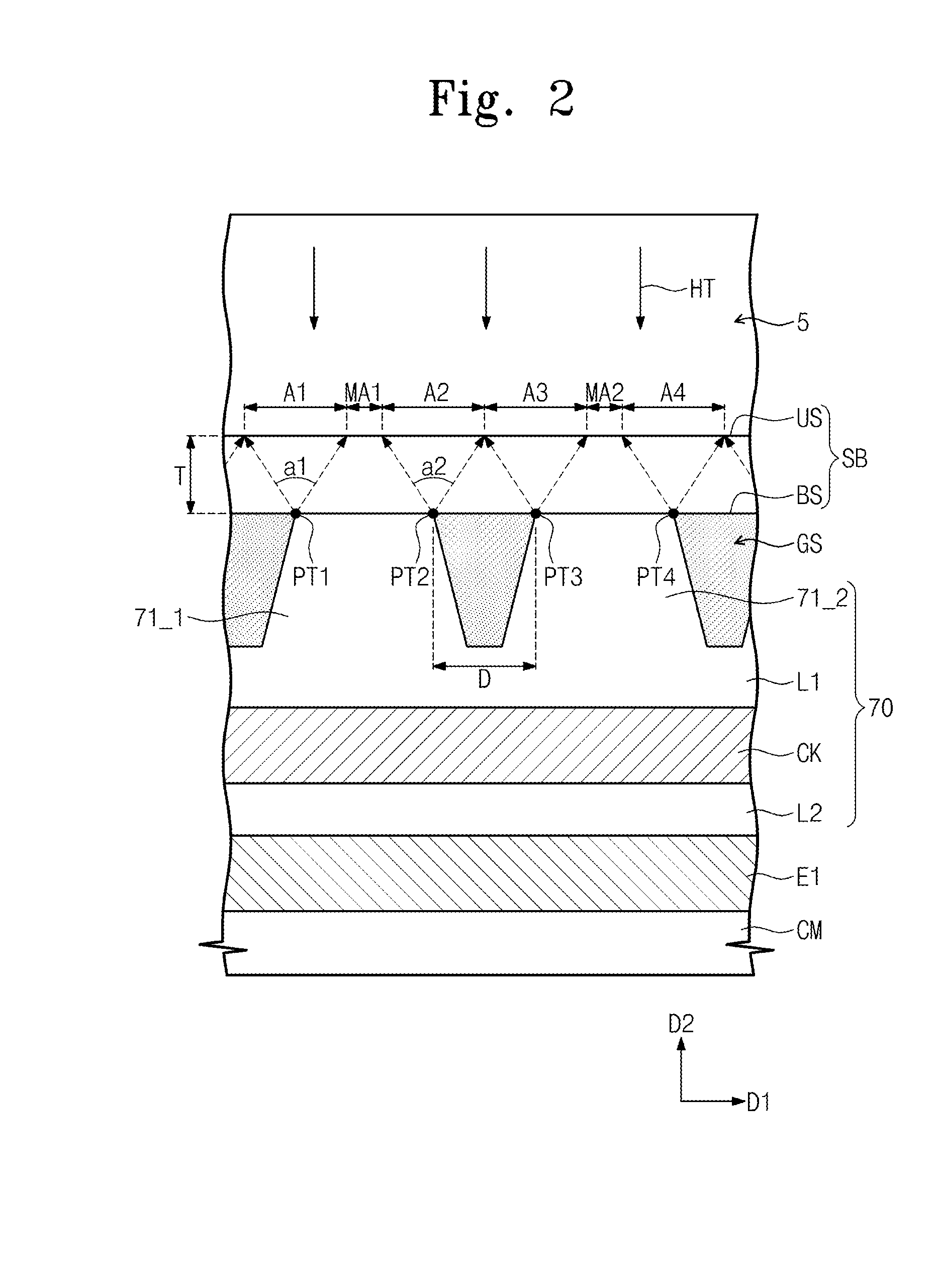

Substrate supporting unit and substrate treating apparatus and method

InactiveUS20140151332A1Electric discharge tubesDecorative surface effectsMechanical engineeringDielectric layer

Owner:SAMSUNG DISPLAY CO LTD

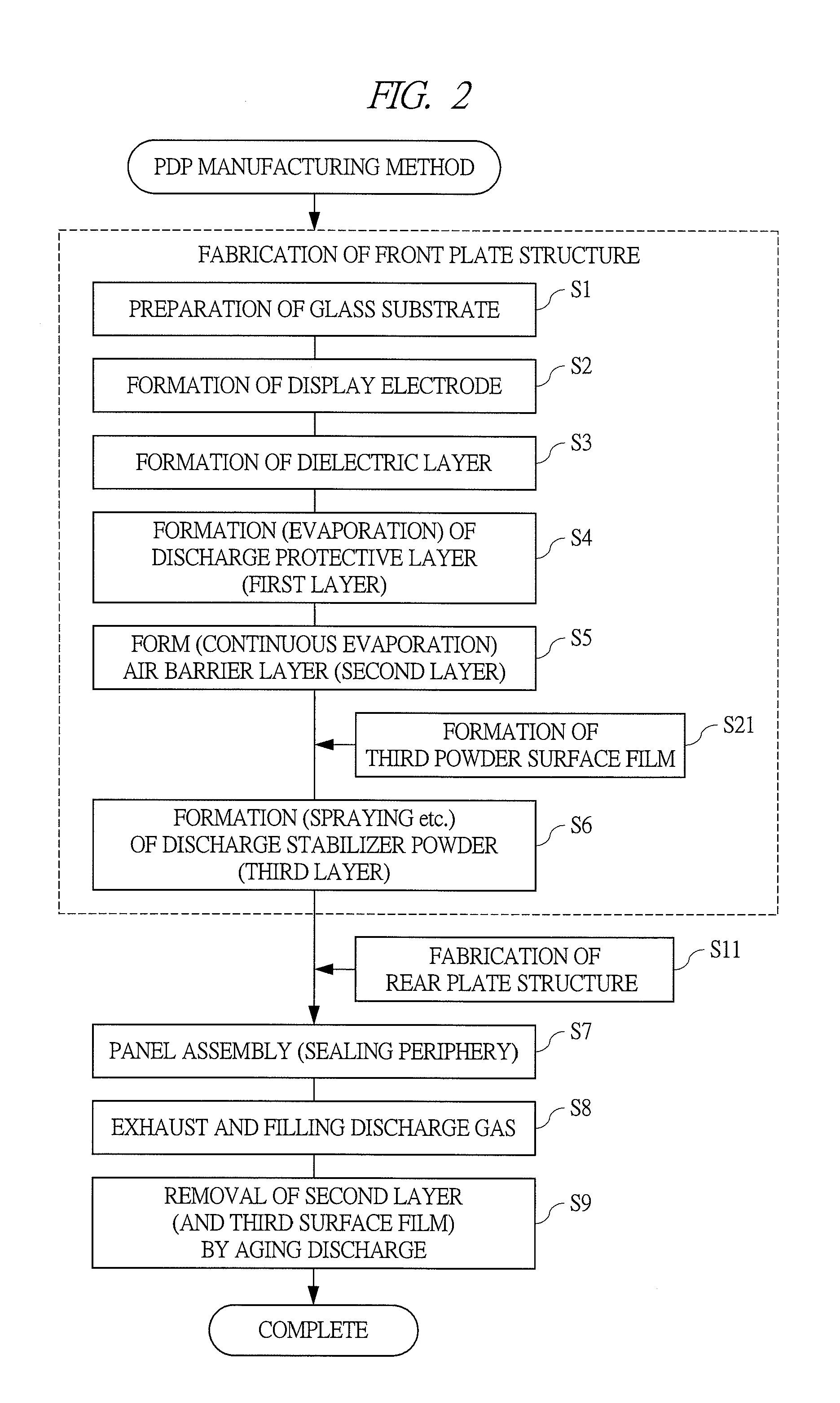

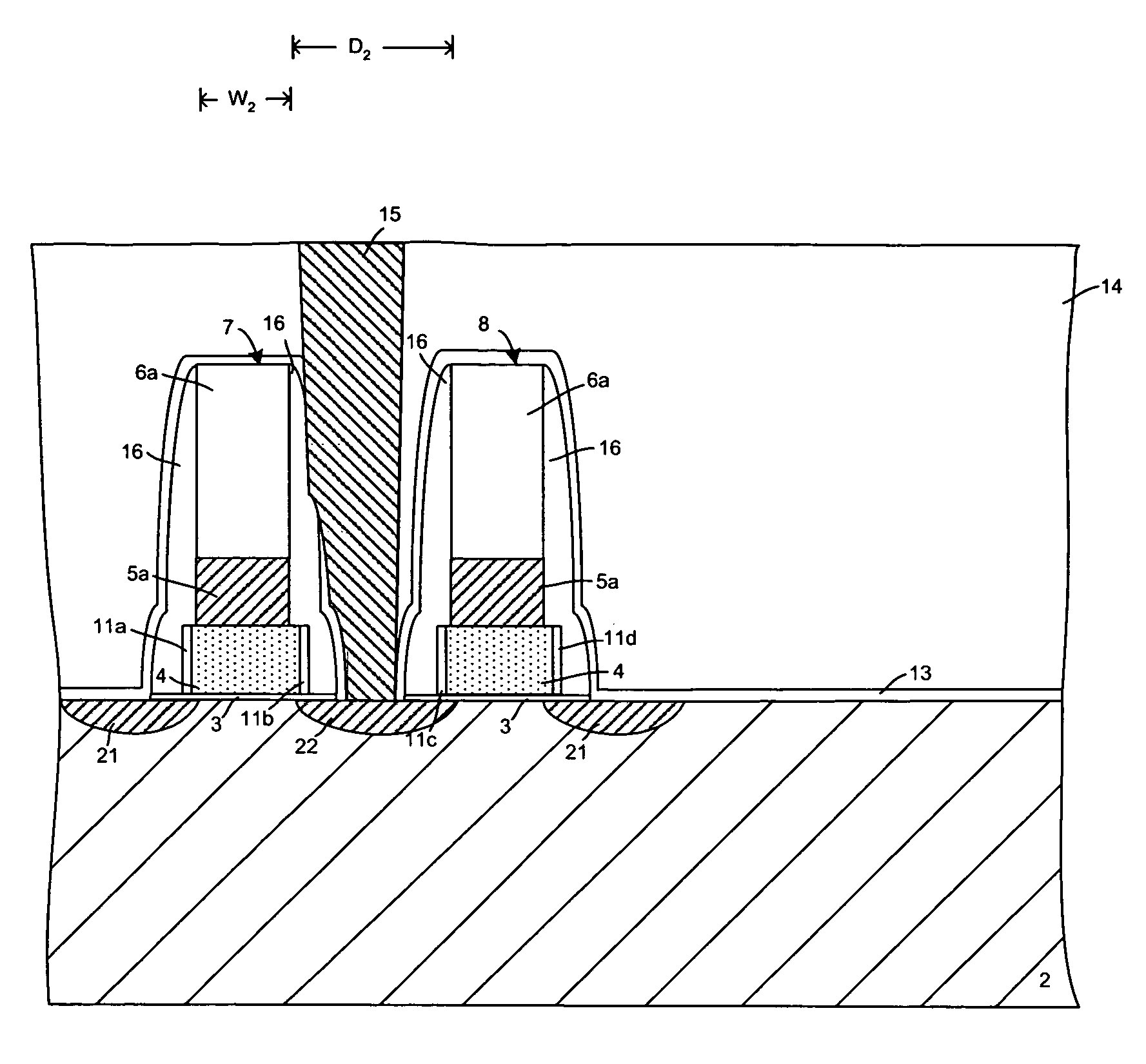

Plasma display panel and method of manufacturing the same, and discharge stabilizer powder

InactiveUS20110001427A1Improve display characteristicsImprovement in discharge delayStatic indicating devicesAlternating current plasma display panelsEngineeringDielectric layer

Owner:MAXELL HLDG LTD

Method for fabricating a group III nitride semiconductor laser device

InactiveUS20050048682A1Improve operating characteristicsSolution to short lifeLaser detailsSemiconductor laser structural detailsWaveguideDislocation

A nitride semiconductor laser device using a group III nitride semiconductor also as a substrate offers excellent operation characteristics and a long laser oscillation life. In a layered structure of a group III nitride semiconductor formed on a GaN substrate, a laser optical waveguide region is formed elsewhere than right above a dislocation-concentrated region extending so as to vertically penetrate the substrate, and electrodes are formed on the top surface of the layered structure and on the bottom surface of the substrate elsewhere than right above or below the dislocation-concentrated region. In a portion of the top surface of the layered structure and in a portion of the bottom surface of the substrate right above and below the dislocation-concentrated region, dielectric layers may be formed to prevent the electrodes from making contact with those regions.

Owner:SHARP KK +1

Production method of a capacitor

ActiveUS20070141745A1Increase capacitanceExcellent ESR performanceHybrid capacitor electrolytesSolid electrolytic capacitorsCapacitanceElectrolytic agent

A method for producing a capacitor having a good capacitance appearance factor and a low ESR comprising, as one electrode (anode), an electric conductor having pores and having formed on the surface thereof a dielectric layer and, as the other electrode (cathode), a semiconductor layer formed on the electric conductor by energization in an electrolytic solution, the method comprising impregnating pores with a semiconductor layer-forming precursor before energization to render the concentration of semiconductor layer-forming precursor in pores higher than that of semiconductor layer-forming precursor in the electrolytic solution; a capacitor produced by the method; and an electronic circuit and an electronic device using the capacitor.

Owner:RESONAC CORP

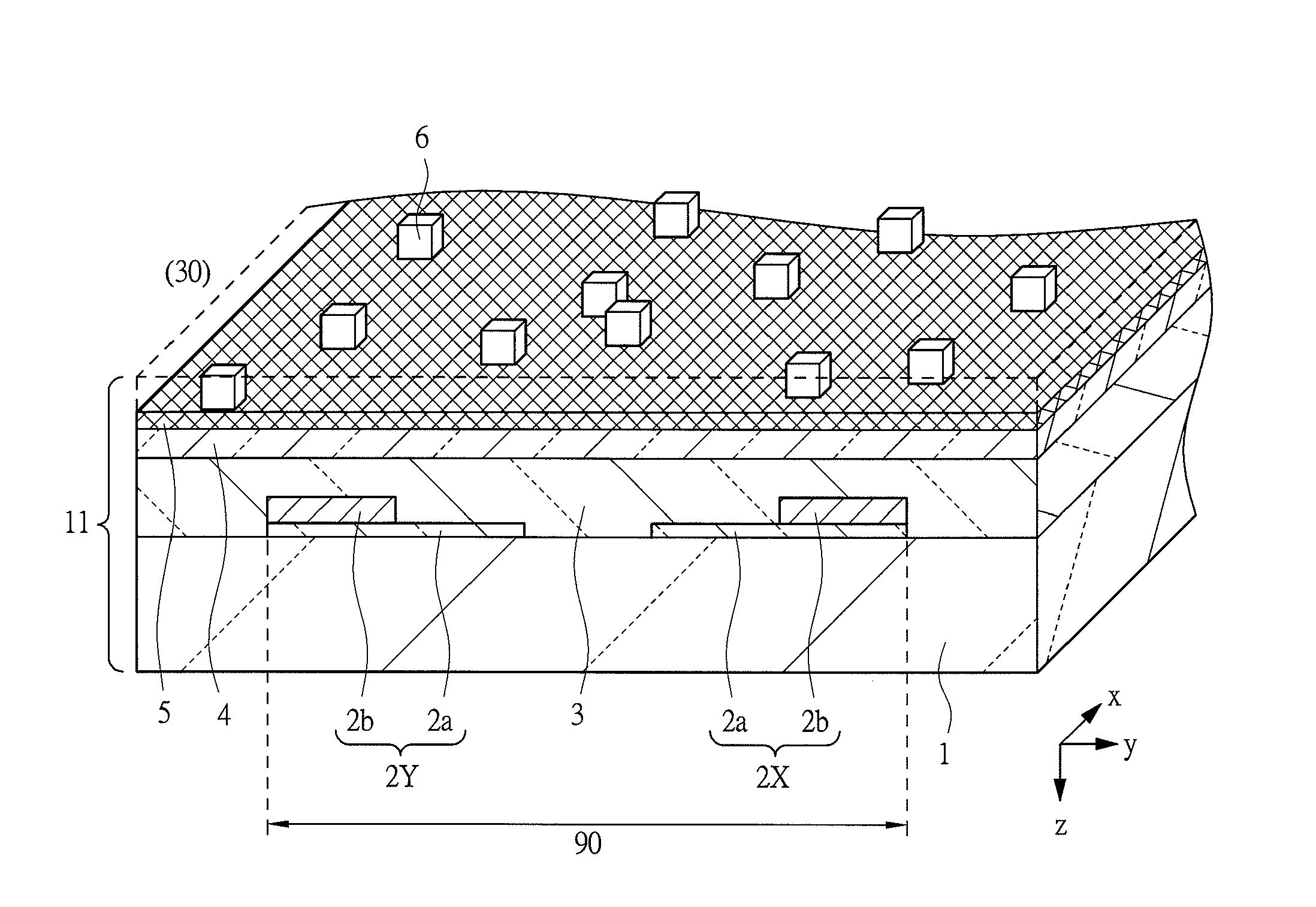

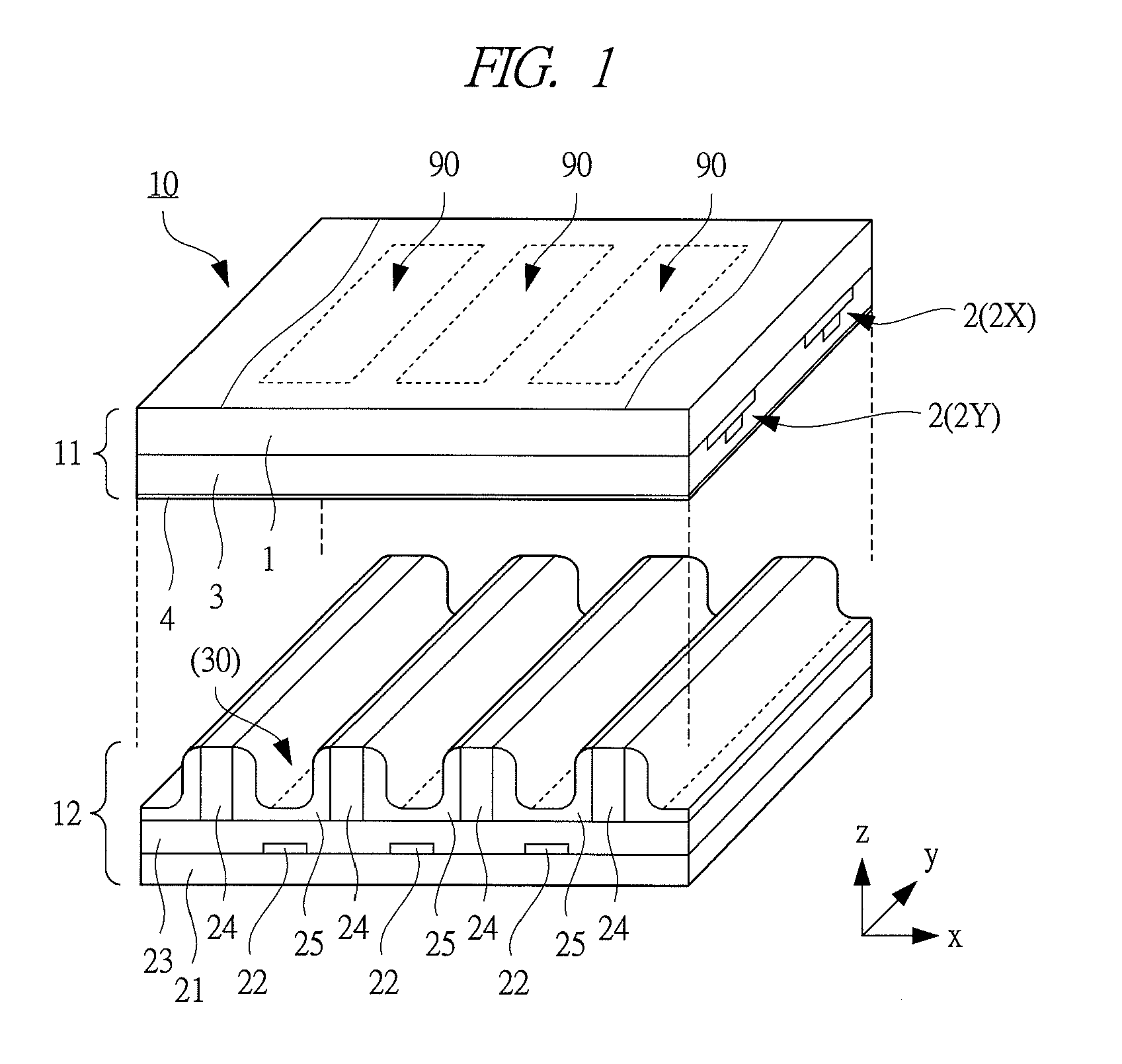

Antenna apparatus

ActiveUS20220013911A1Easily downsizedHigh gainSimultaneous aerial operationsRadiating elements structural formsSoftware engineeringDielectric permittivity

An antenna apparatus includes: a first dielectric layer having a first dielectric constant; a first patch antenna pattern disposed in the first dielectric layer; a second dielectric layer having a second dielectric constant; a second patch antenna pattern disposed on the second dielectric layer; a first feed via coupled to the first patch antenna pattern; and a second feed via coupled to the second patch antenna pattern. The first dielectric constant is higher than the second dielectric constant, and a frequency of a signal transmitted / received by the first patch antenna pattern is lower than a frequency of a signal transmitted / received by the second patch antenna pattern.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Method for forming CMOS structure with void-free dielectric film

InactiveUS7163881B1Reduce widthEasy to fillSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSDielectric layer

Owner:INTEGRATED DEVICE TECH INC

Rectangular waveguide covered with dielectric layer

InactiveCN103700914AIncrease the electric field strengthReduce divergenceWaveguidesLeaky-waveguide antennasElectrical field strengthEngineering

Owner:BEIJING JIAOTONG UNIV

Semiconductor device with contact etching stop layer and forming method thereof

InactiveCN101740498AAvoid phenomena such as poor reliabilityAvoid damageSemiconductor/solid-state device detailsSolid-state devicesHigh densityGate oxide

The invention discloses a method for forming a semiconductor device with a contact etching stop layer, which comprises the following steps of: providing a substrate on which at least one grid structure is formed; putting the substrate in a settling chamber to carry out the settlement of the contact etching stop layer; oxidizing the contact etching stop layer in situ to form an oxide film on the surface of the contact etching stop layer; taking out the substrate on which the oxide film is formed; and forming an interlayer dielectric layer on the oxide film by high-density plasma chemical vapour deposition equipment. The invention also discloses the semiconductor device with the contact etching stop layer. The semiconductor device with the contact etching stop layer and the forming method thereof of the invention can effectively prevent damages which are caused by using the high-density and large-power plasma in the step of settling the interlayer dielectric layer to a gate oxide layer and voids phenomena of device performance drift, device reliability reduction and the like.

Owner:SEMICON MFG INT (BEIJING) CORP

Method for forming fuse structure

InactiveCN102054765AControl thicknessWon't hurtSemiconductor/solid-state device detailsSolid-state devicesDielectric layerSemiconductor

The invention relates to a method for forming a fuse structure which comprises the following steps: providing a semiconductor substrate, forming a fuse structure on the semiconductor substrate; forming a first dielectric layer with a target thickness on the semiconductor substrate for covering the fuse structure; forming an etching termination layer on the first dielectric layer; forming a second dielectric layer on the etching termination layer; selectively etching the second dielectric layer; and forming an opening above the fuse structure, and exposing the bottom of the opening out of the etching termination layer. The method provided by the invention can efficiently control the thickness of the dielectric layer resided above the fuse structure and increase the reliability of elements.

Owner:CSMC TECH FAB1 +1

Nanotube memory structure and preparation method thereof

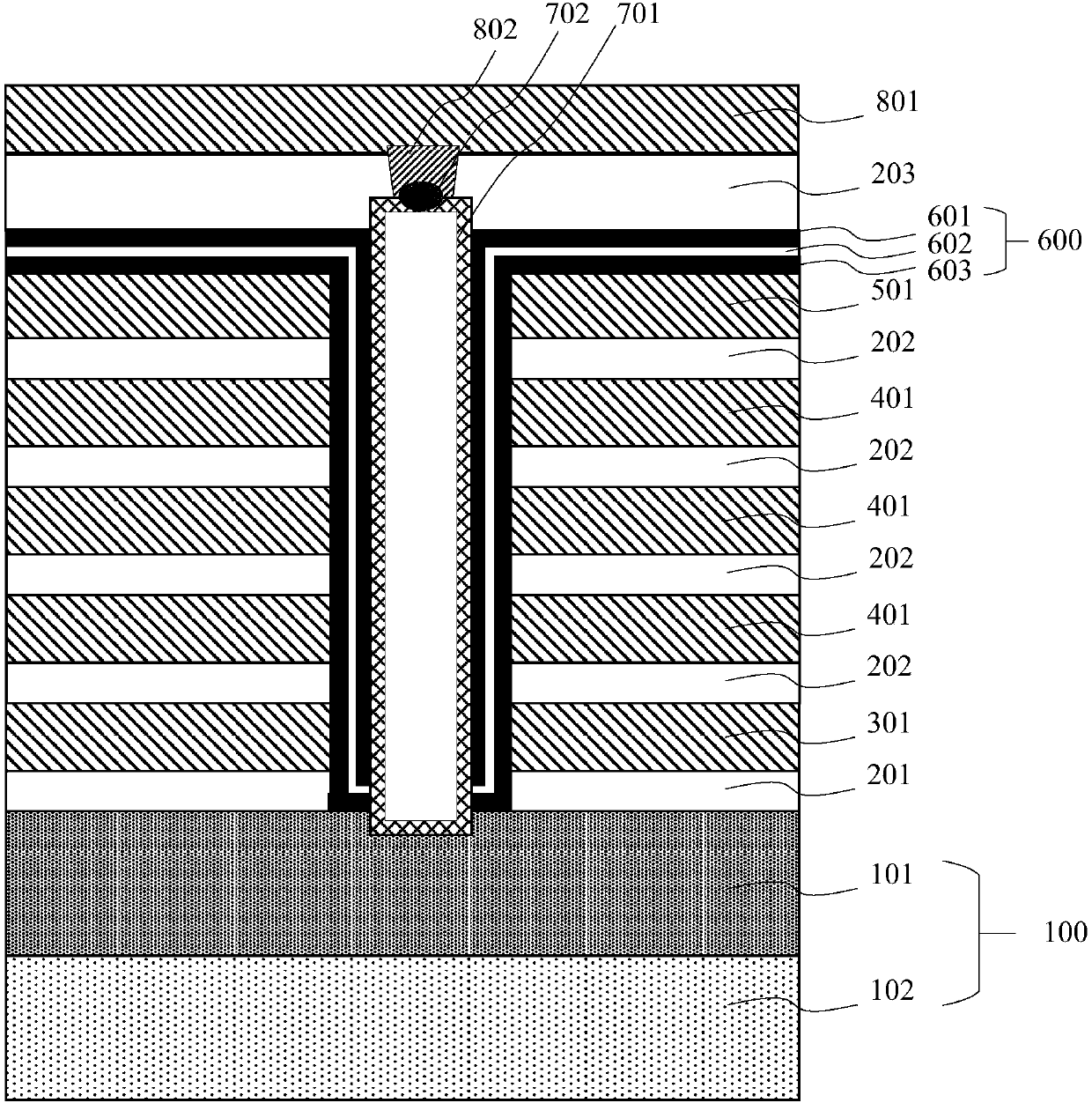

ActiveCN107768381ASimple structureThe preparation process is simple and controllableSolid-state devicesSemiconductor devicesBit lineVertical channel

Owner:ZING SEMICON CORP

Thick film dielectric structure for thick dielectric electroluminescent displays

InactiveUS20050255708A1Improved smoothing layerLow densityLiquid surface applicatorsDischarge tube luminescnet screensDielectric structureHYDROSOL

Owner:IFIRE IP CORP

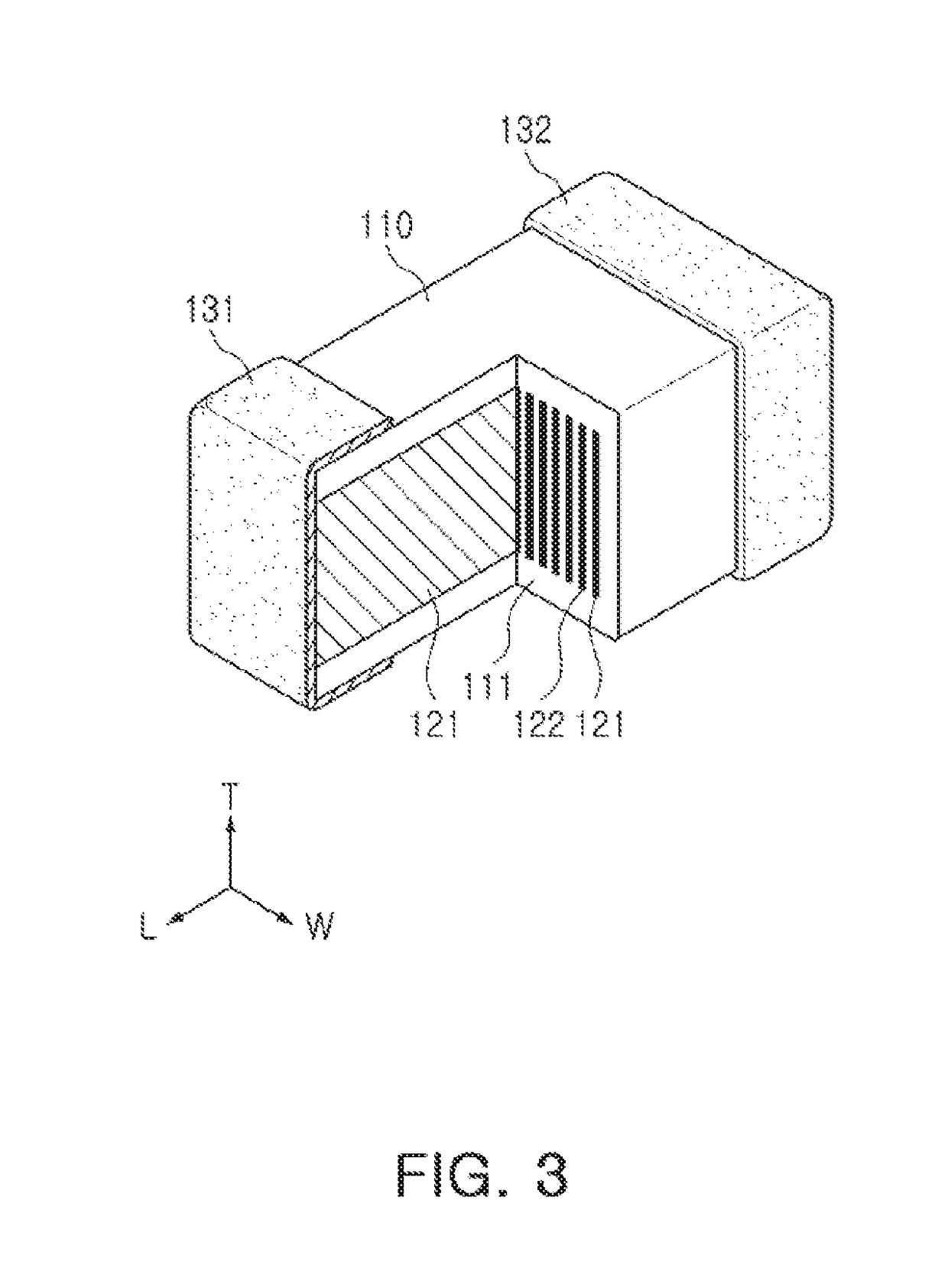

Composite electronic component and board having the same

InactiveUS20190069410A1Reduce noiseFixed capacitor electrodesFixed capacitor dielectricCeramic capacitorElectronic component

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Popular searches

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap