Method for manufacturing flash memory

A manufacturing method and memory technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of difficult etching process, etc., and achieve the effect of maintaining integrity and increasing contact area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

no. 1 example

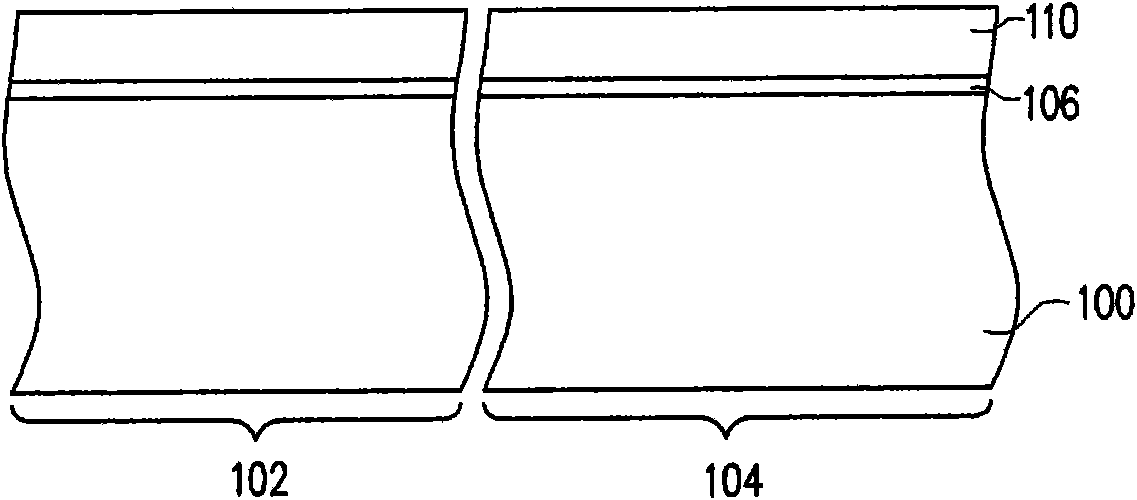

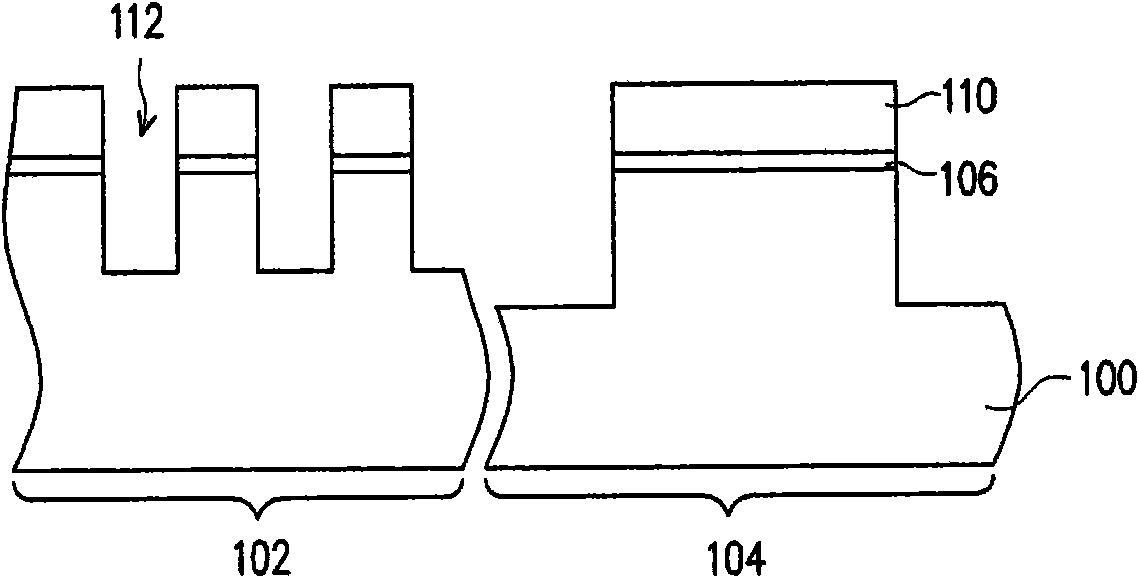

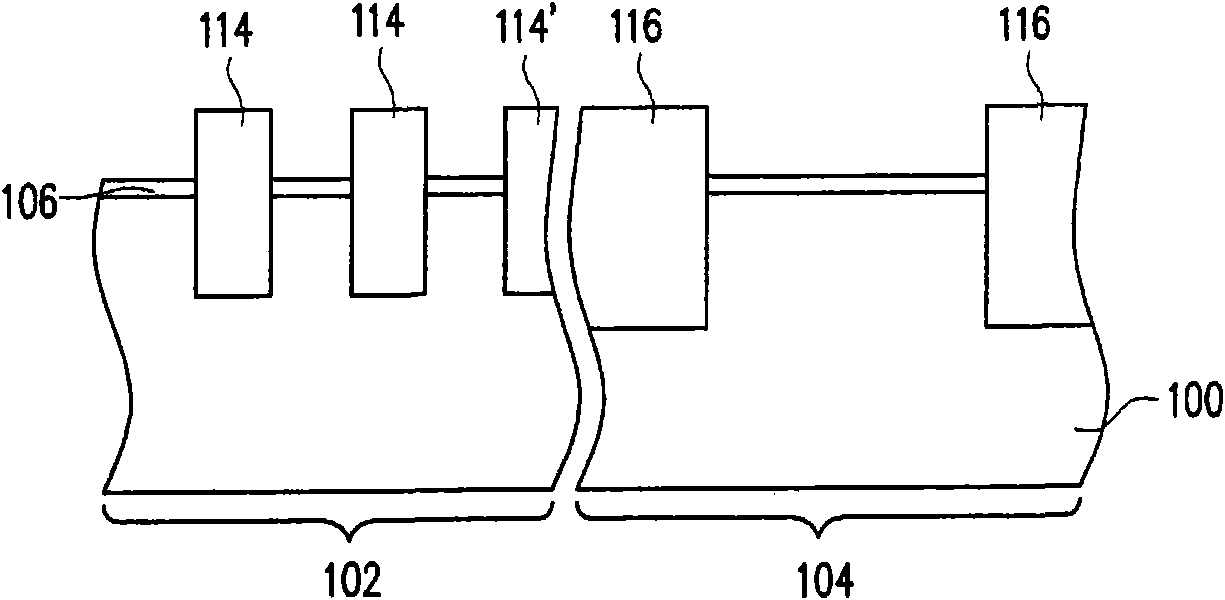

[0033] Figure 1A to Figure 1I is a schematic cross-sectional flow diagram of a method for manufacturing a flash memory according to the first embodiment of the present invention.

[0034] Please refer to Figure 1A , firstly, a substrate 100 is provided. The substrate 100 is, for example, a silicon substrate. The substrate 100 includes a memory area 102 and a peripheral area 104 . Then, a first dielectric layer 106 and a mask layer 110 are sequentially formed on the substrate 100 . The material of the first dielectric layer 106 is, for example, silicon oxide, and its formation method is, for example, thermal oxidation or chemical vapor deposition. The material of the mask layer 110 is, for example, silicon nitride, and its formation method is, for example, chemical vapor deposition.

[0035] Please refer to Figure 1B , and then, removing part of the mask layer 110 , the first dielectric layer 106 and the substrate 100 to form the trench 112 . A method for removing part of

no. 2 example

[0046] Figure 2A to Figure 2C It is a schematic cross-sectional flow diagram of a part of a manufacturing method of a flash memory according to the second embodiment of the present invention. In this embodiment, the front-end process of the flash memory is the same as that in the first embodiment Figure 1A to Figure 1D and its corresponding instructions are similar, so the following is only for the continuation Figure 1D steps are explained.

[0047] Please also refer to Figure 1D and Figure 2A After the stacked tunneling dielectric layer 108 and the floating gate 120 are formed on the substrate 100 between the isolation structures 114, 114', 116, for example, the isolation structures 114, 114', 116 are blanketed ) are removed to form isolation structures 114a, 114'a, 116a. Wherein, the surfaces 124, 125, 126 of the isolation structures 114a, 114'a, 116a are higher than the surface 109 of the tunnel dielectric layer 108, and the surfaces 124, 125, 126 of the isolation s

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap