Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

118results about "Digital storage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

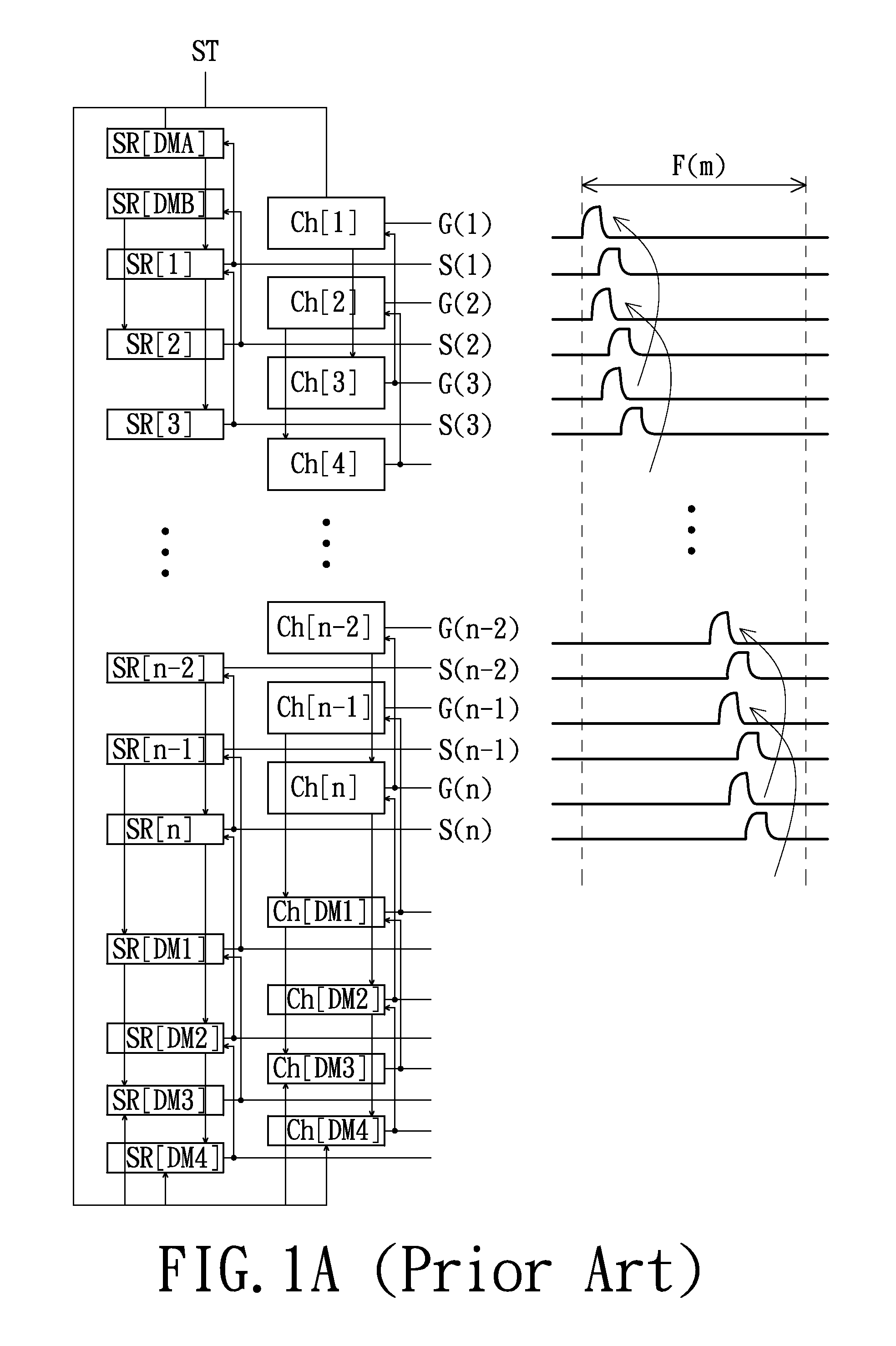

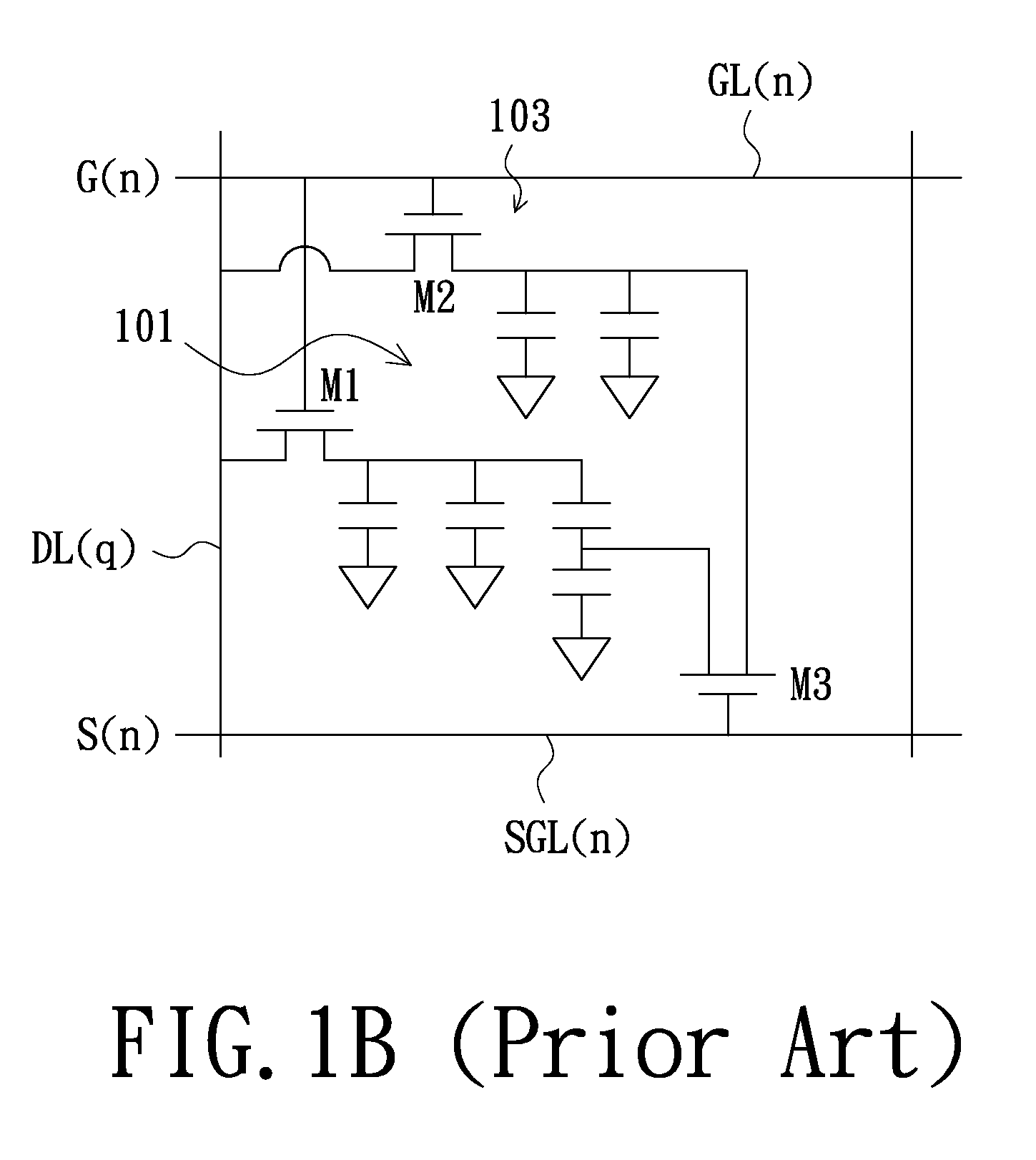

Shift resister and liquid crystal display having the same

Owner:SAMSUNG DISPLAY CO LTD

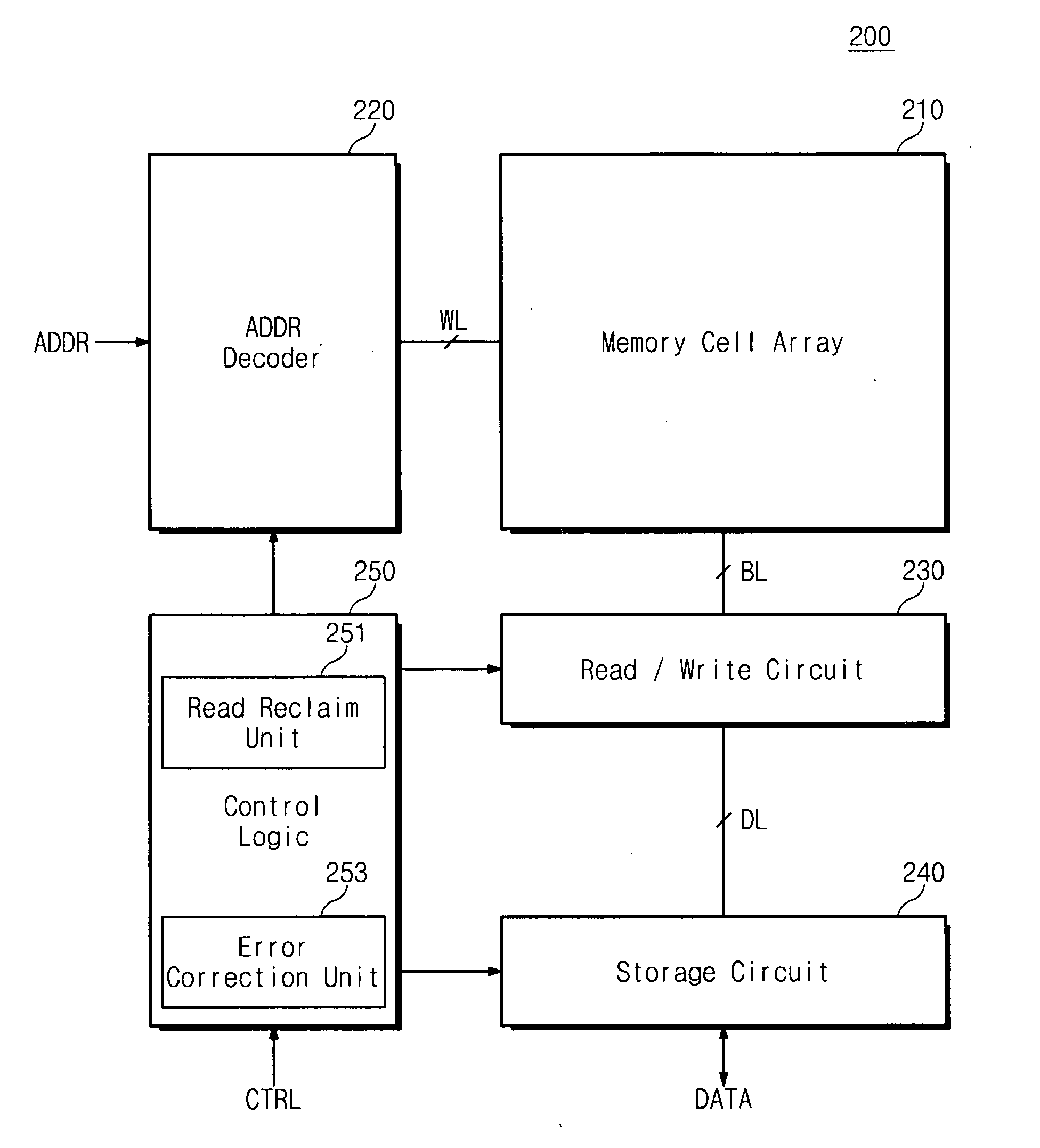

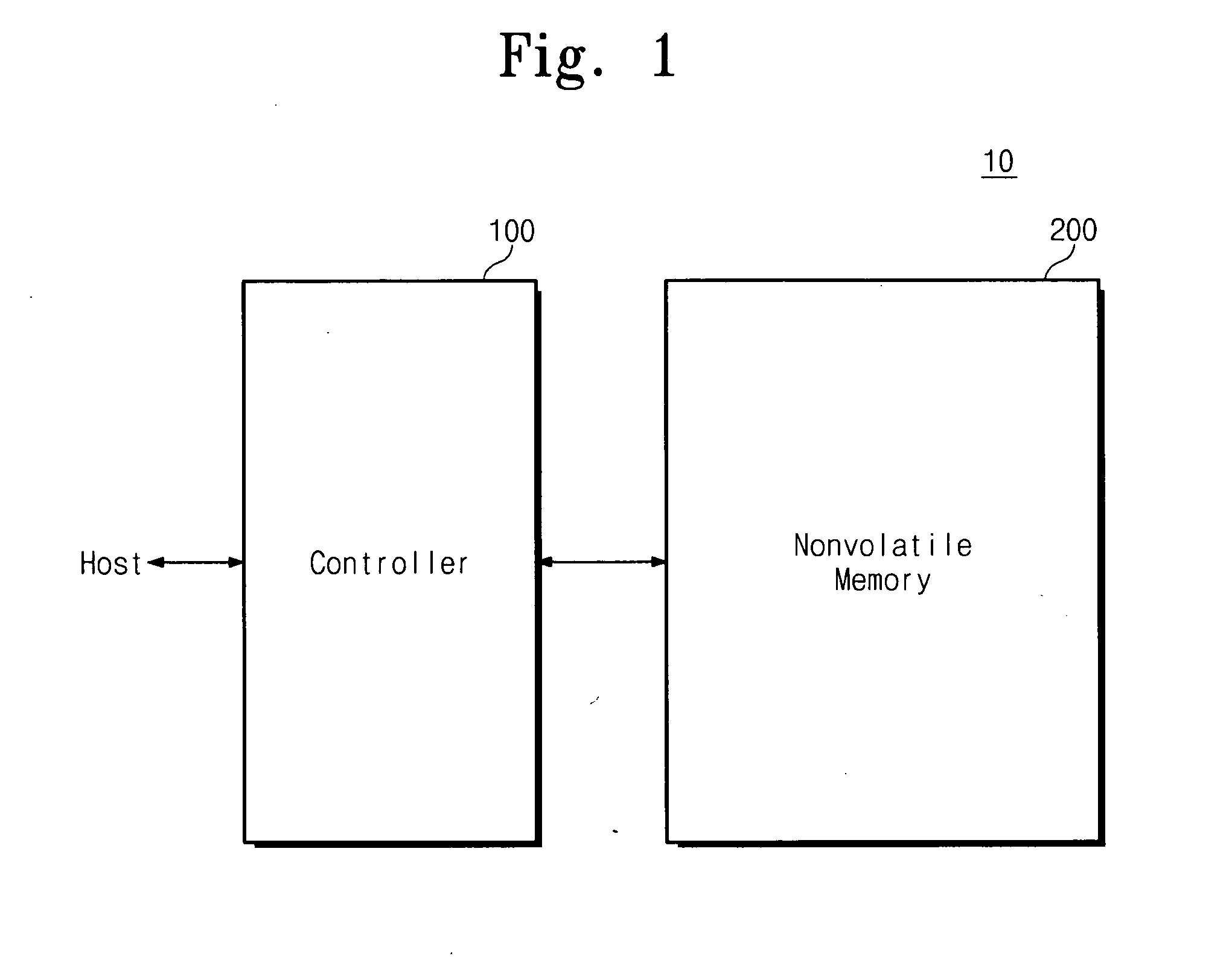

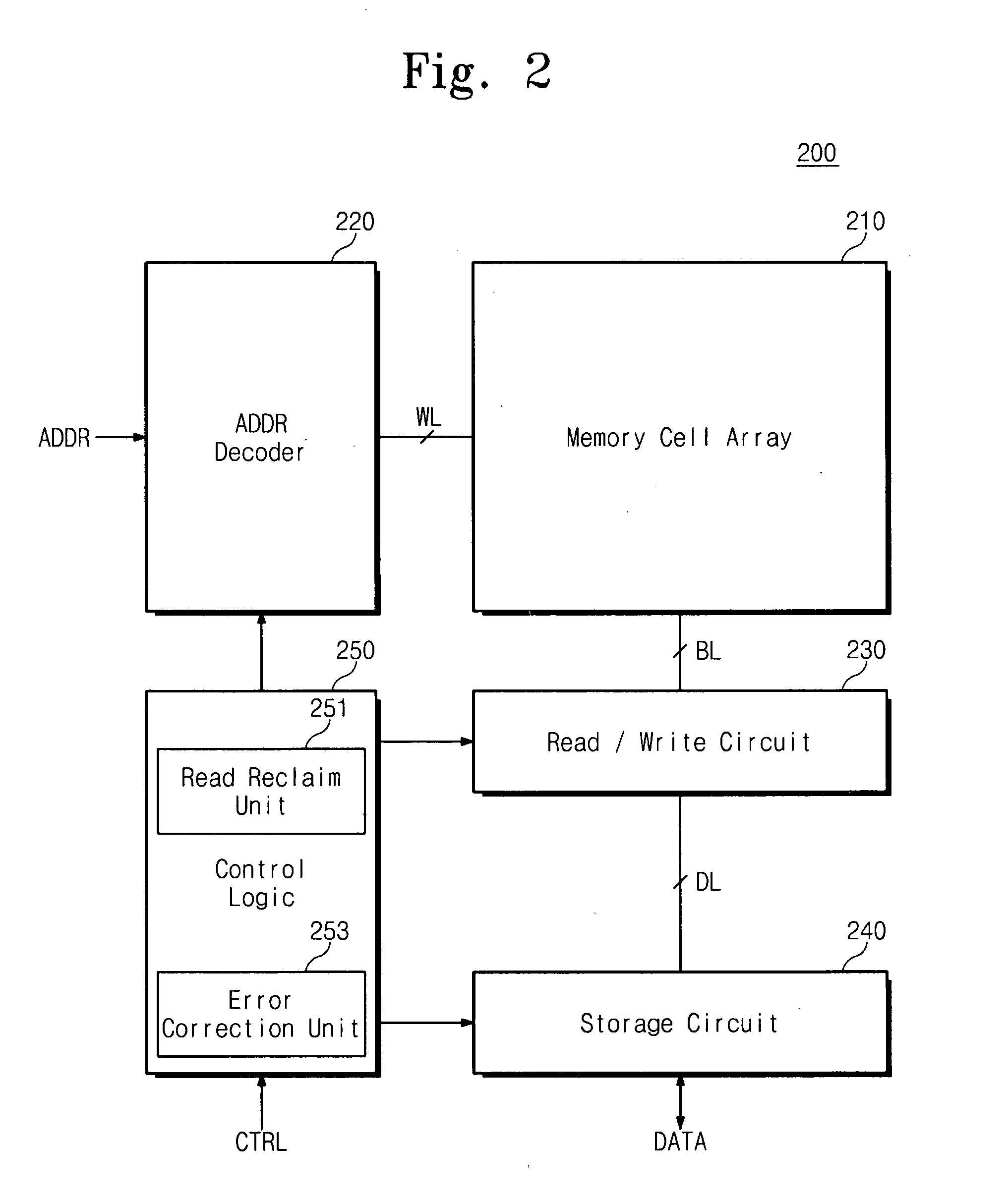

Nonvolatile memory device, method of operating nonvolatile memory device and memory system including nonvolatile memory device

Owner:SAMSUNG ELECTRONICS CO LTD

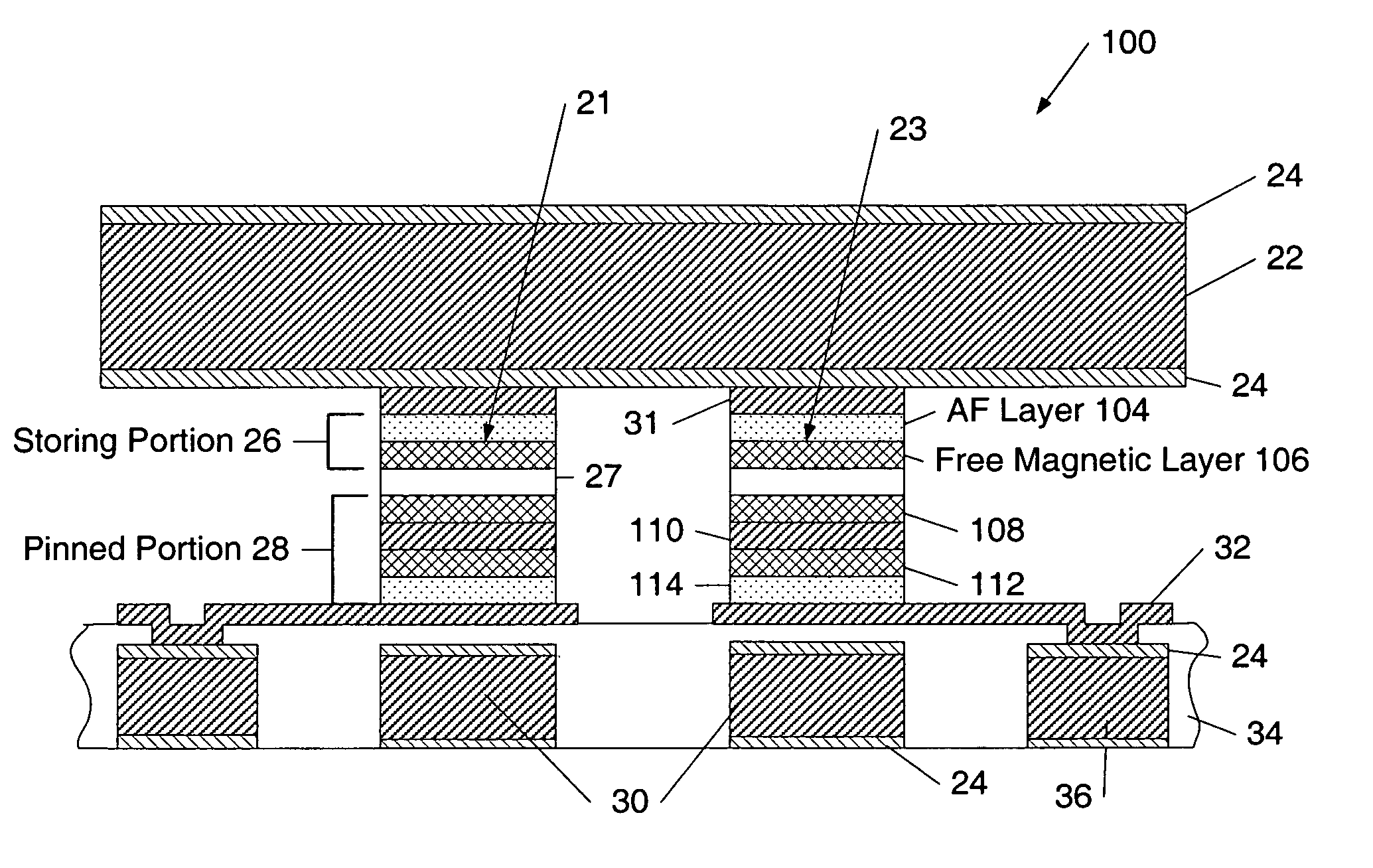

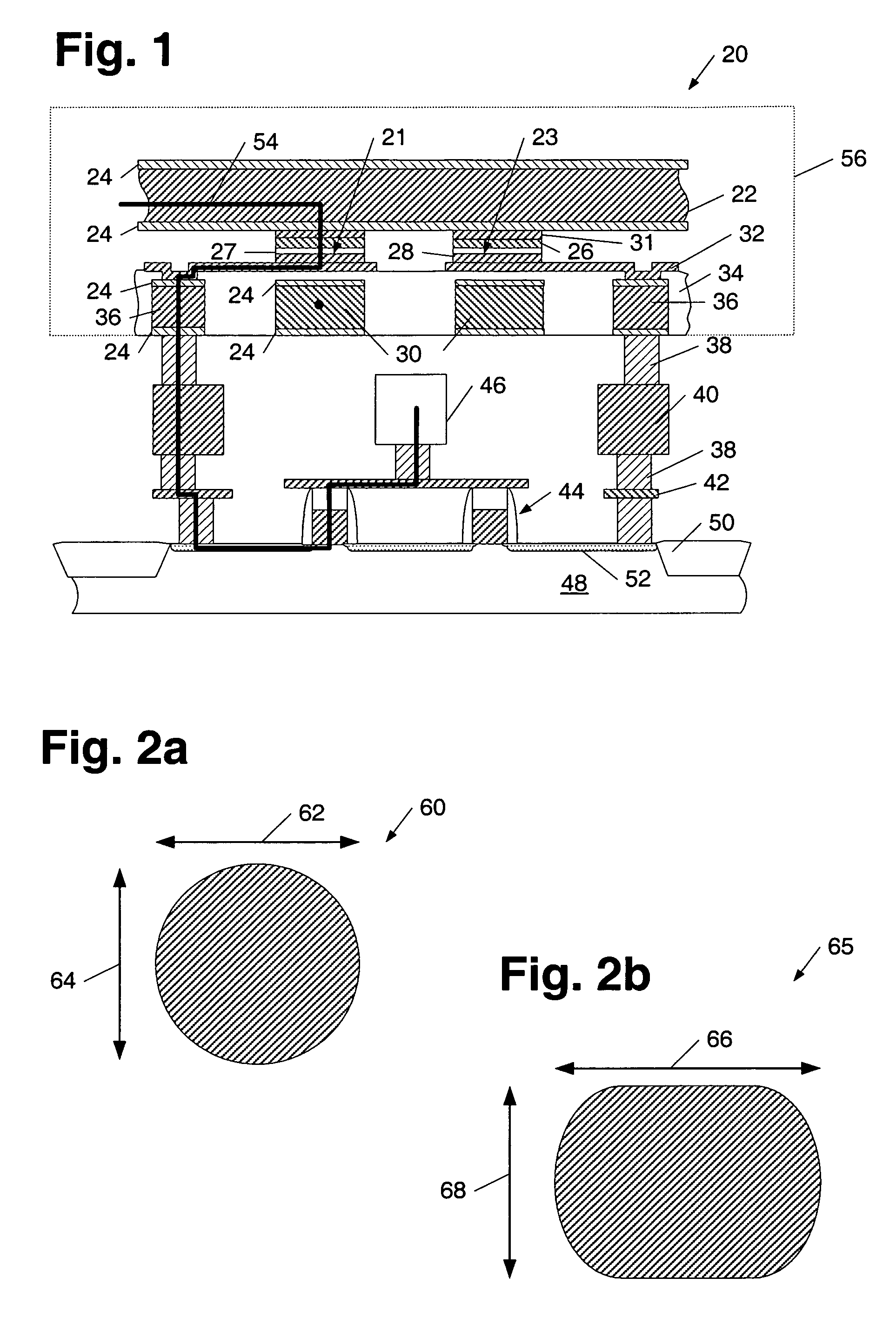

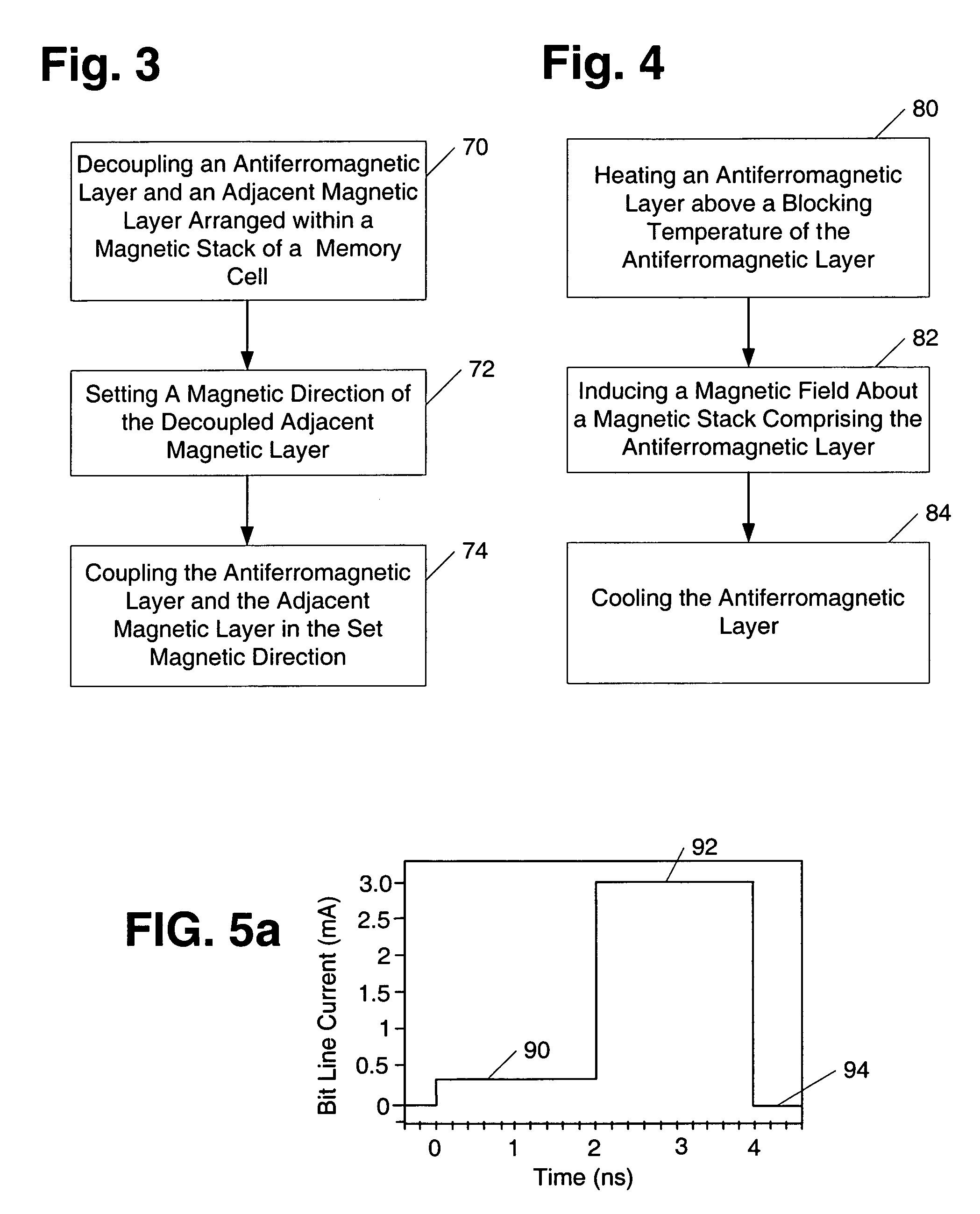

High density MRAM using thermal writing

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

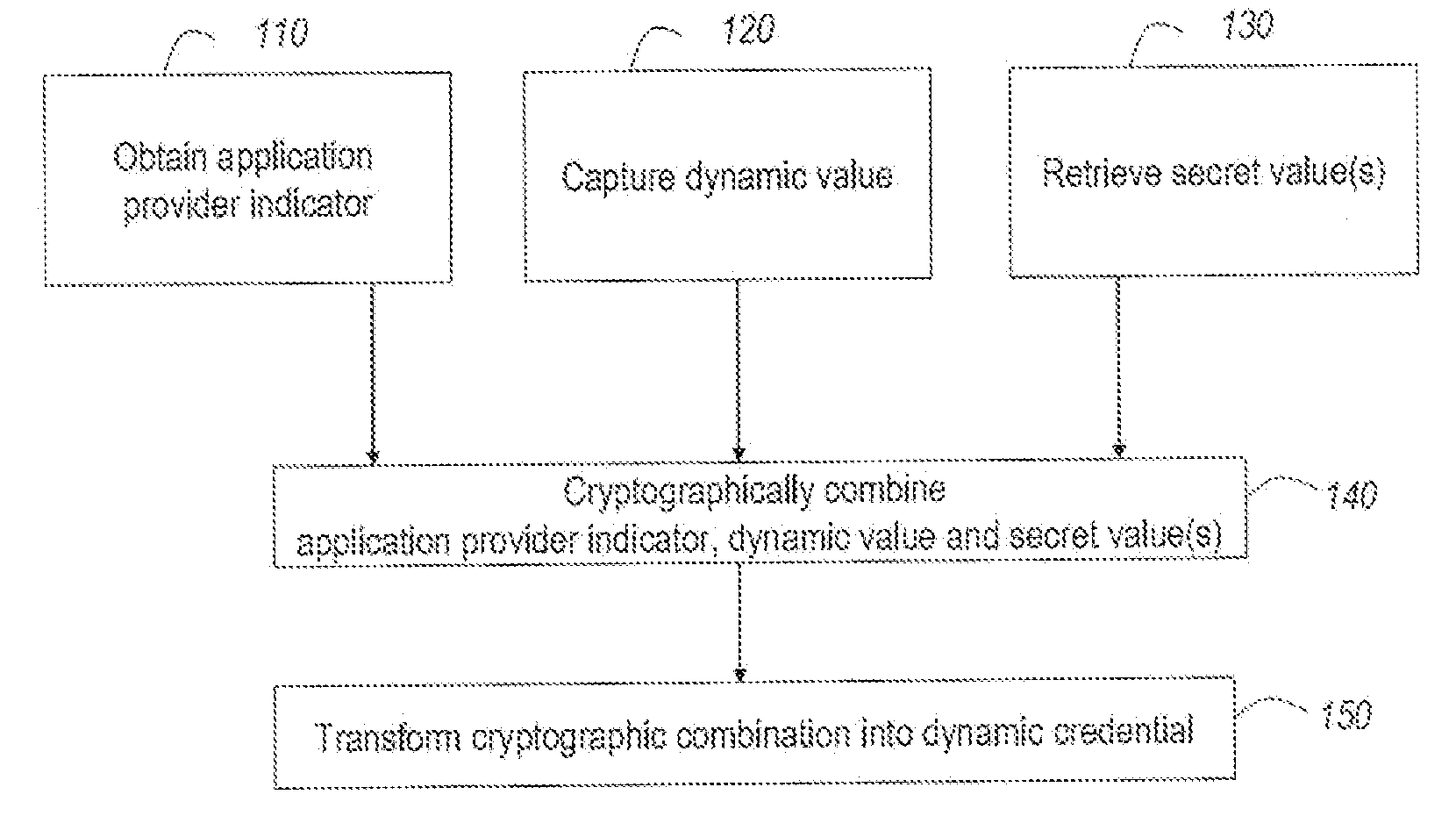

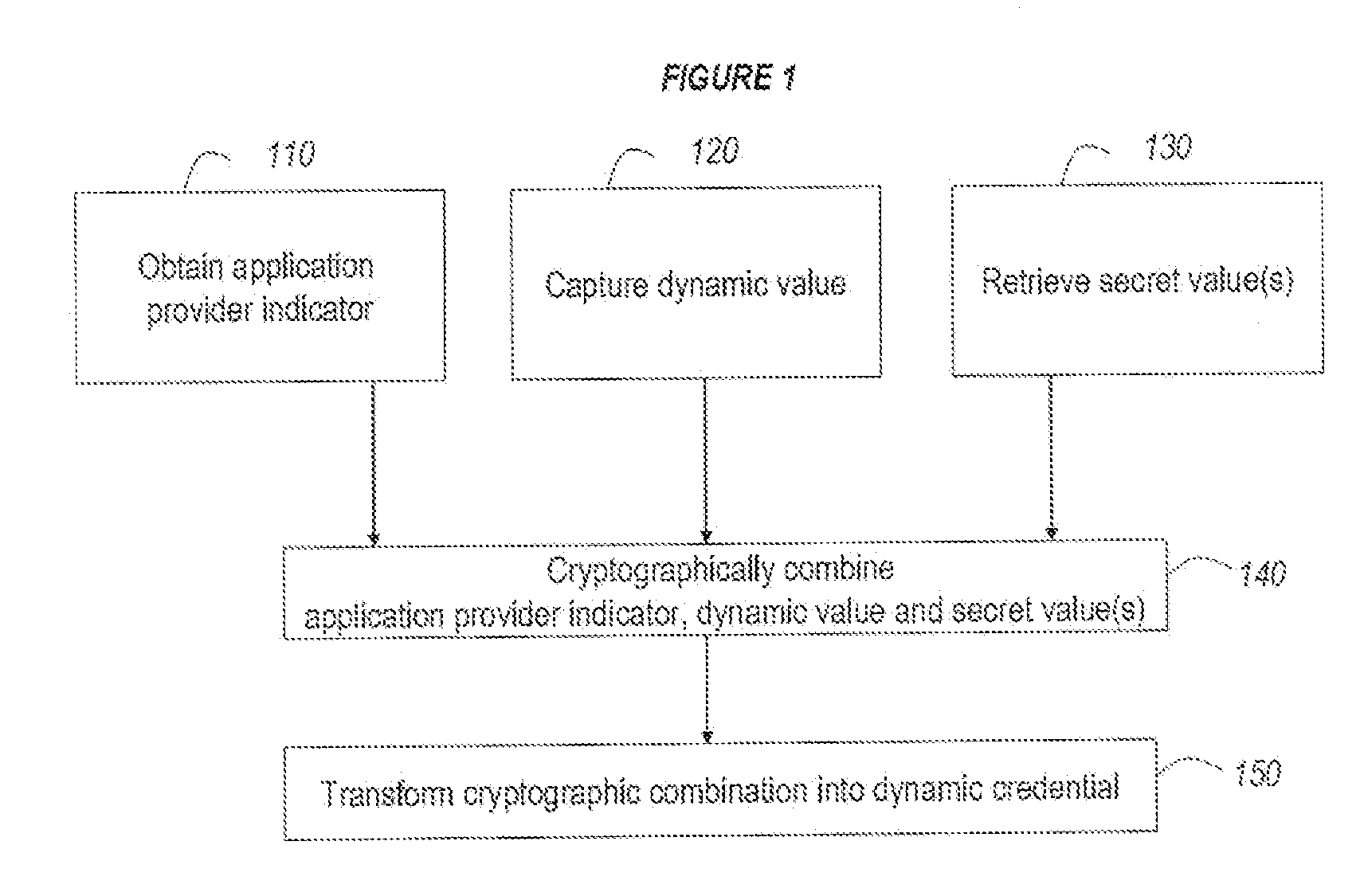

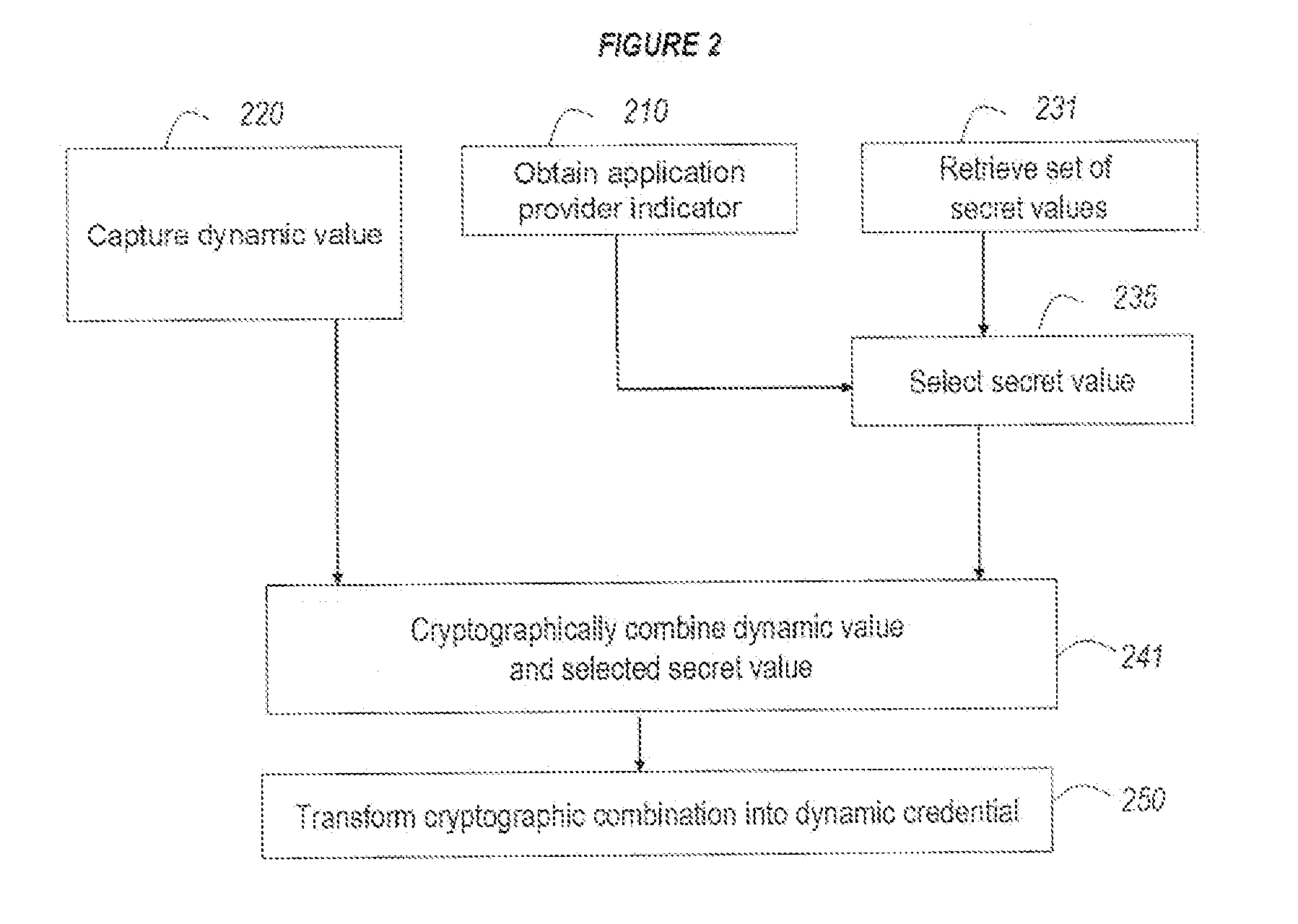

Strong authentication token usable with a plurality of independent application providers

ActiveUS20110099384A1Low costCost can be dividedMultiple keys/algorithms usageDigital data processing detailsPersonalizationUnique identifier

Owner:ONESPAN NORTH AMERICA INC

Apparatus and Method for Variable Authentication Requirements

ActiveUS20120239950A1Volume/mass flow measurementUser identity/authority verificationState dependentAuthentication

Owner:LENOVO PC INT

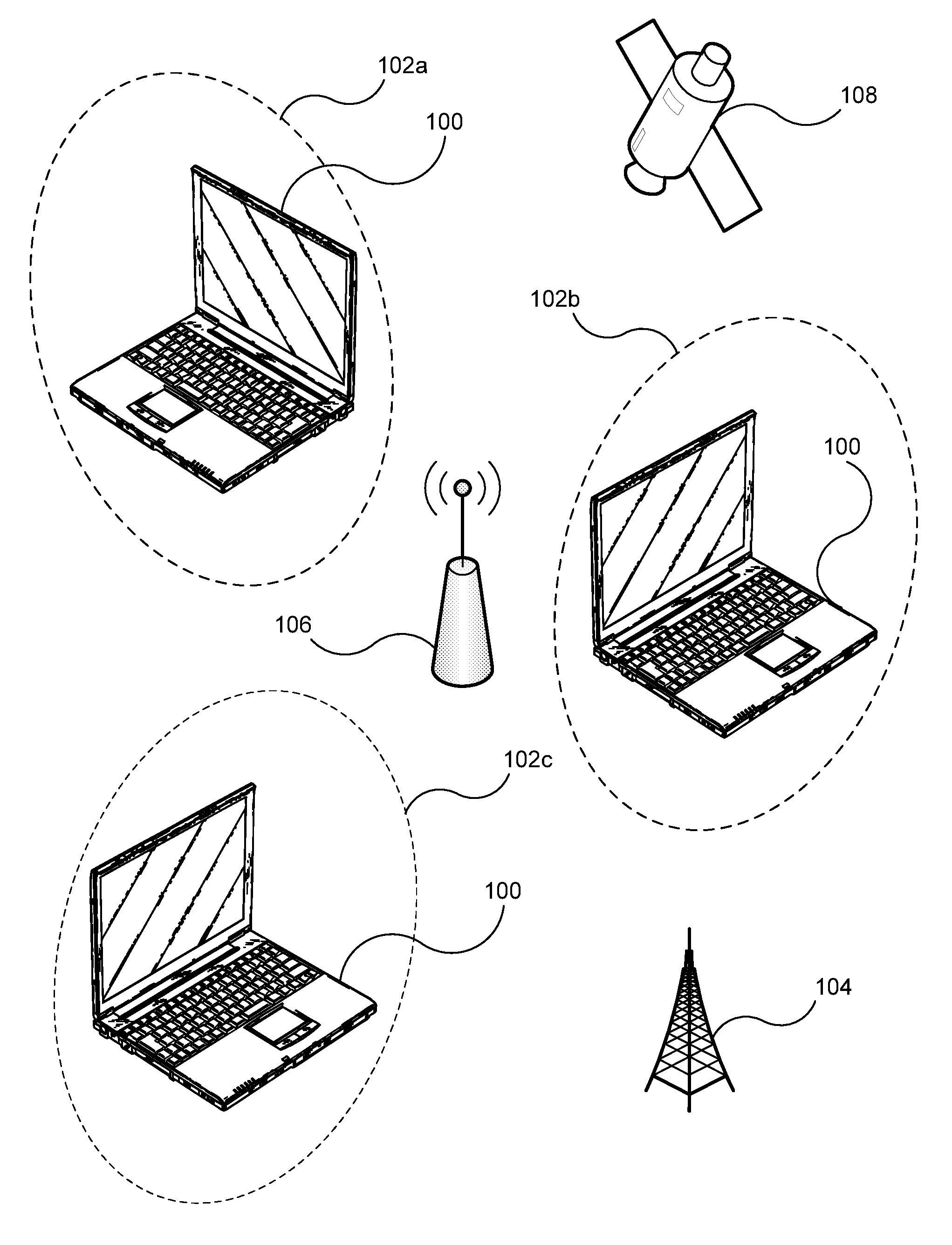

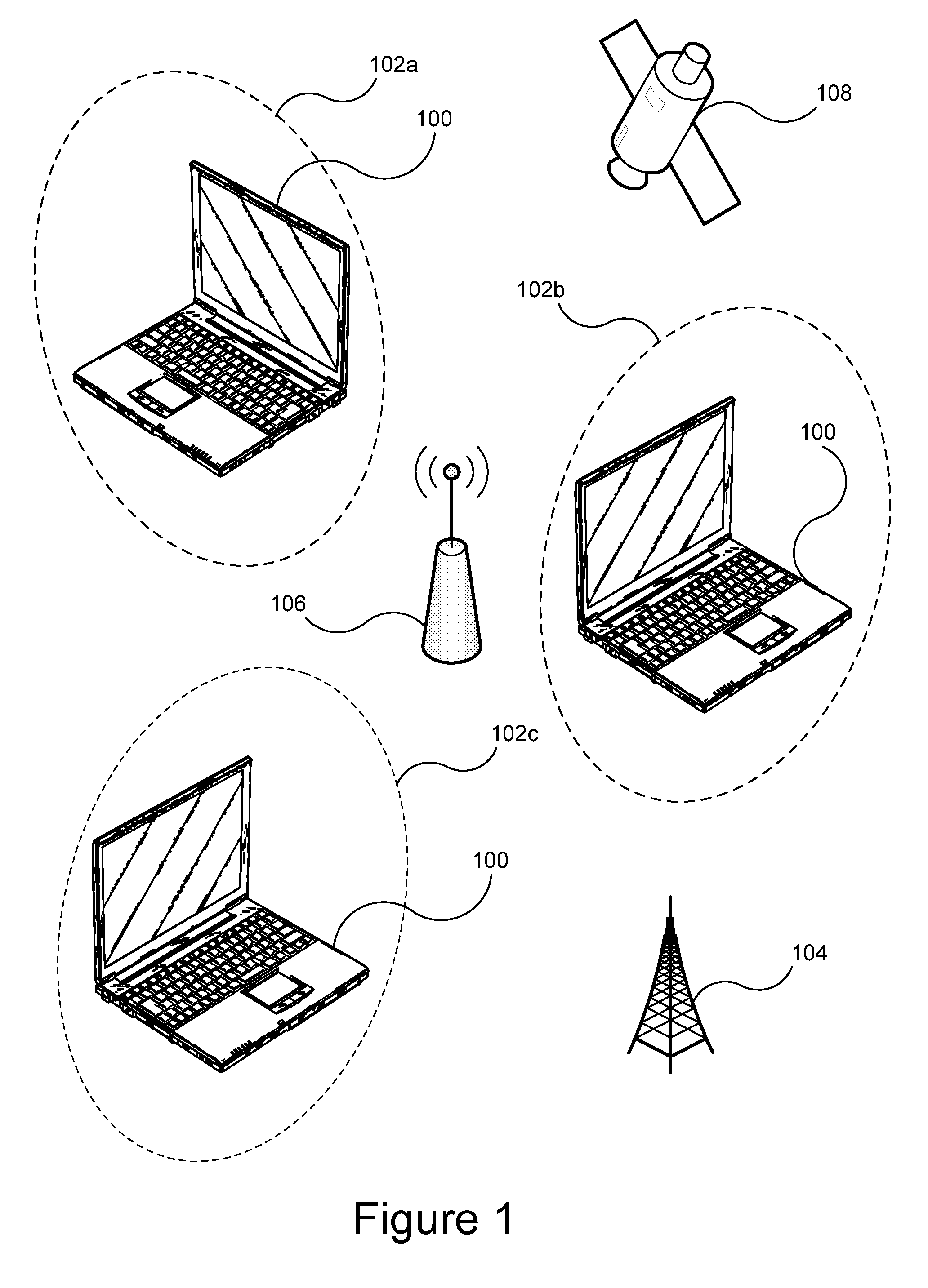

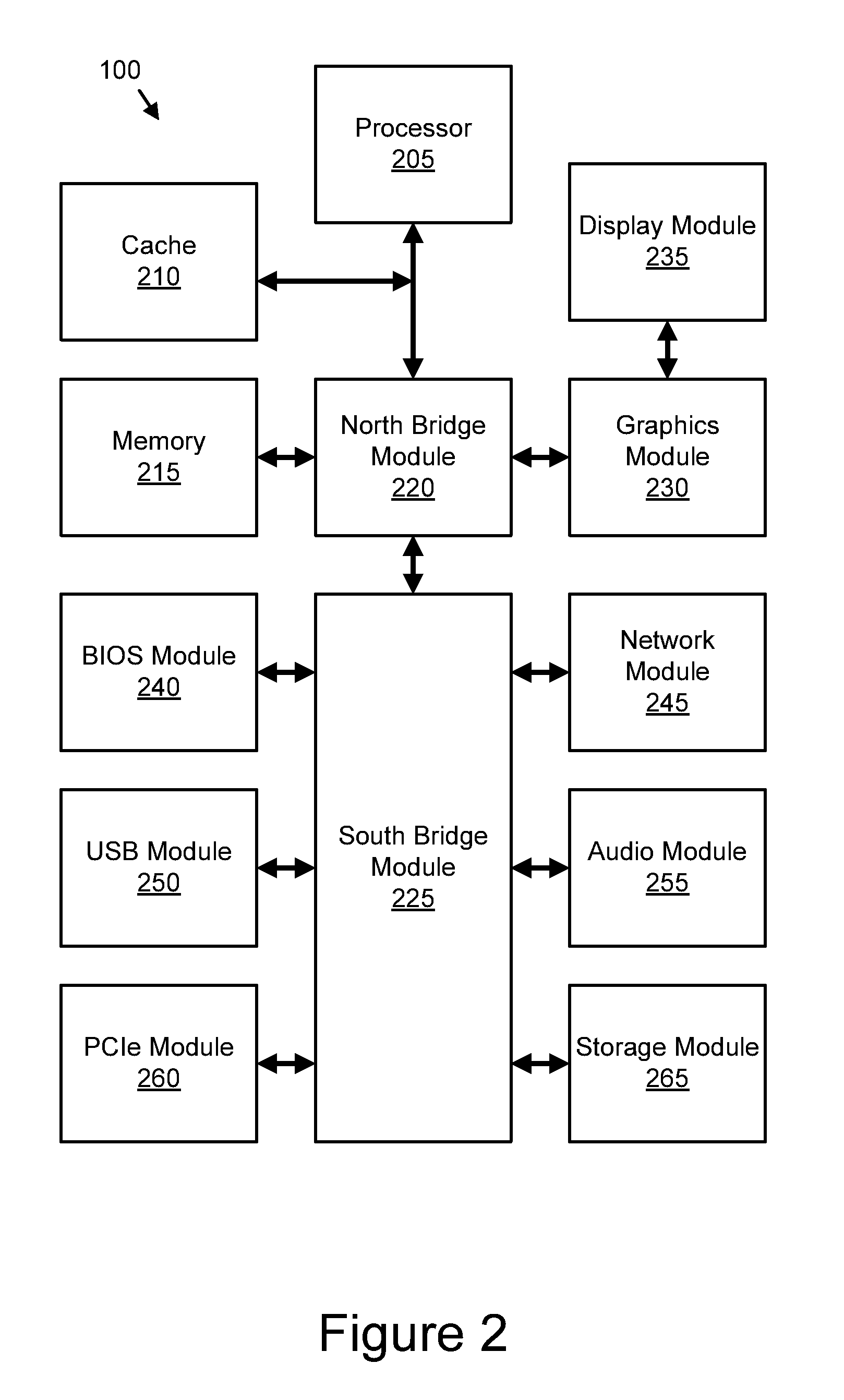

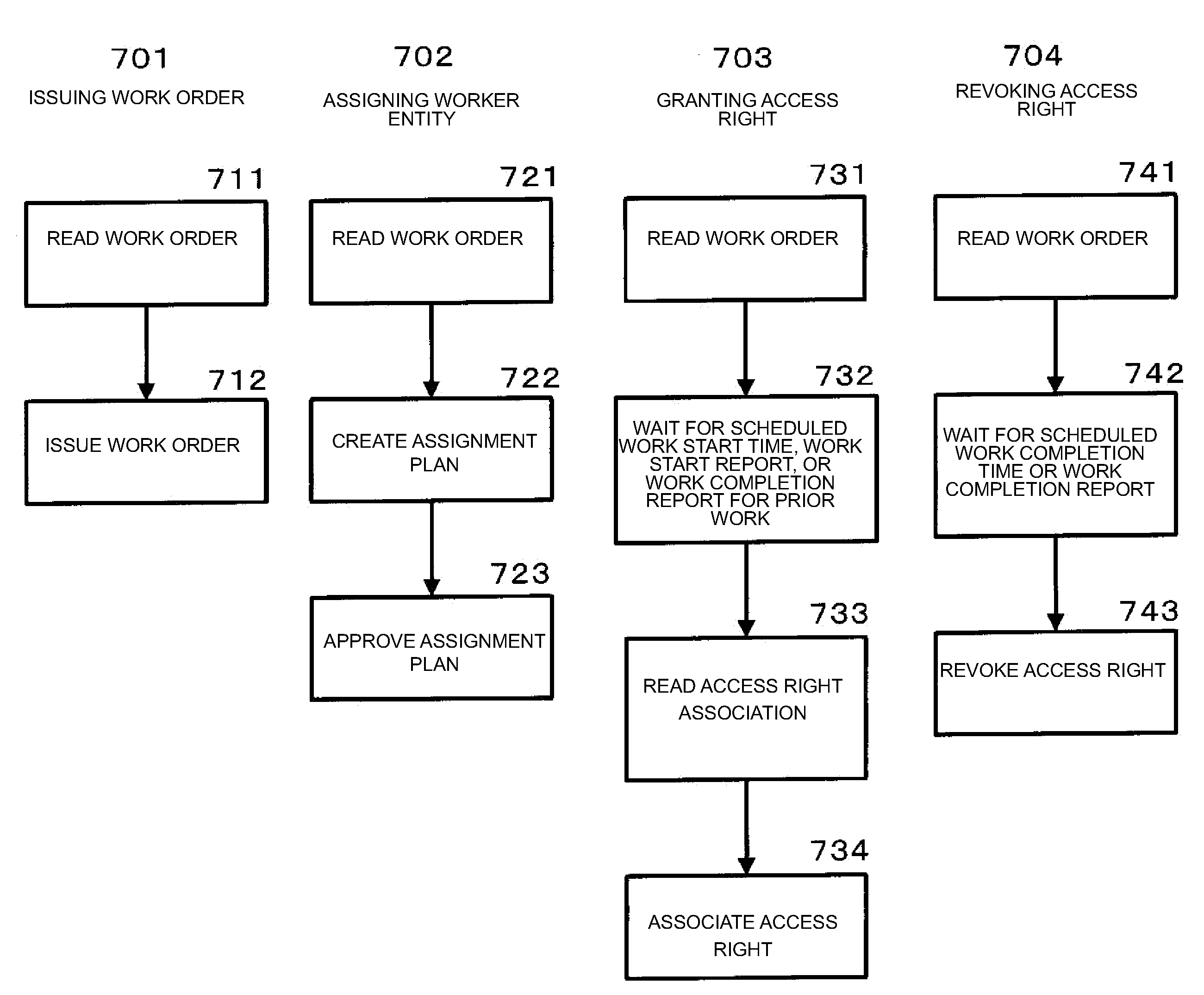

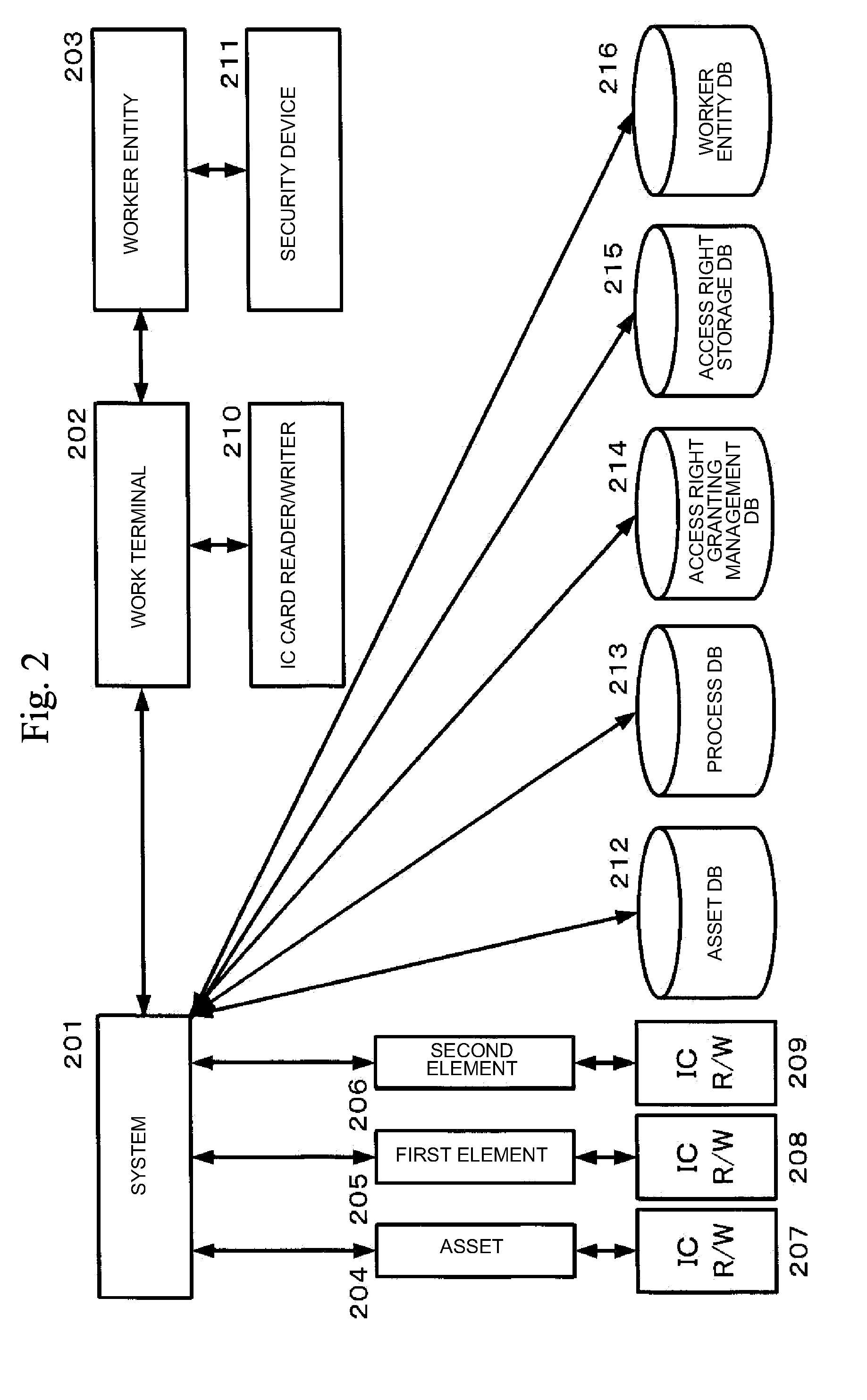

Method of Managing Access Right, and System and Computer Program for the Same

InactiveUS20120095797A1Digital data processing detailsUnauthorized memory use protectionRights managementDigital work

Owner:IBM CORP

Centralized Device Virtualization Layer For Heterogeneous Processing Units

ActiveUS20100146620A1Operational speed enhancementResource allocationVirtualizationOperational system

A method for providing an operating system access to devices, including enumerating hardware devices and virtualized devices, where resources associated with a first hardware device are divided into guest physical resources creating a software virtualized device, and multiple instances of resources associated with a second hardware device are advertised thereby creating a hardware virtualized device. First and second permission lists are generated that specify which operating systems are permitted to access the software virtualized device and the hardware virtualized device, respectively. First and second sets of virtual address maps are generated, where each set maps an address space associated with either the software virtualized device or the hardware virtualized device into an address space associated with each operating system included in the corresponding permission list. The method further includes arbitrating access requests from each of the plurality of operating systems based on the permission lists and the virtual address maps.

Owner:NVIDIA CORP

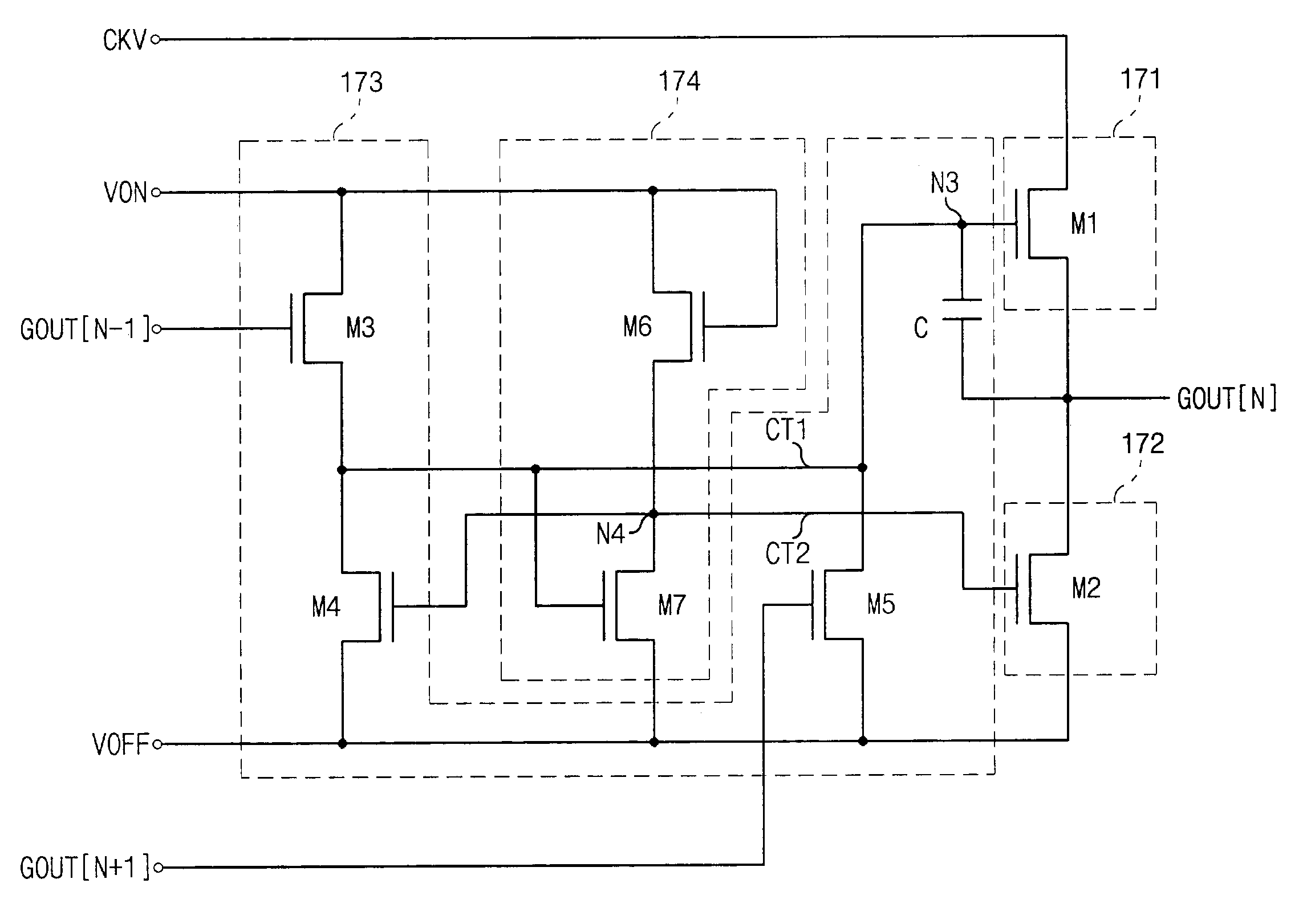

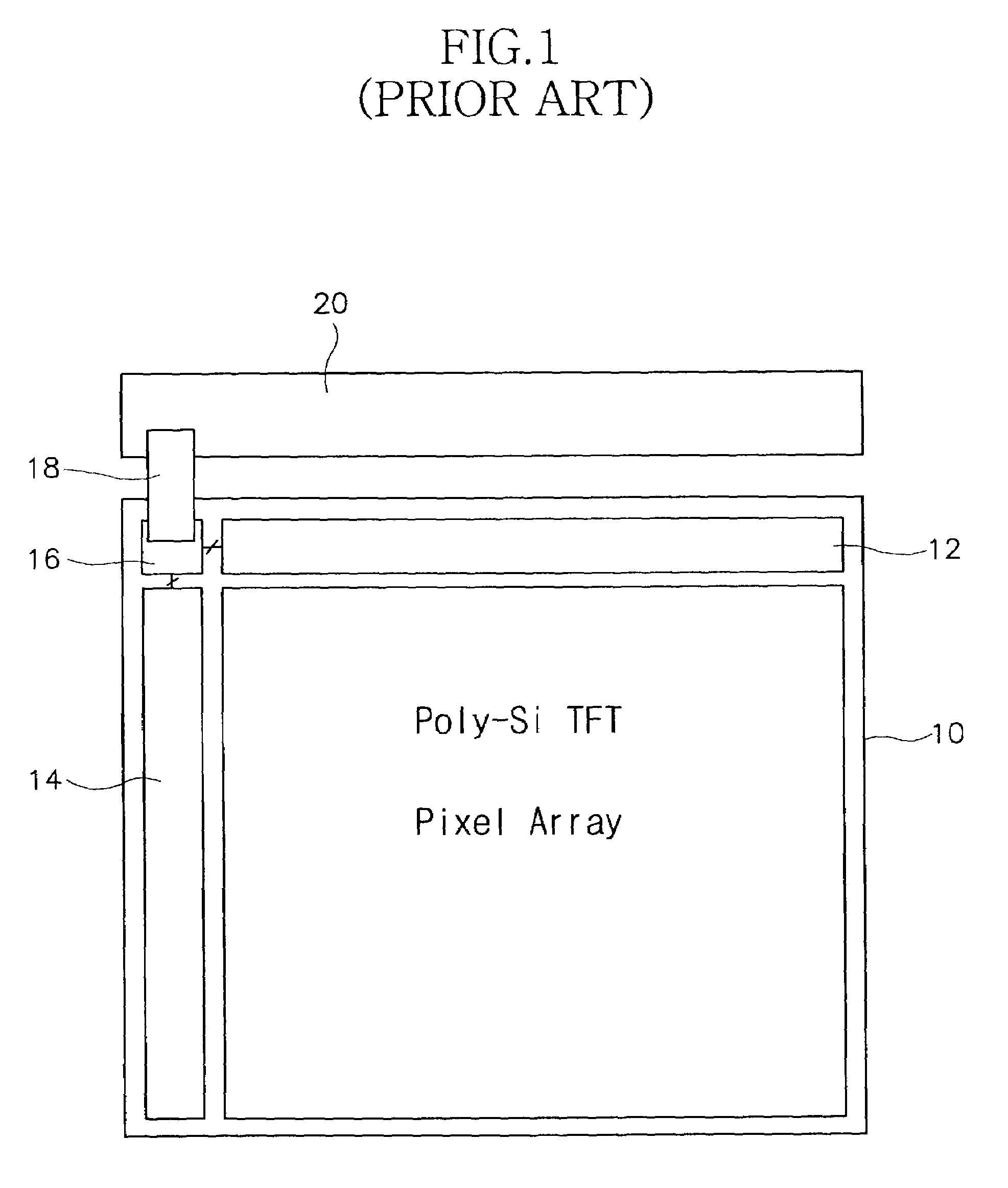

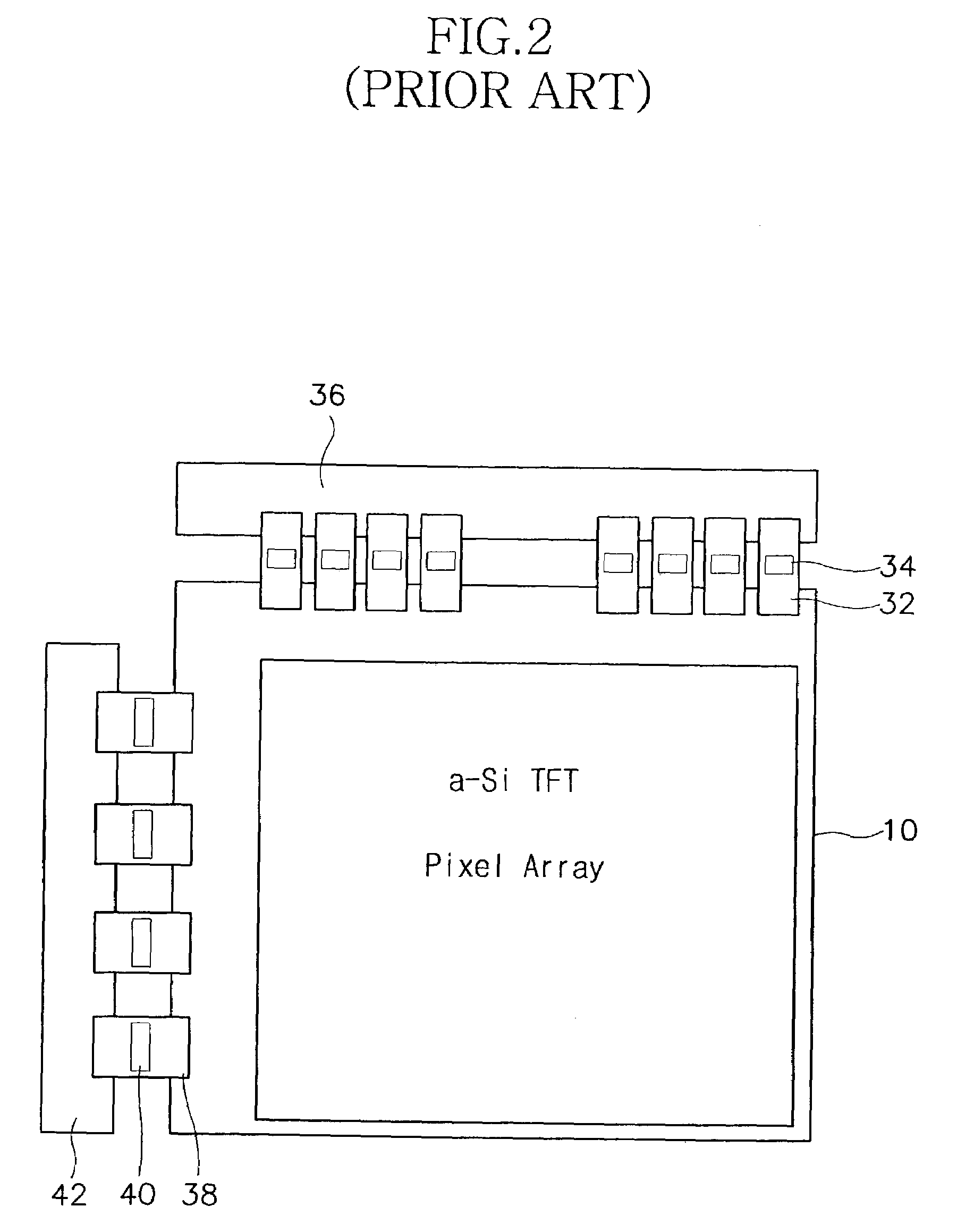

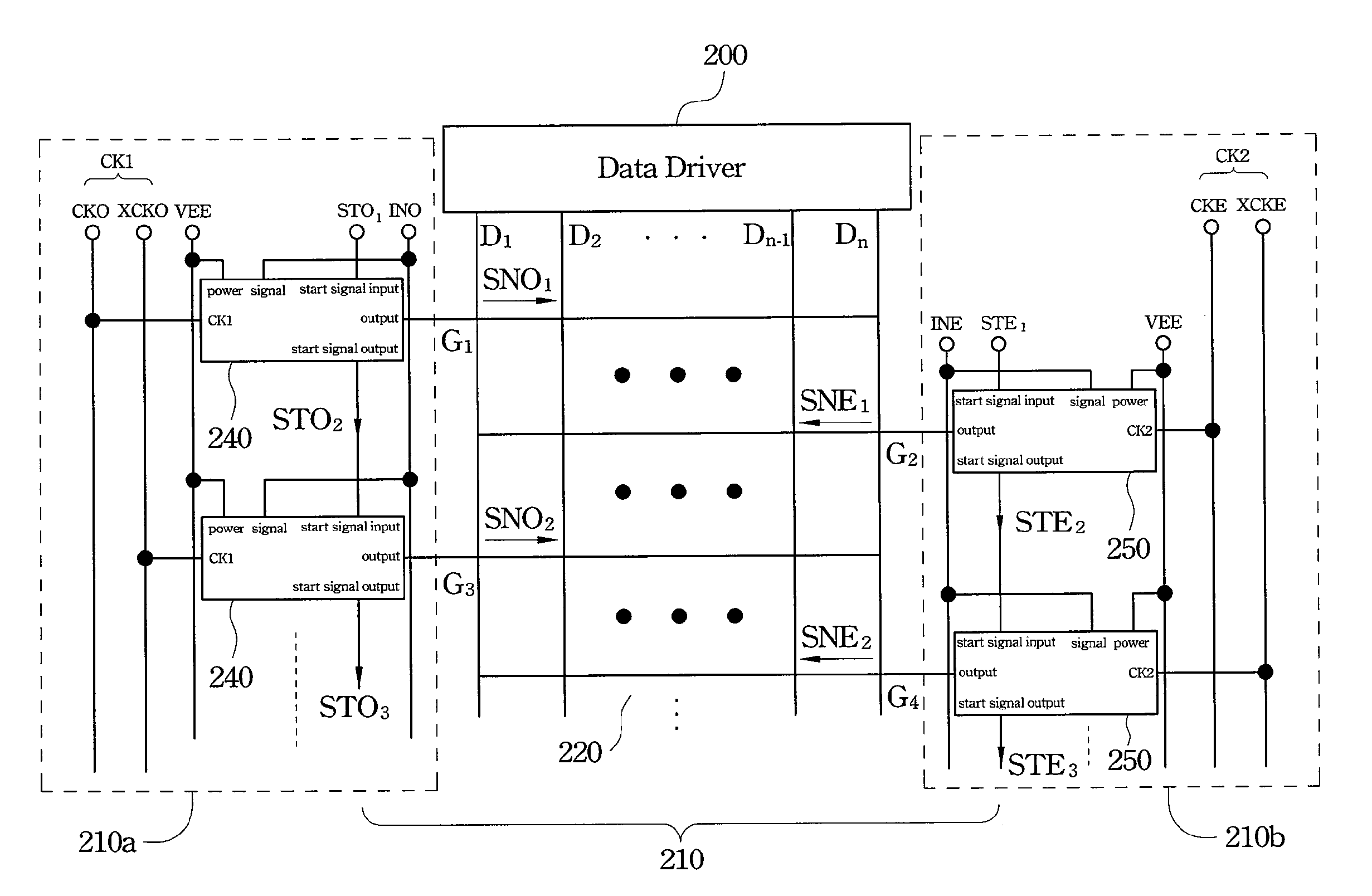

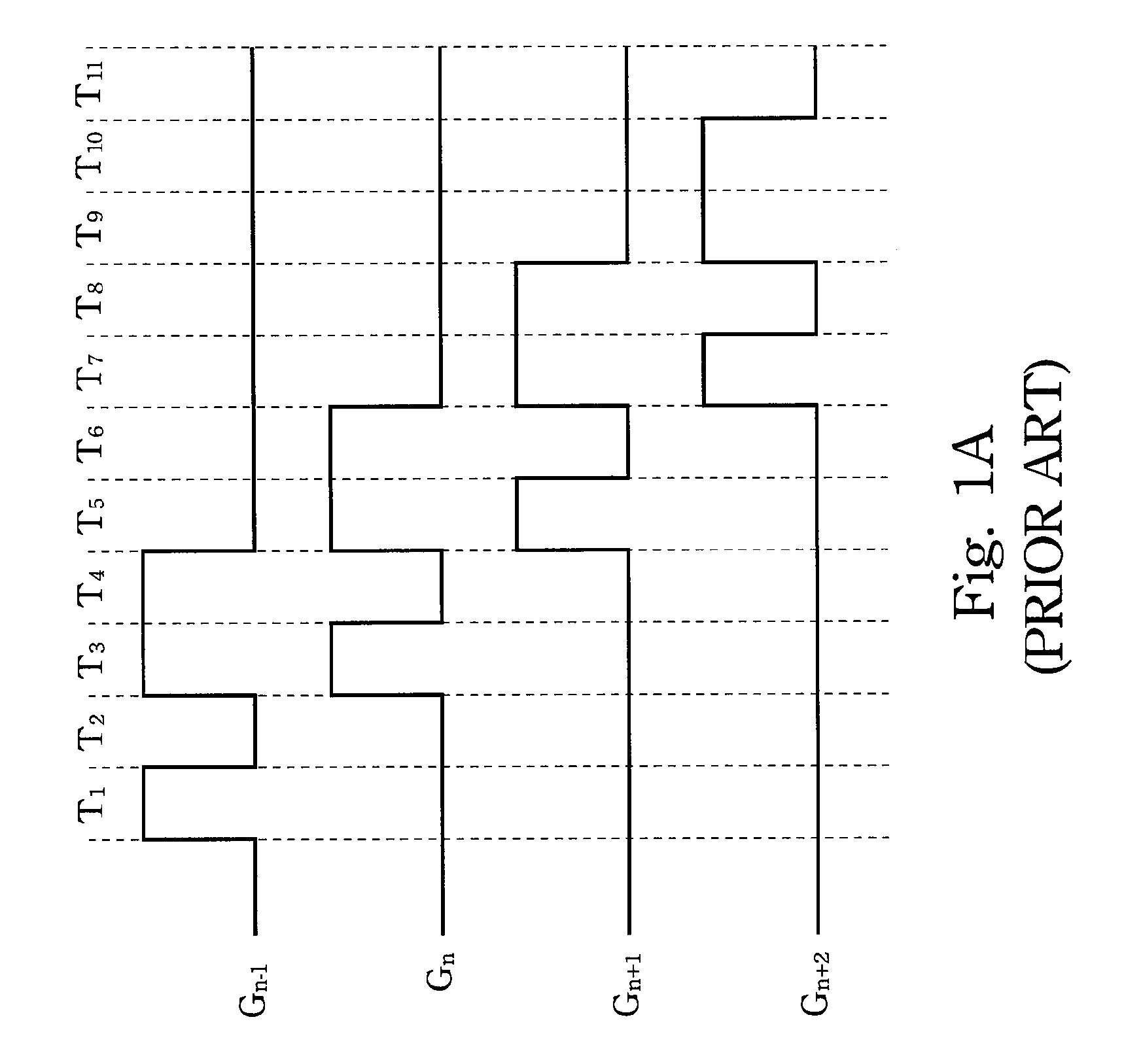

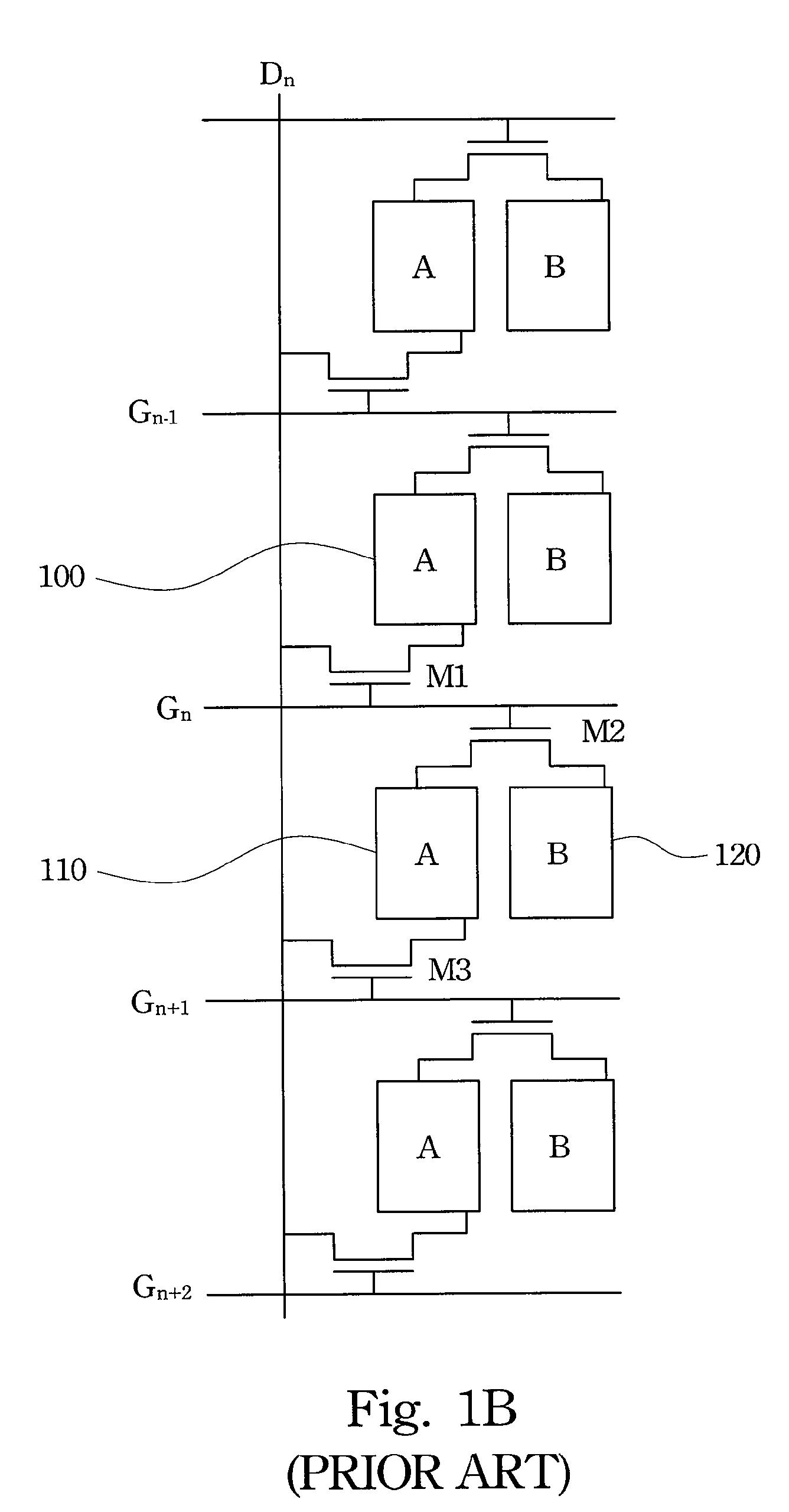

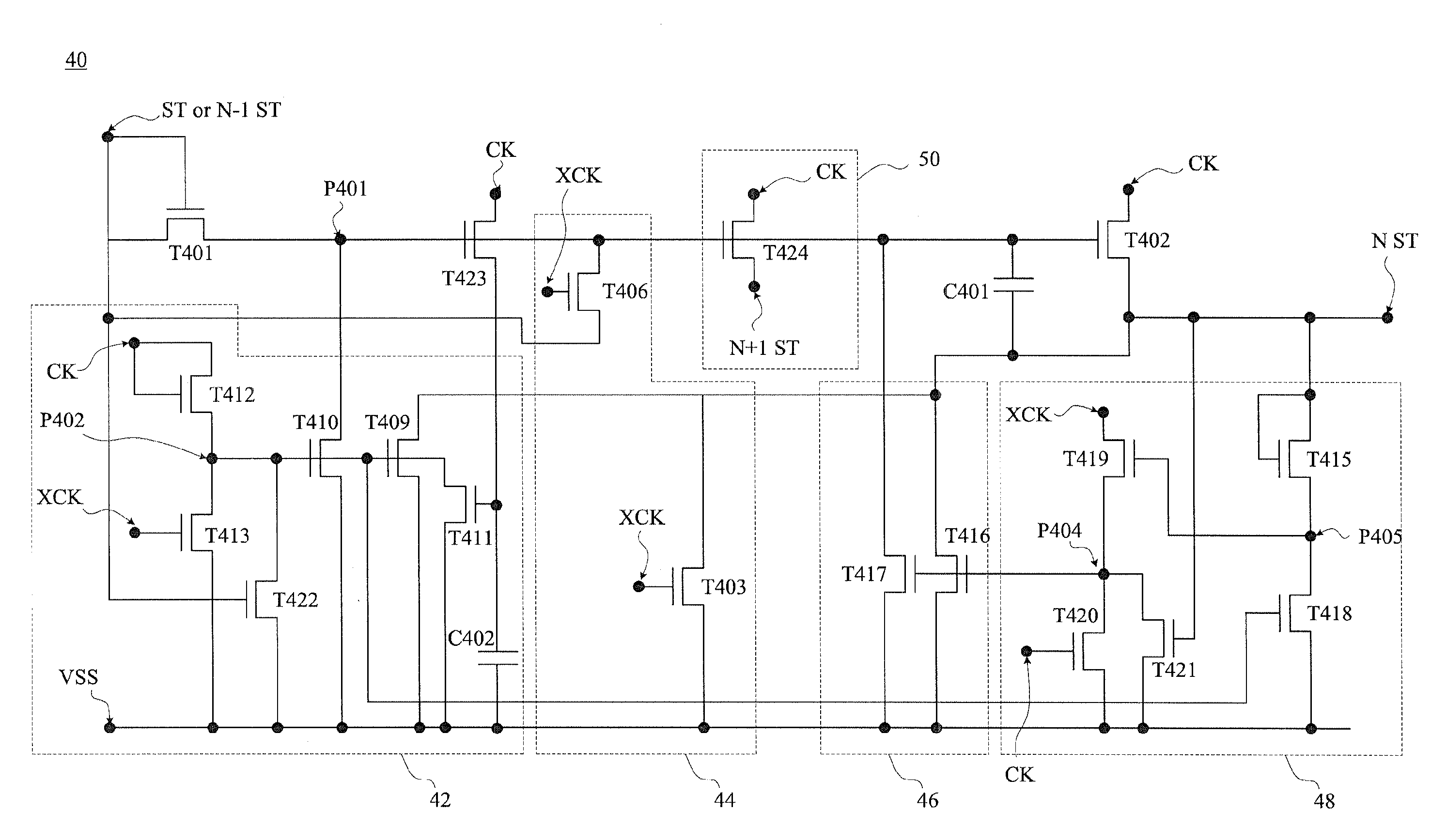

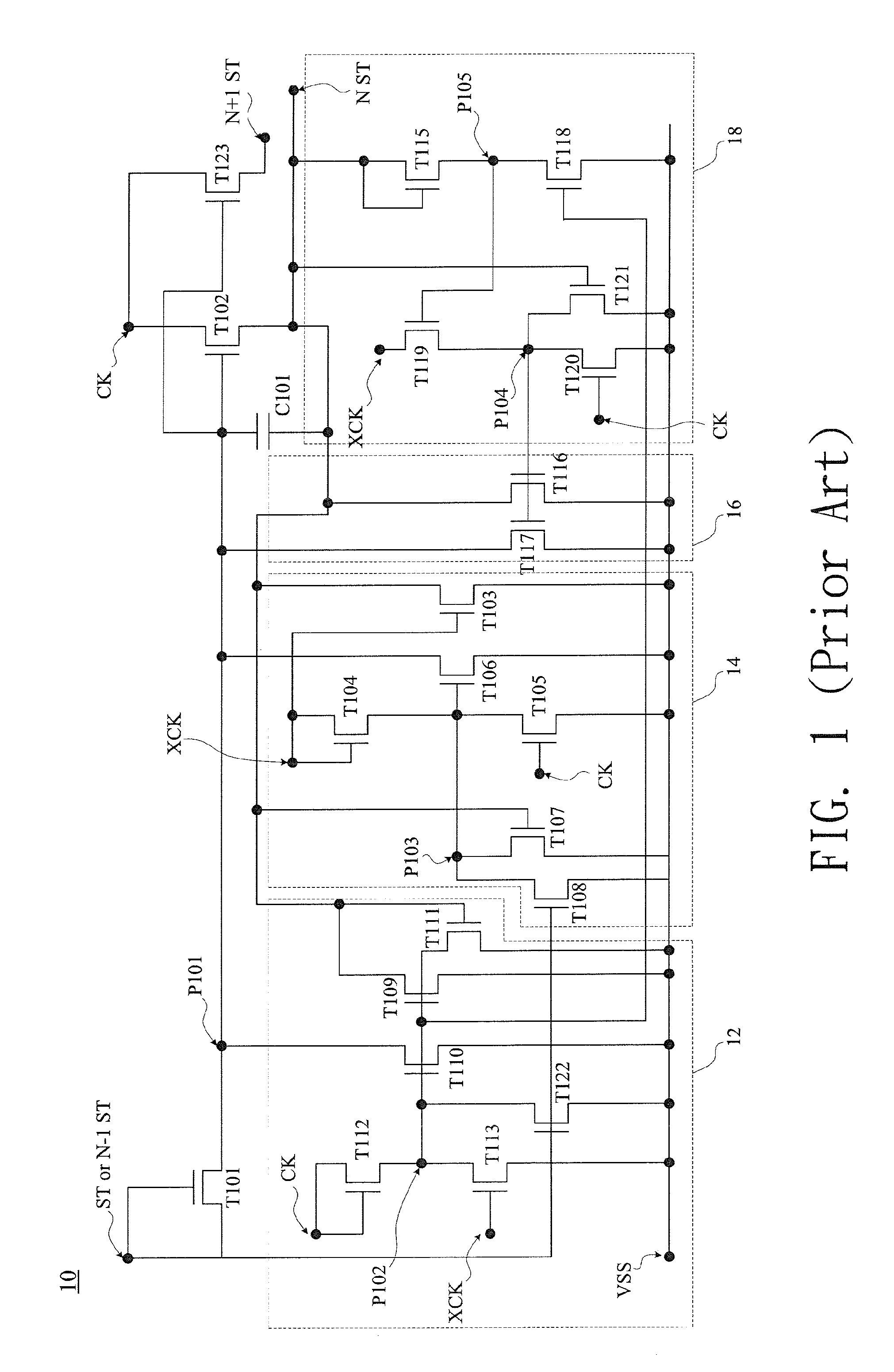

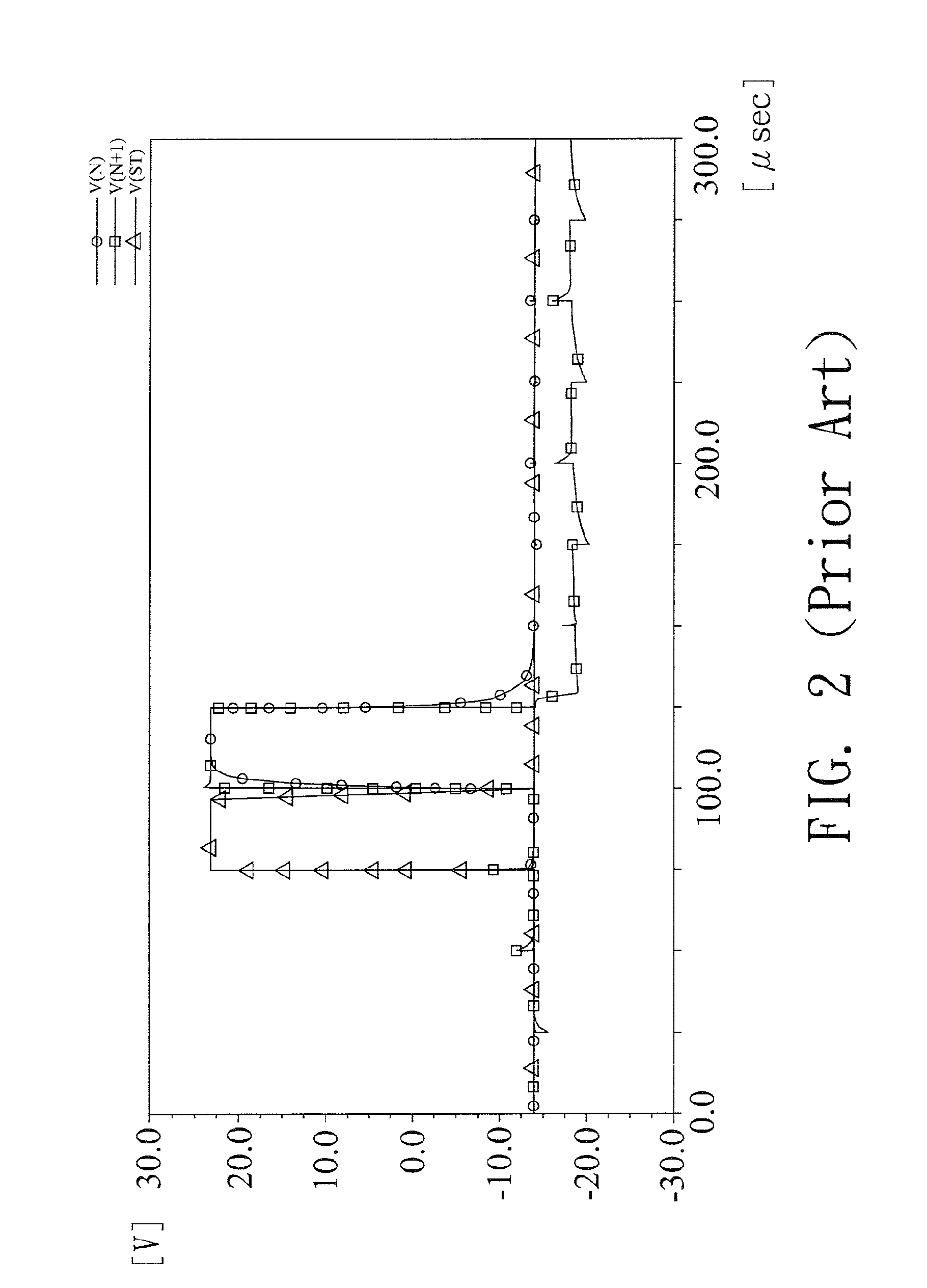

Gate Driver and Driving Method Thereof in Liquid Crystal Display

ActiveUS20080174580A1Low production costCathode-ray tube indicatorsDigital storageStart signalGate driver

Owner:AU OPTRONICS CORP

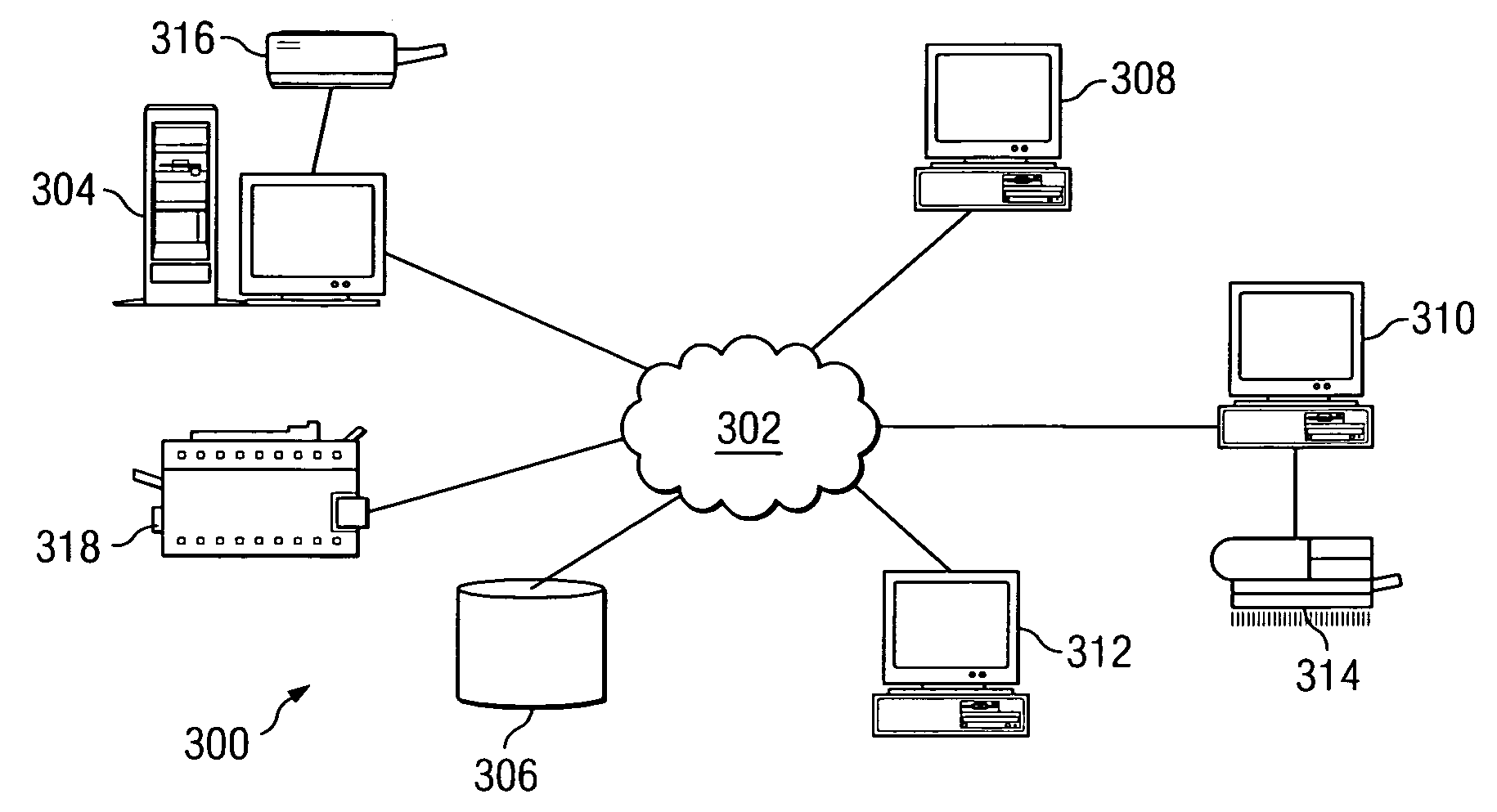

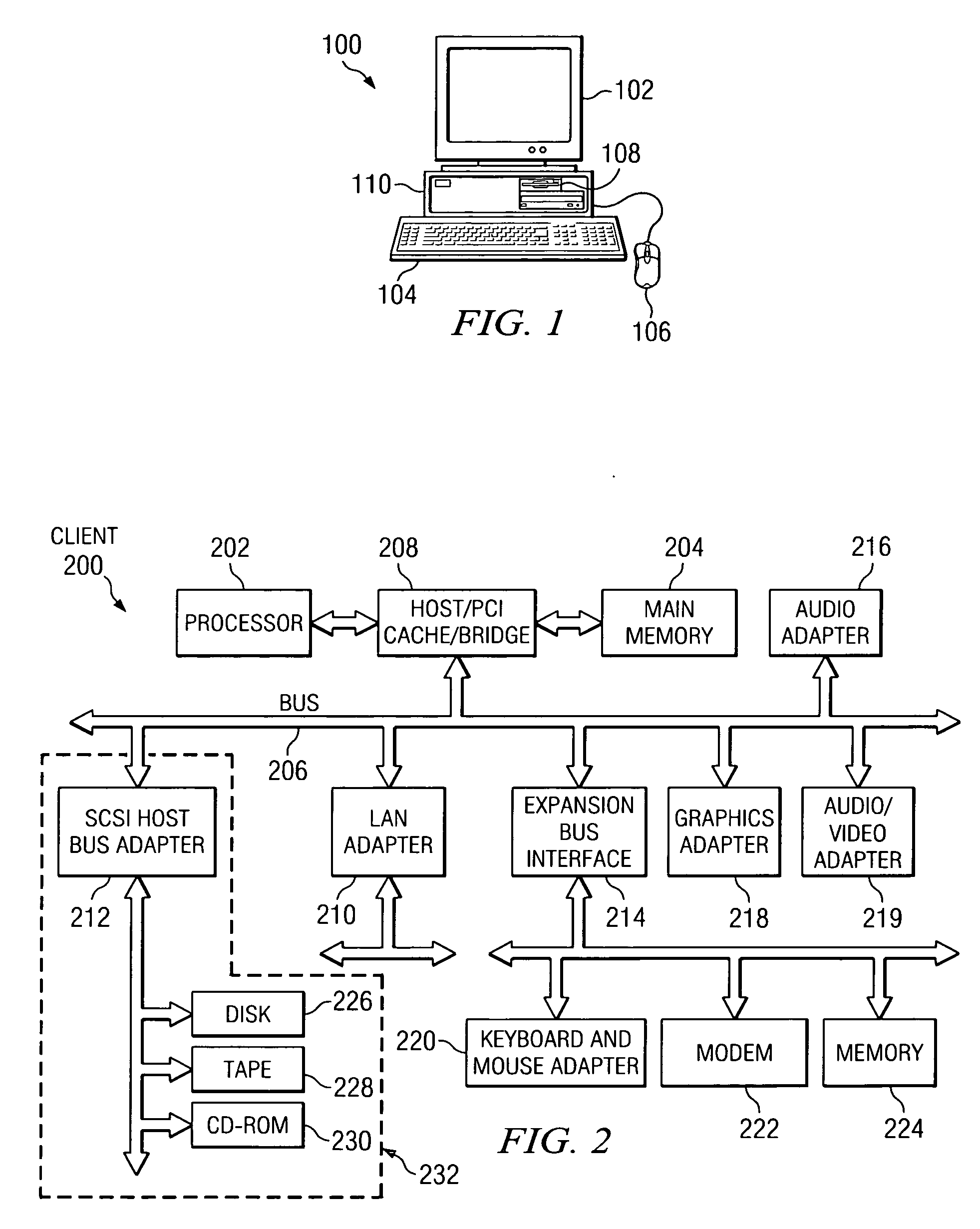

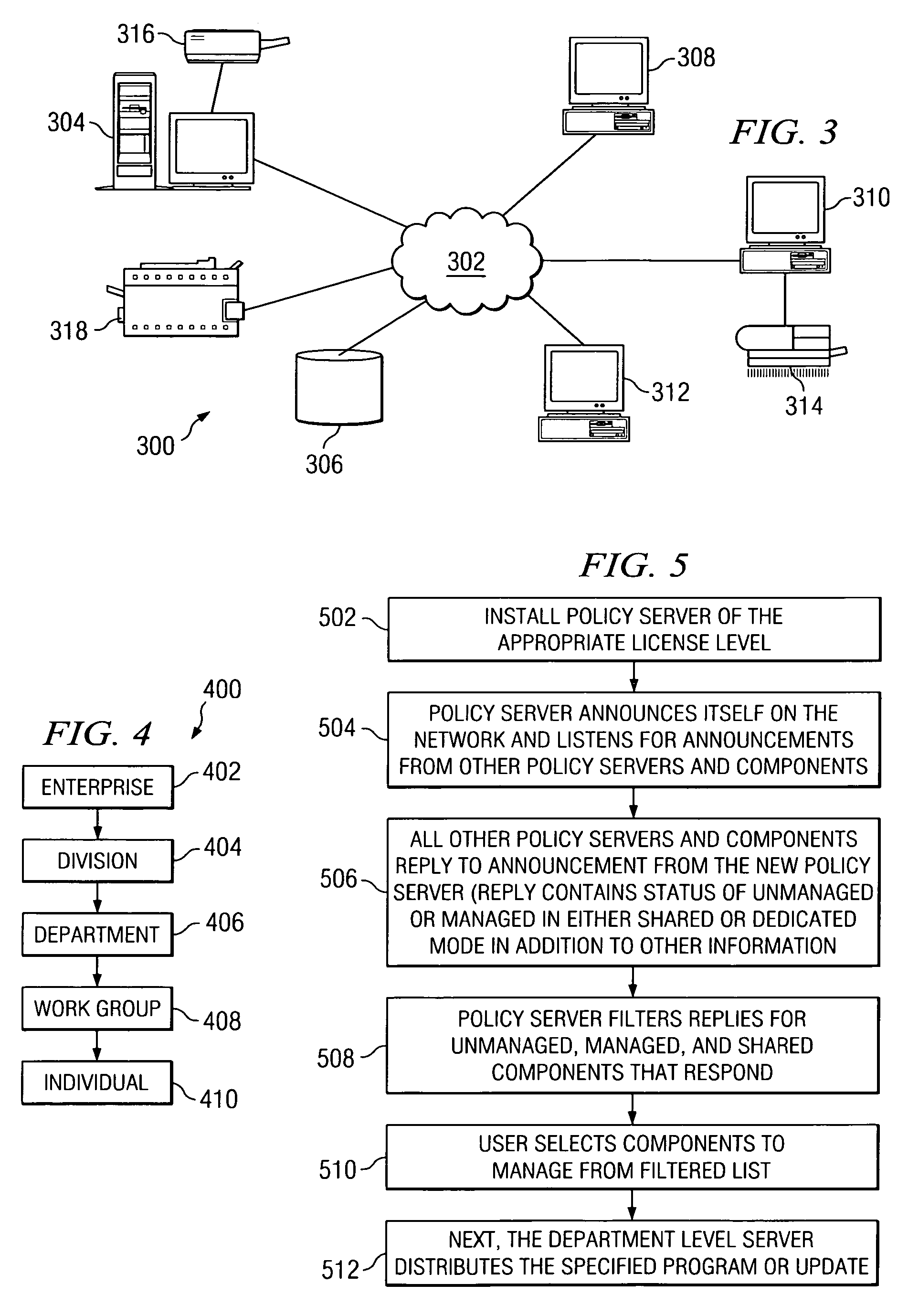

Use of policy levels to enforce enterprise control

InactiveUS20060225123A1Digital data processing detailsUnauthorized memory use protectionDistributed computingSoftware

Owner:TREND MICRO INC

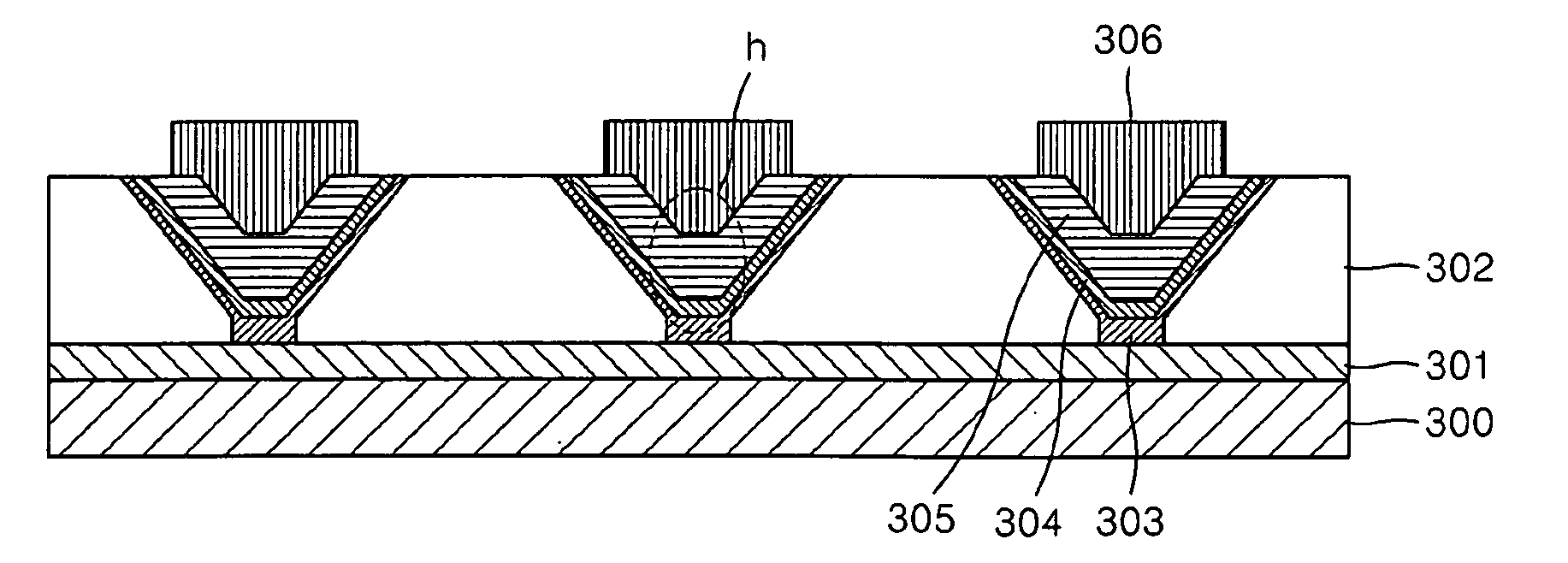

Shift register with individual driving node

ActiveUS20080285705A1Reduce test complexityStatic indicating devicesDigital storageElectricityShift register

Owner:AU OPTRONICS CORP

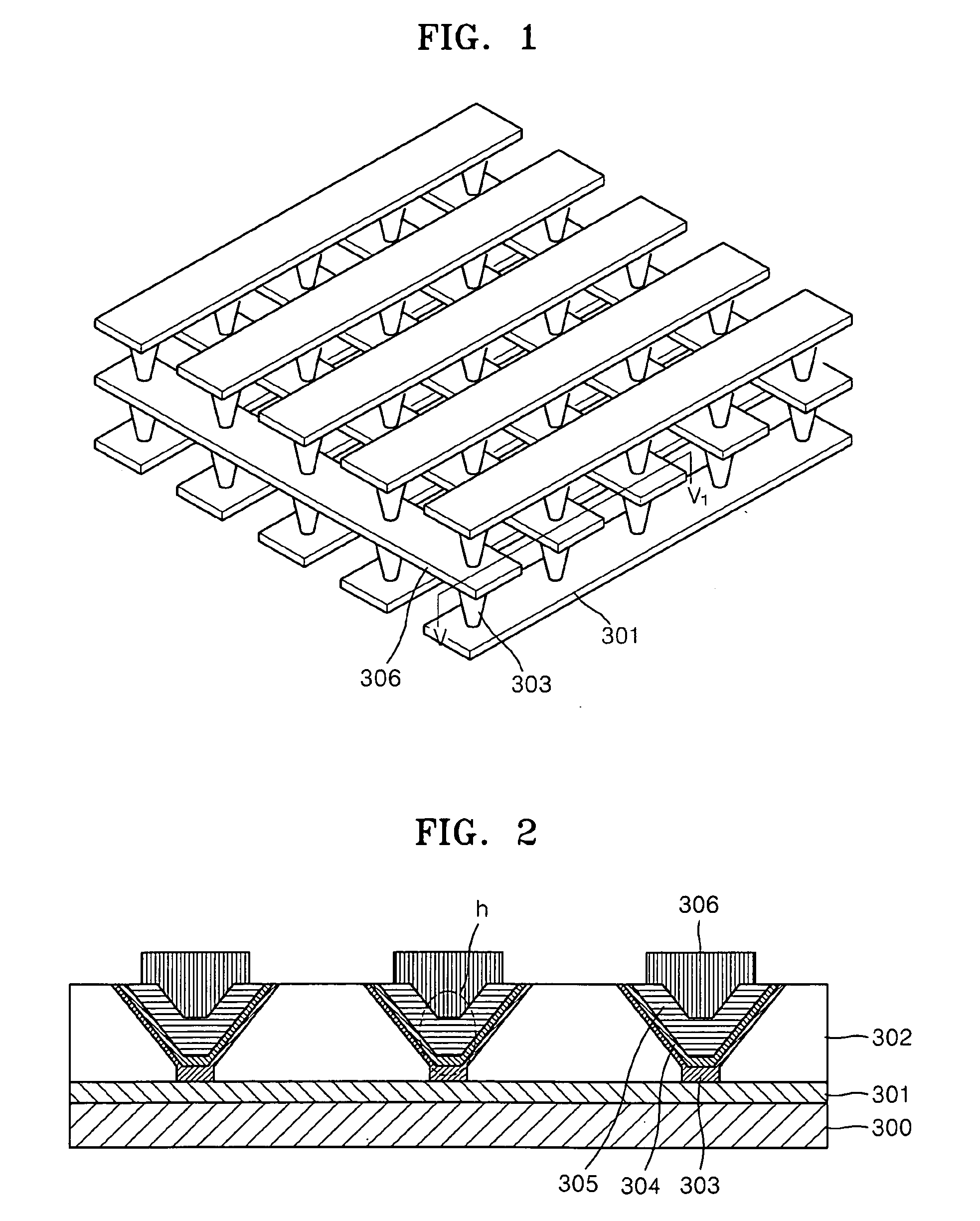

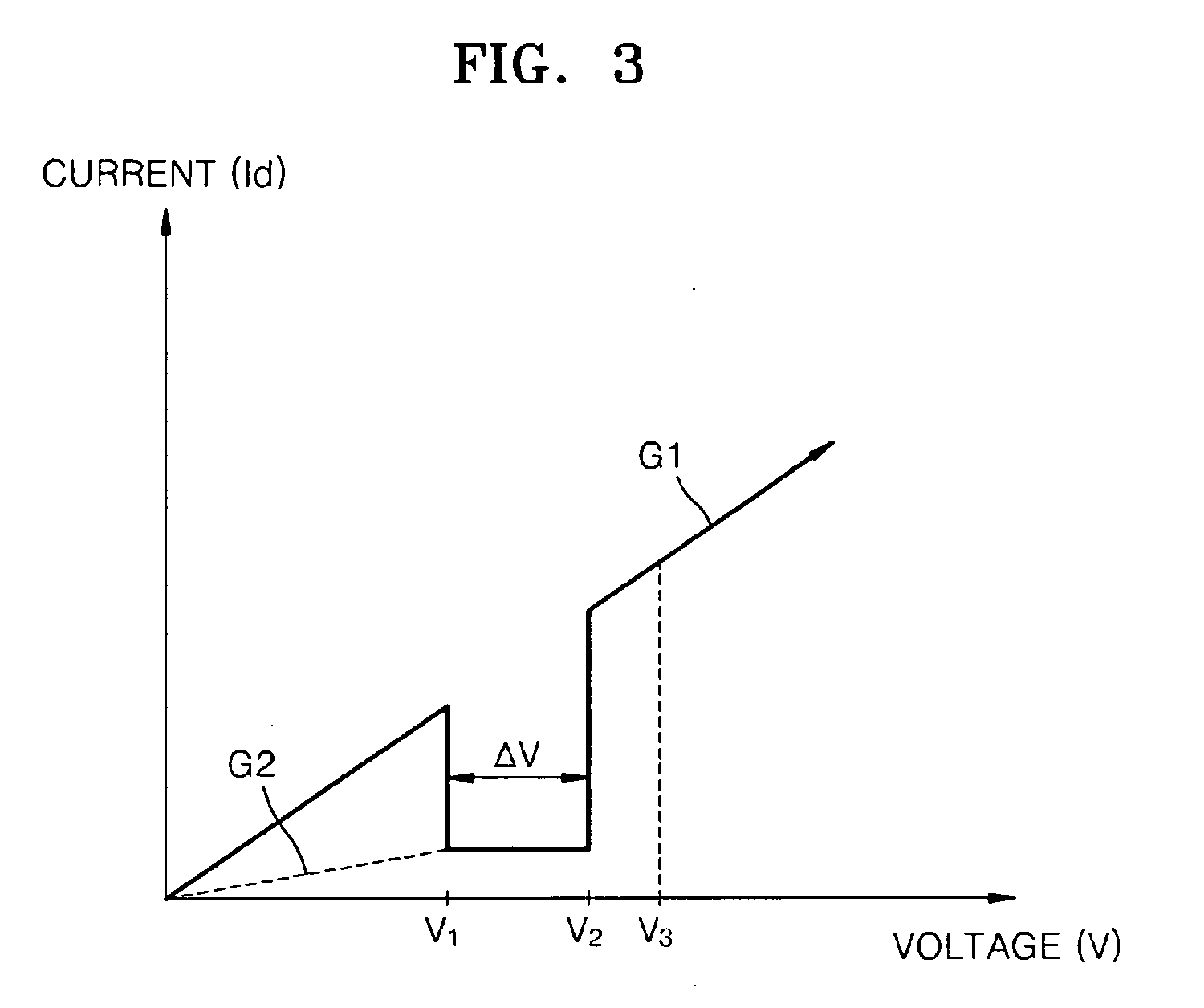

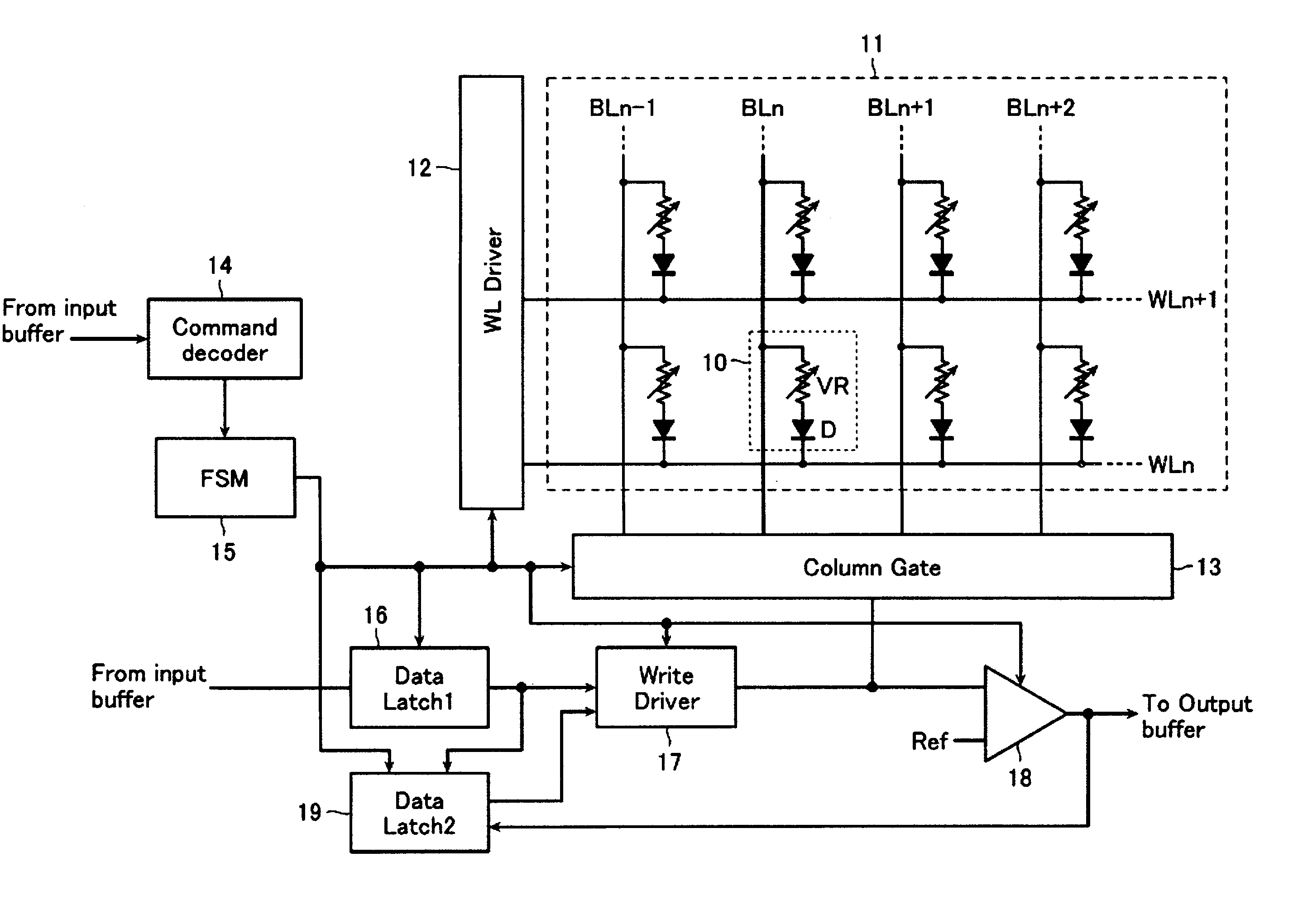

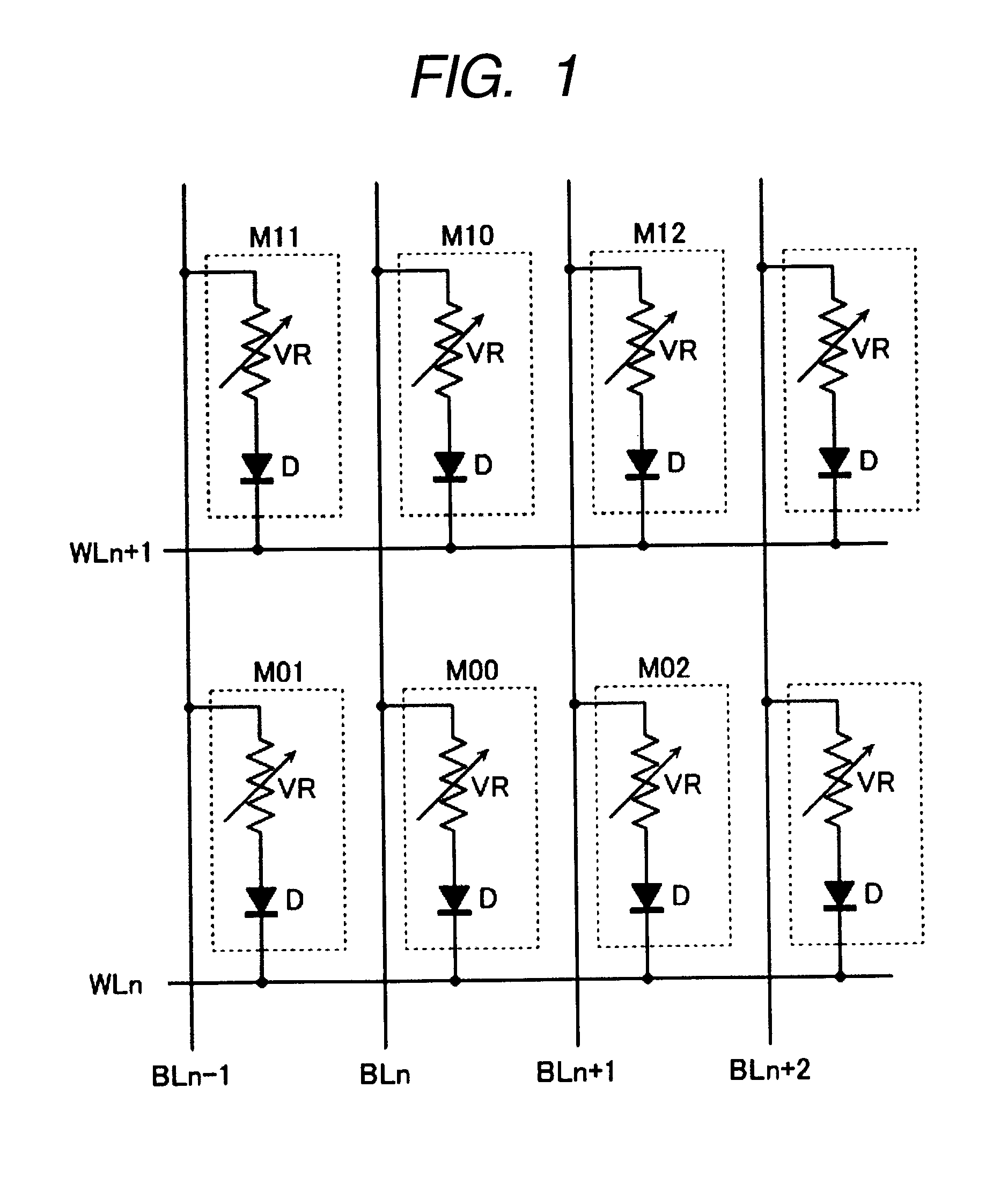

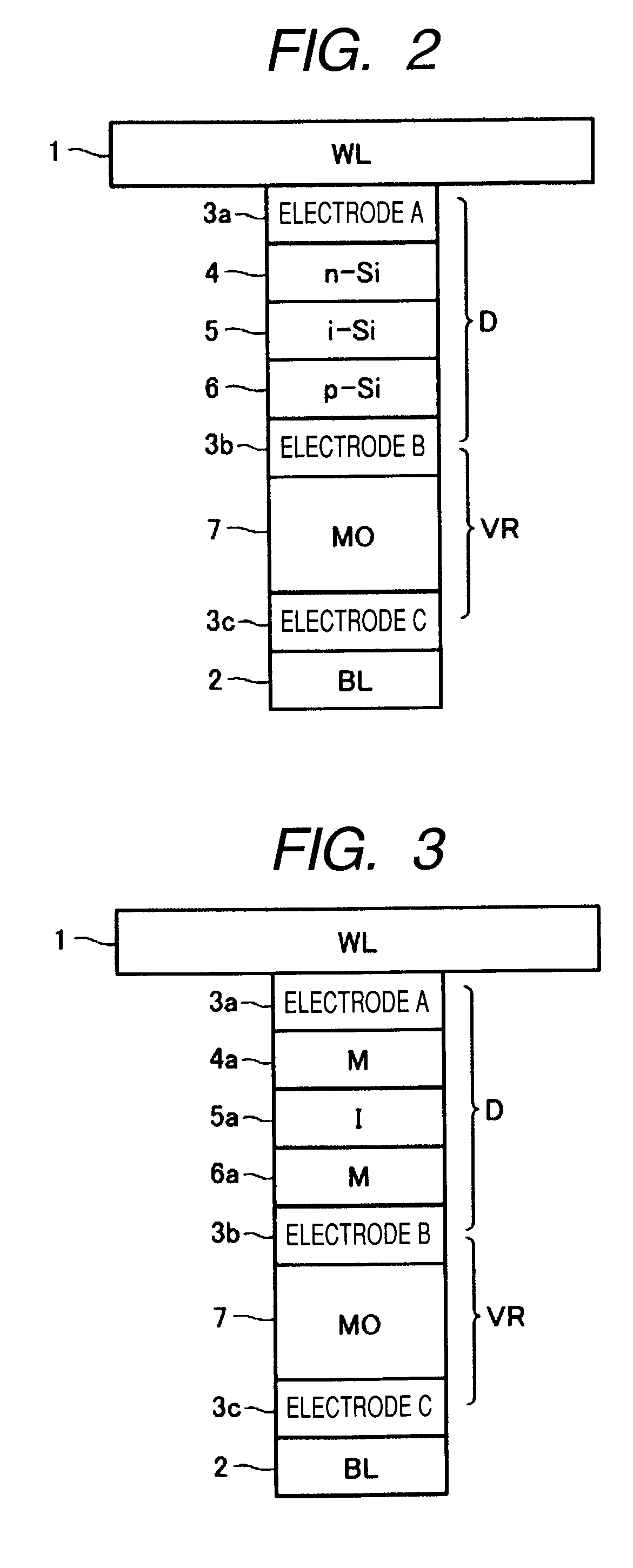

Cross point memory arrays, methods of manufacturing the same, masters for imprint processes, and methods of manufacturing masters

Owner:SAMSUNG ELECTRONICS CO LTD

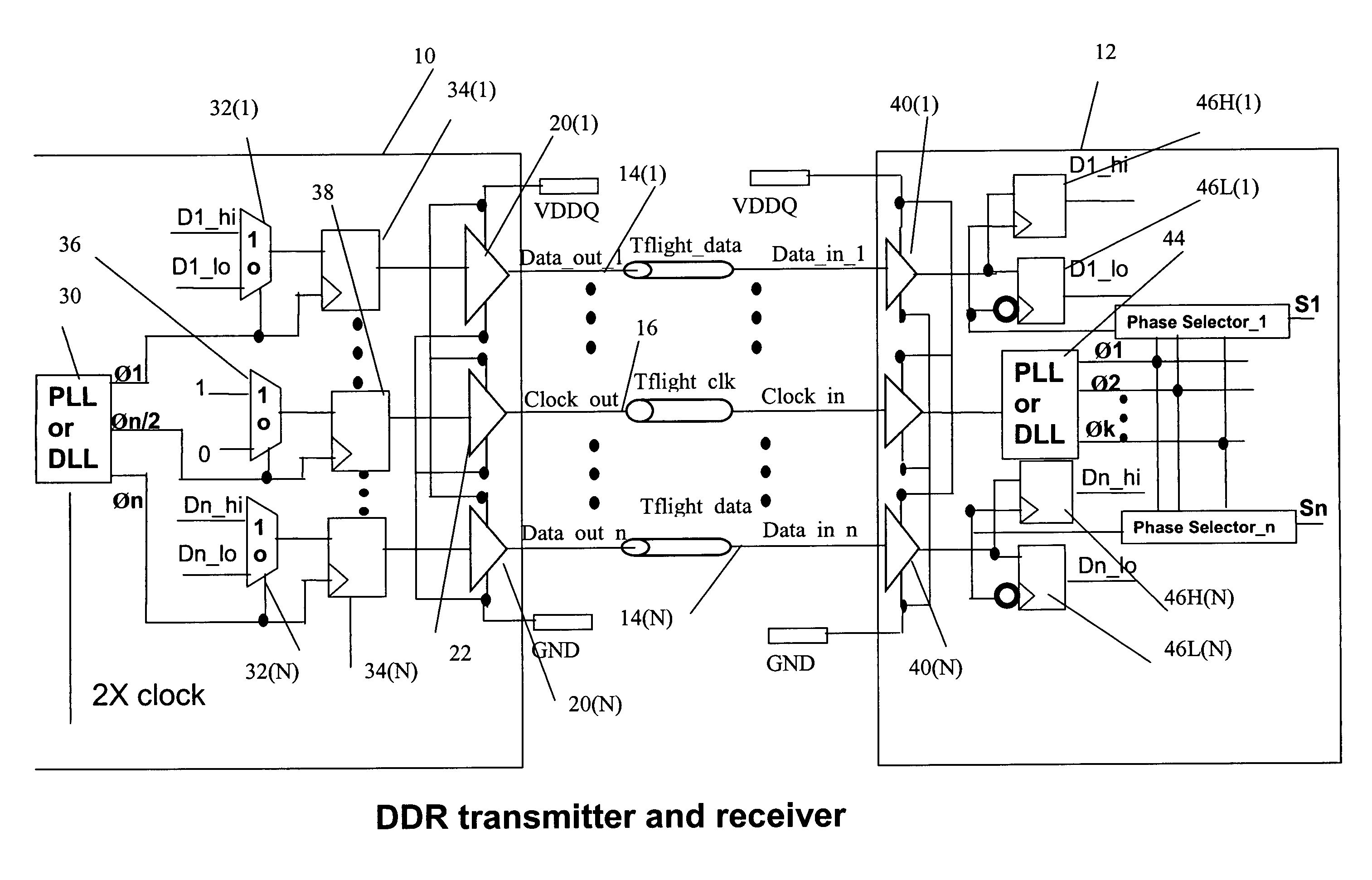

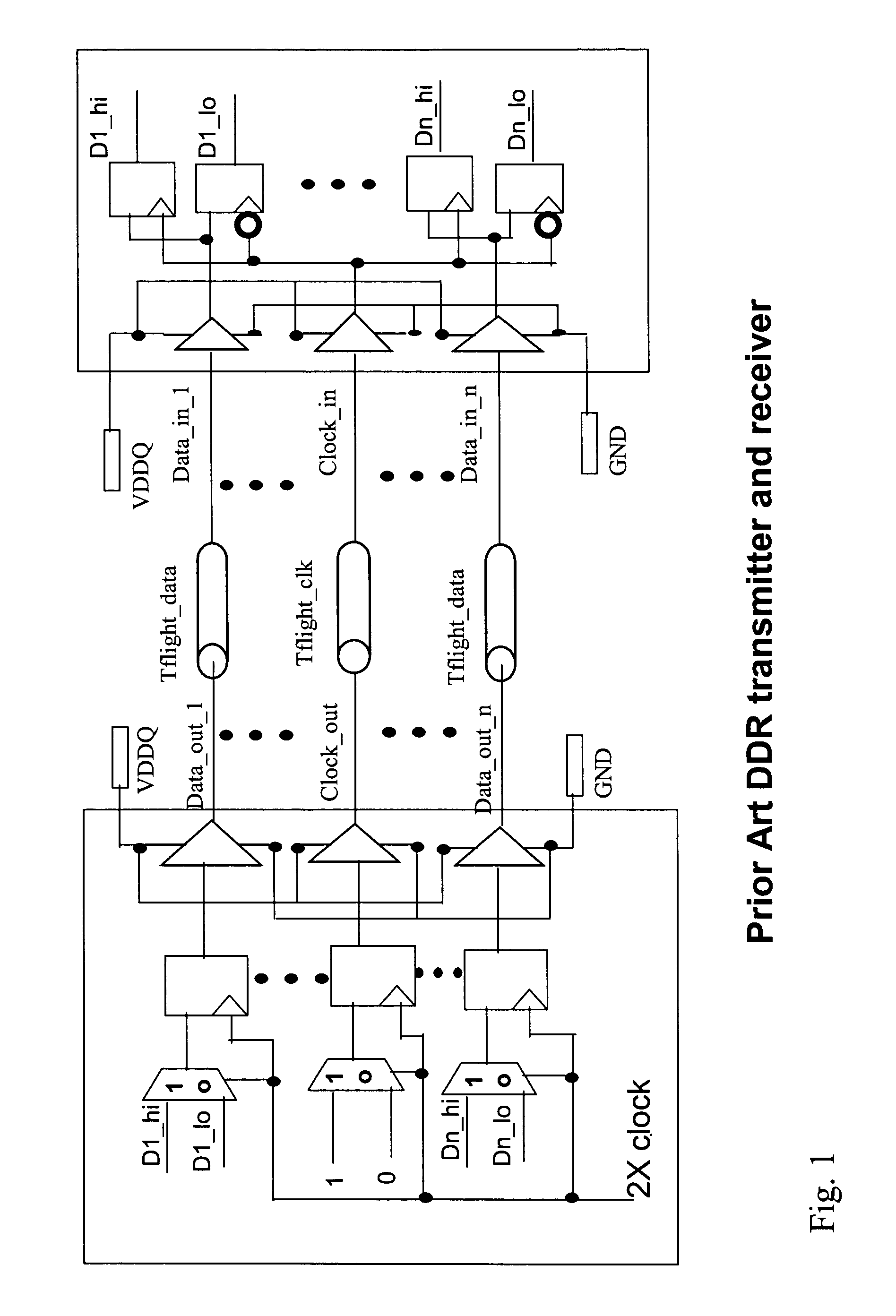

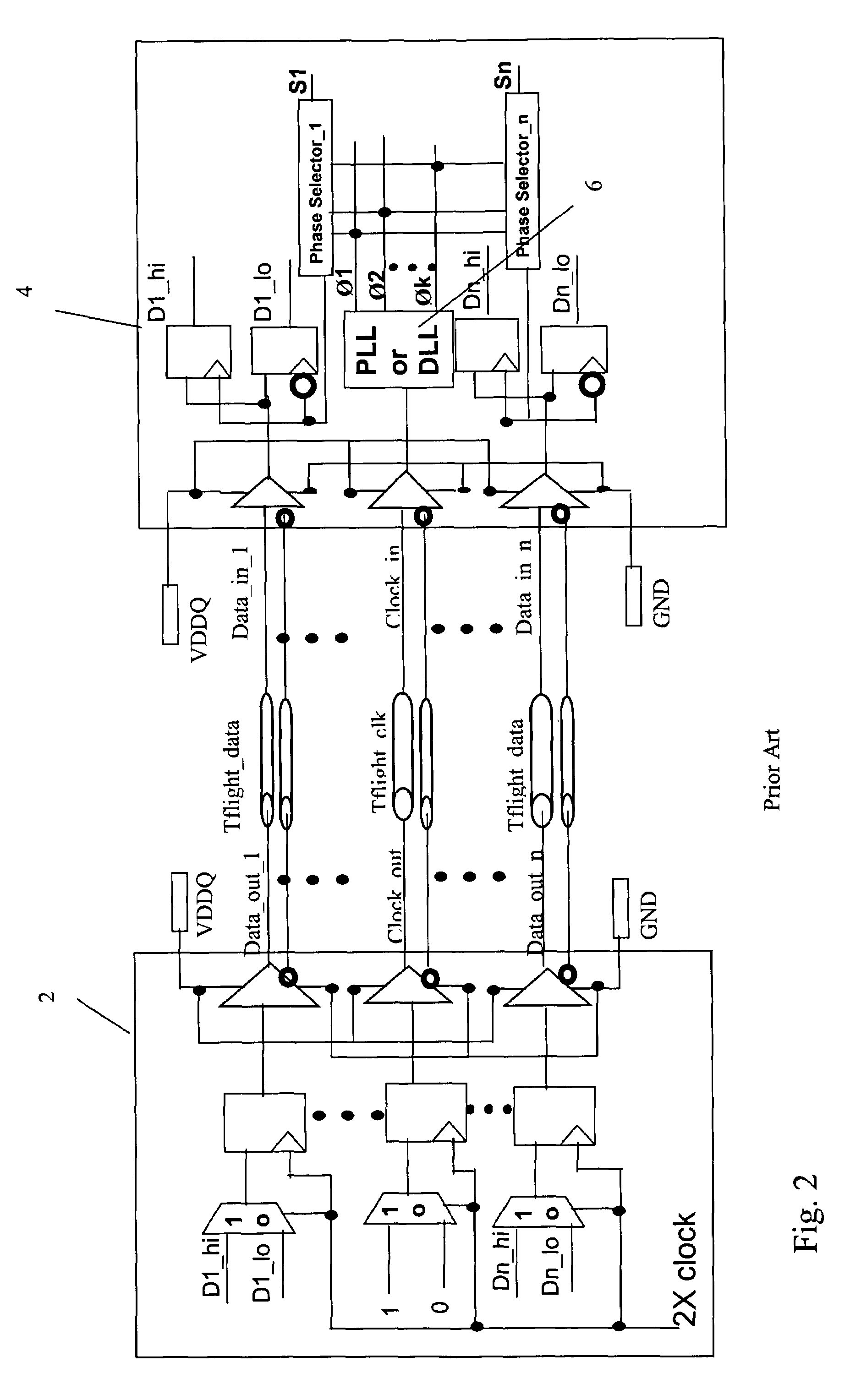

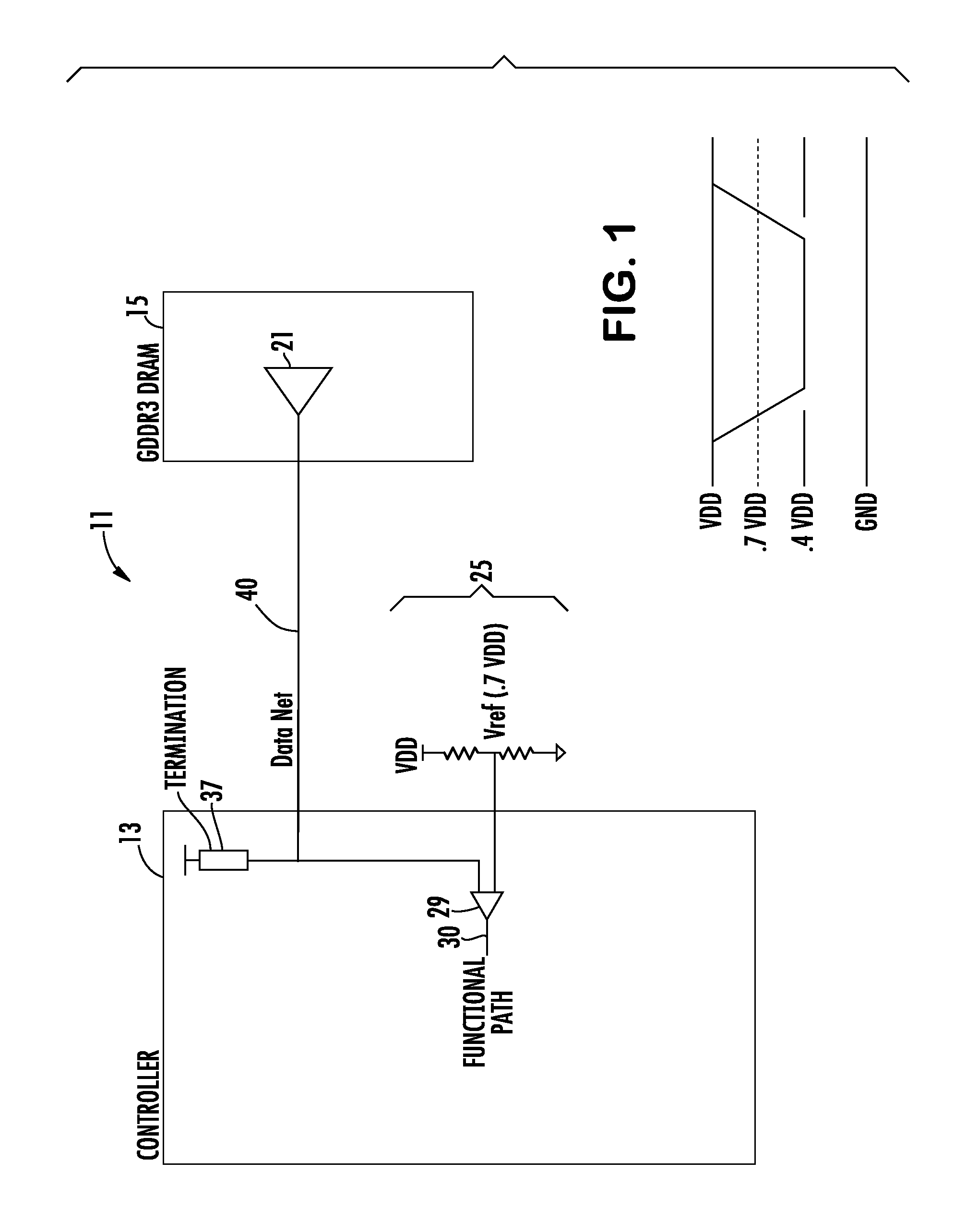

DDR interface for reducing SSO/SSI noise

InactiveUS7486702B1High bandwidthEfficient designDigital data processing detailsTime-division multiplexPhase shiftedHigh density

Owner:CISCO TECH INC

System and Method for the Designation of Items in a Virtual Universe

InactiveUS20110055919A1Facilitates tracking and recoveryData processing applicationsDigital data processing detailsHuman–computer interactionVirtual universe

The present invention enables items in a Virtual Universe to be tagged as available for pickup by one or more designated users. The present invention permits a designated user to be alerted that there is an item designated for that user / avatar and available for pick-up at a location in the Virtual Universe. A user may designate another user (or user's avatar), for example, a minor for whom the designating user has responsibility, as an “item” to be tracked. For privacy and other reasons, this and other features may be implemented on an opt-in basis.

Owner:INT BUSINESS MASCH CORP

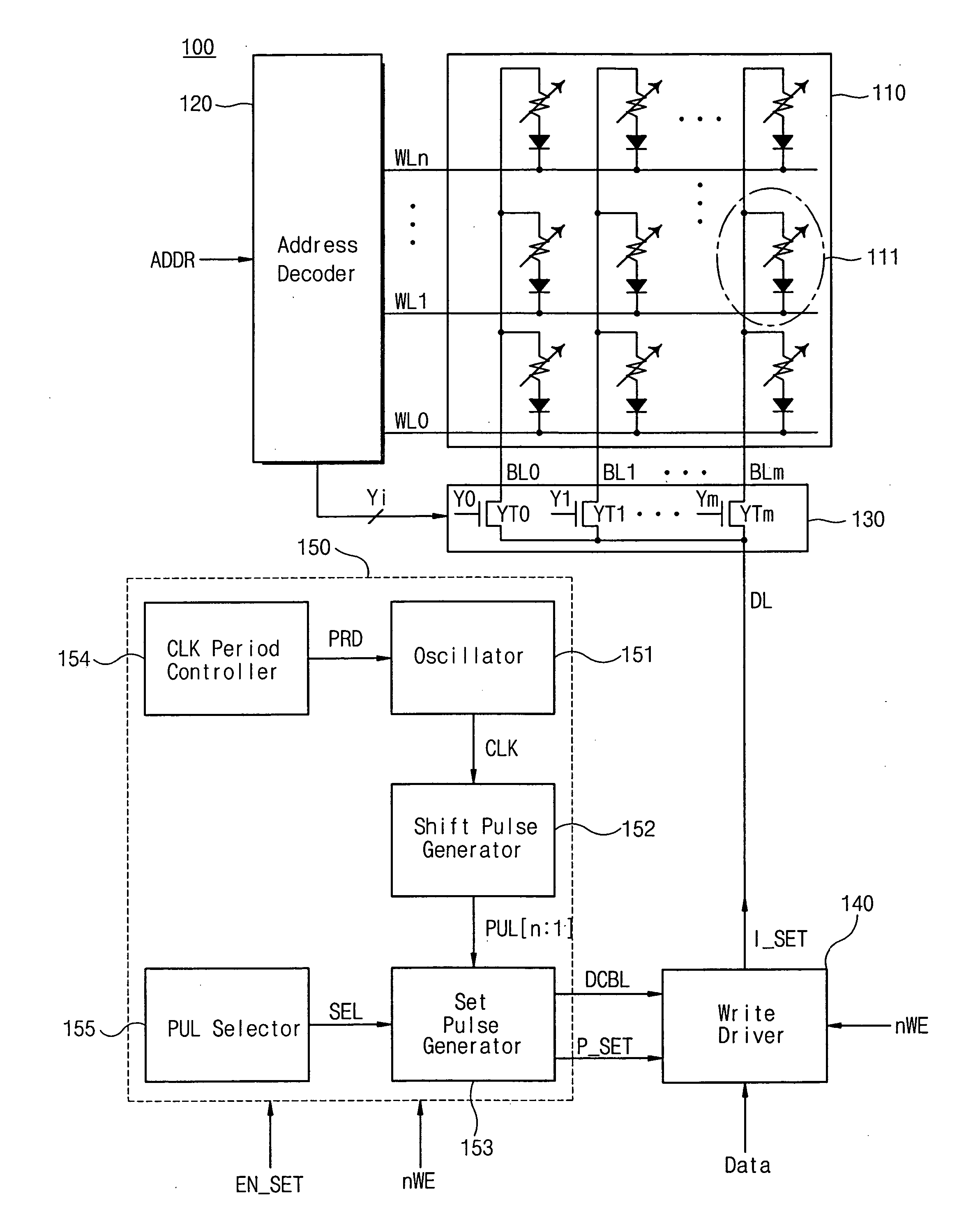

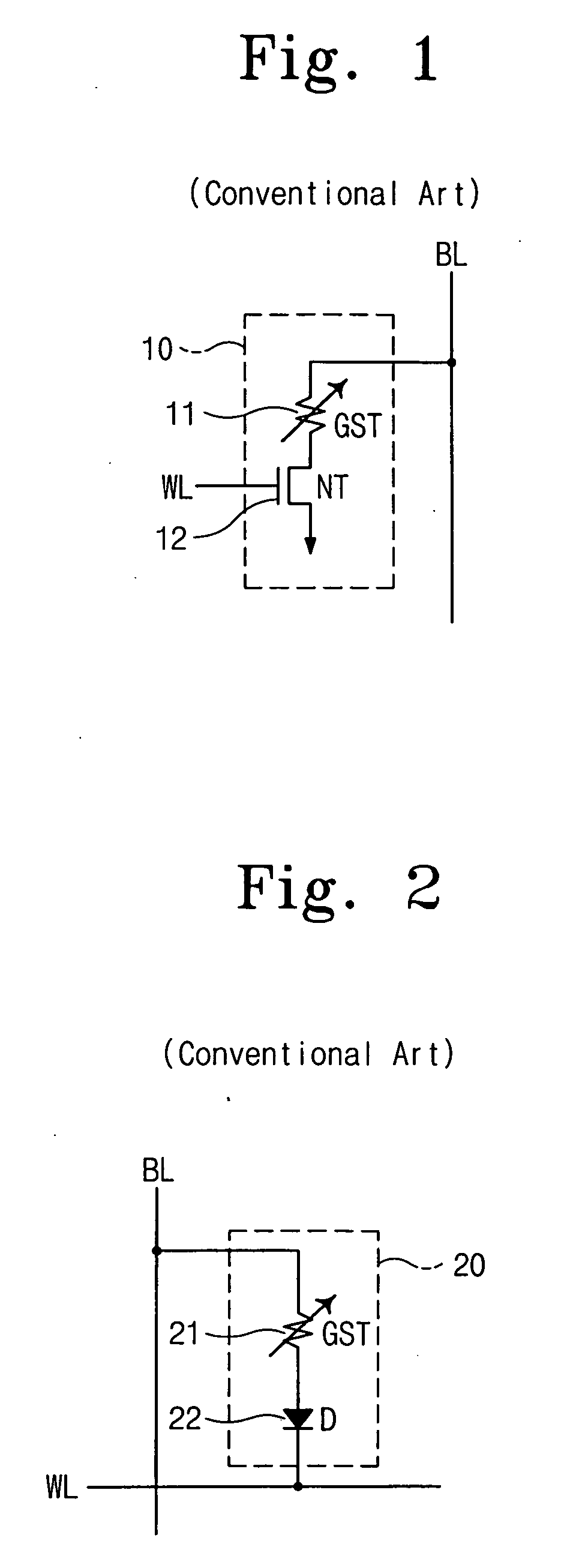

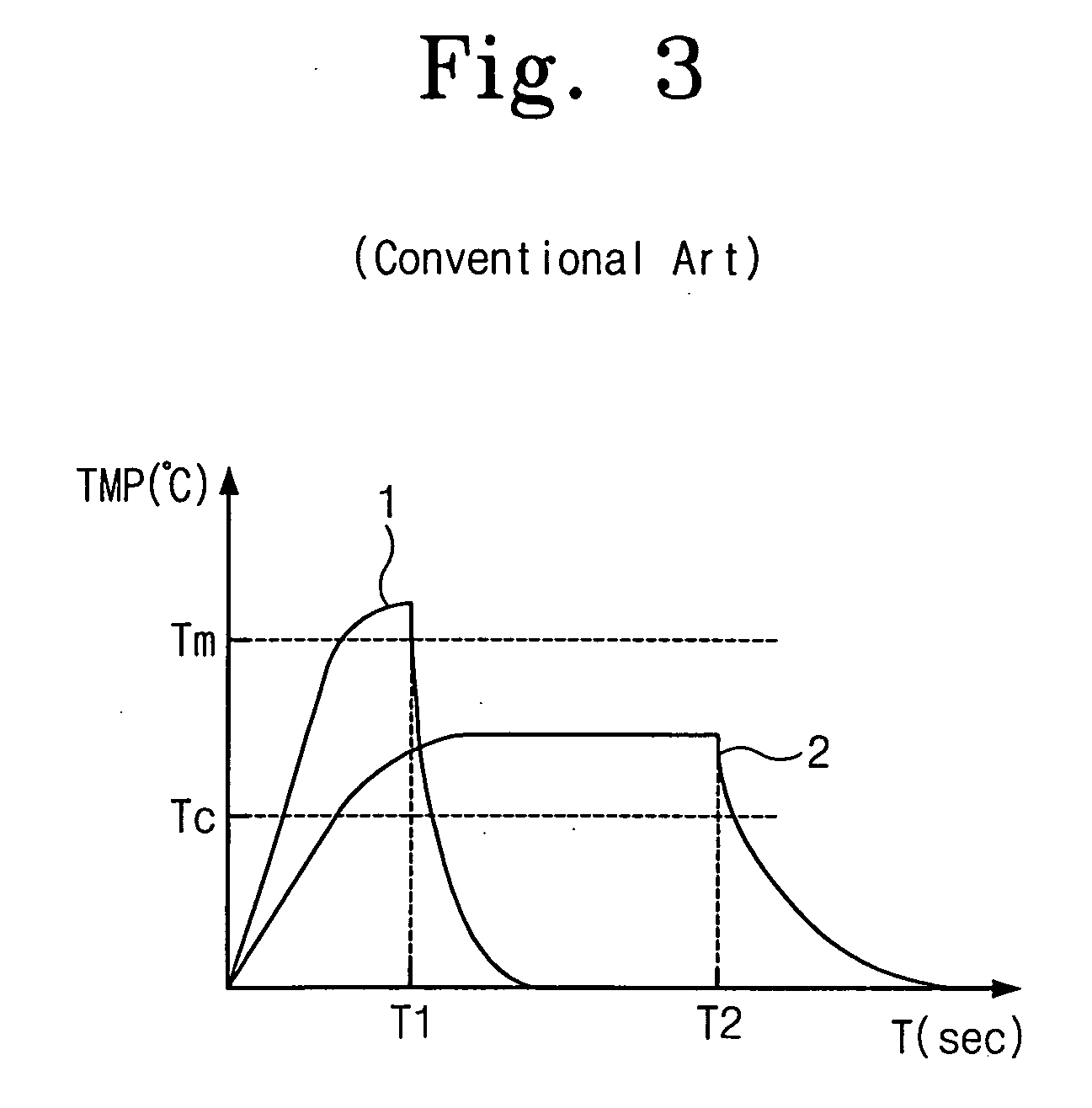

Phase change memory device and method of programming the same

Owner:SAMSUNG ELECTRONICS CO LTD

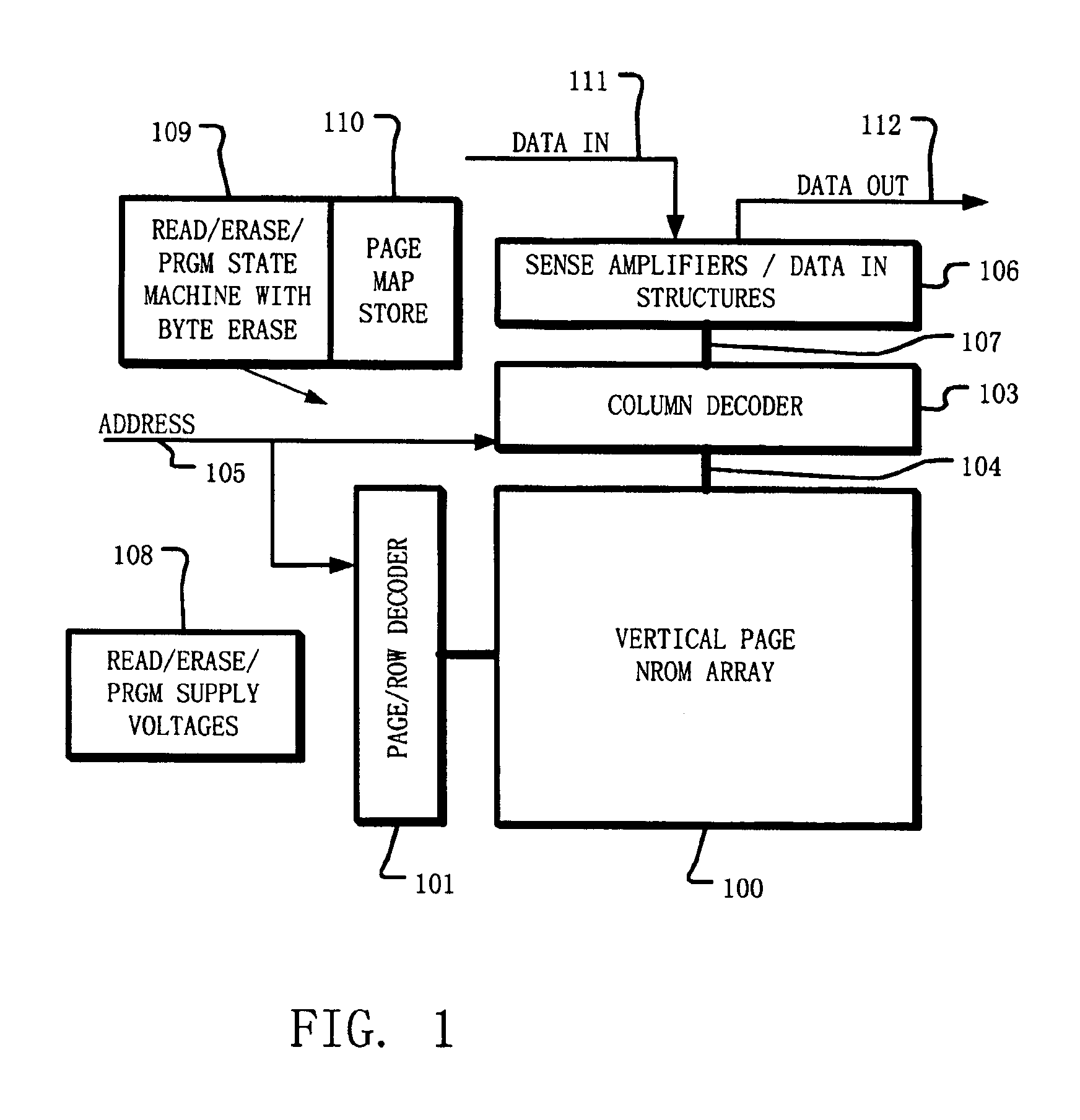

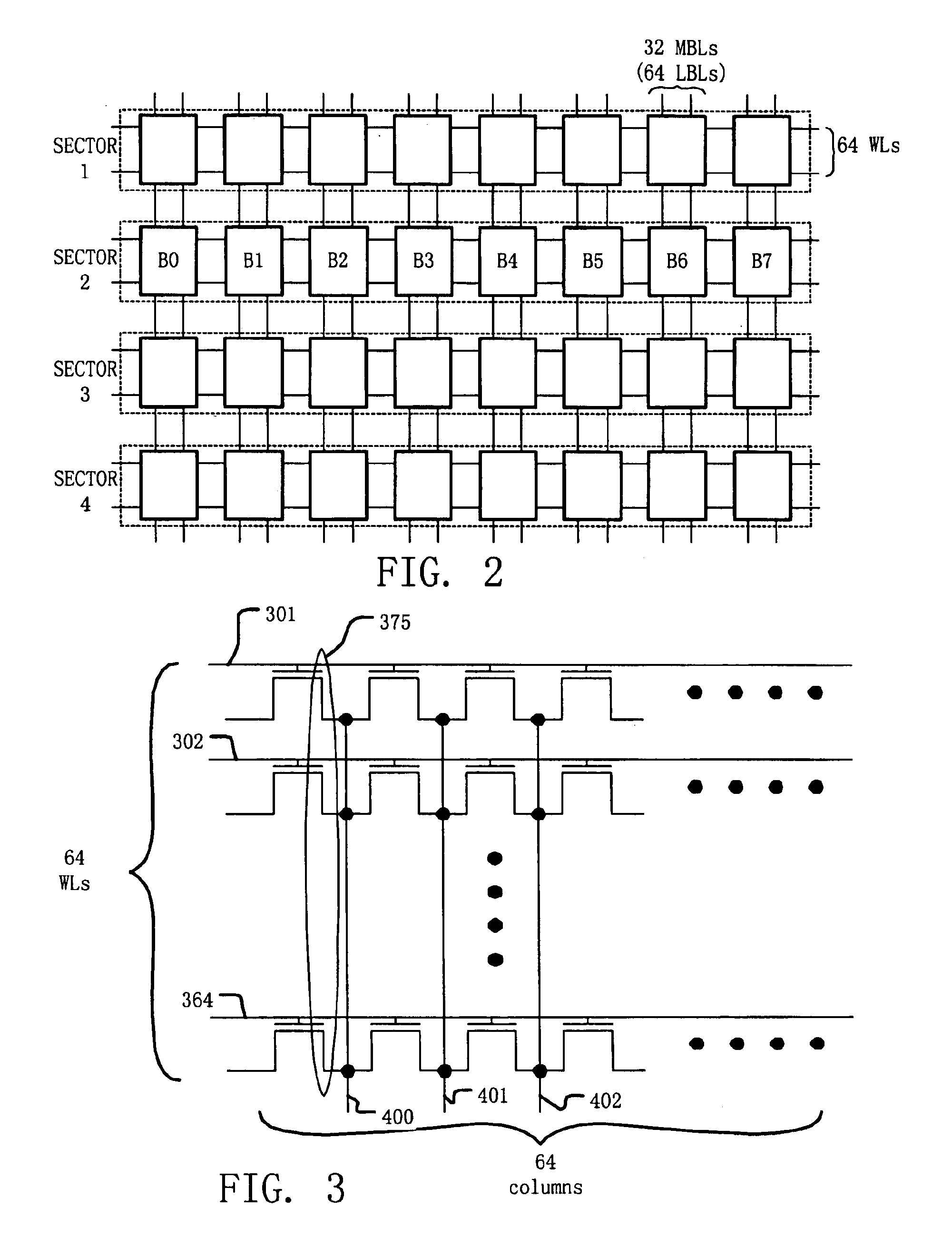

Flash memory device with byte erase

Owner:MACRONIX INT CO LTD

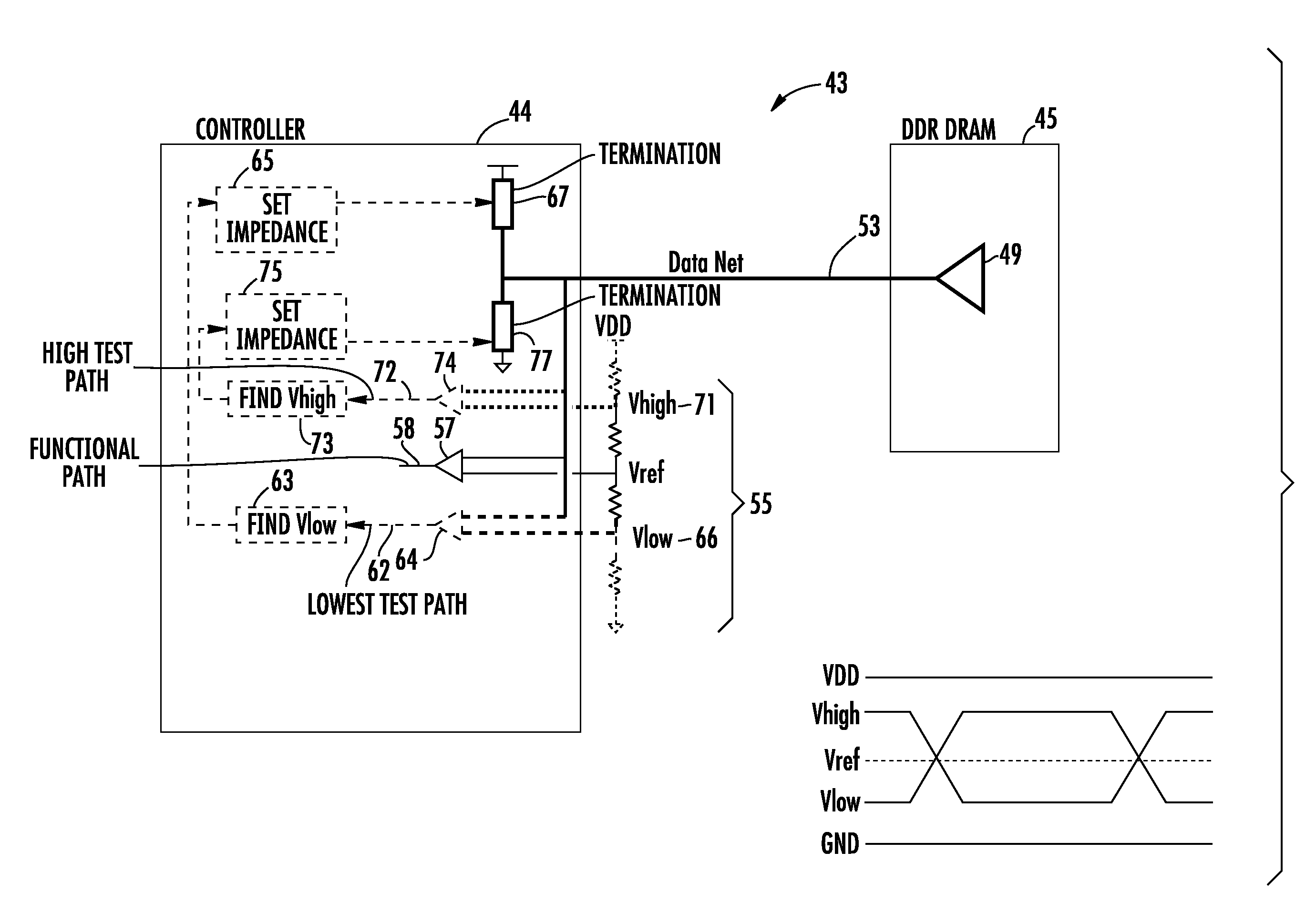

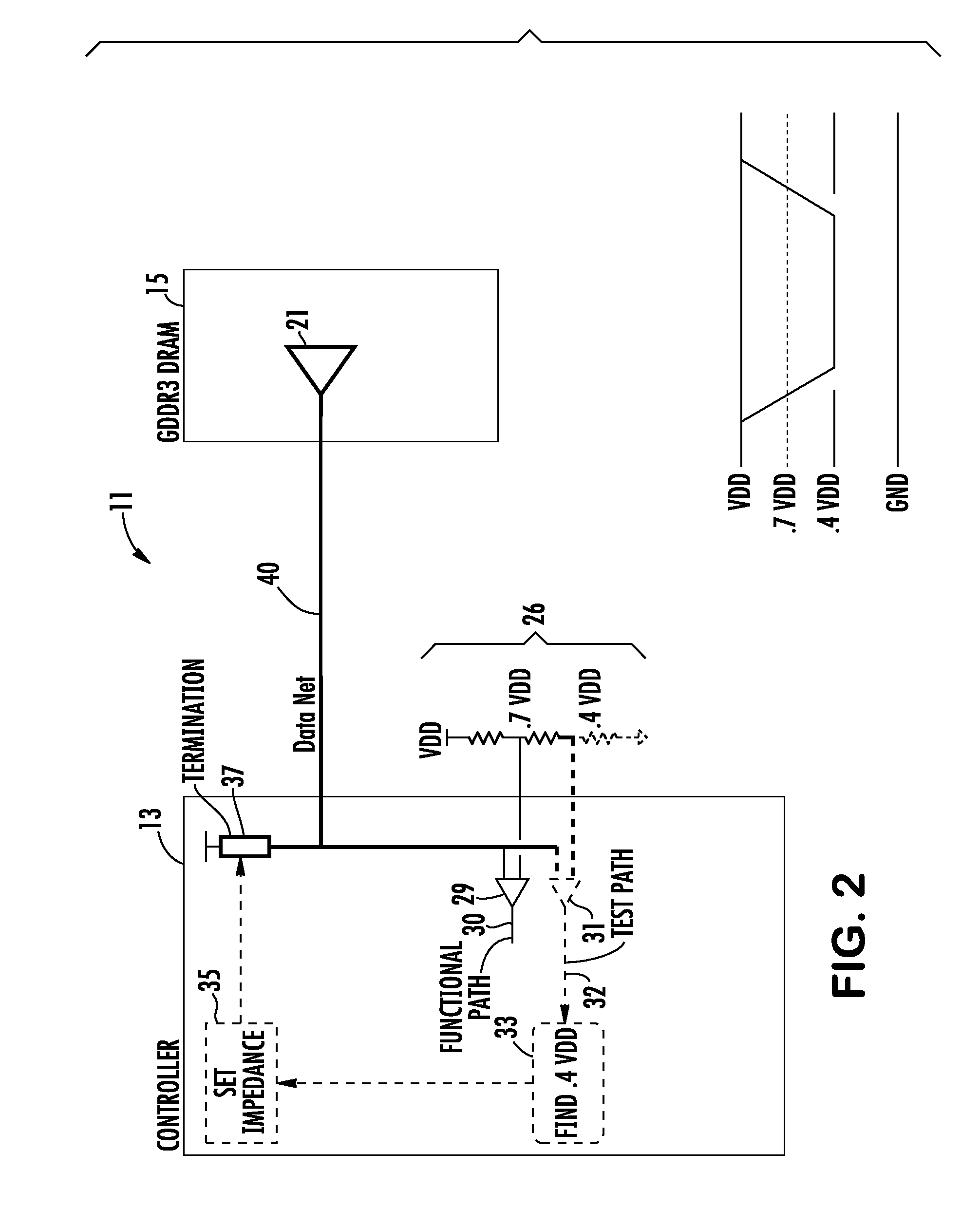

Setting Controller Termination in a Memory Controller and Memory Device Interface in a Communication Bus

InactiveUS20100192000A1Reduce mismatchImprove Timing MarginVolume/mass flow measurementHardware monitoringTiming marginCoupling

Owner:IBM CORP

Non-volatile memory device

Owner:KIOXIA CORP

Semiconductor memory device

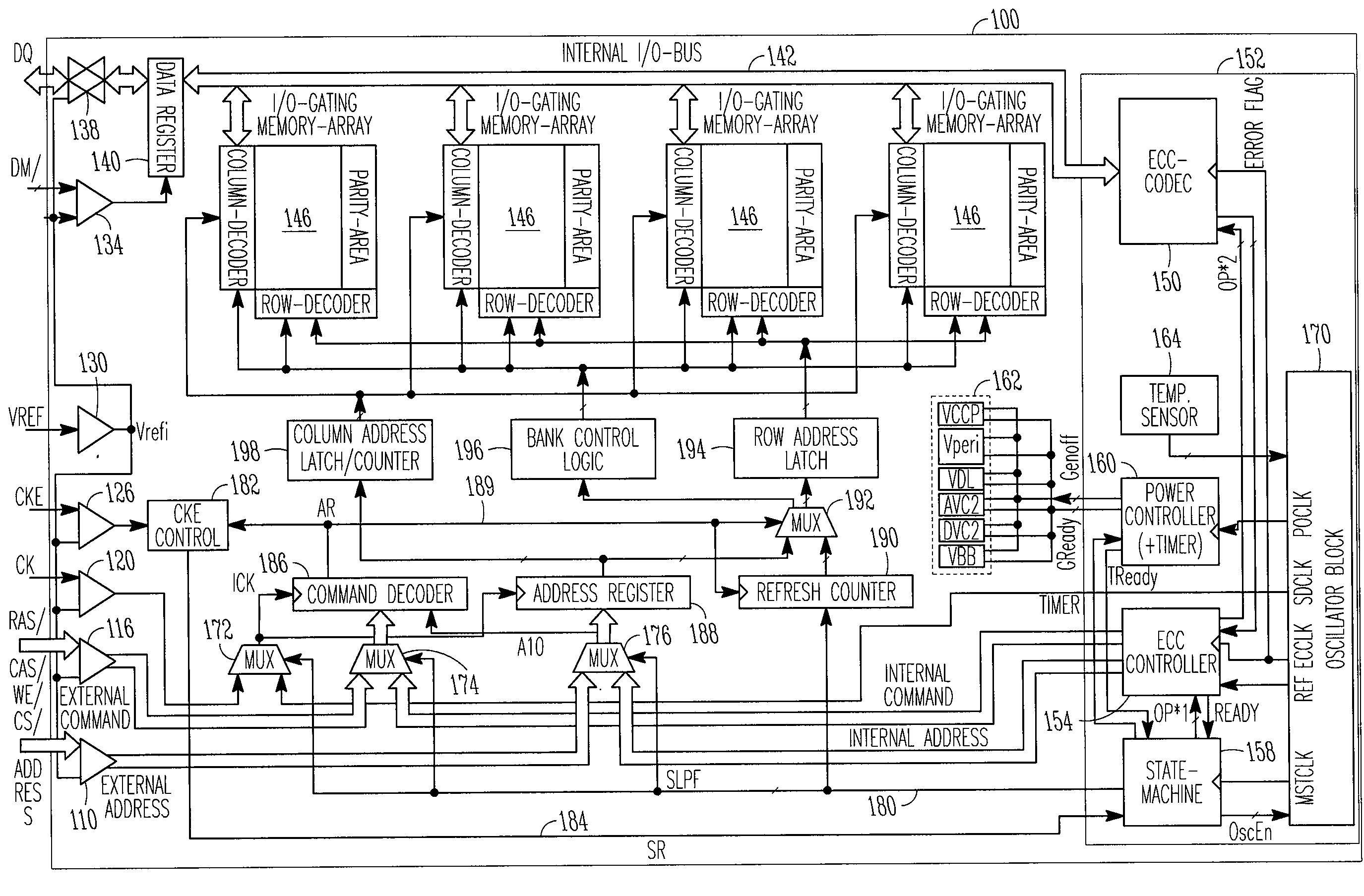

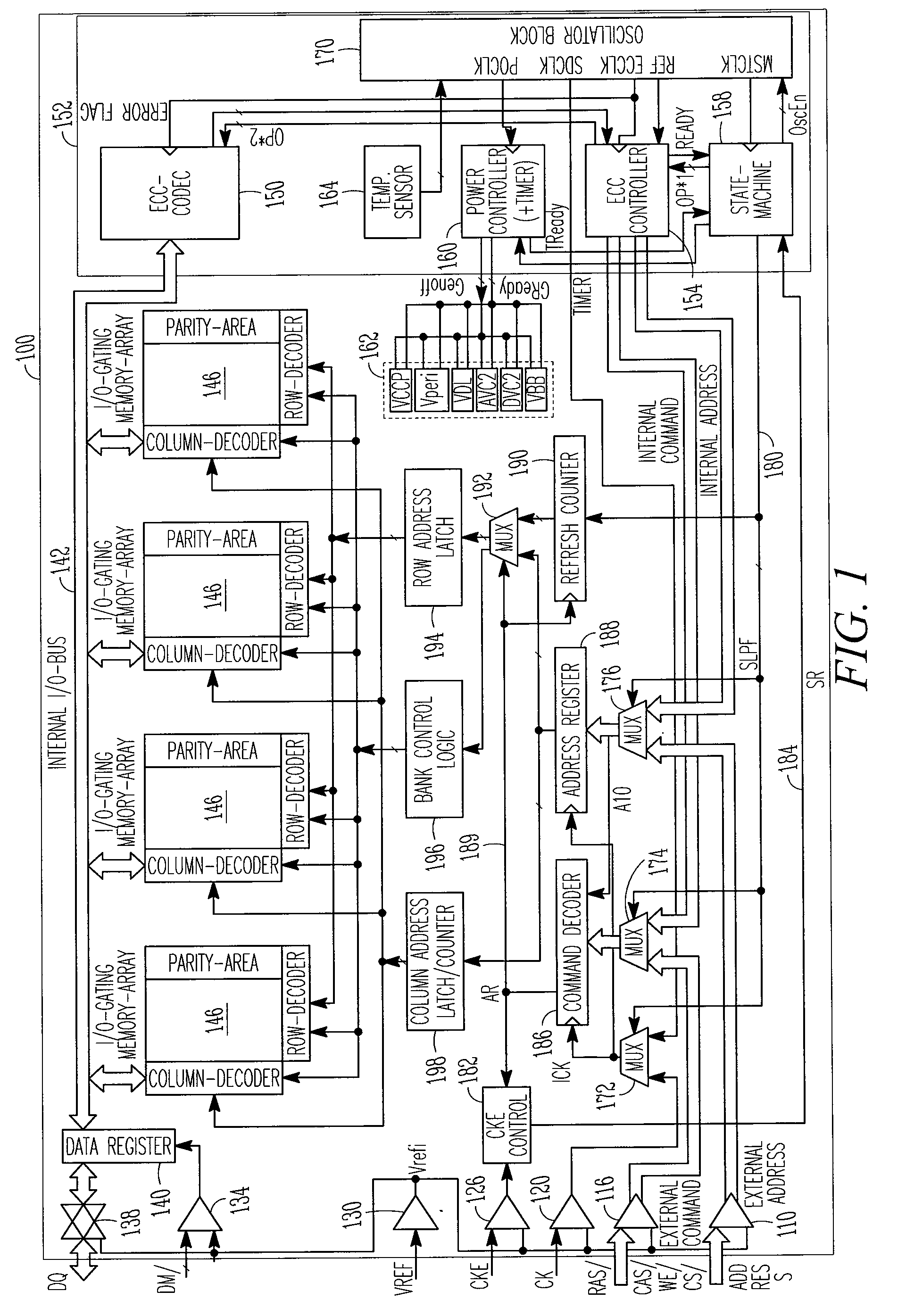

ActiveUS20090219775A1Reduce and eliminate test timeElectronic circuit testingError detection/correctionHemt circuitsEngineering

Semiconductor memory device includes a cell array including a plurality of unit cells; and a test circuit configured to perform a built-in self-stress (BISS) test for detecting a defect by performing a plurality of internal operations including a write operation through an access to the unit cells using a plurality of patterns during a test procedure carried out at a wafer-level.

Owner:SK HYNIX INC

Physically unclonable function (PUF) circuits employing multiple puf memories to decouple a puf challenge input from a puf response output for enhanced security

InactiveUS20190342106A1User identity/authority verificationDigital storagePhysical unclonable functionChallenge response

Physically unclonable function (PUF) circuits employing multiple PUF memories to decouple a PUF challenge input from a PUF response output for enhanced security. The PUF circuit includes a PUF challenge memory and a PUF response memory. In response to a read operation, the PUF challenge memory uses a received PUF challenge input data word to address PUF challenge memory arrays therein to generate a plurality of intermediate PUF challenge output data words. The PUF response memory is configured to generate a second, final PUF response output data word in response to intermediate PUF challenge output data words. In this manner, it is more difficult to learn the challenge-response behavior of the PUF circuit, because the PUF challenge input data word does not directly address a memory array that stores memory states representing final logic values in the PUF response output data word.

Owner:QUALCOMM INC

Display panel and gate driving circuit and driving method for gate driving circuit

An exemplary gate driving circuit is adapted for driving a display panel including multiple pixels and includes a first gate driving unit string and a second gate driving unit string. The first gate driving unit string includes multiple cascade-connected first gate driving units and receives a start pulse. The first gate driving units are for generating output pulses to drive the pixels. The second gate driving unit string includes multiple cascade-connected second gate driving units and receives the start pulse. The second gate driving units are for generating output pulses to drive the pixels. The output pulse generated from one of the second gate driving units is provided to one of first gate driving units to determine whether to disable the output pulse of the first gate driving unit which receives the output pulse generated from the second gate driving units.

Owner:AU OPTRONICS CORP

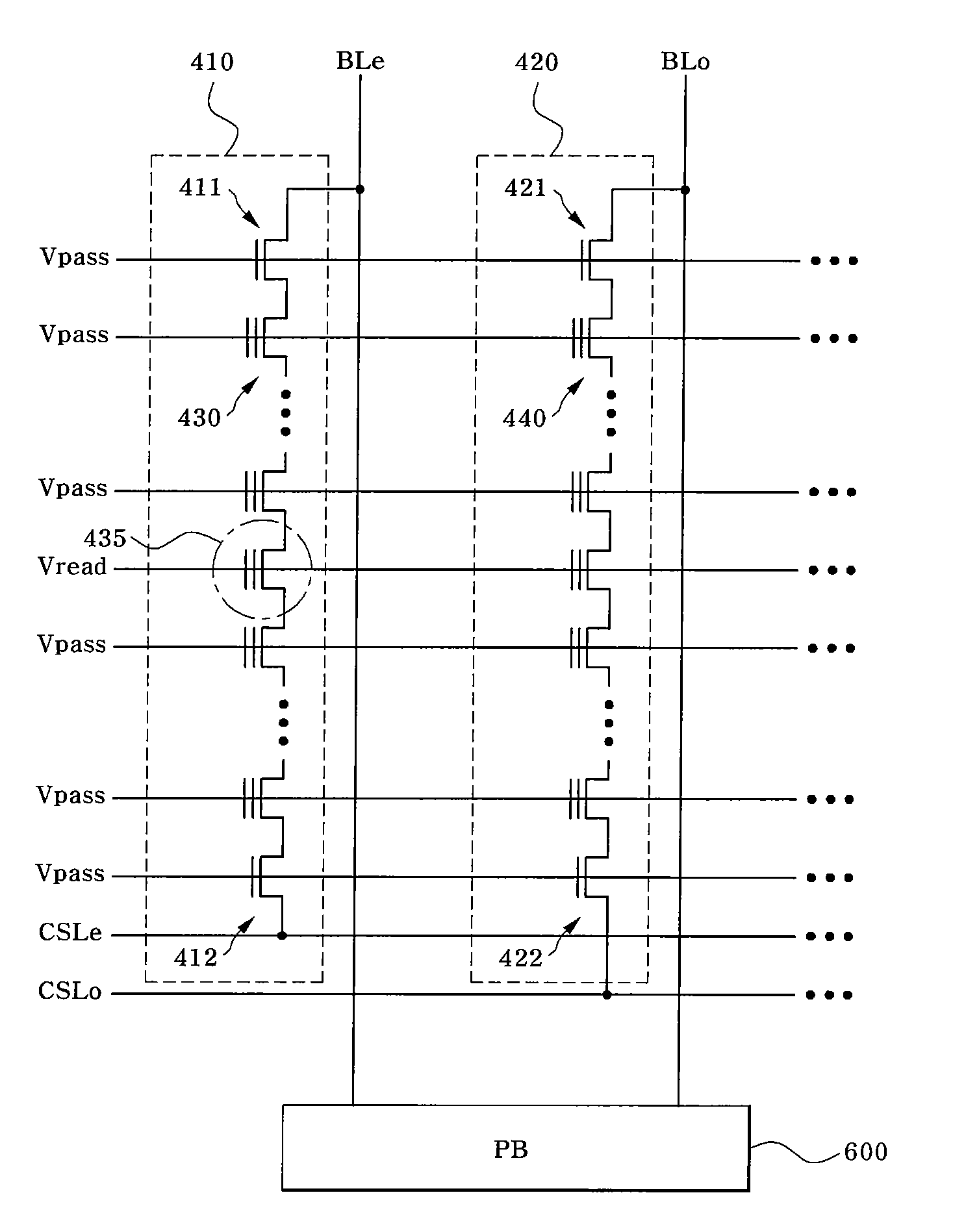

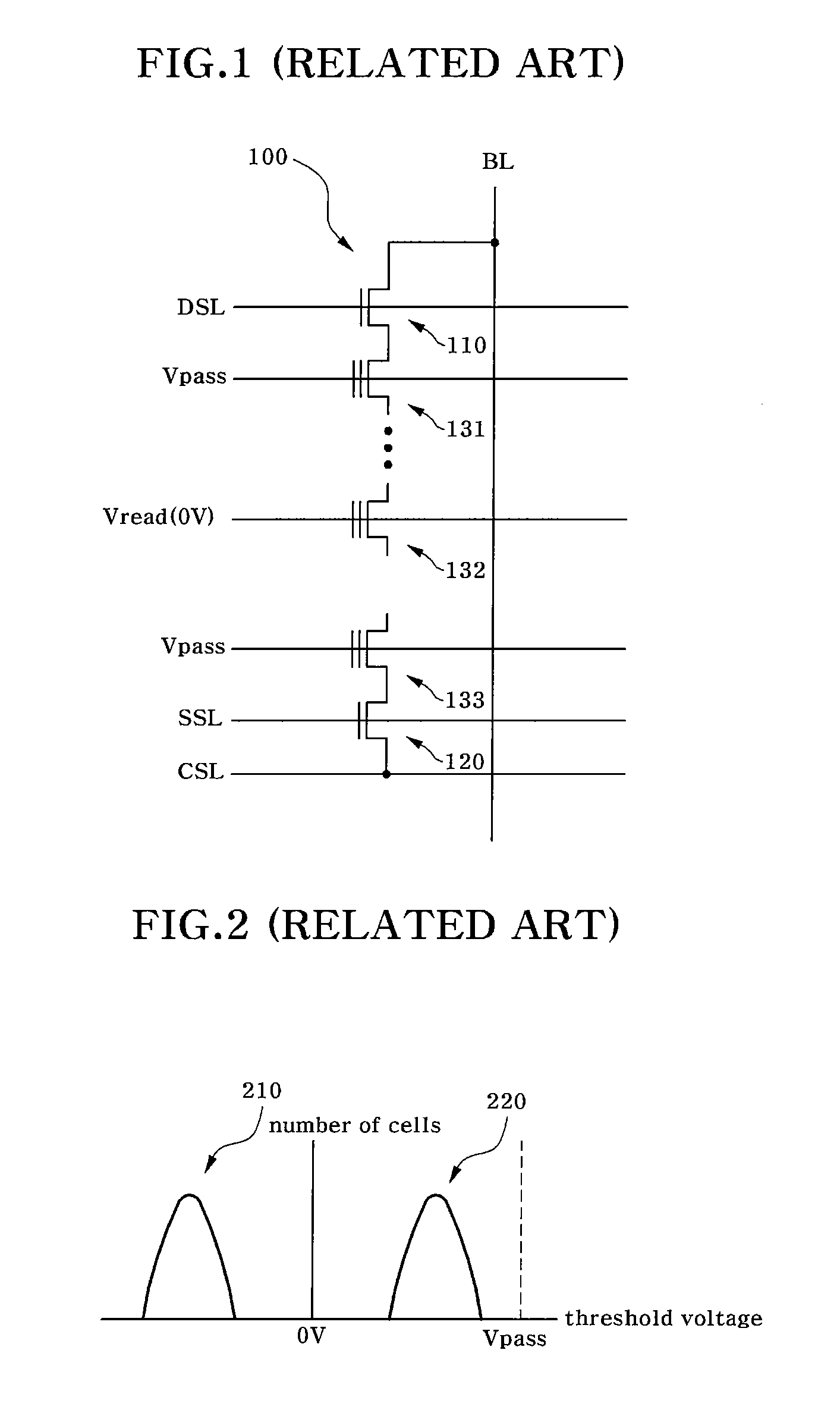

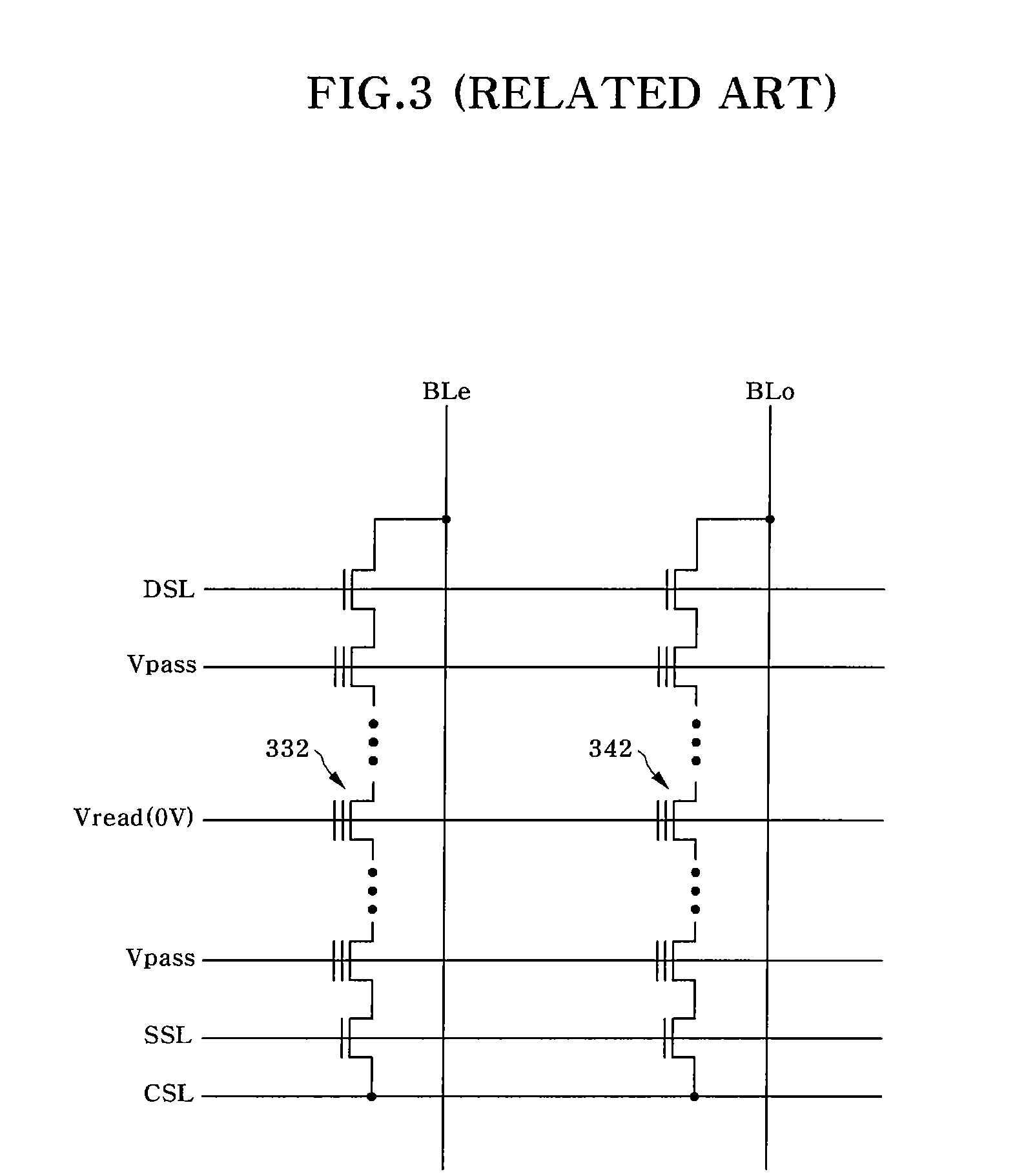

Method for reading NAND flash memory device using self-boosting

Owner:SK HYNIX INC

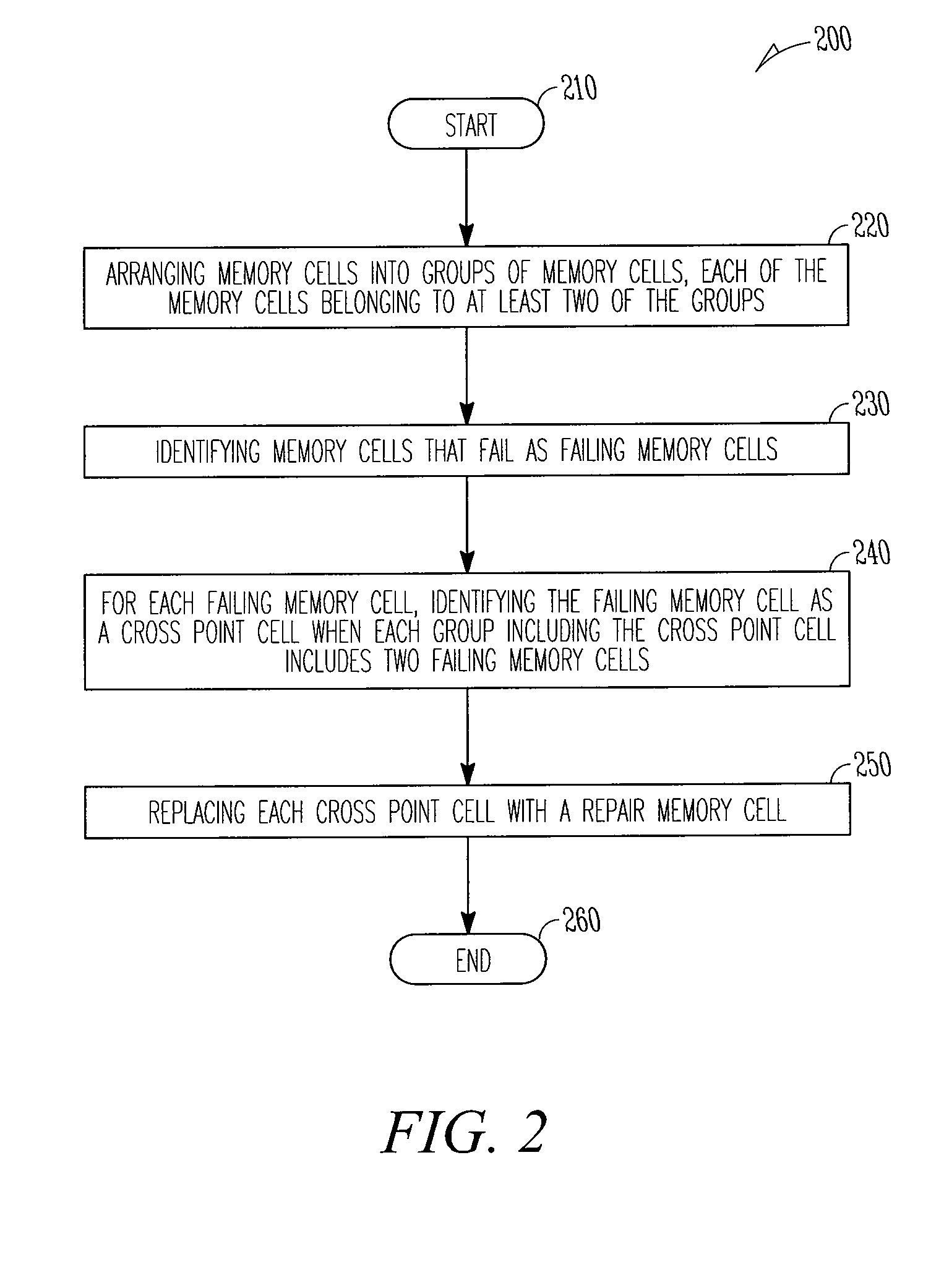

Memory device repair apparatus, systems, and methods

Owner:MICRON TECH INC

Apparatus for dividing bank in flash memory

InactiveUS6963502B2Shorten the lengthImprove the sense of speedRead-only memoriesDigital storageComputer sciencePage buffers

The present invention relates to an apparatus for dividing a bank in a flash memory. A block of the flash memory is divided into two banks and each page buffer is located between the two banks to share an input / output line. Therefore, it is possible to shorten the length of a bit line, improve a data sensing rate, and allow one bank to perform one operation while the other bank performs a read, write or erase operation.

Owner:SK HYNIX INC

Techniques for operating semiconductor devices

Owner:IBM CORP

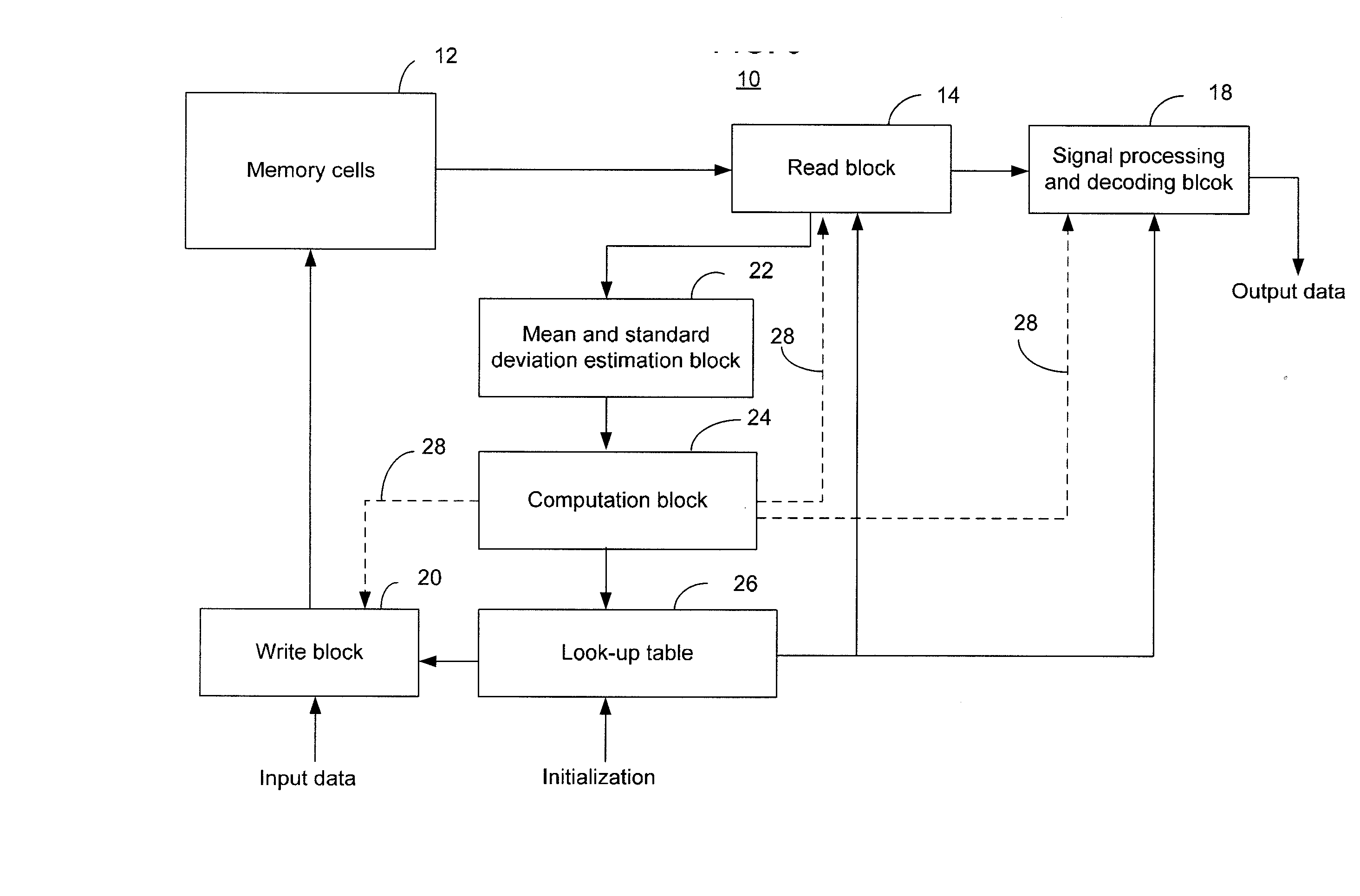

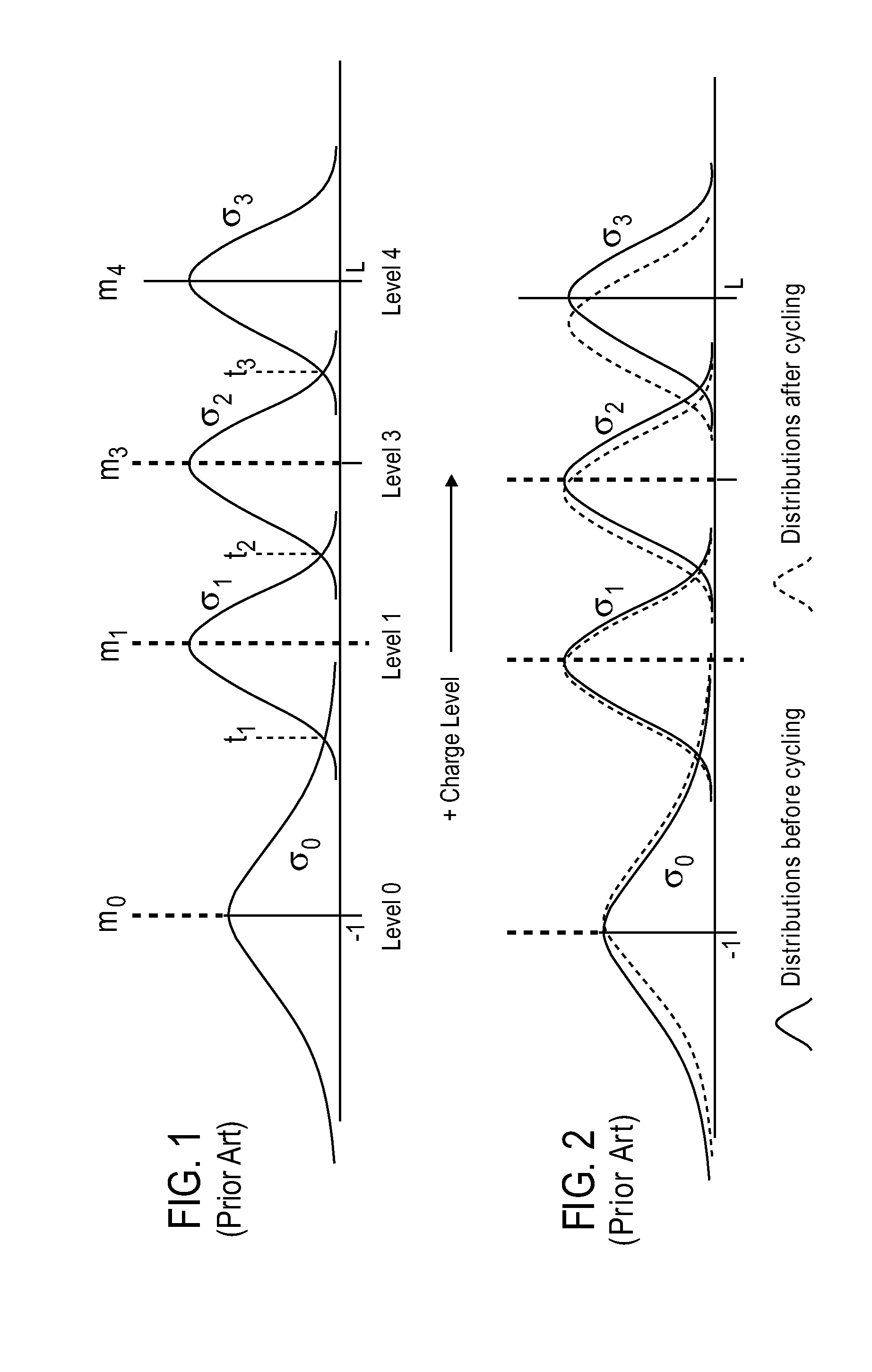

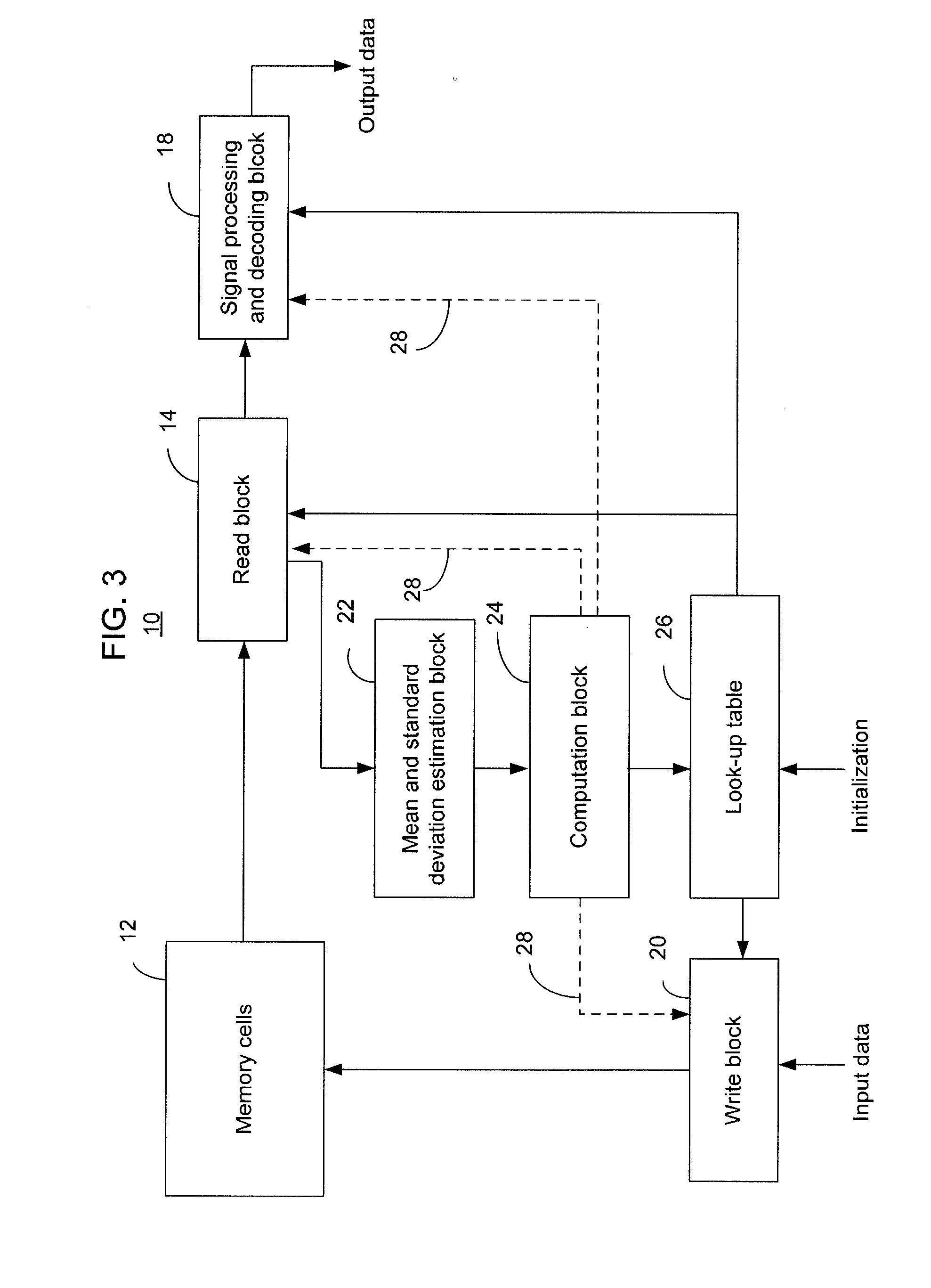

Adaptive read and write systems and methods for memory cells

ActiveUS20080106936A1Facilitate writing and readingRead-only memoriesDigital storageSelf adaptiveThreshold voltage

Adaptive memory read and write systems and methods are described herein that adapts to changes to threshold voltage distributions of memory cells as of result of, for example, the detrimental affects of repeated cycling operations of the memory cells. The novel systems may include at least multi-level memory cells, which may be multi-level flash memory cells, and a computation block operatively coupled to the multi-level memory cells. The computation block may be configured to compute optimal or near optimal mean and detection threshold values based, at least in part, on estimated mean and standard deviation values of level distributions of the multi-level memory cells. The optimal or near optimal mean and detection threshold values computed by the computation block may be subsequently used to facilitate writing and reading, respectively, of data to and from the multi-level memory cells.

Owner:MARVELL ASIA PTE LTD

High-voltage switch with low output ripple for non-volatile floating-gate memories

A high-voltage switch has a high-voltage input terminal, receiving a high voltage, and an output terminal. A pass transistor, having a control terminal, is connected between the high-voltage input terminal and the output terminal. The output of a voltage-multiplying circuit of the charge-pump type is connected to the control terminal. The voltage-multiplying circuit is of a symmetrical type, has first and second charge-storage means, receiving a clock signal of a periodic type, and has a first circuit branch and a second circuit branch, which are symmetrical to one another and operate in phase opposition with respect to the clock signal.

Owner:MICRON TECH INC

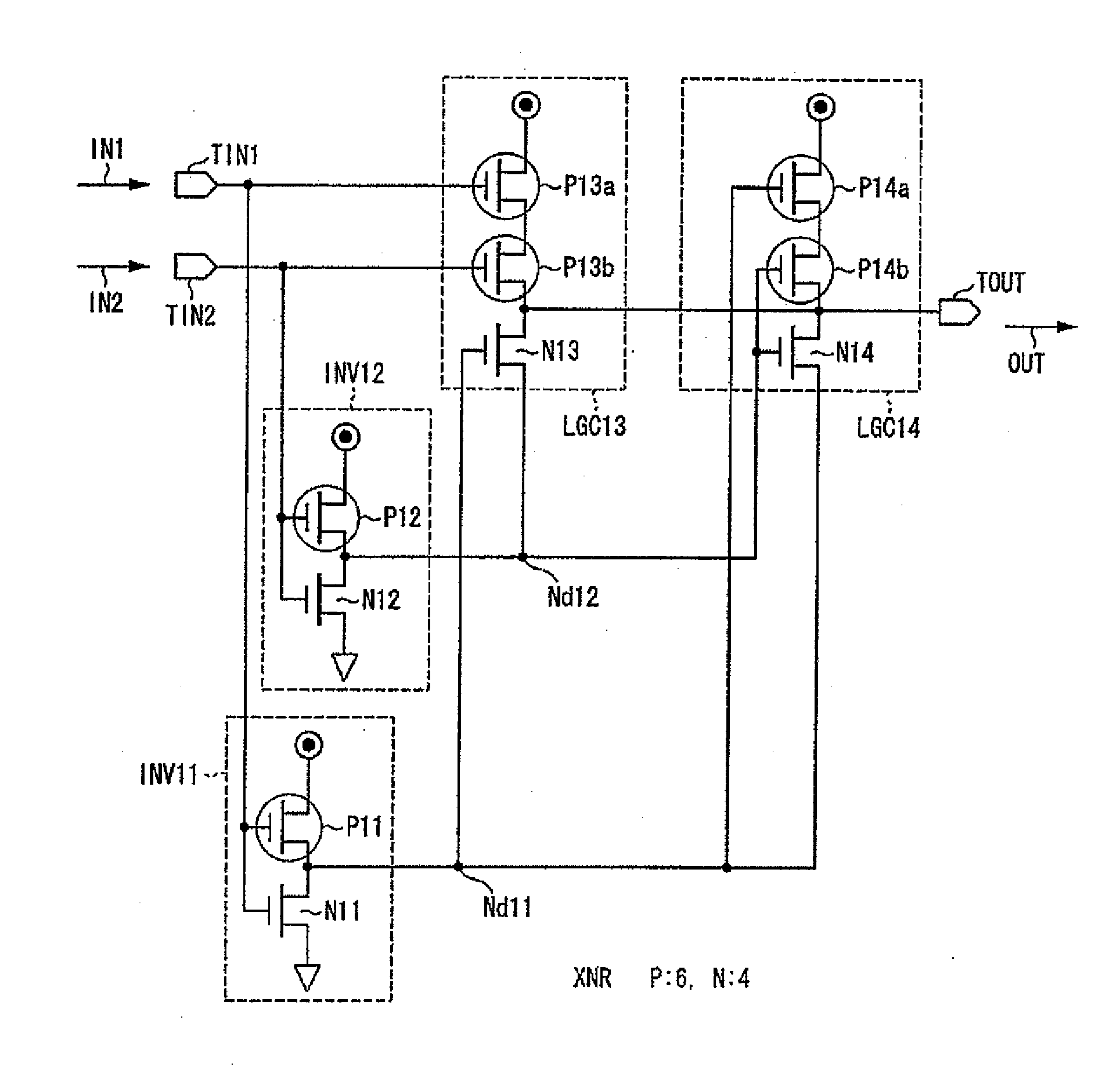

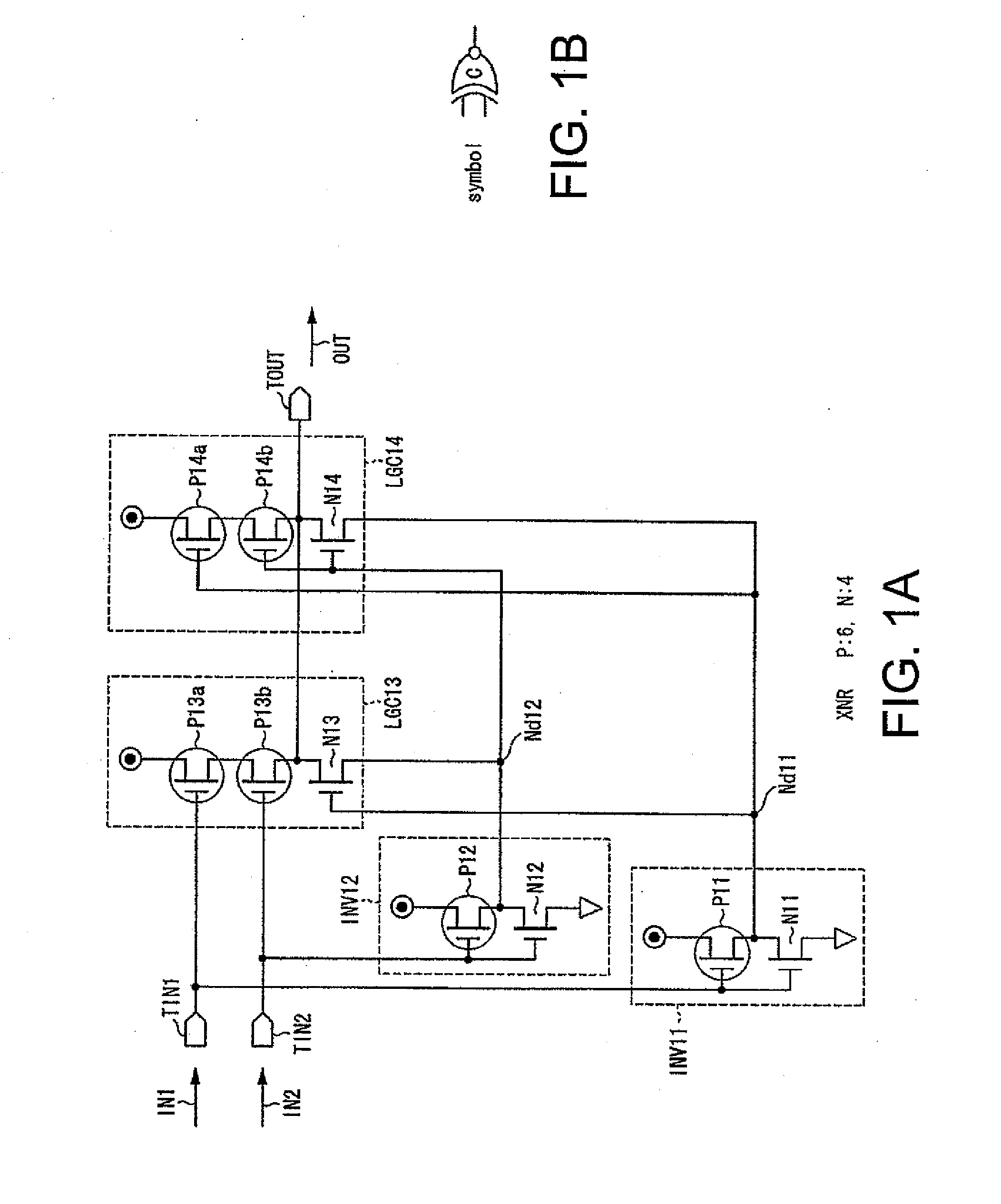

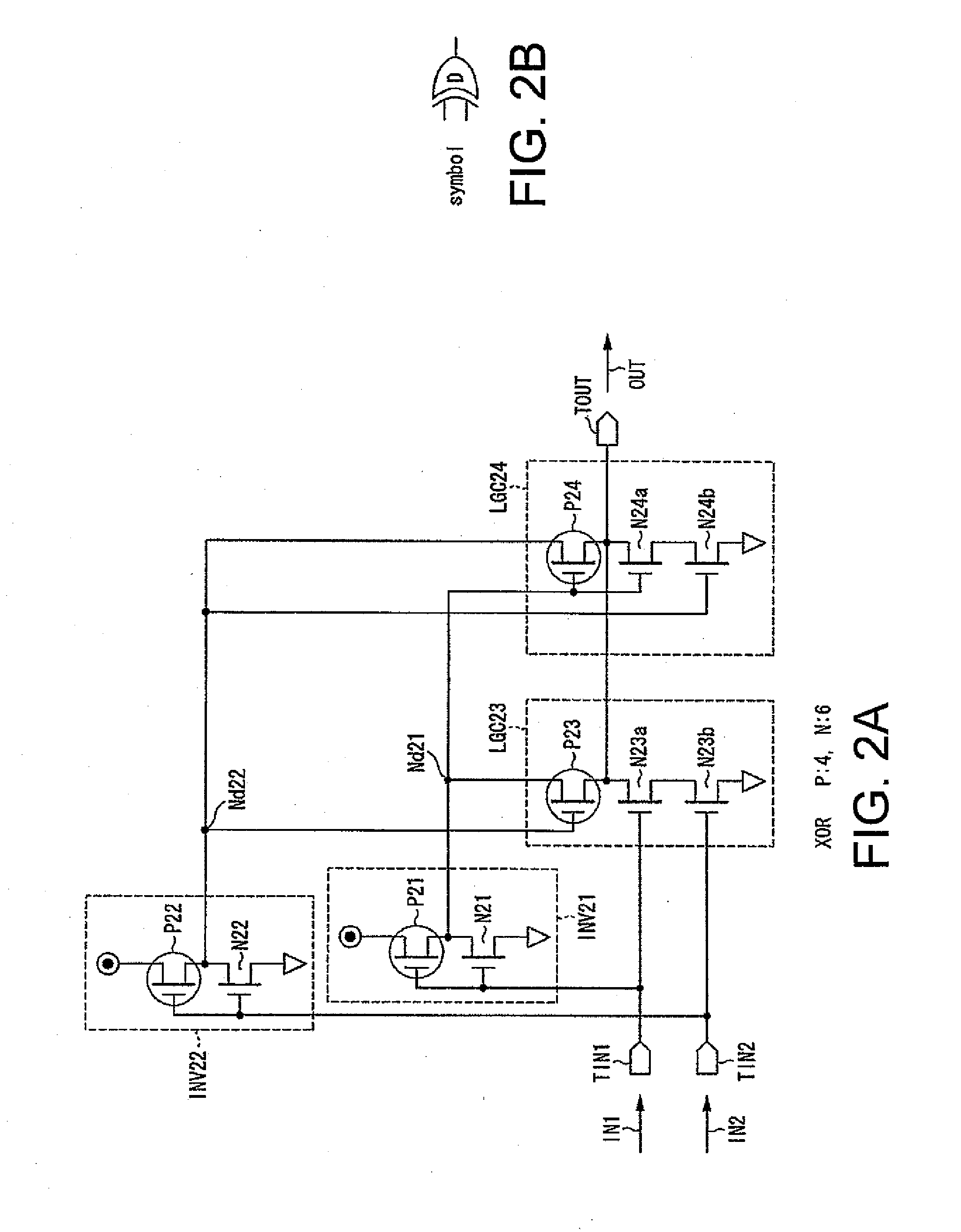

Semiconductor device including multiple-input logic circuit with operation rate balanced with driving ability

InactiveUS20130082736A1Logic circuits characterised by logic functionLogic circuits coupling/interface using field-effect transistorsSemiconductorElectrical and Electronics engineering

Owner:PS4 LUXCO SARL

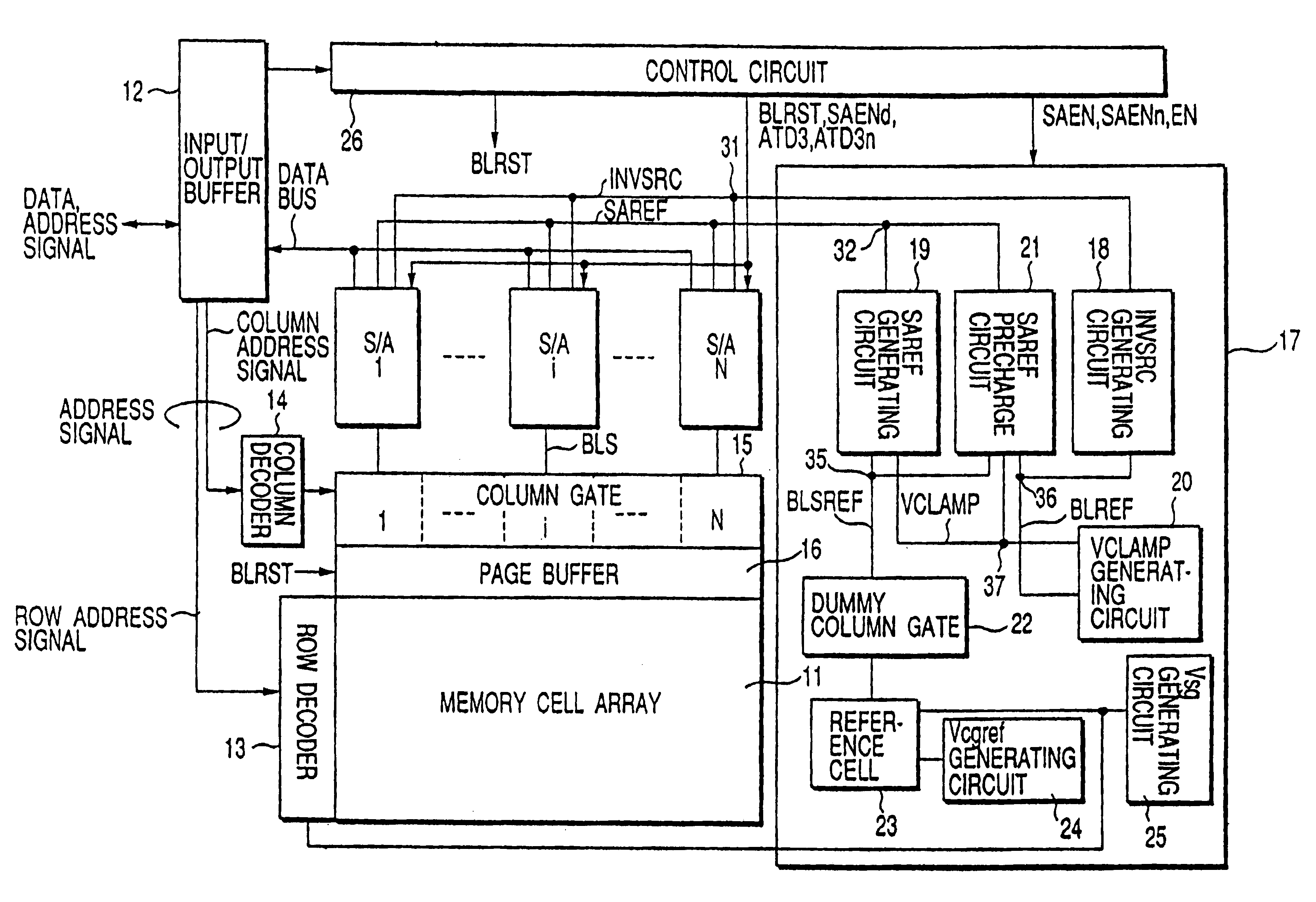

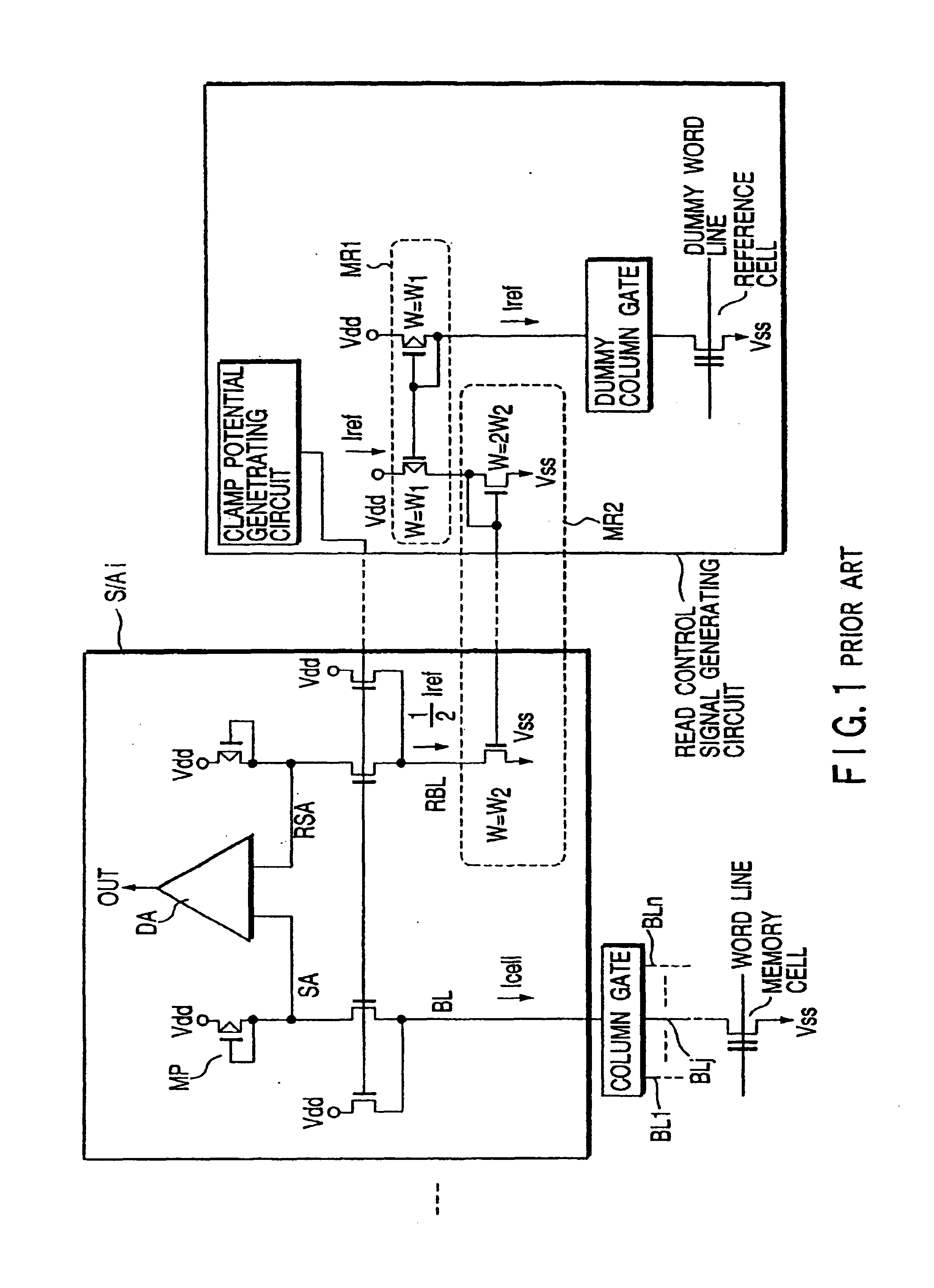

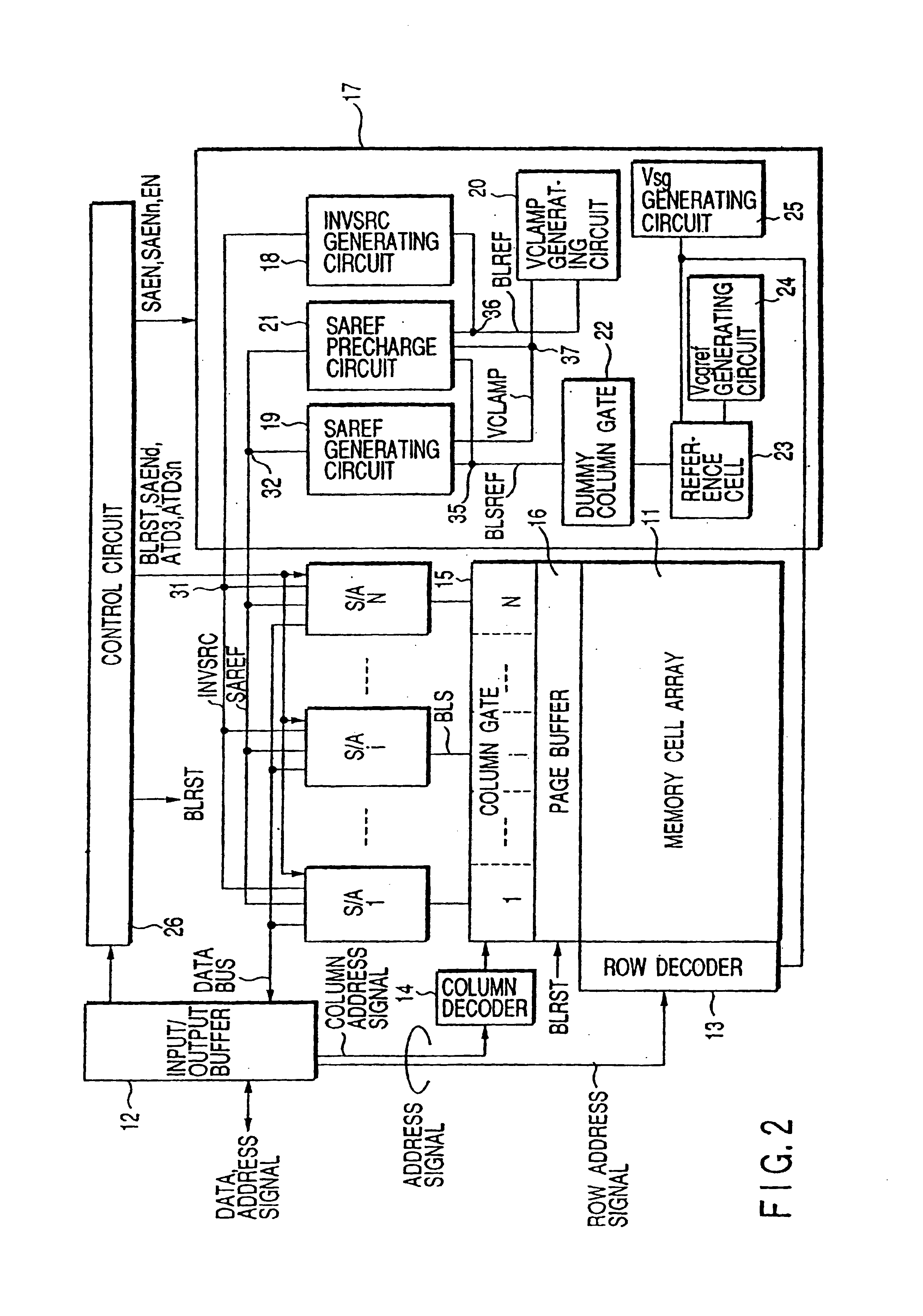

Read circuit of nonvolatile semiconductor memory

InactiveUS6845047B2Total current dropPerforming readRead-only memoriesDigital storageBit lineComputer architecture

Owner:KK TOSHIBA

Resistance variable memory device performing program and verification operation

A variable resistance memory device includes: a memory cell array comprising a plurality of memory cells, a pulse shifter shifting a plurality of program pulses to generate a plurality of shifted program pulses, a write and verification driver receiving the plurality of shifted program pulses to provide a program current that varies with the plurality of shifted program pulses to the plurality of memory cells, and control logic providing the plurality of program pulses to the pulse shifter and the write and verification driver during a program / verification operation, such at least two write data bits are programmed to the memory cell array in parallel during the program / verification operation.

Owner:SAMSUNG ELECTRONICS CO LTD

Popular searches

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap