Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

39results about "Electronic circuit testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

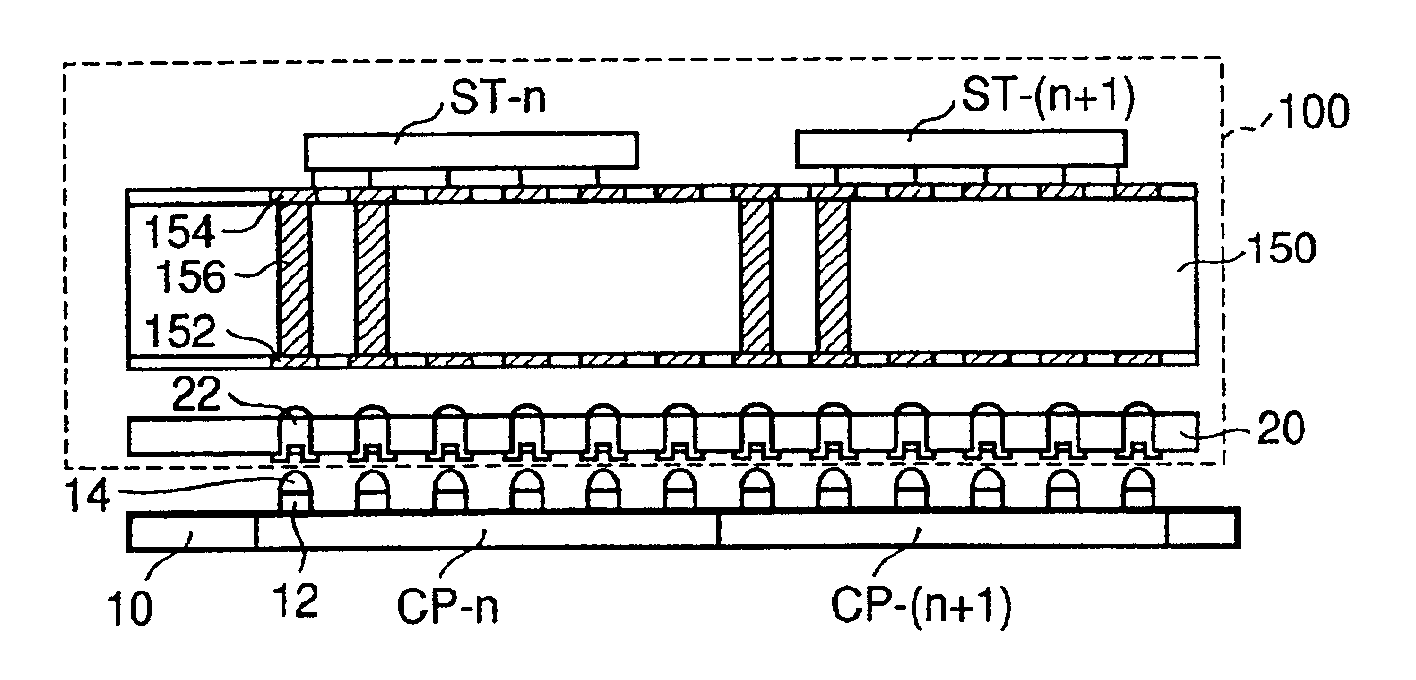

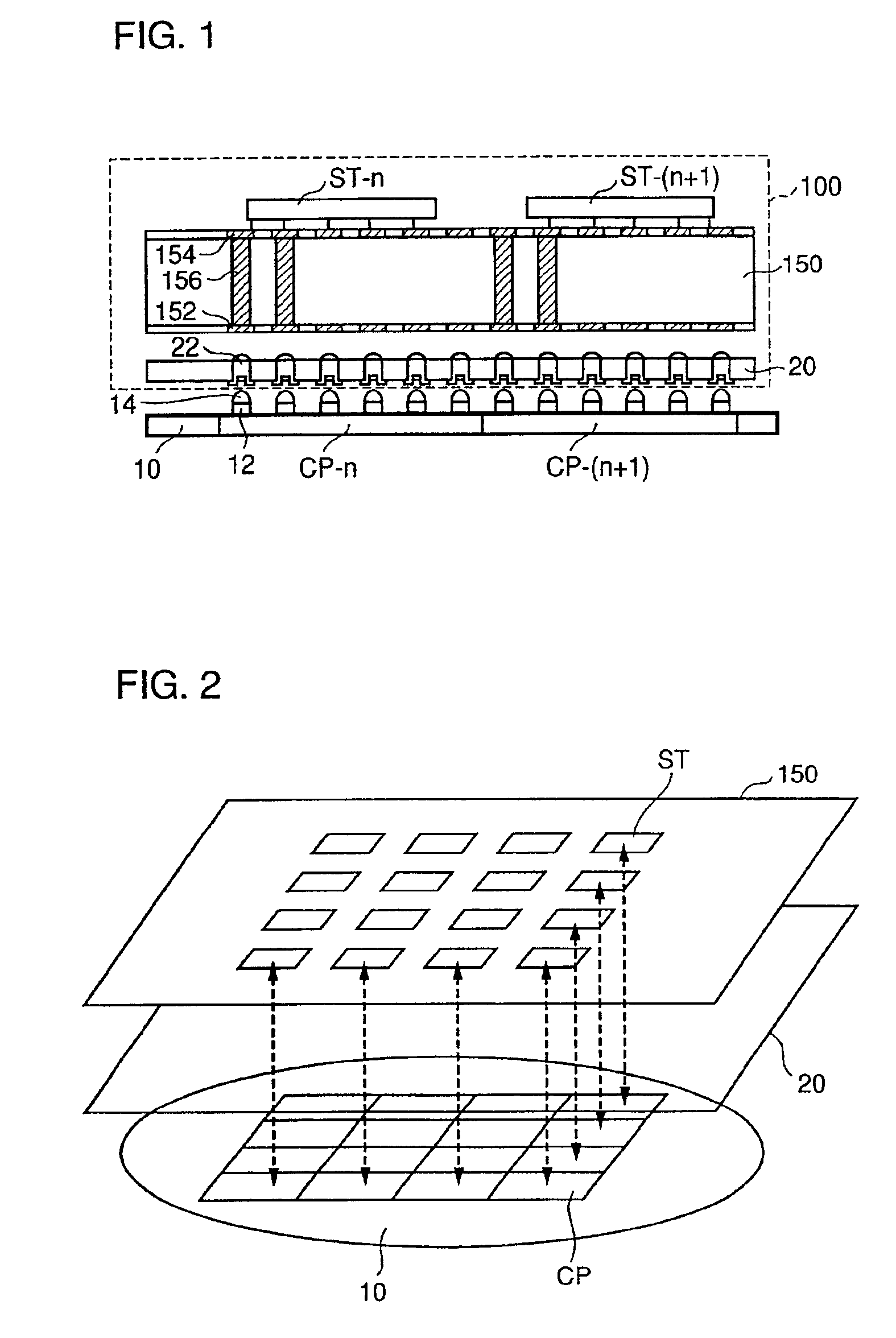

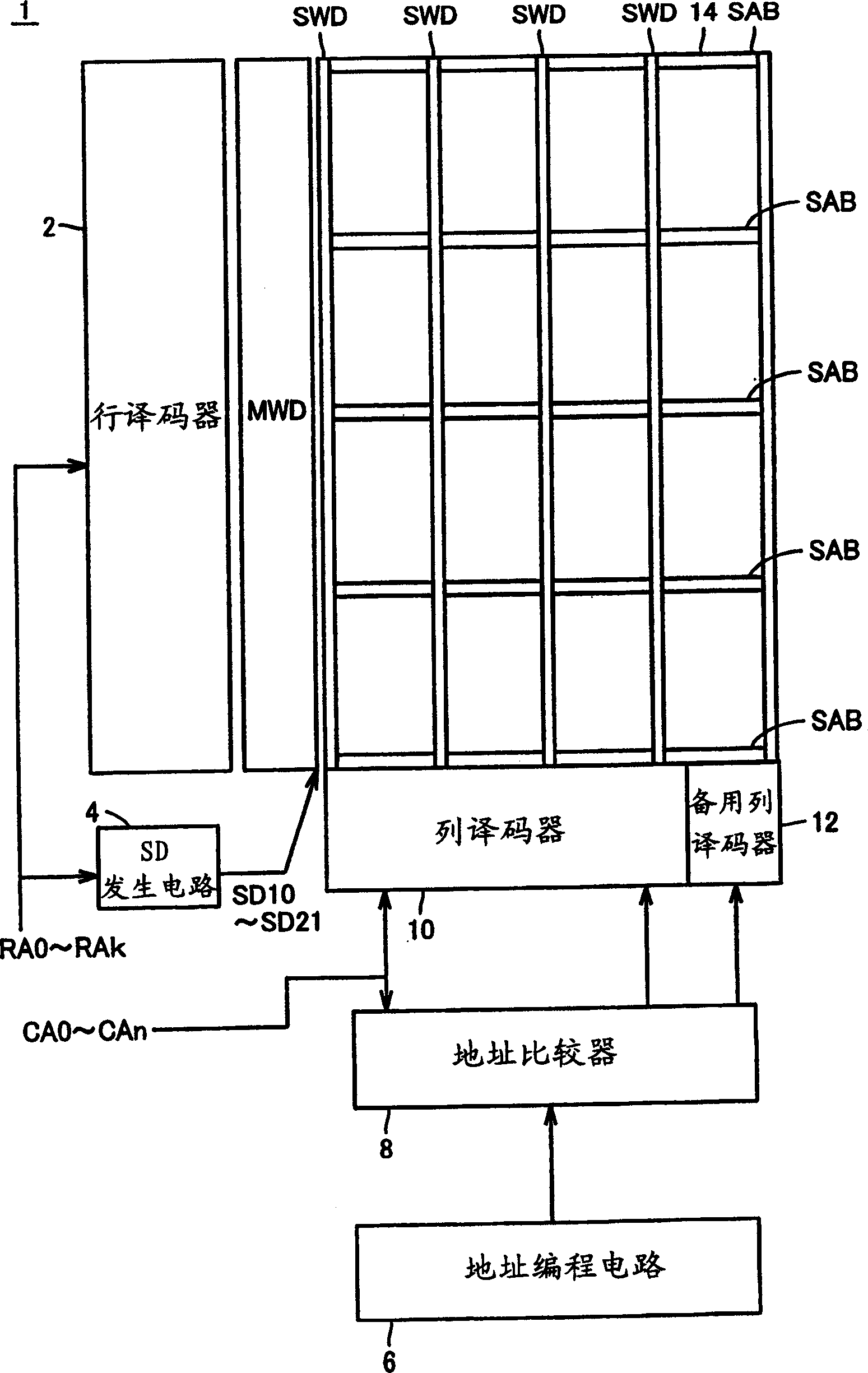

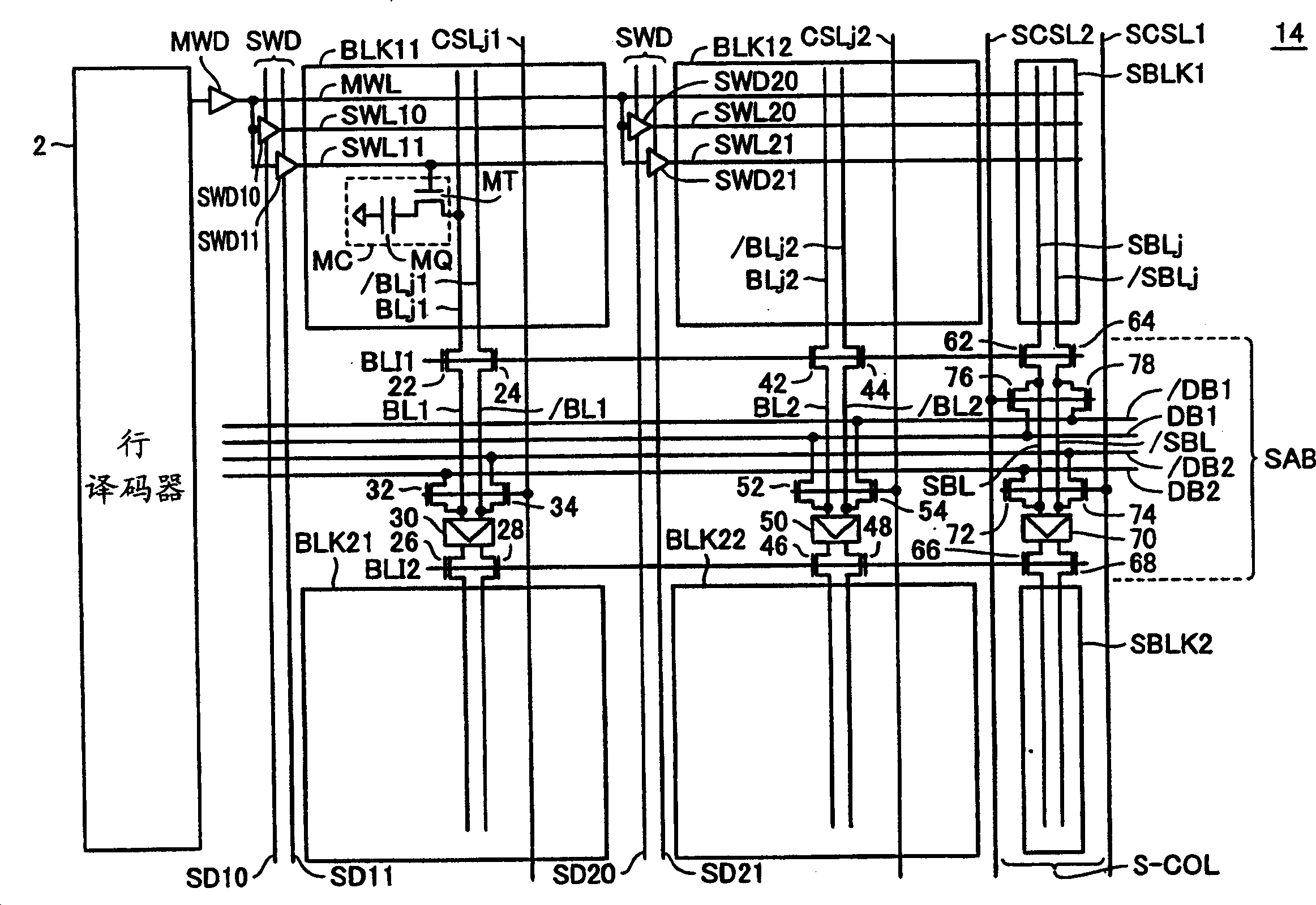

Semiconductor test device for conducting an operation test in parallel on many chips in a wafer test and semiconductor test method

InactiveUS6845477B2Suppressing increase in layout area of chipSimple processSemiconductor/solid-state device testing/measurementElectronic circuit testingContactorElectricity

Owner:RENESAS ELECTRONICS CORP

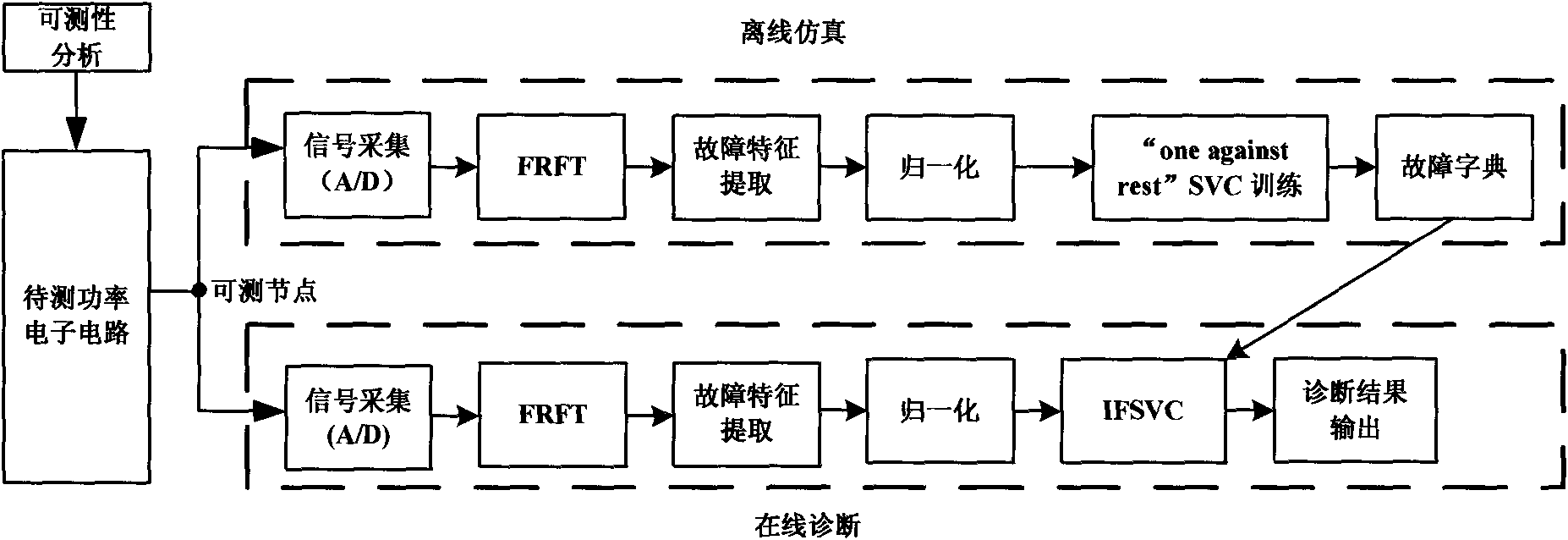

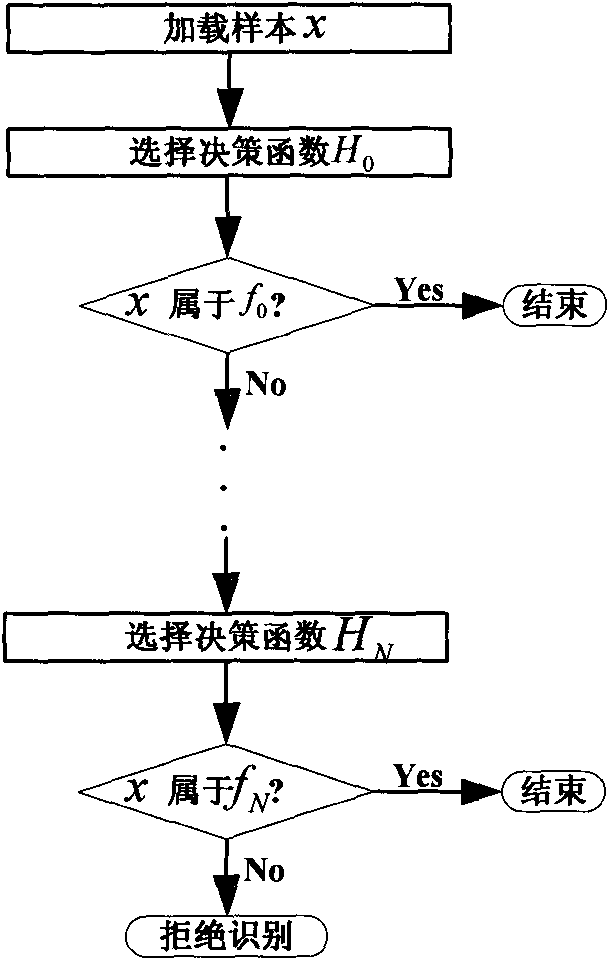

Online intelligent fault diagnosis method of power electronic circuit based on FRFT and IFSVC

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

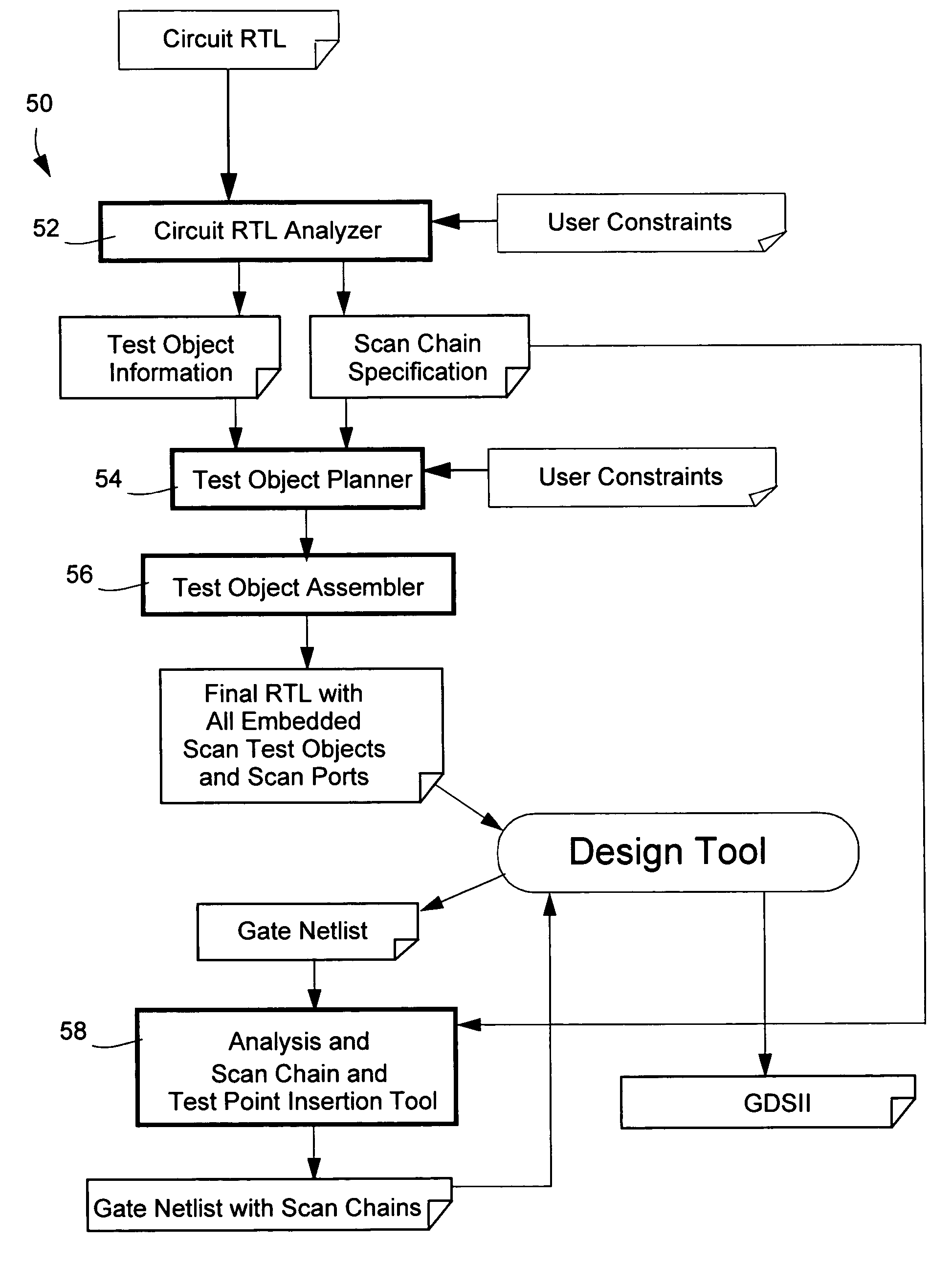

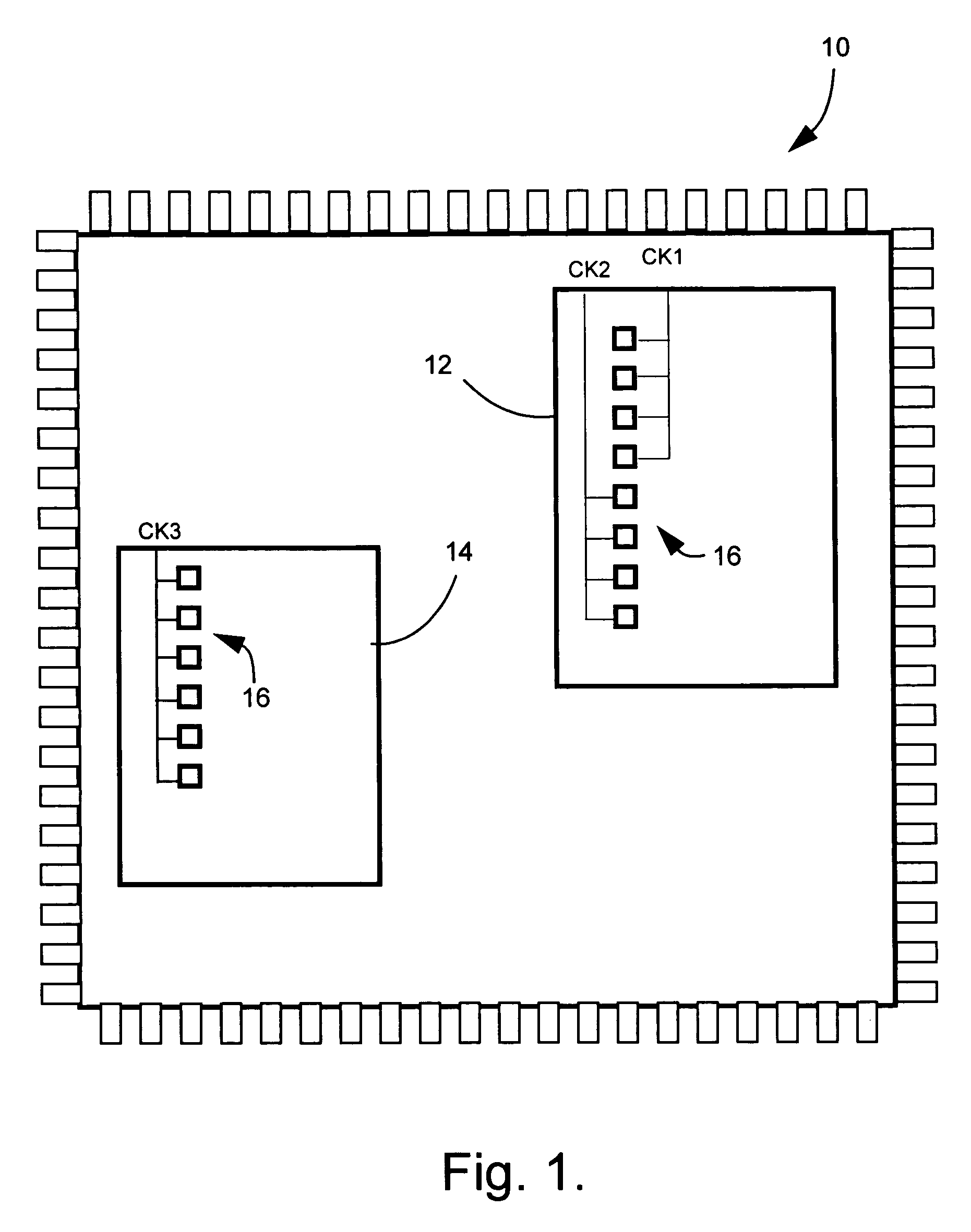

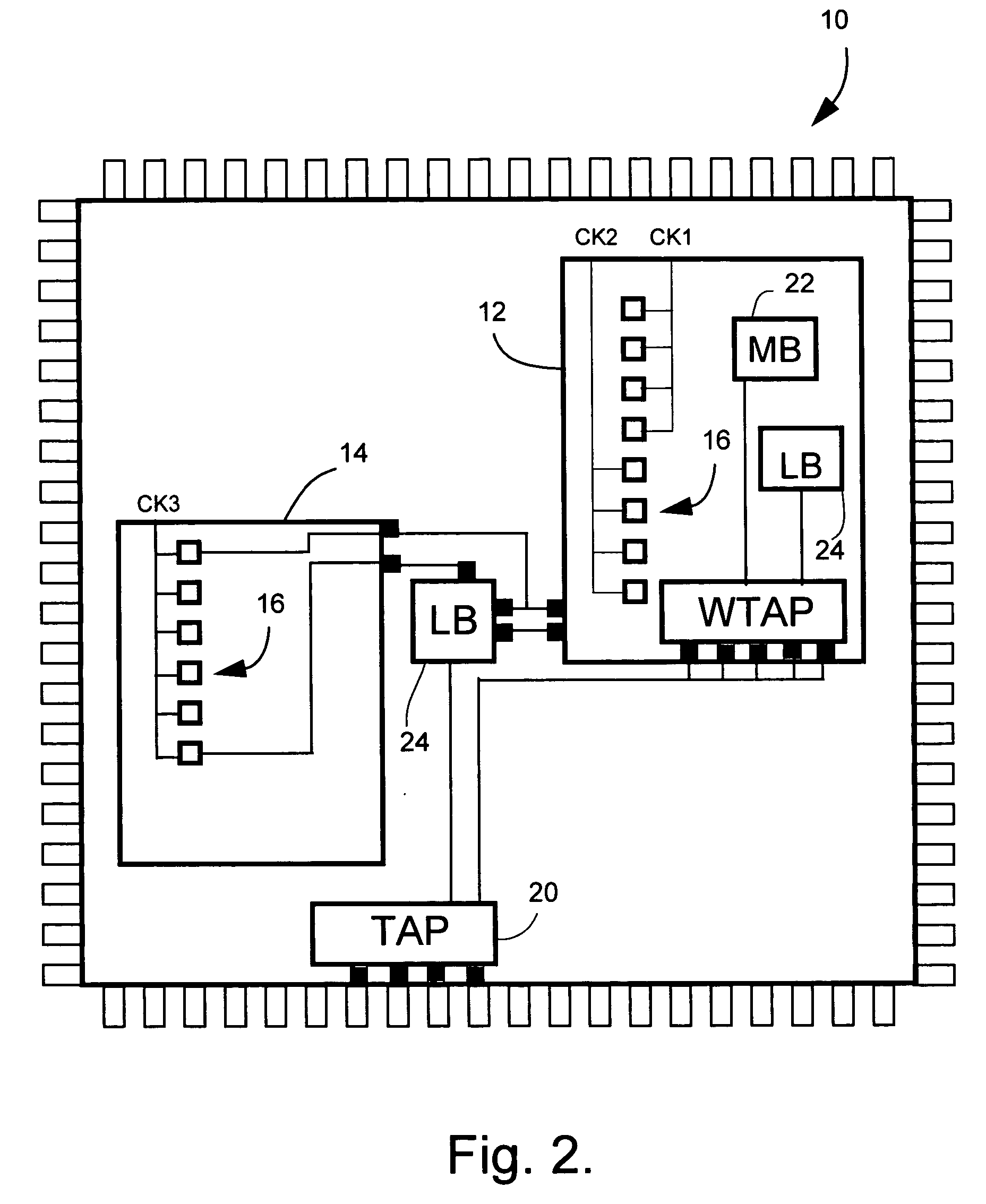

Insertion of embedded test in RTL to GDSII flow

InactiveUS20050273683A1Electronic circuit testingSoftware simulation/interpretation/emulationTest objectRegister-transfer level

A method of designing a scan testable integrated circuit with embedded test objects for use in scan testing the circuit, comprises compiling a register-transfer level (RTL) circuit description of the circuit into an unmapped circuit description; extracting information from the unmapped circuit description for use in generating and inserting RTL descriptions of test objects into the RTL circuit description and for use in generating and inserting scan chains into the circuit; generating and inserting the RTL descriptions of the test objects into the RTL circuit description to produce a modified RTL circuit description; storing the modified RTL circuit description; synthesizing the modified RTL description into a gate level circuit description of the circuit; and constructing and inserting scan chains into the gate level circuit description according to information extracted from the unmapped circuit description.

Owner:LOGICVISION

Semiconductor memory device

ActiveUS20090219775A1Reduce and eliminate test timeElectronic circuit testingError detection/correctionHemt circuitsEngineering

Semiconductor memory device includes a cell array including a plurality of unit cells; and a test circuit configured to perform a built-in self-stress (BISS) test for detecting a defect by performing a plurality of internal operations including a write operation through an access to the unit cells using a plurality of patterns during a test procedure carried out at a wafer-level.

Owner:SK HYNIX INC

Electronic article surveillance marker

InactiveUS20070194927A1Improve production yieldImprove reliabilityElectronic circuit testingBurglar alarm by hand-portable articles removalMagnetic tension forceMonitoring system

Owner:PHENIX LABEL

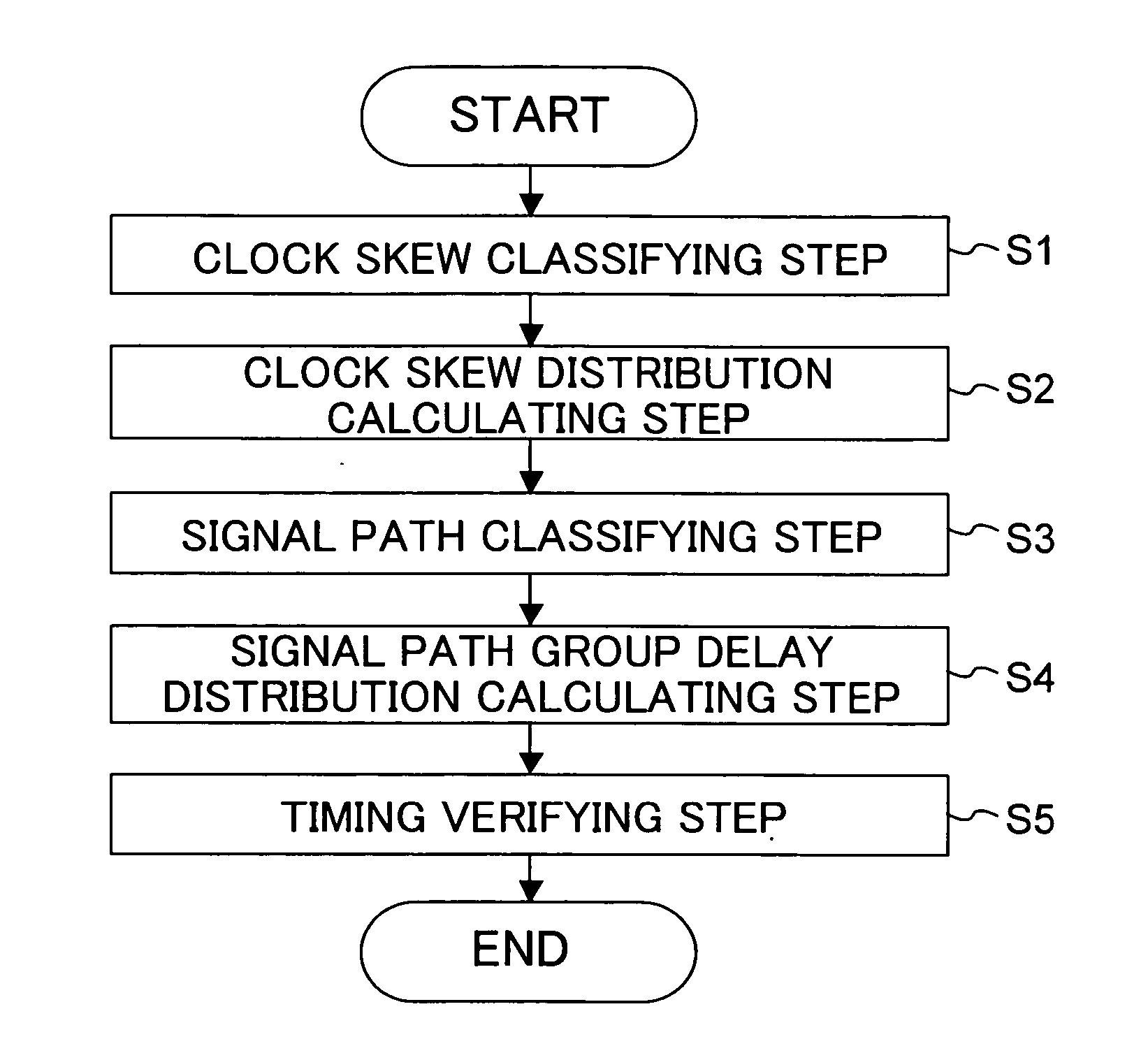

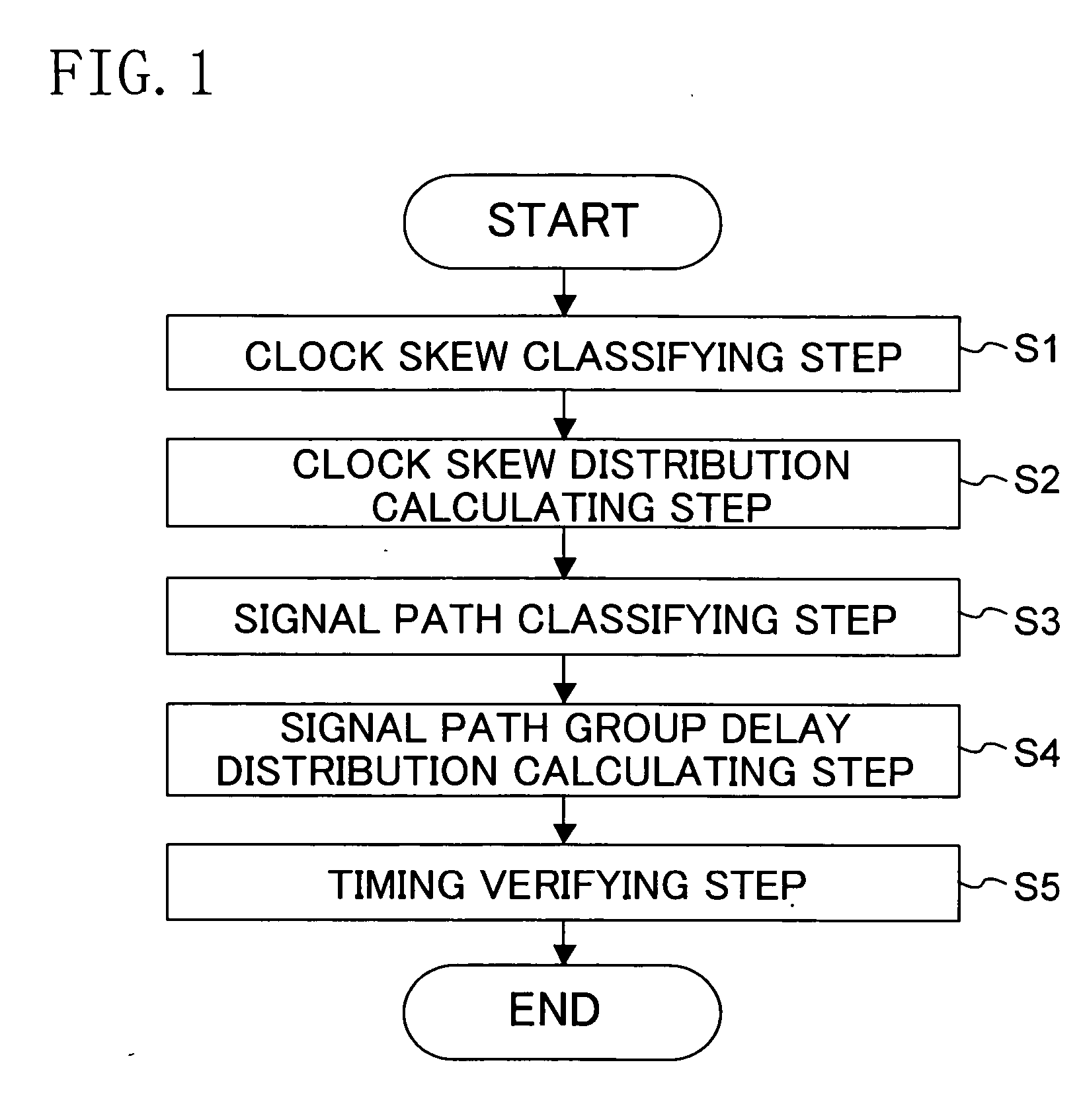

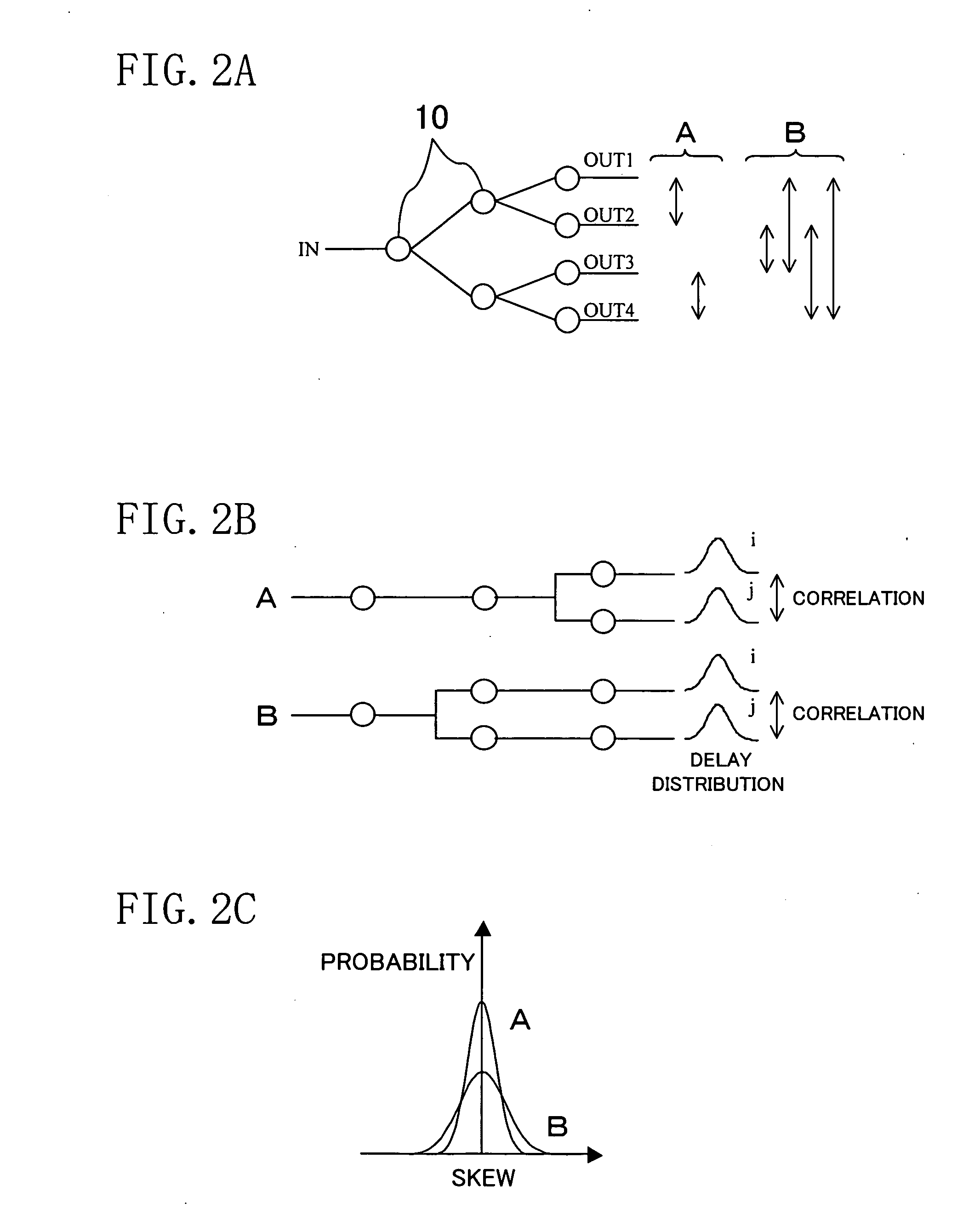

Timing verification method for semiconductor integrated circuit

ActiveUS20070050742A1Improve reliabilityNoise figure or signal-to-noise ratio measurementElectronic circuit testingComputer scienceSemiconductor

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

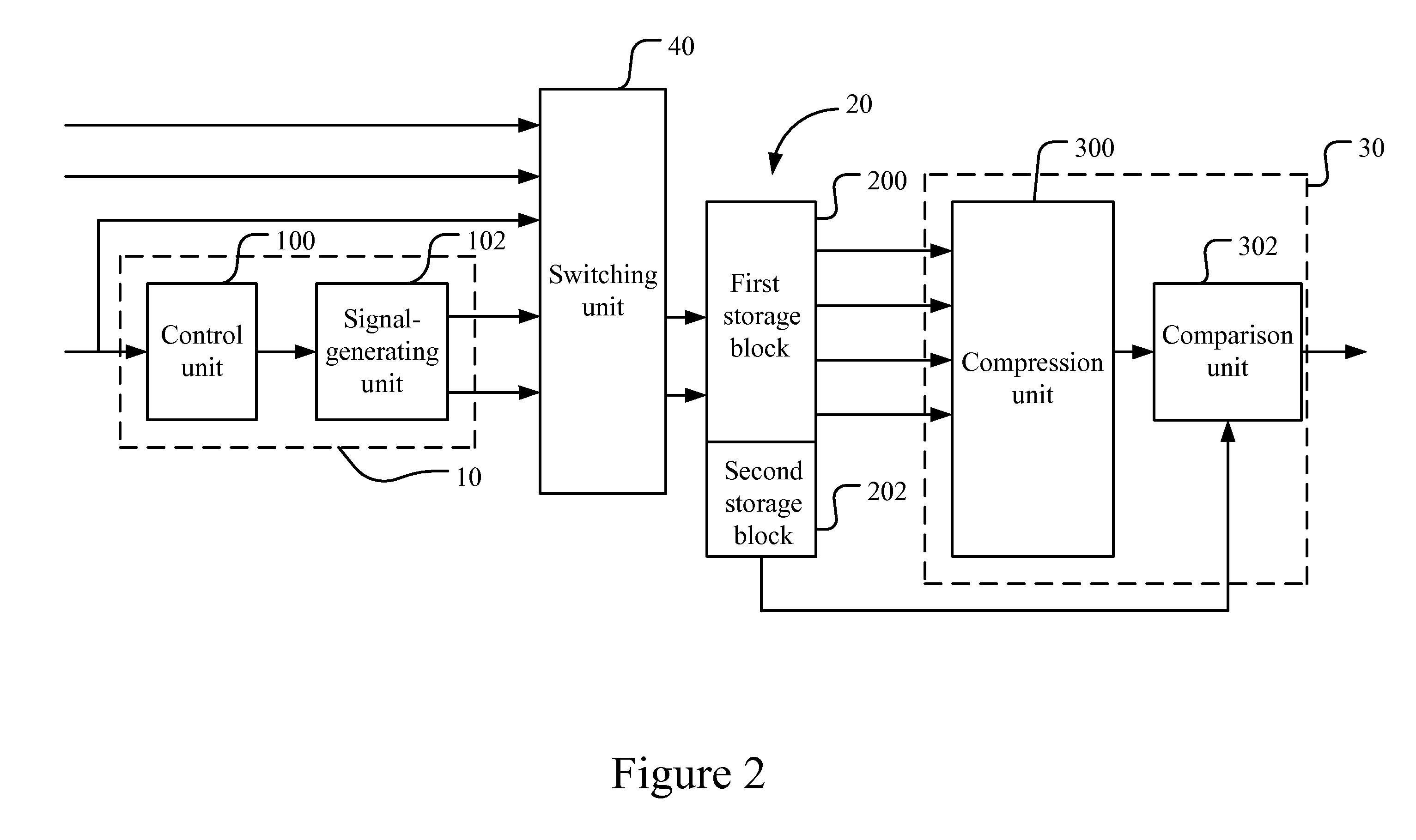

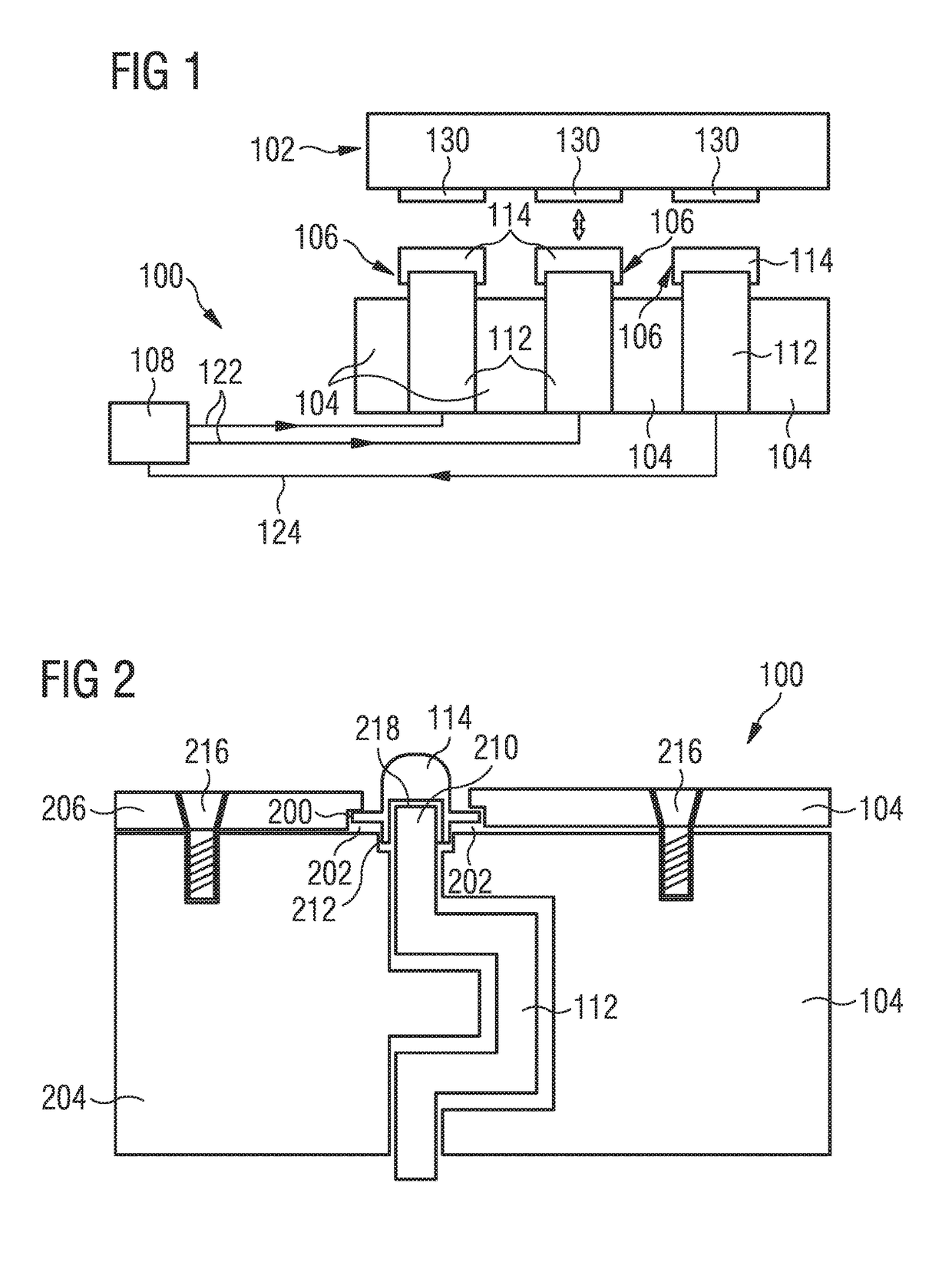

System and method for measuring a high speed signal

ActiveUS20050013355A1Transmitters monitoringElectric signal transmission systemsVoltage generatorFall time

An apparatus is provided for measuring an output of a high-speed data transmission circuit. The apparatus includes a programmable reference voltage generator operable to generate a reference voltage that is variable between a plurality of levels. The apparatus also includes a quantizer to quantize an output of the high-speed data transmission circuit relative to the reference voltage level input thereto. Also included is a clock generator operable to generate a clock having a transitioning time (rise-time, fall-time or both) that is less than one quarter of a minimum switching period of the output of the circuit. Finally, the apparatus includes a sampler operable to sample the quantized output with the clock to produce a plurality of samples which measure the output of the circuit.

Owner:MARVELL ASIA PTE LTD

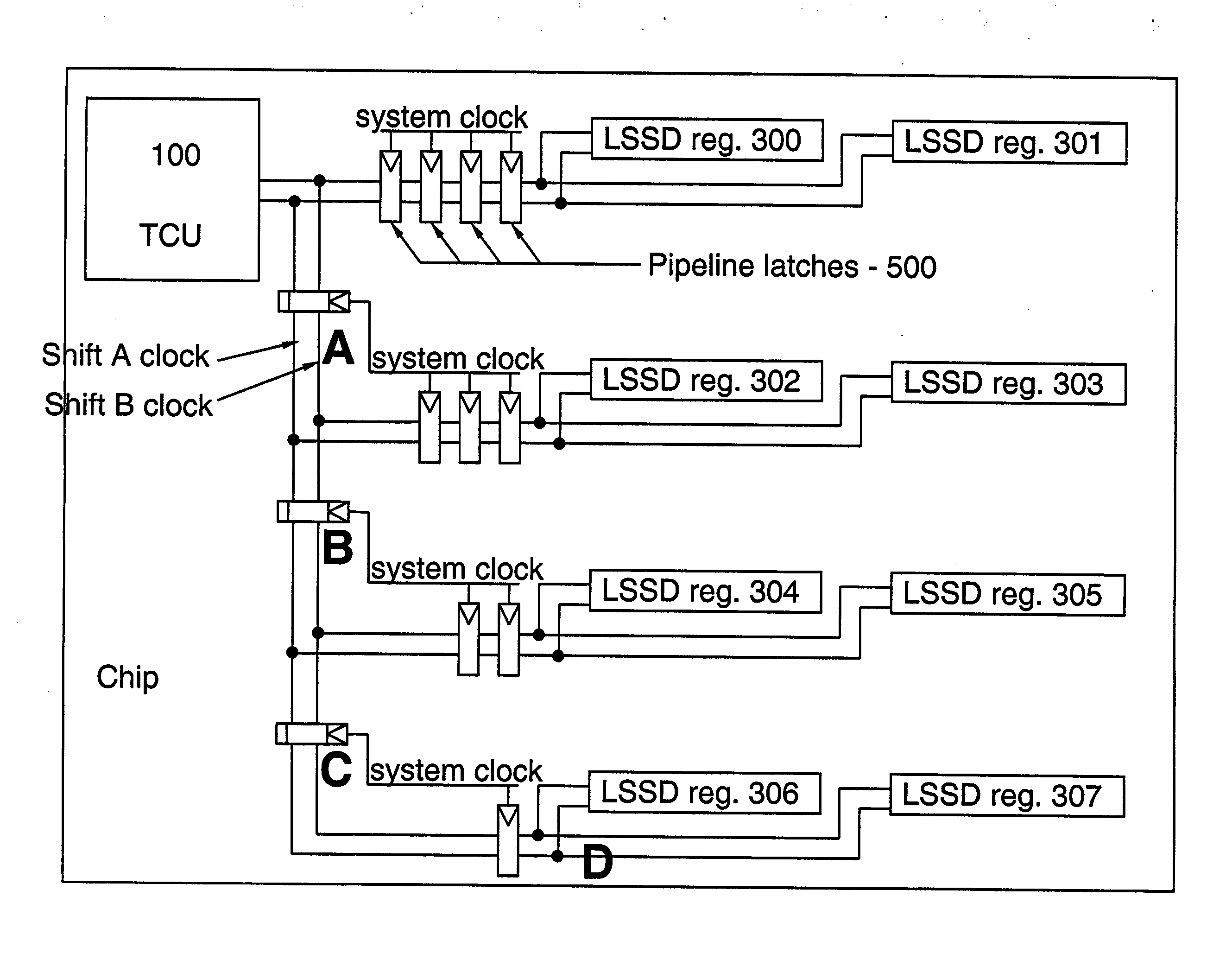

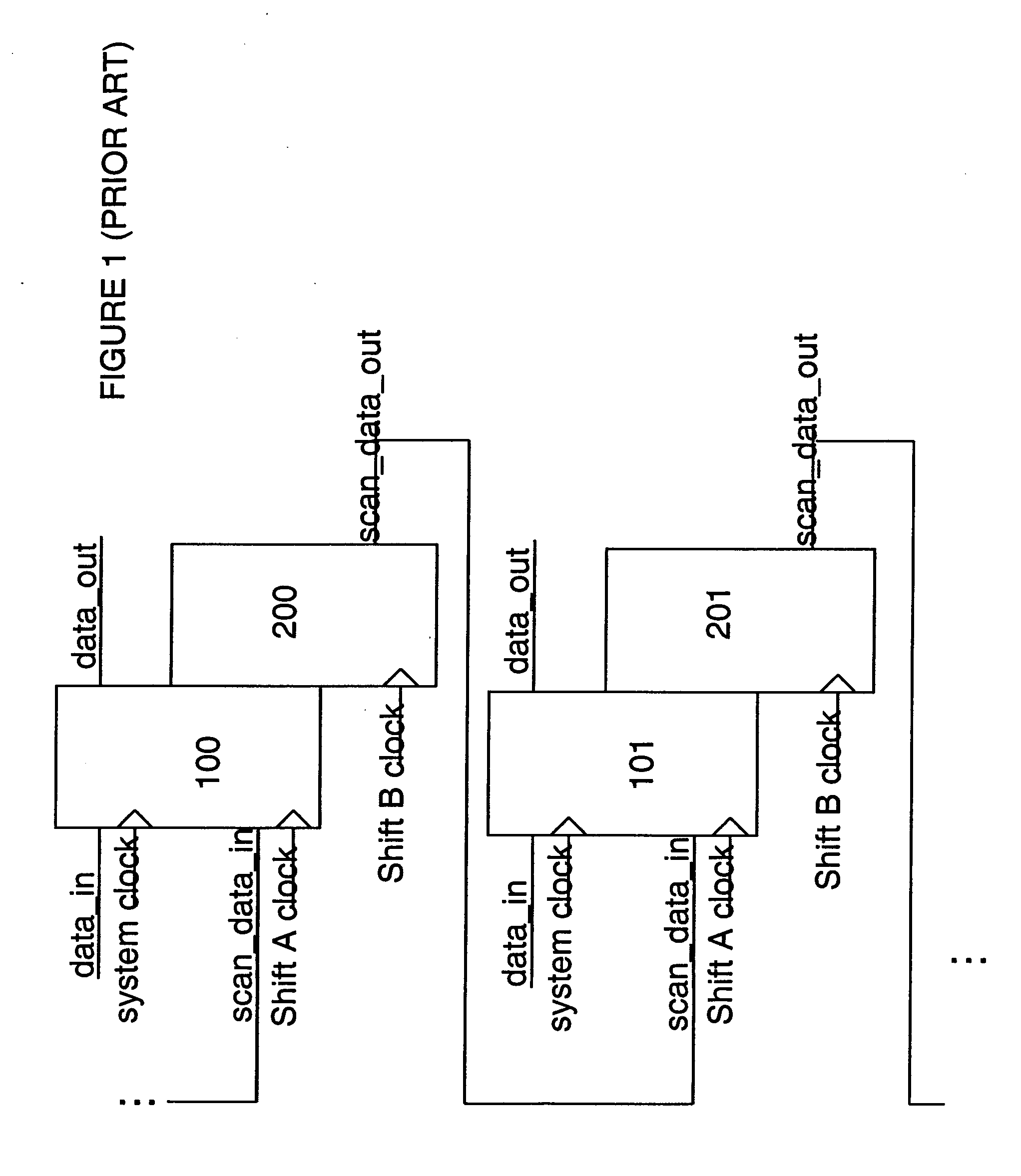

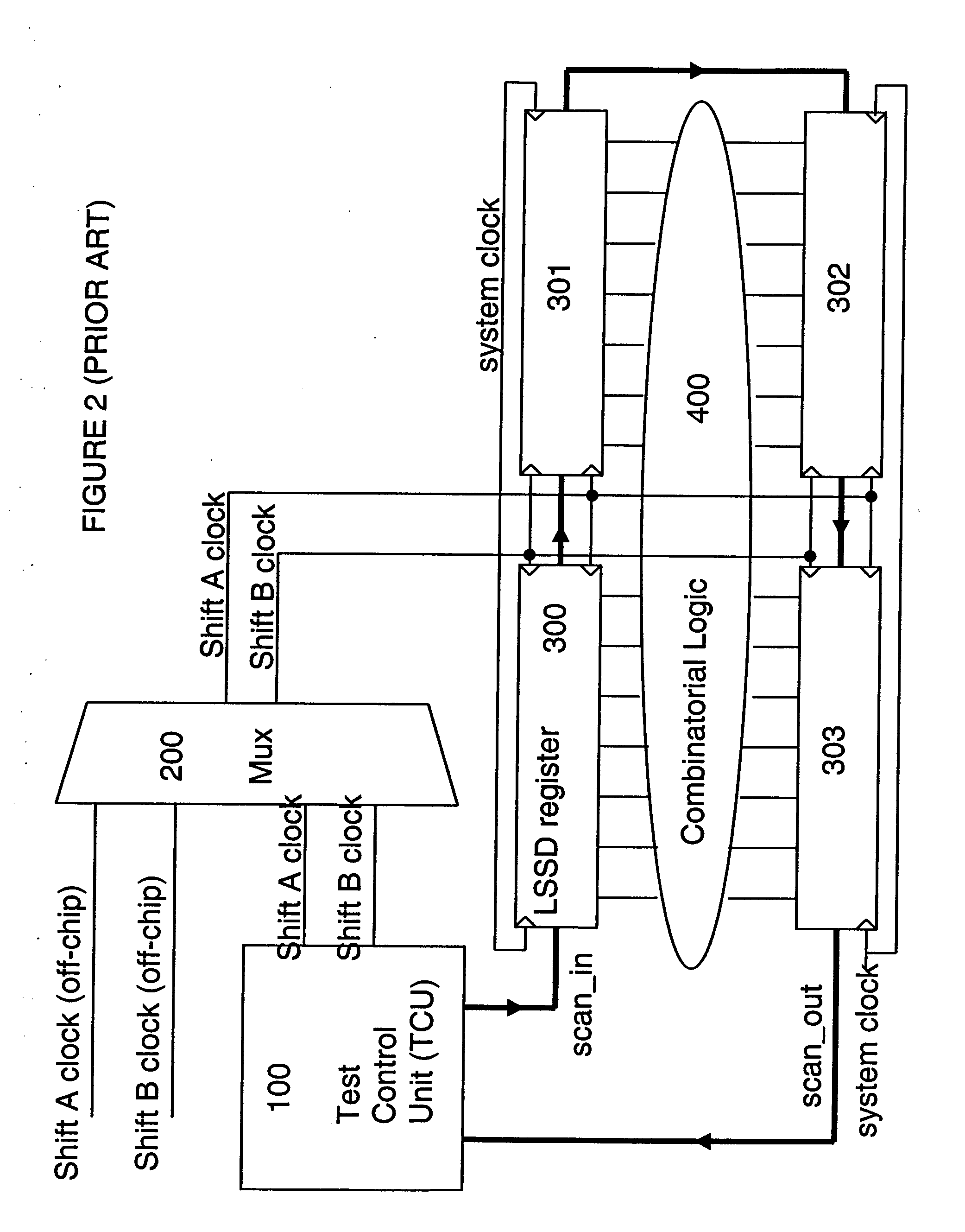

High-speed level sensitive scan design test scheme with pipelined test clocks

InactiveUS20060242506A1OptimizationElectronic circuit testingError detection/correctionSystem testingDesign testing

Owner:IBM CORP

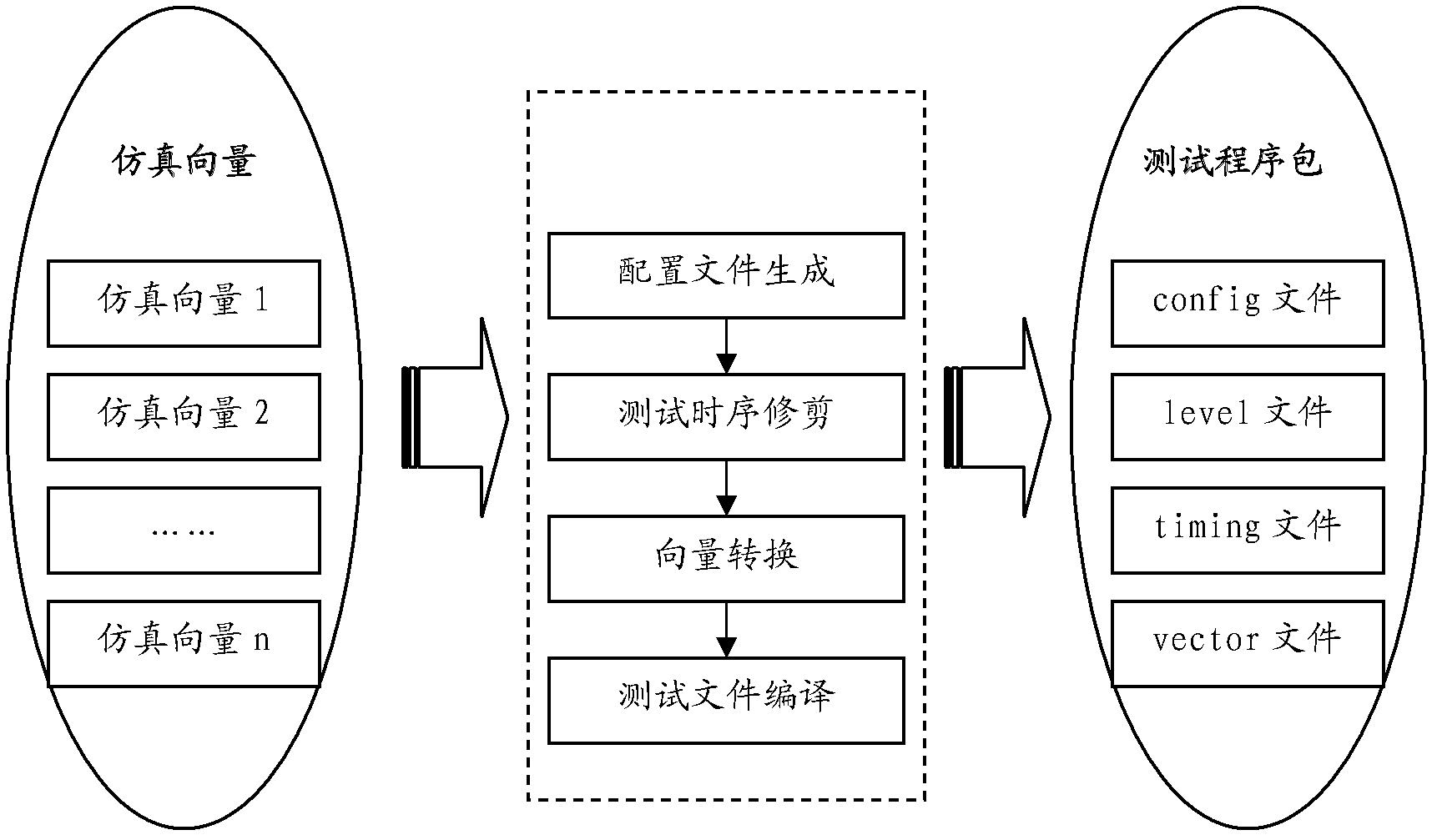

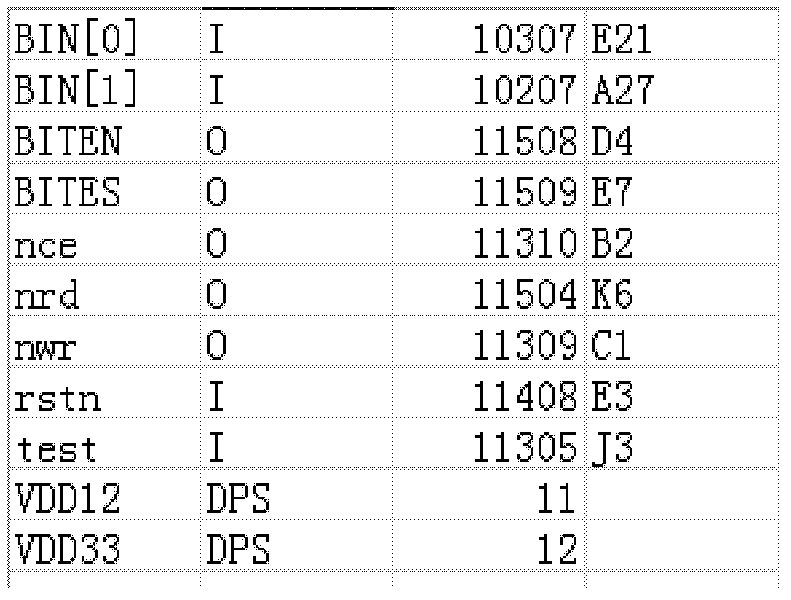

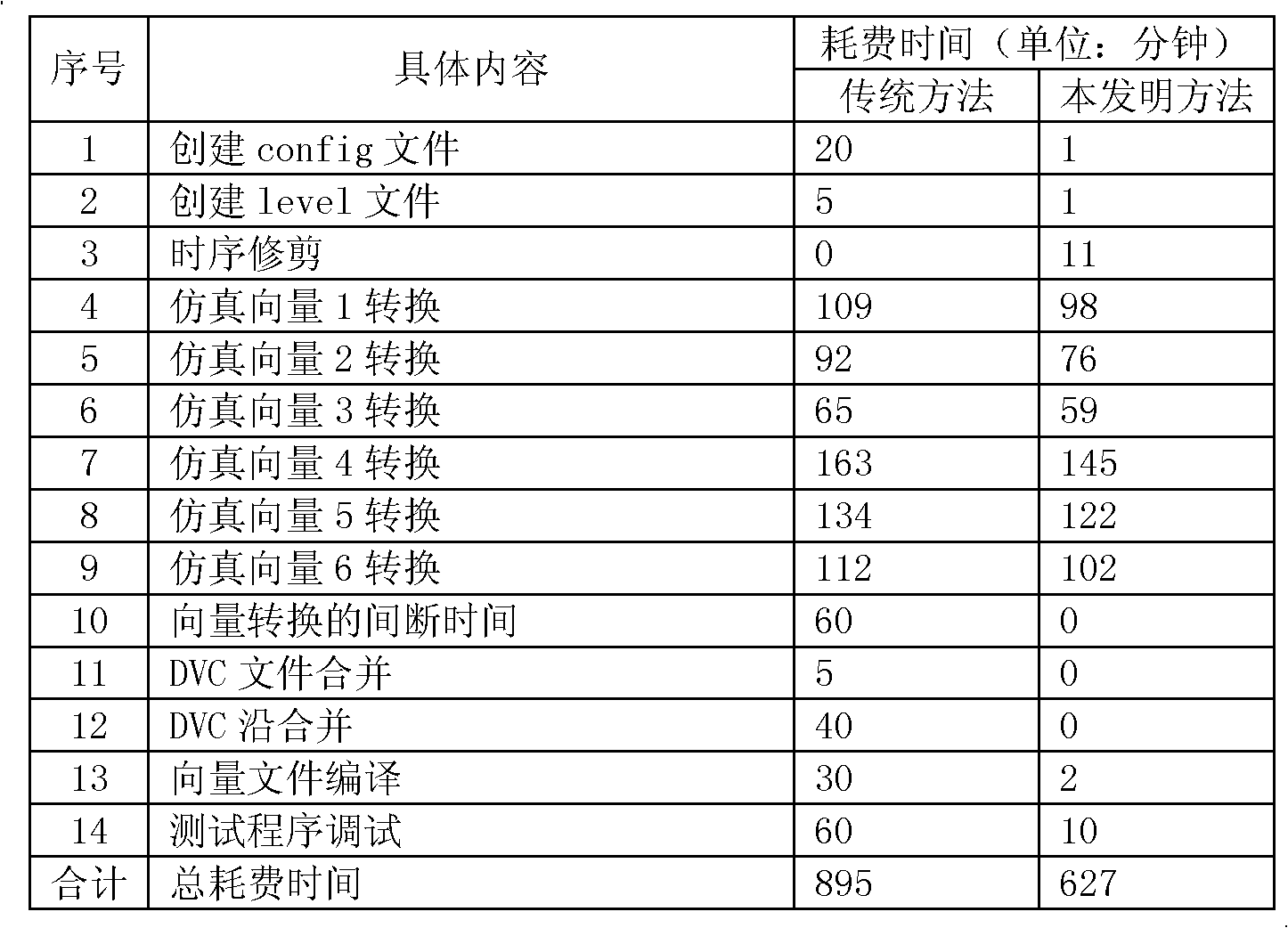

Method for rapidly creating integrated circuit test program package

InactiveCN102608517AAvoid errors caused by manual entryAvoid introducing errorsElectronic circuit testingCompact discTime information

Owner:FIFTH ELECTRONICS RES INST OF MINIST OF IND & INFORMATION TECH

Chip-based side channel leakage analysis system and method

PendingCN107783023AImprove signal-to-noise ratioHigh precisionElectronic circuit testingSignal-to-noise ratio (imaging)Security Measure

Owner:NATIONZ TECH INC

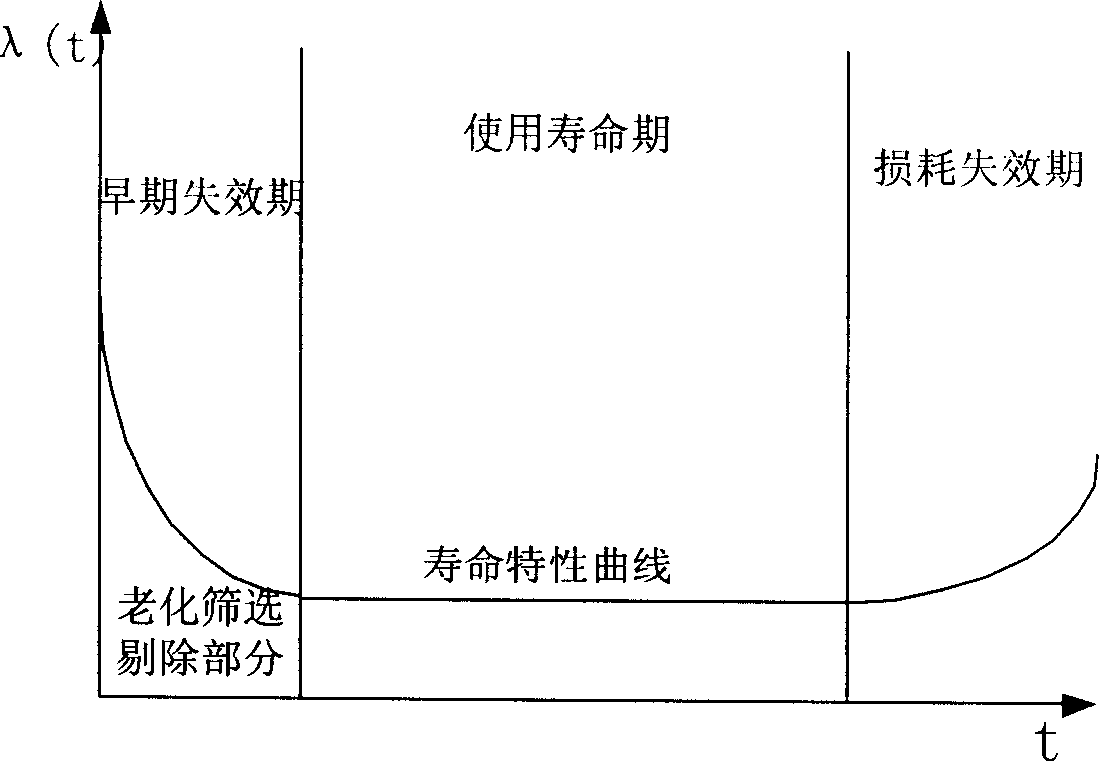

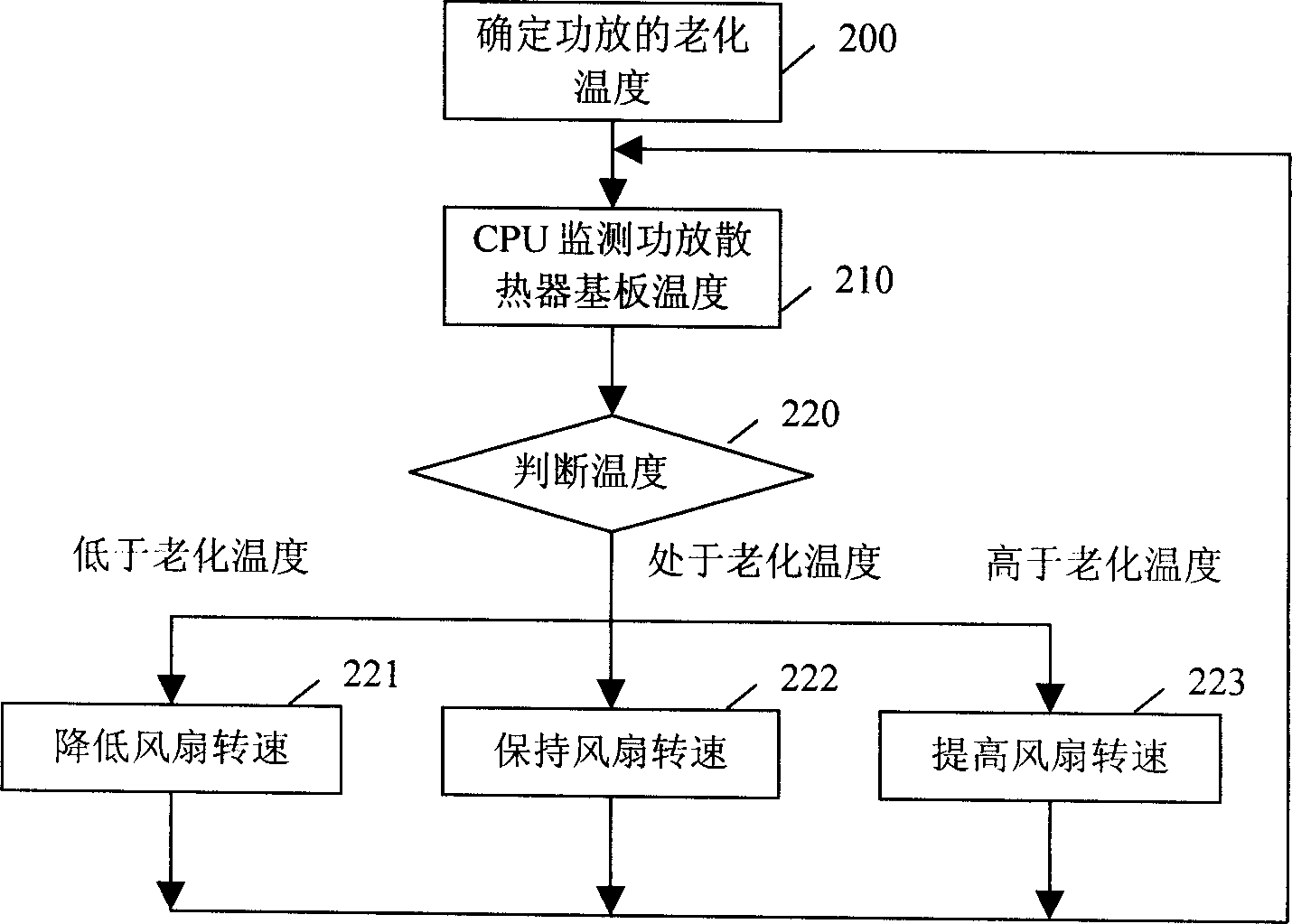

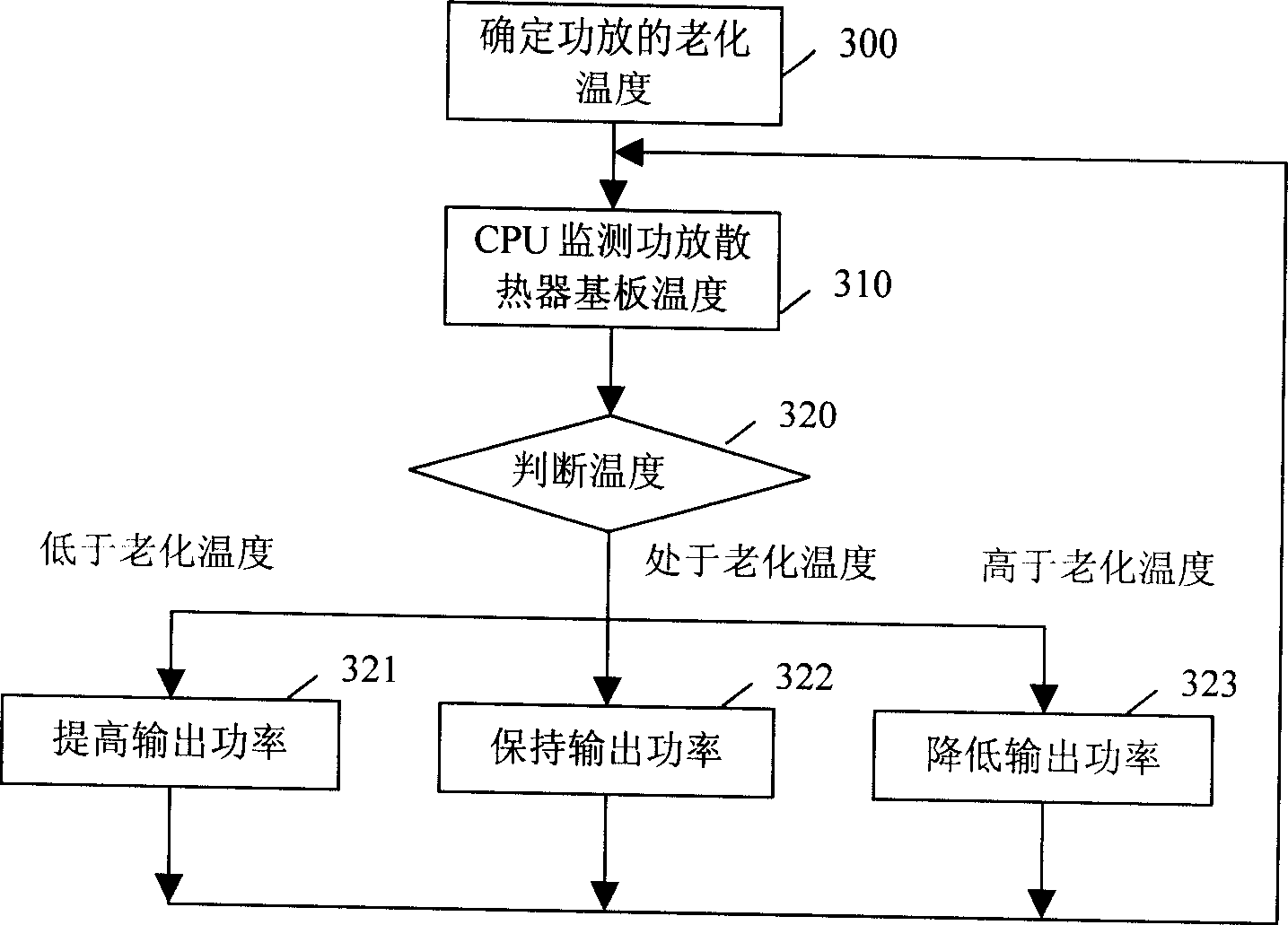

Electronic apparatus aging method based on heat radiator

InactiveCN1755381ASemiconductor/solid-state device testing/measurementElectronic circuit testingWork statusElectric energy

Owner:HUAWEI TECH CO LTD

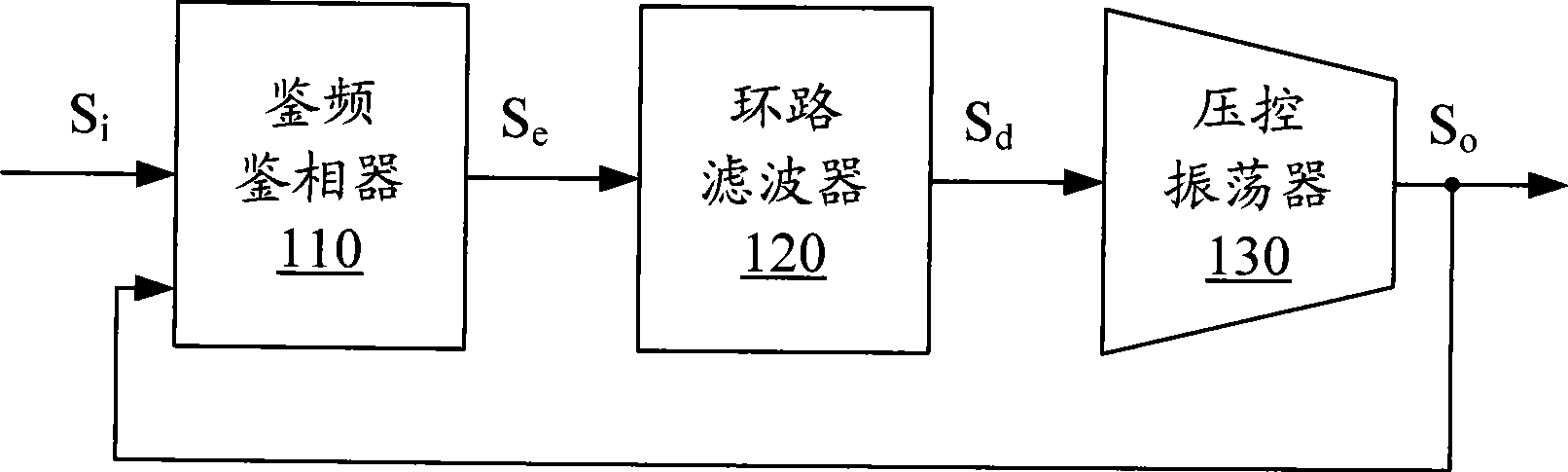

Test method for step response performance of phase-locked loop system

InactiveCN101498761AAvoid elicitingEasy to operateElectronic circuit testingPulse automatic controlEngineeringStep response

Owner:北京芯汇中秀电子技术有限公司

Integrated circuit and methods of measurement and preparation of measurement structure

InactiveUS20050283335A1Shorten analysis timeSemiconductor/solid-state device testing/measurementElectronic circuit testingEngineeringIntegrated circuit

Owner:IBM CORP

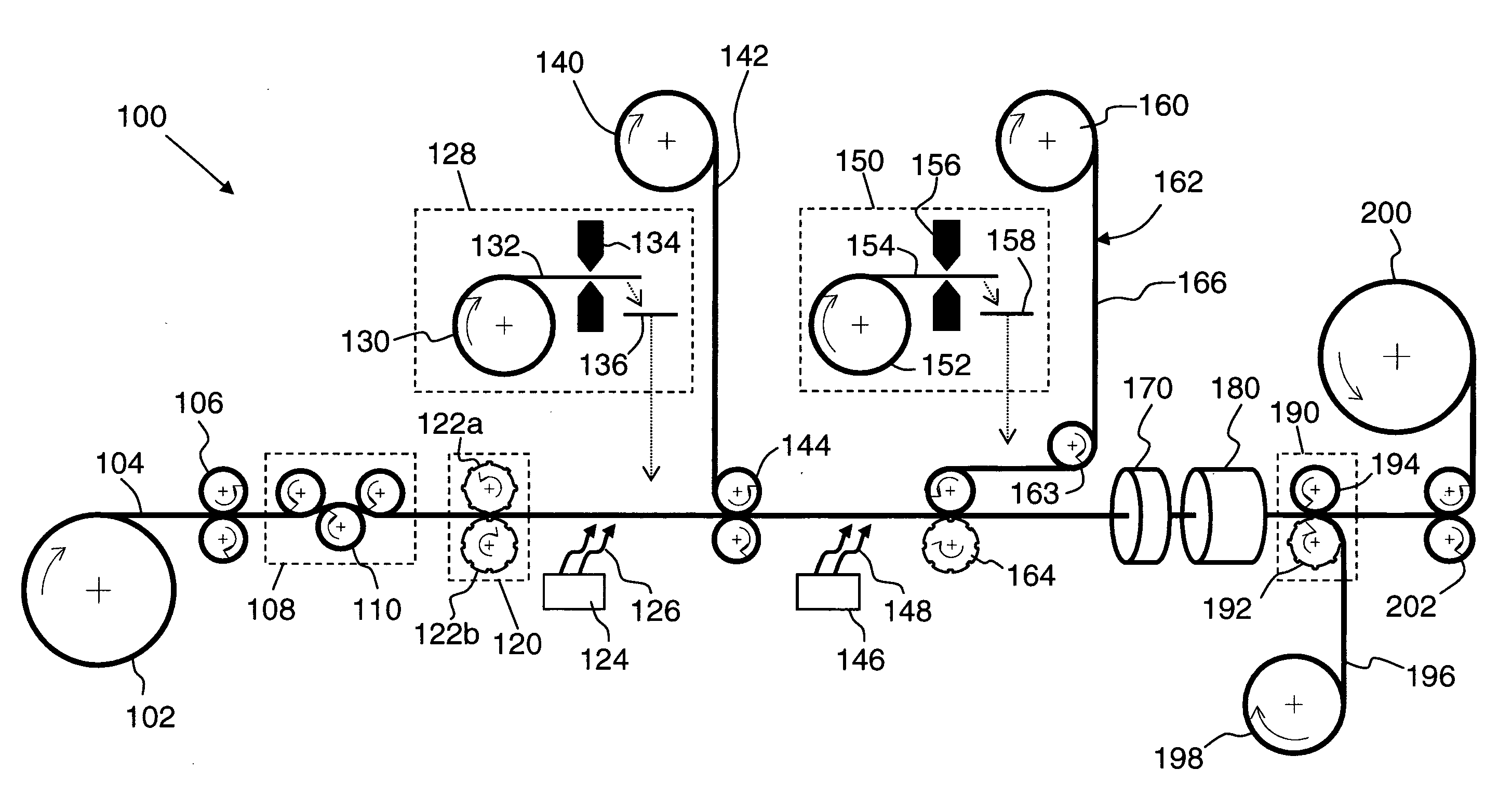

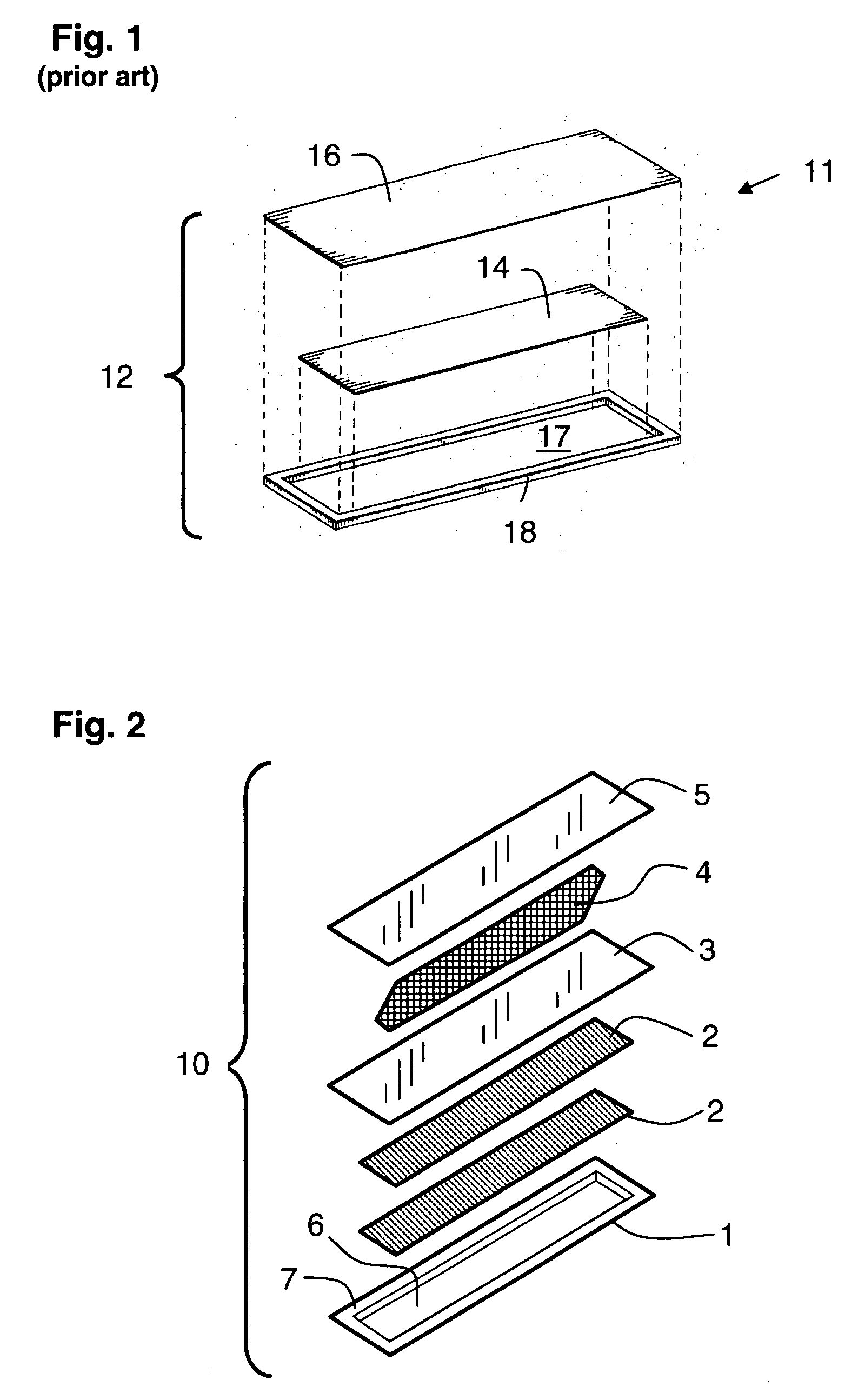

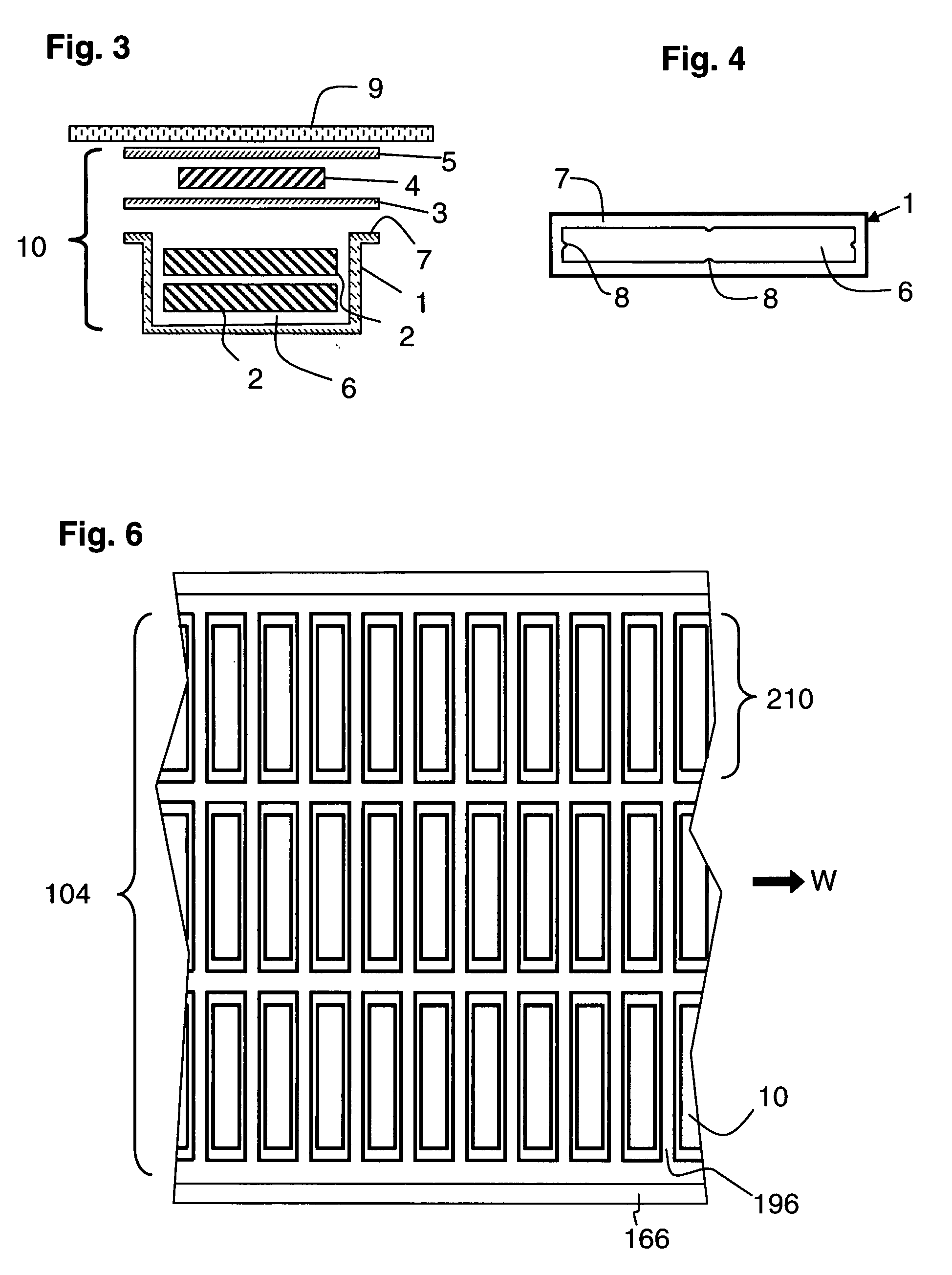

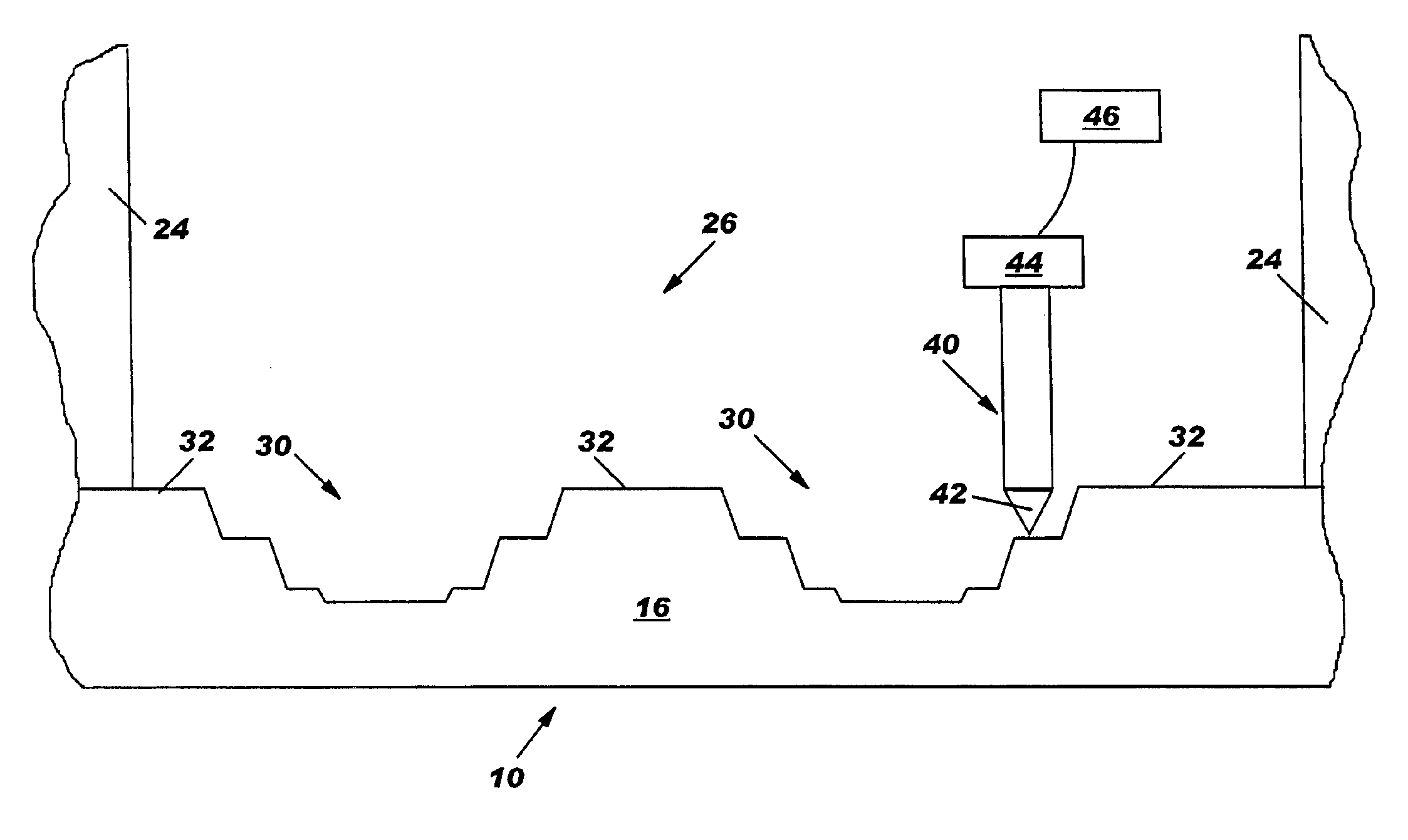

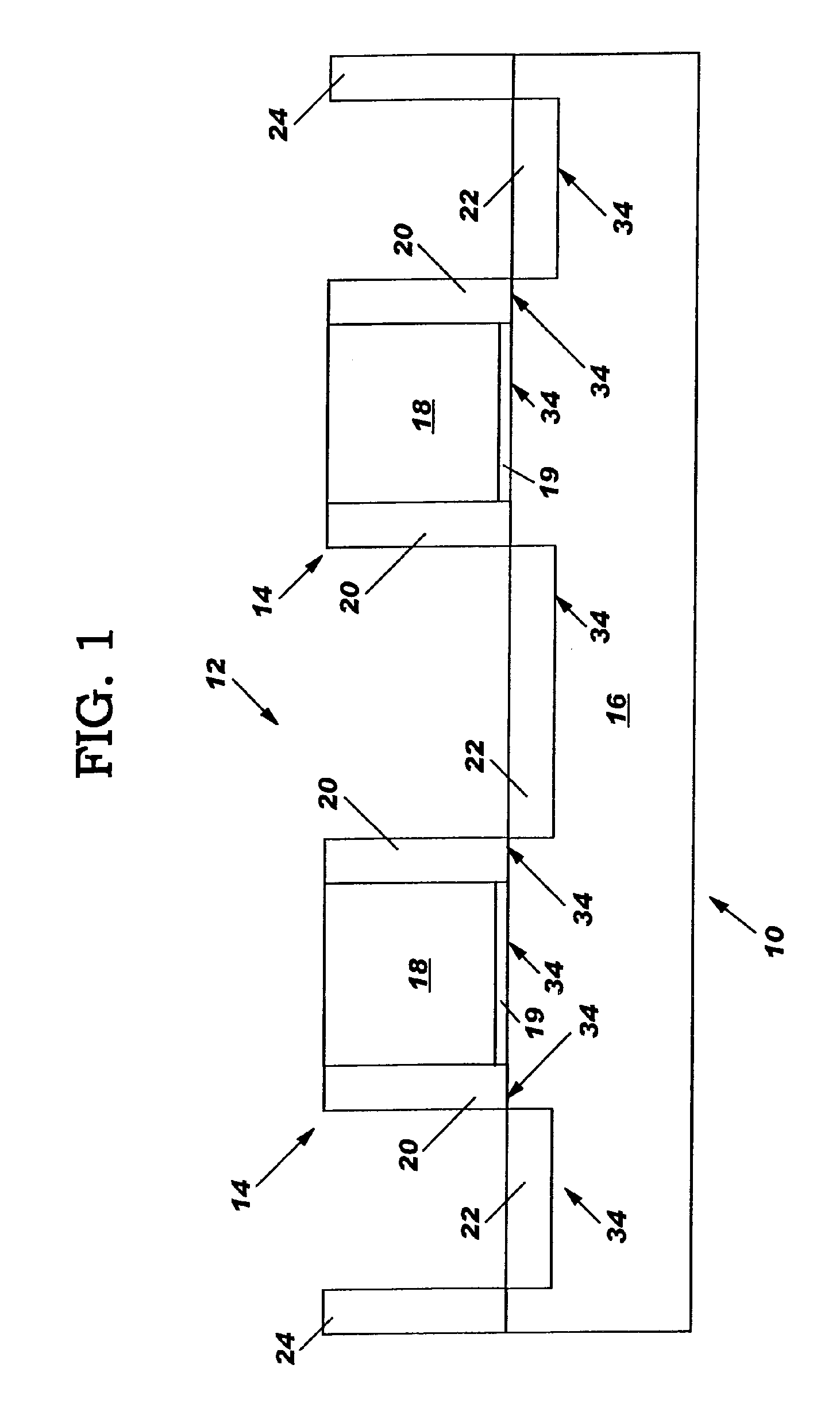

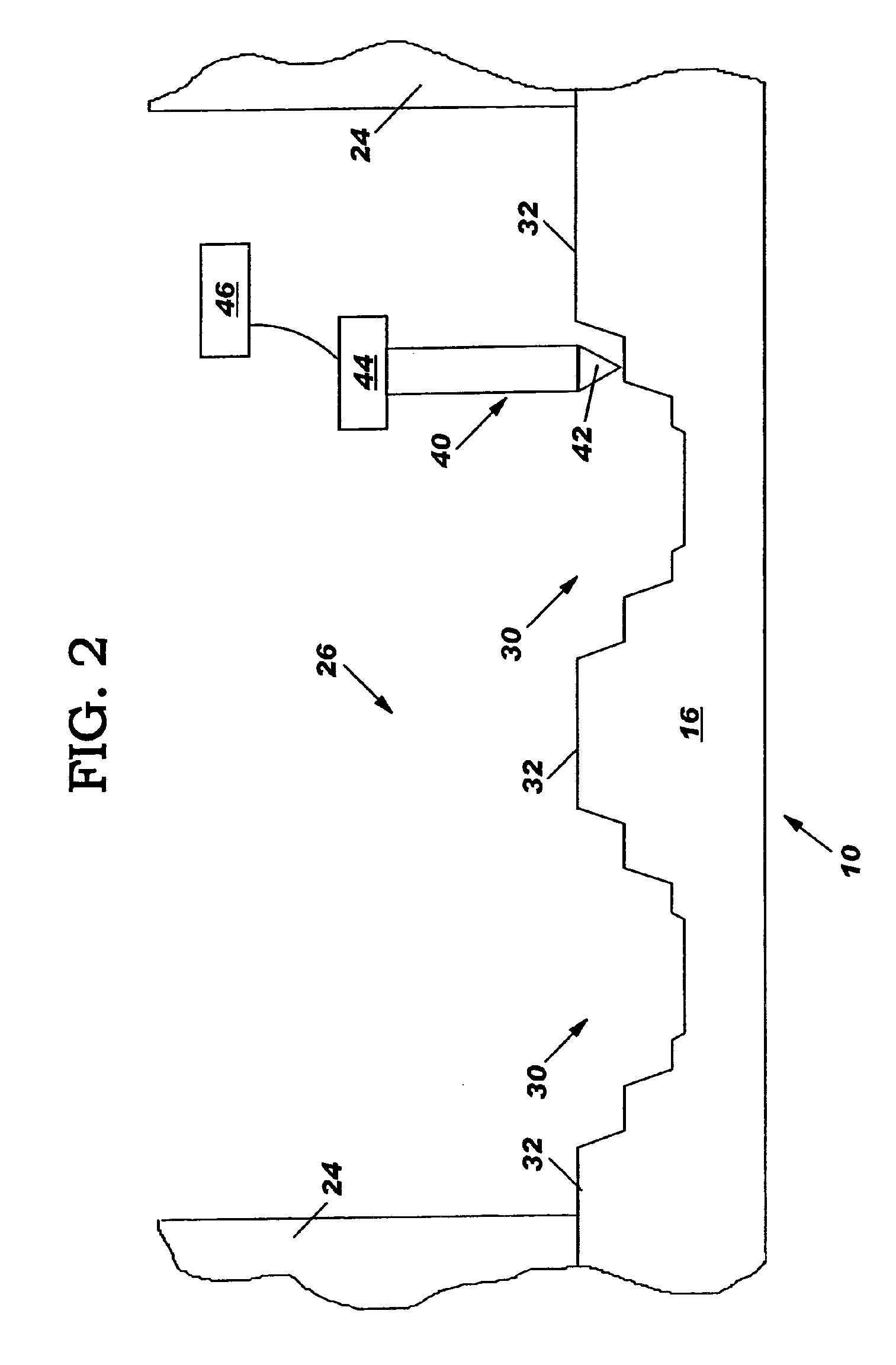

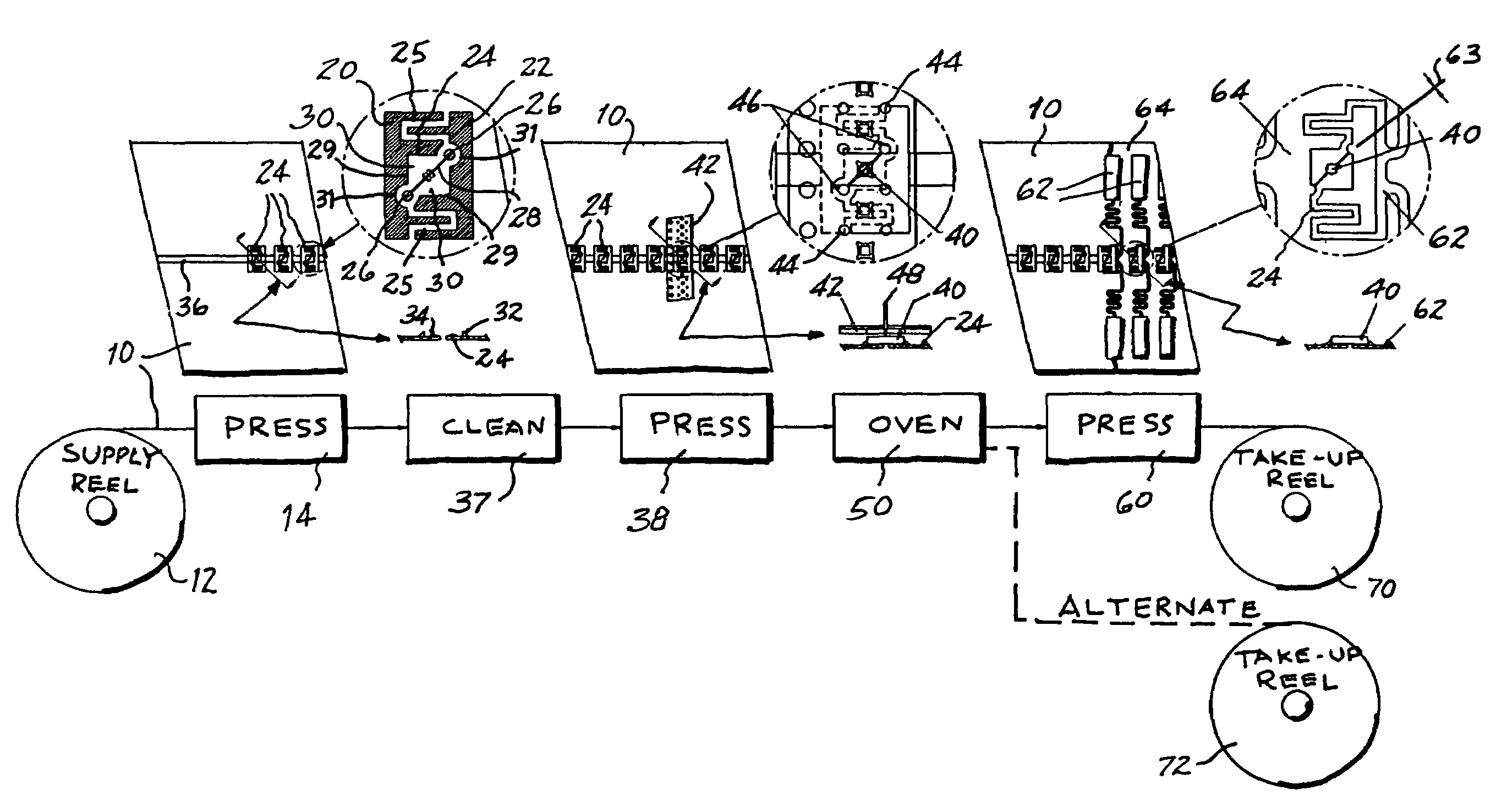

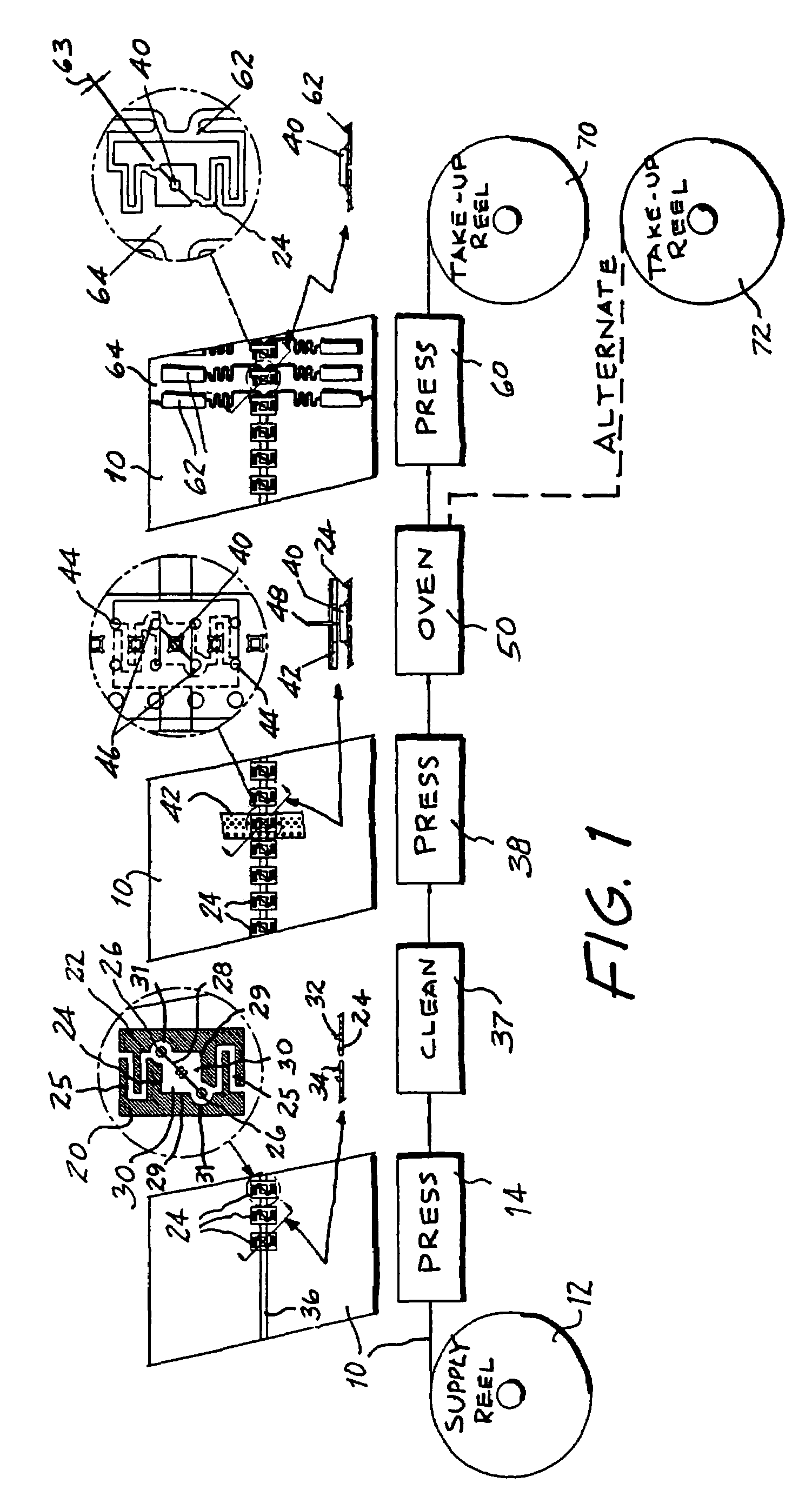

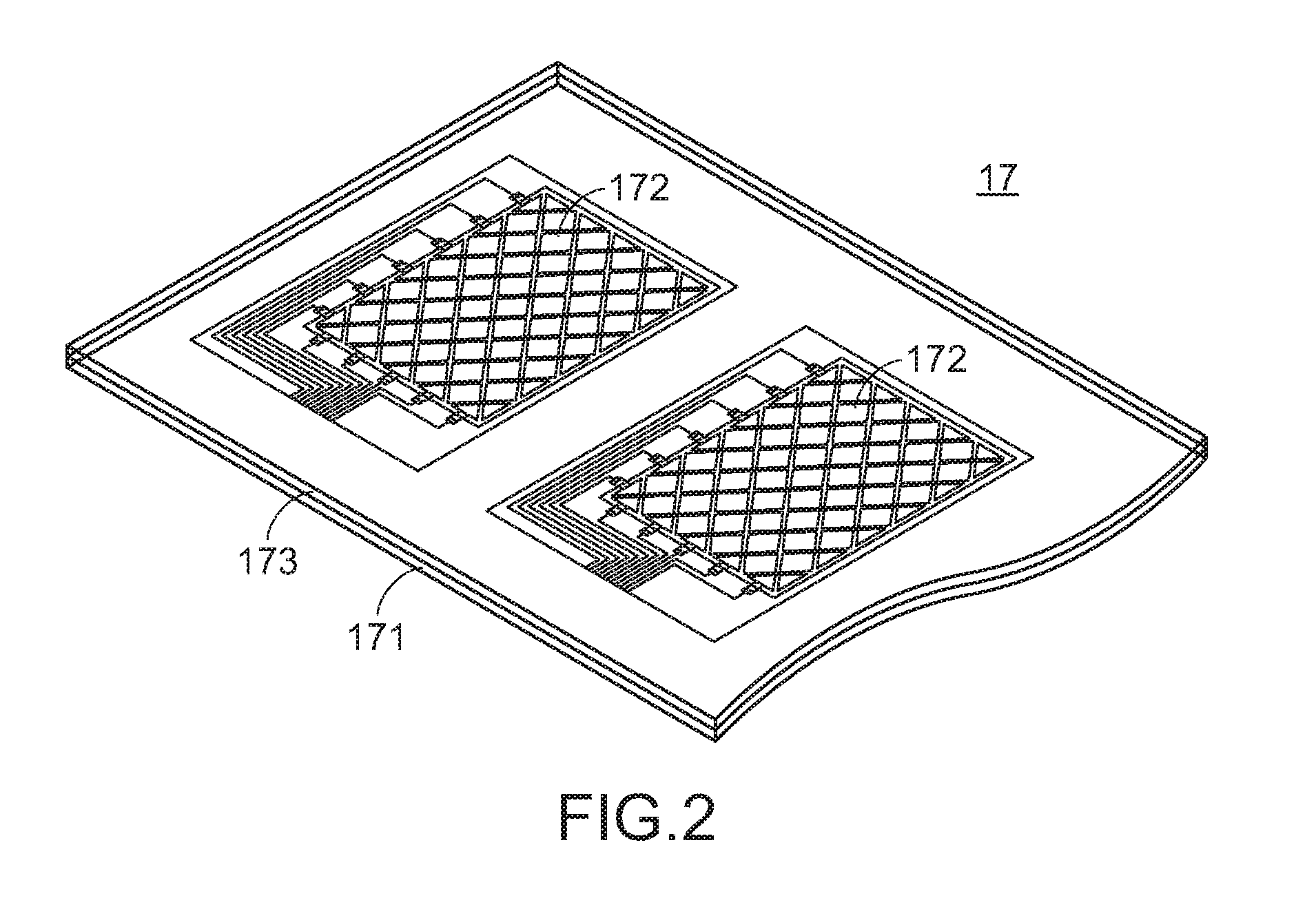

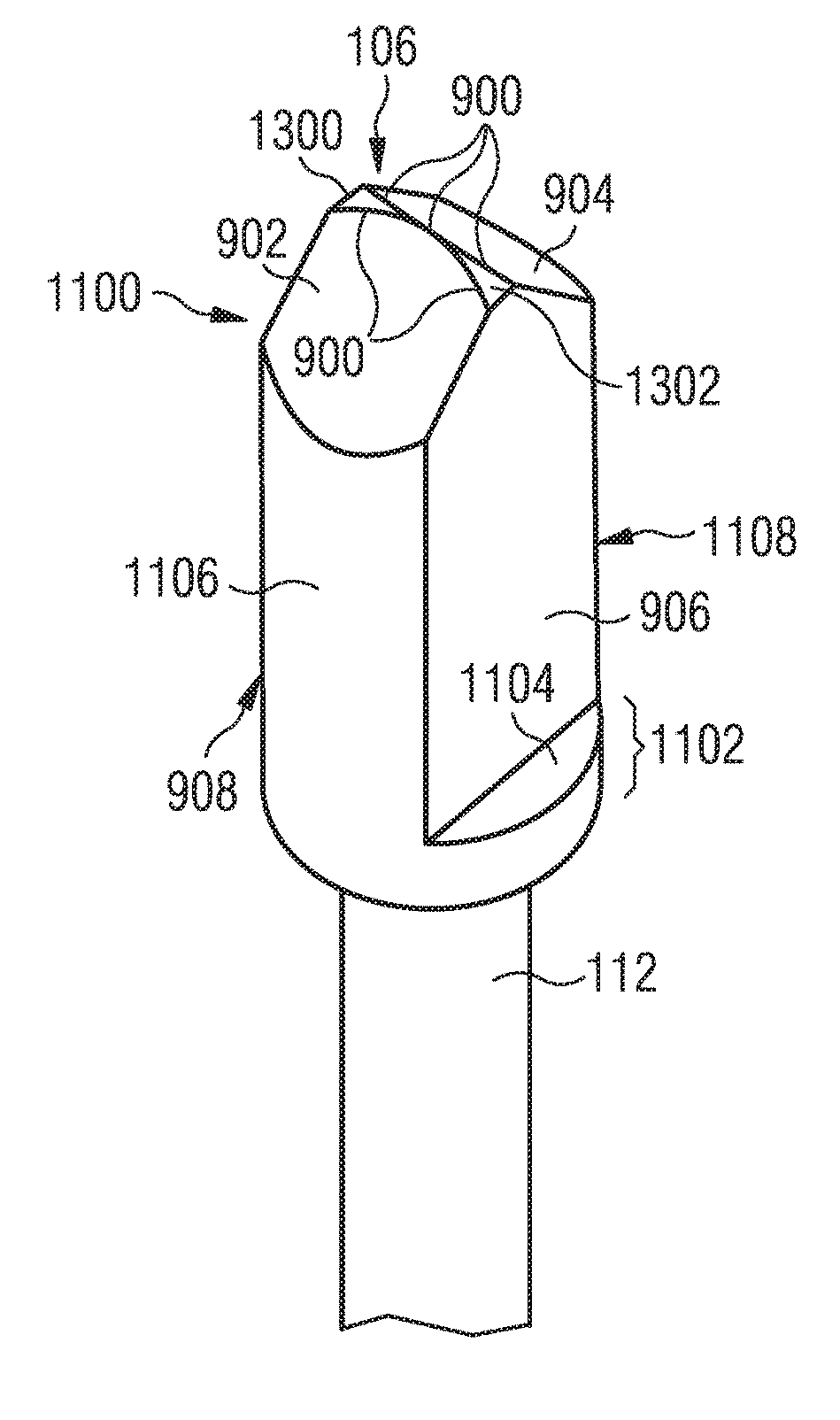

Manufacture of RFID tags and intermediate products therefor

InactiveUS7229018B2Easy to manufactureHighly effectiveLine/current collector detailsElectronic circuit testingCouplingEngineering

Owner:A K STAMPING

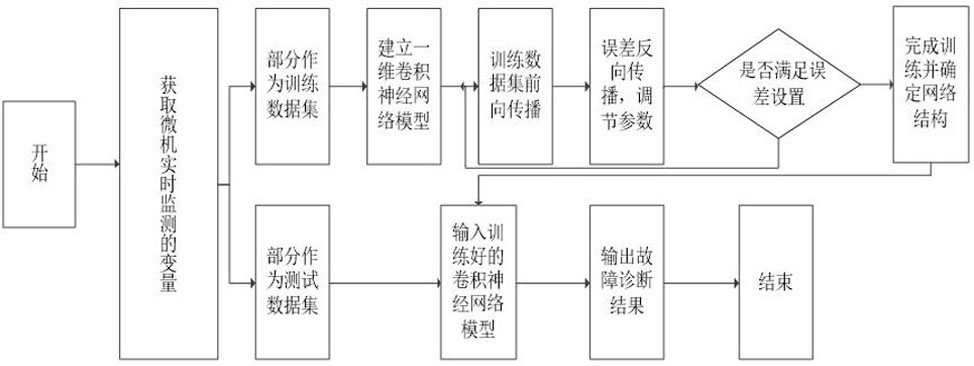

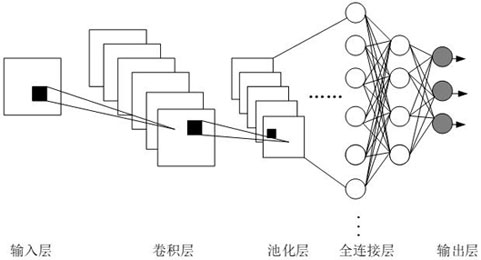

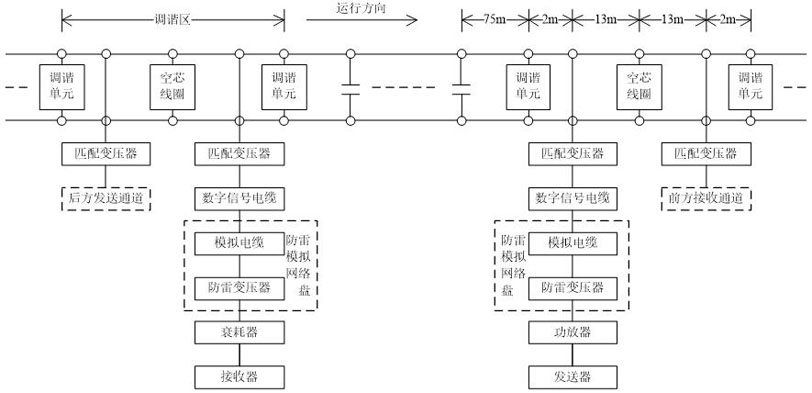

Track circuit fault automatic diagnosis method based on deep convolutional neural network

PendingCN111626416AImprove fault diagnosis efficiencyImprove accuracyElectronic circuit testingNeural architecturesData setAlgorithm

Owner:黑龙江瑞兴科技股份有限公司

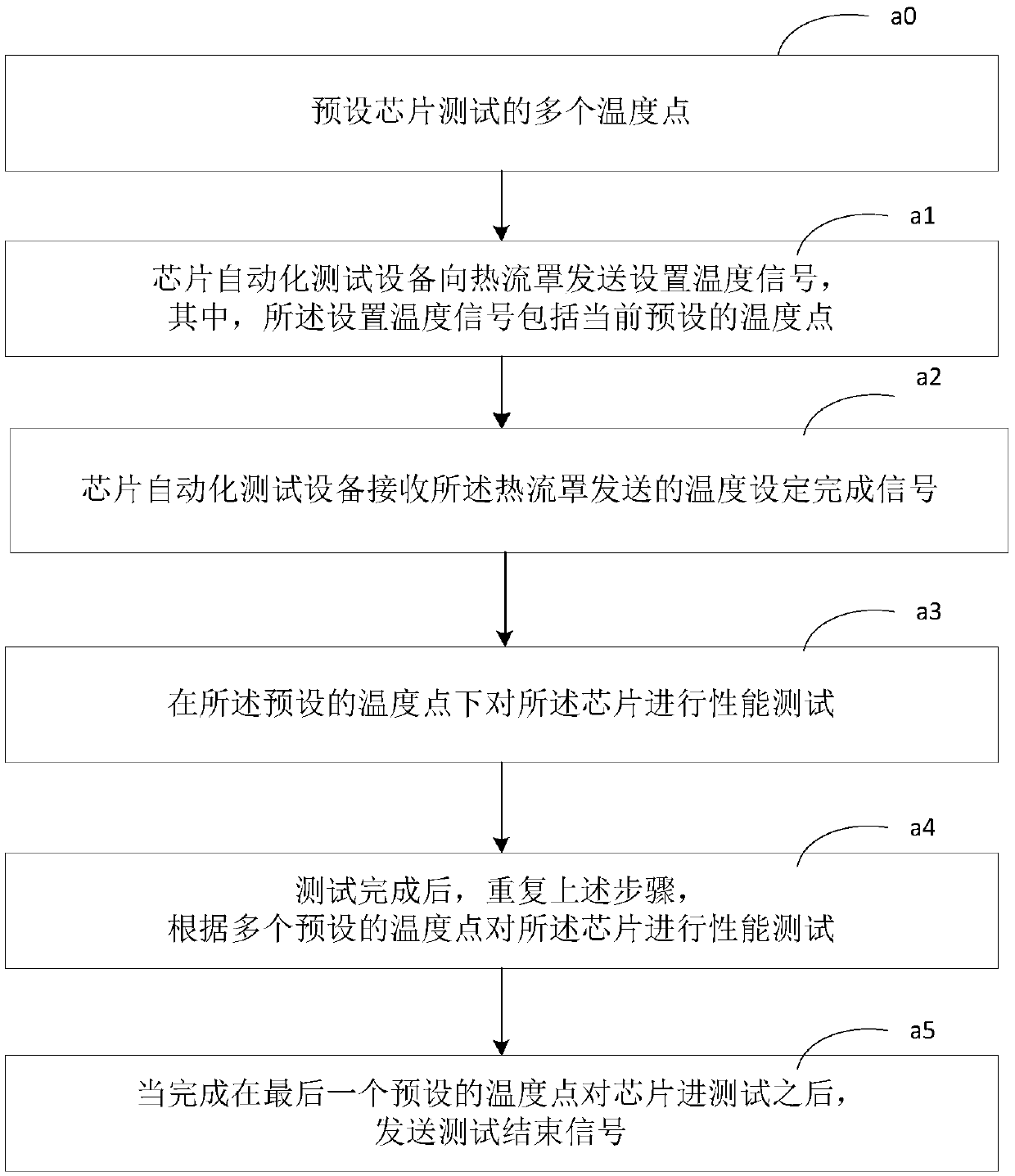

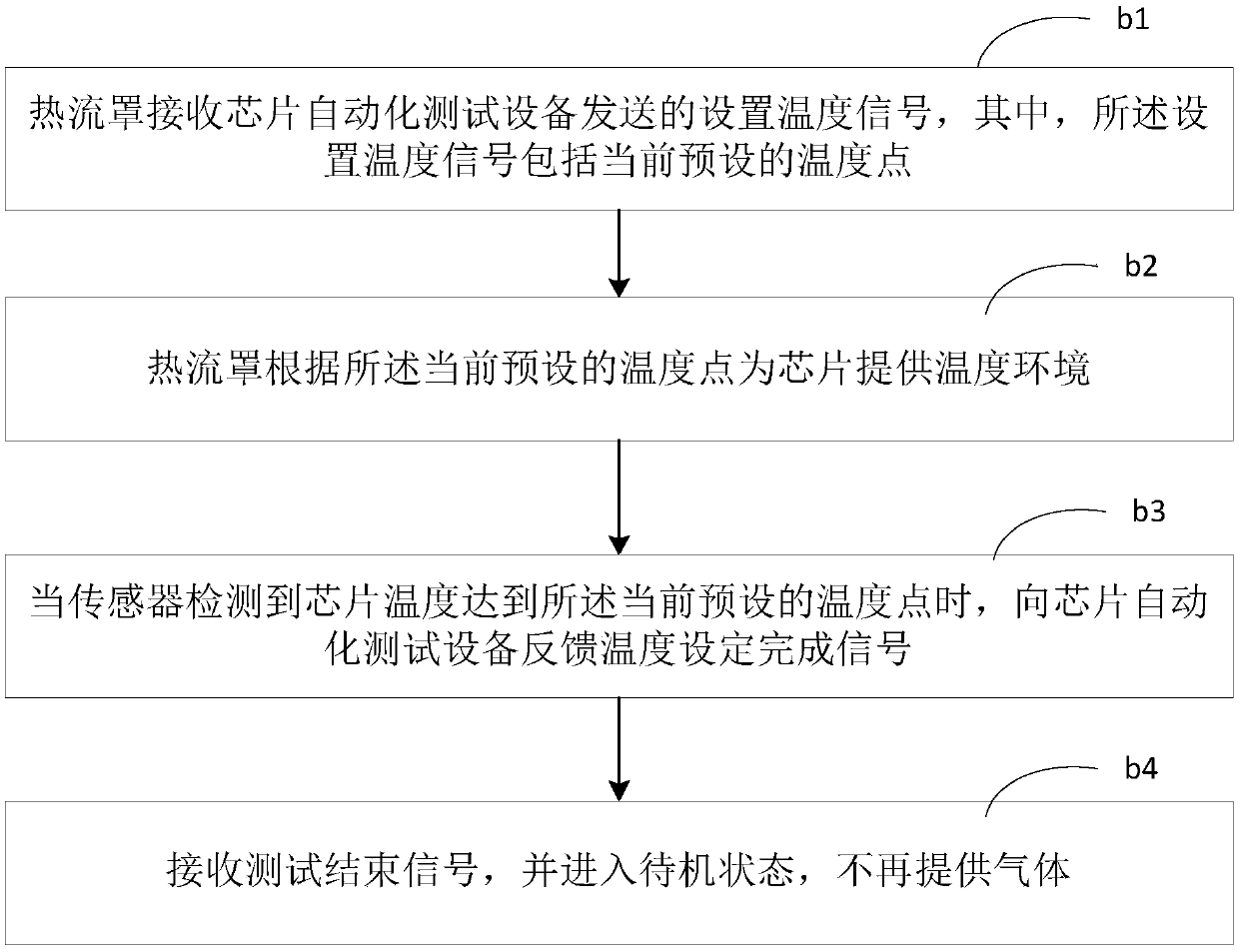

Method for testing chip parameters at different temperatures

Owner:BEIJING SMARTCHIP MICROELECTRONICS TECH COMPANY +1

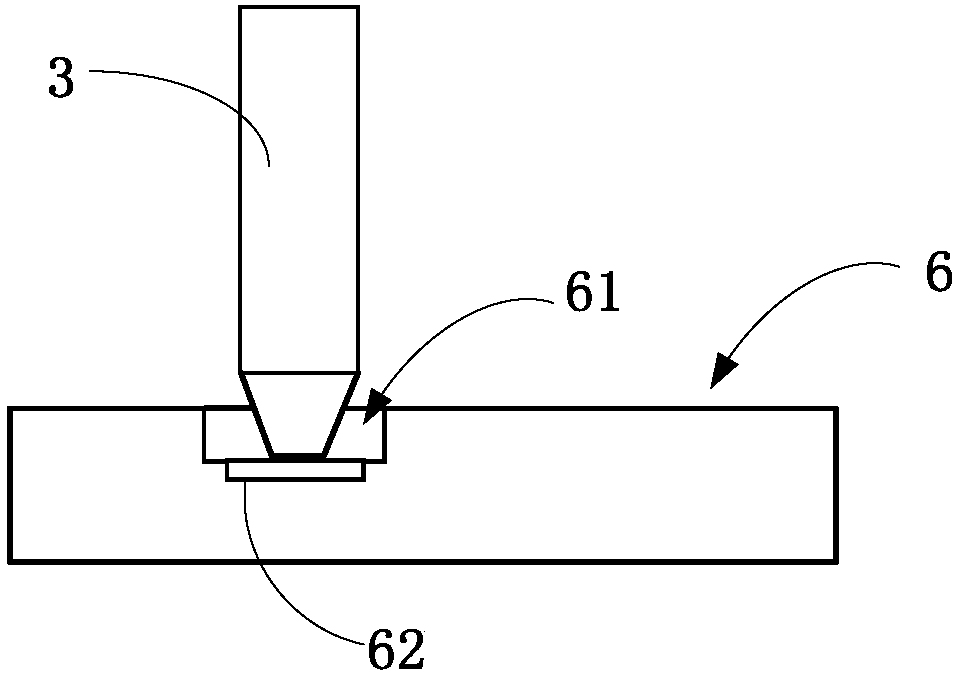

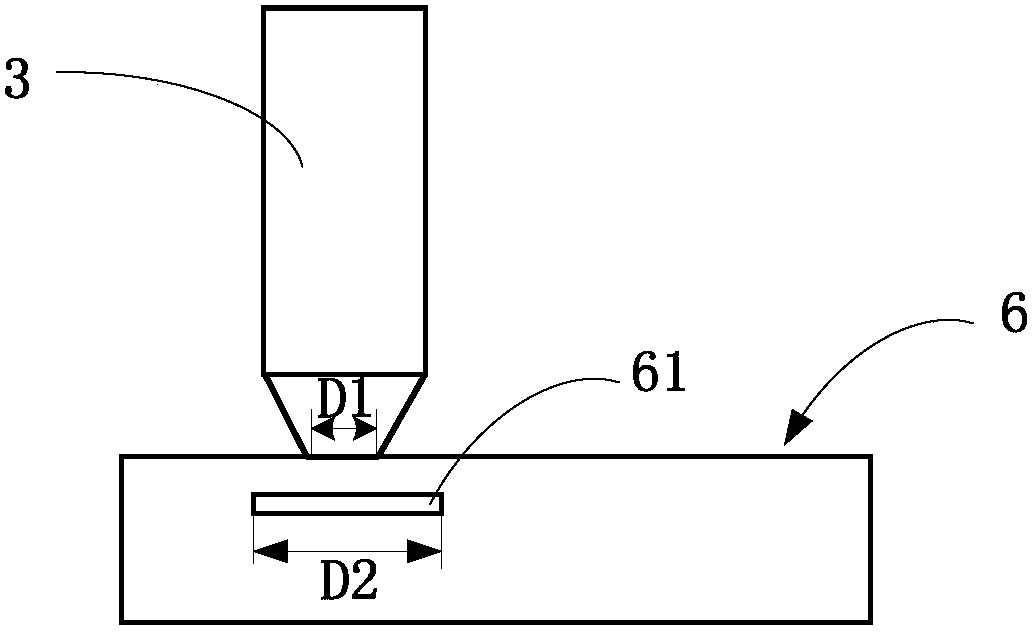

Test structure and method for monitoring probe mark offset by using same

ActiveCN106783804AReal-time monitoring of driftReduce mistakesSemiconductor/solid-state device testing/measurementElectronic circuit testingMetalIntegrated circuit

The invention relates to the technical field of integrated circuit testing, particularly to a test structure and a method for monitoring probe mark offset by using the same. According to the test structure disclosed by the invention, a novel test structure is introduced to conventional WAT (wafer acceptance test); the number N (N is greater than or equal to 4) of metal bond pads is consistent to the number of monitored probe clamping pins; an active device is put below each metal bond pad; gates, sources and drains of the N (N is greater than or equal to 4) active devices, and a substrate are connected in parallel to be connected to four different bond pads respectively; and by measuring saturation current of the active devices in different positions below the bond pads, the offset condition of the probe pins can be monitored in real time.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

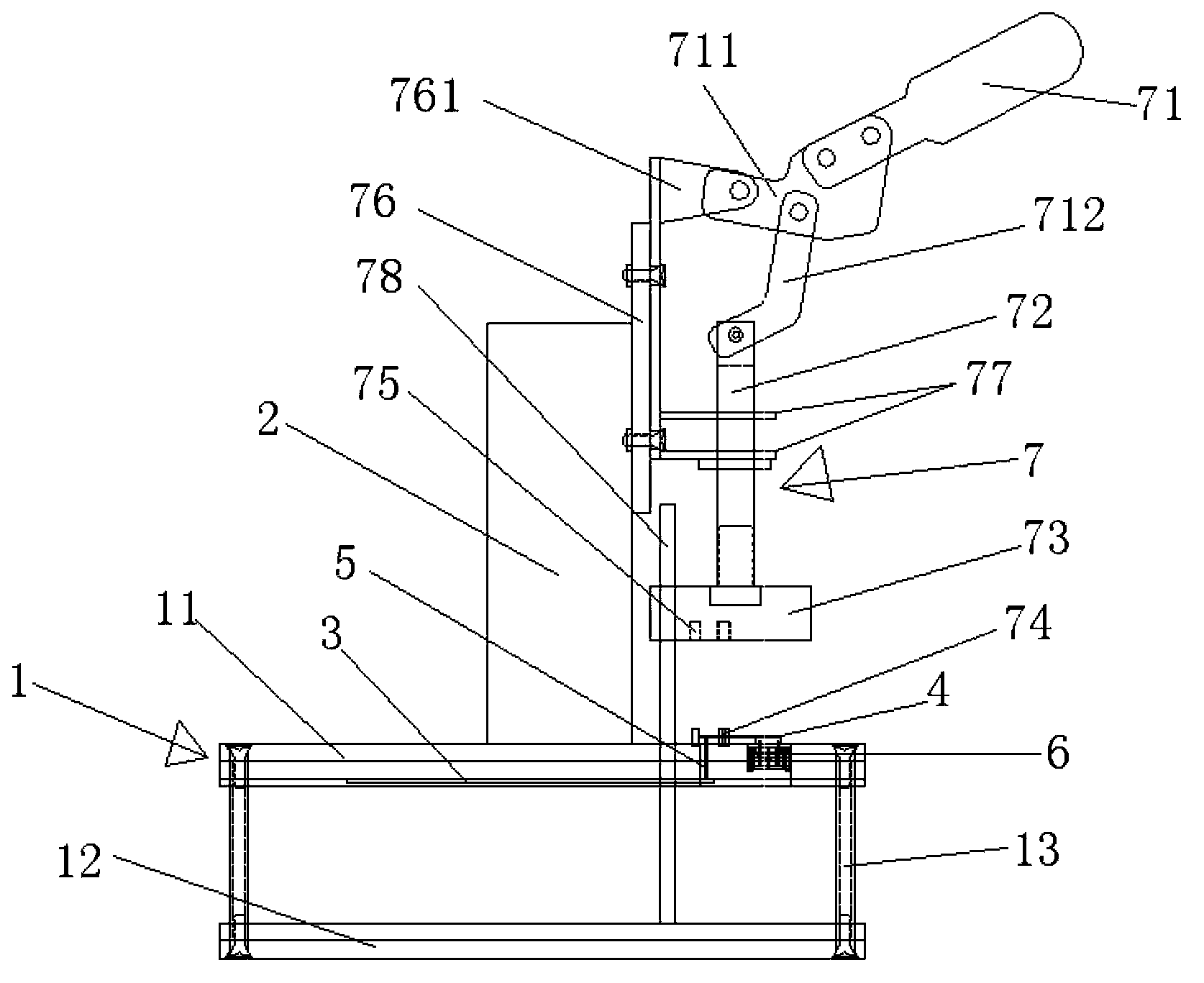

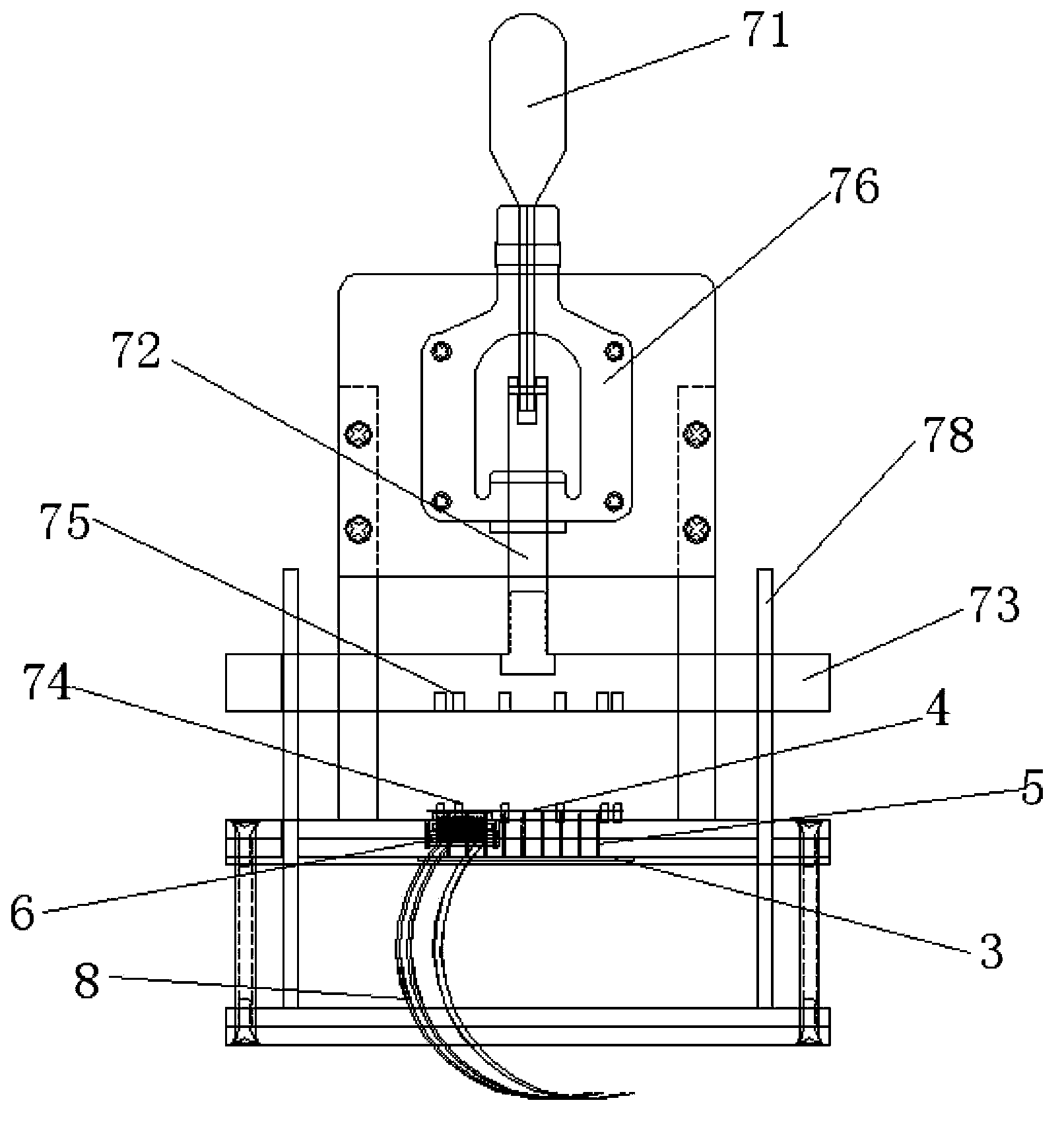

Functional tester with elastic connector

Owner:昆山意力电路世界有限公司

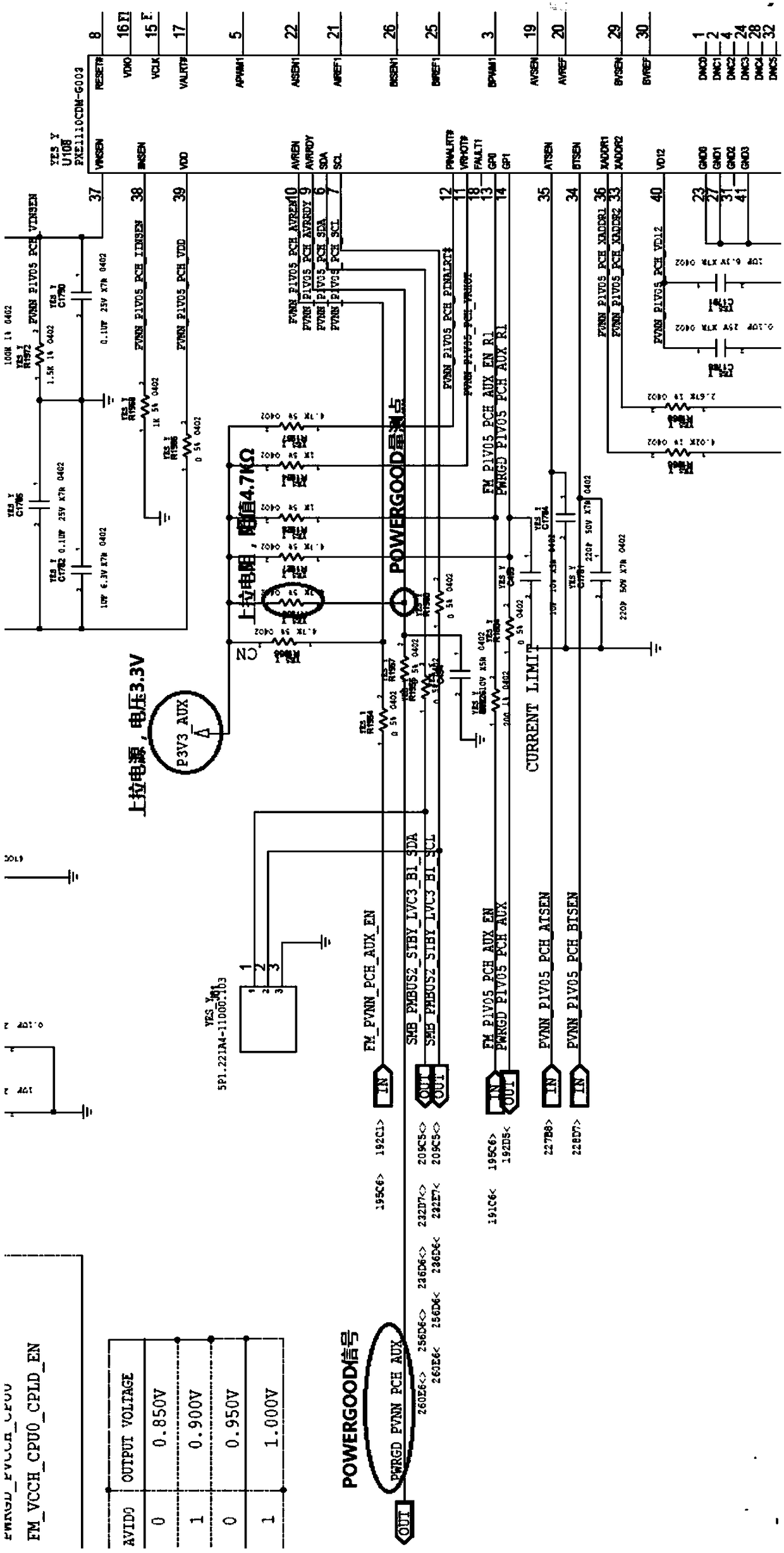

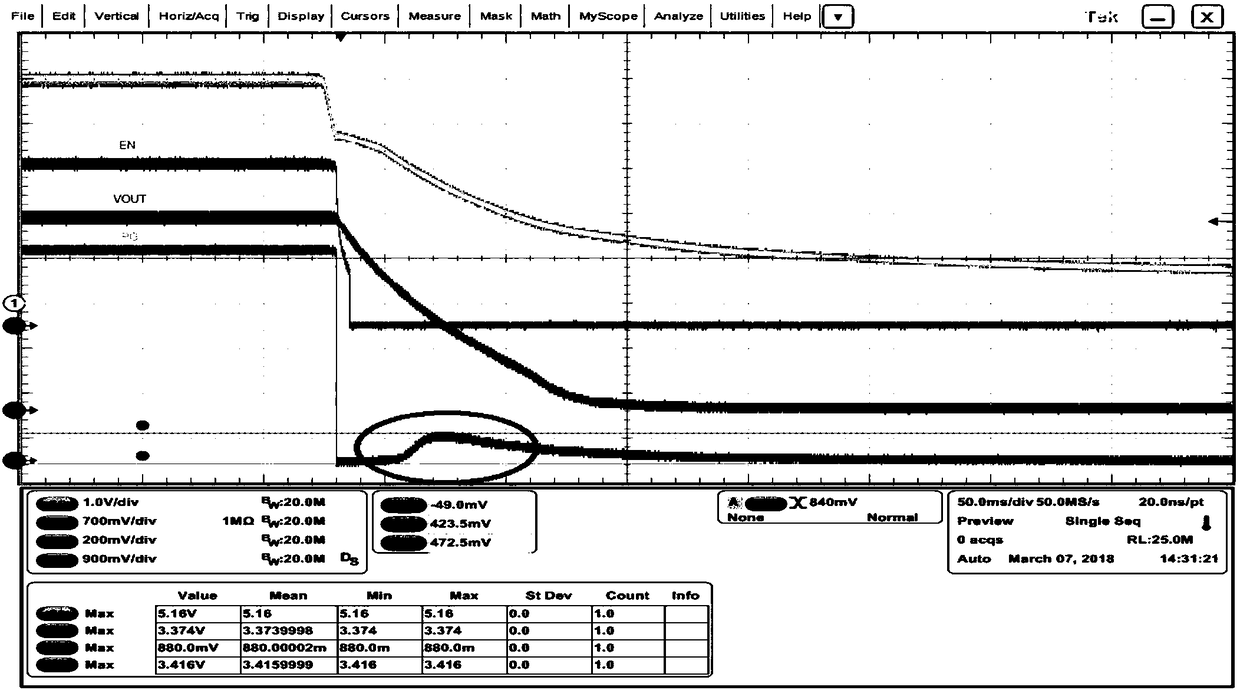

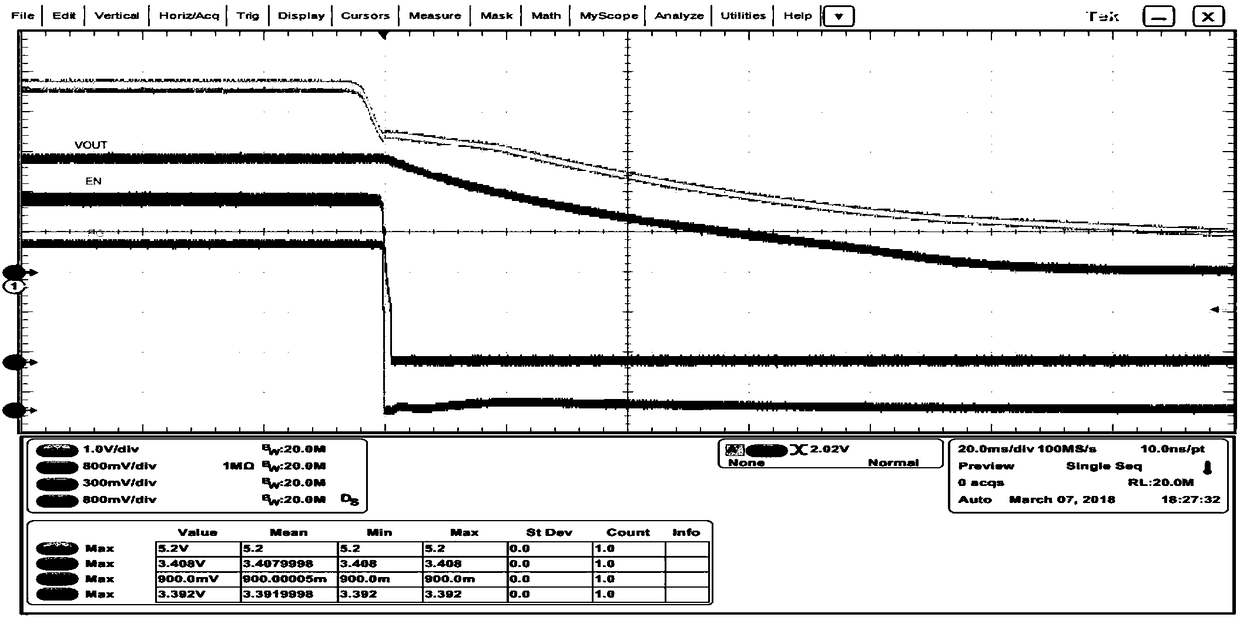

Method and system of solving non-monotonous POWERGOOD signals in VR power-failure sequential test

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

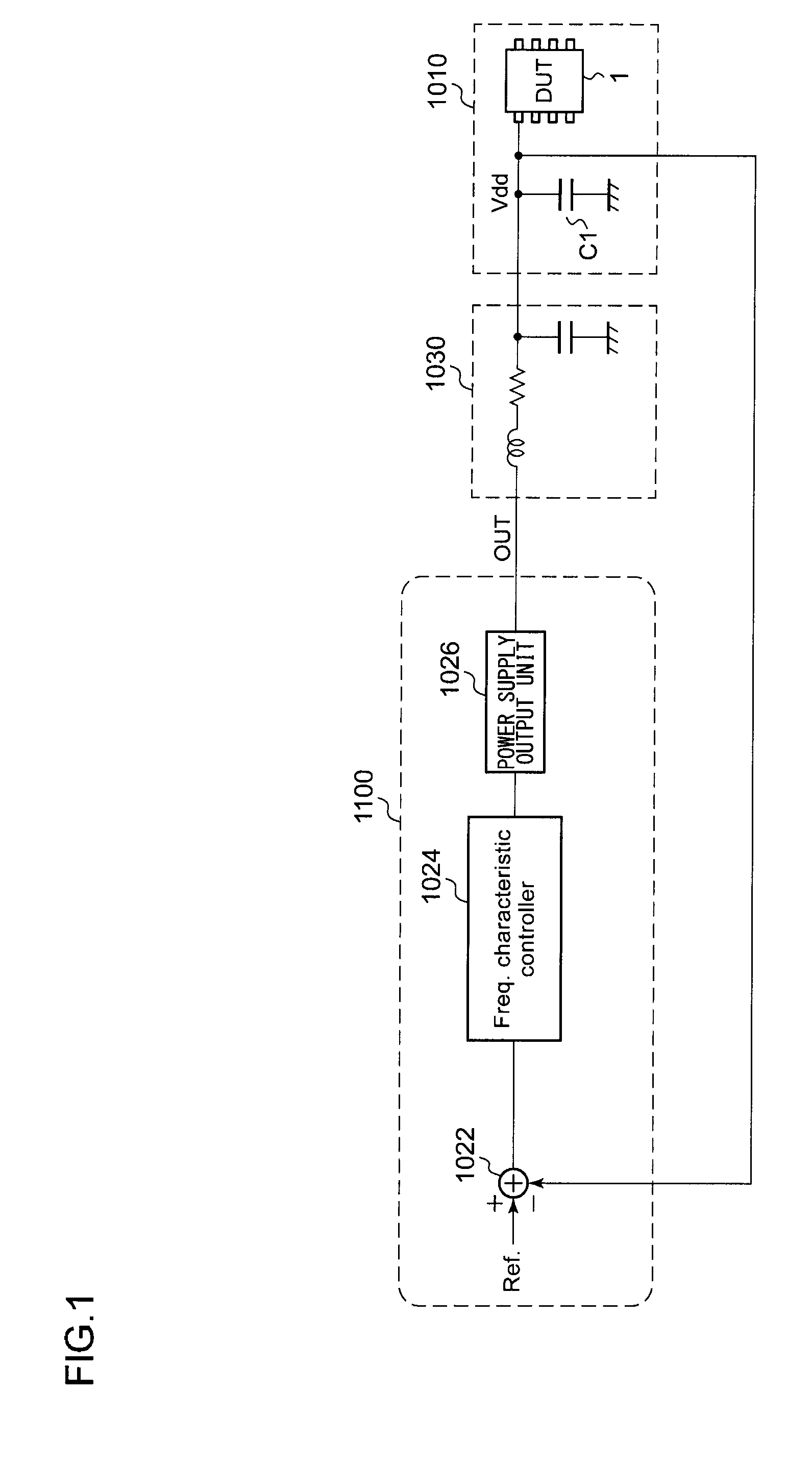

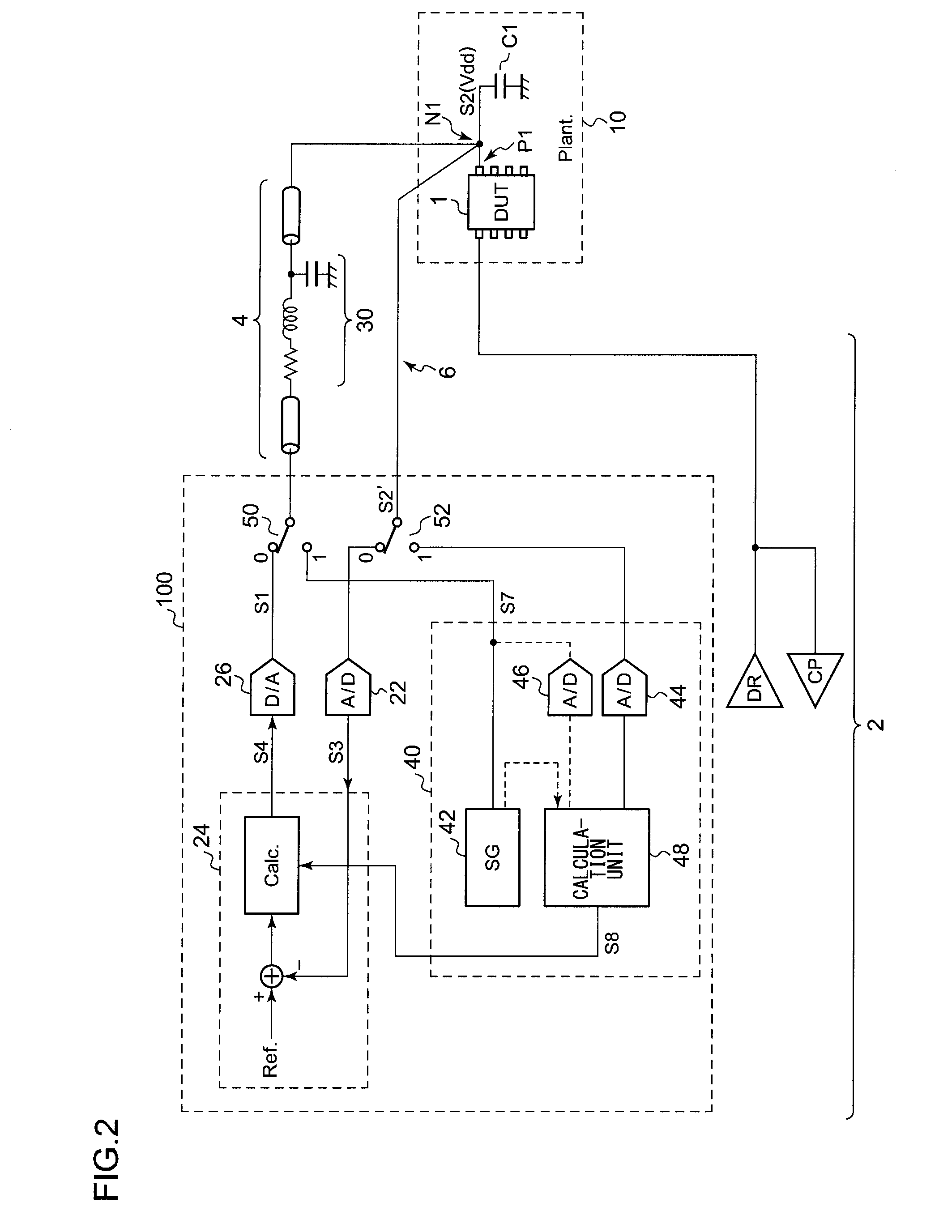

Power supply apparatus for test apparatus

ActiveUS20120218004A1Analogue/digital conversionMultiple input and output pulse circuitsDigital signal processingA d converter

Owner:ADVANTEST CORP

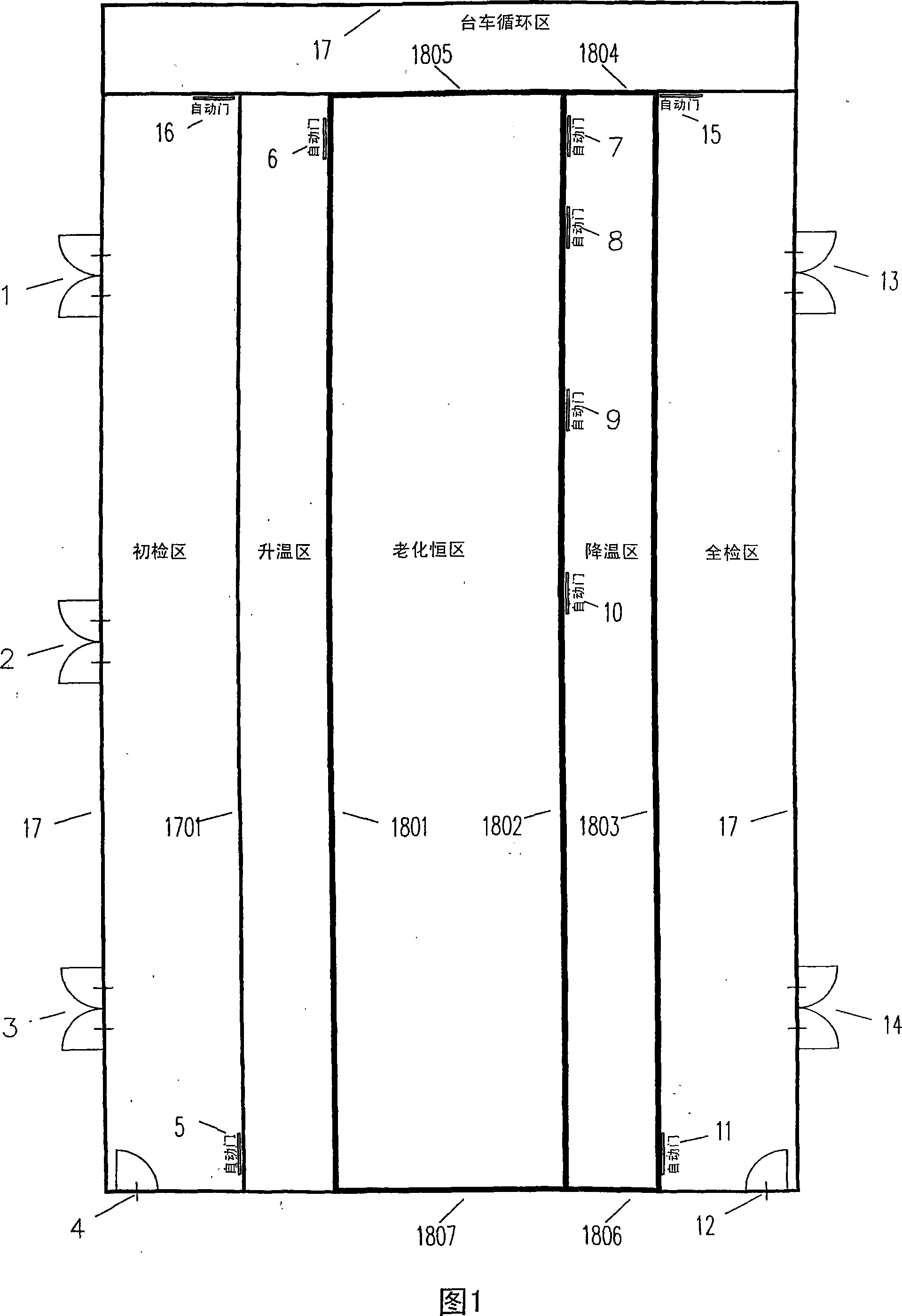

Aging room used for the last assembling process of LCD screen

InactiveCN101238406ASemiconductor/solid-state device testing/measurementElectronic circuit testingEnergy lossAging test

Owner:萧富壬

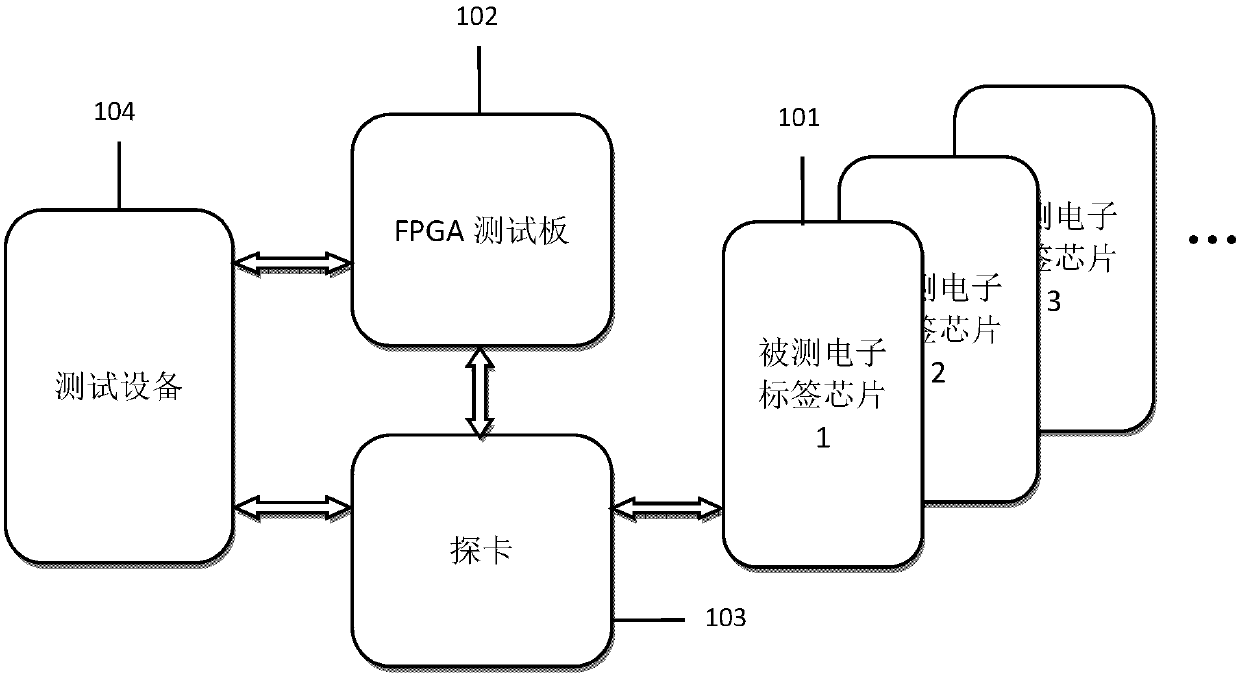

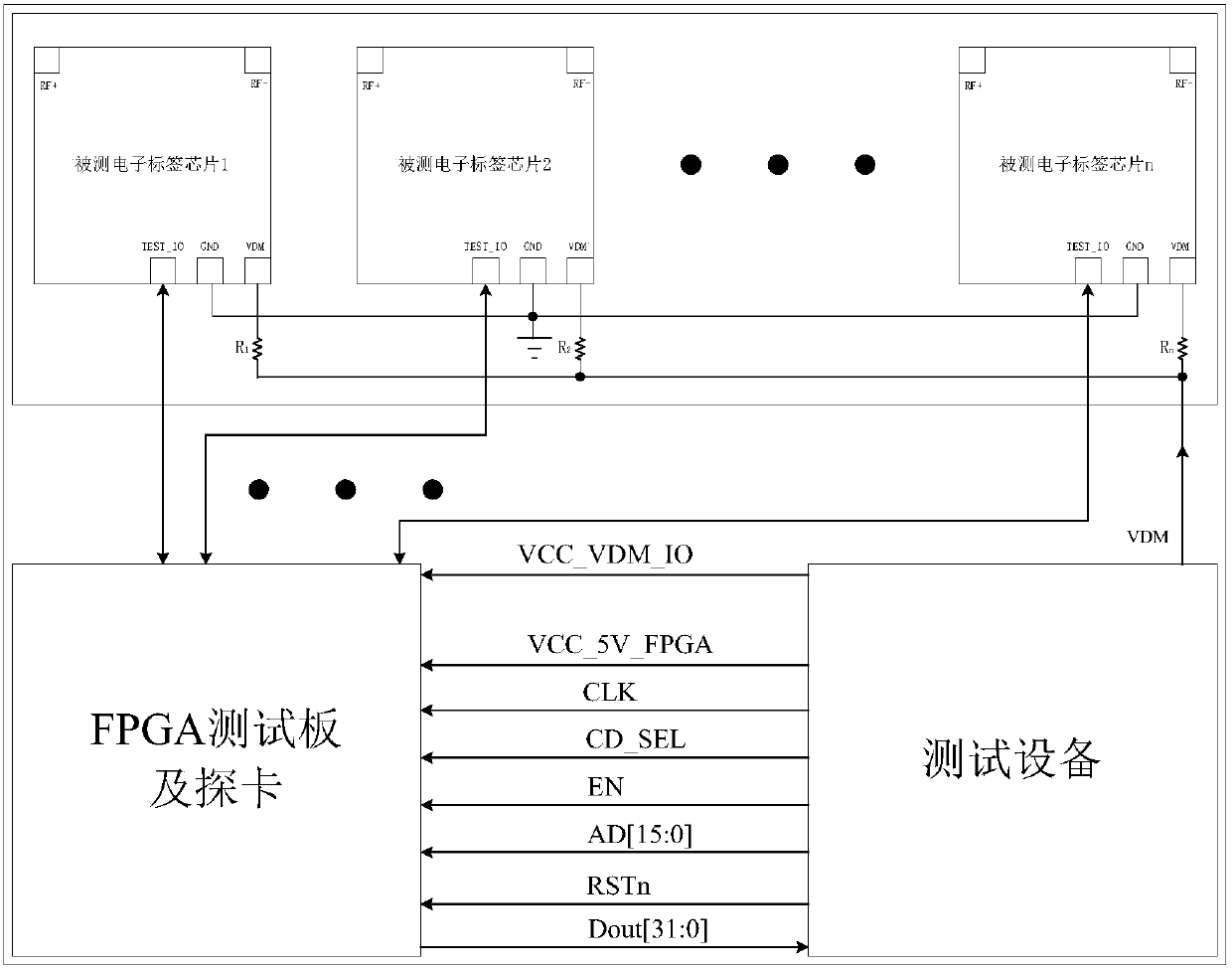

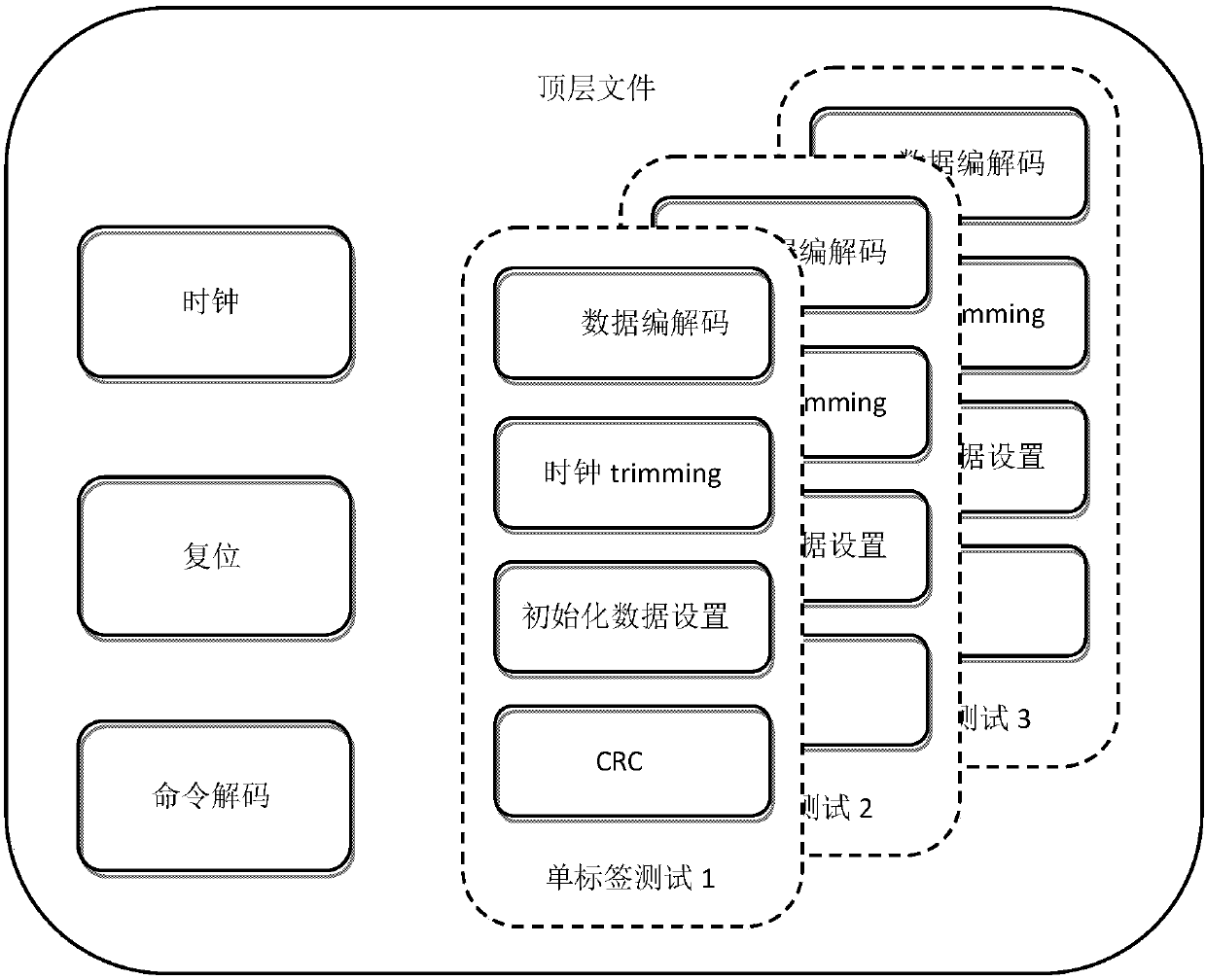

Radio frequency tag testing device based on FPGA

The invention provides a radio frequency tag testing device based on an FPGA, and the device comprises an FPGA test board and a probe card. An electronic tag chip is used for receiving a test commandtransmitted by the FPGA test board, executing the testing operation after decoding, and outputting a testing state after testing so that the FPGA test board carries out the sampling. The FPGA test board receives the test command transmitted by test equipment, completes the command decoding and data coding and transmits the data to the electronic tag chip, and also receives the testing state afterthe testing of the electronic tag chip, and transmits the testing state to the test equipment. The probe card is an electric contact interface of a tested electronic tag chip and the test equipment. The test equipment transmits the test command and data to the FPGA test boar, and determines whether the function of the electronic tag chip is correct or not according to the output testing state of the FPGA test board. The invention also provides a radio frequency tag testing method based on the FPGA.

Owner:华大恒芯科技有限公司

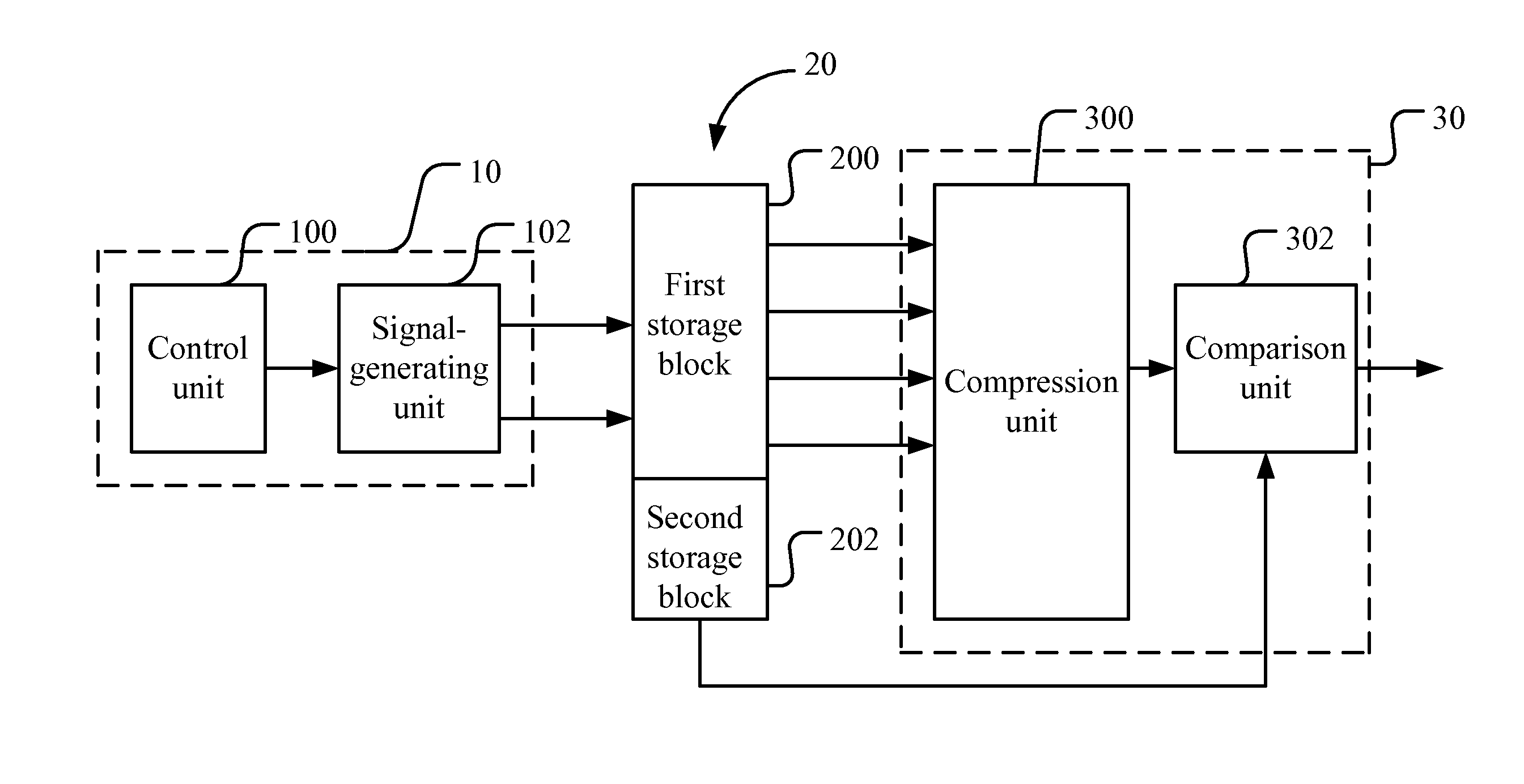

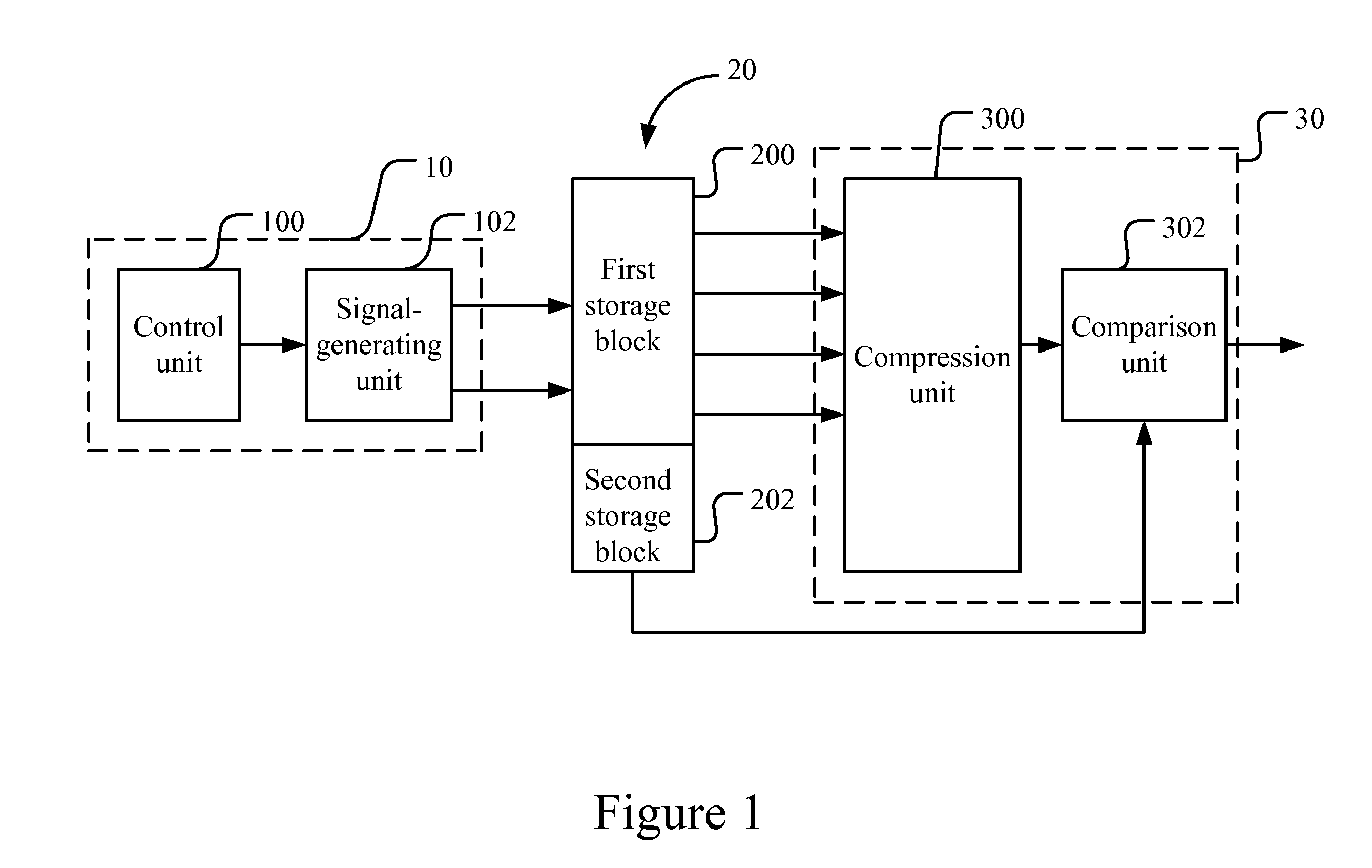

Memory with Self-Test Function and Method for Testing the Same

ActiveUS20110179323A1Low costSave hardware resourcesElectronic circuit testingFunctional testingStorage cellSelf test

Owner:REALTEK SEMICON CORP

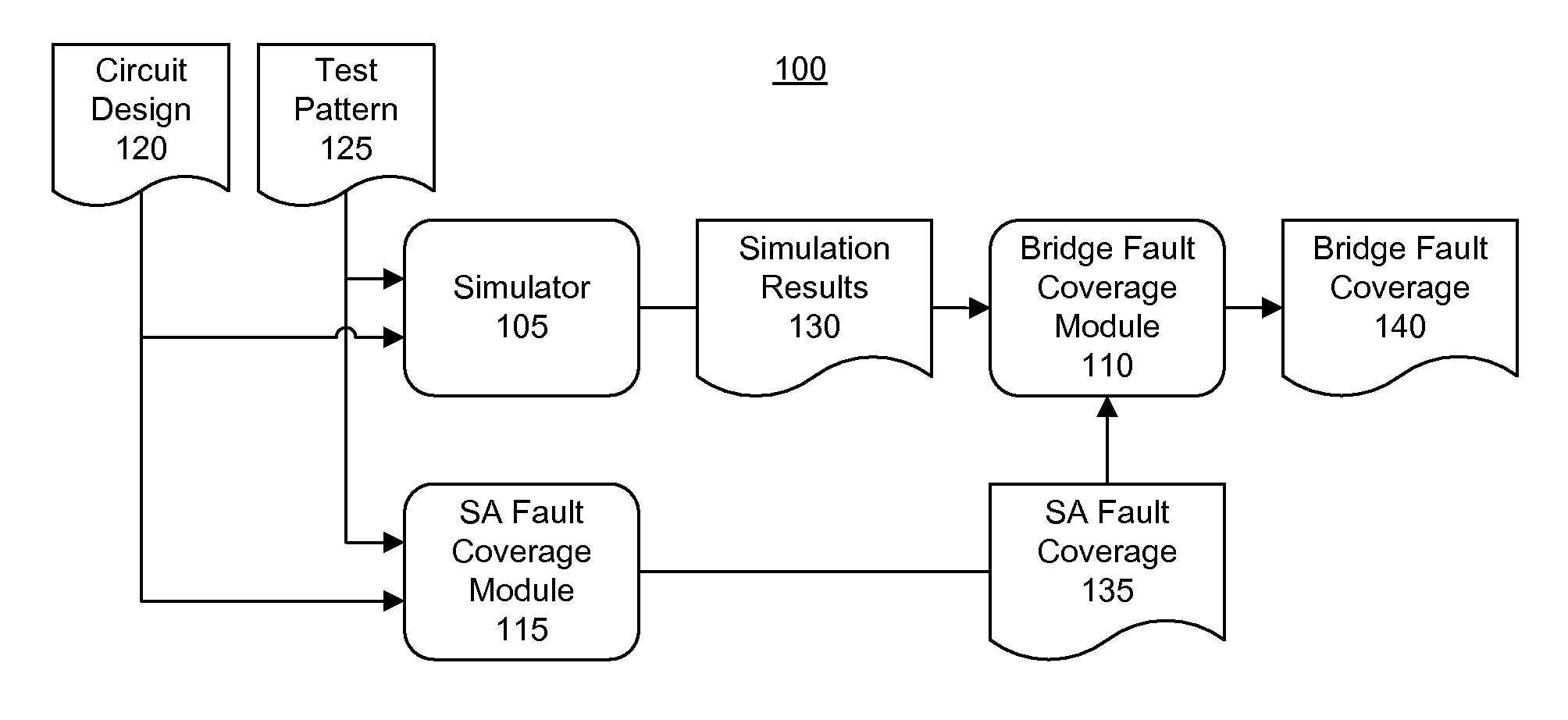

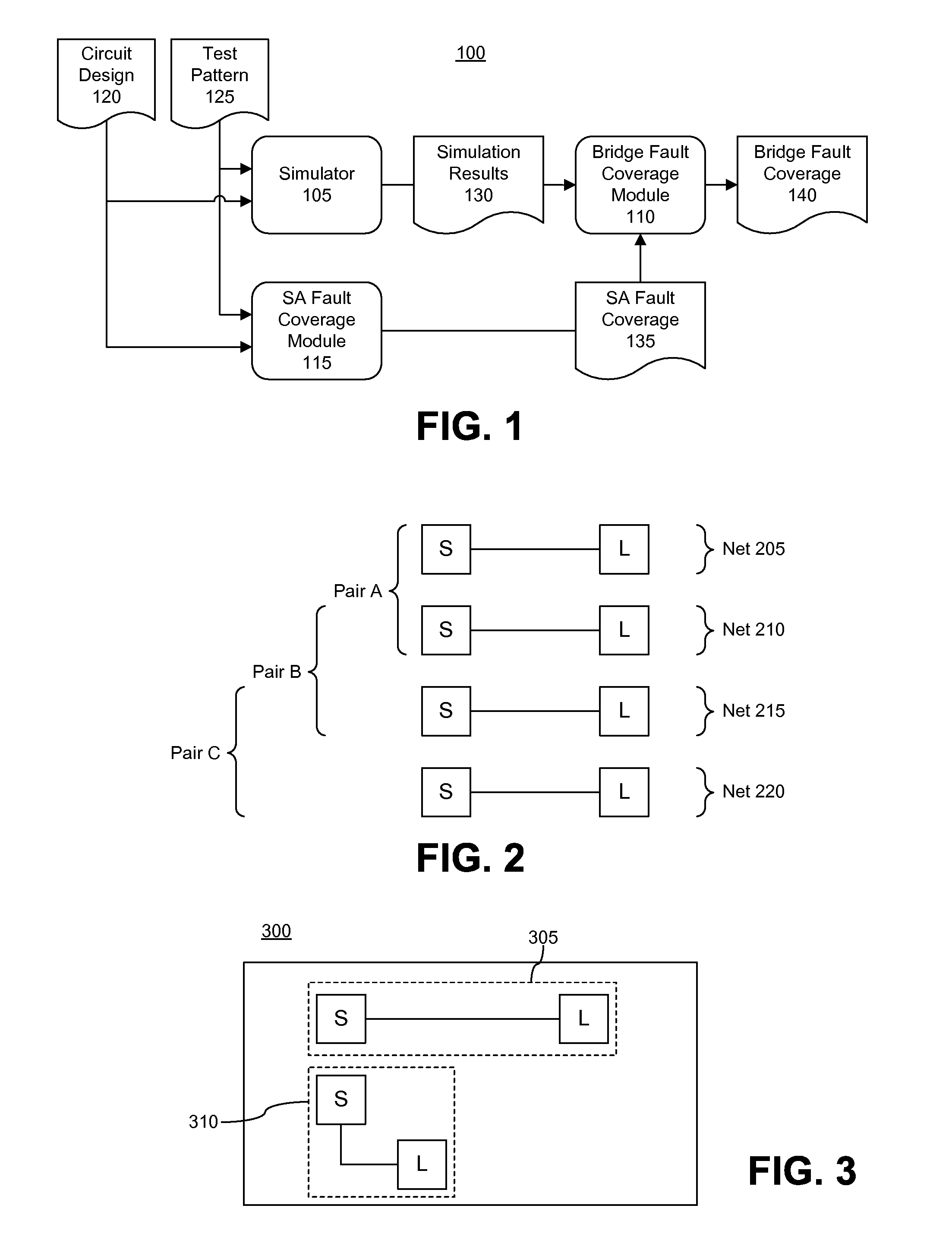

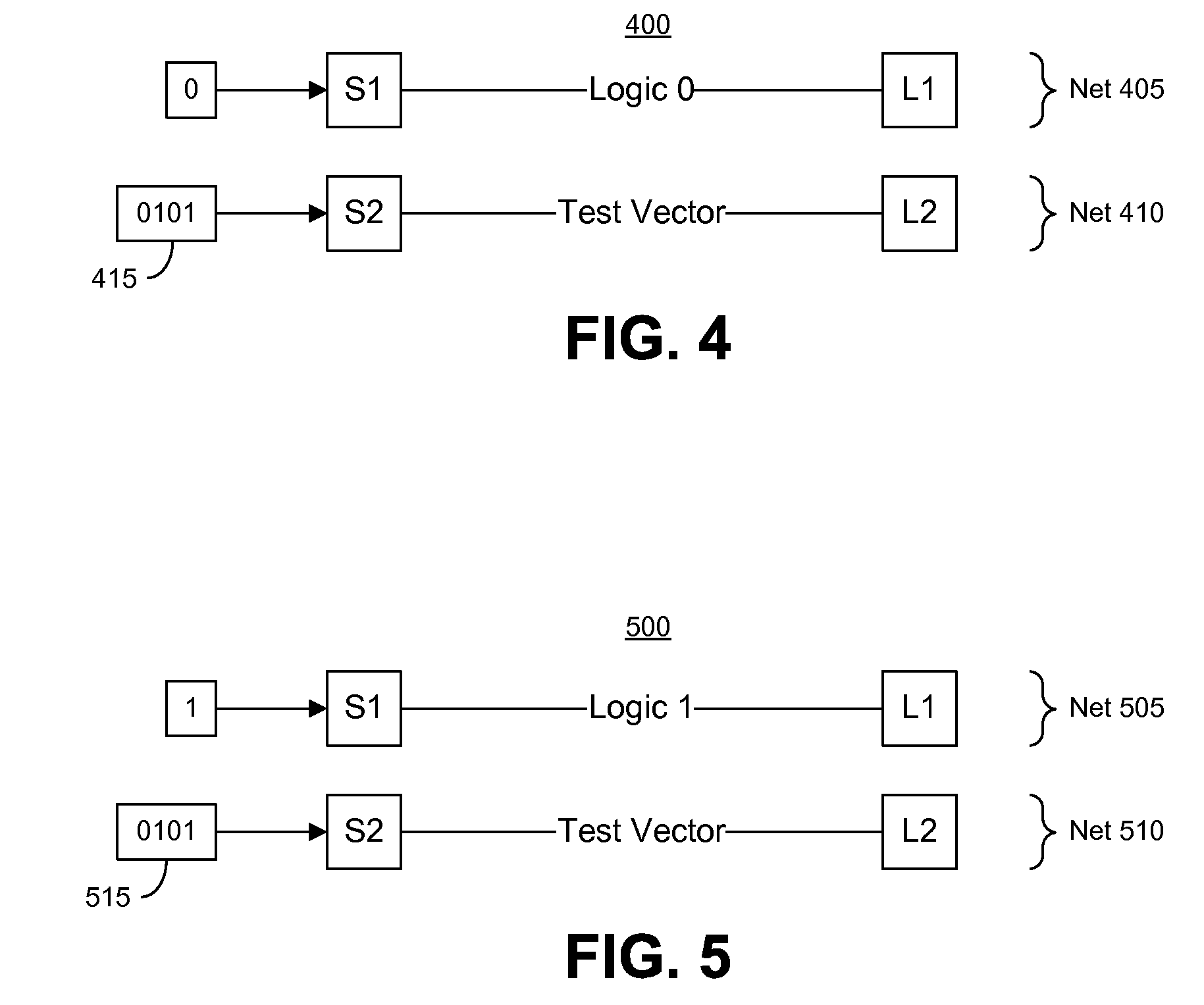

Measuring bridge-fault coverage for test patterns within integrated circuits

InactiveUS8001438B1Resistance/reactance/impedenceElectronic circuit testingProgrammable logic deviceBridging fault

Owner:XILINX INC

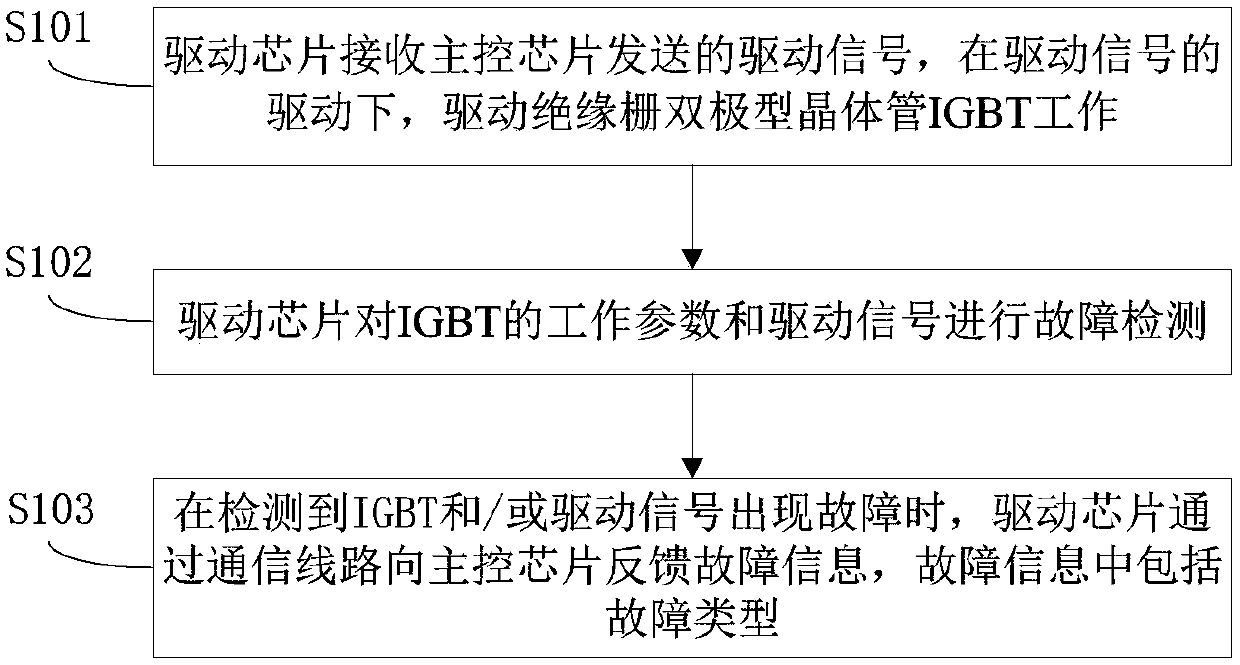

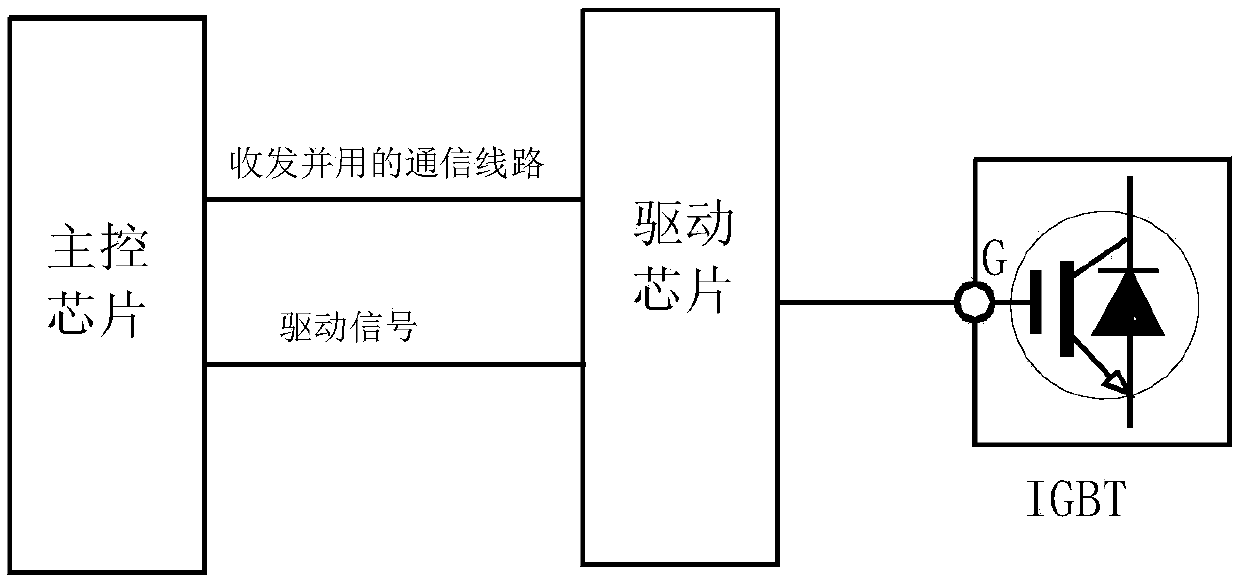

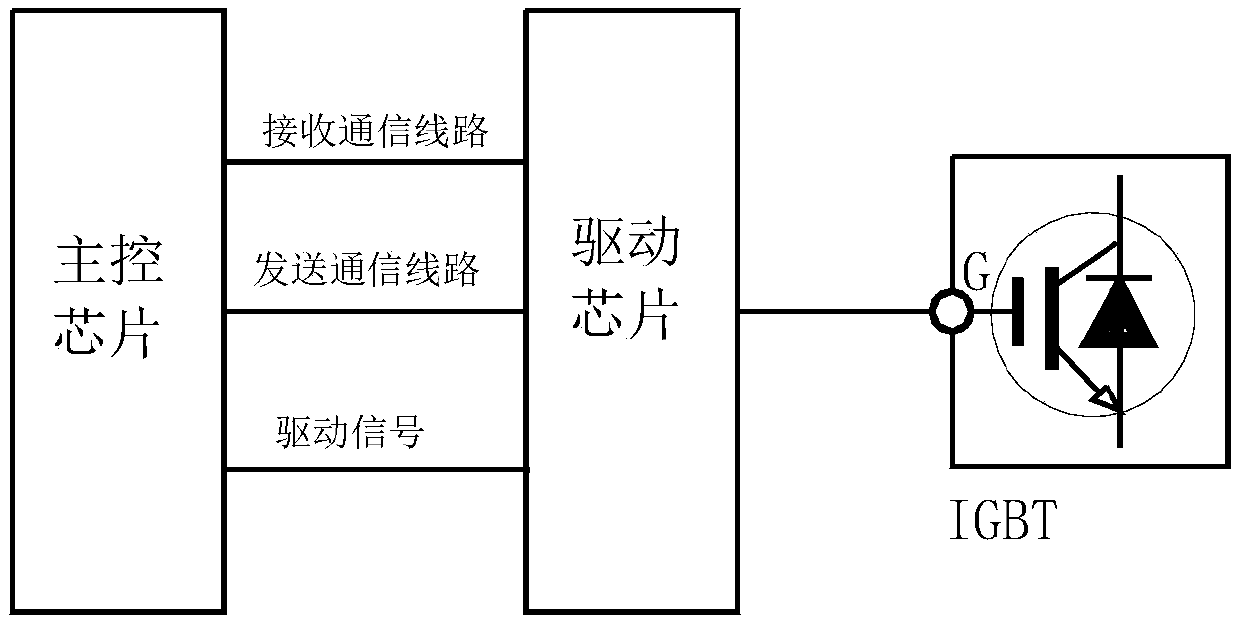

Driving chip fault detection method, driving chip and main control chip

Owner:FOSHAN SHUNDE MIDEA ELECTRICAL HEATING APPLIANCES MFG CO LTD

Touch panel producing method

InactiveUS20150059161A1Electronic circuit testingWave amplification devicesEngineeringControl circuit

Owner:PRIMAX ELECTRONICS LTD

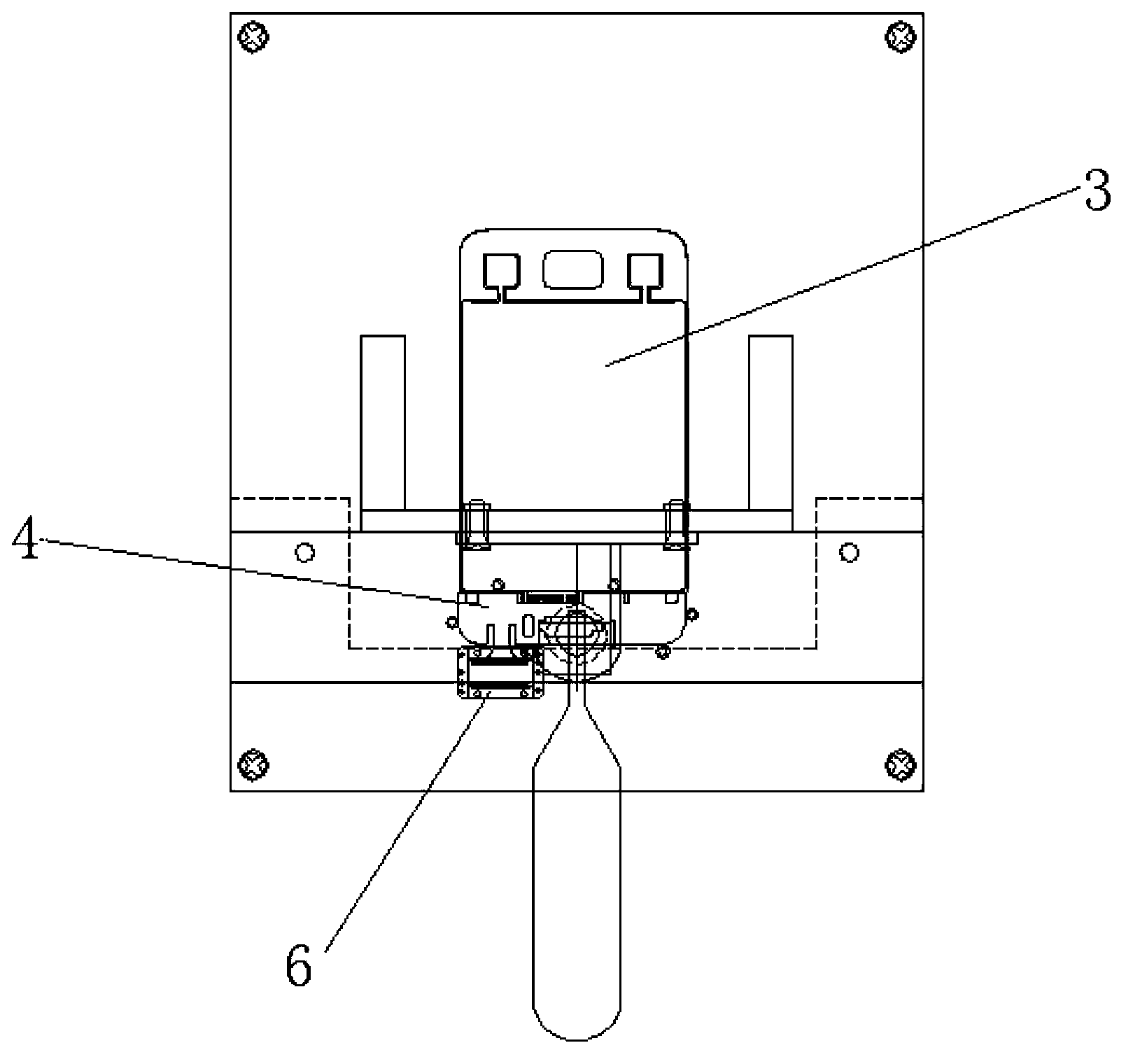

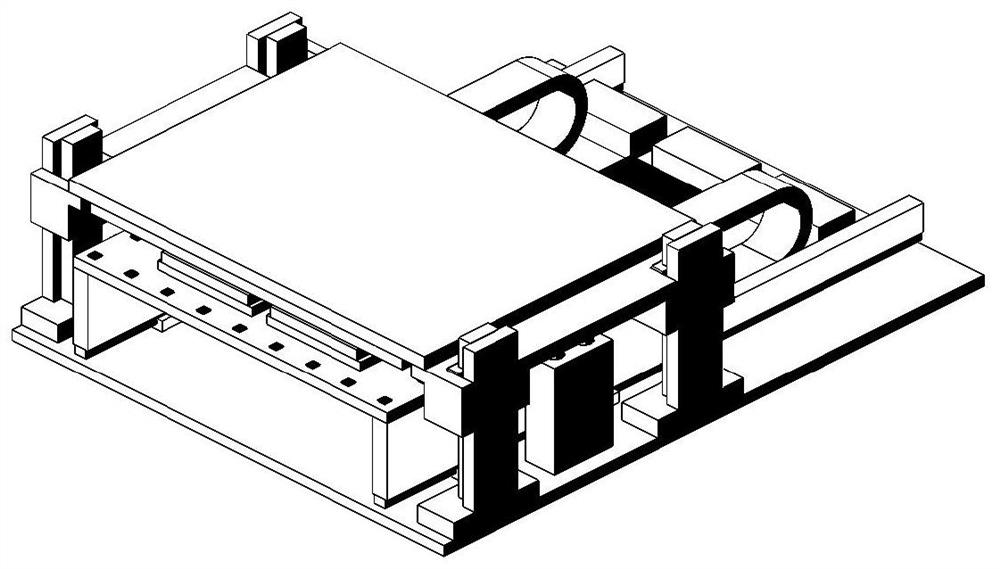

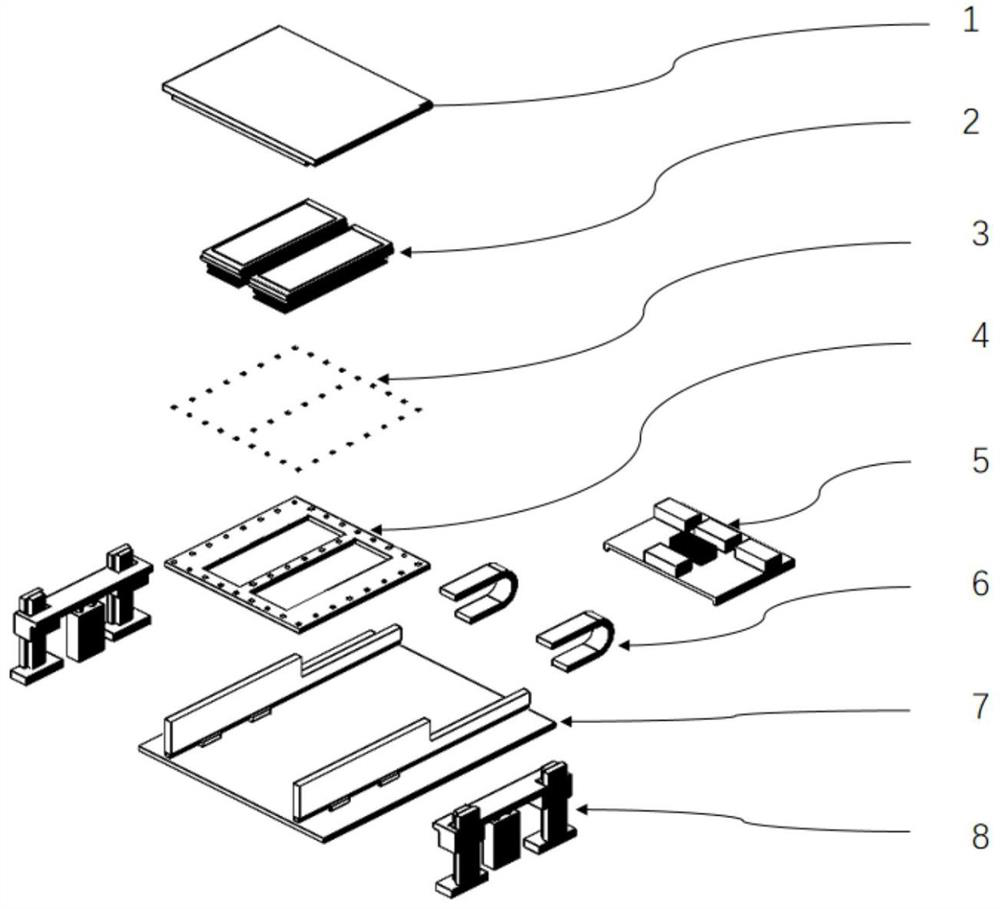

Elastic deformation adjusting device for frame plate in FCT tester

PendingCN111948524AElectronic circuit testingElectrical/magnetic solid deformation measurementPhysicsStrain gauge

Owner:P&R MEASUREMENT INC

Semiconductor memory device with improved saving rate for defective chips

Owner:MITSUBISHI ELECTRIC CORP

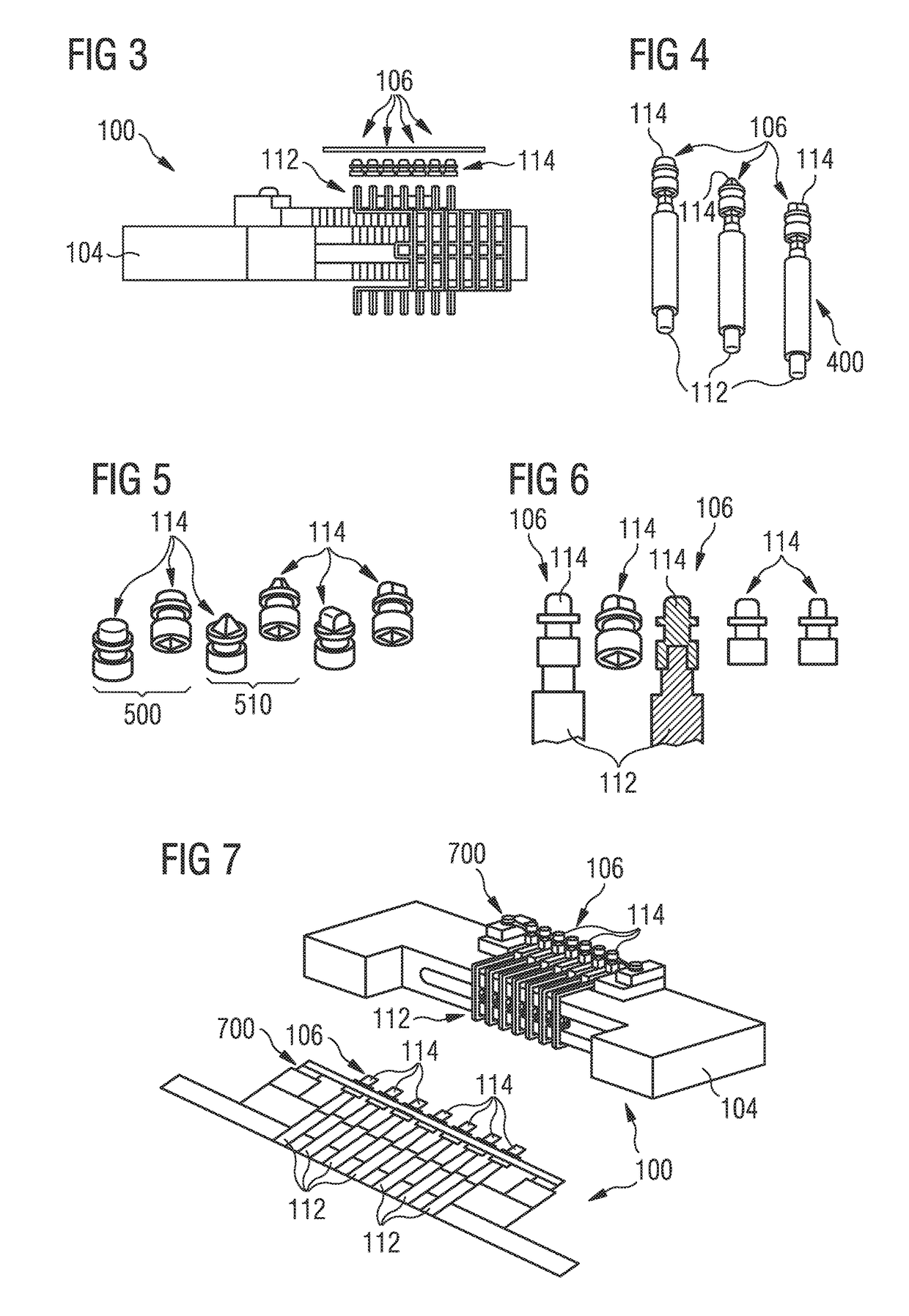

Test Pin Configuration for Test Device for Testing Devices Under Test

InactiveUS20170176494A1Smooth connectionImprove test reliabilityElectronic circuit testingElectrical measurement instrument detailsTest fixtureTest facility

Owner:INFINEON TECH AG

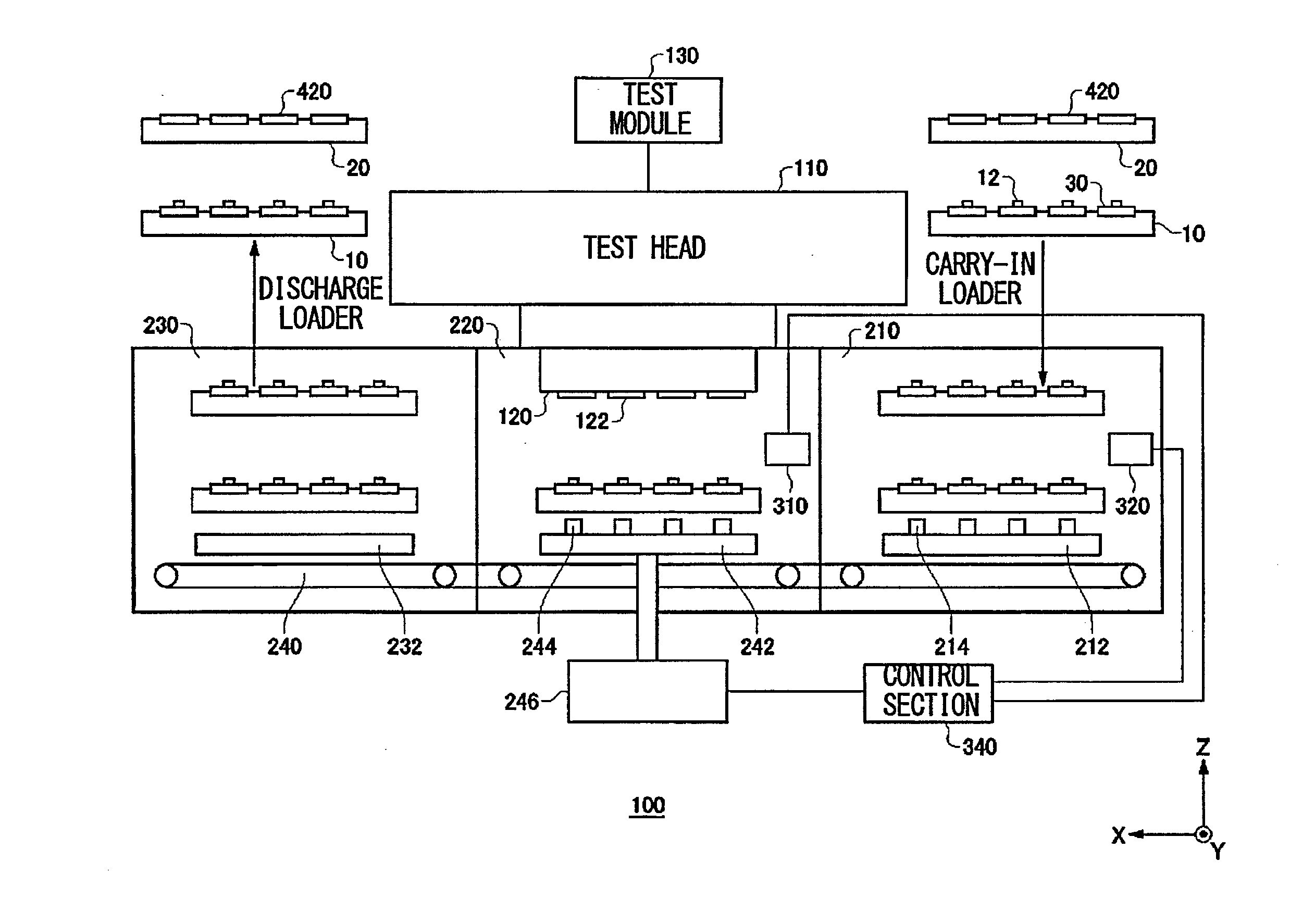

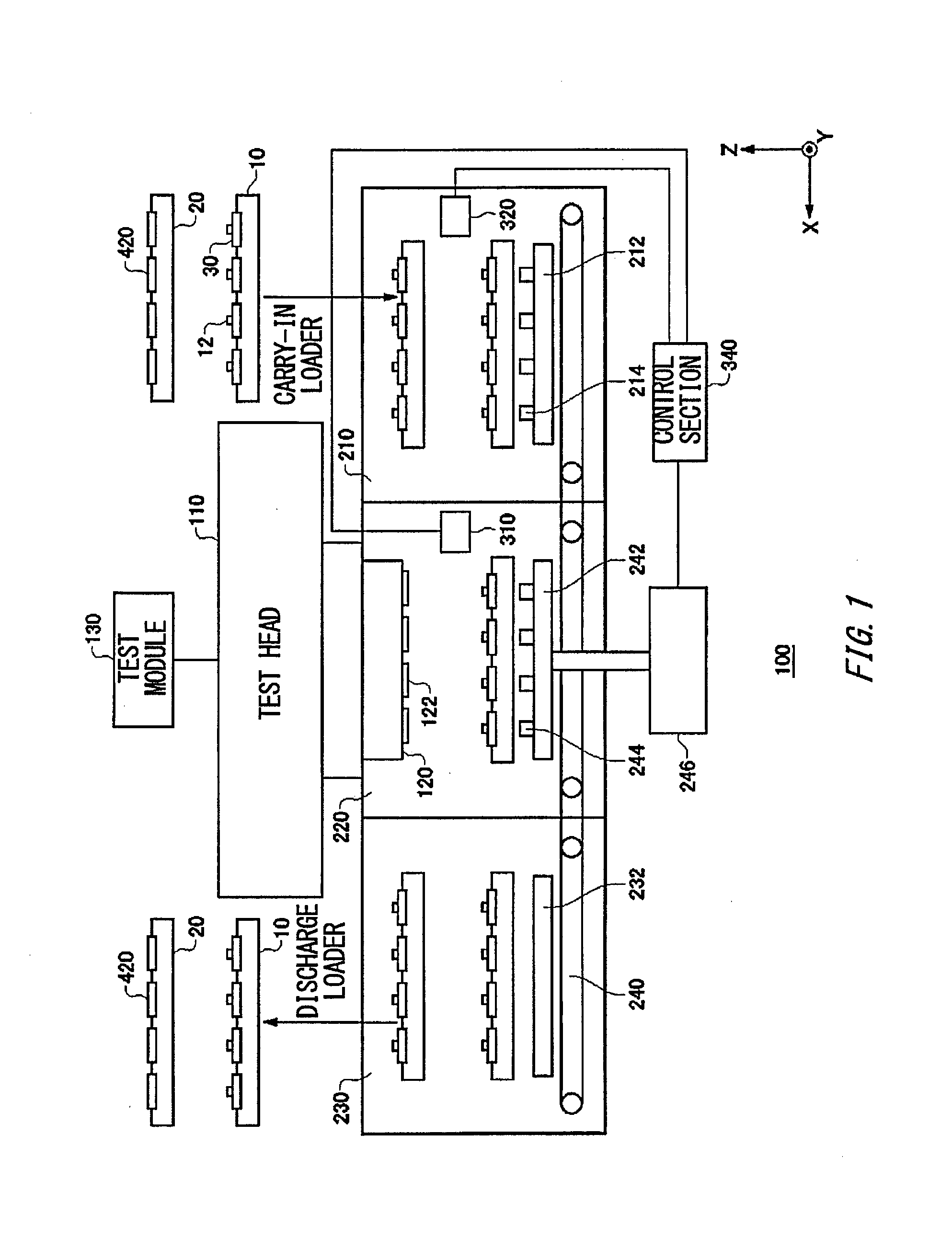

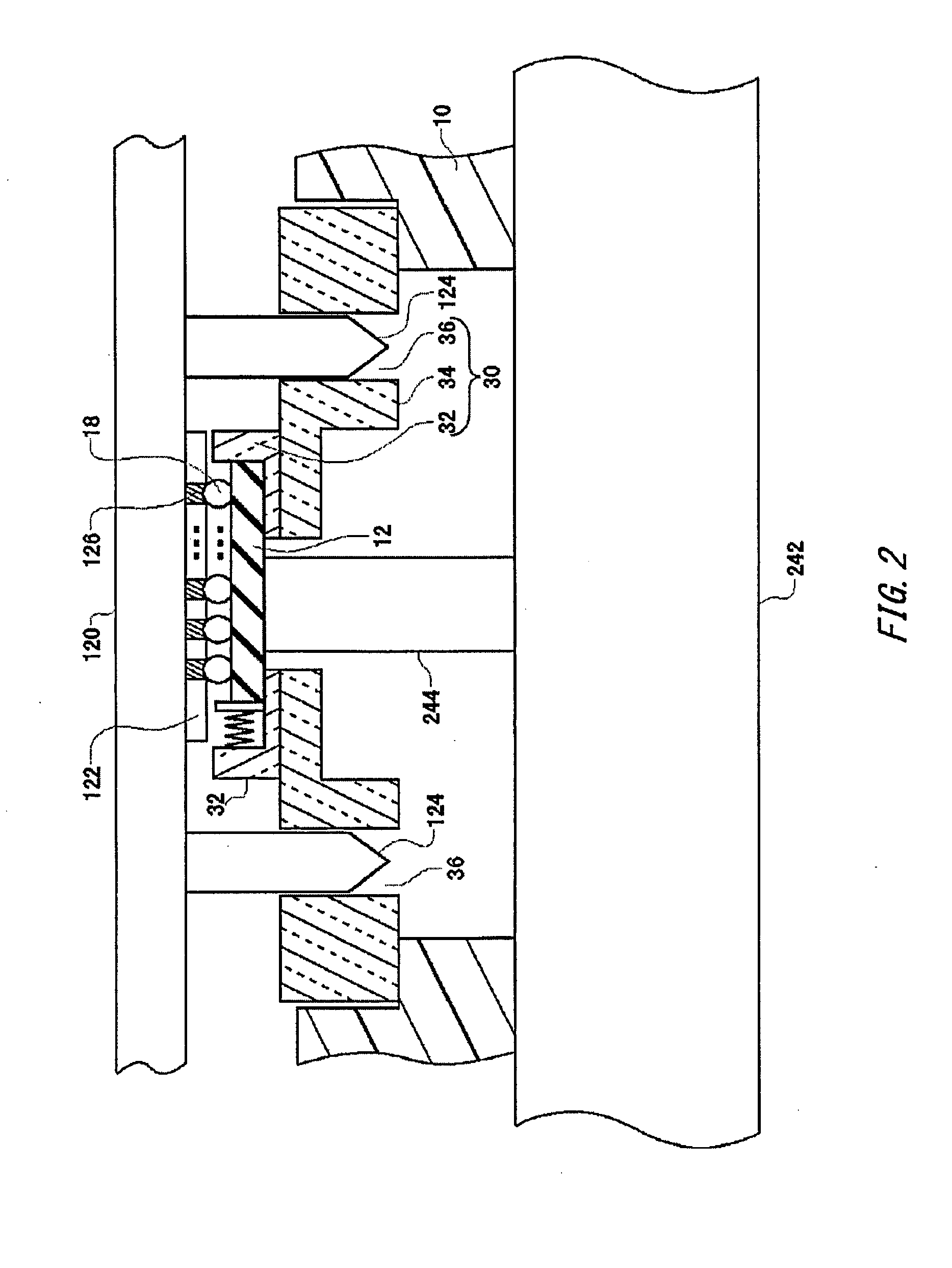

Handler apparatus, adjustment method of handler apparatus, and test apparatus

ActiveUS20150276861A1Electronic circuit testingPhotogrammetry/videogrammetryDevice under testTest set

Owner:ADVANTEST CORP

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap