Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

54results about "Electric signal transmission systems" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

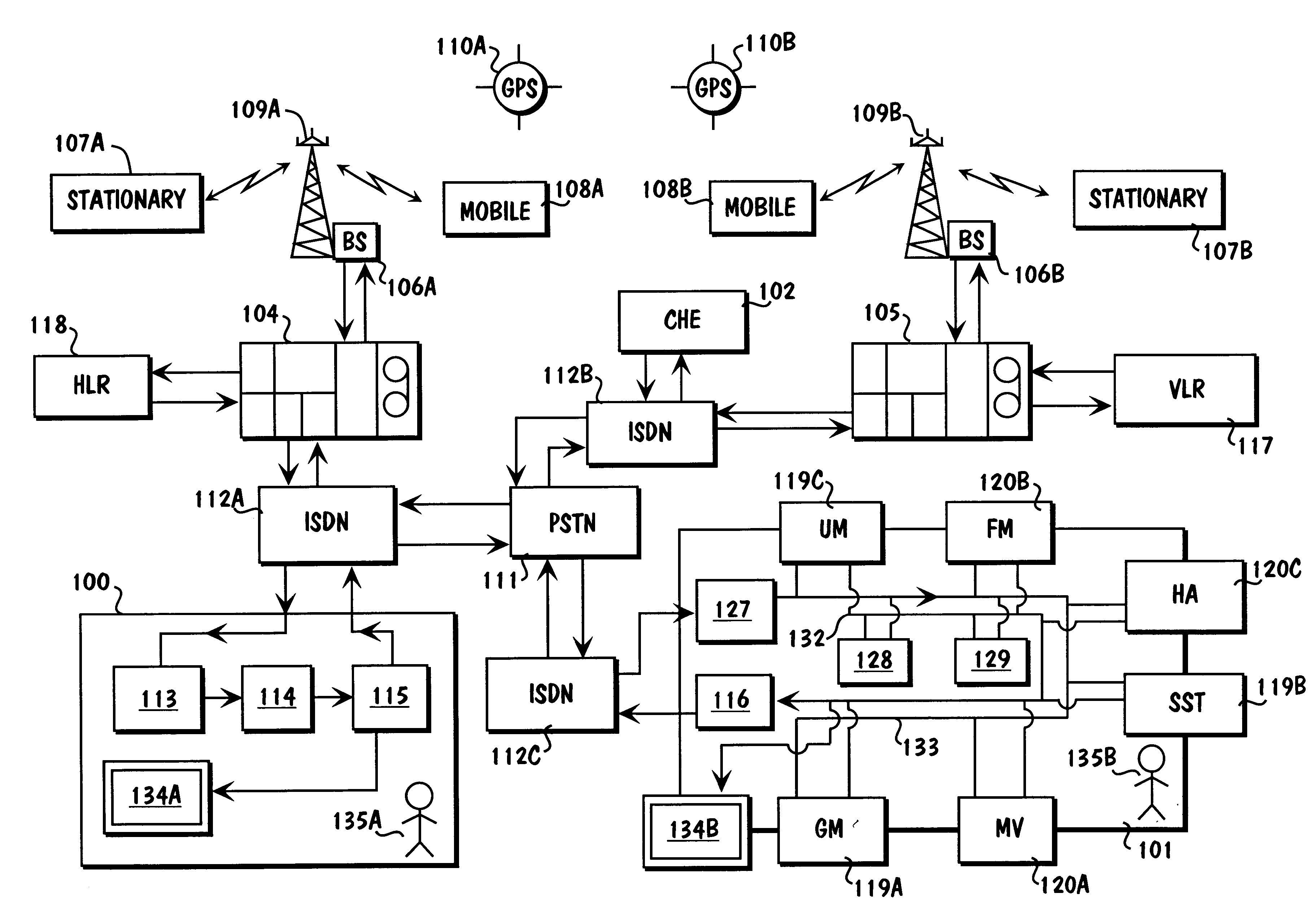

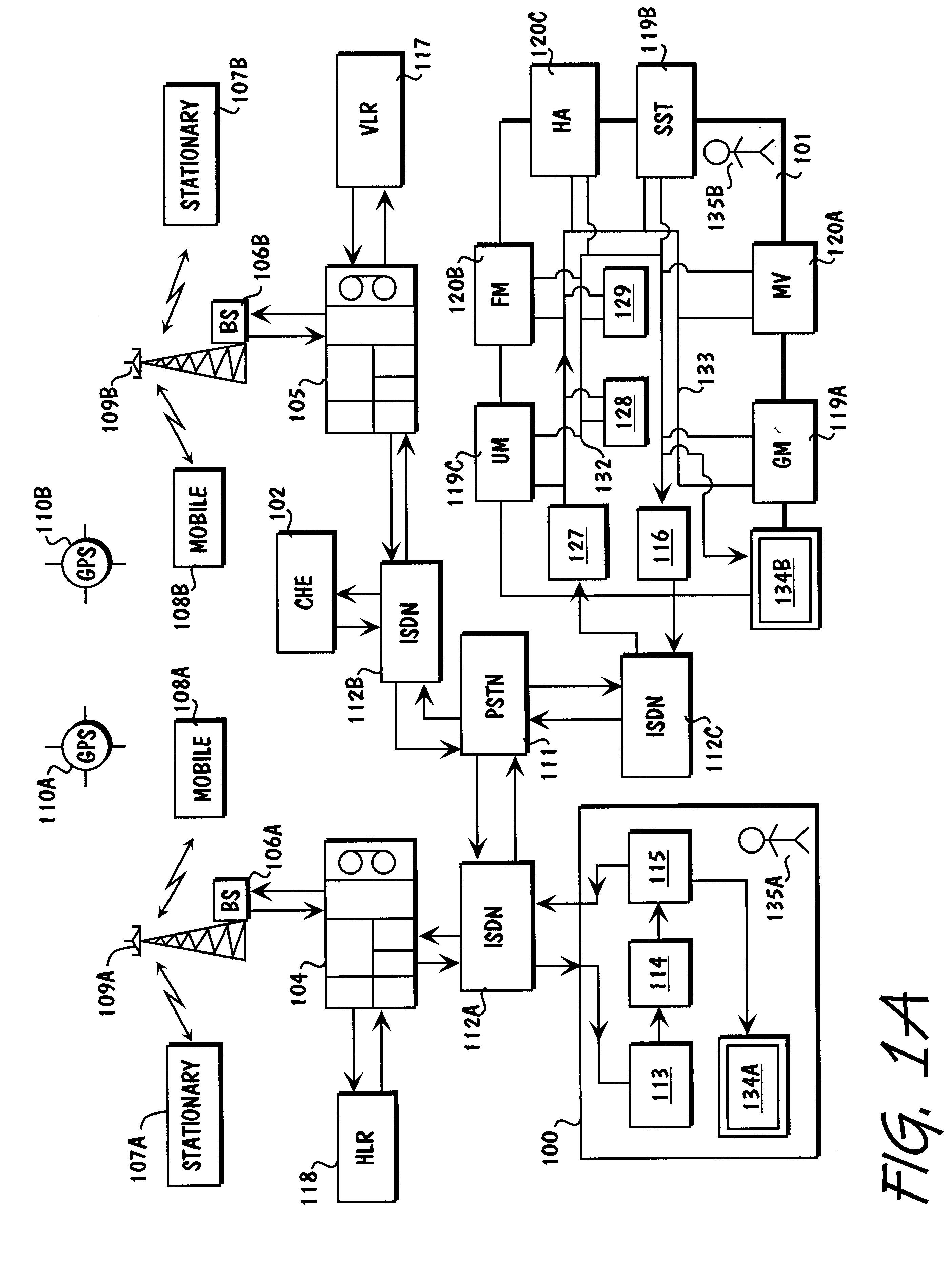

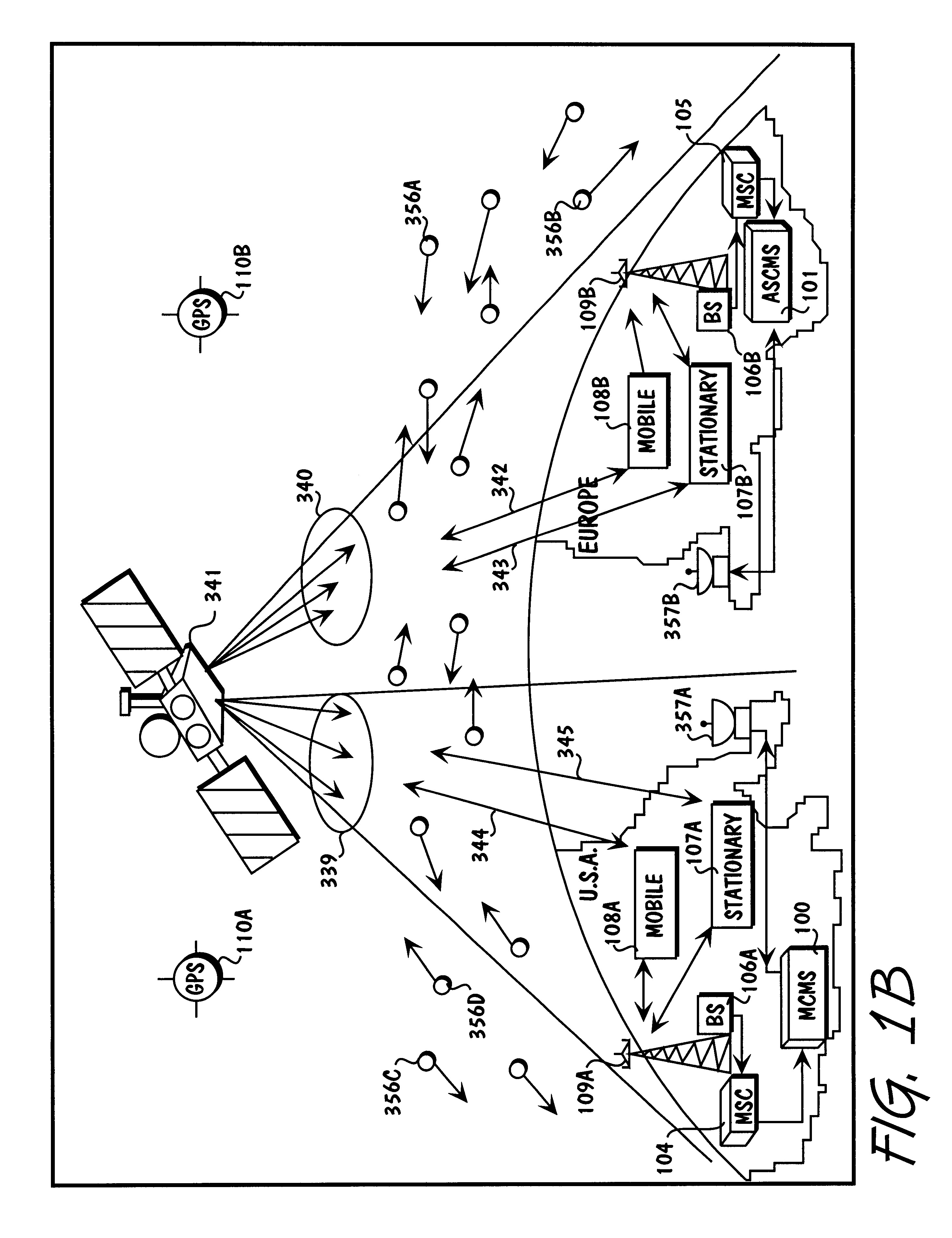

Wireless communications application specific enabling method and apparatus

InactiveUS6285868B1Electric signal transmission systemsUnauthorised/fraudulent call preventionData conversionTelecommunications

Owner:AERIS COMM

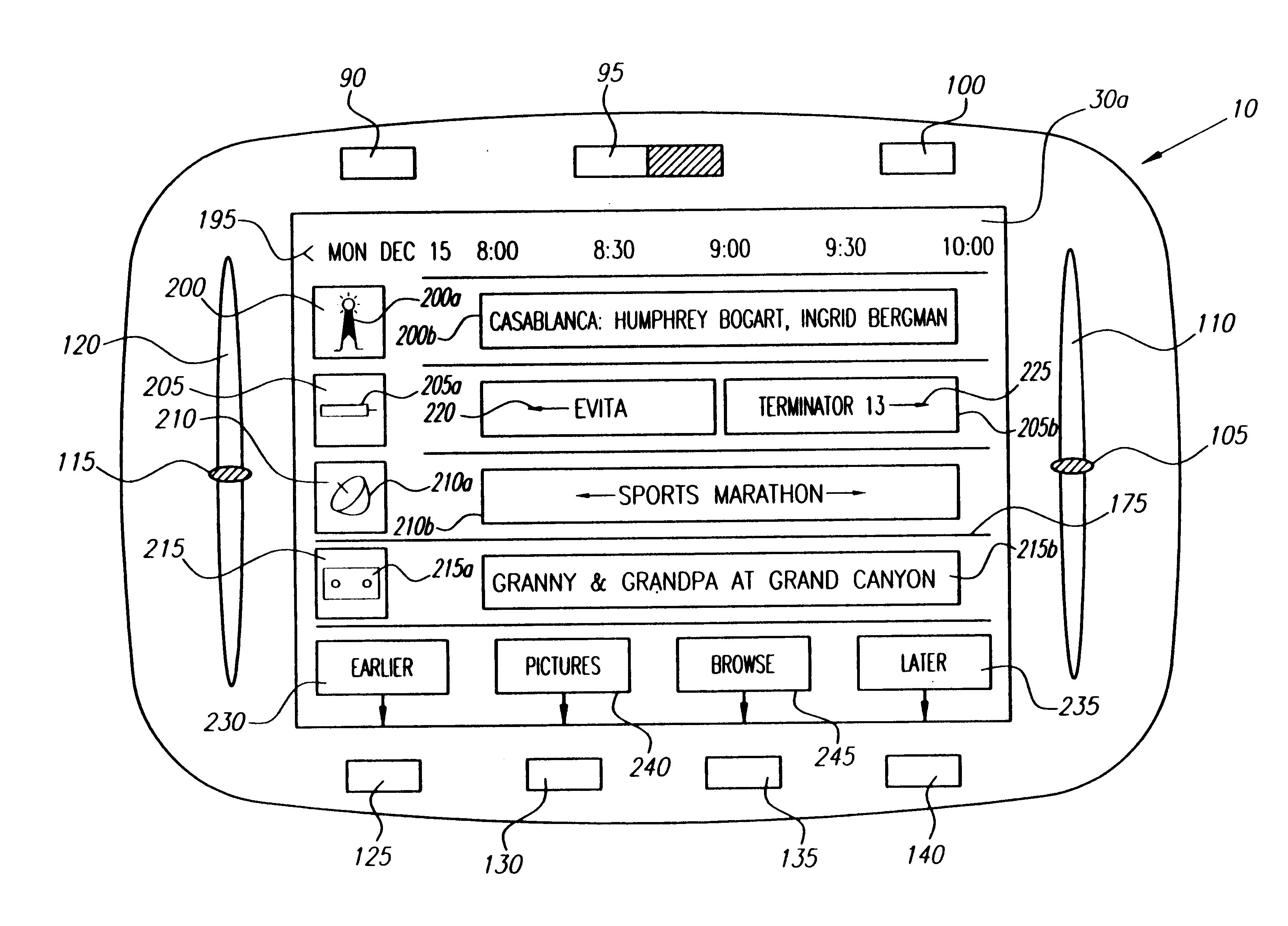

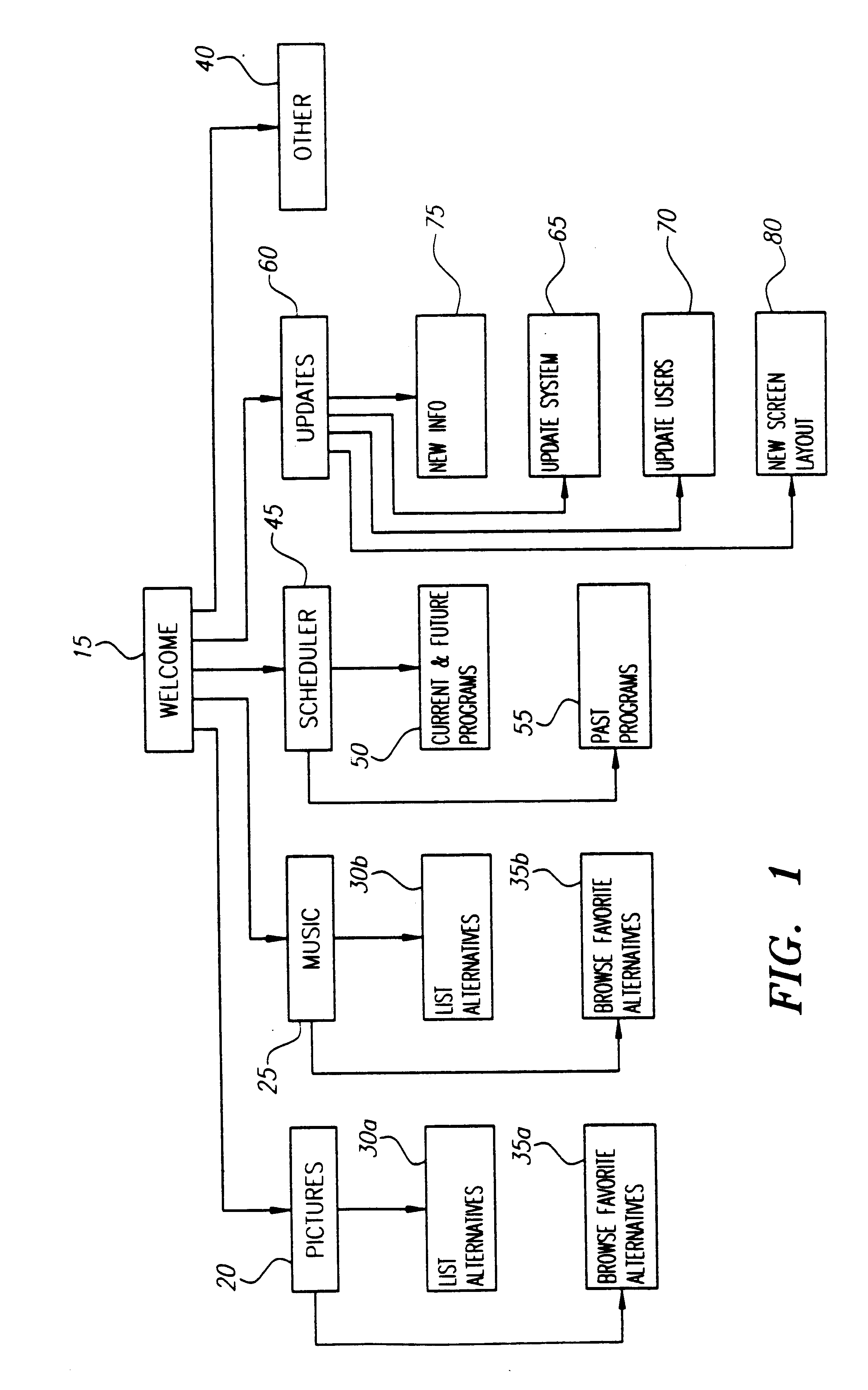

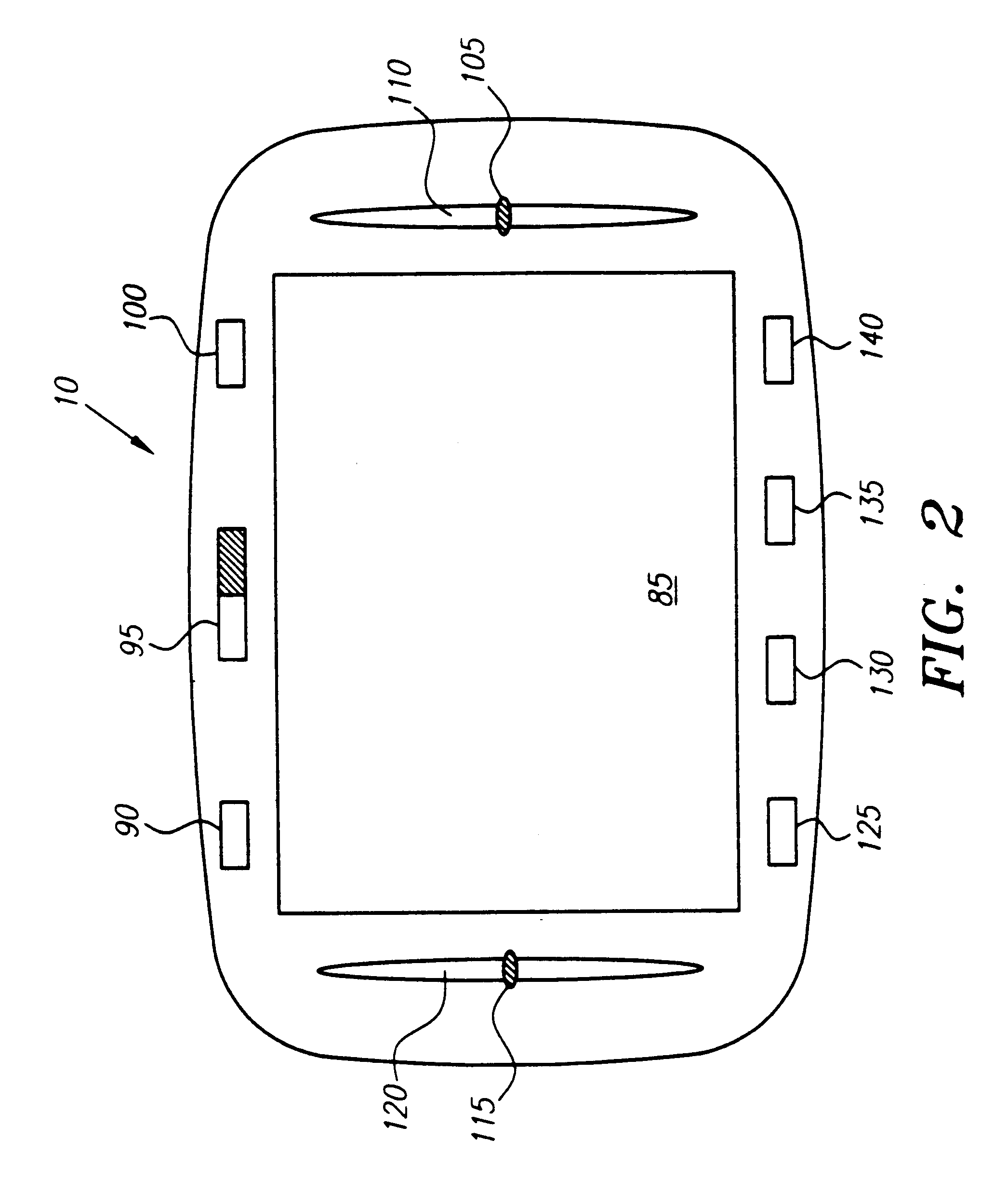

Portable internet-enabled controller and information browser for consumer devices

InactiveUS6882299B1The process is simple and easy to understandTelevision system detailsElectric signal transmission systemsGraphicsRemote control

Owner:RES INVESTMENT NETWORK

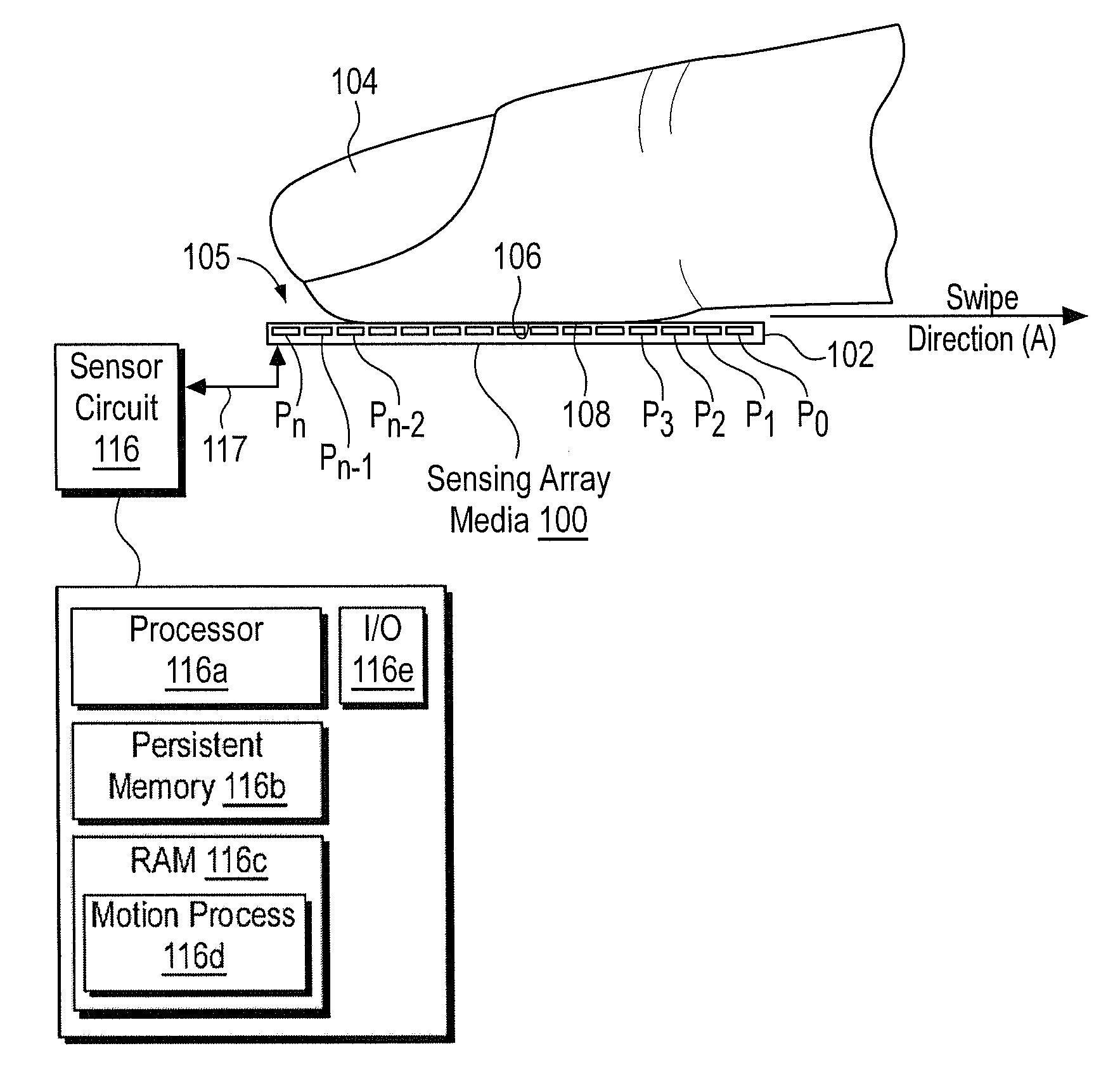

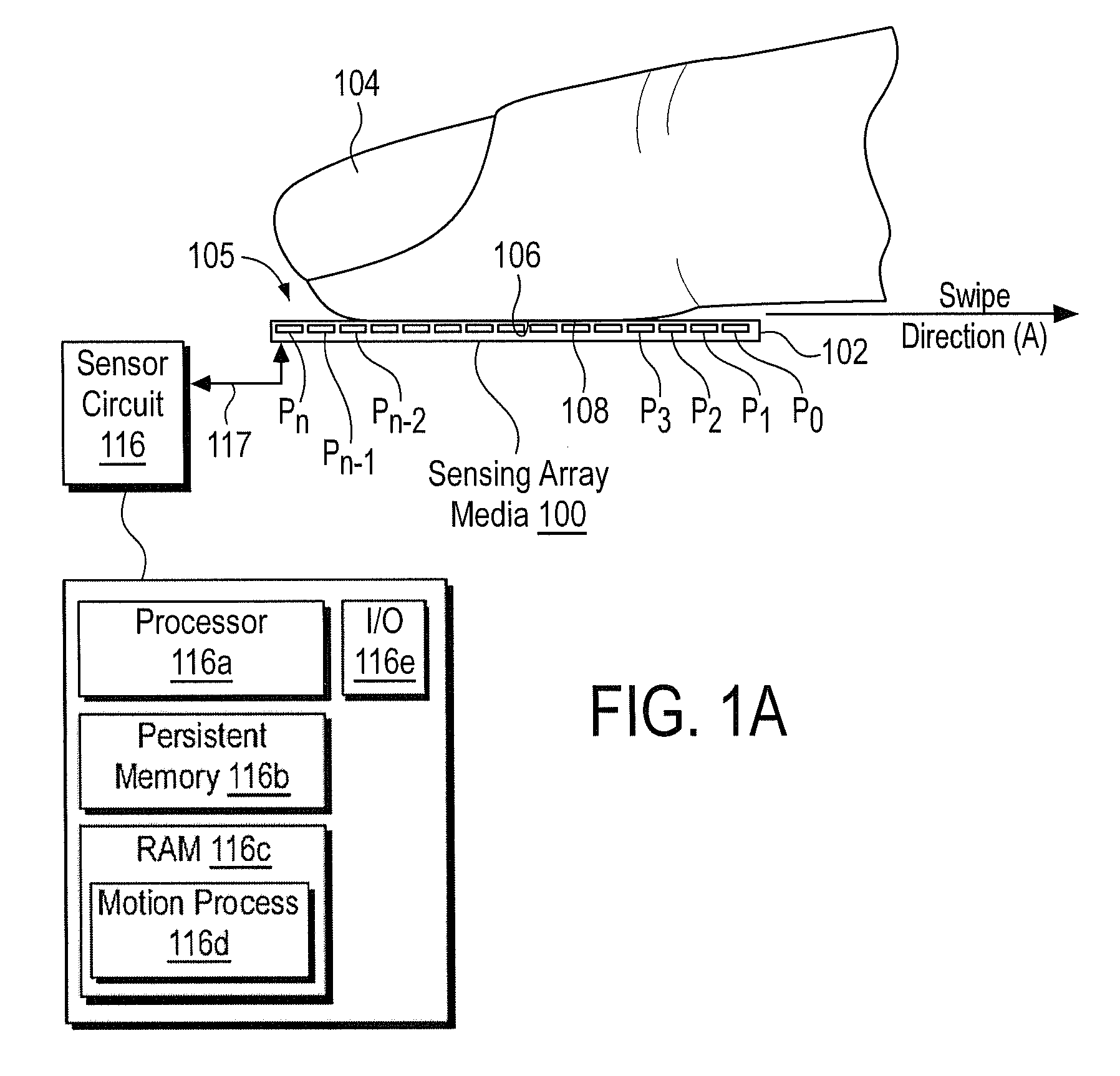

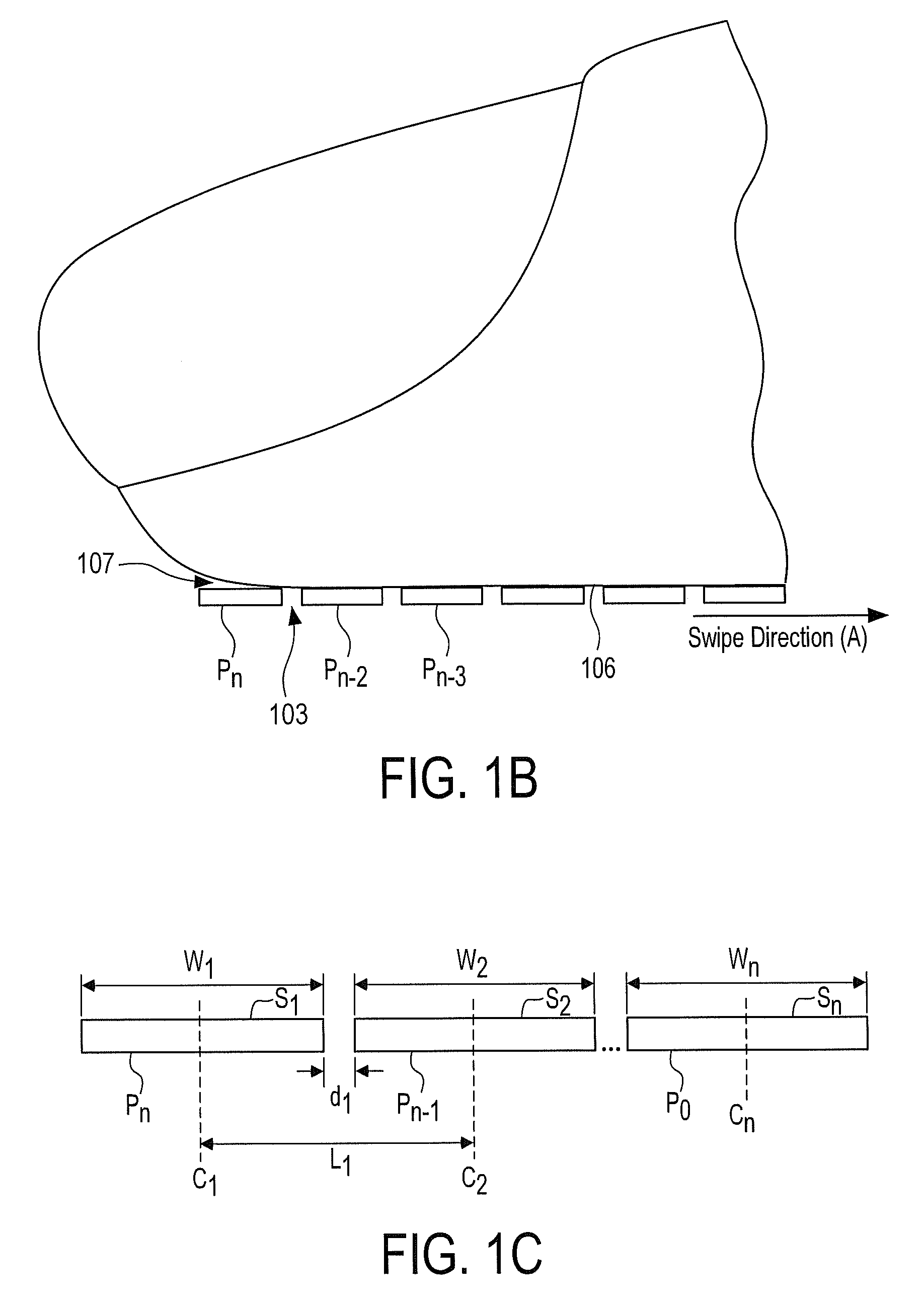

Method and Apparatus for Fingerprint Image Reconstruction

Owner:SYNAPTICS INC

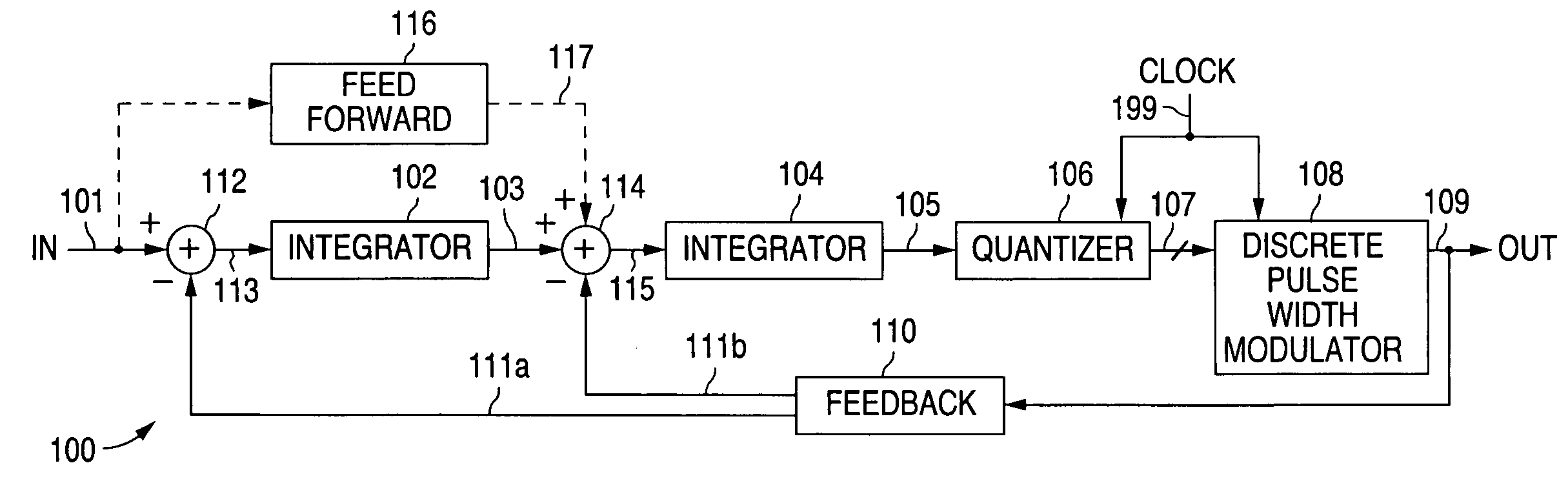

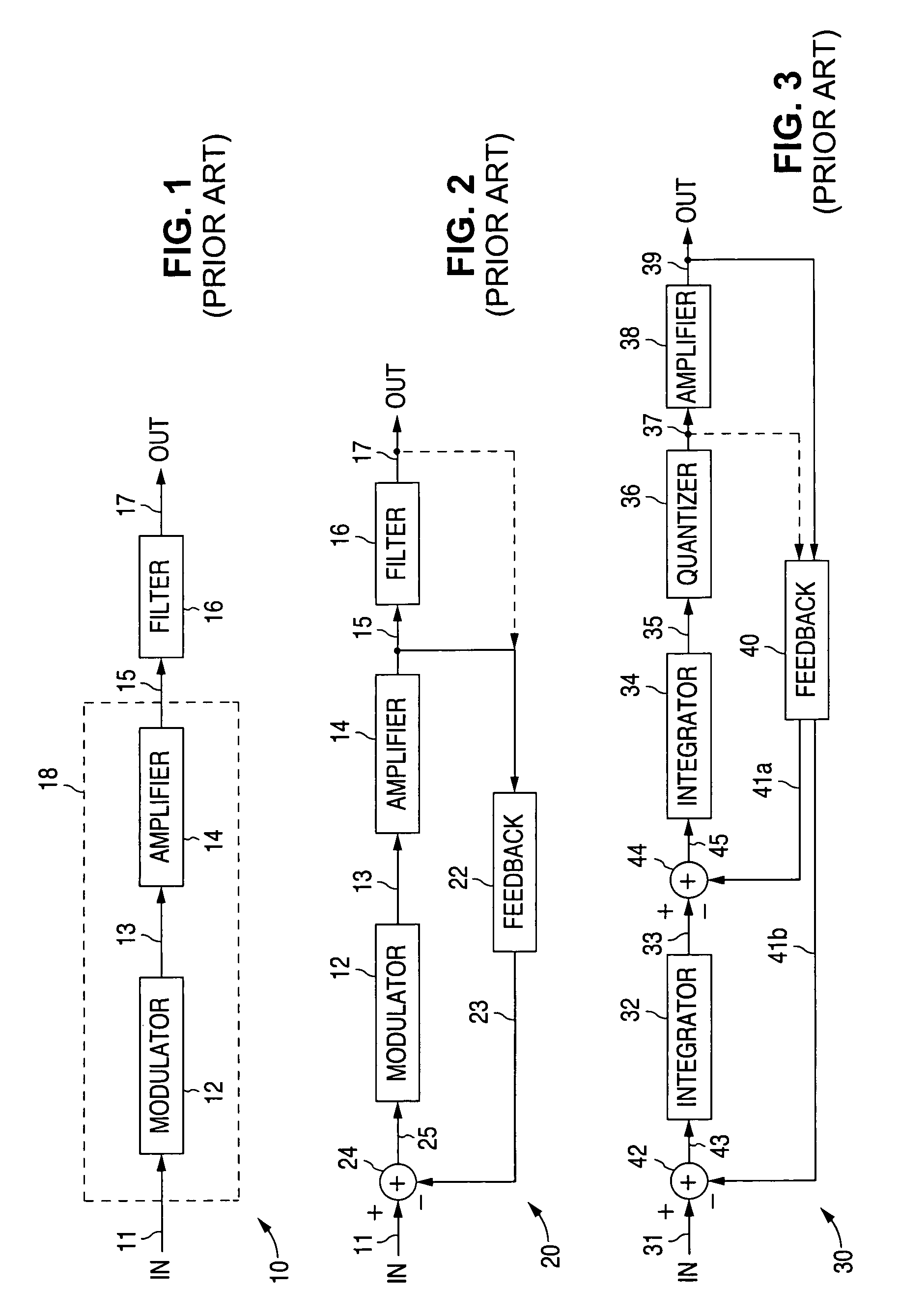

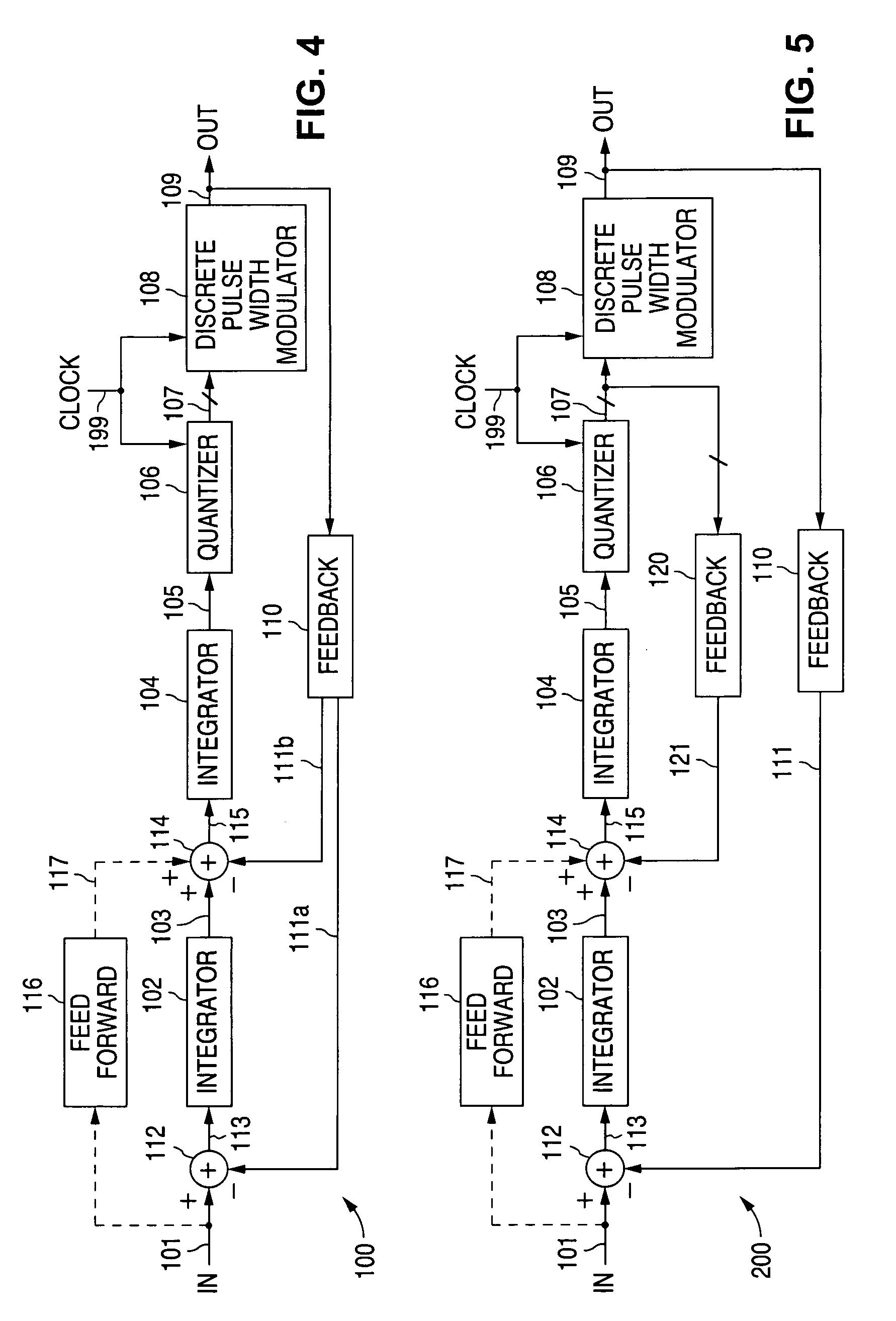

Apparatus and method for converting analog signal to pulse-width-modulated signal

InactiveUS6970503B1Analogue/digital conversionElectric signal transmission systemsAudio power amplifierEngineering

Owner:NAT SEMICON CORP

Detection of broadcast signals for defining useable frequency bands for powerline communication

ActiveUS20050035850A1Electric signal transmission systemsSystems with measurements/testing channelsFrequency bandPower-line communication

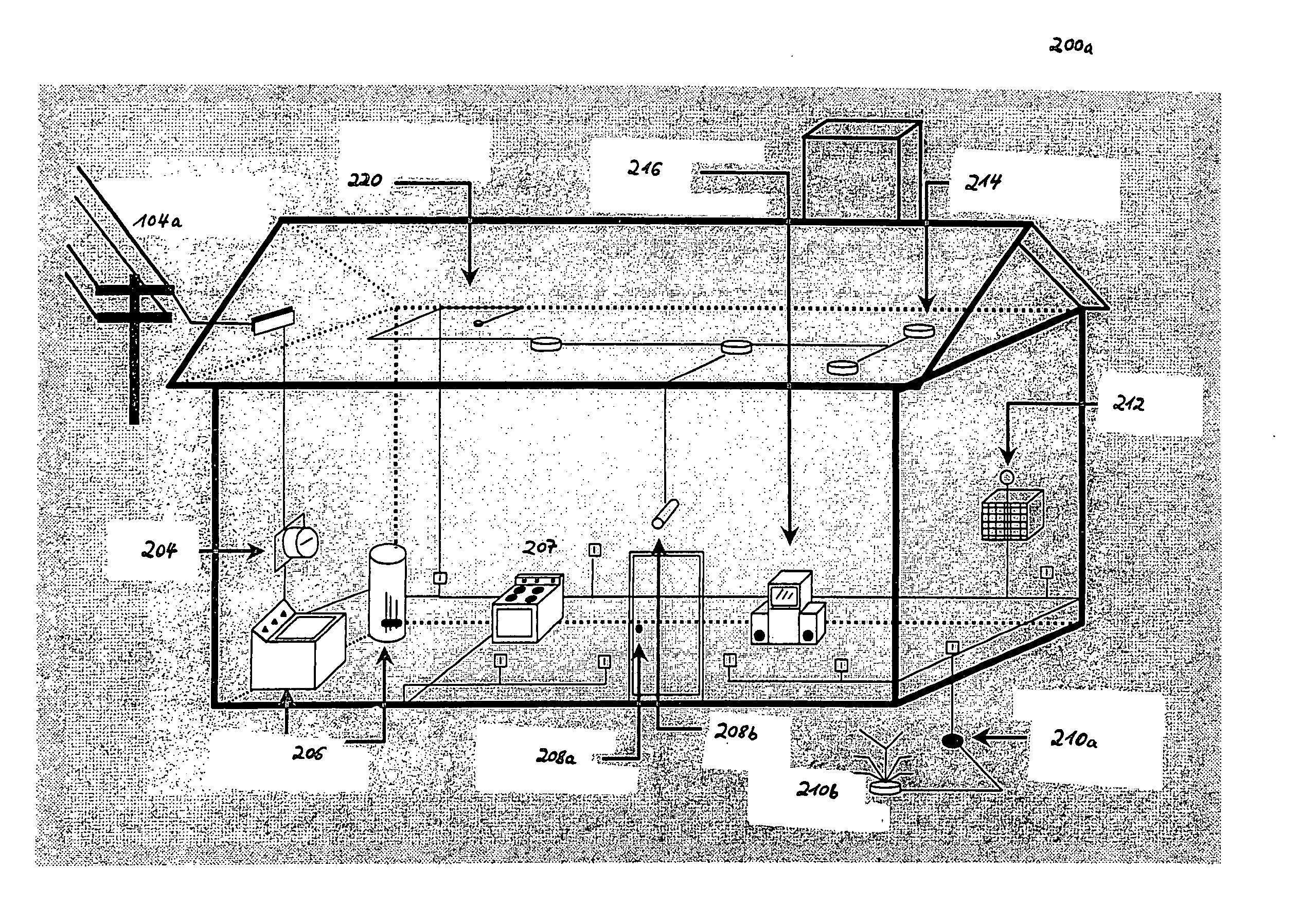

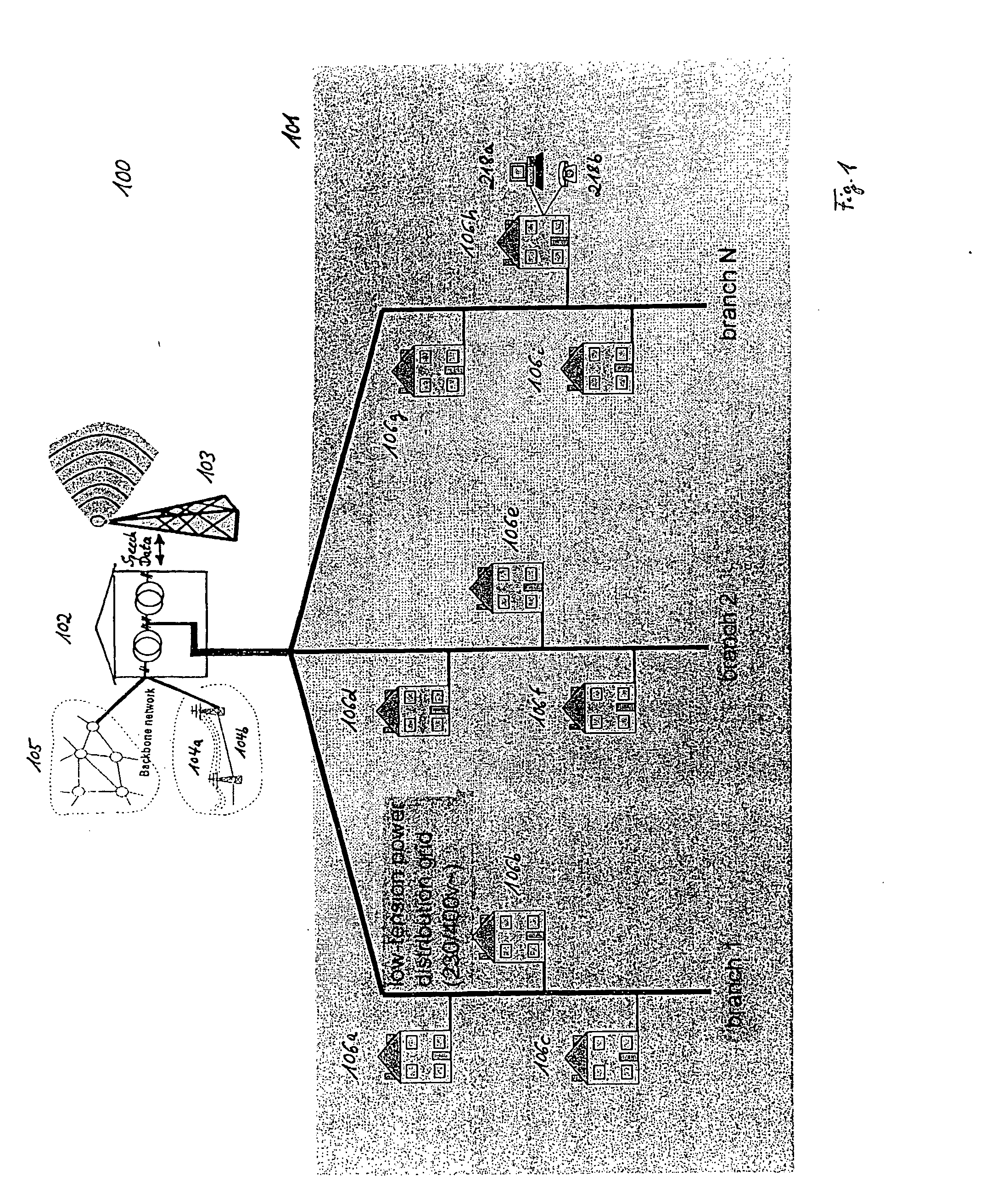

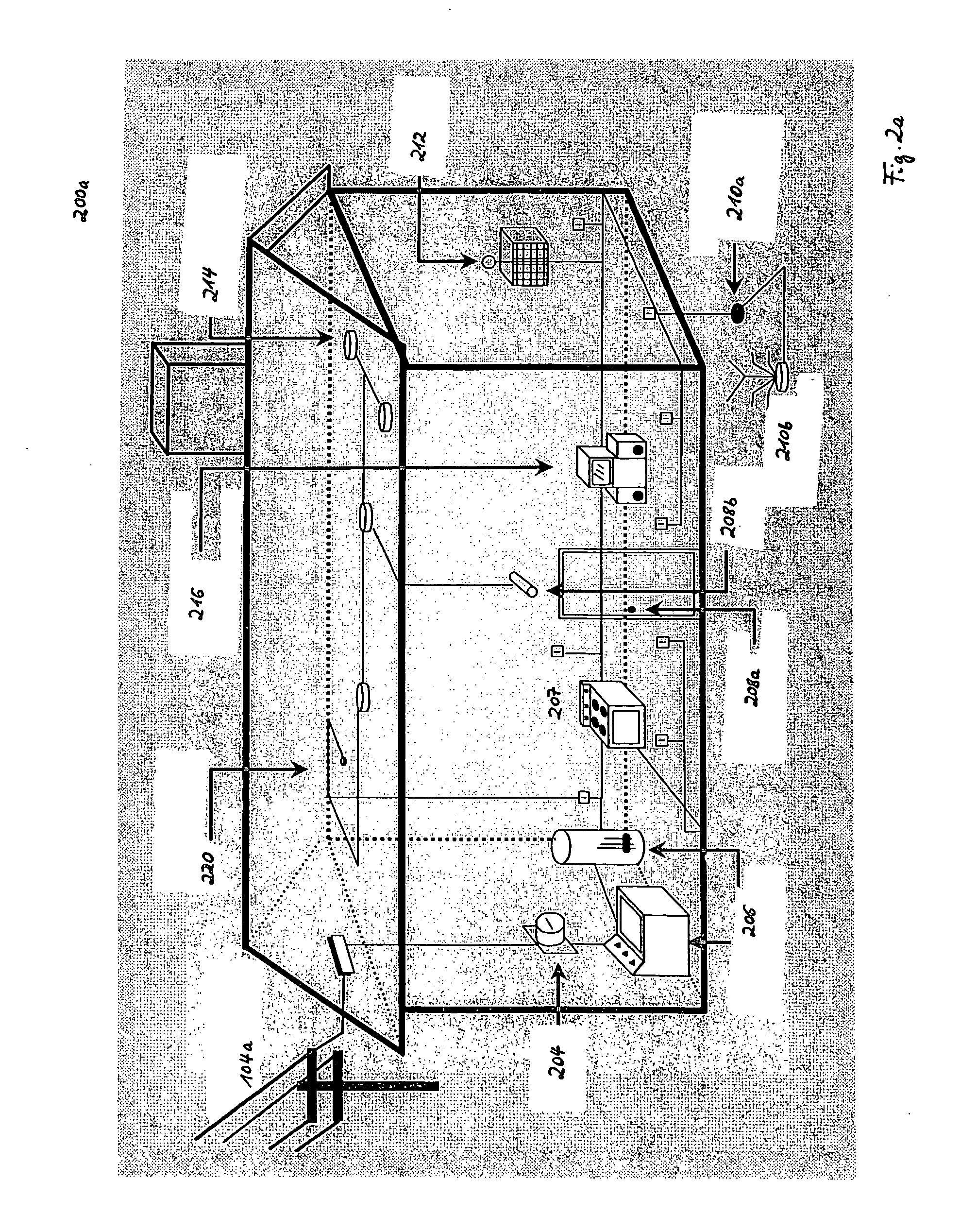

The present invention refers to a method for defining useable frequency bands for a powerline communication (PLC) system (101) using power supply lines of a power supply network (104a) for interconnecting a number of PLC nodes (302, 306) such that electromagnetic emissions generated by PLC signals (s(t)) transmitted via said power supply lines do not interfere with broadcast RF signals radiated in the same frequency bands. Before starting own communication activities, PLC nodes (302, 306) participating in a PLC session scan (S1a) the entire frequency range designated for powerline communication to detect (S1b) frequency bands which are occupied by broadcast services. During powerline communication the occurrence of broadcast signals is regularly checked (S2) by screening (S2a) the entire frequency range designated for powerline communication and detecting (S2b) relevant broadcast bands that should be omitted during powerline communication to avoid interference noise (n(t)). After that, new frequency bands for powerline communication are allocated (S3) within said frequency range, provided that these new bands are not occupied by any detected wireless service.

Owner:SONY DEUT GMBH

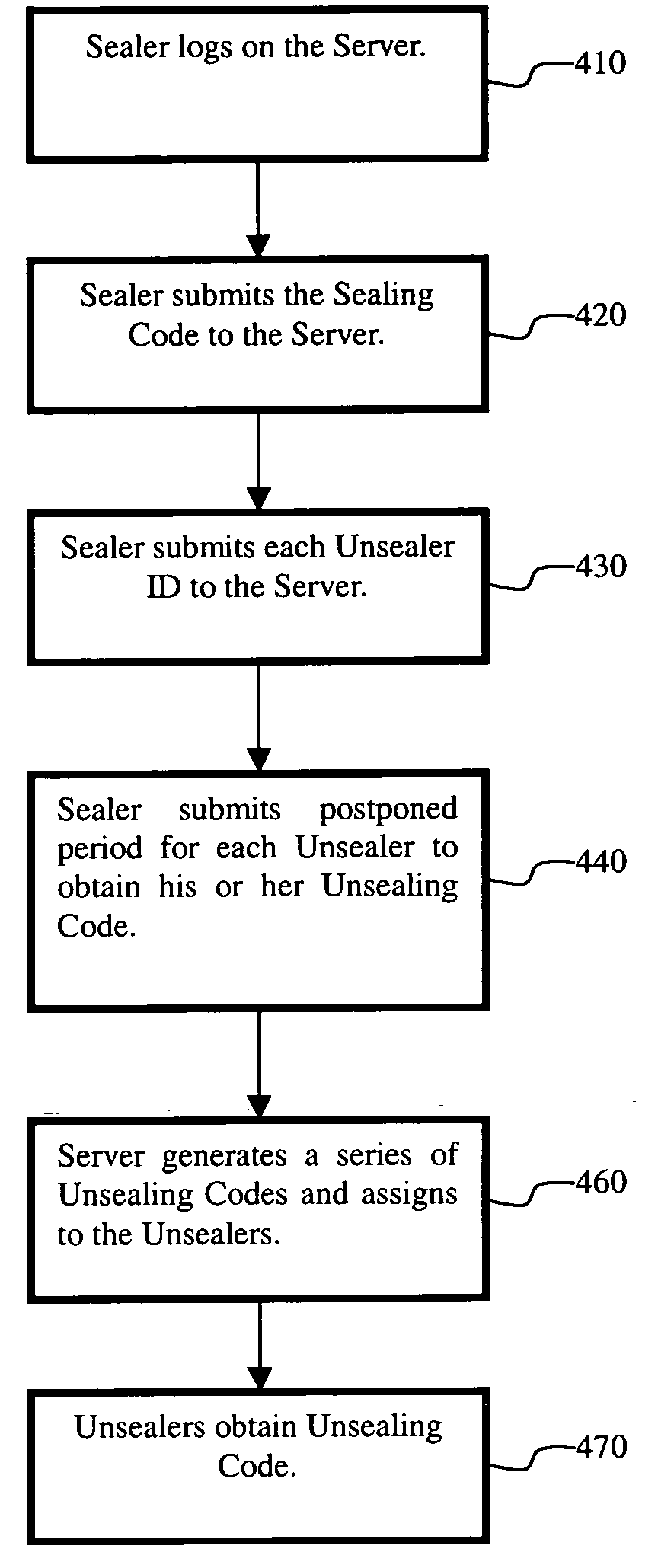

Cargo theft prevention method and system

InactiveUS20050219037A1StampsKey distribution for secure communicationComputer hardwareCommunications system

Owner:HUANG TAO

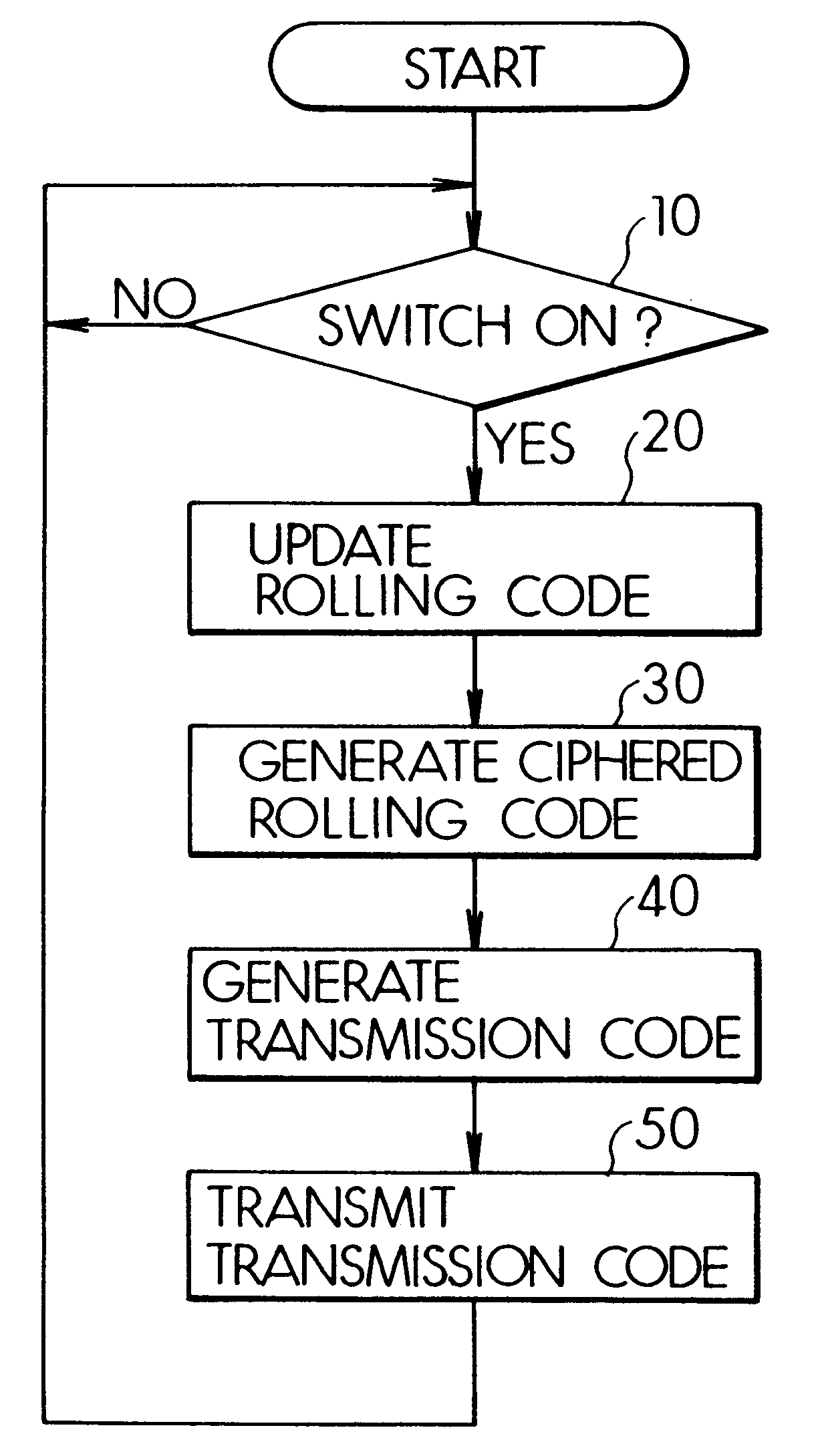

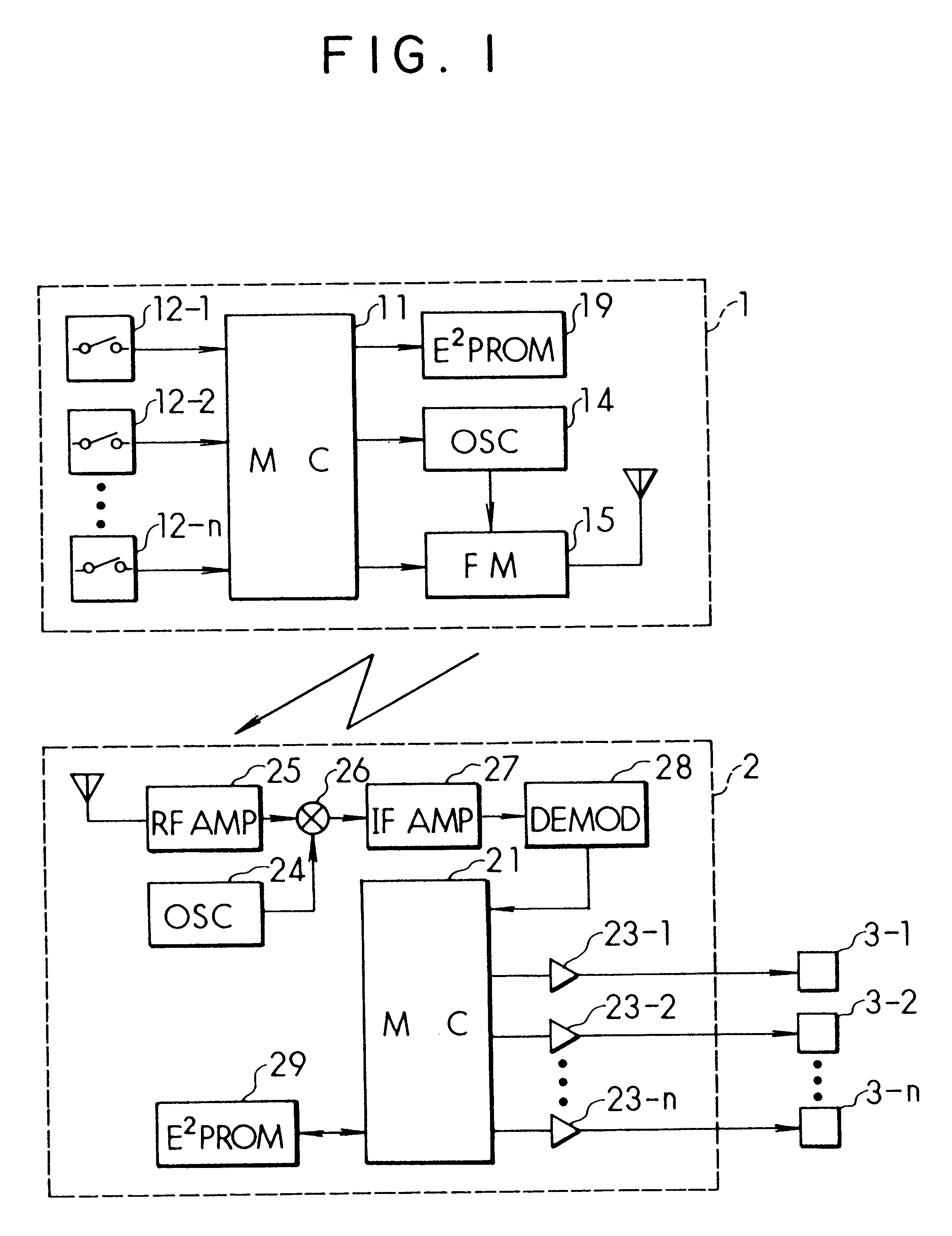

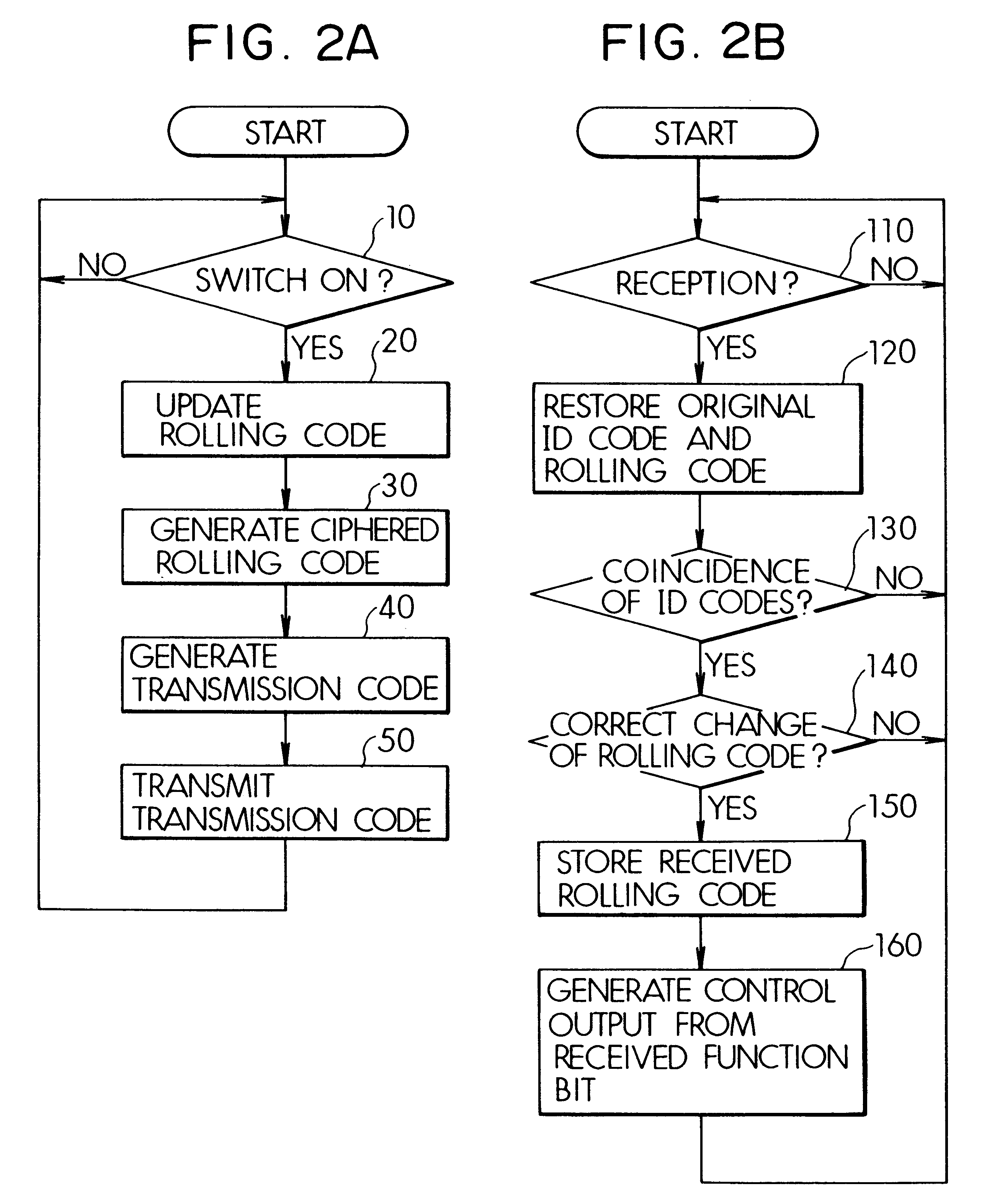

Remote control system and method having a system-specific code

InactiveUS6181252B1Key distribution for secure communicationElectric signal transmission systemsEEPROMRolling code

Owner:DENSO CORP

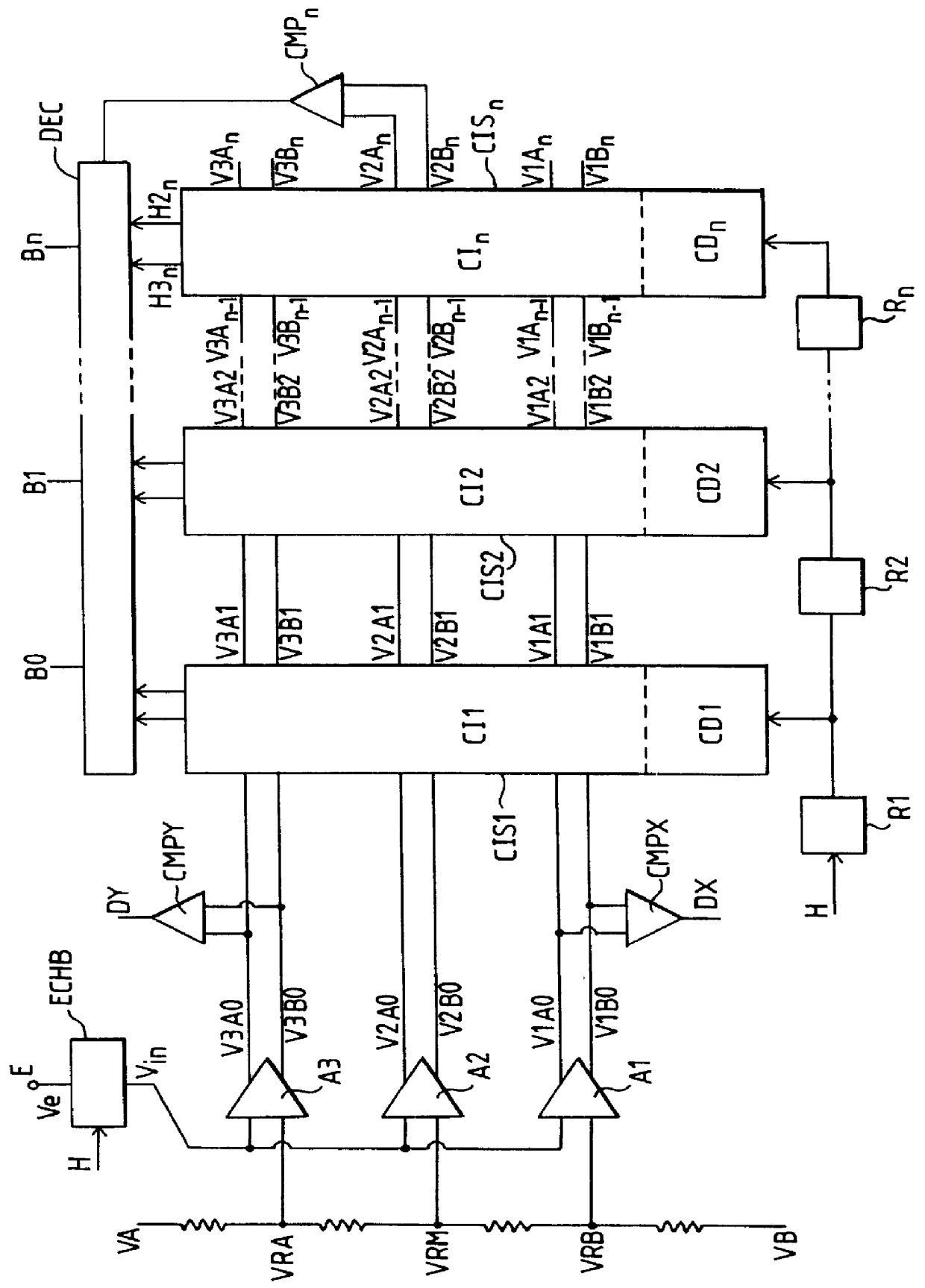

Differential pipelined analog to digital converter with successive approximation register subconverter stages

InactiveUS6879277B1Improve conversion speedReduce power consumptionElectric signal transmission systemsAnalogue-digital convertersAnalog-to-digital converterCapacitor

Pipelined analog to digital conversion systems are provided having cascaded multi-bit successive approximation register subconverter stages. Capacitor arrays are provided in the subconverter stages, where switching logic selectively couples the capacitors to operate in sample, conversion, and residue amplification modes for generating multi-bit subconverter digital outputs and analog subconverter residue outputs. In one implementation, the capacitors are switched according to a thermometer code to reduce differential converter non-linearity, and the first subconverter stage gain is reduced to improve the conversion system bandwidth.

Owner:TEXAS INSTR INC

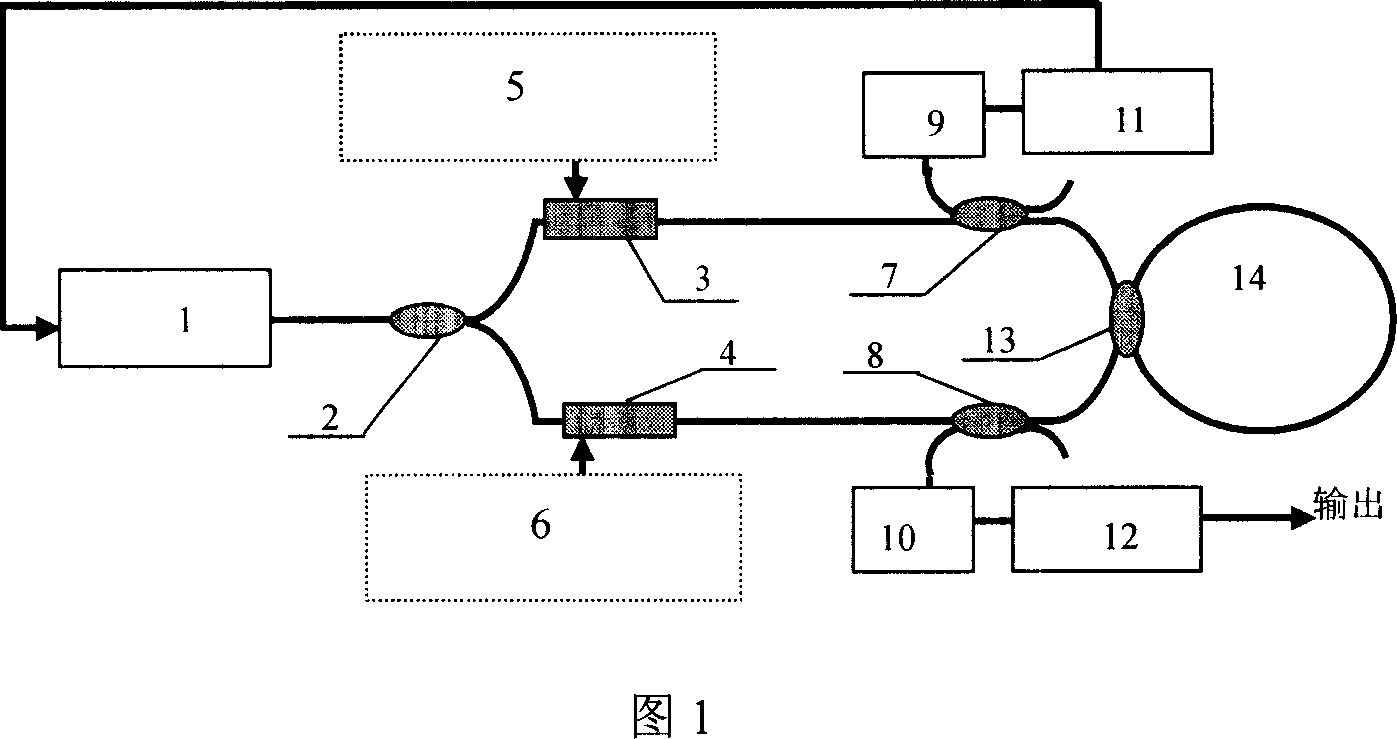

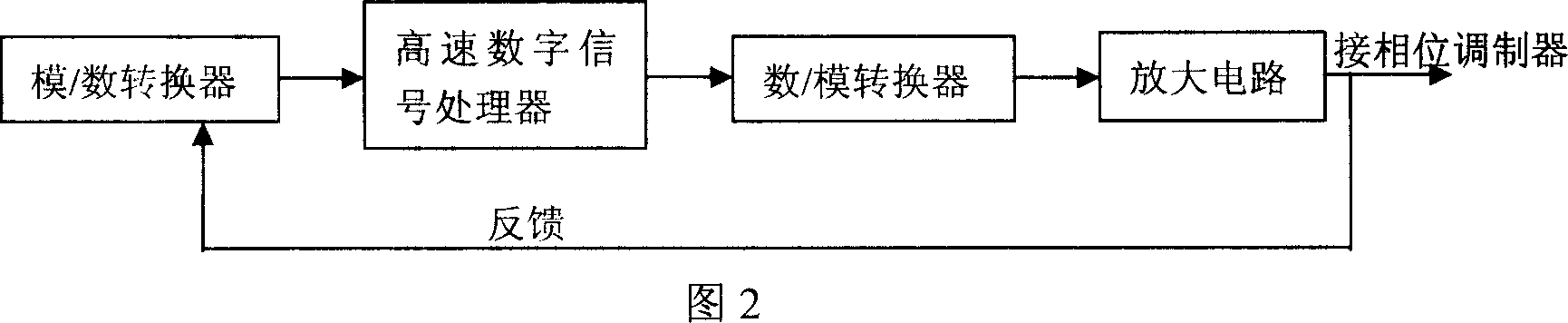

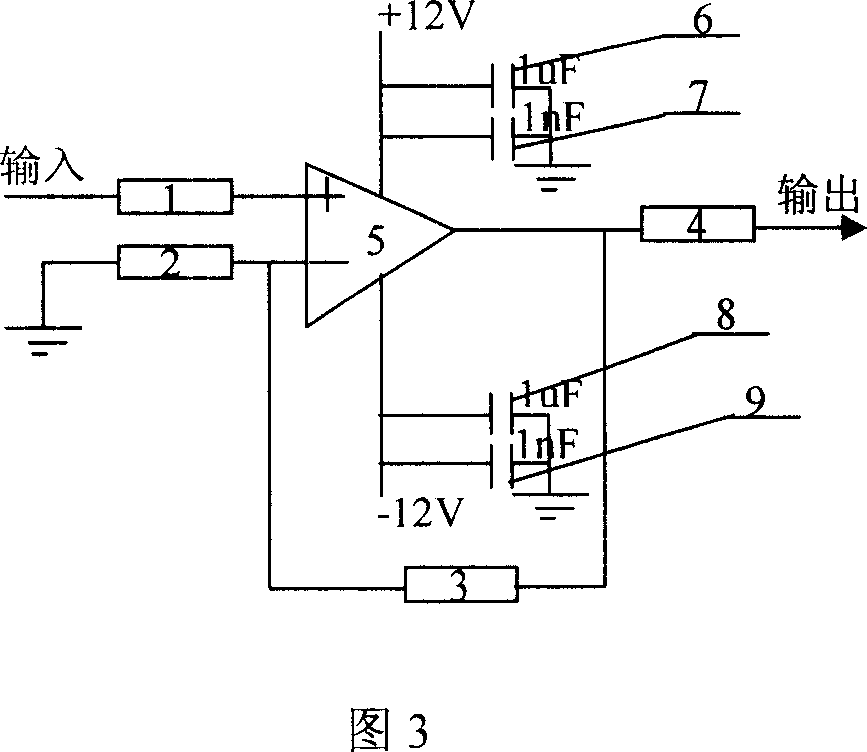

Triangular wave phase modulation method of resonant cavity optical fiber gyroscope and apparatus thereof

InactiveCN101042471ASuppress noiseAvoid influenceAnalogue/digital conversionElectric signal transmission systemsResonant cavityGyroscope

Owner:ZHEJIANG UNIV

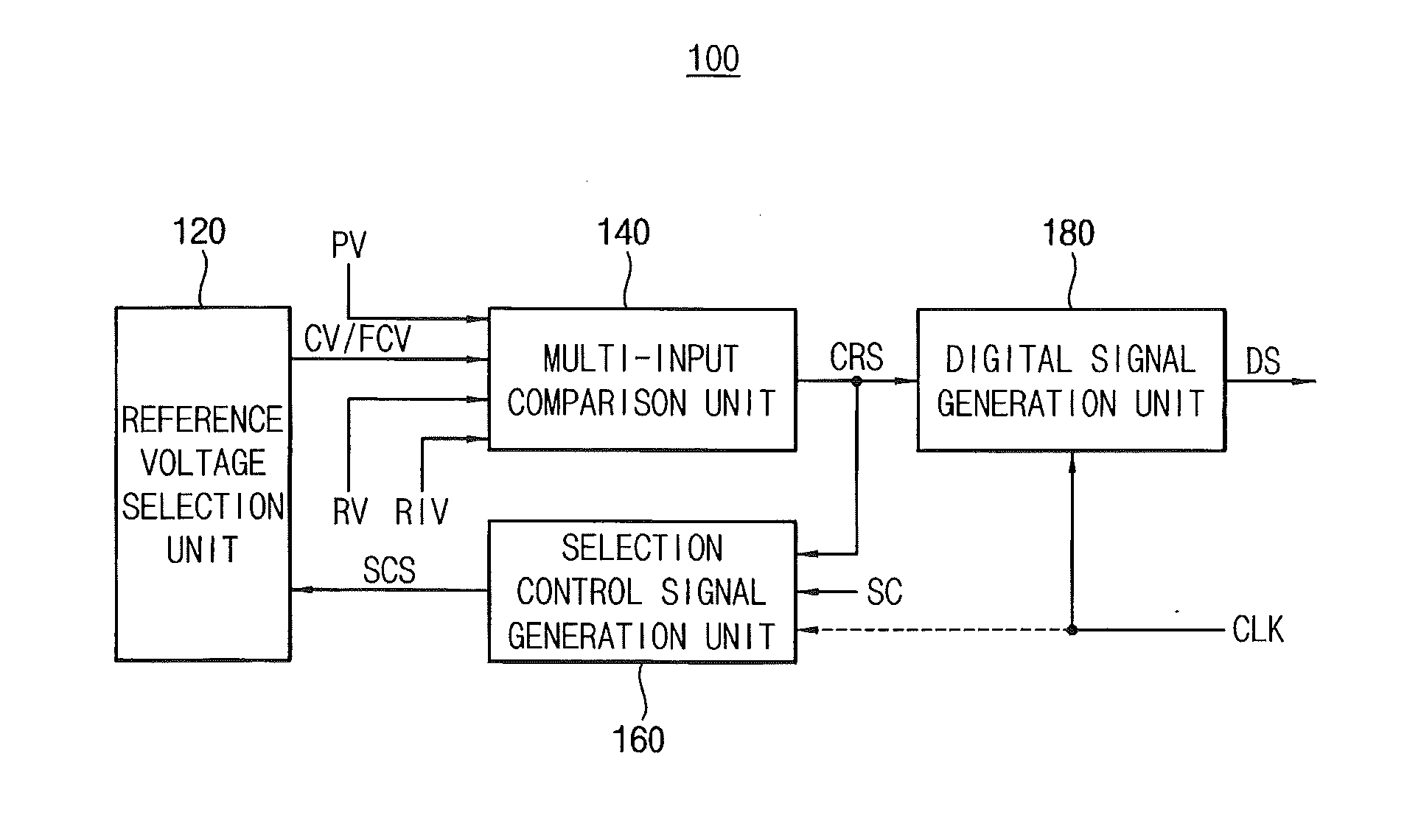

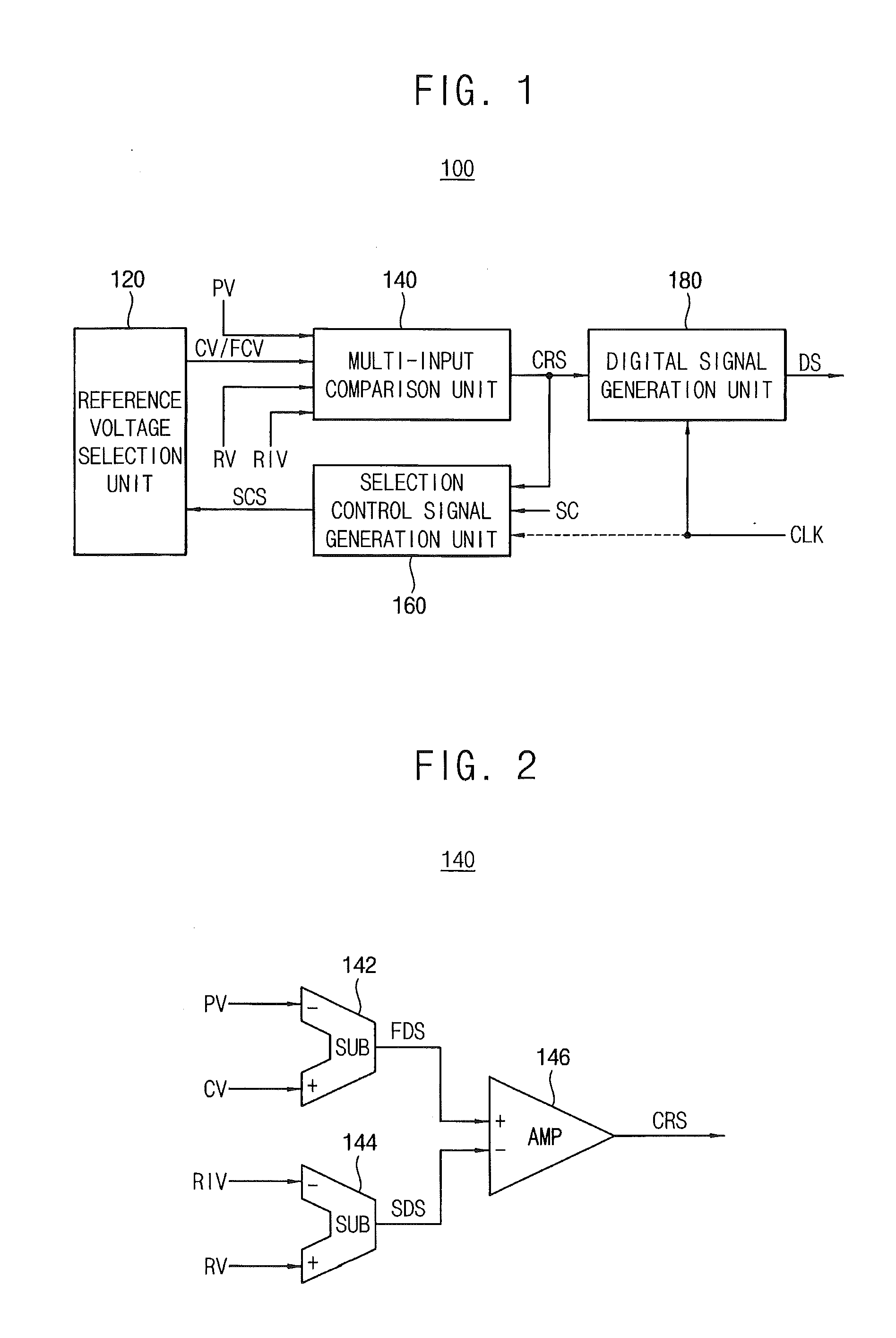

Analog to Digital Converters, Image Sensor Systems, and Methods of Operating the Same

ActiveUS20120113286A1Television system detailsElectric signal transmission systemsMulti inputControl signal

Owner:SAMSUNG ELECTRONICS CO LTD

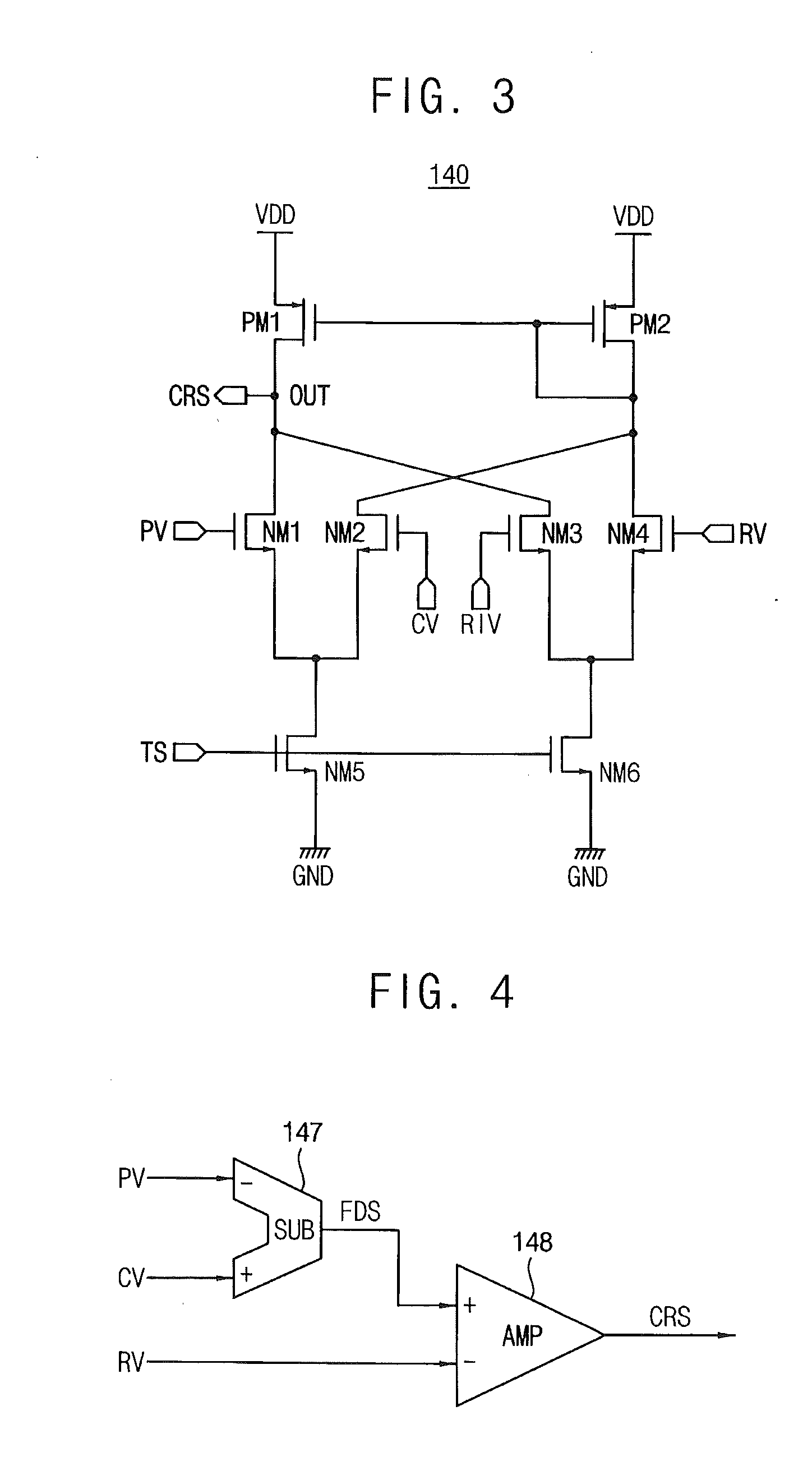

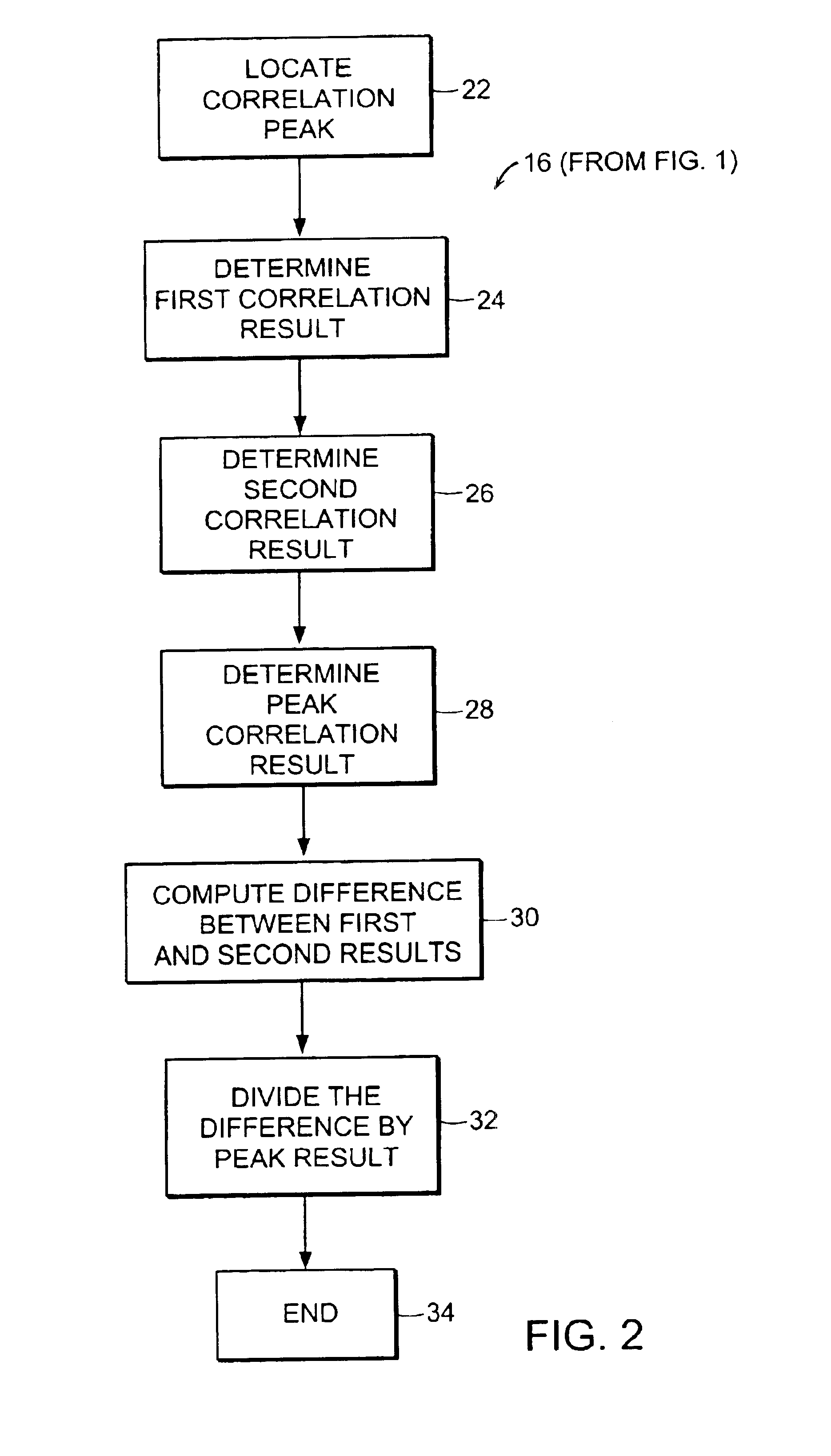

Method of correlation of images in biometric applications

InactiveUS6961449B2Reduce background noiseElectric signal transmission systemsImage analysisPattern recognitionPalm print

Owner:UNIVERSITY OF MASSACHUSETTS LOWELL

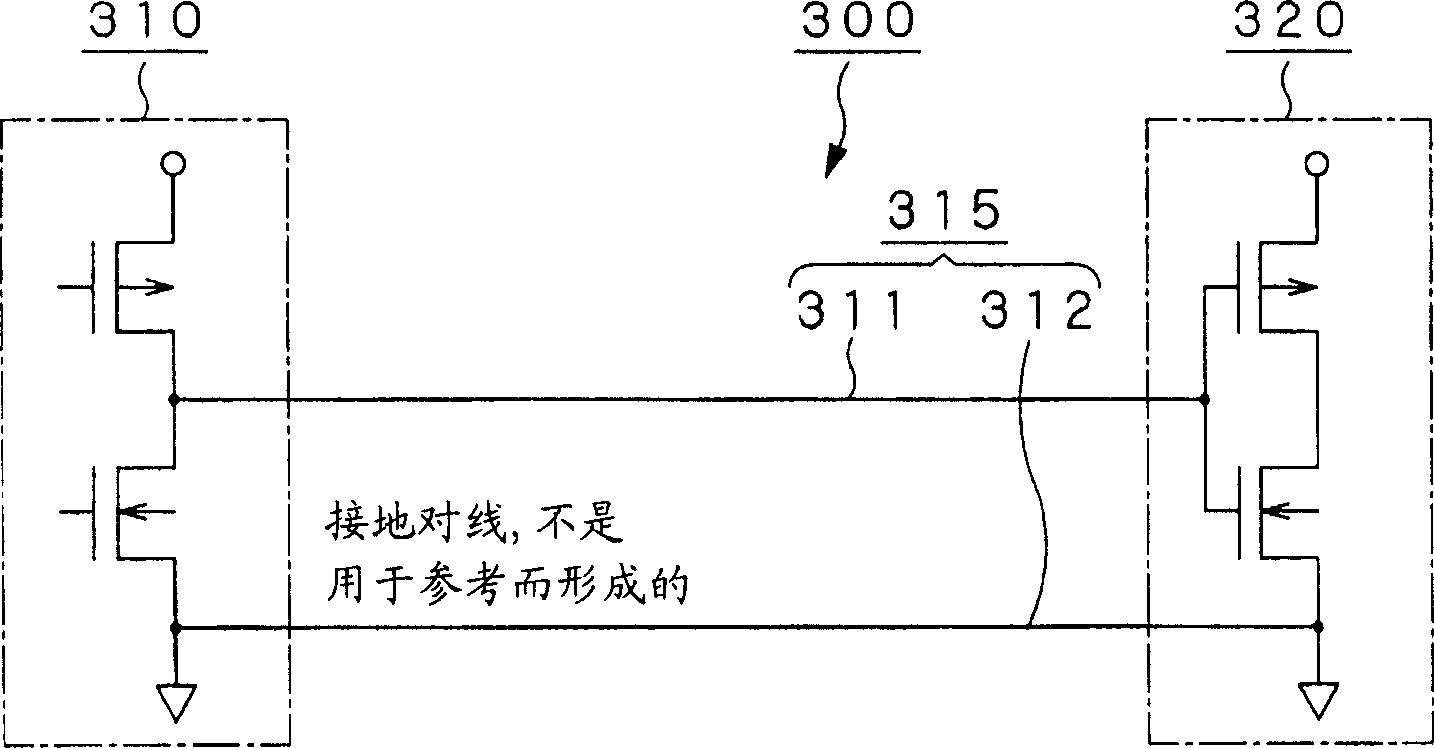

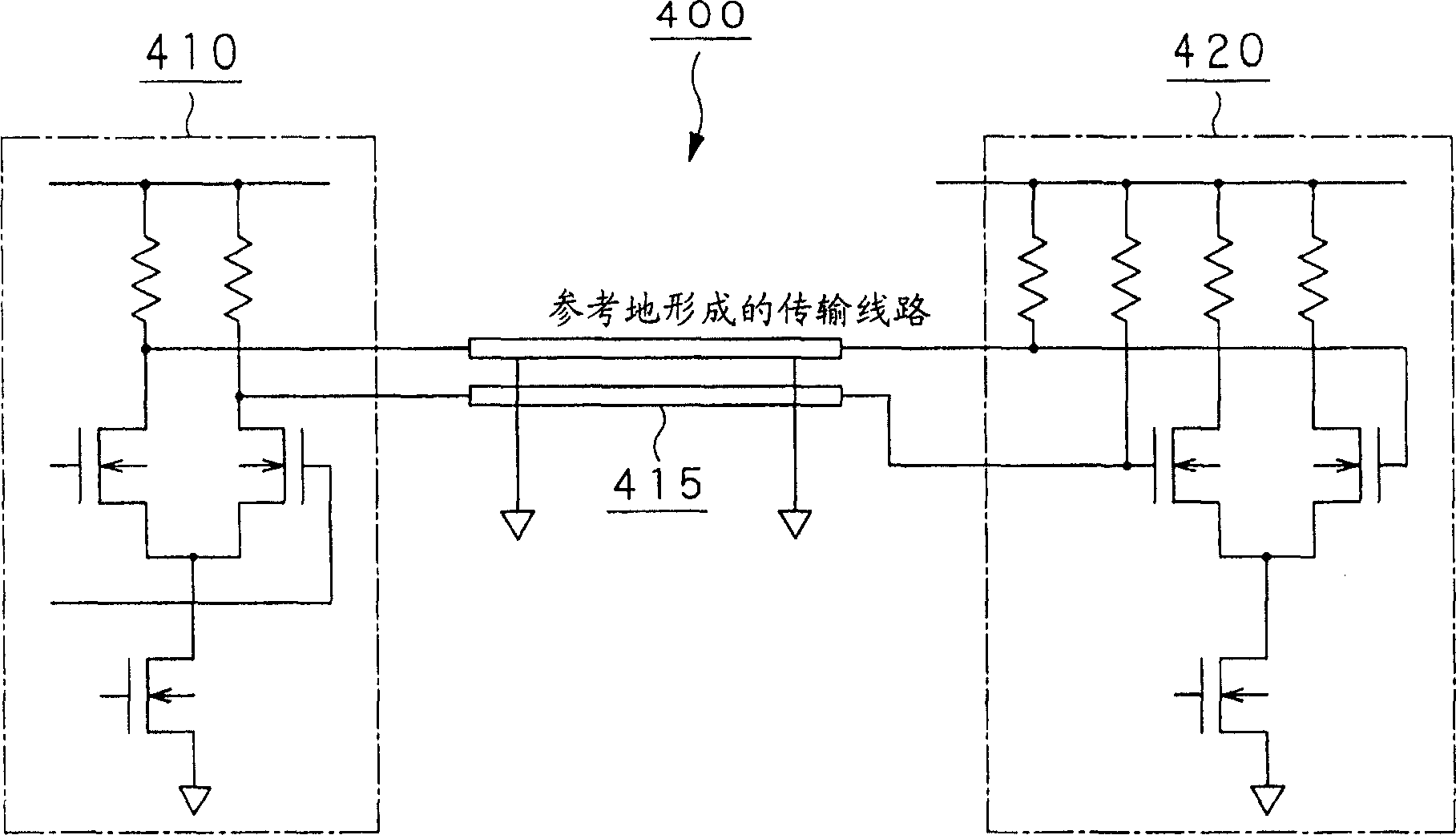

Signal transmission system, and signal transmission line

ActiveCN1617120ATransistorElectric signal transmission systemsDifferential lineDifferential signaling

Owner:大冢宽治

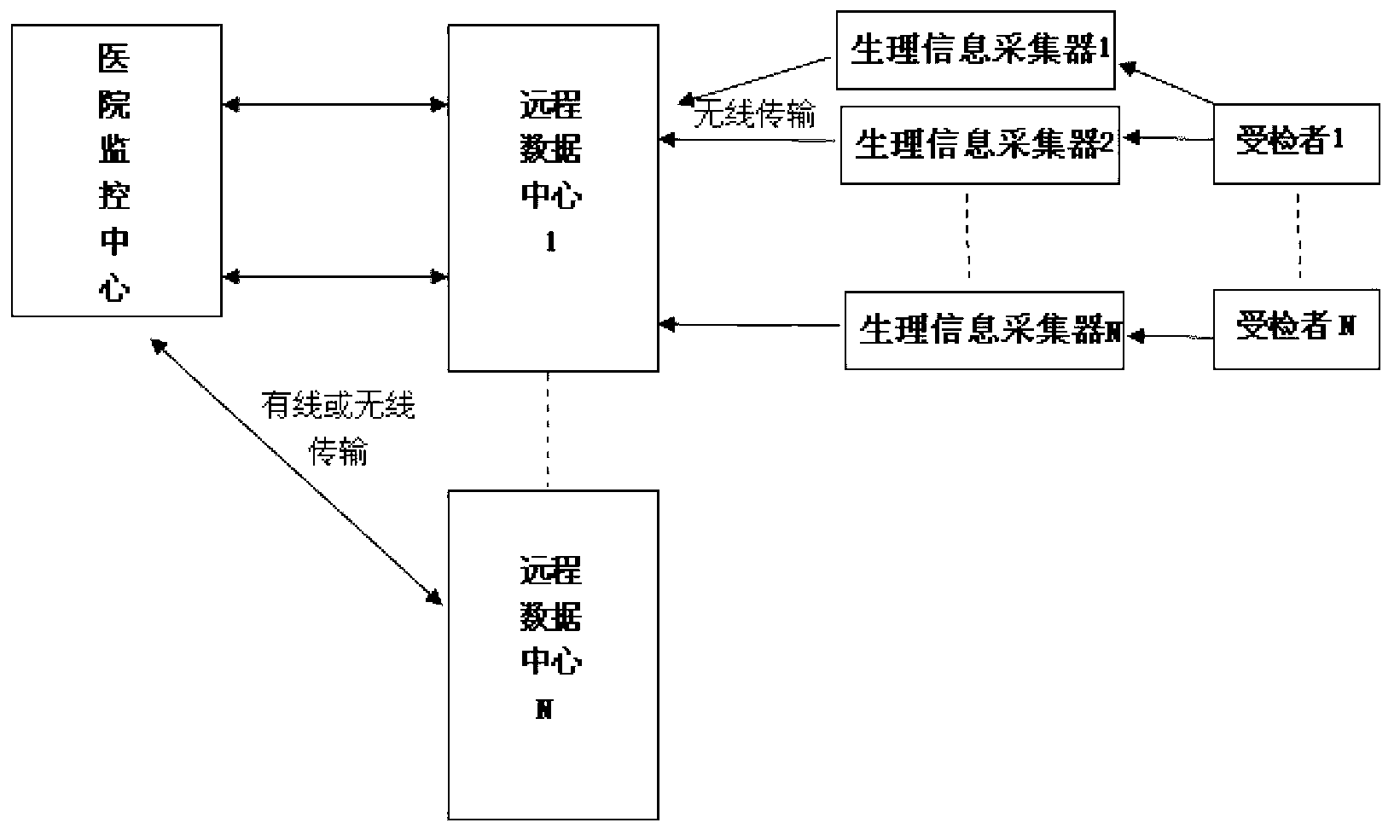

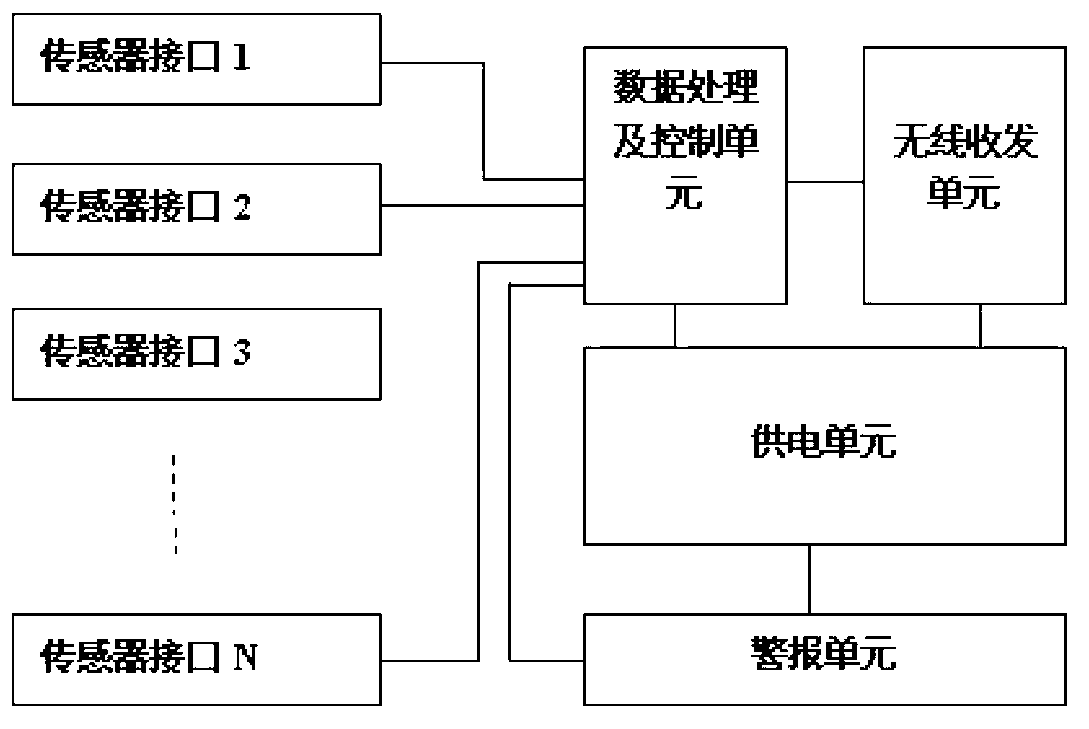

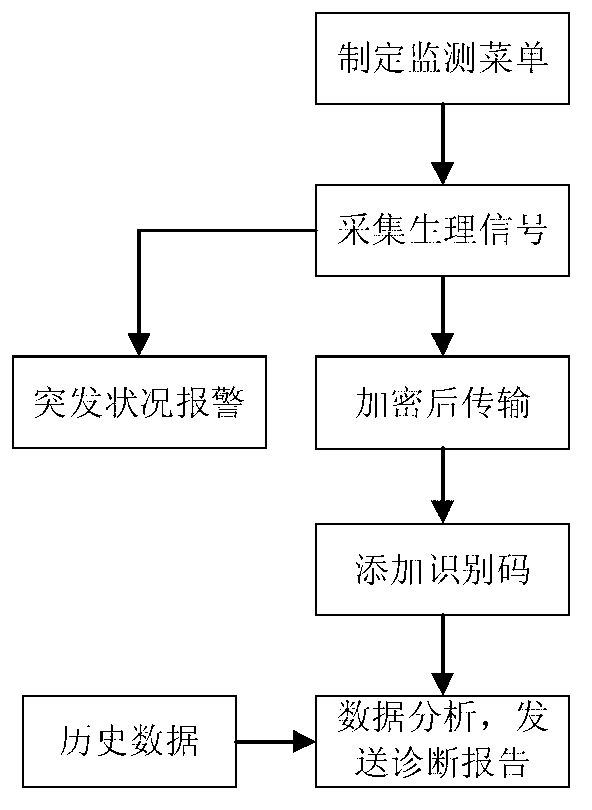

Physiological information monitoring system and monitoring method

ActiveCN103230261APrevent leakageGuarantee privacy and securityElectric signal transmission systemsSensorsMedical emergencyInformation monitoring

The invention discloses a physiological information monitoring system comprising a physiological information collector, a remote data terminal and a hospital monitoring center, wherein the physiological information collector is used for collecting a physiological signal, encrypting the collected physiological signal data and transmitting the physiological signal data to the remote data terminal, the remote data terminal is used for adding an identification code on the received physiological signal data and transmitting the physiological signal data to the hospital monitoring center, and the hospital monitoring center is used for decrypting, storing and analyzing the physiological signal data and sending a diagnostic report to the remote data terminal. The invention further provides a monitoring method. The physiological information monitoring system and the physiological information monitoring method disclosed by the invention are used for solving the problem of low privacy safety of subjects and low utilization rate of monitoring information, the collected physiological signal data are transmitted after being encrypted, thereby preventing the physiological information of the subjects from being leaked by illegal monitoring in the transmission process; and the hospital monitoring center analyzes the received data and provides the diagnostic report to provide illness condition caution to the subjects in time.

Owner:MIANYANG DEHUI AUTOMATION TECH CO LTD

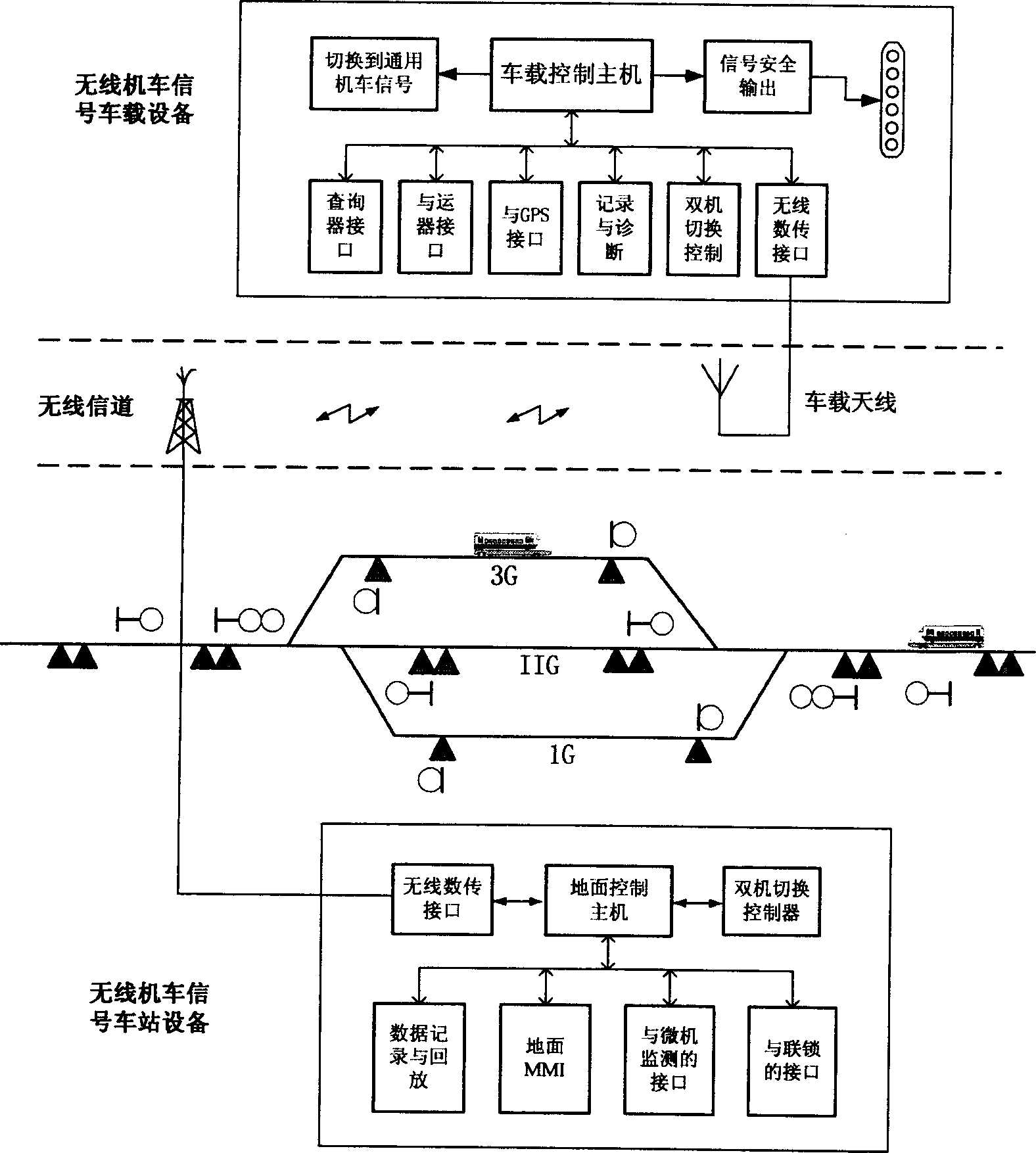

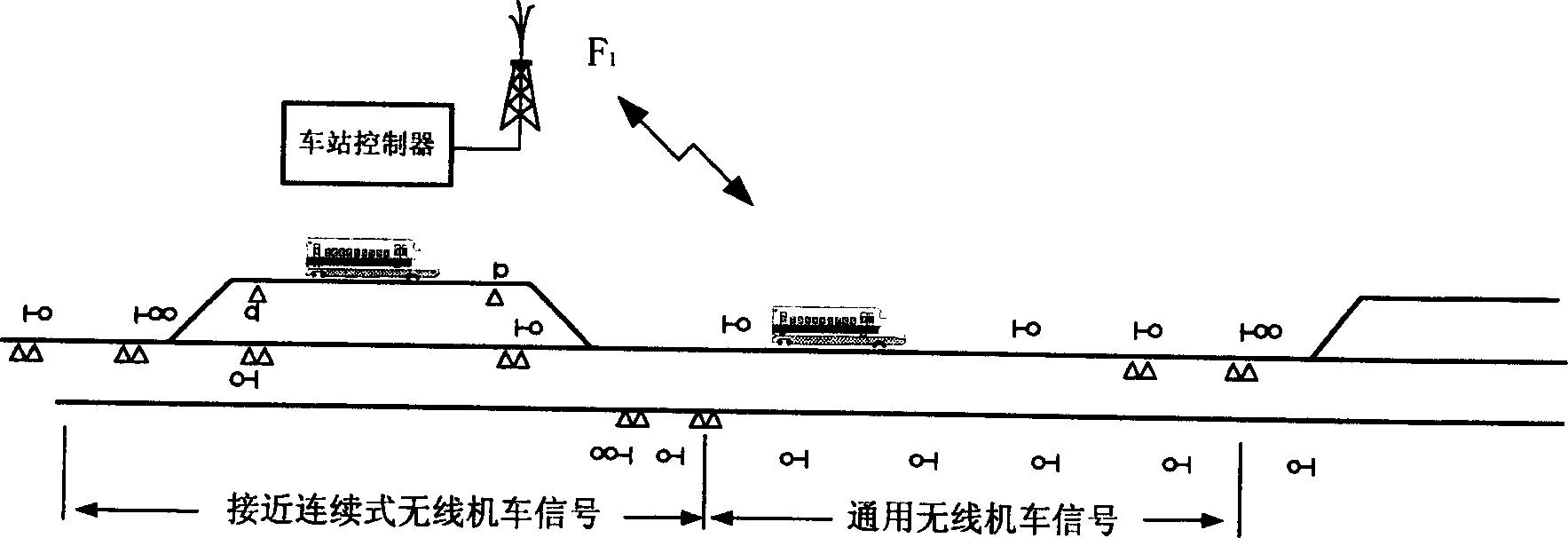

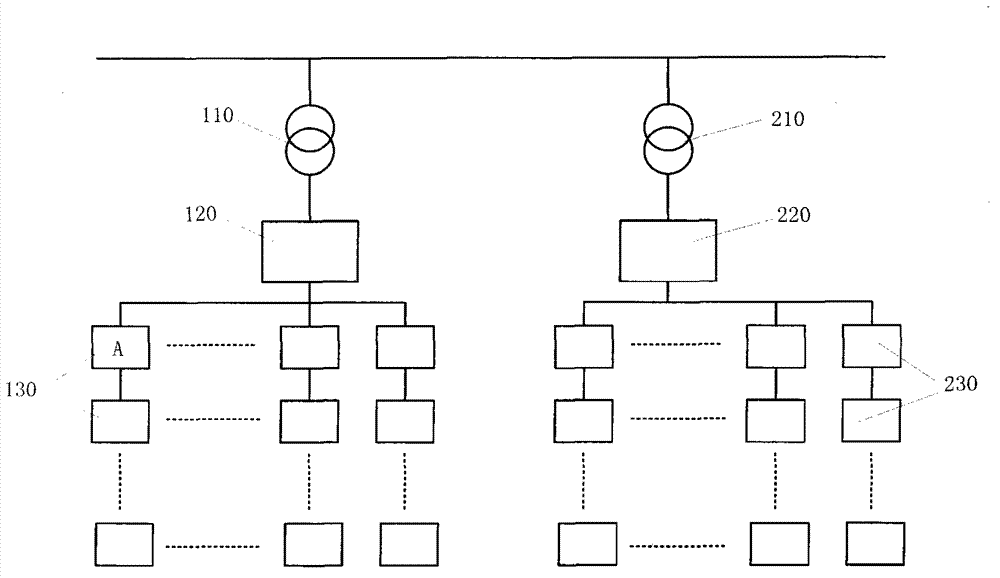

Method of realizing locomotive signal principalization using radio locomotive signal

InactiveCN1794690AA large amount of information is transmittedImprove transmission reliabilityElectric signal transmission systemsStar/tree networksTelecommunicationsComputer module

Owner:BEIJING JIAOTONG UNIV

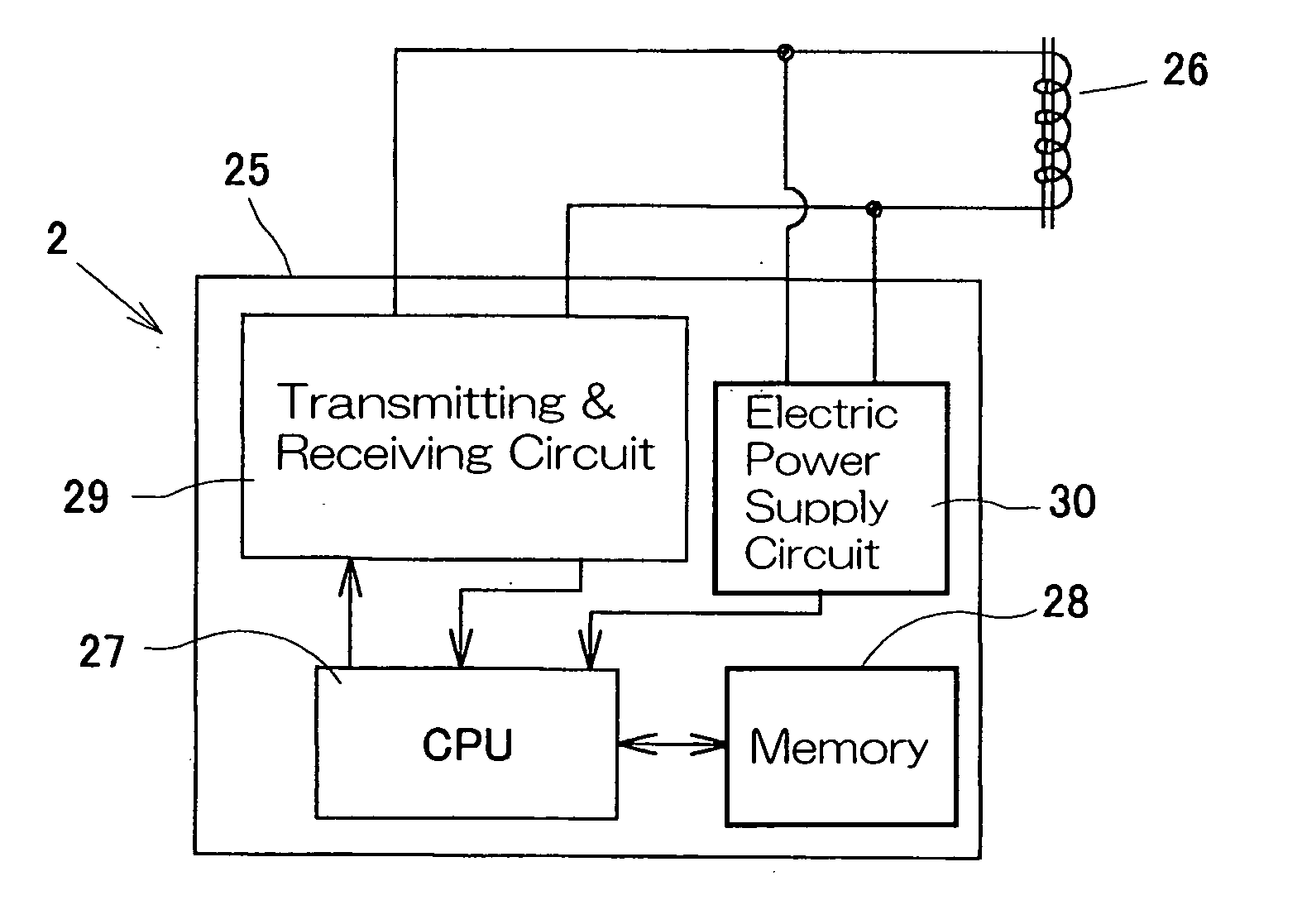

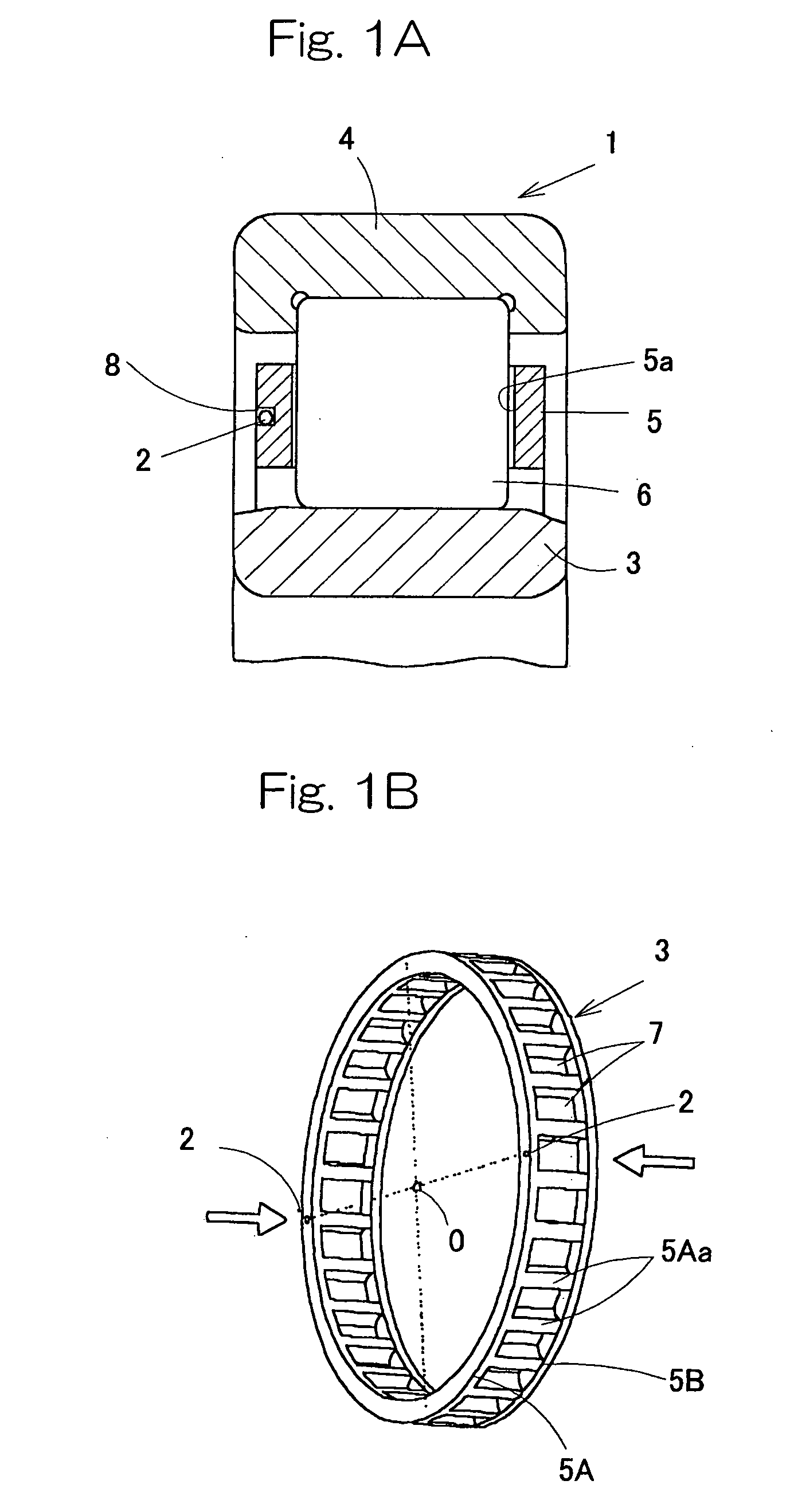

Machine element part with ic tag

InactiveUS20060289620A1Increase storage capacityAvoid disruptionElectric signal transmission systemsRoller bearingsElectrical and Electronics engineering

Owner:NTN CORP

Credit card verification system and method

InactiveUS6912312B1Accurate comparisonElectric signal transmission systemsImage analysisCredit cardCommunication unit

The invention provides a credit card verification system, including a credit card company data storage and communication unit (4) for recording and storing data concerning authorized credit card holders, including an electronically reproducible image of each credit card holder, means (6) for introducing the image into the company data storage unit, and at least one remotely positioned credit card reader (10) and image display meants (12) communicating with the company data storage unit, for selectively retrieving data from the storage unit to be displayed on the image display means, to be viewed and approved by the person providing sales services. The invention also provides a method for verifying the identity of a credit card holder effecting a tansaction and a method enabling credit companies to monitor and verify credit card holder identity when a payment transaction is performed at a sales terminal.

Owner:CALLAHAN CELLULAR L L C

Digital to analog converter

ActiveUS6992609B1Electric signal transmission systemsDigital-analogue convertorsDigital analog converterSubject matter

The present invention provides a high speed digital-to-analog converter (DAC), and components for a high speed DAC. One embodiment of the present invention provides a novel current switching circuit that surmounts parasitic capacitance of the circuit elements. In another embodiment, the DAC includes a novel built-in-test circuit, which allows tests of the DAC at high speeds. One feature of the DAC constructed according to the present invention, is that it enables direct digital synthesis of communication waveforms. This Abstract is provided for the sole purpose of complying with the Abstract requirement rules that allow a reader to quickly ascertain the subject matter of the disclosure contained herein. This Abstract is submitted with the explicit understanding that it will not be used to interpret or to limit the scope or the meaning of the claims.

Owner:NVIDIA CORP

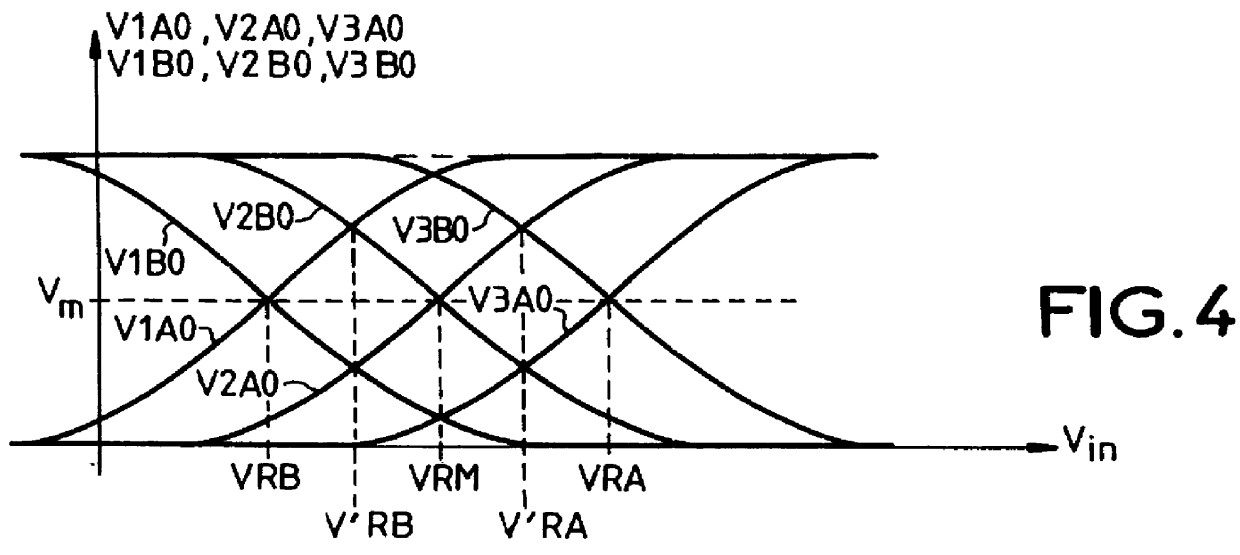

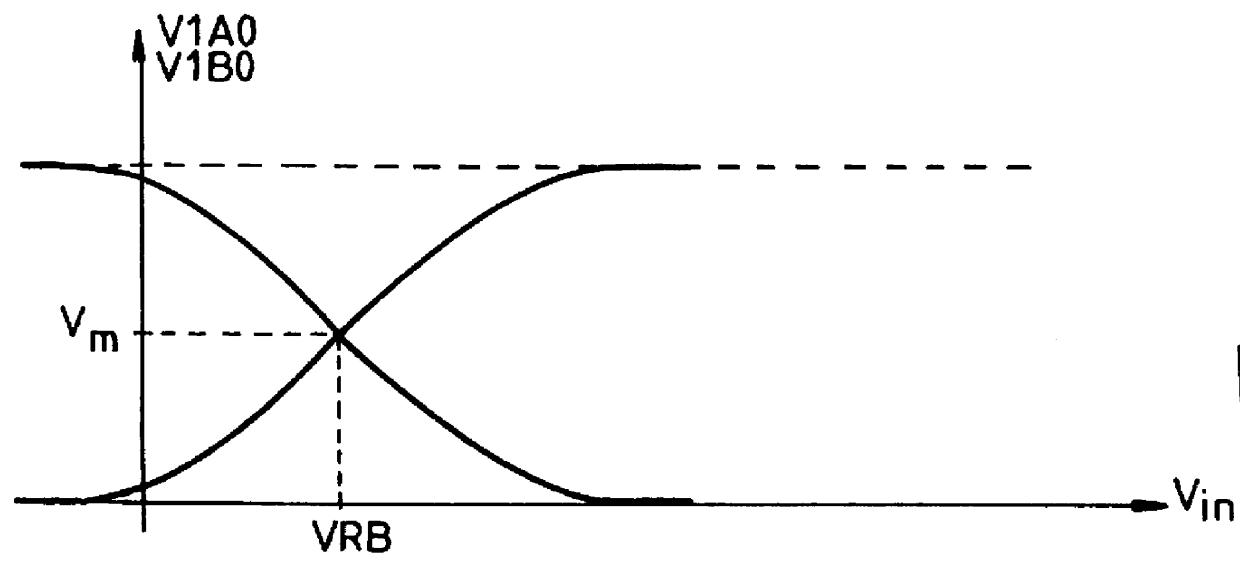

Analog to digital converter using several cascade-connected interpolation circuits

InactiveUS6166674AElectric signal transmission systemsAnalogue-digital convertersA d converterDigital conversion

Owner:THOMSON CSF SA

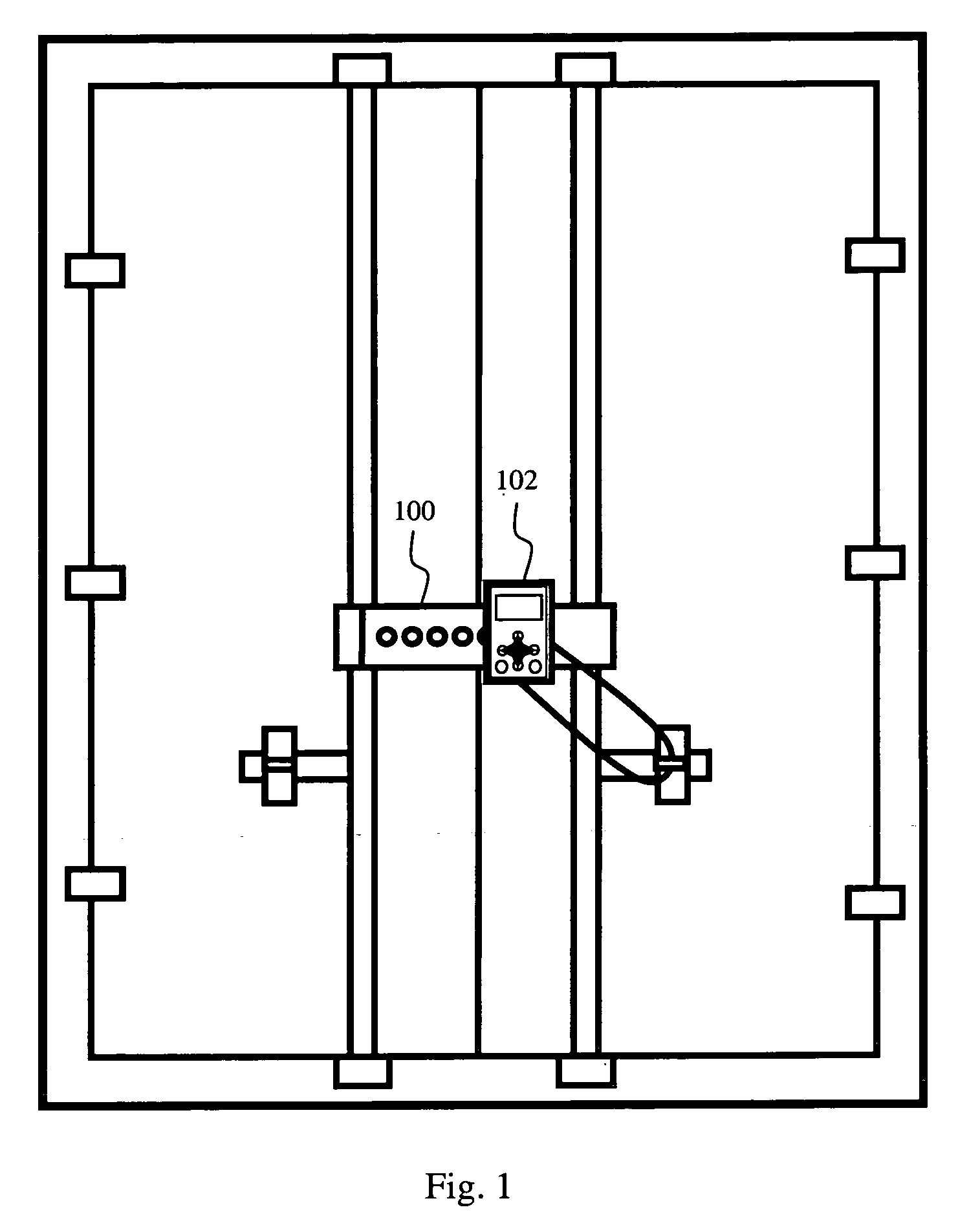

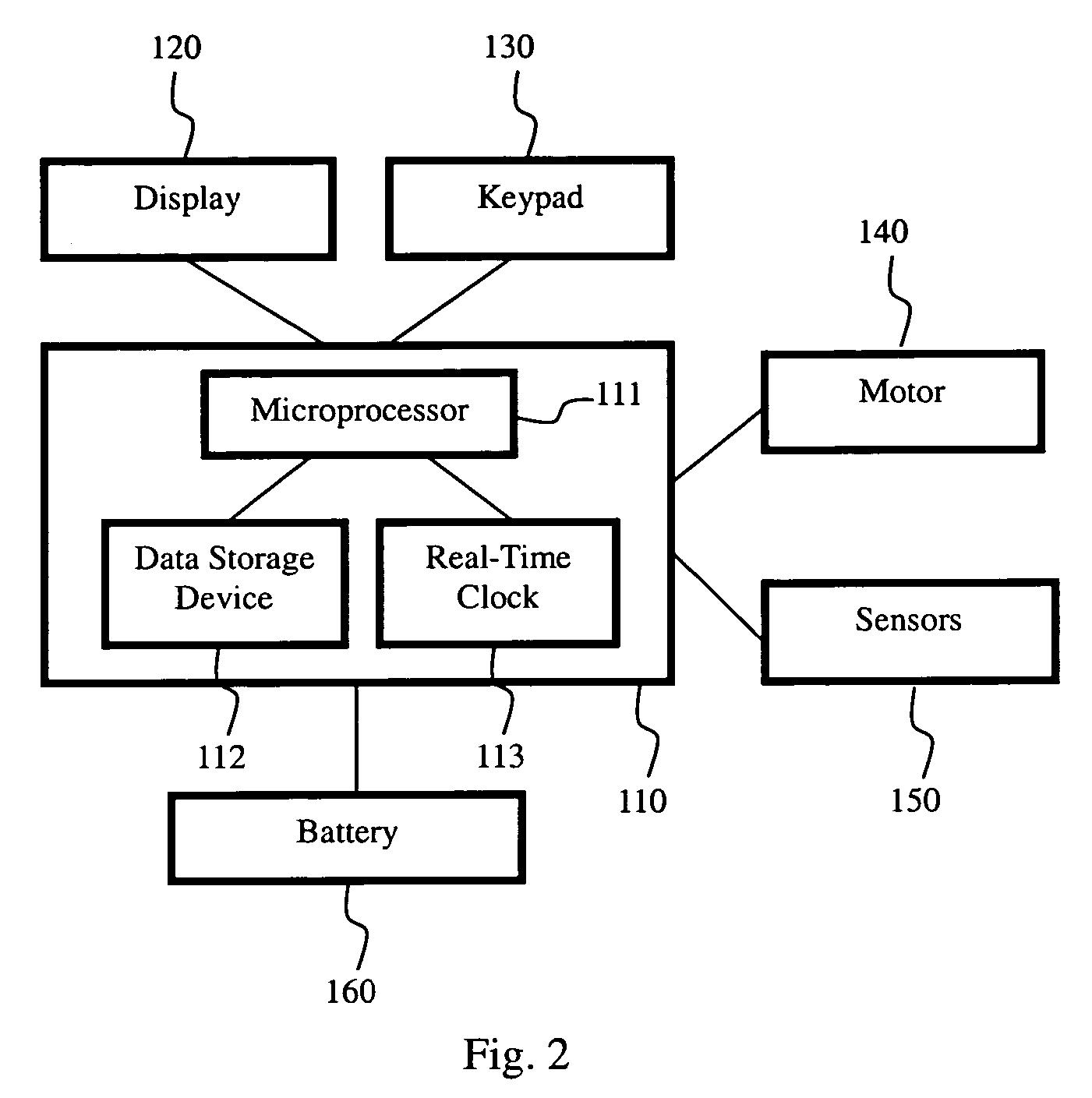

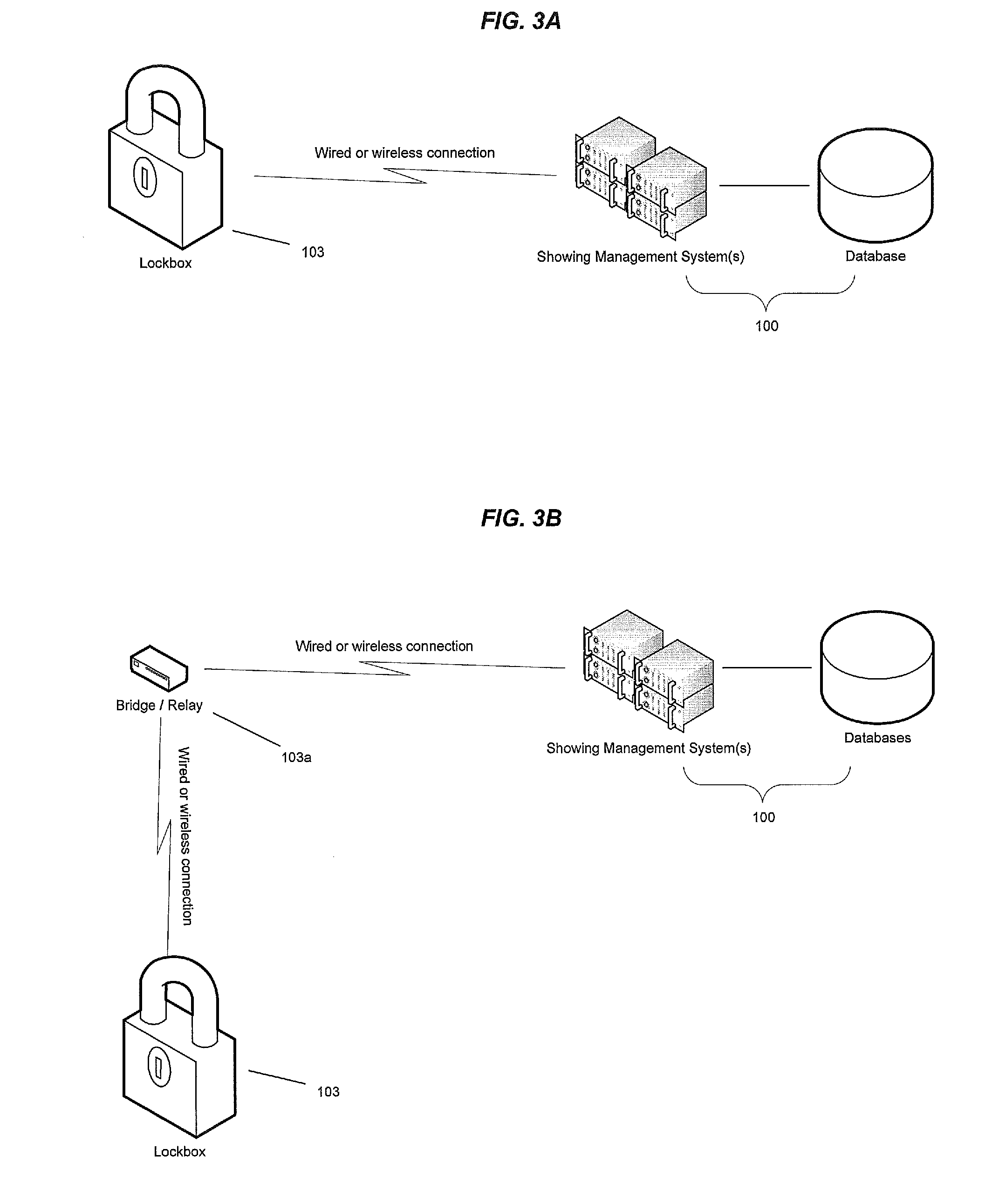

Showing management system to automatically match and control electronic lockboxes

ActiveUS20090219133A1Limited accessProgramme controlElectric signal transmission systemsAutomatic controlAccess time

Owner:MFTB HOLDCO INC

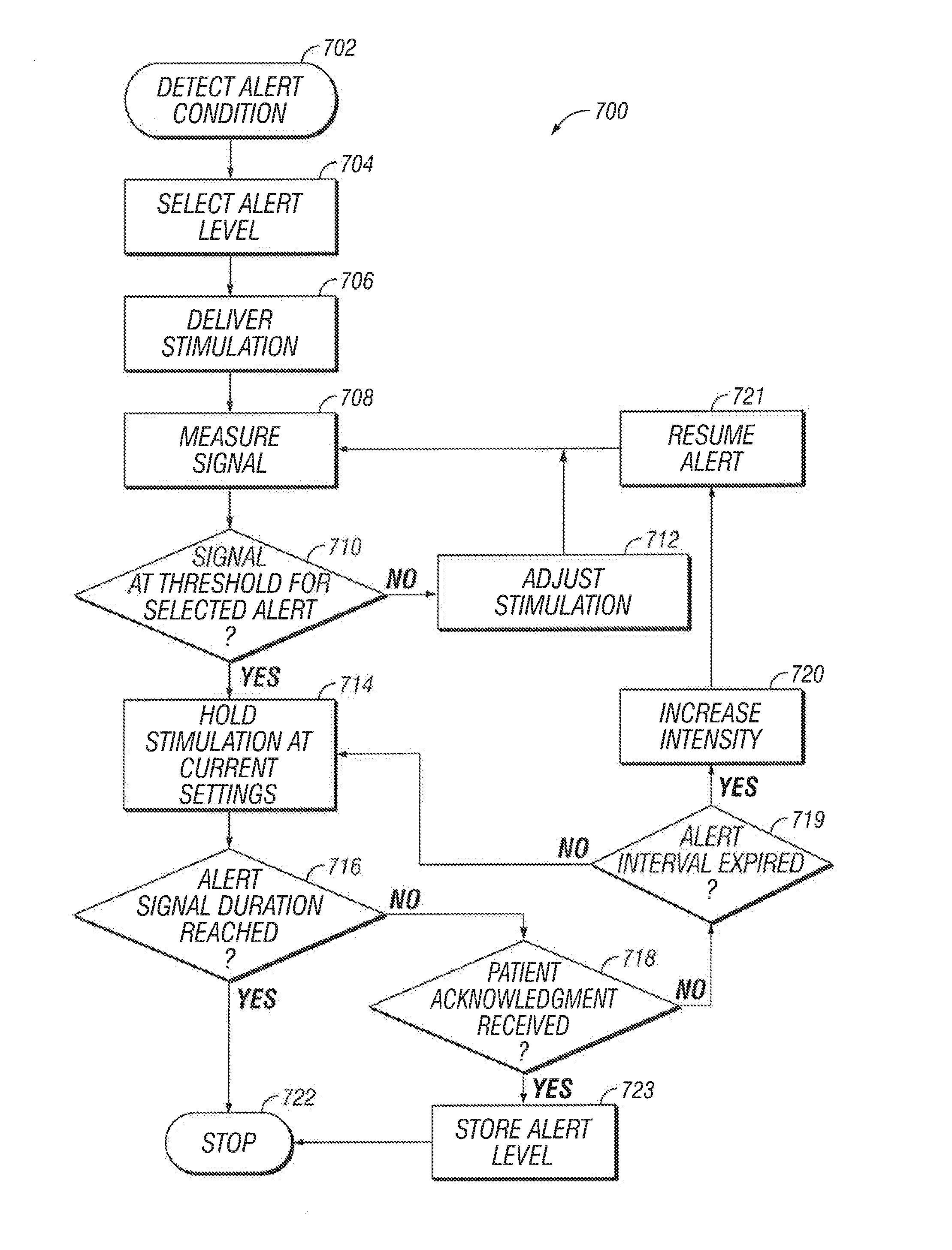

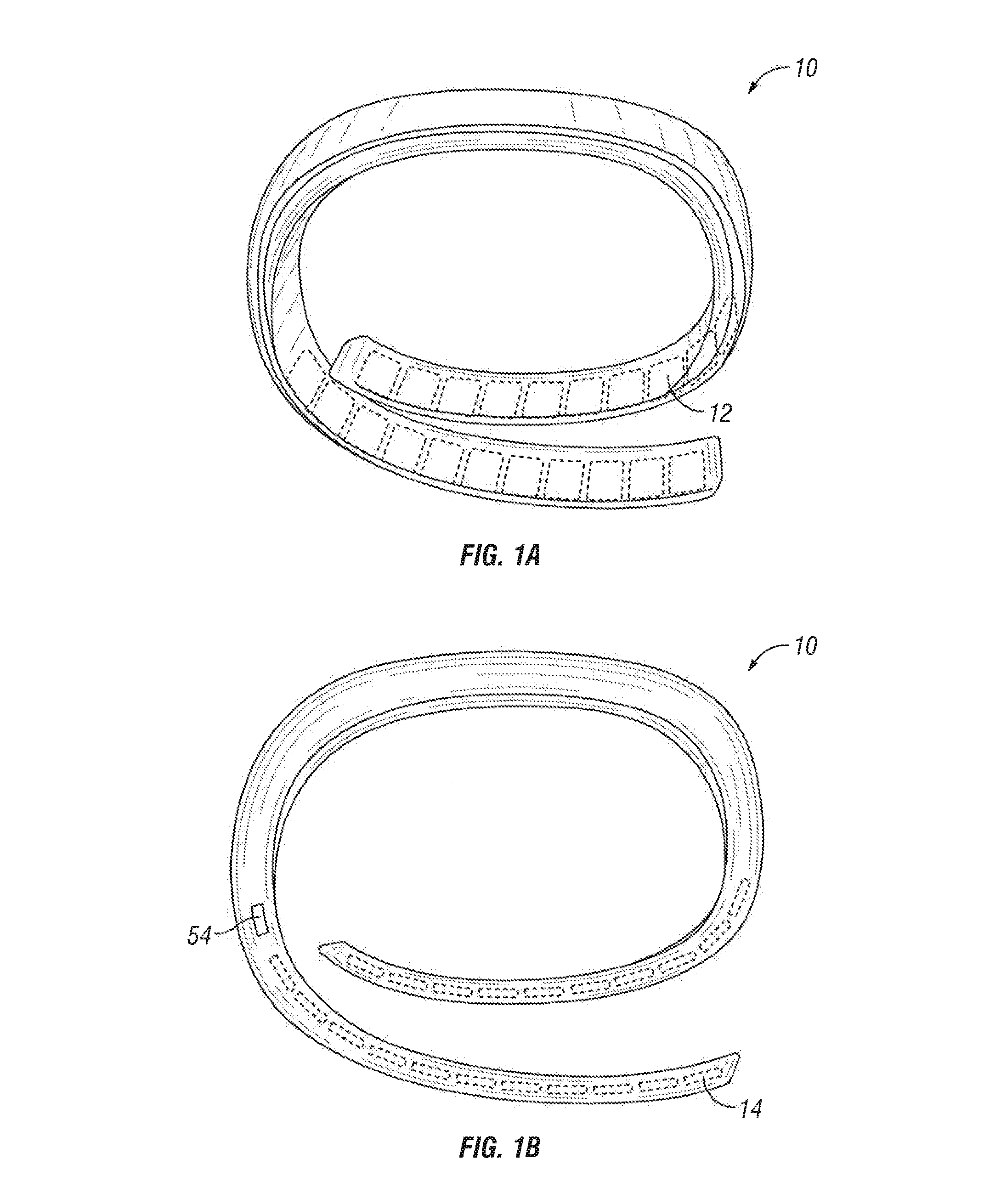

User or patient monitoring methods using one or more analysis tools

ActiveUS20140247156A1Electric signal transmission systemsTelephonic communicationTelemetry EquipmentReal-time computing

Owner:FITBIT INC

Neuromorphic calculation circuit based on multi-bit parallel binary synaptic array

ActiveCN110378475AReduce power consumptionReduce areaAnalogue/digital conversionElectric signal transmission systemsIntegratorHigh energy

The invention discloses a neuromorphic calculation circuit based on a multi-bit parallel binary synapse array. The neuromorphic calculation circuit comprises a neural axon module, the multi-bit parallel binary RRAM synapse array, a time division multiplexer, a plurality of integrators and a shared successive approximation analog-to-digital converter, wherein the neural axon module comprises two basic units, namely a time sequence scheduler and an adder, and the time sequence scheduler is used for arranging the time sequence of signals, so that input signals are sequentially input into a multi-bit parallel binary RRAM synapse array by adopting a dendritic priority strategy; the adder is used for expanding the array scale, and when the configured neural network input layer is greater than the input of one RRAM array, the adder is used for adding the calculation results of the plurality of arrays to obtain the output of the network layer. Compared with the current system, the method has the advantages of high precision and low power consumption, can be configured into most deep neural network applications, and is particularly suitable for being deployed in edge computing equipment with high energy consumption requirements.

Owner:ZHEJIANG UNIV

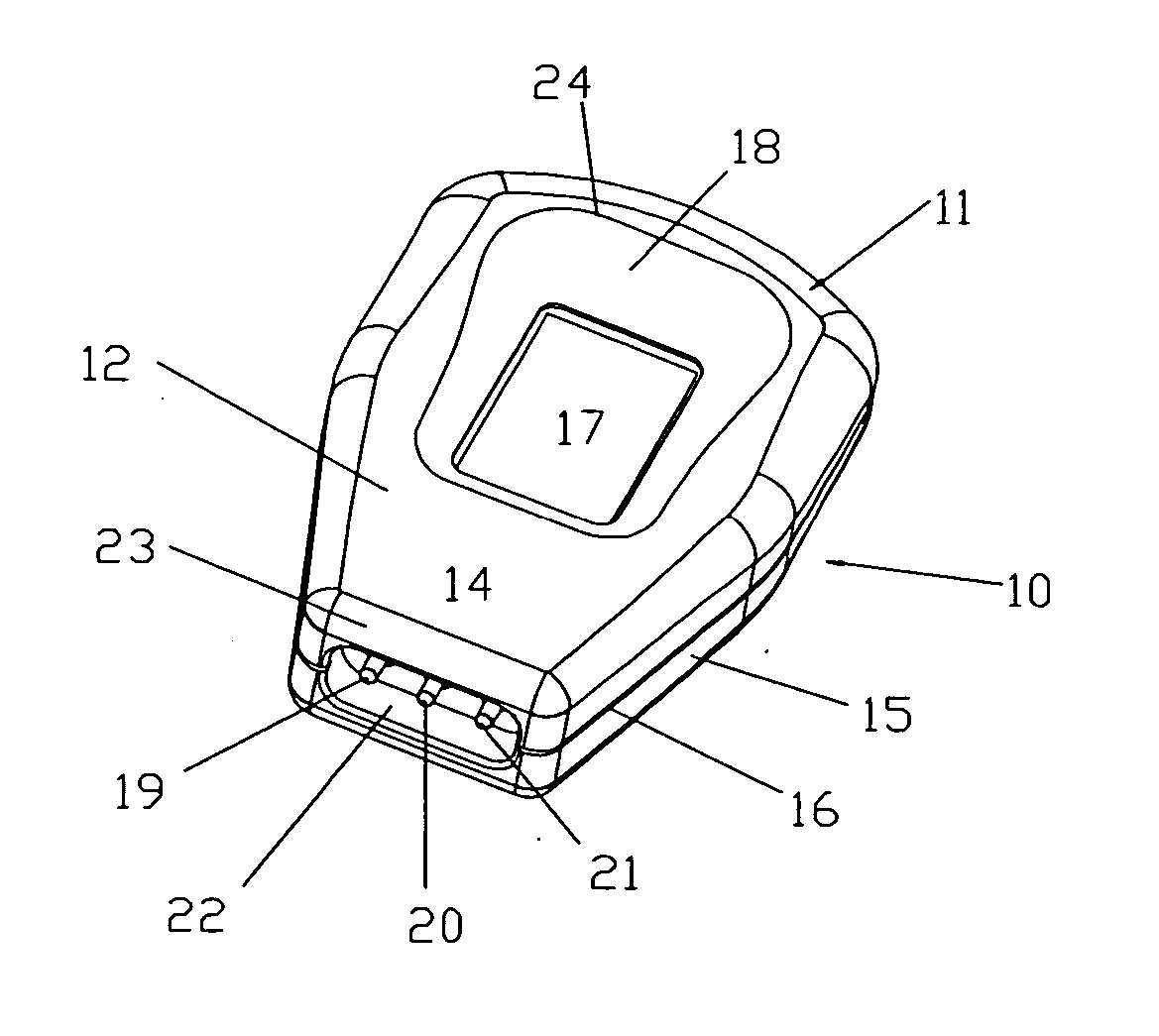

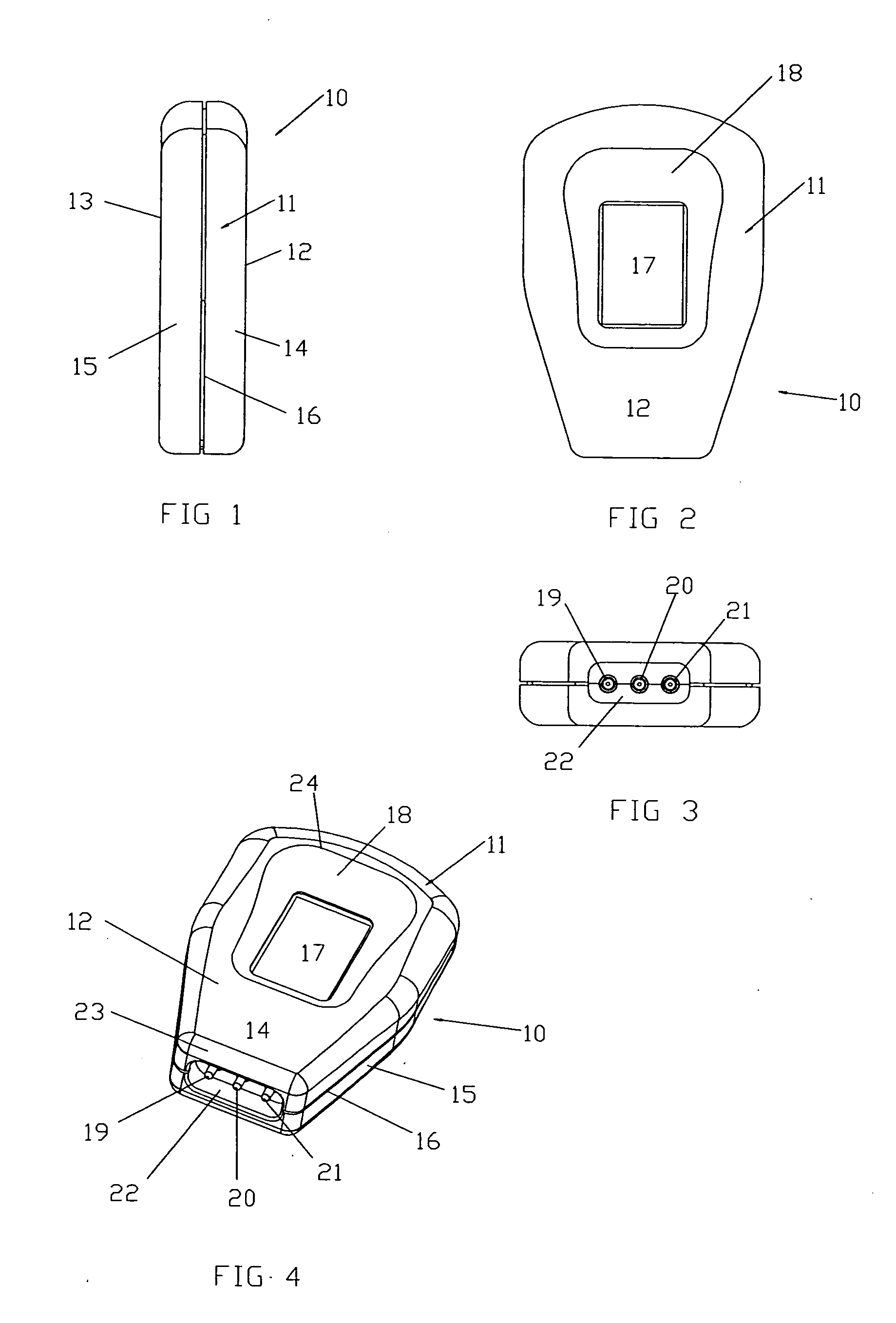

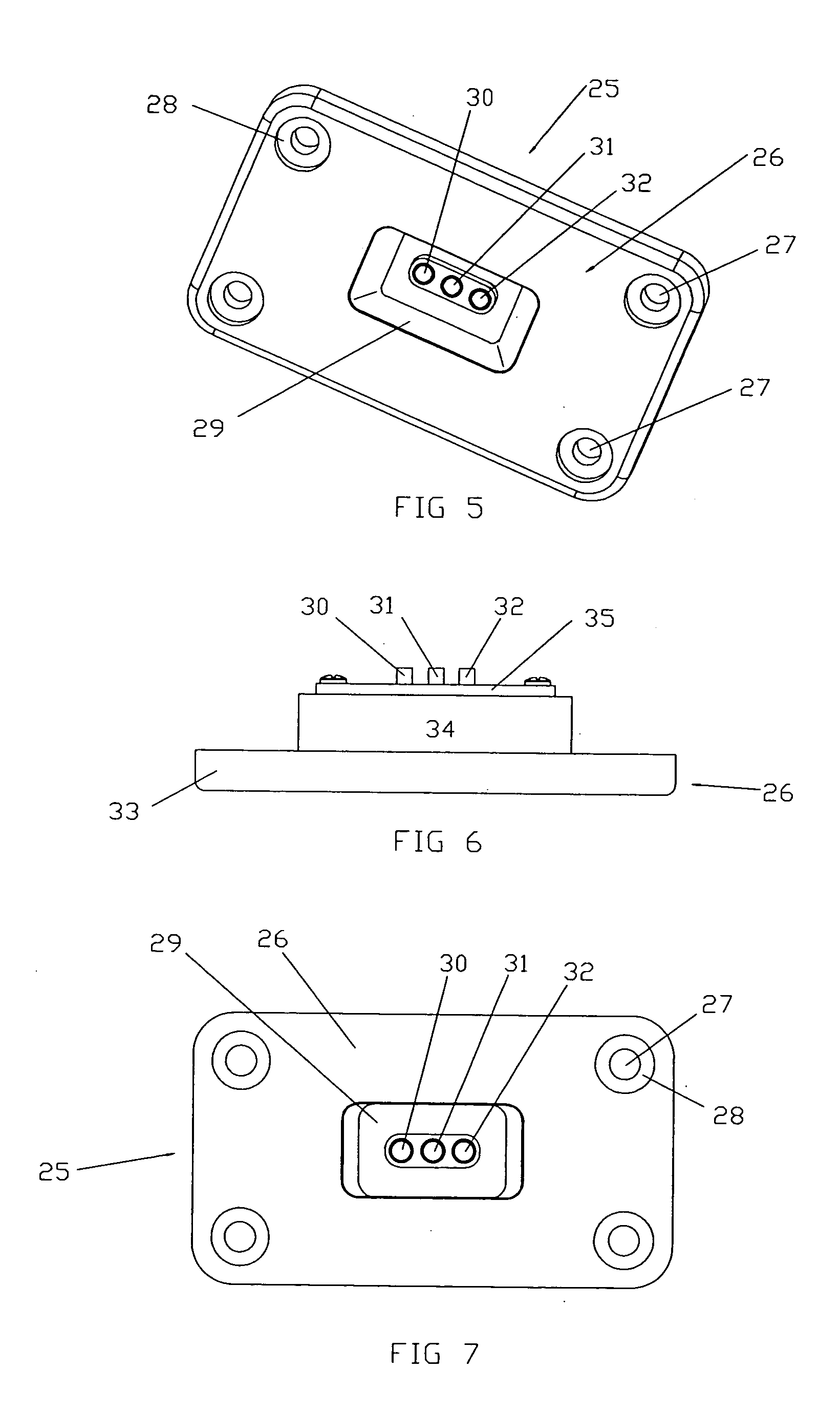

Biometric security assembly

InactiveUS20050182947A1Limited supplyNot to damageElectric signal transmission systemsDigital data processing detailsEngineeringBiometric data

A biometric key (10) having a body or housing (11) incorporating a biometric sensor (17) uses a plurality of contacts (19, 20, 21) enabling the key to gain access to a facility. There is also provided a receptor (25) for receiving the biometric key (10), wherein the biometric key (10) and receptor (24) have contacts (19, 20, 21) and mating contacts (30, 31, 32), respectively, for communicating. The biometric key (10) can communicate biometric data acquired from a key operator to the receptor (25). The biometric key (10) can communicate with the receptor (25) when received in a first orientation and also when received in a second orientation where the contacts (19, 20, 21) are inverted from the first orientation.

Owner:MU HUA INVESTMENT

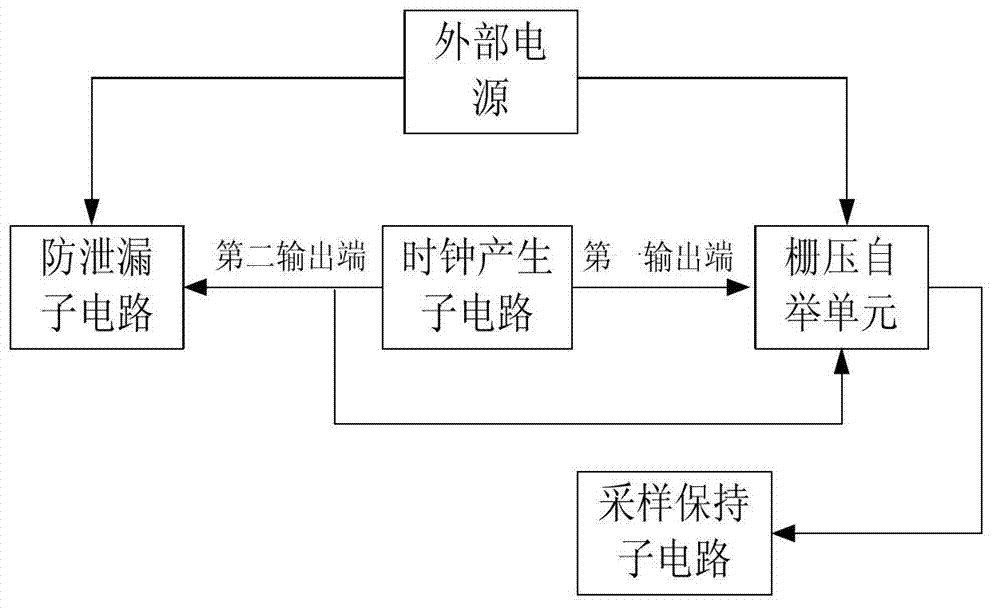

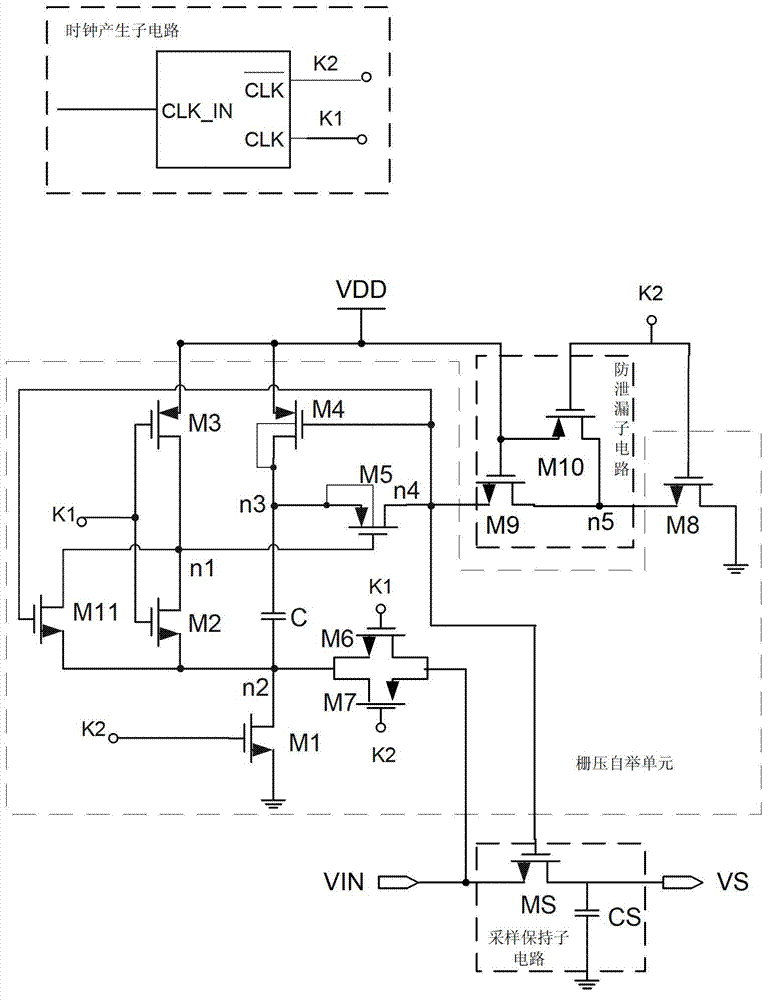

Sampling hold circuit

InactiveCN103036569ALeak won'tImprove linearityAnalogue/digital conversionElectric signal transmission systemsCapacitanceLinearity

Owner:IPGOAL MICROELECTRONICS (SICHUAN) CO LTD

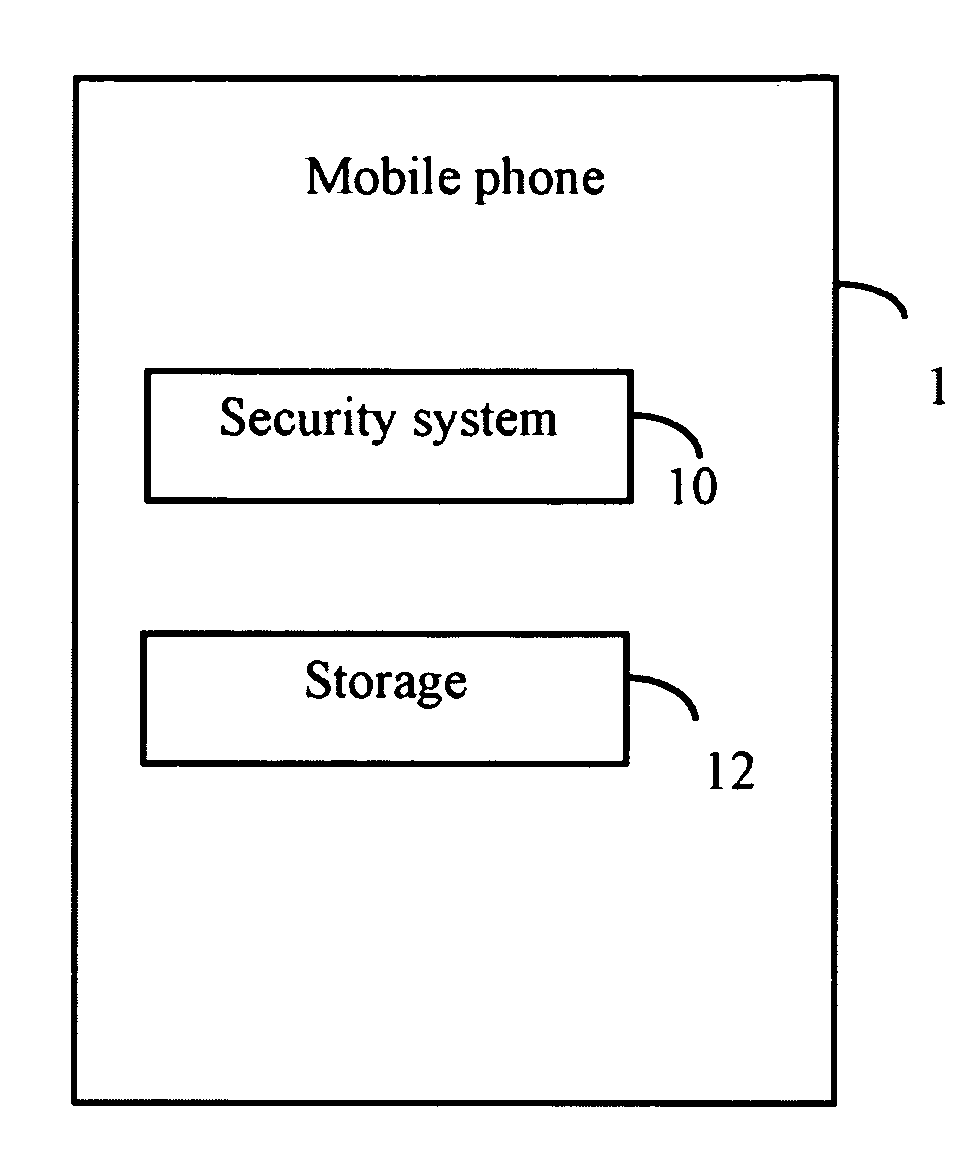

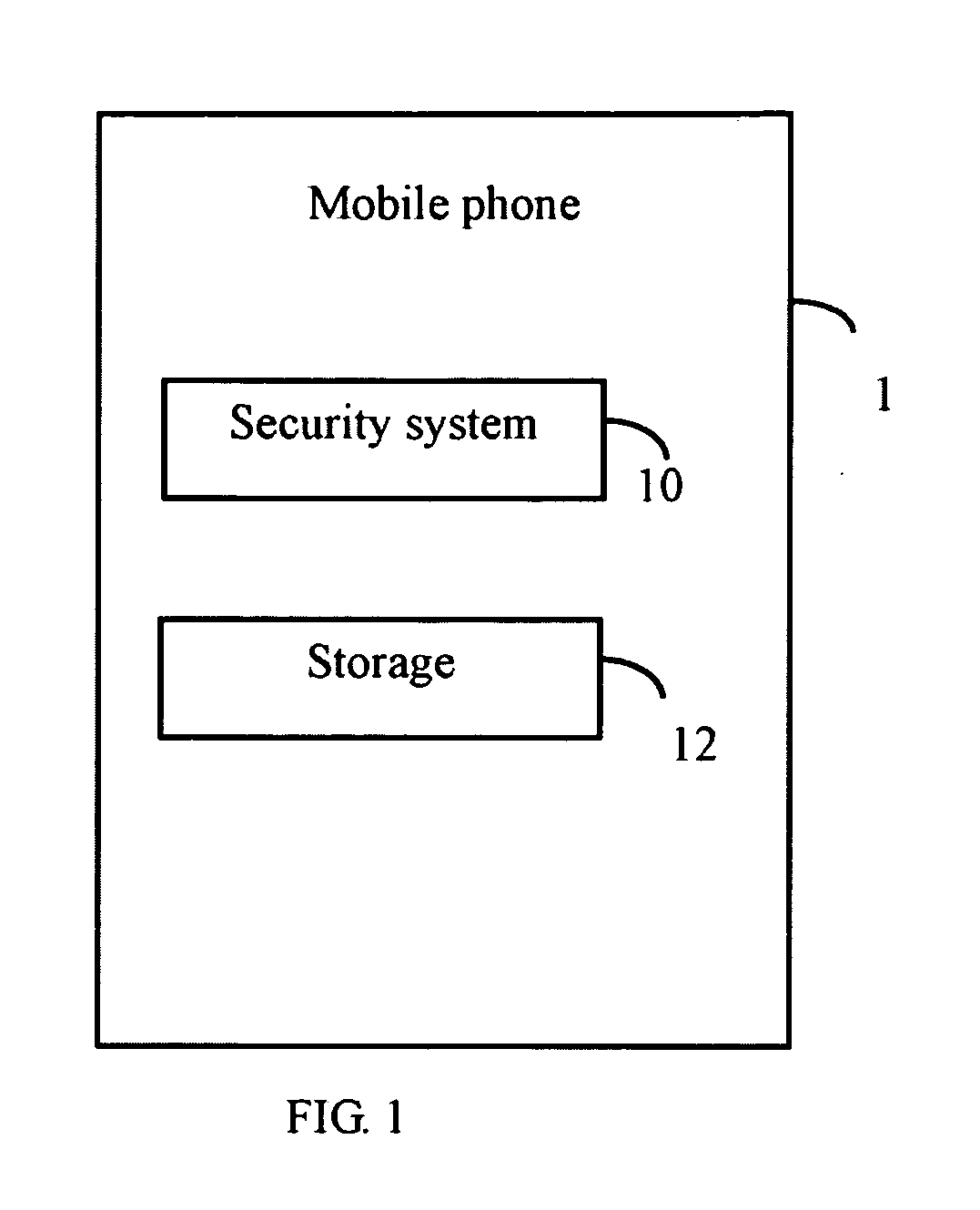

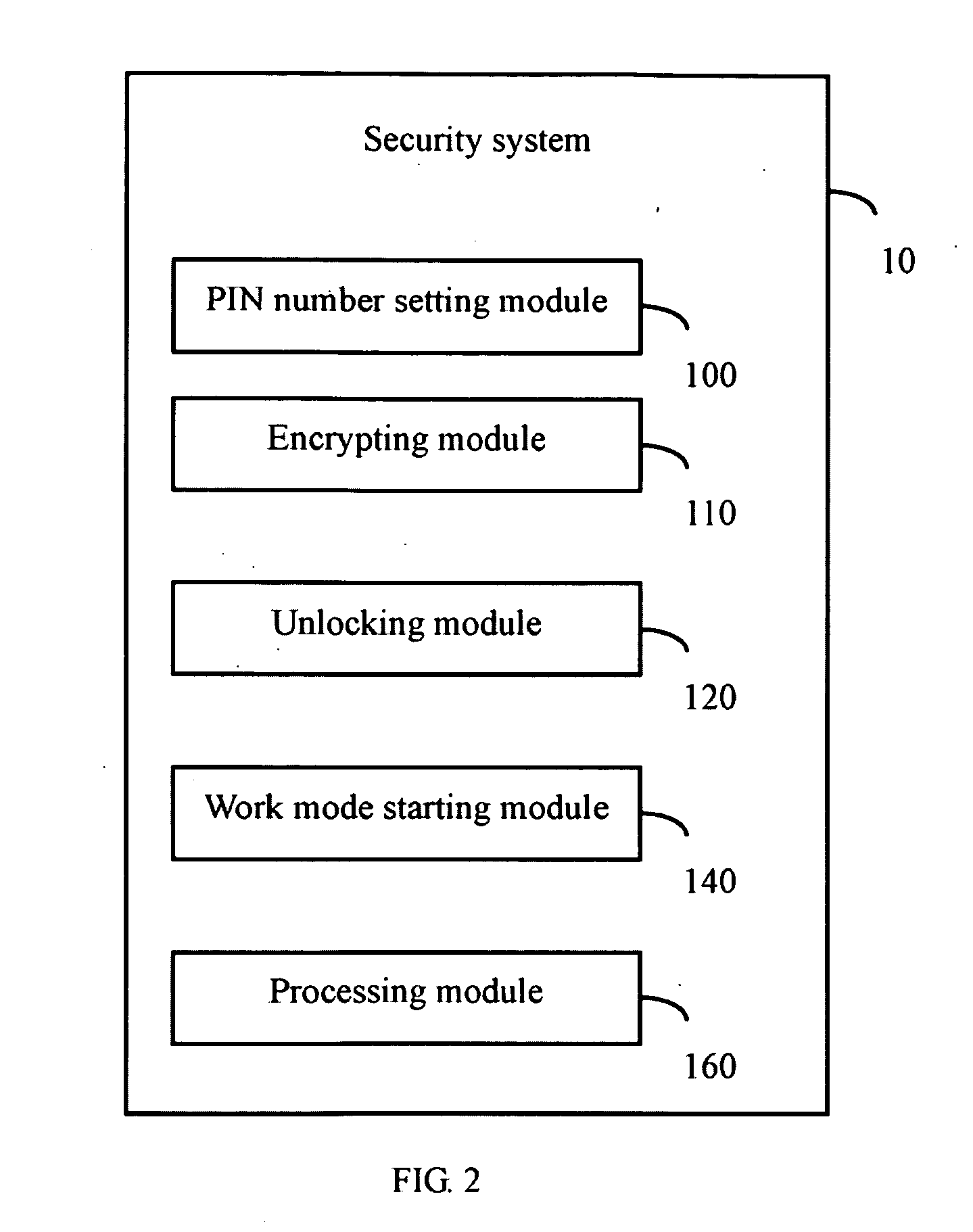

Security system and method for a mobile phone

InactiveUS20090098856A1Satisfies needElectric signal transmission systemsUnauthorised/fraudulent call preventionPower userMobile phone

Owner:CHI MEI COMM SYST INC

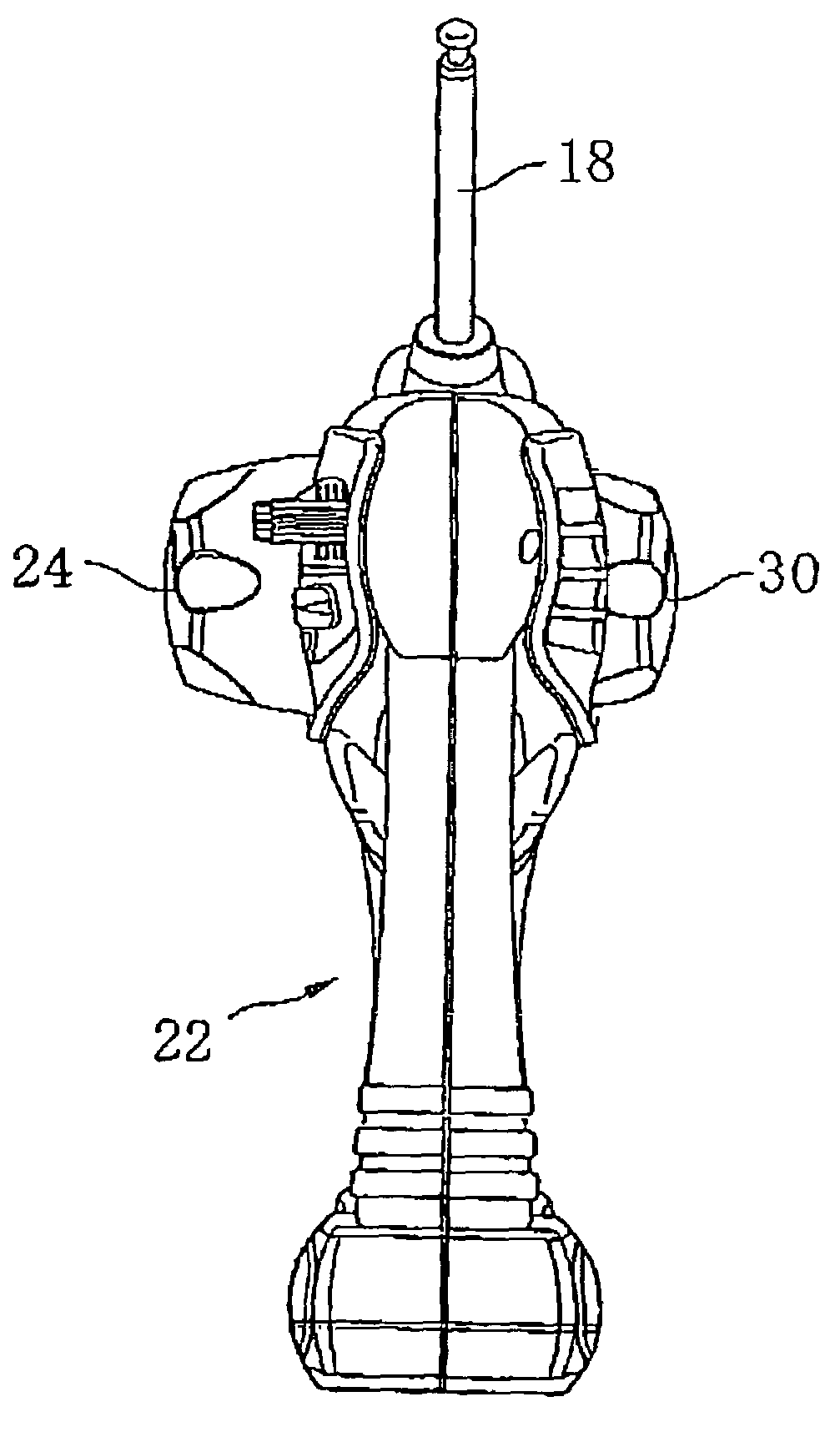

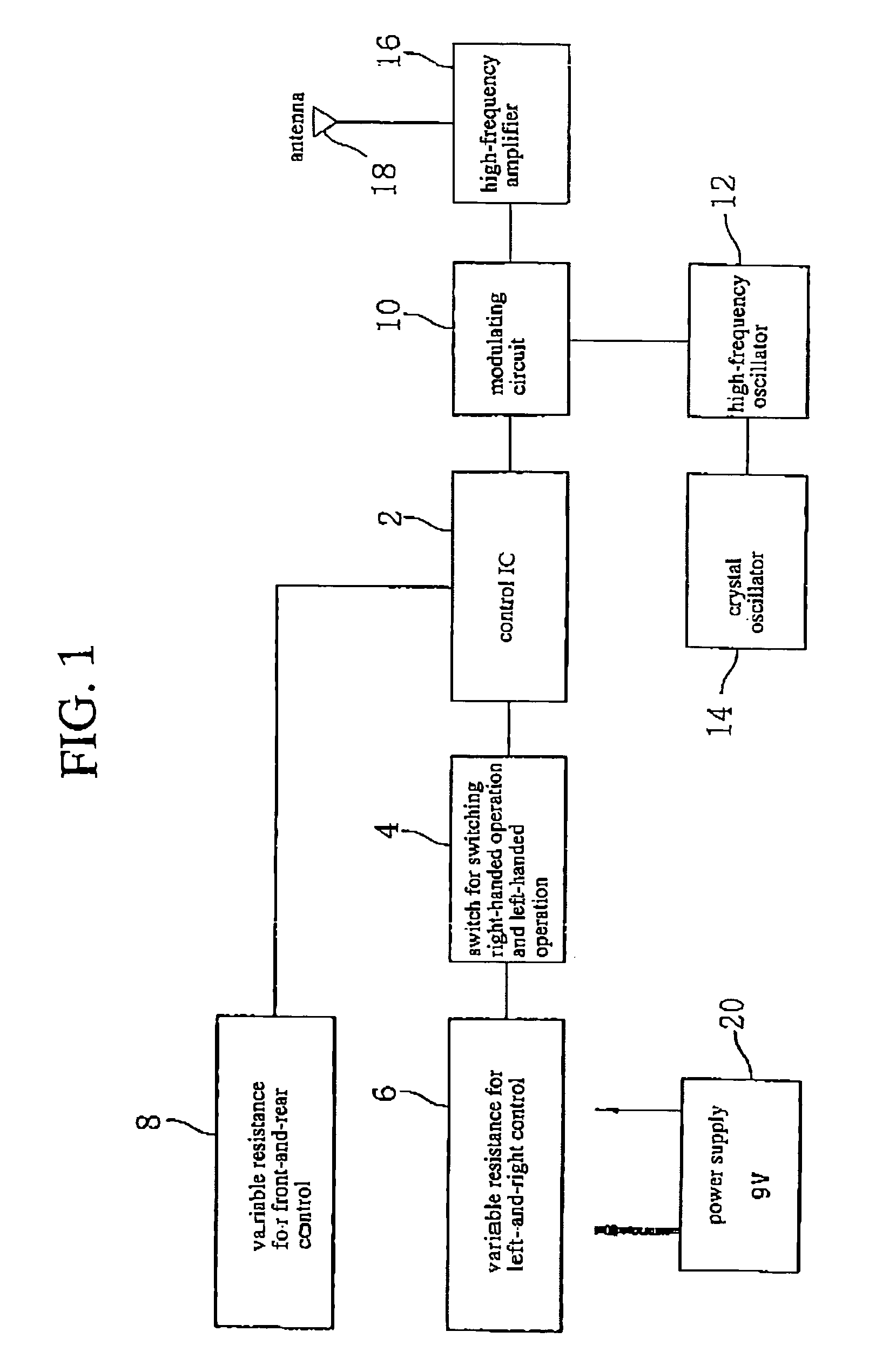

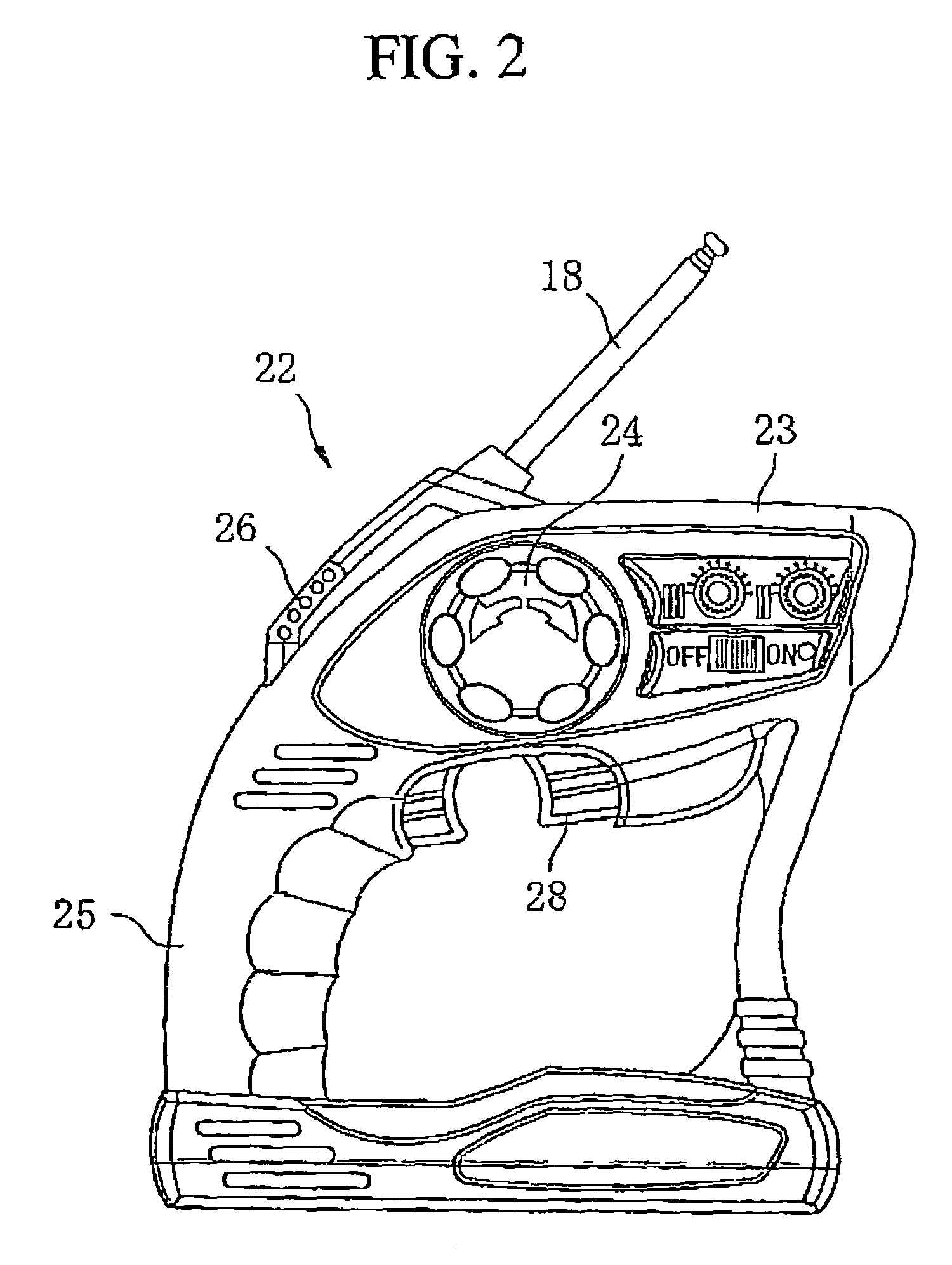

Transmitter for radio control

InactiveUS7202806B2Avoid relative motionElectric signal transmission systemsEqual length code transmitterRotation controlTransmitter

Owner:NDC CORPORATION

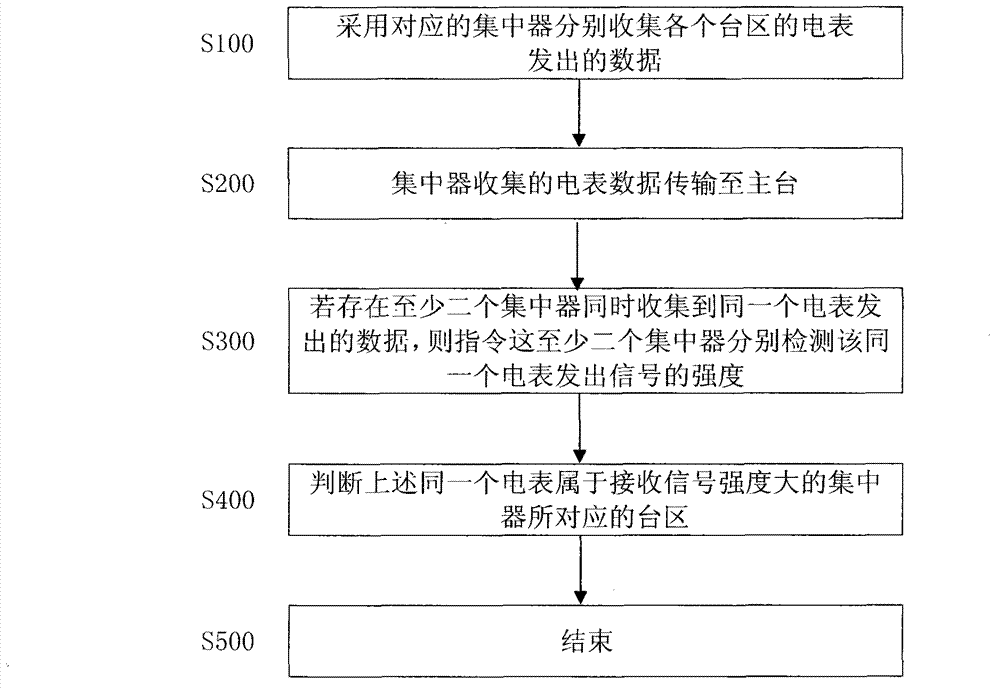

Method and device for determining region of ammeter by detecting signal intensity

InactiveCN103310623AElectric signal transmission systemsTransmission noise suppressionData transmissionAutomatic meter reading

Owner:BEIJING XIAOCHENG TECH CO LTD

System and method for measuring a high speed signal

ActiveUS20050013355A1Transmitters monitoringElectric signal transmission systemsVoltage generatorFall time

An apparatus is provided for measuring an output of a high-speed data transmission circuit. The apparatus includes a programmable reference voltage generator operable to generate a reference voltage that is variable between a plurality of levels. The apparatus also includes a quantizer to quantize an output of the high-speed data transmission circuit relative to the reference voltage level input thereto. Also included is a clock generator operable to generate a clock having a transitioning time (rise-time, fall-time or both) that is less than one quarter of a minimum switching period of the output of the circuit. Finally, the apparatus includes a sampler operable to sample the quantized output with the clock to produce a plurality of samples which measure the output of the circuit.

Owner:MARVELL ASIA PTE LTD

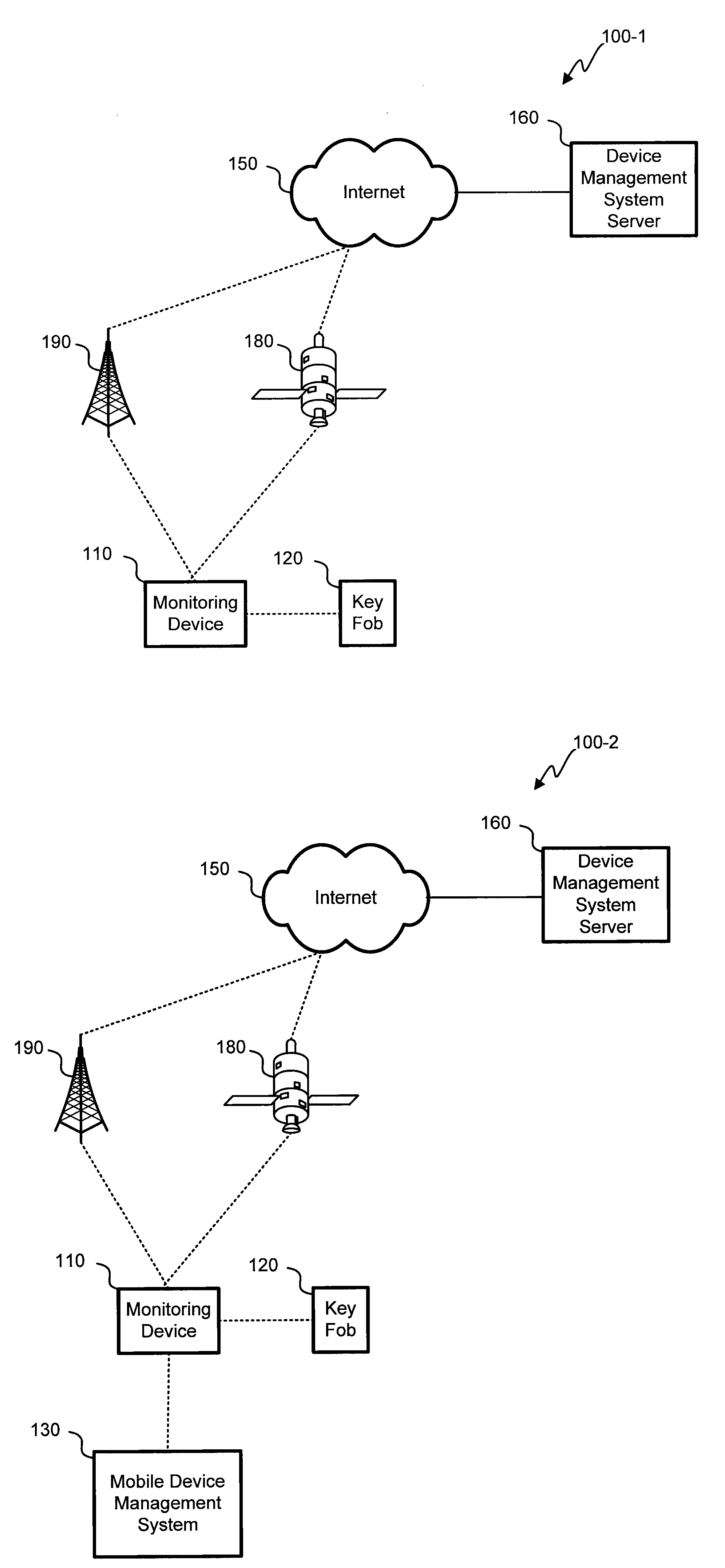

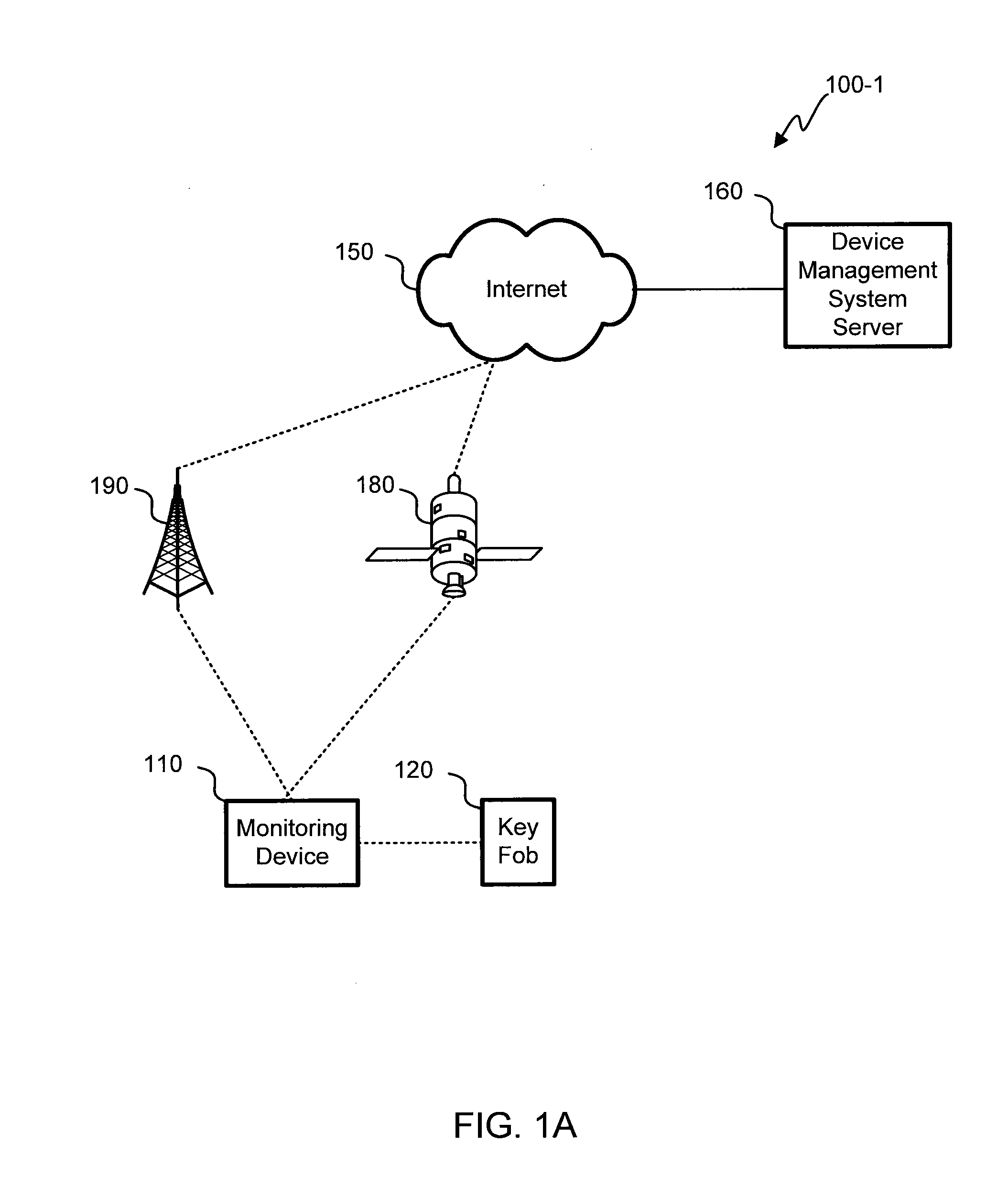

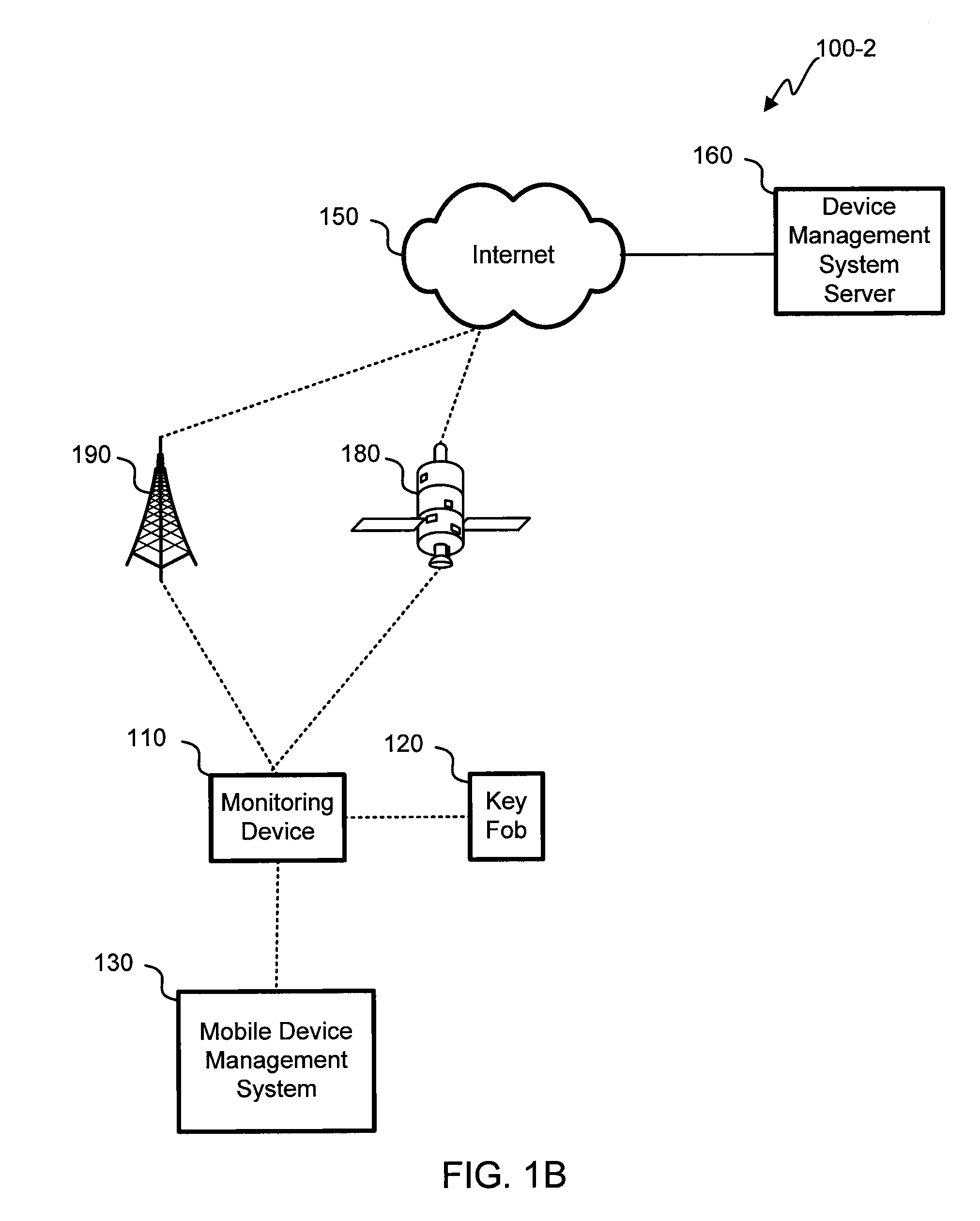

Monitoring unit configuration management

InactiveUS20120262272A1Programme controlElectric signal transmission systemsMonitor unitConfiguration management

Owner:CUBIC CORPORATION

Electronic tag broadcasting system and broadcasting method using electronic tag

InactiveUS20100245035A1Electric signal transmission systemsDigital data processing detailsBroadcast systemElectronic tags

An electronic tag broadcasting system and a broadcasting method using an electronic tag are provided. The electronic tag broadcasting system makes it possible to include information on photographed objects in a broadcasting signal, greatly change the combination of information by means of conventional manual operations, increase benefits of bi-directional broadcasting and the combination of broadcasting / communication by using recognition information included in broadcasting contents, and create a lot of new products and a large market. Popularity of broadcasting increases usage of electronic tags and their related application, thereby providing various service convergence that combines RFID, USN, communication, broadcasting, etc. and leading to a convenient ubiquitous society.

Owner:ELECTRONICS & TELECOMM RES INST

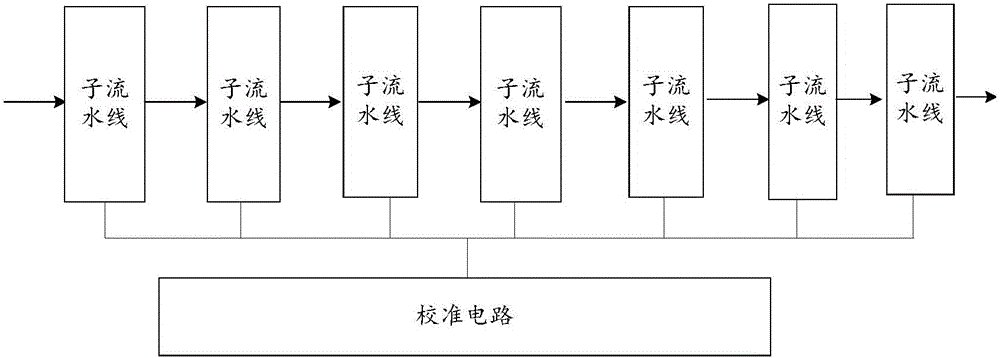

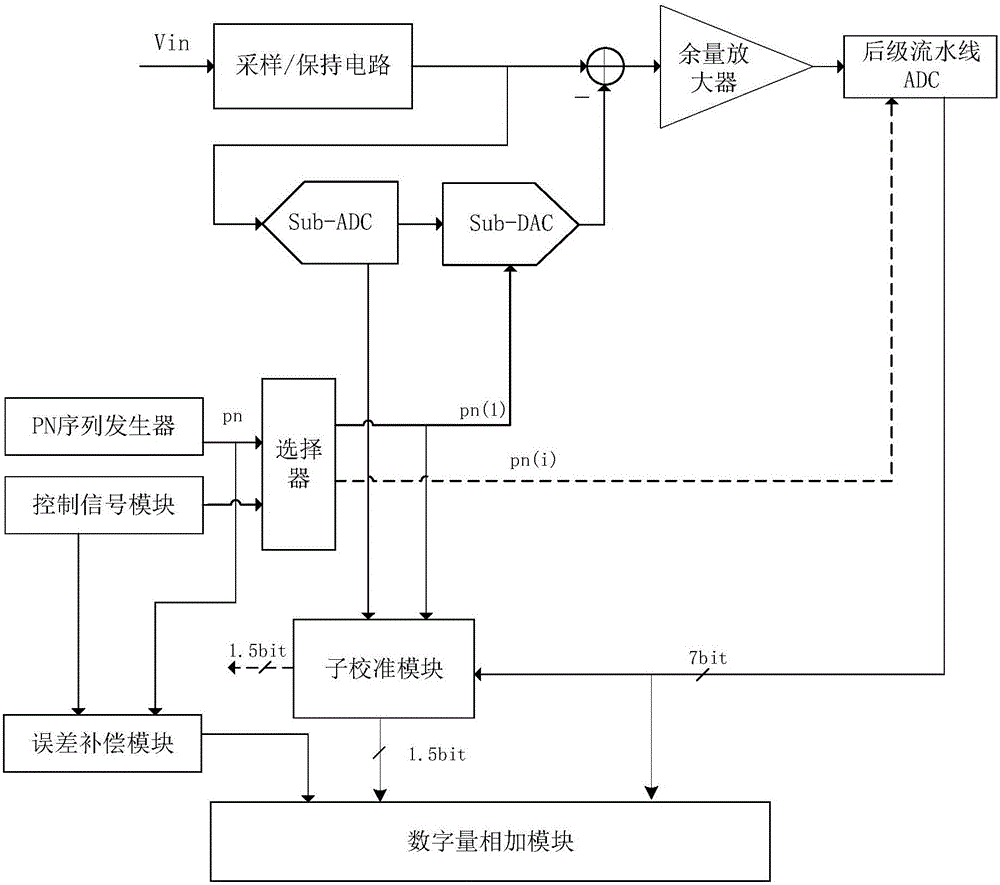

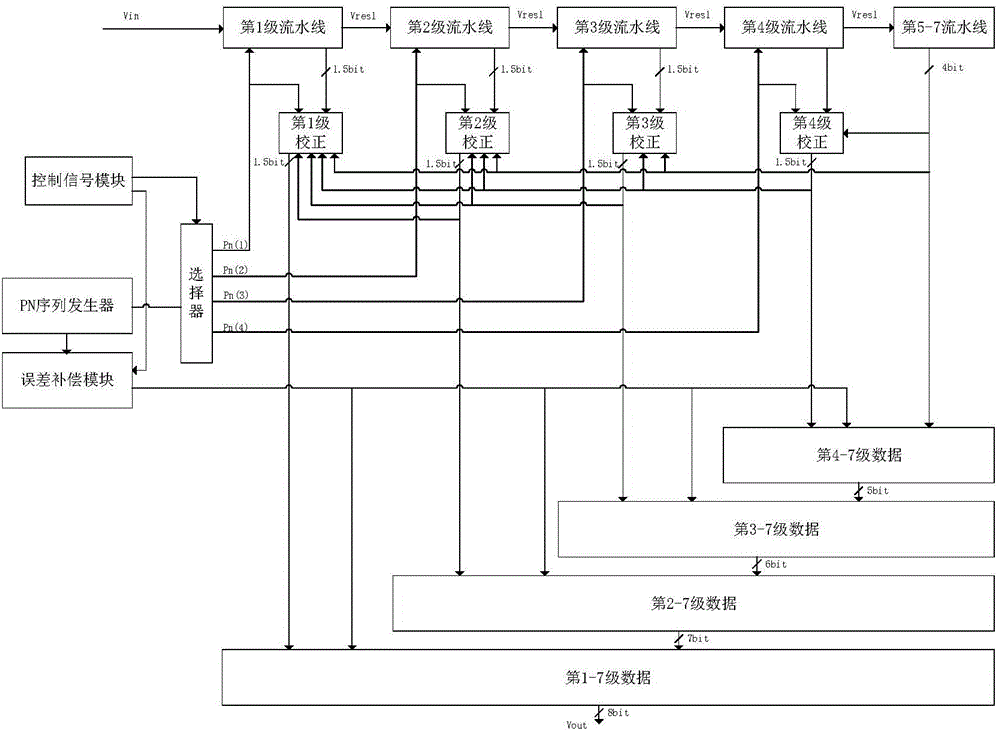

Digital background calibration device for pipeline ADC

InactiveCN105959005AElectric signal transmission systemsAnalogue/digital conversion calibration/testingCalibration algorithmAnalog circuit design

Owner:BEIJING JIAOTONG UNIV

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap