Digital background calibration device for pipeline ADC

A calibration device and assembly line technology, applied in the field of ADC calibration, can solve the problems of complex circuit design and no consideration of the influence of calibration algorithms

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

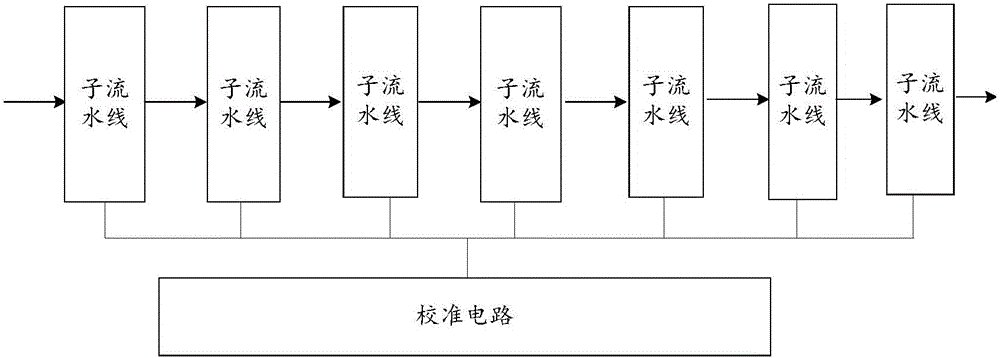

[0053] The embodiment of the present invention provides a digital background calibration device for pipeline ADC, the structural block diagram of the device is as follows figure 1 As shown, it consists of multi-stage cascaded sub-pipelines and calibration circuits, each sub-pipeline includes a sample / hold circuit, a margin amplifier, Sub-ADC and Sub-DAC, and the calibration circuit is connected to each sub-pipeline circuit .

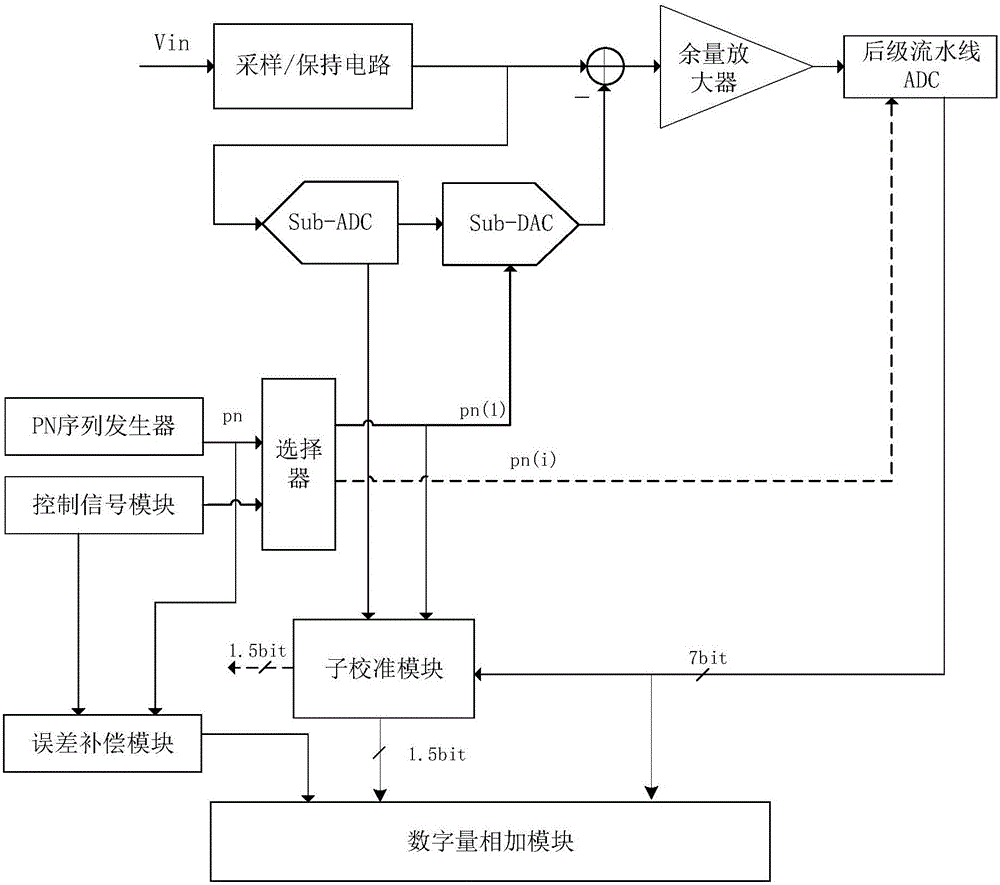

[0054] The analog signal passes through each sub-pipeline of the pipeline ADC in turn. While the analog input is calibrated to the sub-pipeline, the PN sequence (Pseudo-noise Sequence, pseudo-random sequence) generated by the calibration circuit is input to the calibrated sub-pipeline. In the Sub-DAC of the pipeline, the analog output of the calibrated sub-pipeline and the pseudo-random sequence pass through the margin amplifier and then enter the subsequent sub-pipeline;

[0055] The calibration circuit uses the pseudo-random sequence and the calibrate

Embodiment 2

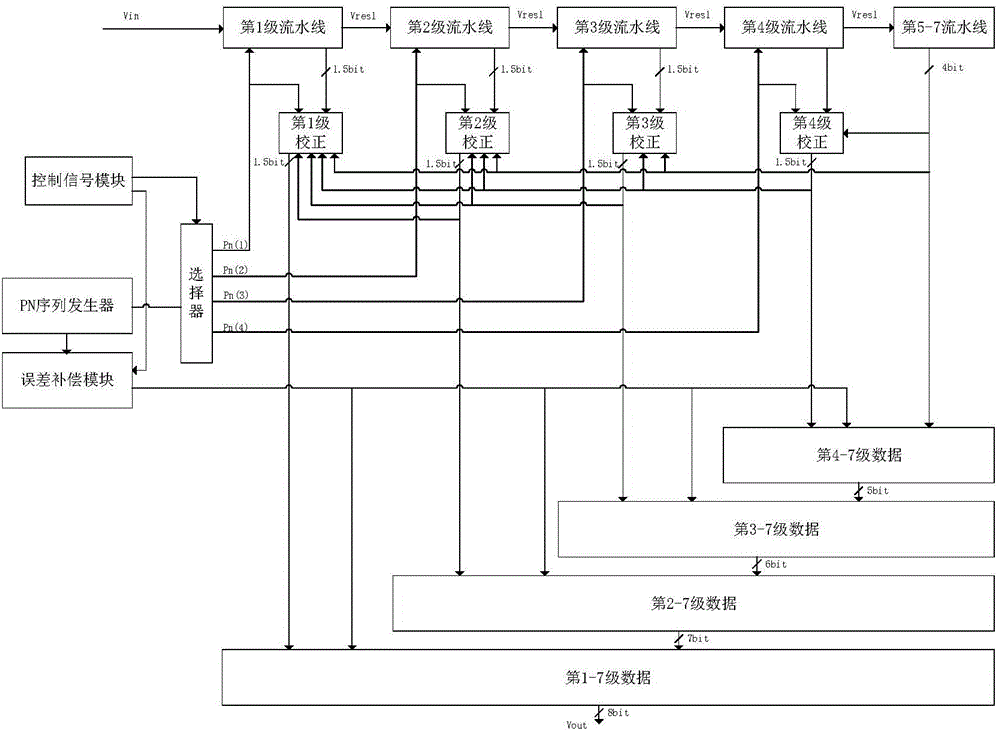

[0076] The structural diagram of a digital background calibration device of a pipelined ADC composed of 7-stage sub-pipeline cascades provided by this embodiment is as follows image 3 As shown, each of the first 6 stages generates 1.5bit digital bits, and the seventh stage generates 2bit digital bits. The analog signal passes through each stage of the pipeline ADC in turn, and generates a 1.5bit (the last stage is 2bit) digital quantity, and finally obtains the final 8bit digital quantity through dislocation and addition.

[0077] Calibration only calibrates the first 4 levels, and the object of calibration is the error caused by the capacitance loss and the limited gain of the operational amplifier. When a certain stage structure needs to be calibrated, the pseudo-random sequence generated by the PN sequence generator will be input into the Sub-DAC of the calibrated stage while the analog quantity is input into the stage structure. The input analog quantity and the pseudo-rand

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap