Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

237 results about "Capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Capacitance is the ratio of the change in an electric charge in a system to the corresponding change in its electric potential. There are two closely related notions of capacitance: self capacitance and mutual capacitance. Any object that can be electrically charged exhibits self capacitance. A material with a large self capacitance holds more electric charge at a given voltage than one with low capacitance. The notion of mutual capacitance is particularly important for understanding the operations of the capacitor, one of the three elementary linear electronic components (along with resistors and inductors).

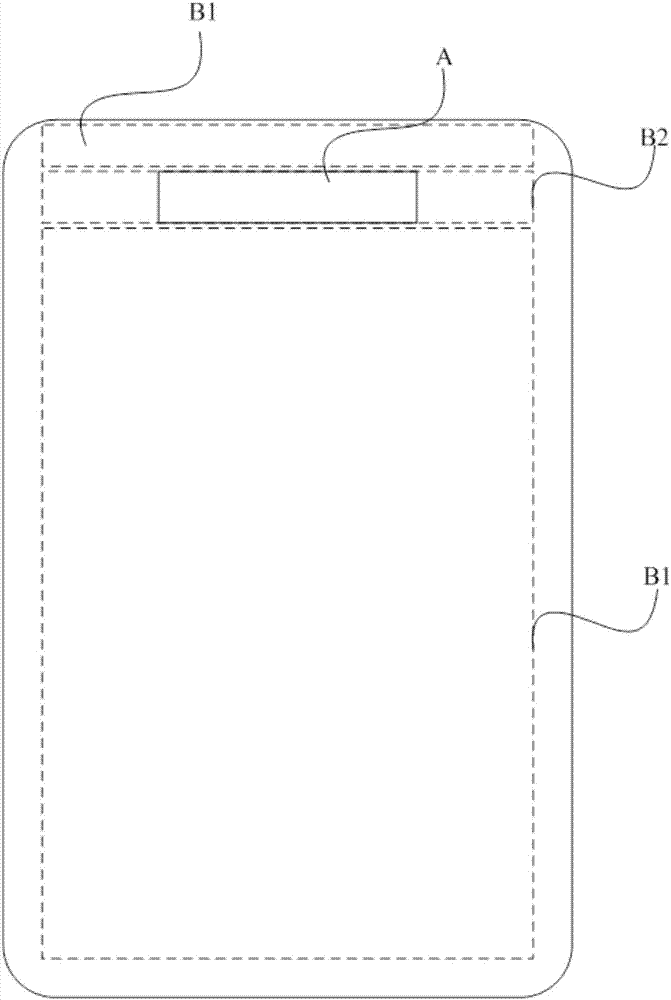

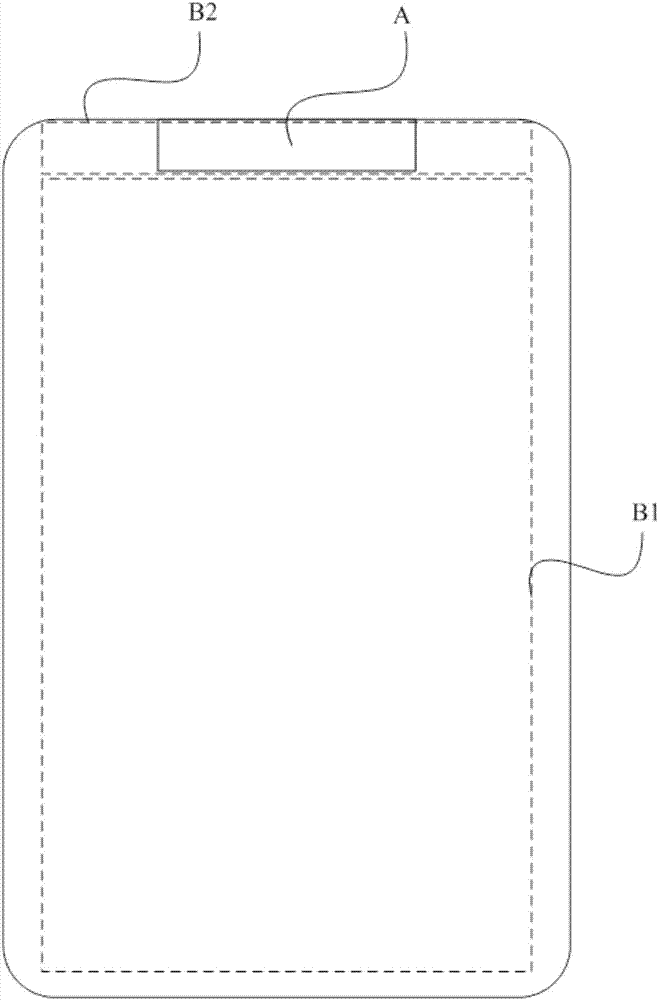

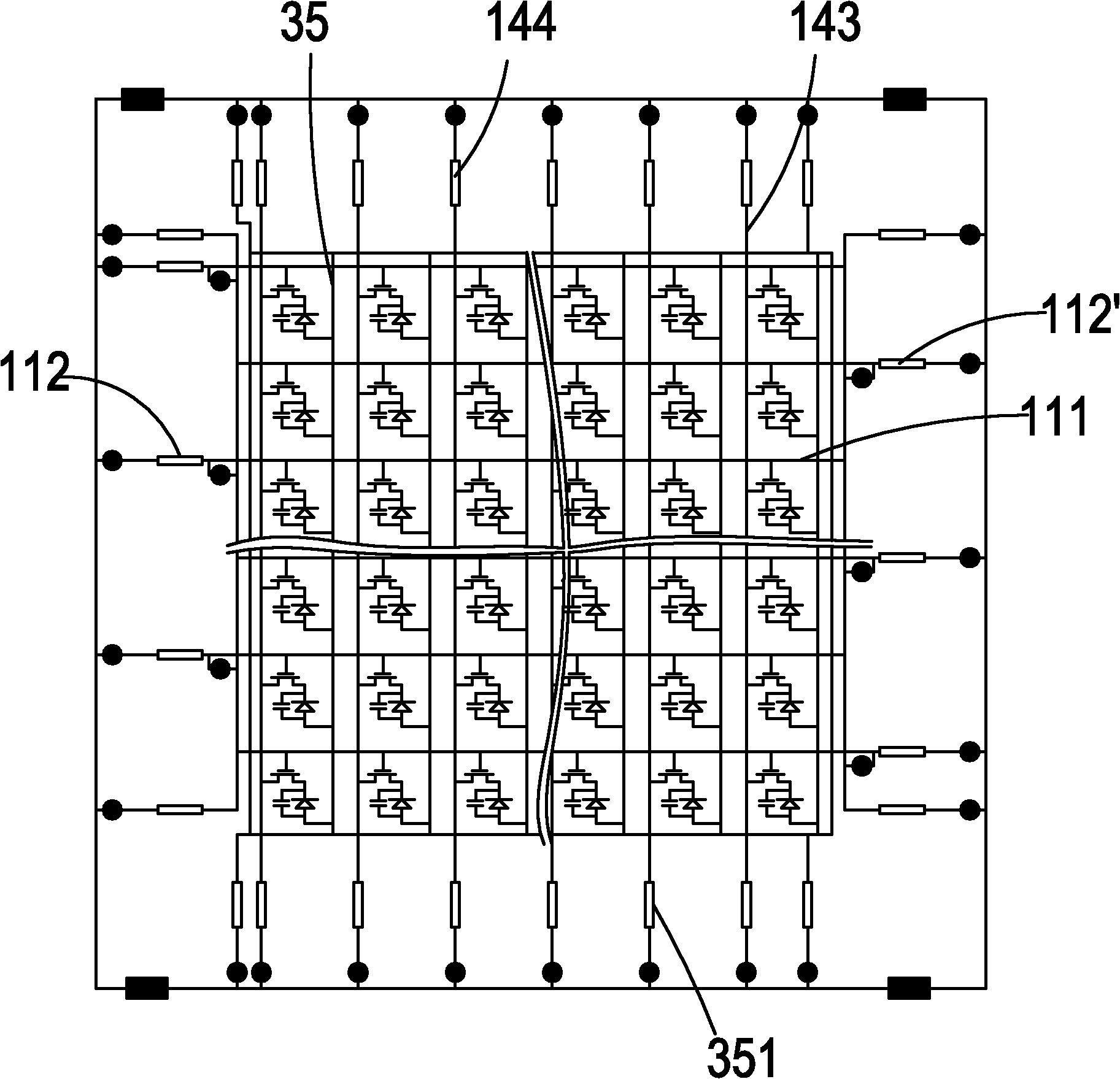

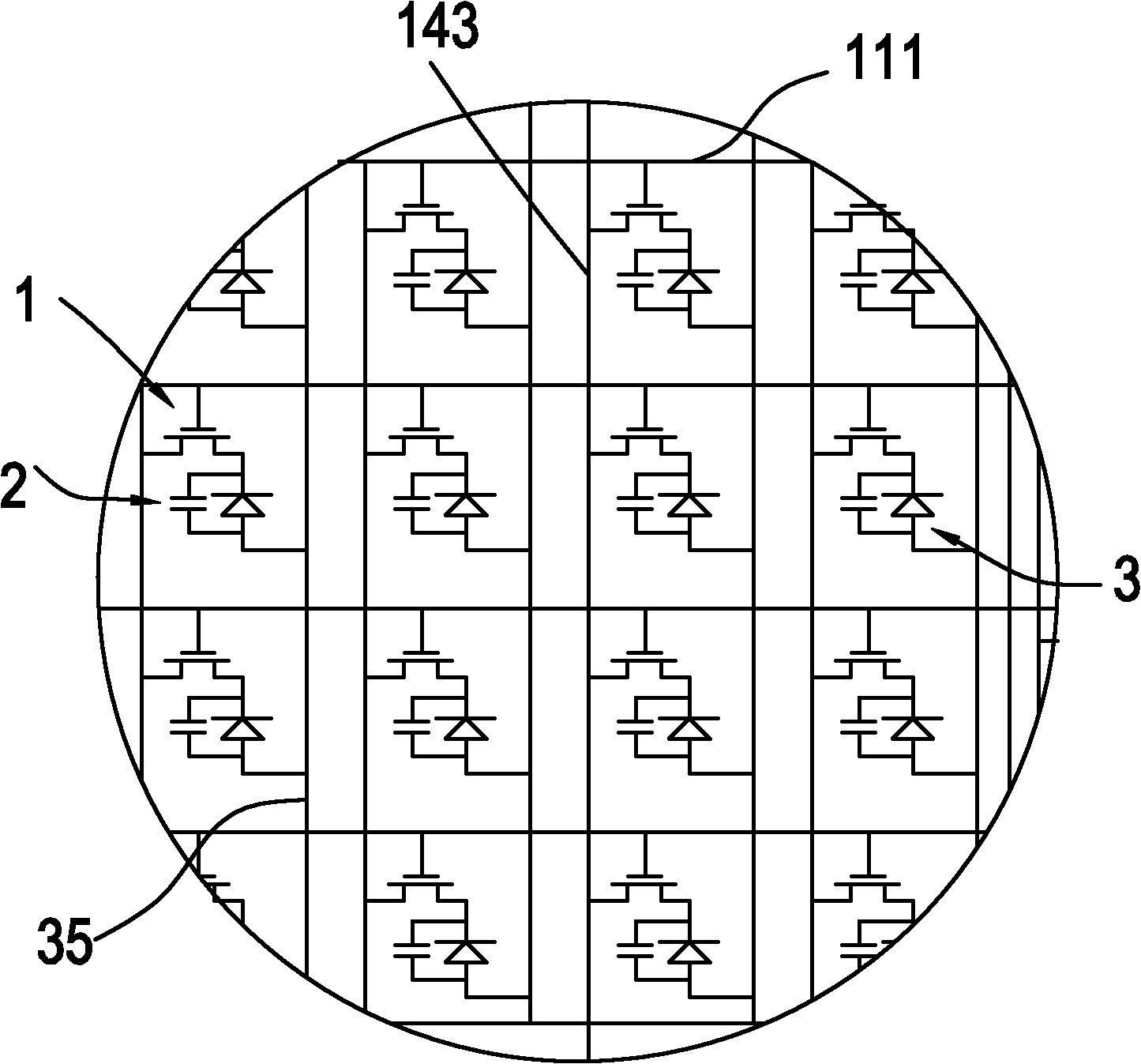

Display panel and display device

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

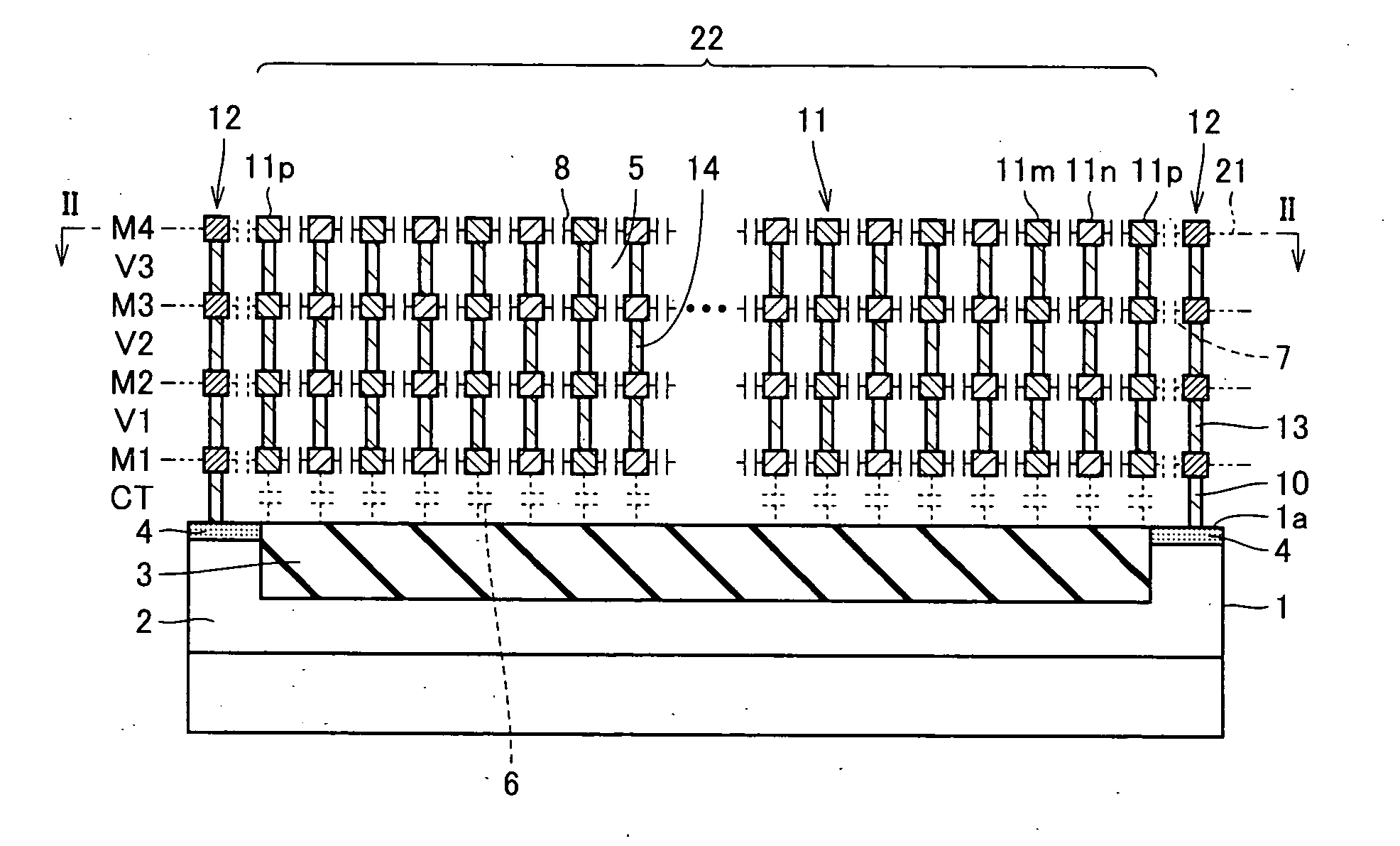

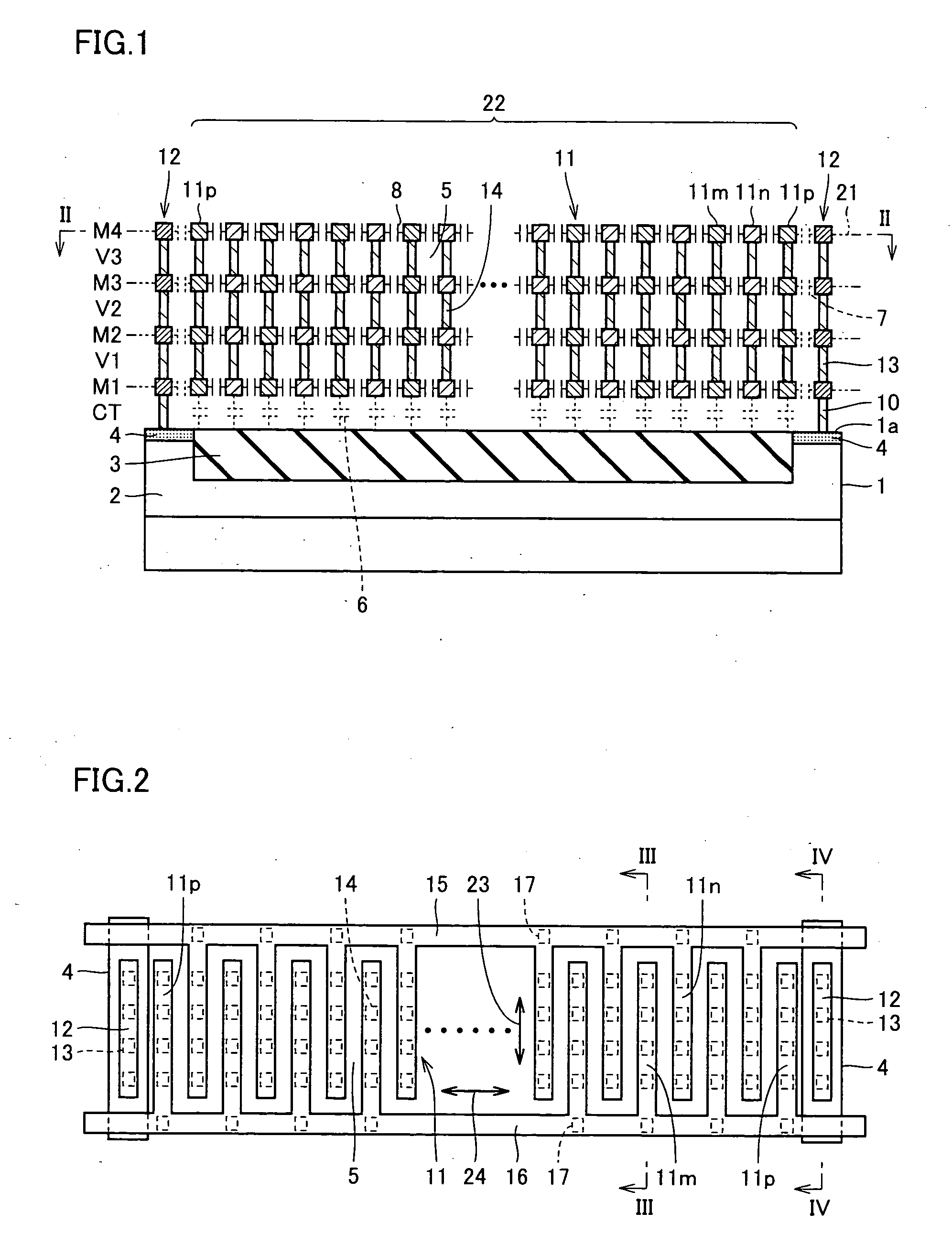

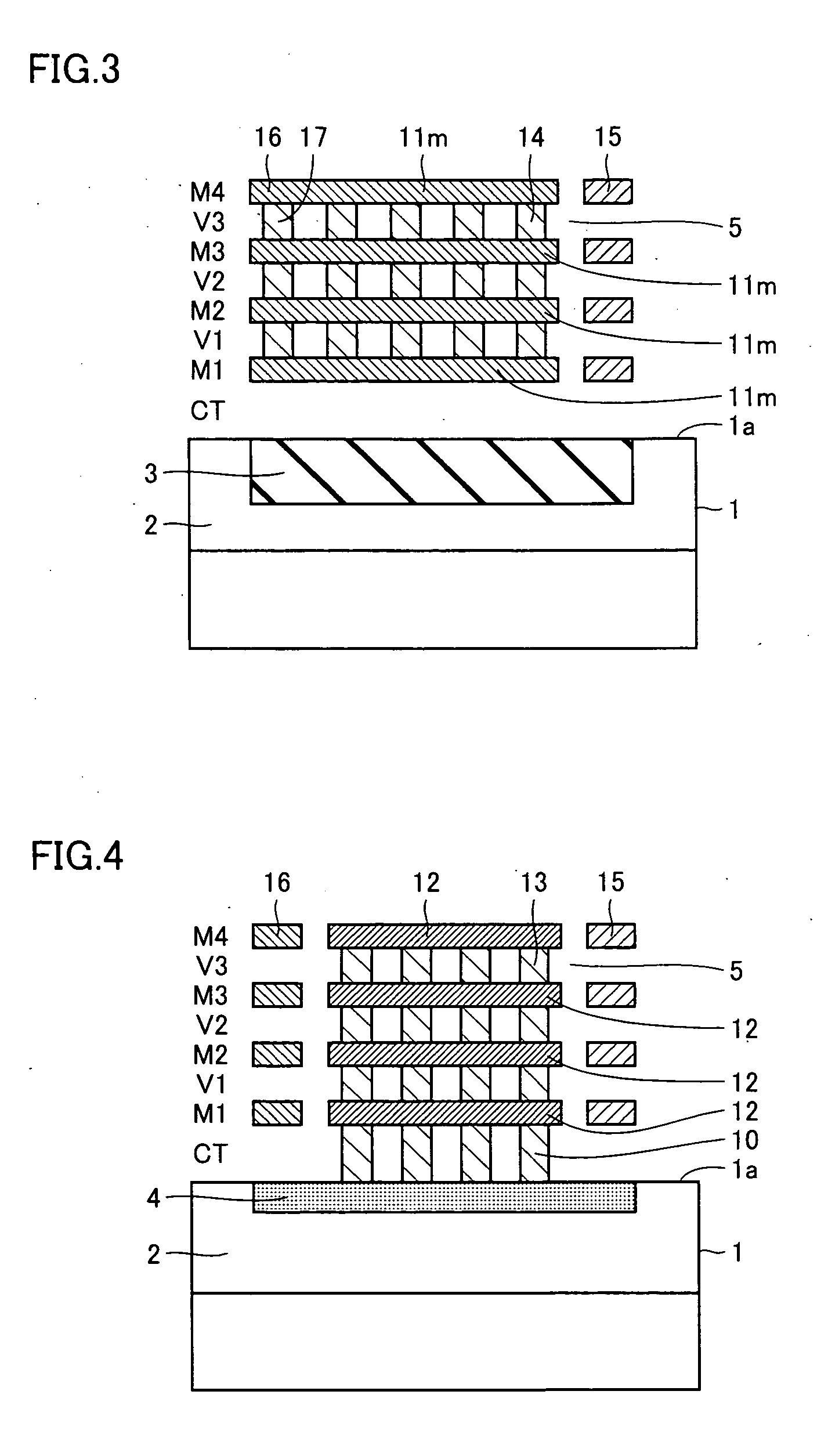

Semiconductor device

ActiveUS20050145987A1Reduce distractionsDesired characteristicTransistorSemiconductor/solid-state device detailsCapacitanceDevice material

Owner:RENESAS ELECTRONICS CORP +1

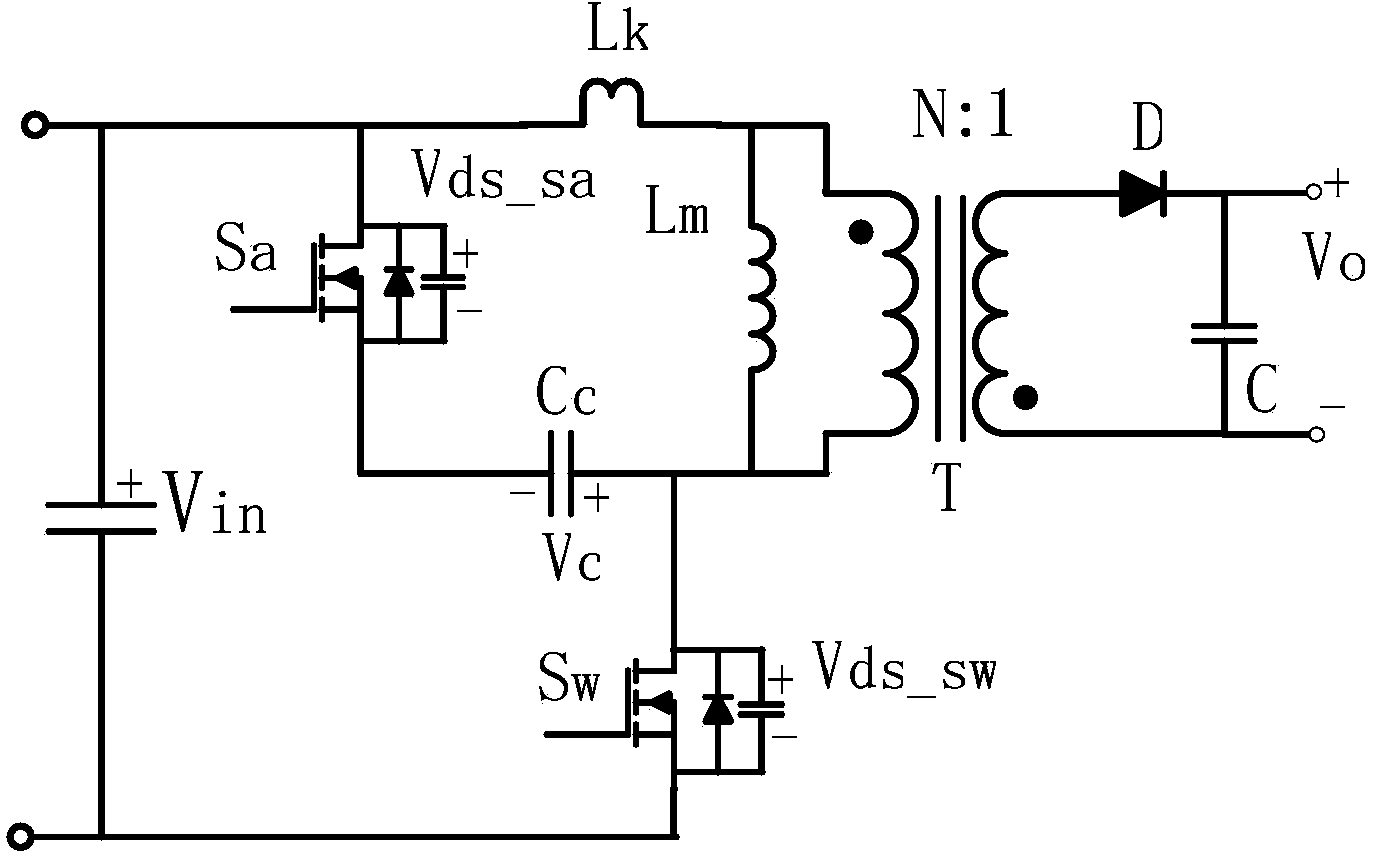

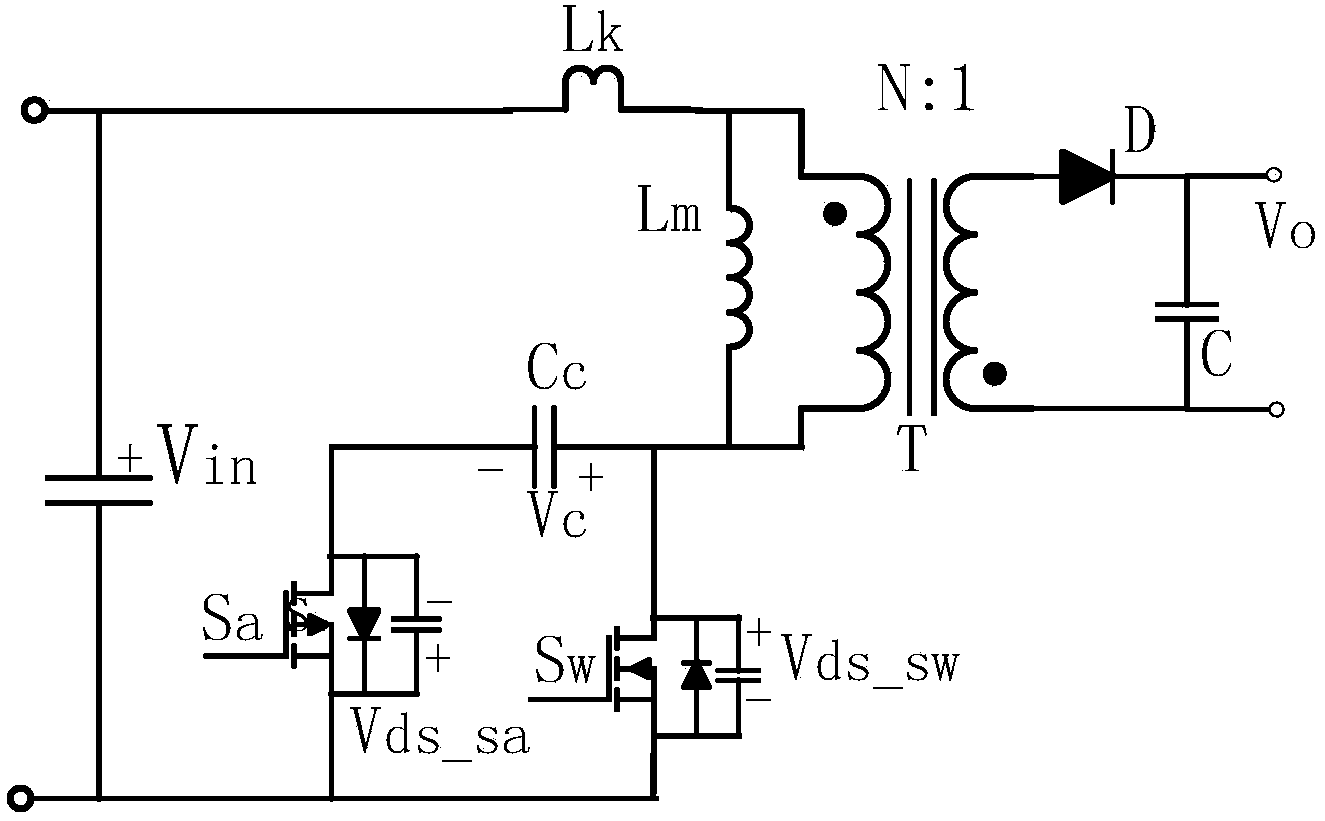

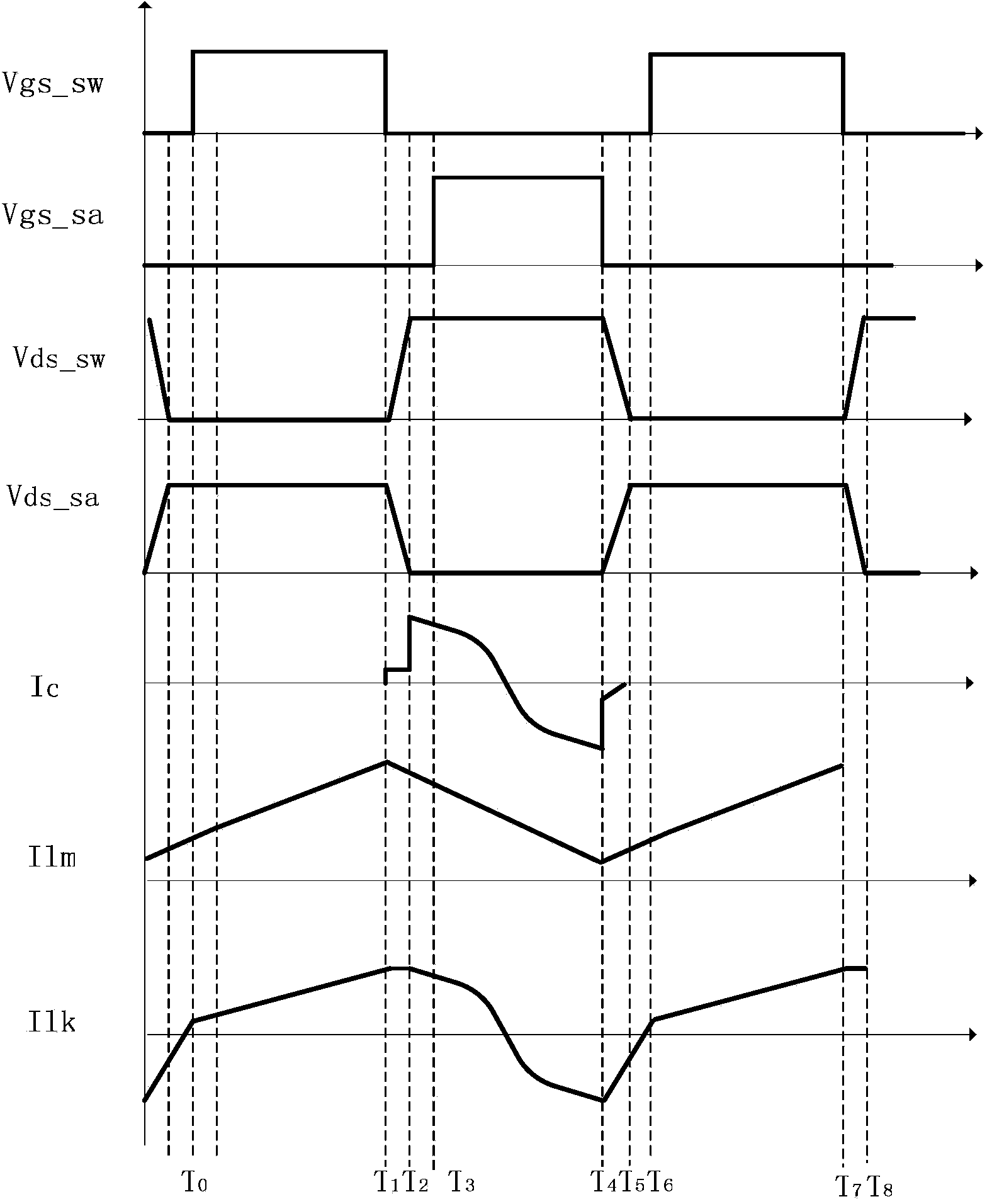

Flyback converter and control method of flyback converter

ActiveCN104300795AGuaranteed efficiencyReduce distractionsDc-dc conversionElectric variable regulationClamp capacitorCapacitance

Owner:MORNSUN GUANGZHOU SCI & TECH

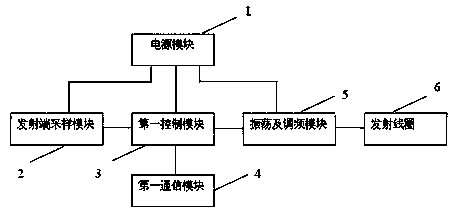

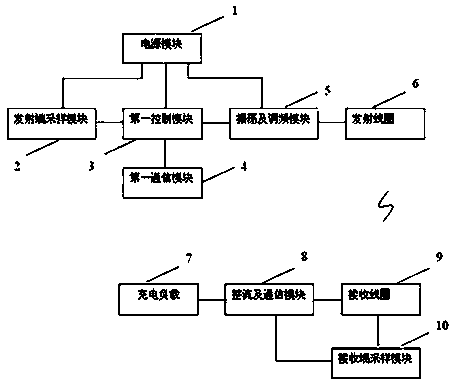

Wireless charging sending device, wireless charging system and wireless charging control method

Owner:BYD CO LTD

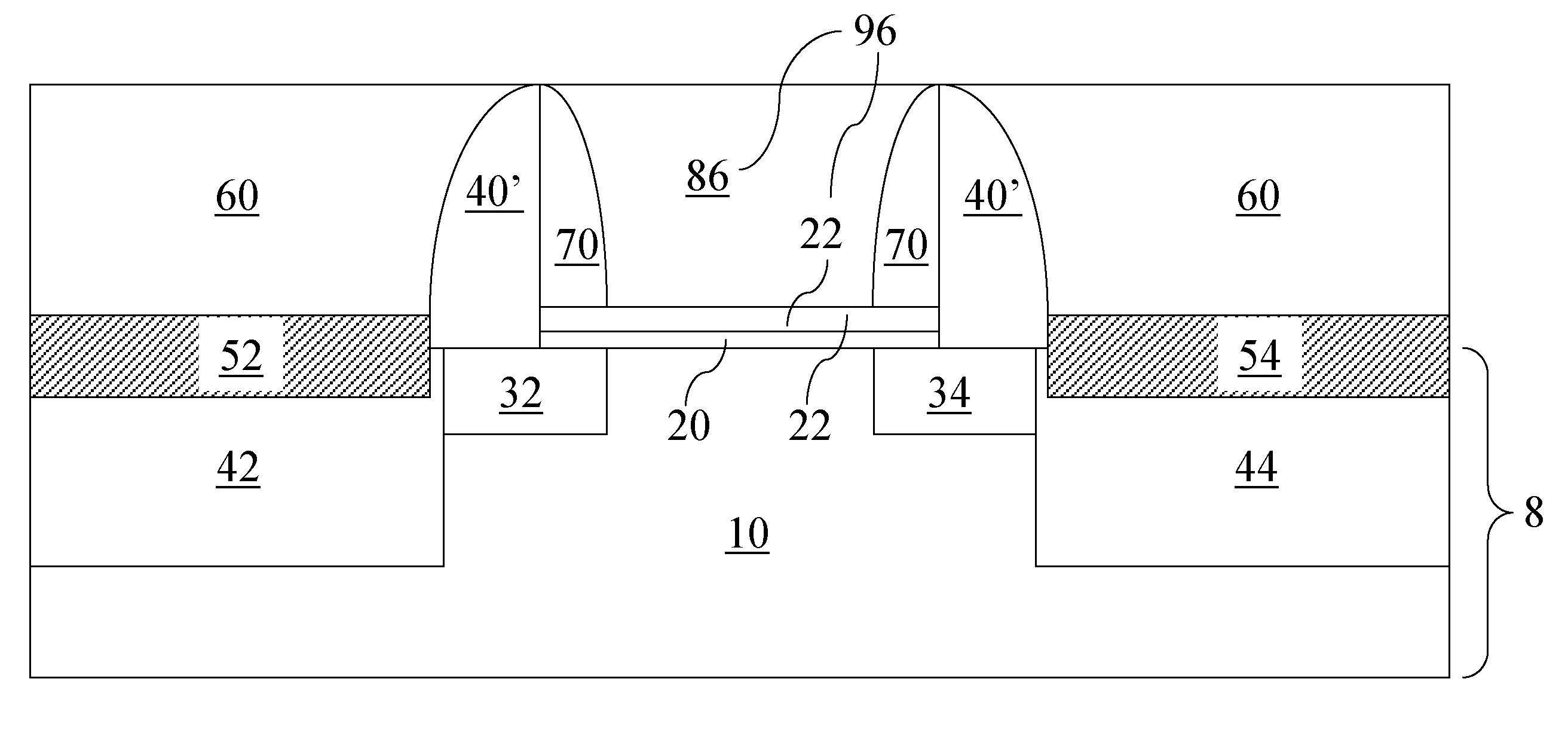

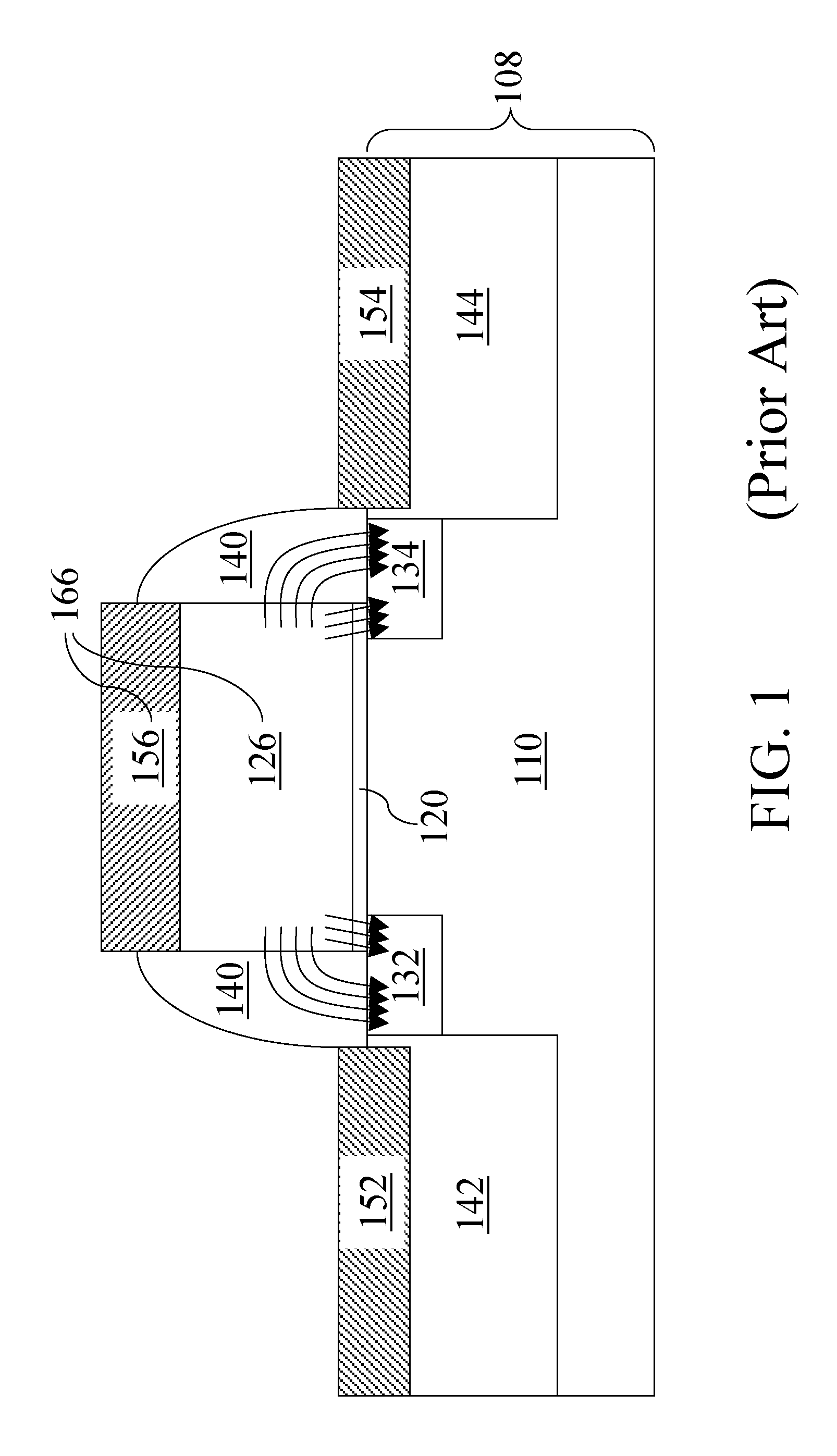

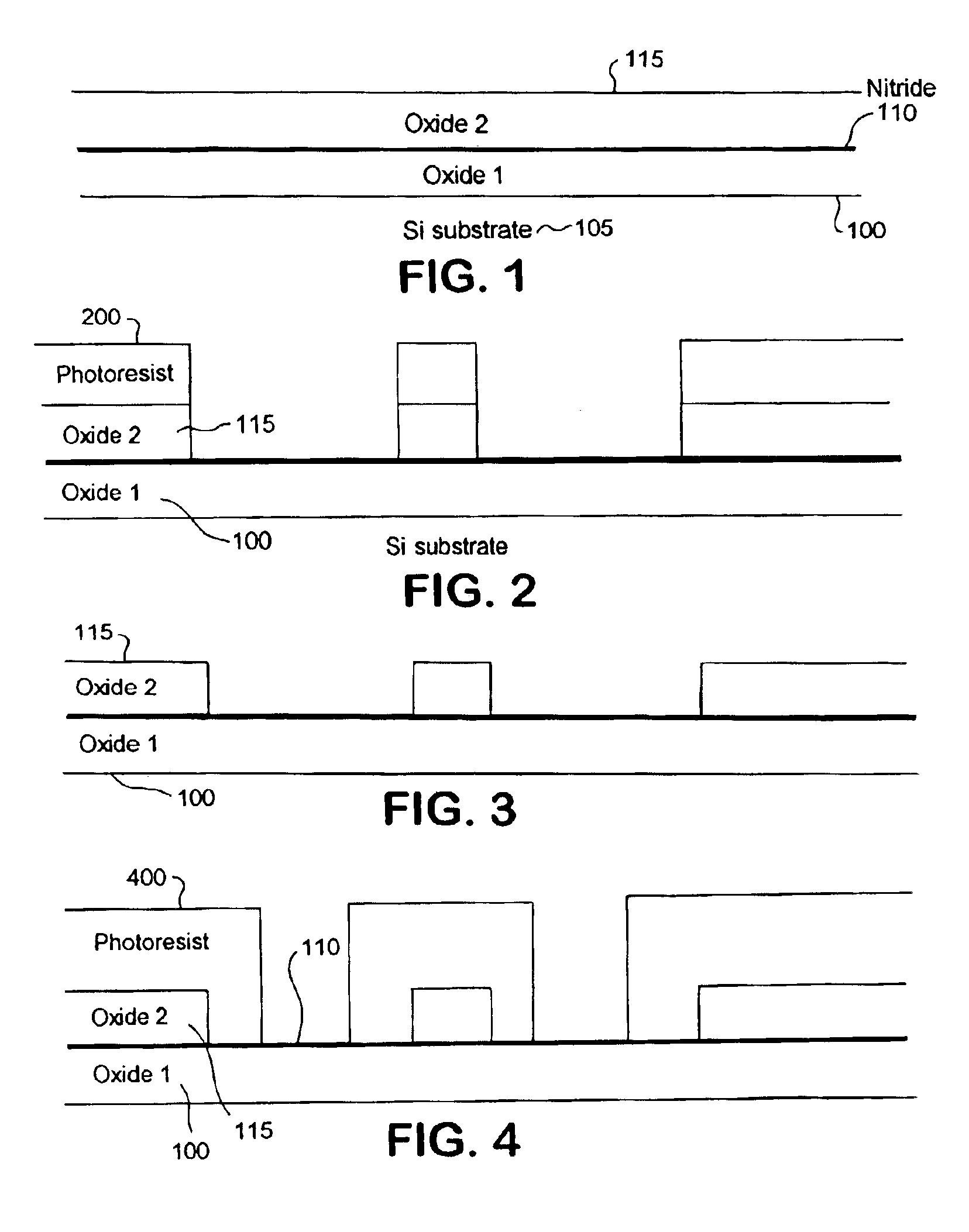

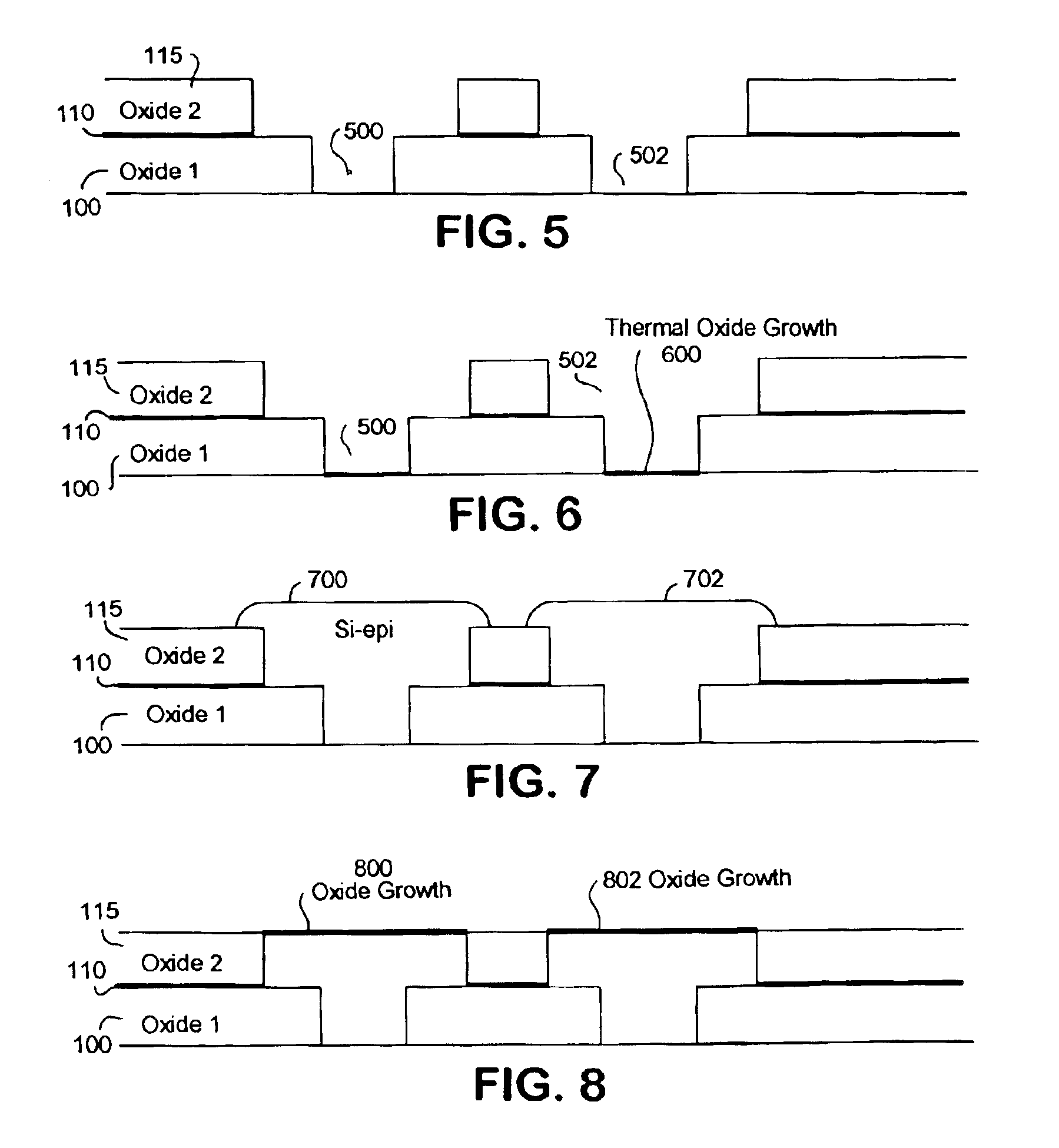

Field effect transistor with reduced overlap capacitance

InactiveUS20090212332A1Reduce Overlap CapacitanceTransistorSemiconductor/solid-state device manufacturingCapacitanceElectrical conductor

Owner:GLOBALFOUNDRIES INC

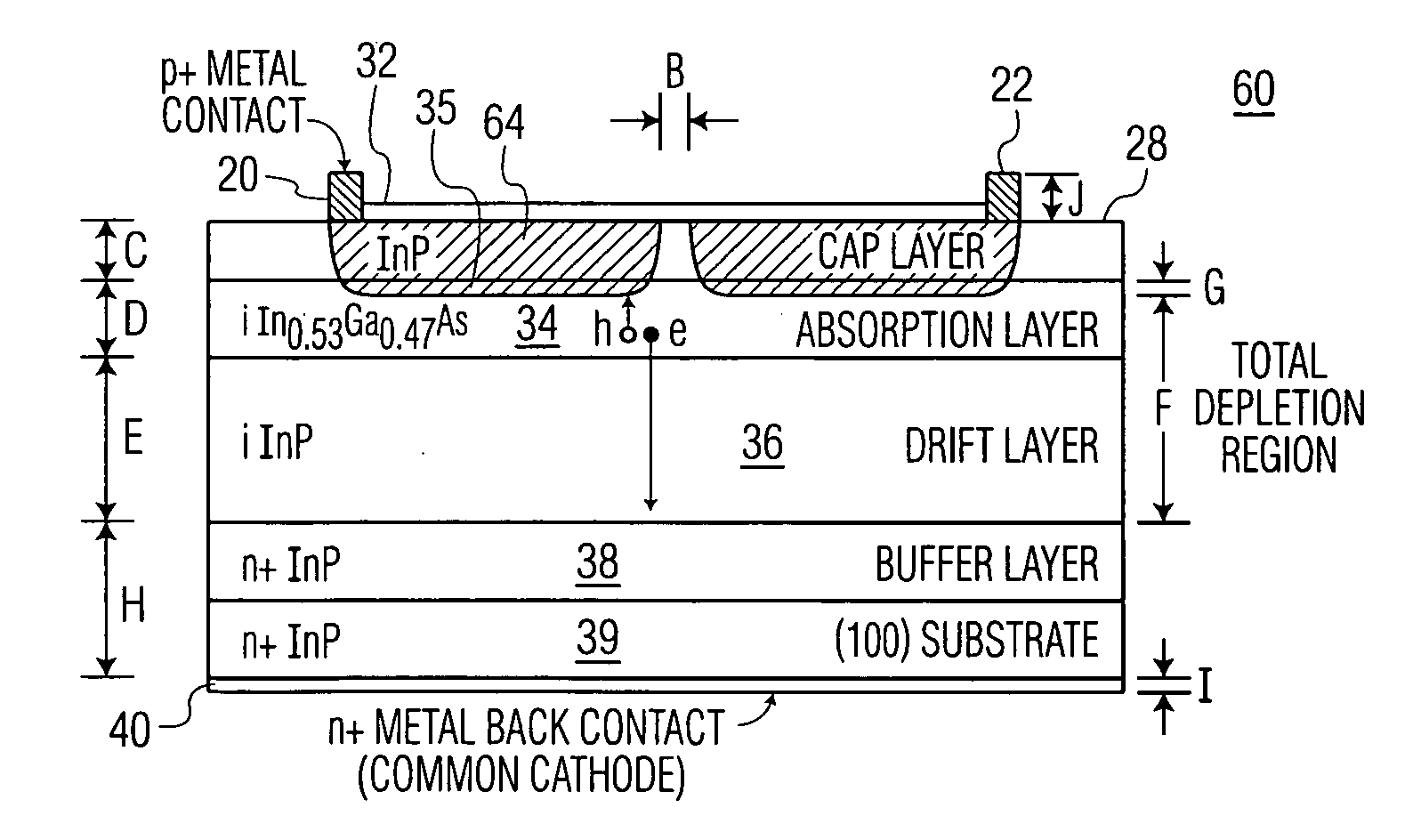

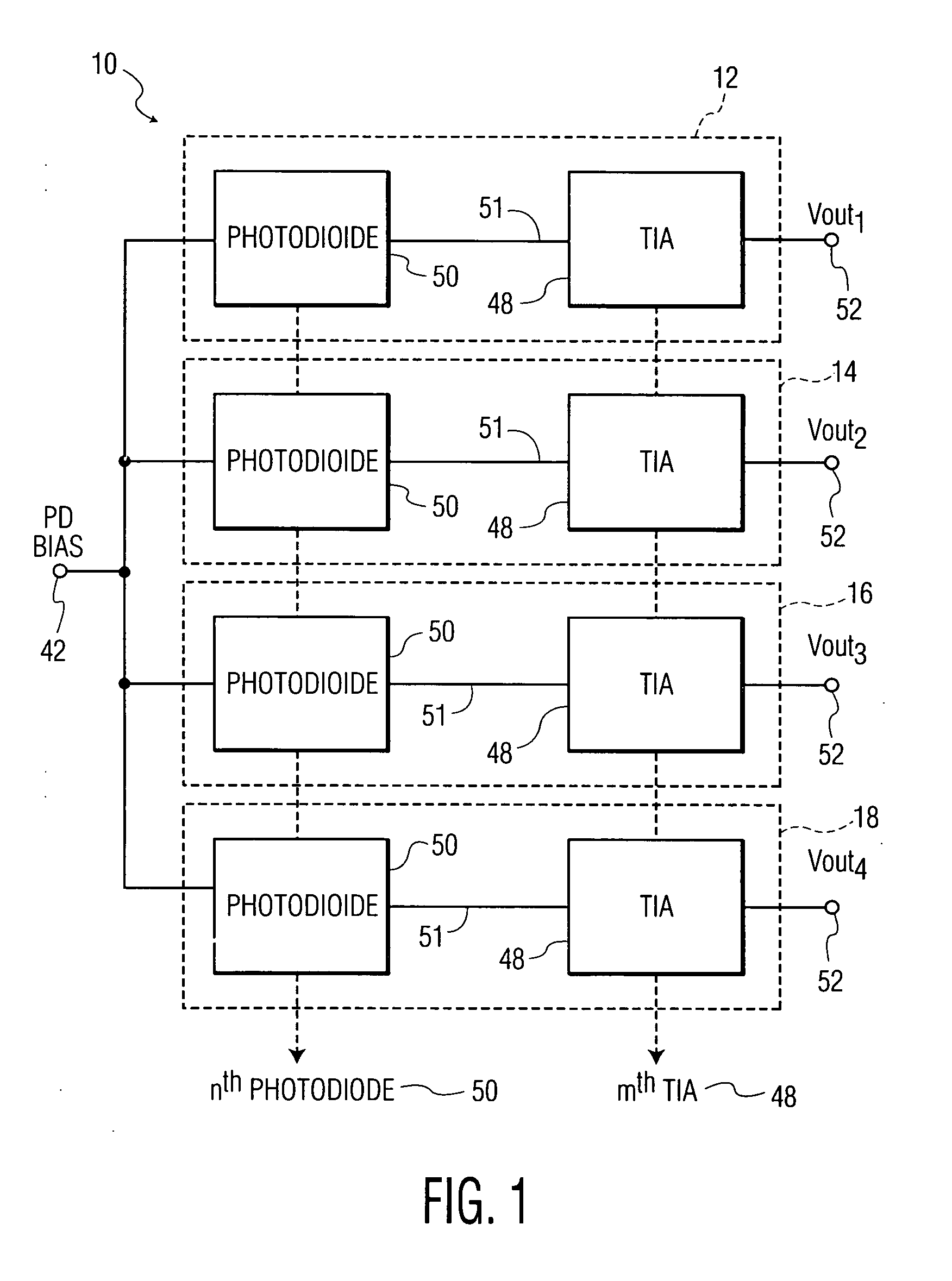

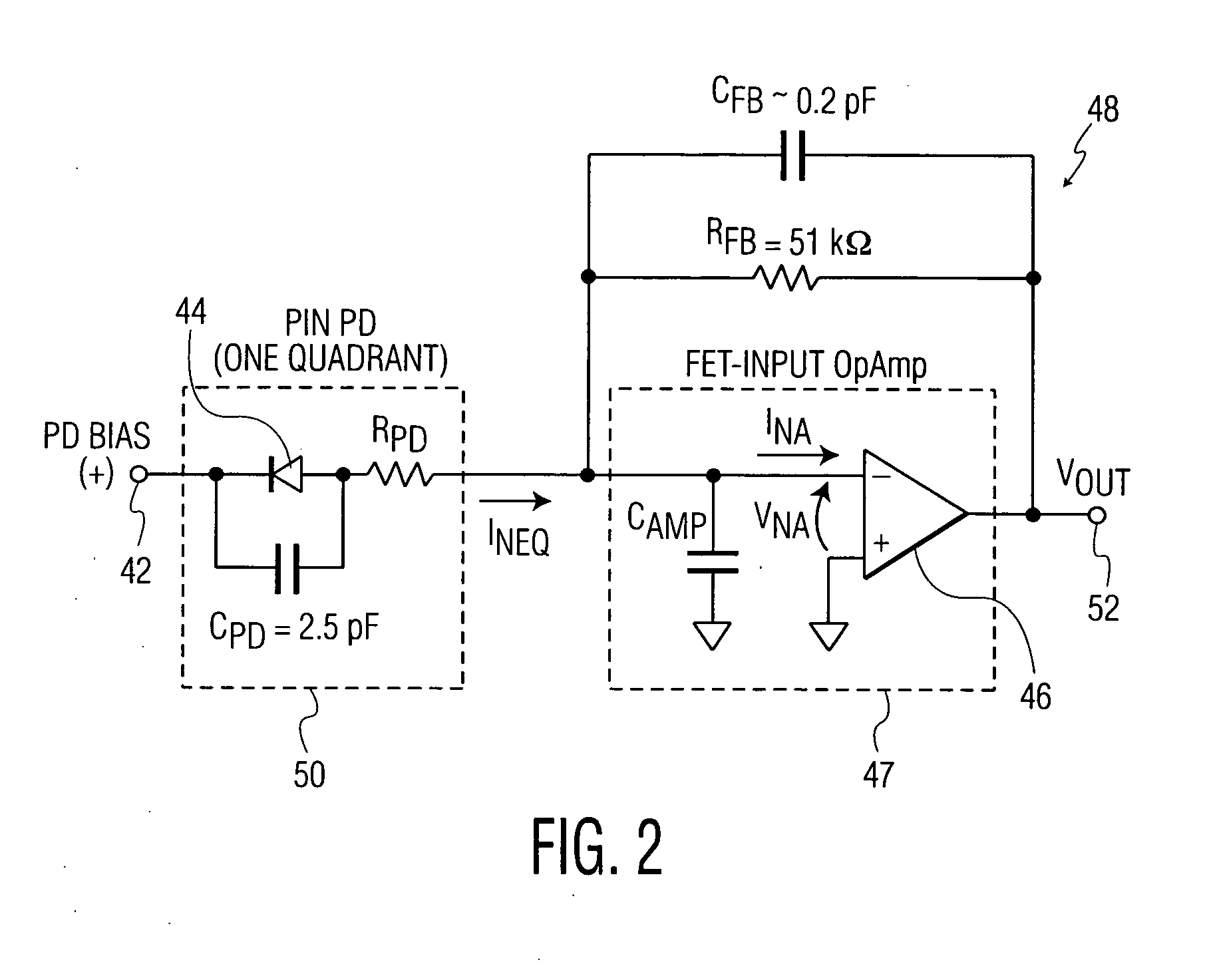

Low-noise large-area photoreceivers with low capacitance photodiodes

Owner:DISCOVERY SEMICON

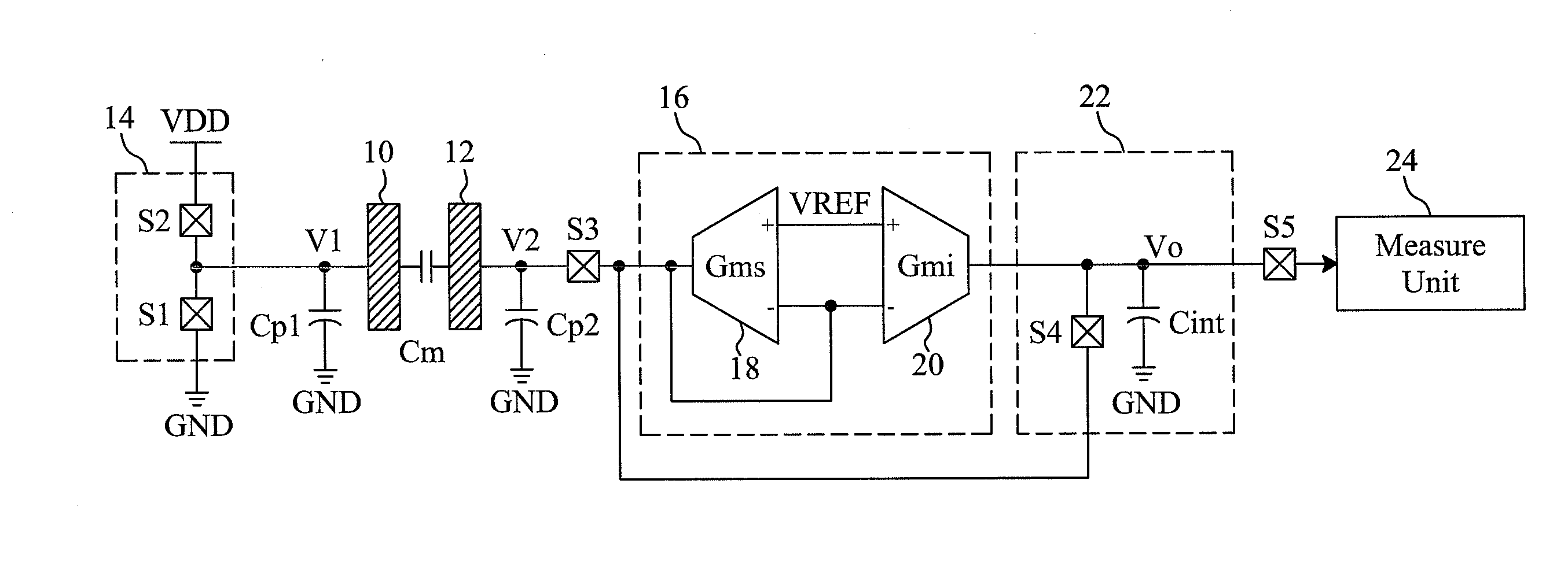

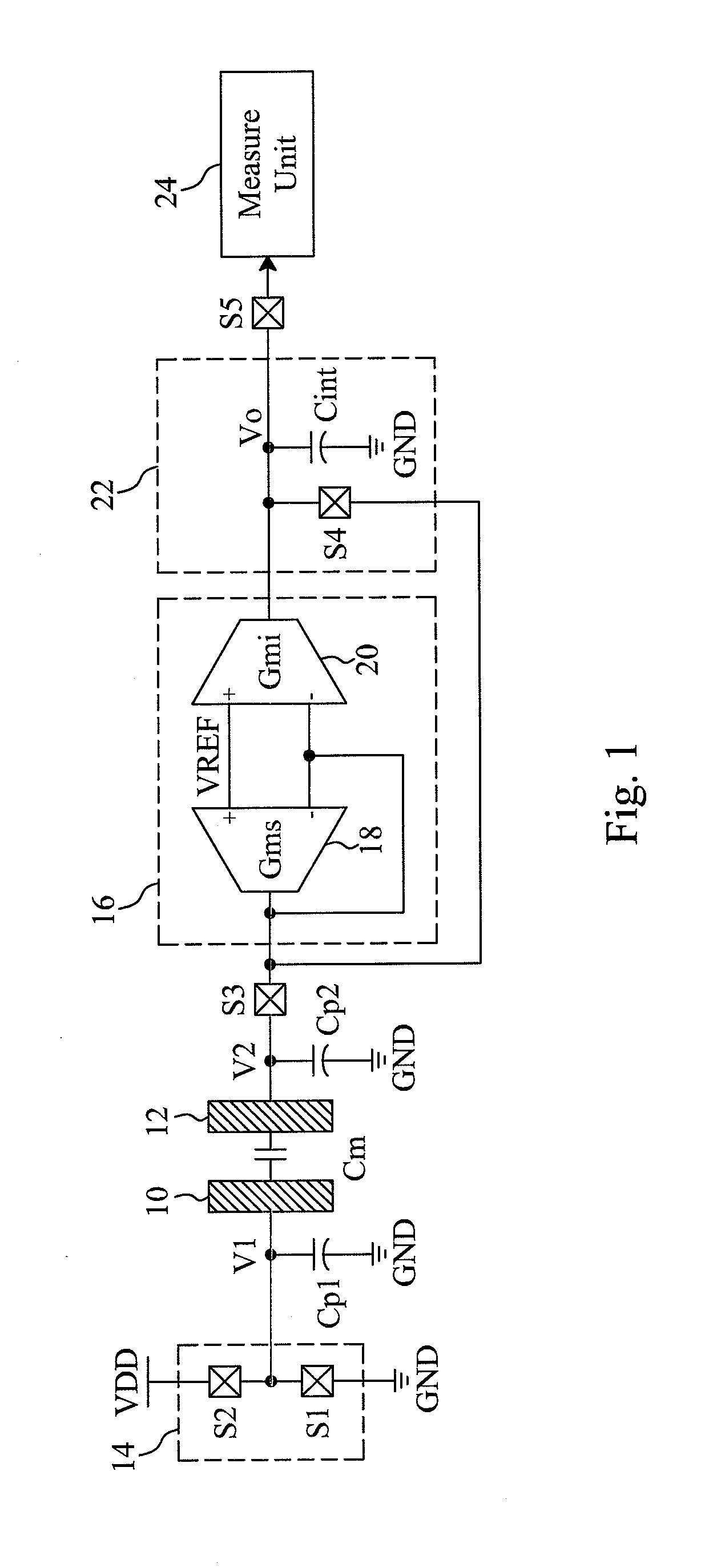

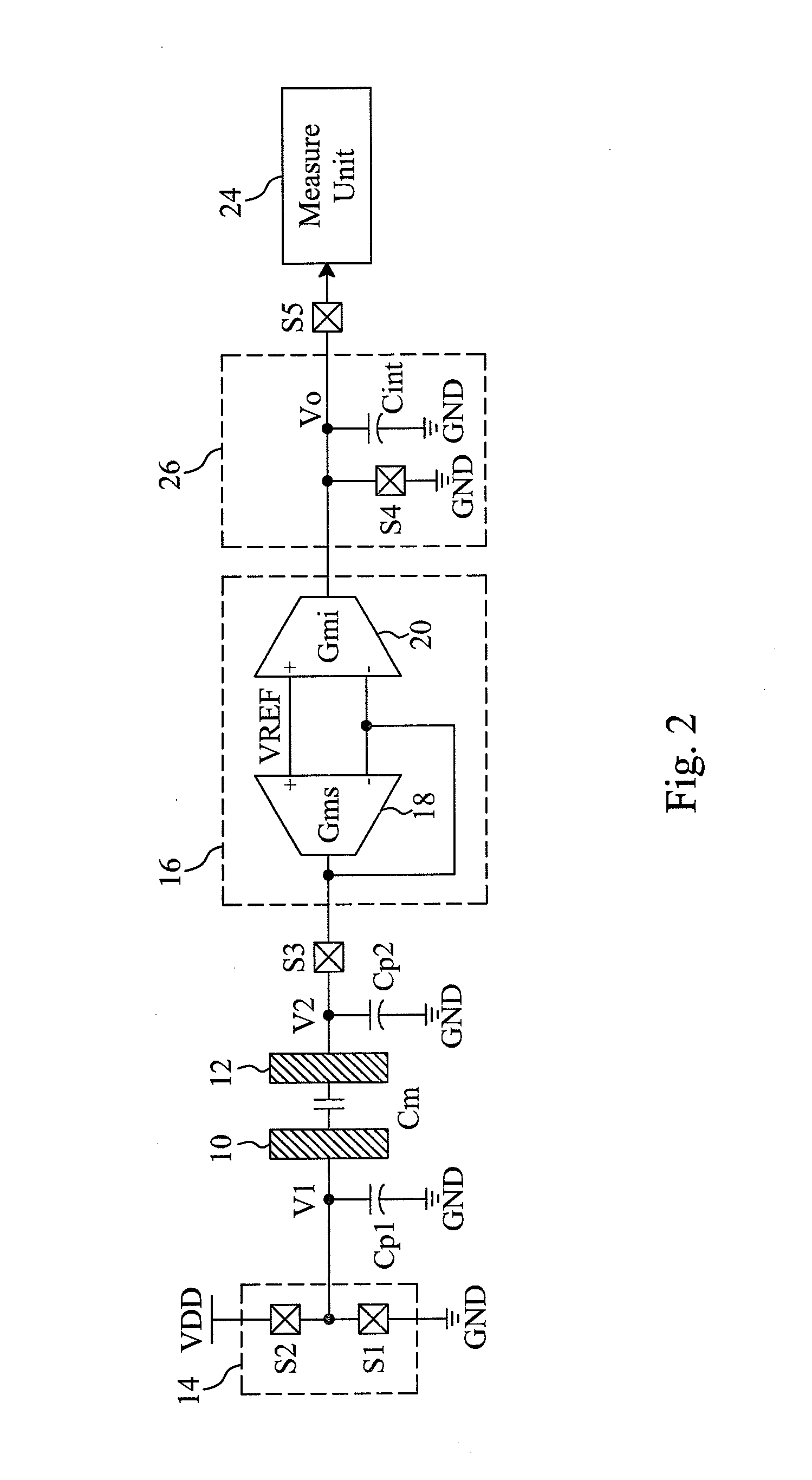

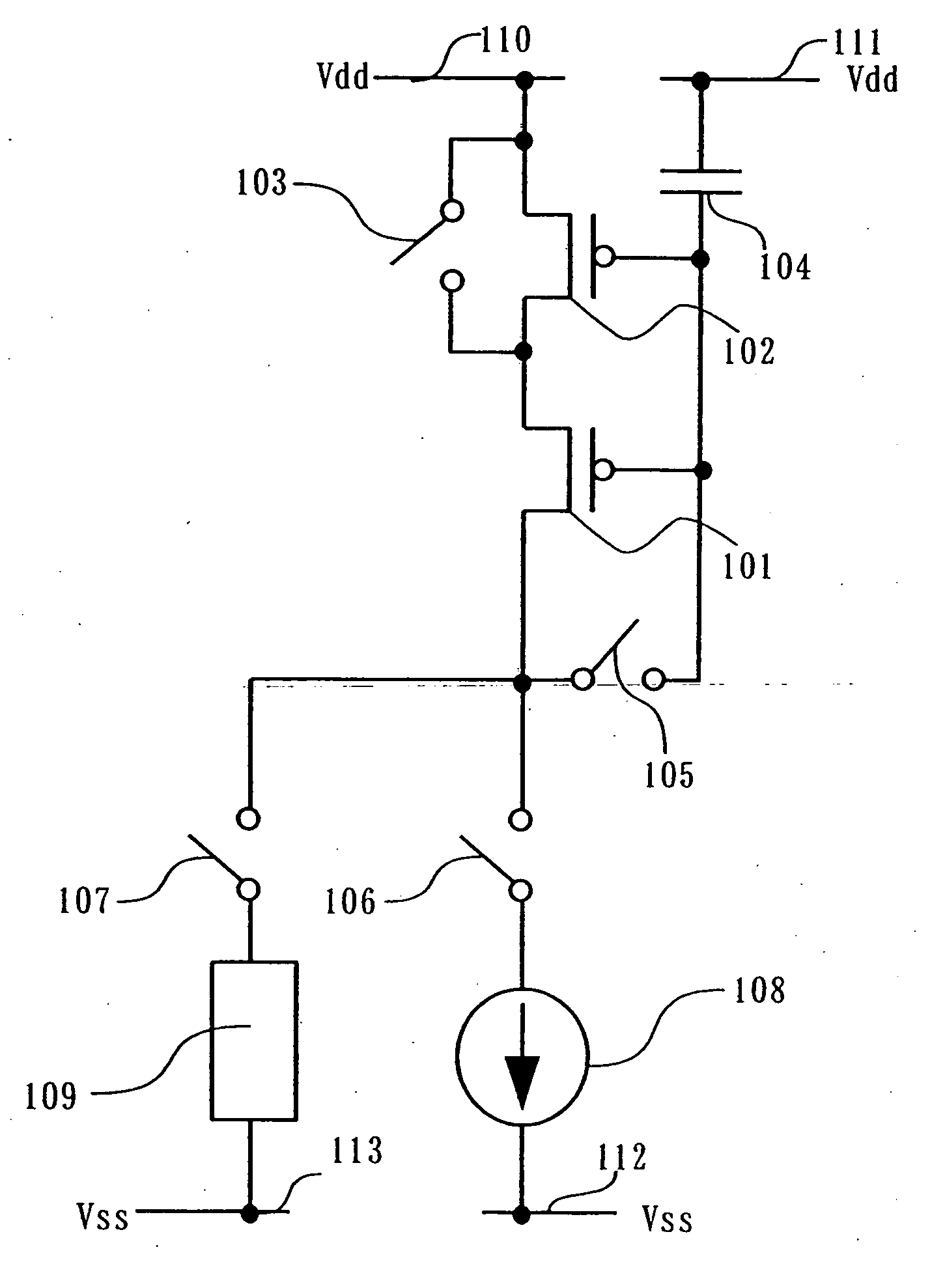

Circuit and method for sensing a capacitance

ActiveUS20120146726A1Capacitance measurementsElectrical measurement instrument detailsCapacitanceAudio power amplifier

Owner:ELAN MICROELECTRONICS CORPORATION

Method and circuit for controlling an electric power plant

InactiveUS20060132103A1High precisionEmergency protective circuit arrangementsDynamo-electric converter controlCapacitancePower station

A control circuit is for an electric power plant including an asynchronous generator of an AC voltage, a motor to rotate a rotor of the asynchronous generator as a function of a first control signal of a developed motor torque, and a bank of capacitors coupled to the asynchronous generator and having a total capacitance varying as function of a second control signal. The control circuit may include a monitor circuit to monitor at least one parameter of the AC voltage, and a control signal generator circuit cooperating with the monitor circuit to generate the first and second control signals by soft-computing techniques both as a function of the frequency and of a representative value of an amplitude of the AC voltage to make the AC voltage have a desired amplitude and frequency.

Owner:STMICROELECTRONICS SRL

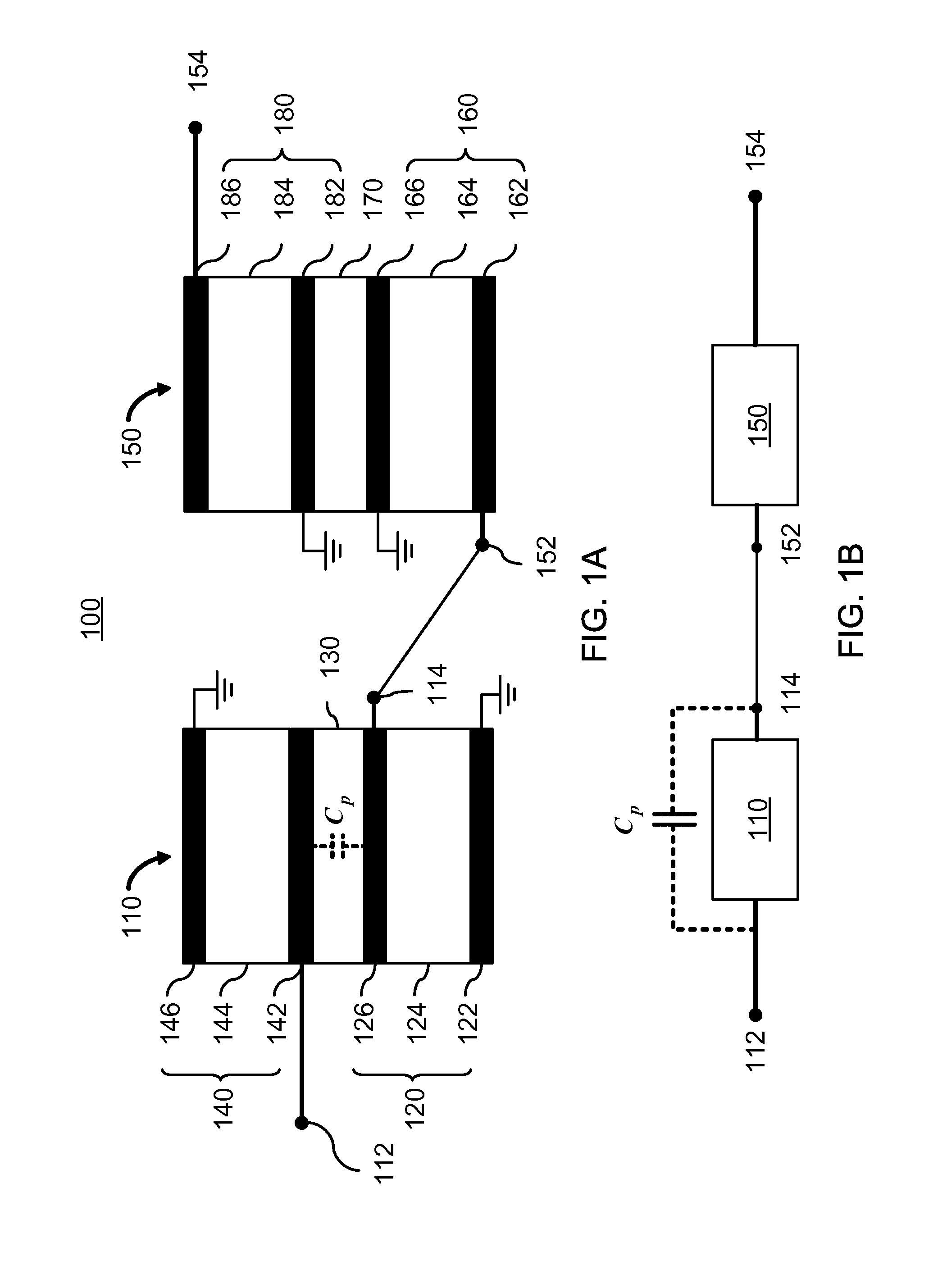

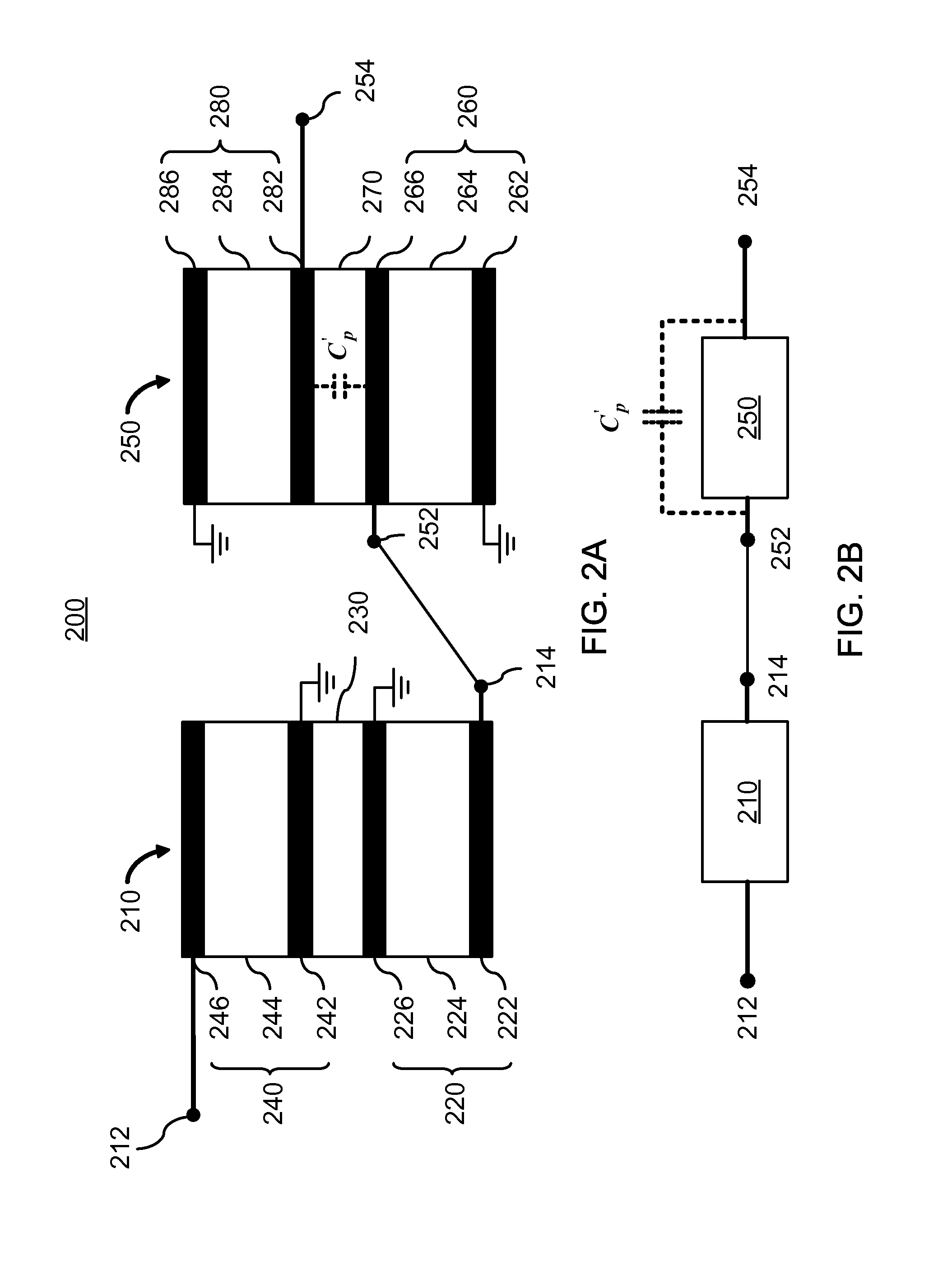

Coupled acoustic devices

Owner:PANG WEI +1

MOSFET using gate work function engineering for switching applications

InactiveUS20060273379A1Highly functionalLower capacitance CgdSemiconductor devicesCapacitanceWork function engineering

This invention discloses a new MOSFET device. The MOSFET device has an improved operation characteristic achieved by manufacturing a MOSFET with a higher gate work function by implementing a P-doped gate in an N-MOSFET device. The P-type gate increases the threshold voltage and shifts the C-Vds characteristics. The reduced Cgd thus achieves the purpose of suppressing the shoot through and resolve the difficulties discussed above. Unlike the conventional techniques, the reduction of the capacitance Cgd is achieved without requiring complicated fabrication processes and control of the recess electrode.

Owner:ALPHA & OMEGA SEMICON LTD

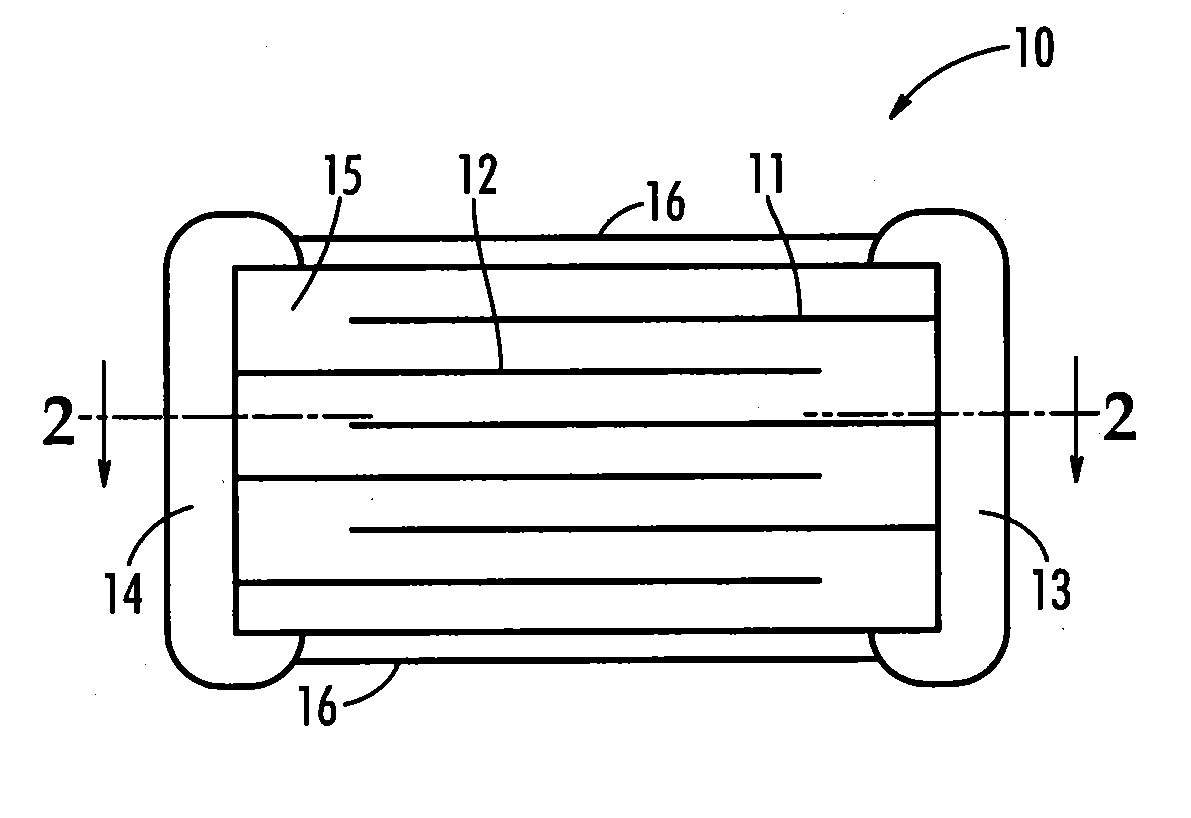

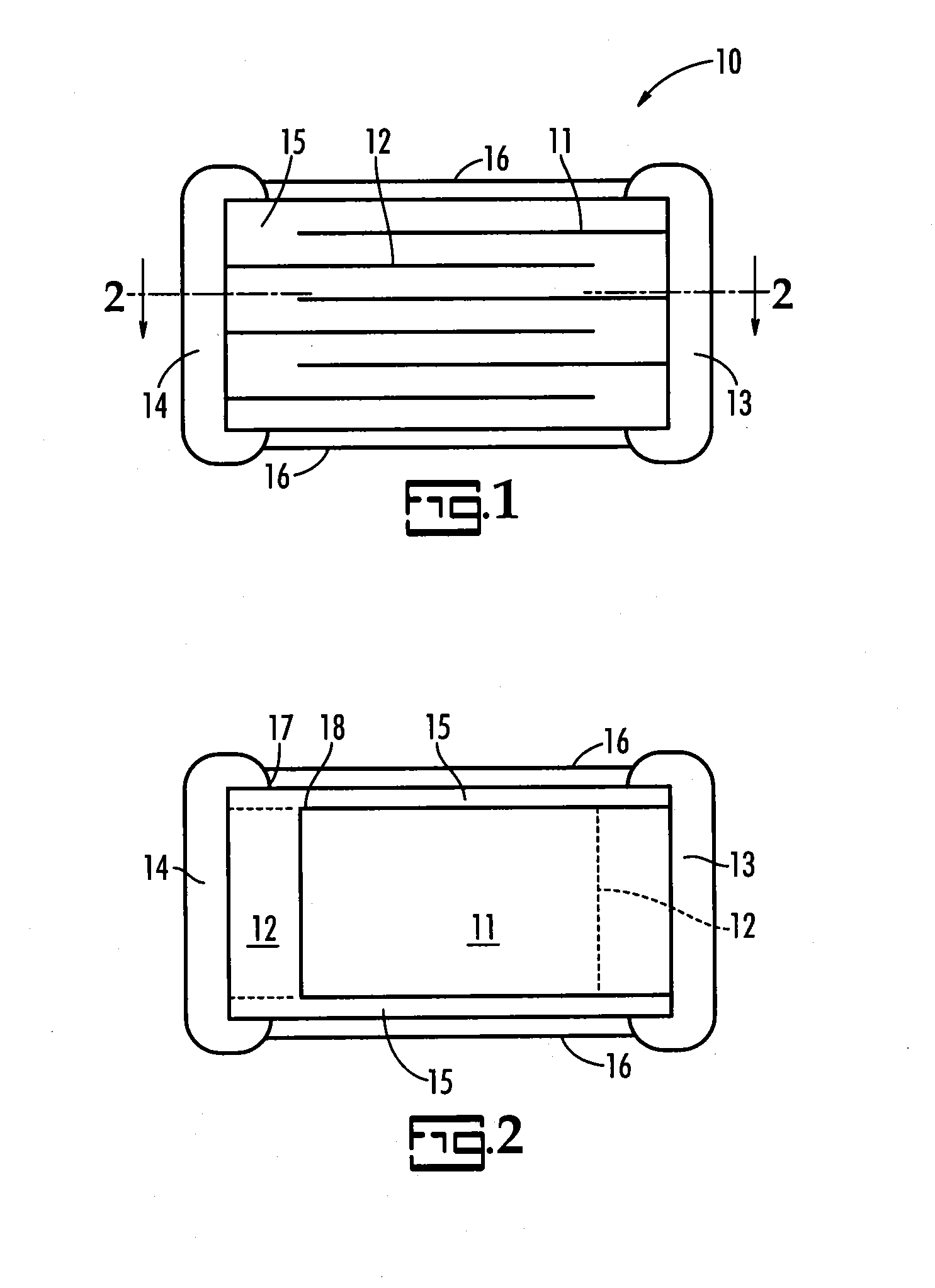

High capacitance multilayer with high voltage capability

ActiveUS20110002082A1Improve adhesionFixed capacitor electrodesFixed capacitor dielectricCapacitanceState of art

Owner:KEMET ELECTRONICS CORP

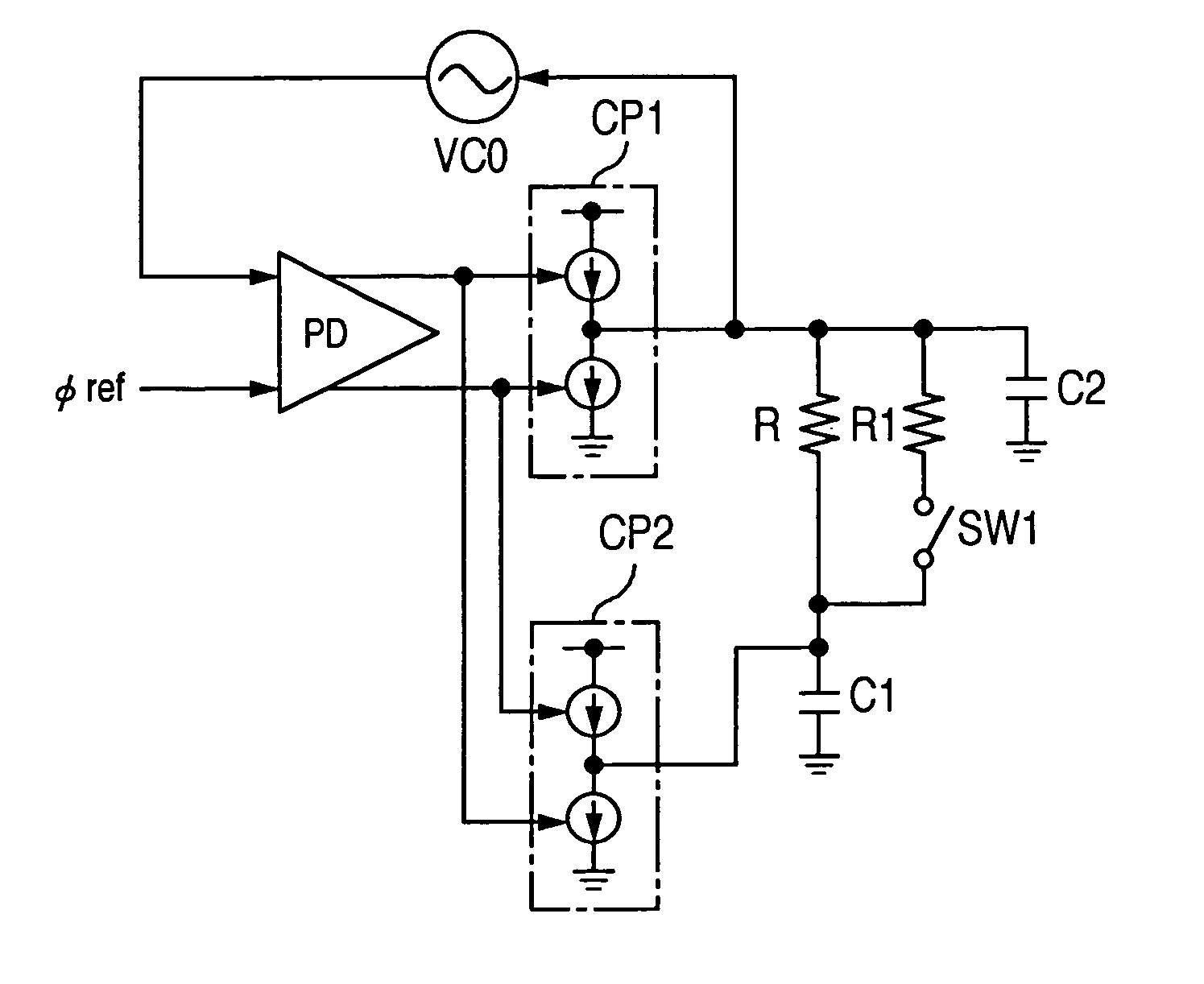

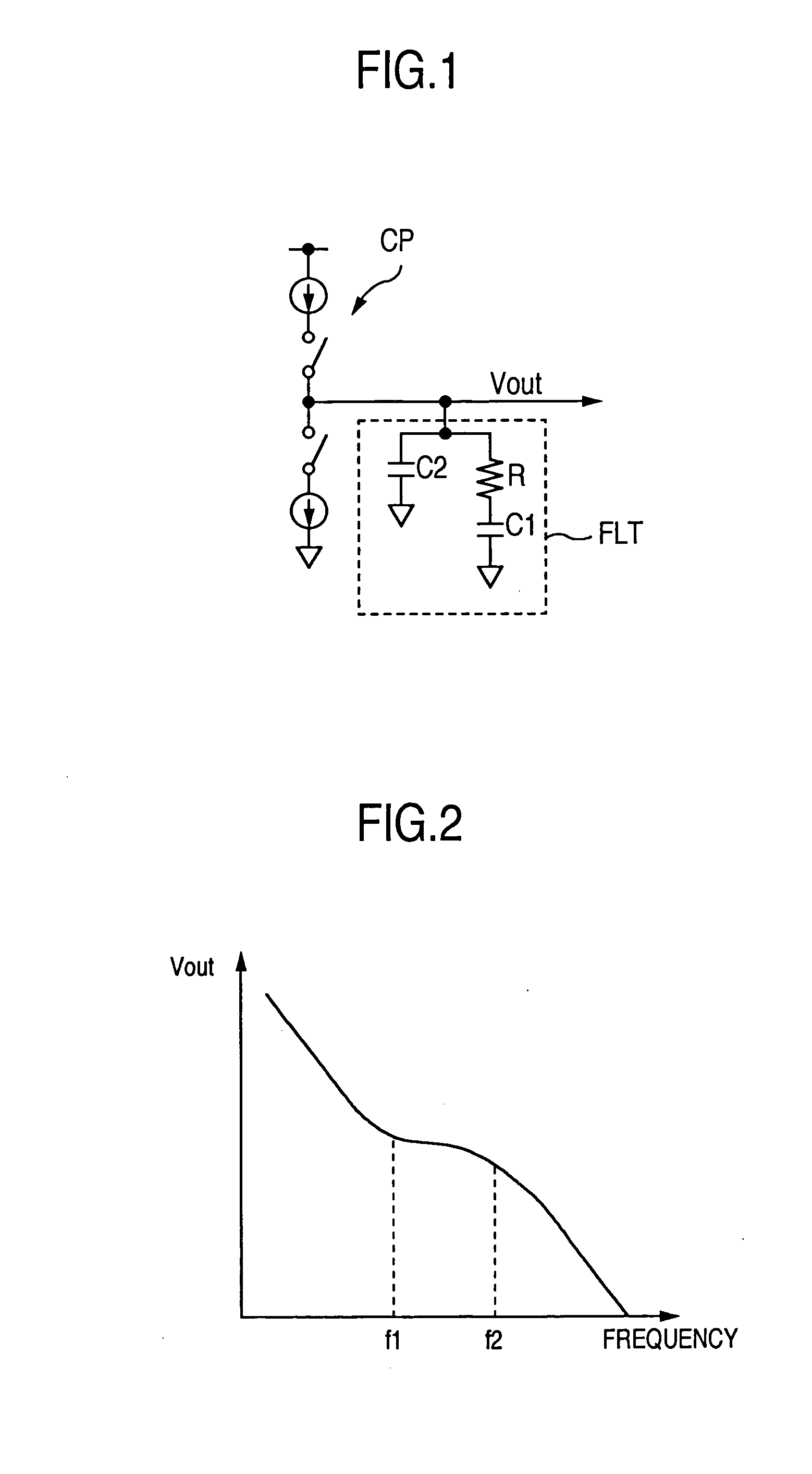

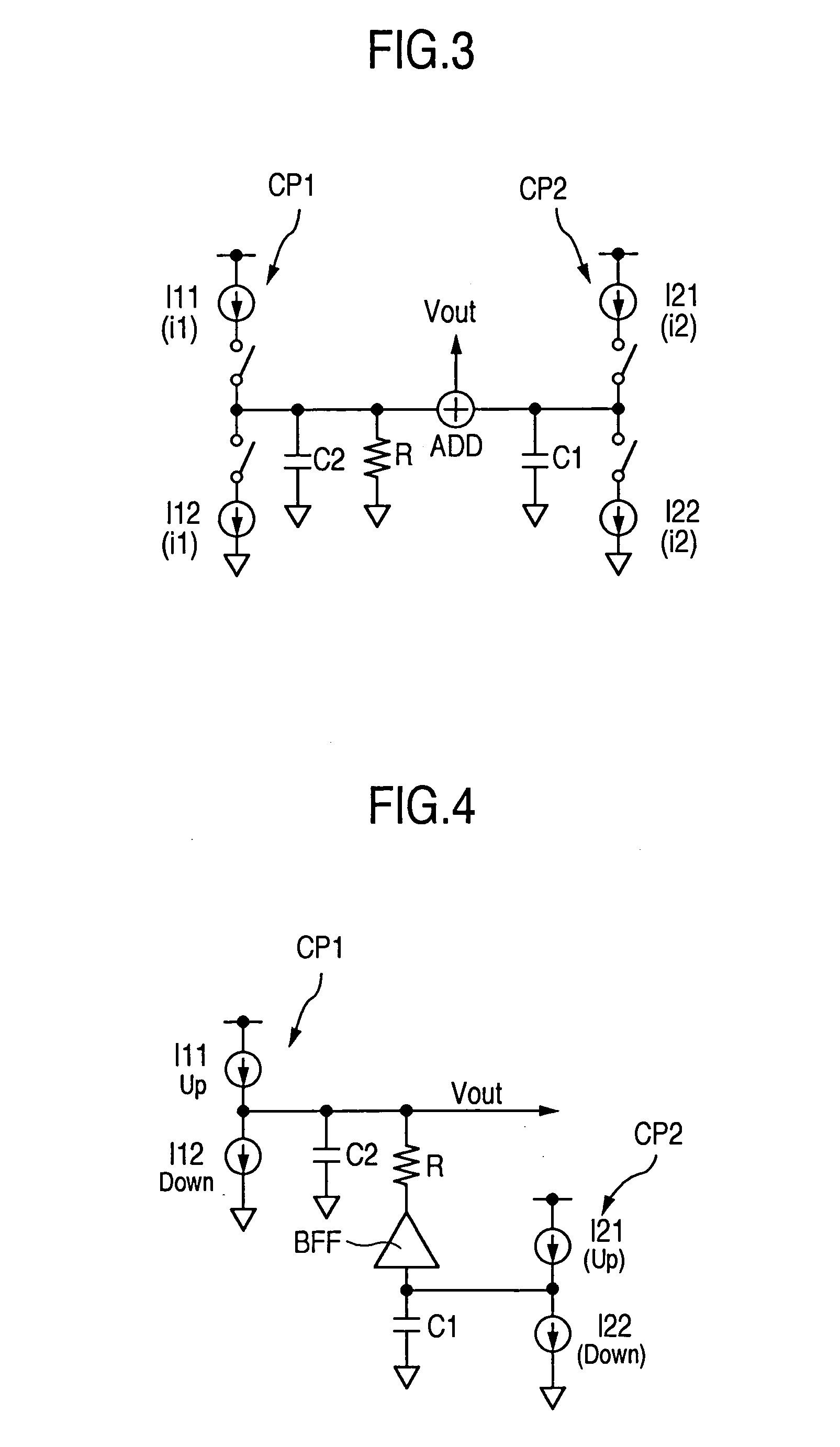

Semiconductor integrated circuit having built-in PLL circuit

ActiveUS20050134391A1Avoid mistakesEliminate needPulse automatic controlAngle demodulation by phase difference detectionCapacitanceEngineering

Owner:RENESAS ELECTRONICS CORP +1

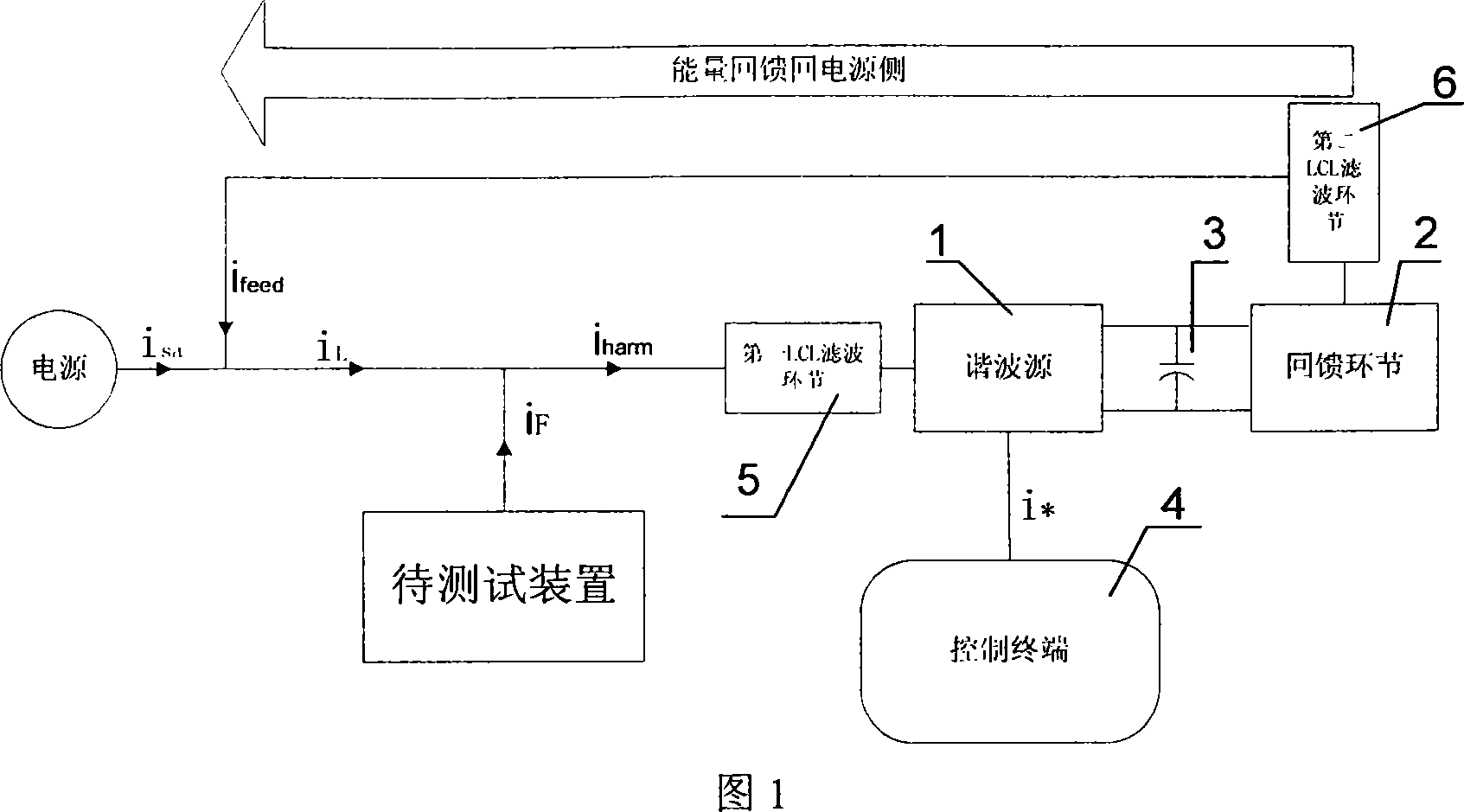

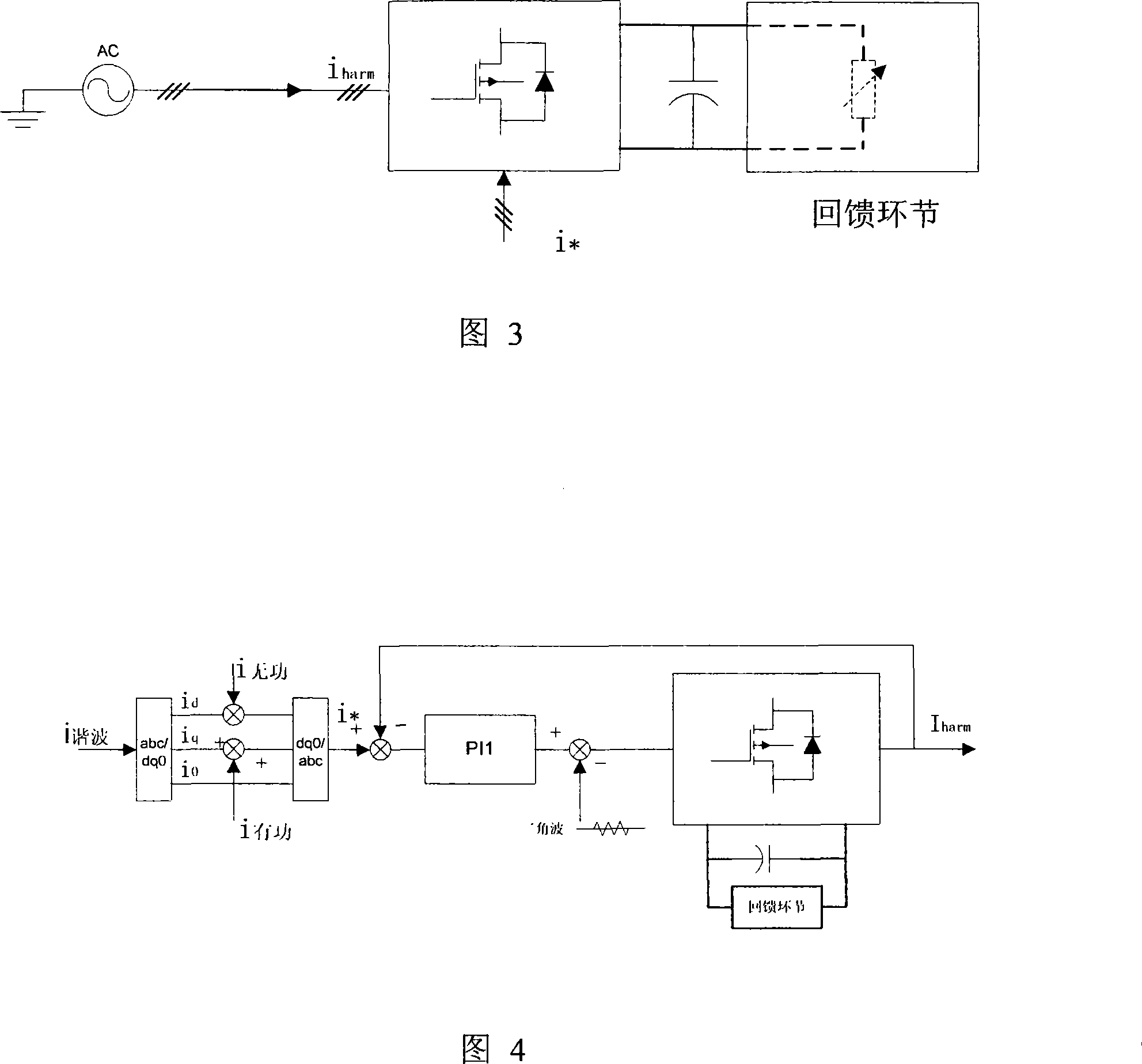

Energy feeding type electrical energy mass perturbance generating device

Owner:SOUTHEAST UNIV

Amorphous silicon image sensor with storage capacitor structure

ActiveCN102157533AIncreased charge storage capacityImprove signal dynamic rangeRadiation controlled devicesCapacitanceDynamic range

Owner:CARERAY DIGITAL MEDICAL TECH CO LTD

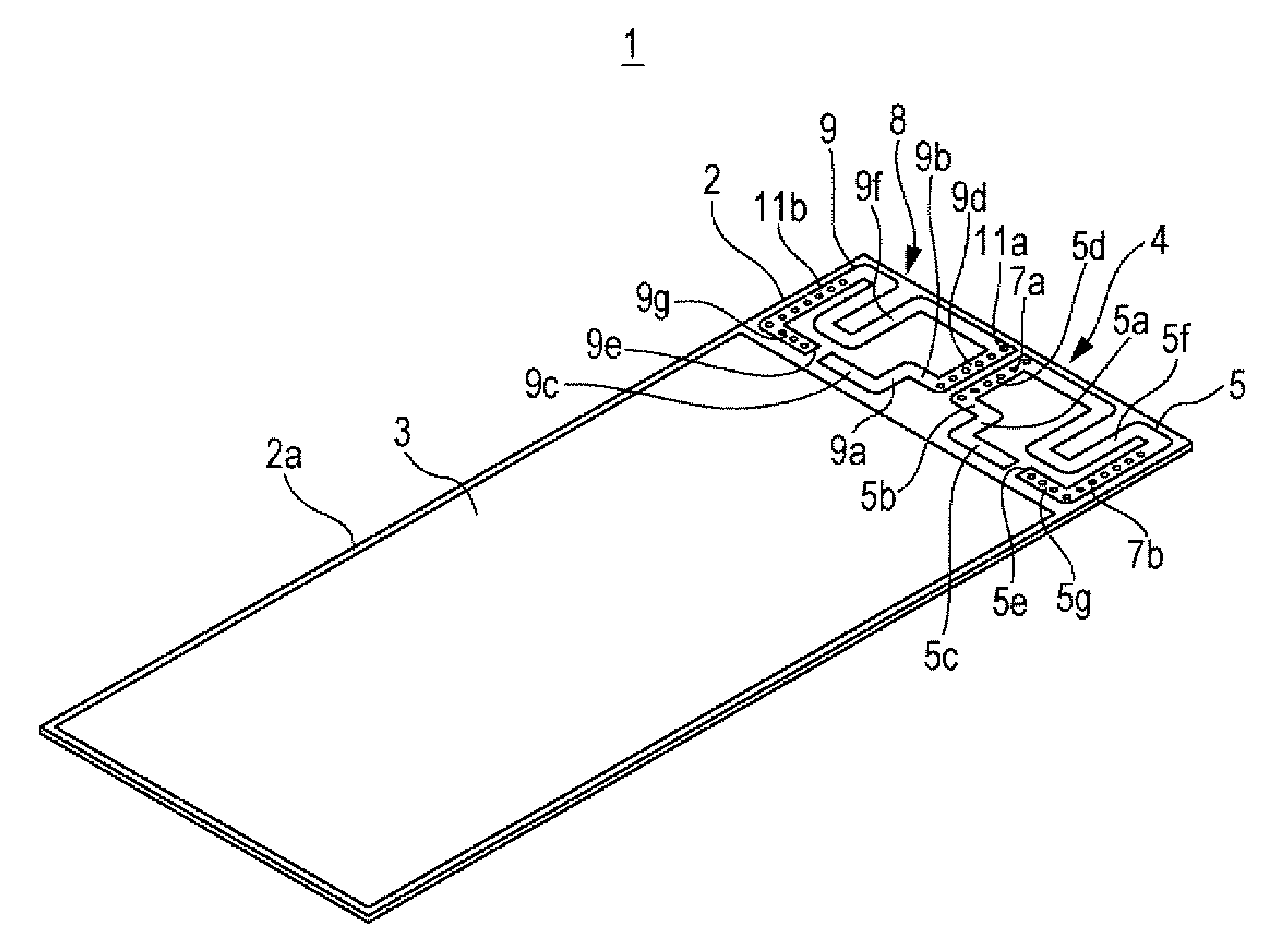

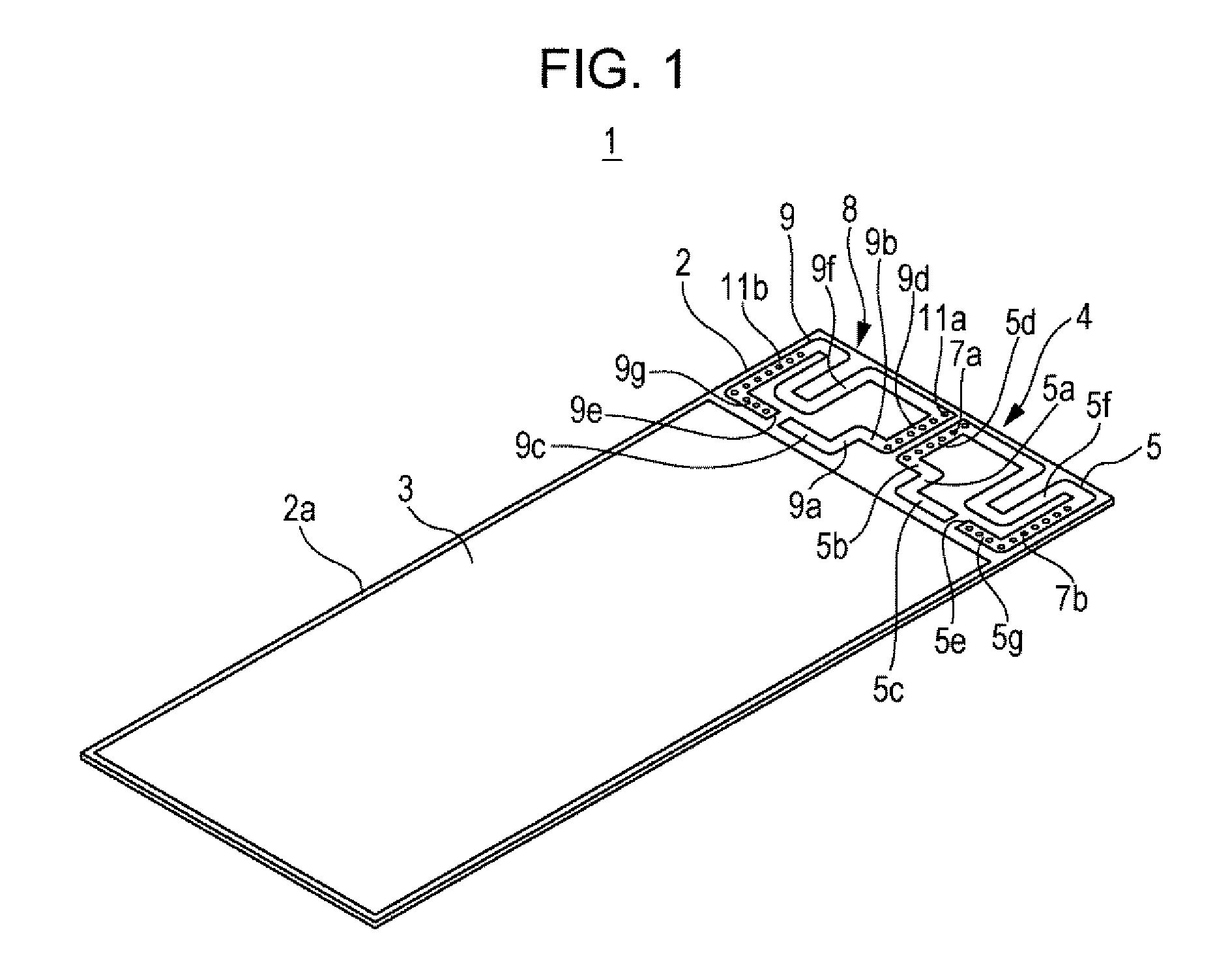

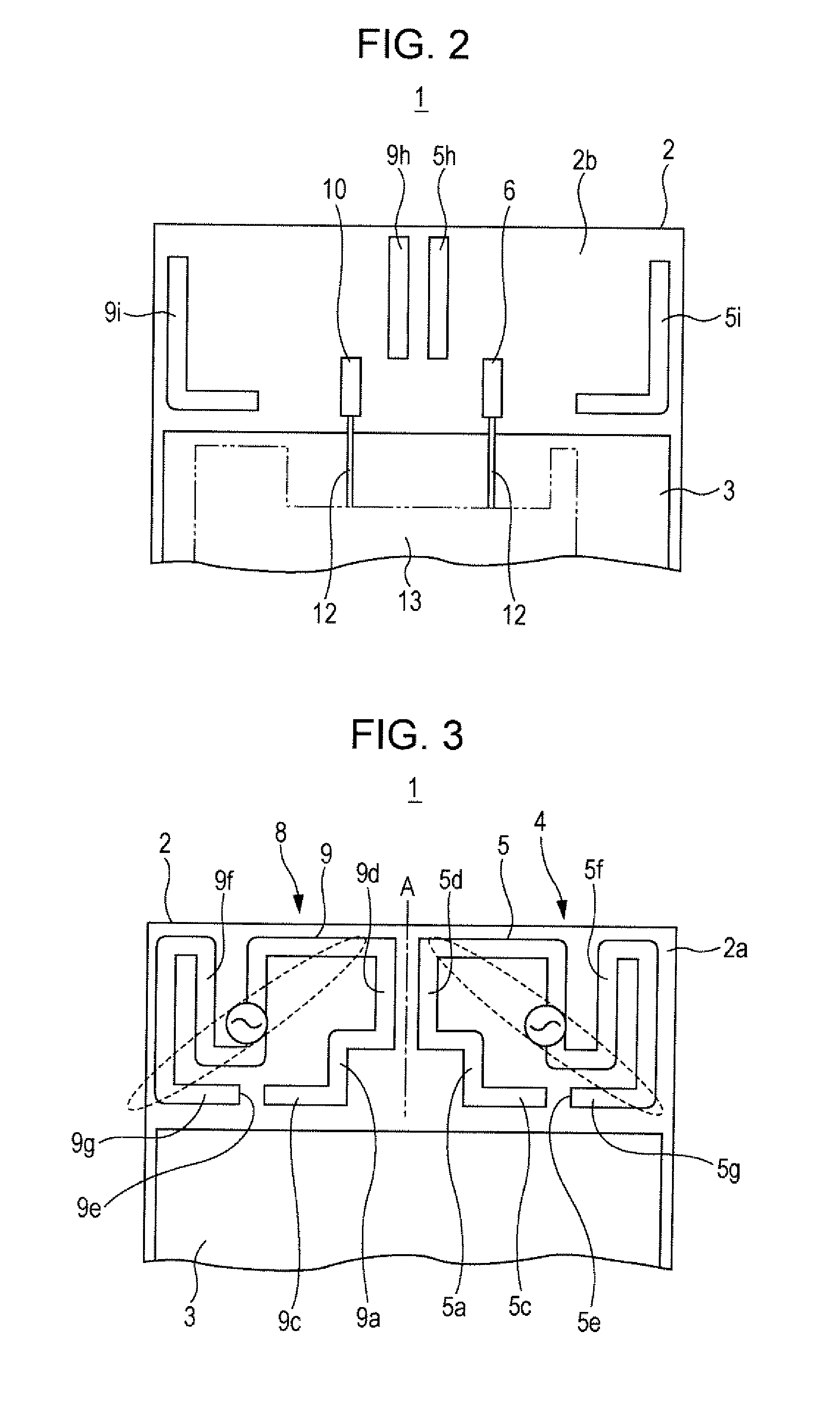

Antenna apparatus

ActiveUS20110133992A1Avoid interferenceSmall sizeSimultaneous aerial operationsRadiating elements structural formsCapacitanceElectricity

Owner:ALPS ALPINE CO LTD

Variable capacitance element and tunable filter

ActiveUS20130342285A1Reduce size and thicknessSmall sizeImpedence networksCapacitor with voltage varied dielectricCapacitanceDielectric layer

A variable capacitance element includes a piezoelectric substrate, a buffer layer located on the piezoelectric substrate with an orientation, a dielectric layer located on the buffer layer and having a relative dielectric constant that varies in accordance with an applied voltage, and a first electrode and a second electrode arranged to apply an electric field to the dielectric layer.

Owner:MURATA MFG CO LTD

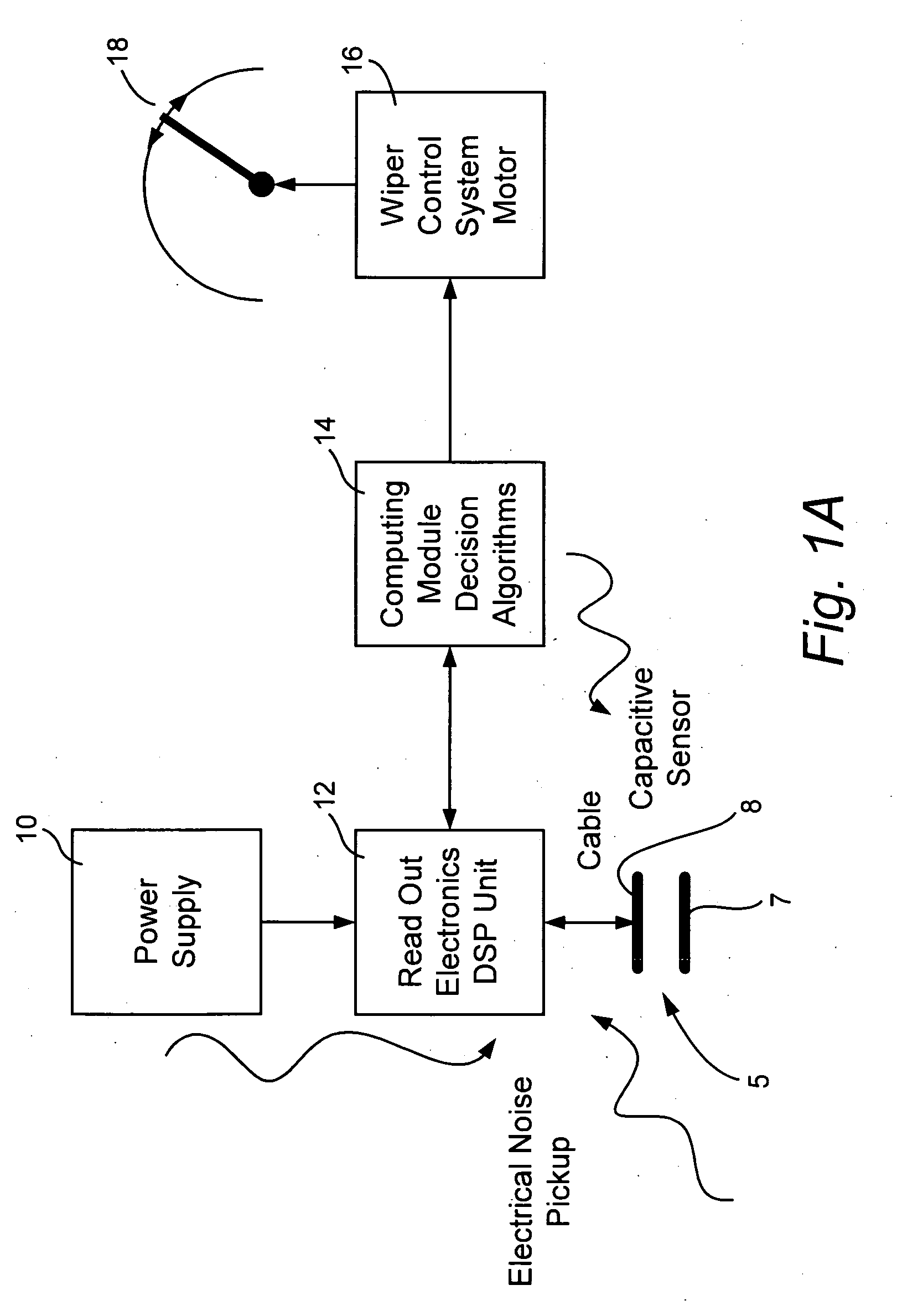

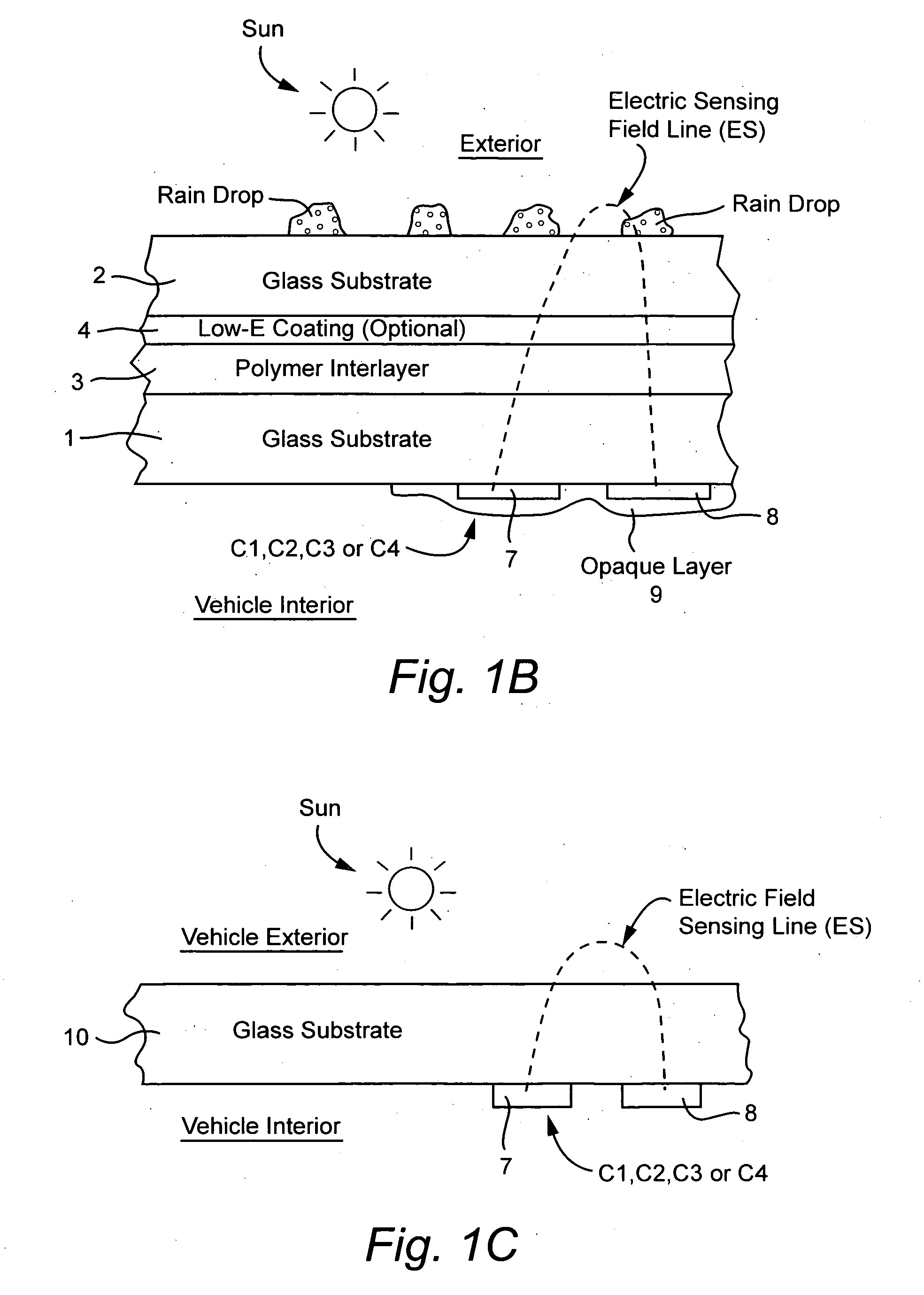

Rain sensor with sigma-delta modulation and/or footprinting comparison(s)

InactiveUS20070157721A1Hazard reductionReduce distractionsDC motor speed/torque controlEmergency protective circuit arrangementsCapacitanceEngineering

Owner:GUARDIAN GLASS LLC

Active SOI structure with a body contact through an insulator

Owner:POLARIS INNOVATIONS

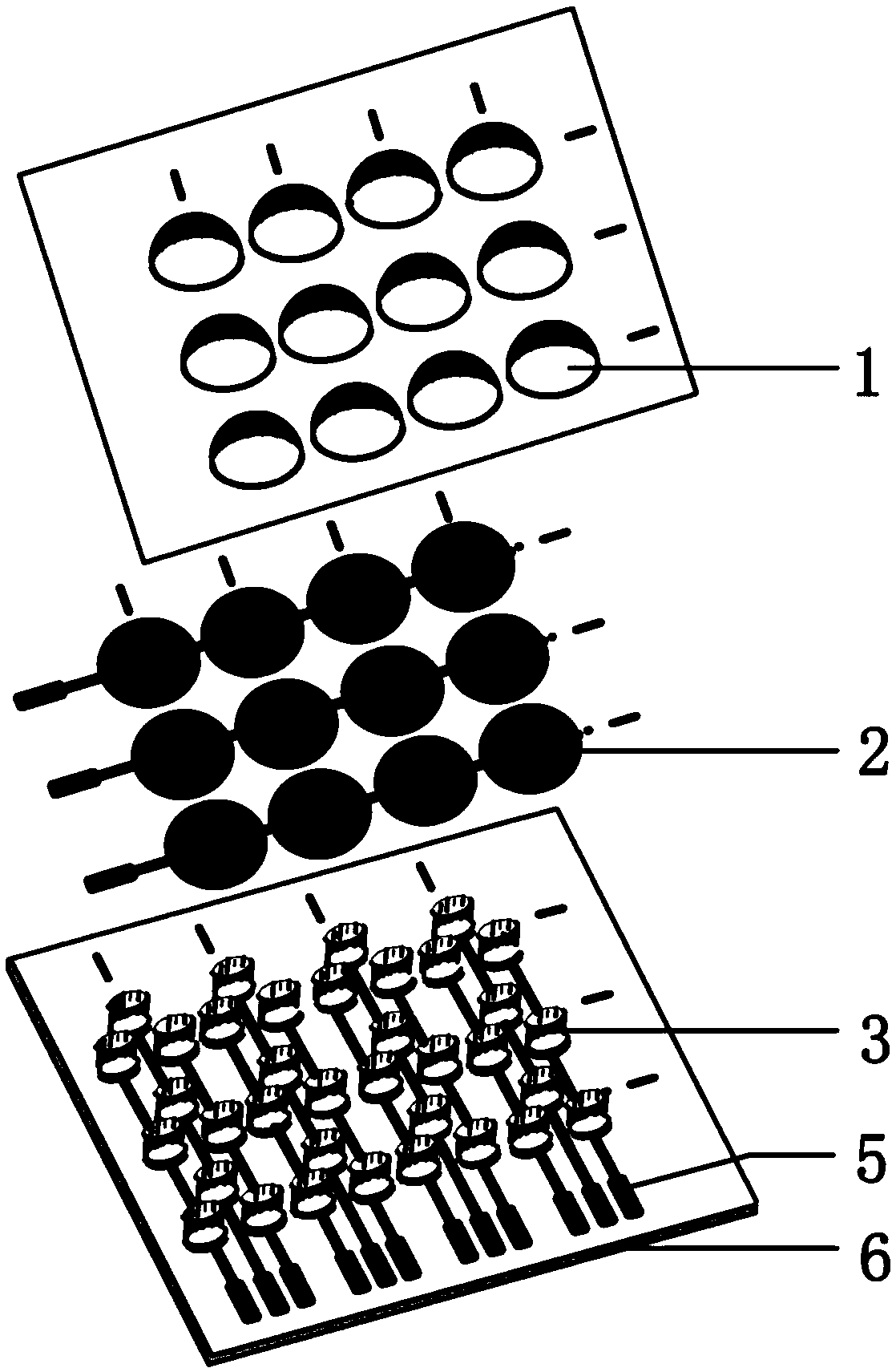

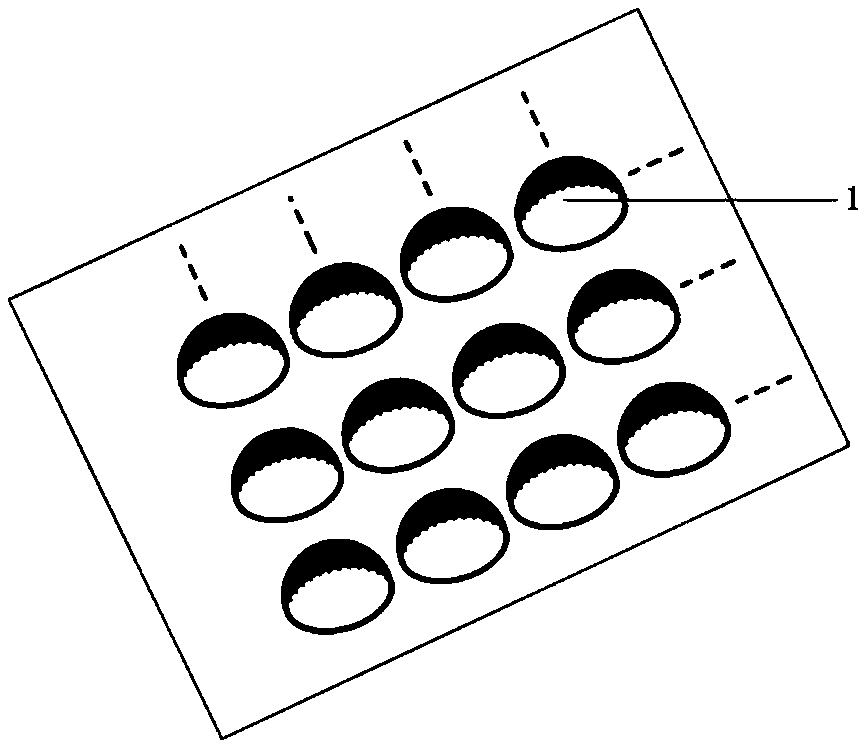

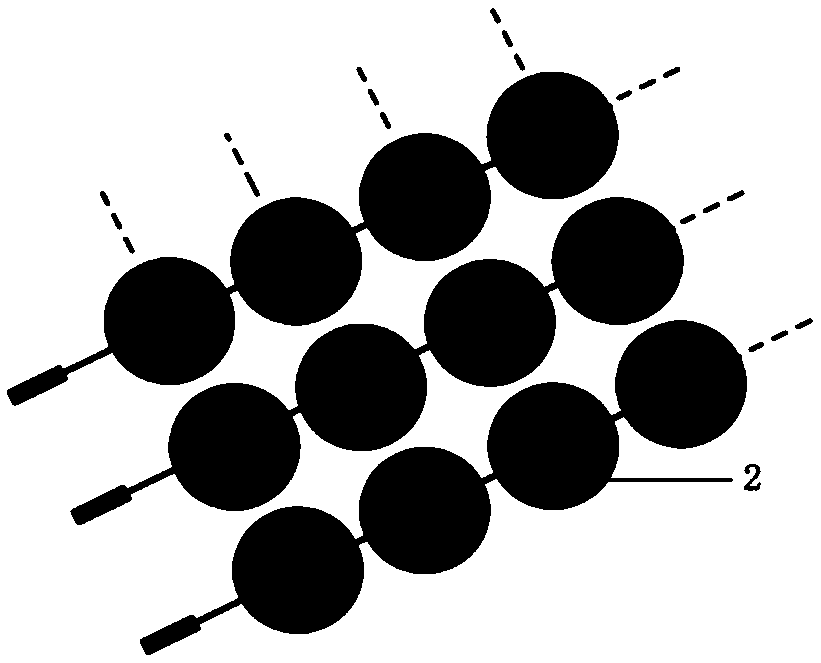

Flexible piezoelectric three-dimensional tactile sensor array and preparation method thereof

PendingCN109406012AForce measurement using piezo-electric devicesConverting sensor output electrically/magneticallyCapacitanceTactile sensor

Owner:SOUTH CHINA UNIV OF TECH

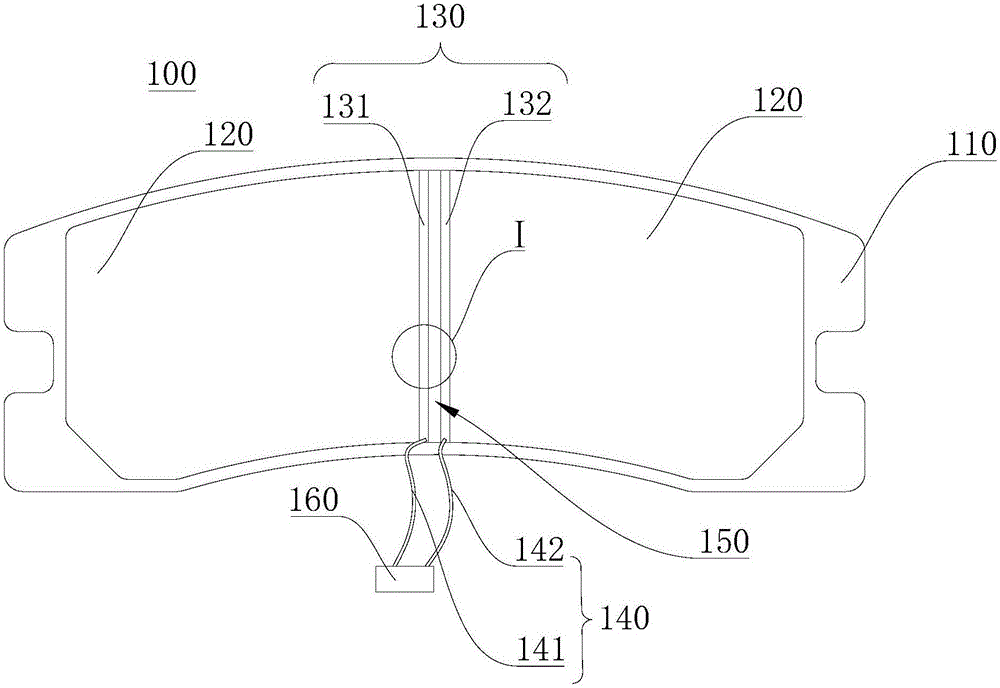

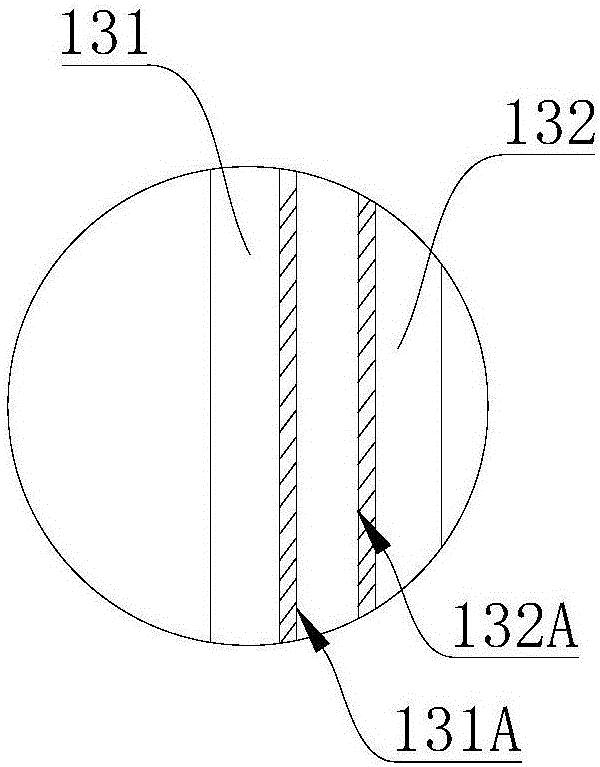

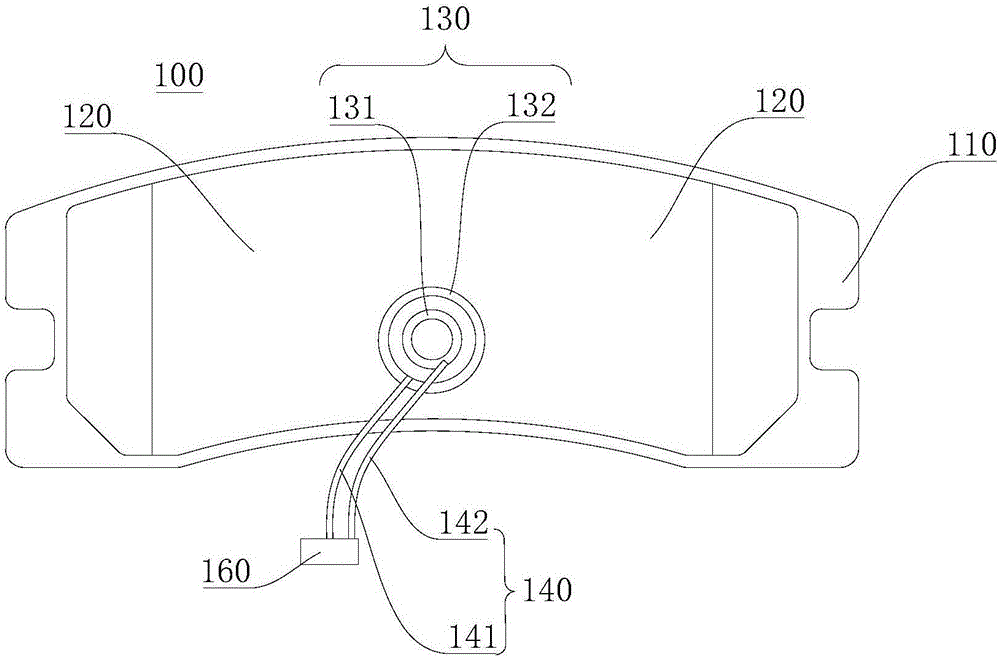

Brake pad and thickness detection method

InactiveCN106556336ABraking membersElectrical/magnetic thickness measurementsThermal insulationCapacitance

Owner:TONGREN UNIV

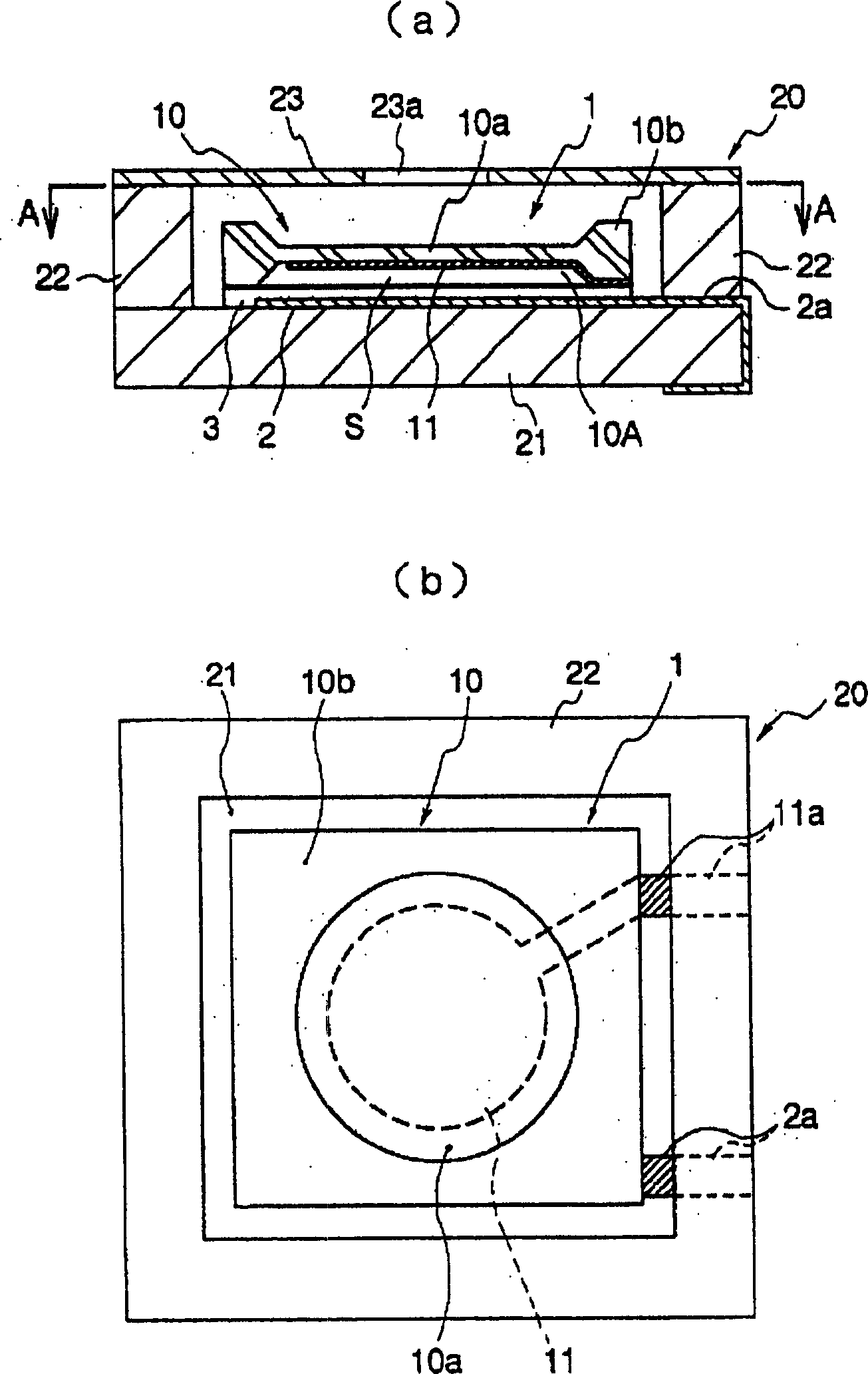

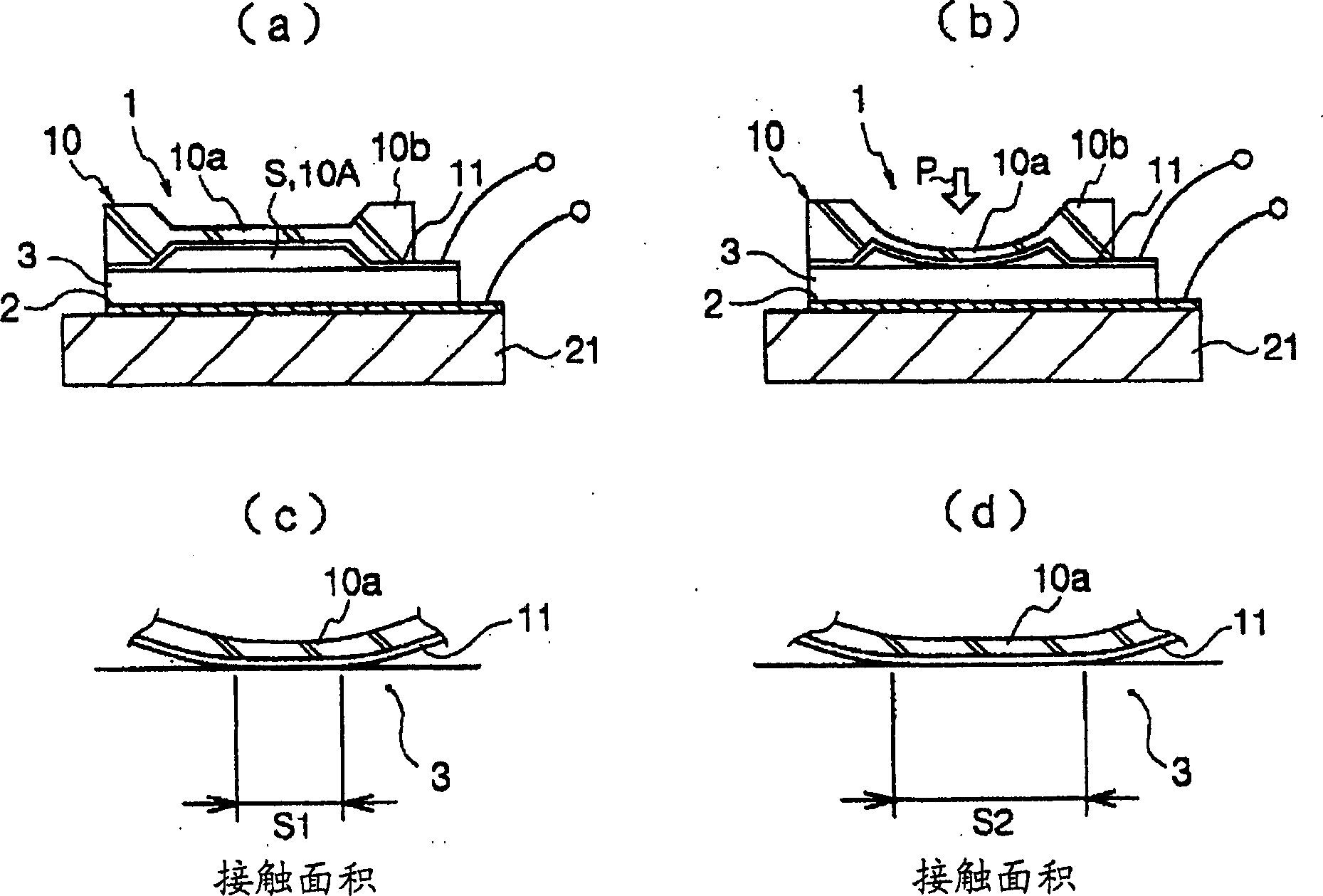

Quartz type pressure sensor, and production method therefor

InactiveCN1813179AEasy to strictly manage the thicknessLittle change over the yearsFluid pressure measurement using capacitance variationDielectricCapacitance

Owner:SEIKO EPSON CORP

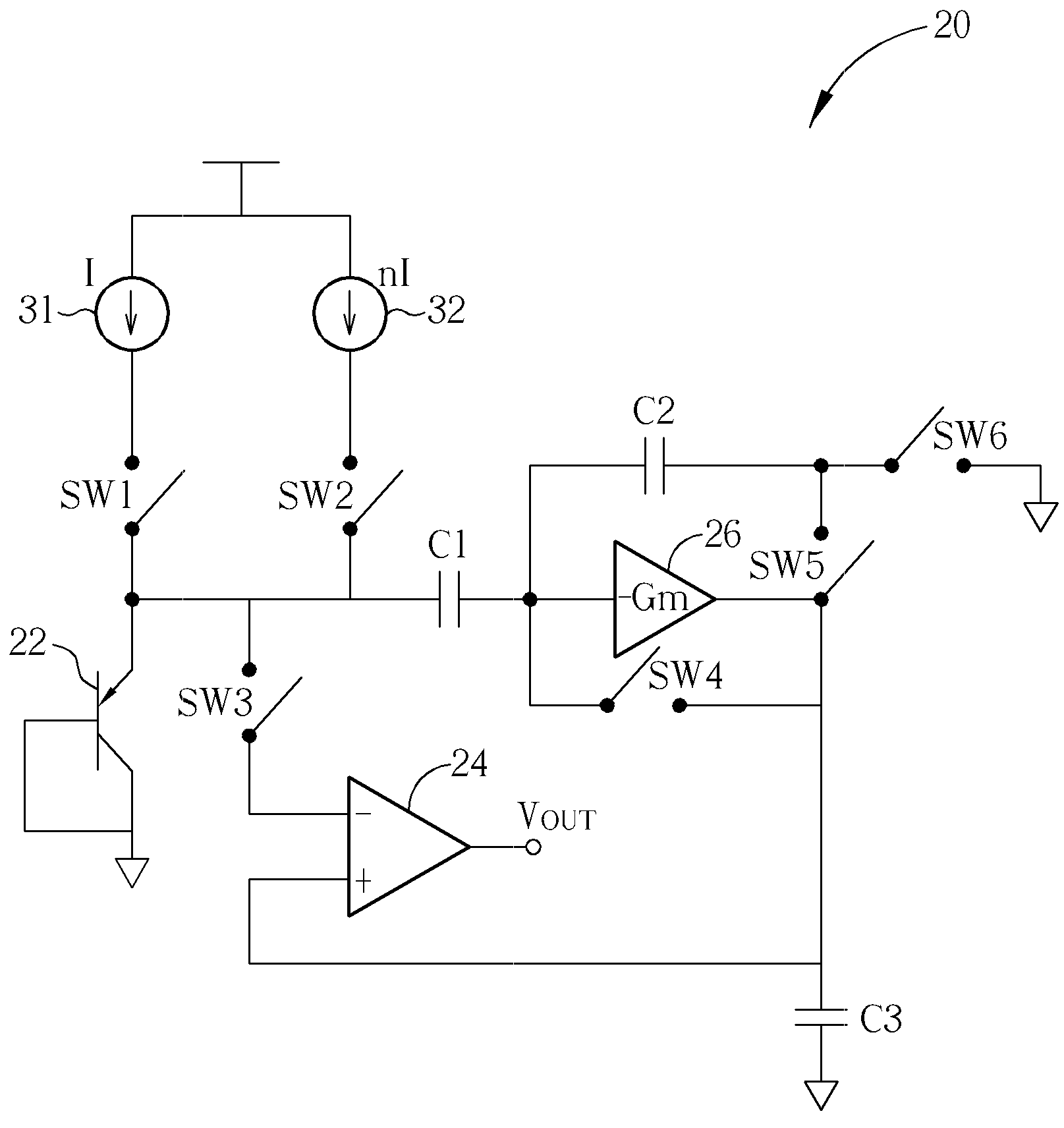

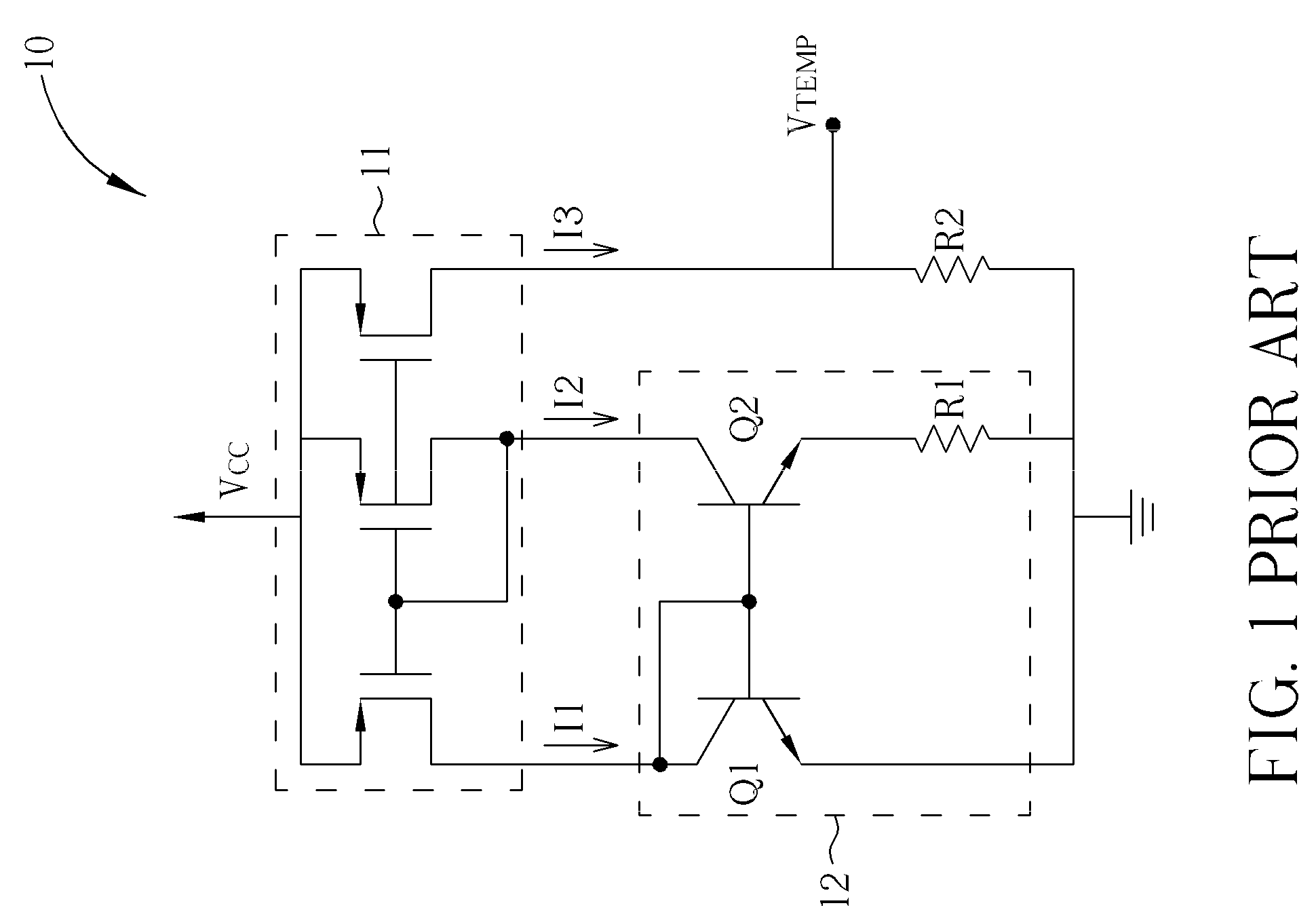

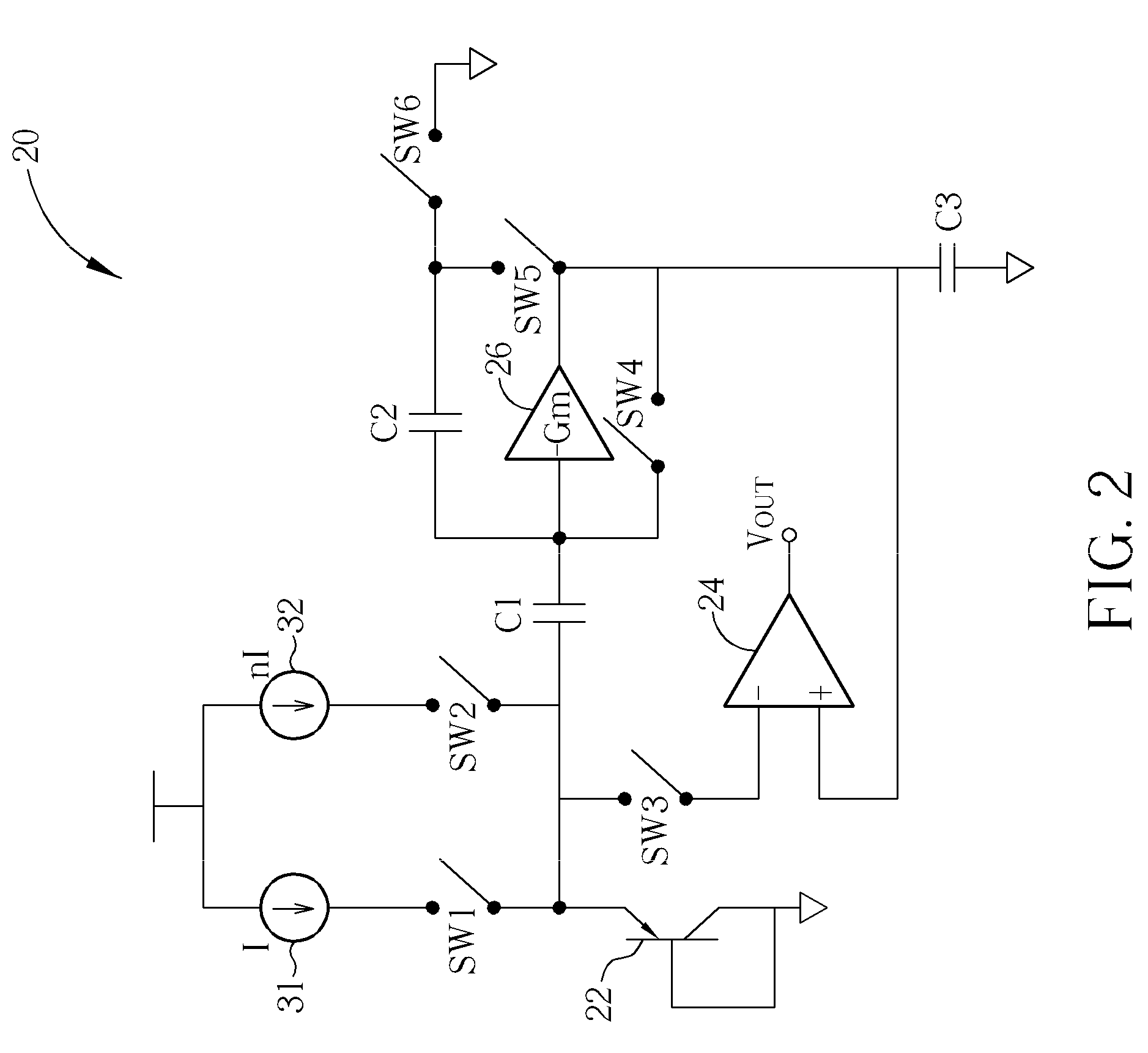

Temperature sensing circuit using CMOS switch-capacitor

InactiveUS20100111137A1Thermometers using electric/magnetic elementsUsing electrical meansTransconductanceCapacitance

Owner:ADVANCED ANALOG TECH INC

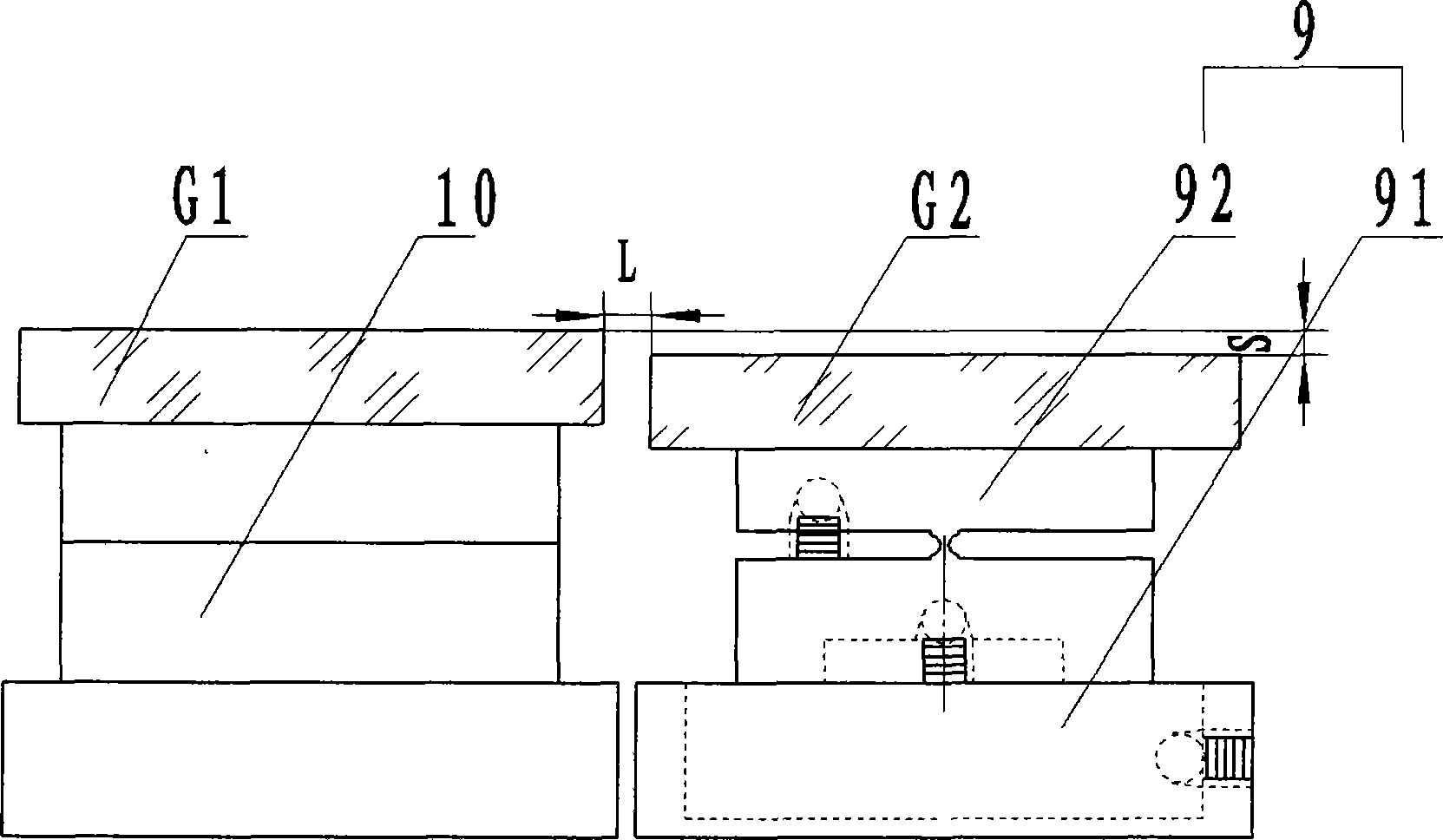

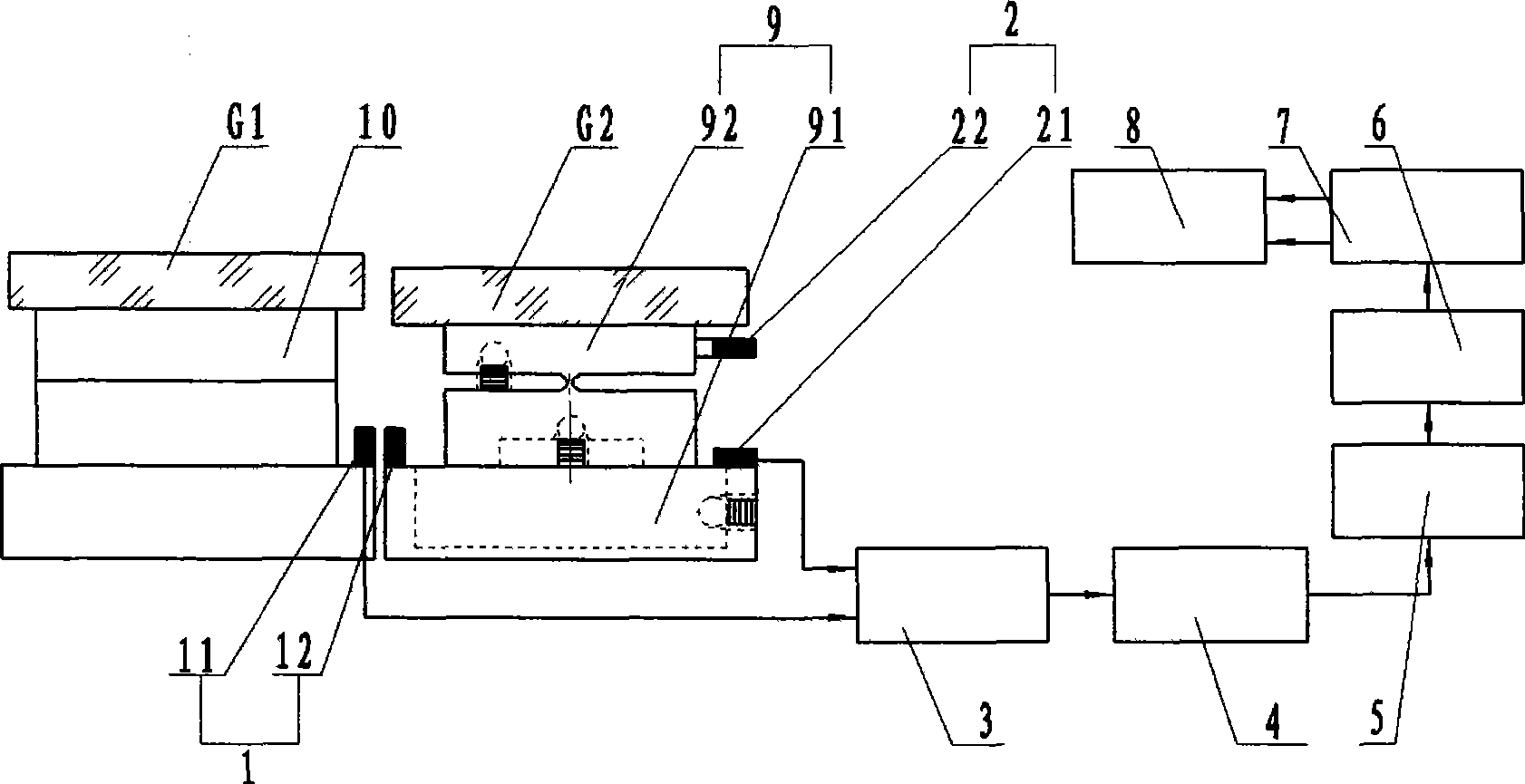

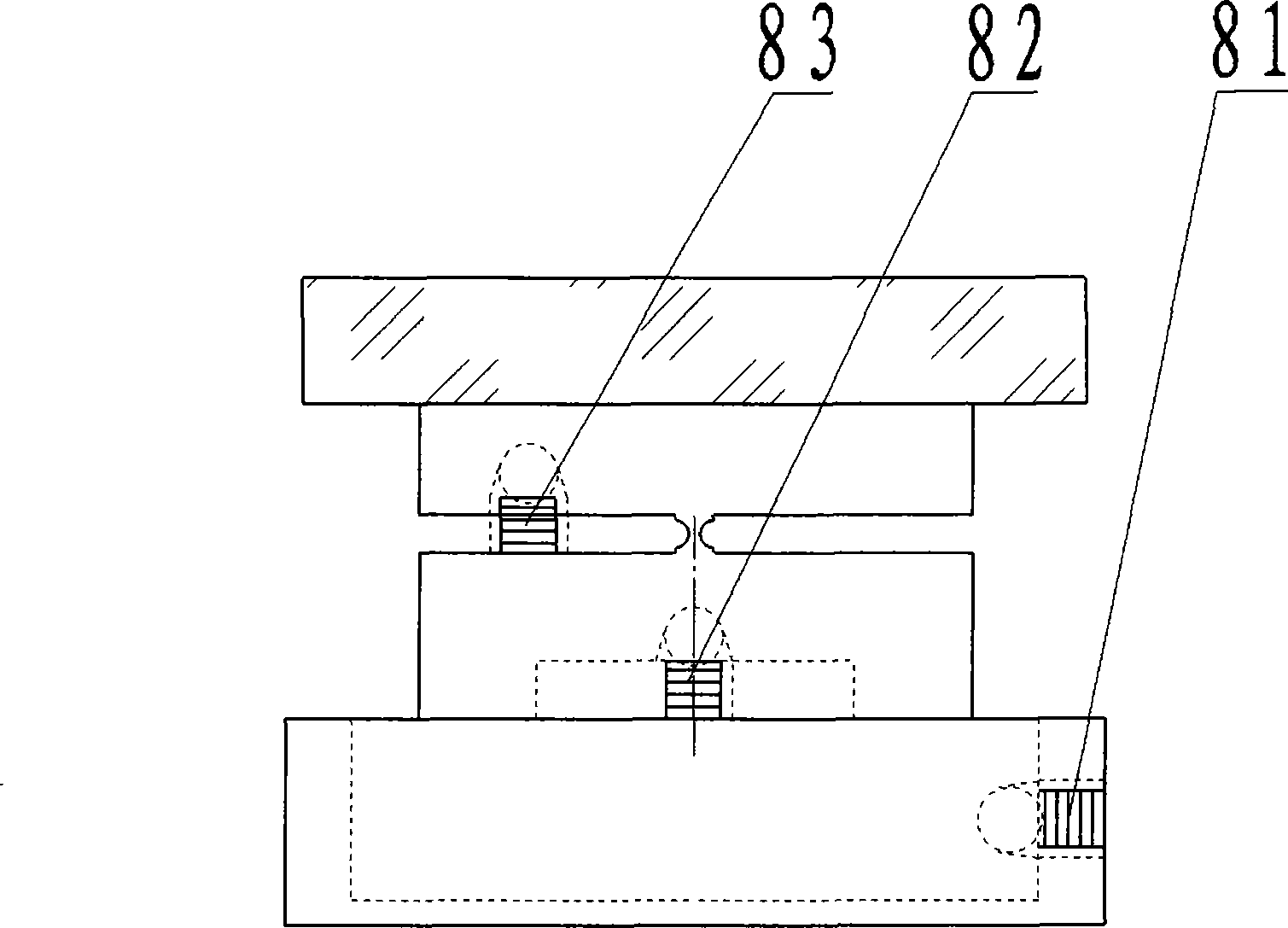

Split pattern displacement deviation monitoring system

InactiveCN101419319AImprove stabilityGood adjustment and control stabilityUsing electrical meansMountingsElectricityCapacitance

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

Method of forming an ESD protection device

InactiveUS20010010954A1Lower breakdown voltageLower junction capacitanceTransistorThyristorCapacitanceGate dielectric

The invention discloses a method of forming an ESD protection device without adding the extra mask layers into the traditional CMOS process. At first, P-wells, N-wells, and isolations are formed in a semiconductor substrate. Next, an NMOS transistor with a gate dielectric layer, a gate electrode, source / drain regions, lightly doped source / drain regions, and insulator spacers is formed on the substrate. Particularly, N-wells are also formed in a part of the source / drain regions of the NMOS transistor. Thereafter, ESD protection regions are formed under the source / drain regions by performing P+ ESD protection implantation. Such ESD protection device has a low junction breakdown voltage, quick response speed, and a small junction capacitance.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

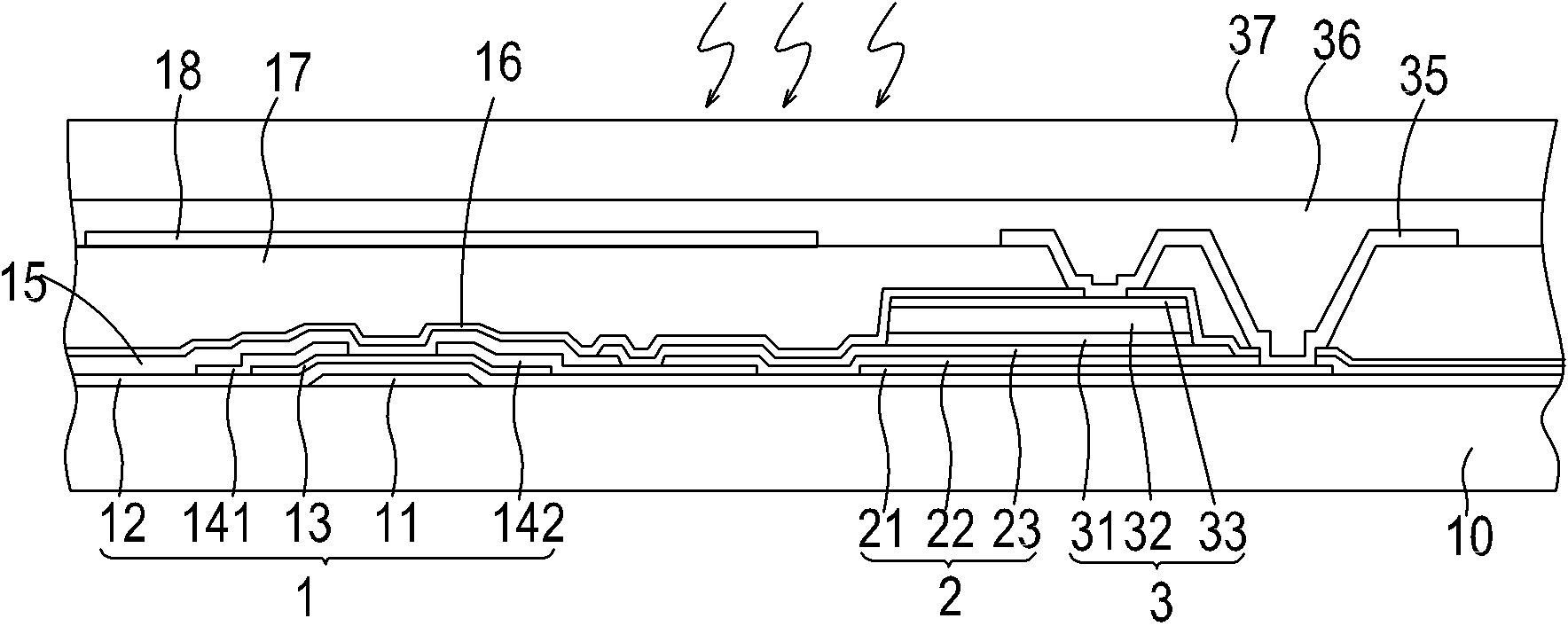

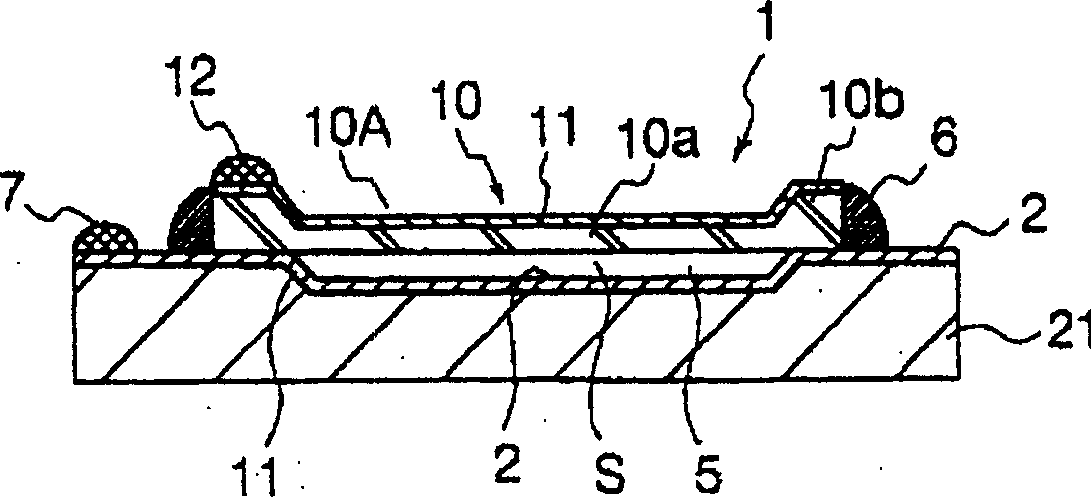

Semiconductor device and display device utilizing the same

InactiveUS20060187730A1High currentLess influenceStatic indicating devicesDigital storageCapacitanceElectrical resistance and conductance

Owner:SEMICON ENERGY LAB CO LTD

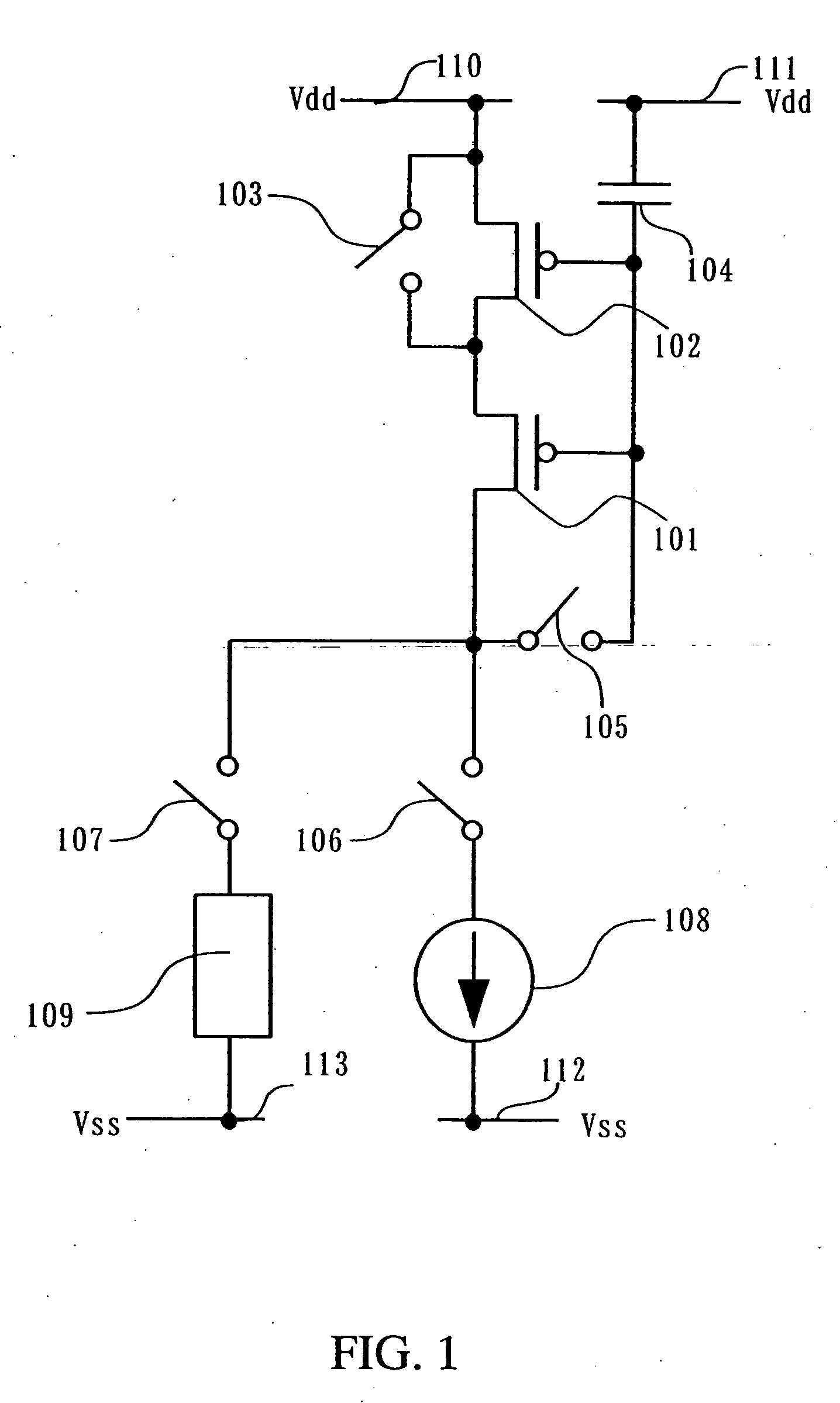

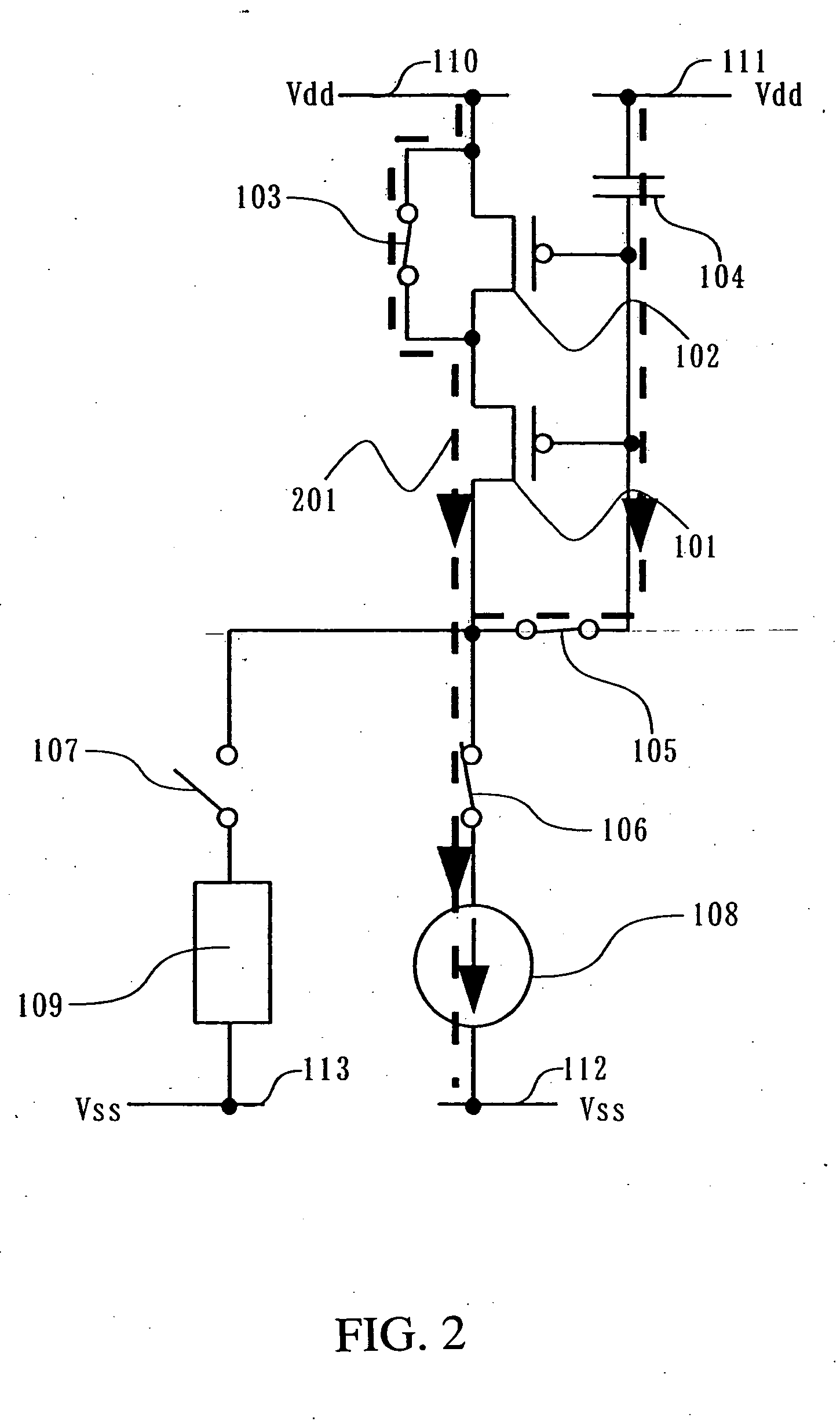

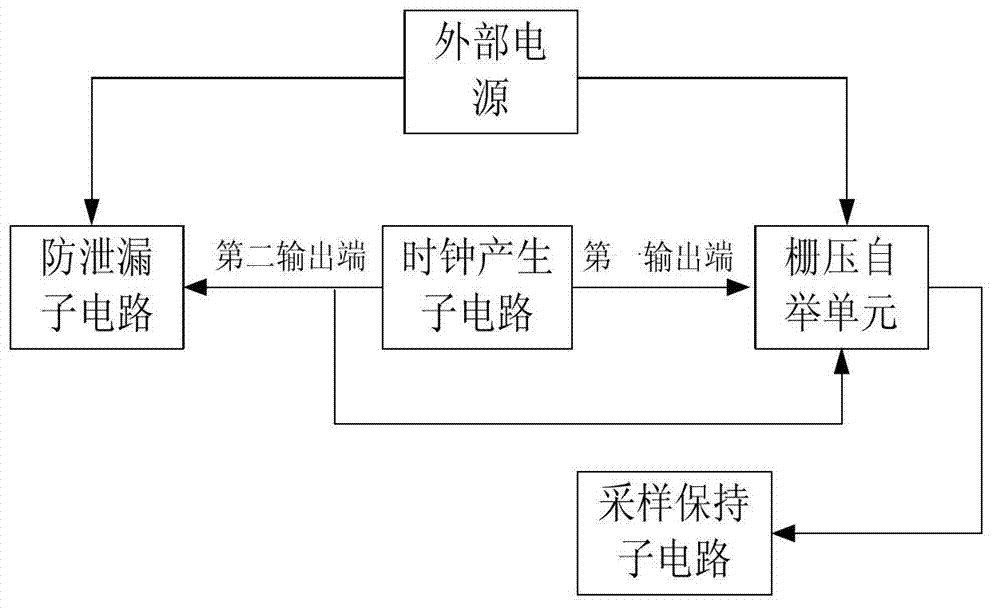

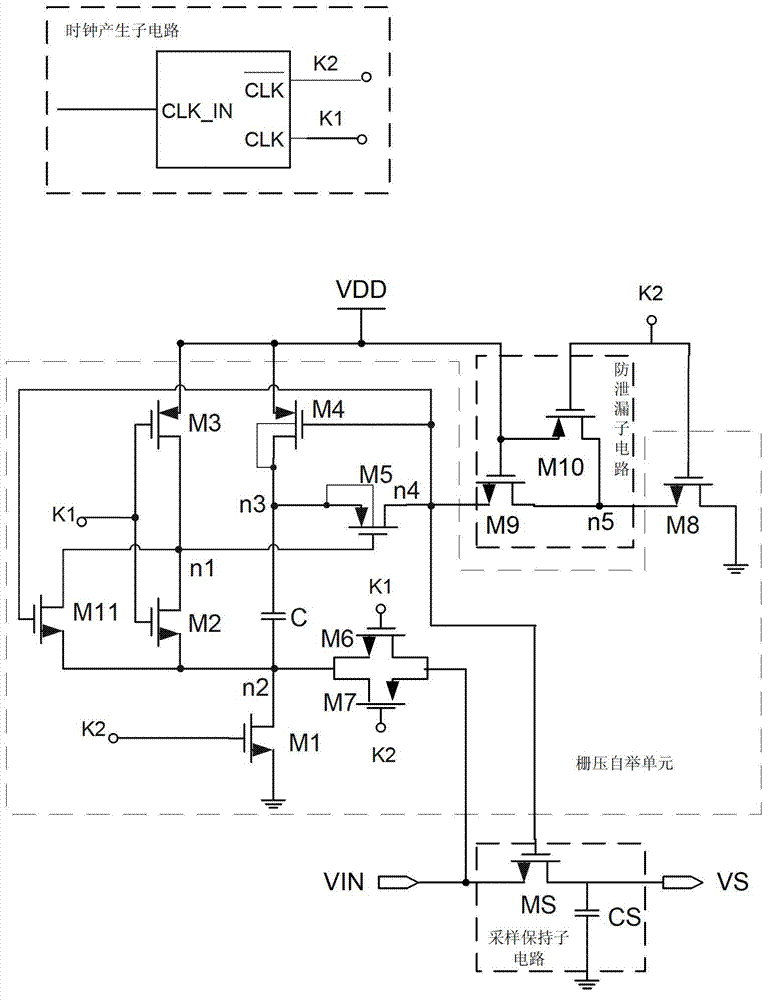

Sampling hold circuit

InactiveCN103036569ALeak won'tImprove linearityAnalogue/digital conversionElectric signal transmission systemsCapacitanceLinearity

Owner:IPGOAL MICROELECTRONICS (SICHUAN) CO LTD

Substrate for liquid crystal display and liquid crystal display having the same

InactiveUS20050248700A1Improve display qualitySimple processTransistorNon-linear opticsCapacitanceLiquid-crystal display

The invention relates to a liquid crystal display used in a display section of an electronic apparatus and a liquid crystal display substrate used for the same and provides a liquid crystal display that can be manufactured through simplified manufacturing processes and that can provide high display quality and a liquid crystal display substrate used for the same. A configuration is employed which includes gate bus lines and drain bus lines formed on a substrate such that they intersect each other with an insulation film interposed therebetween and pixel electrodes provided so as to cover at least one of the gate bus lines and the drain bus lines with a dielectric layer interposed therebetween and forming parasitic capacities between the gate bus lines or drain bus lines and themselves.

Owner:SHARP KK

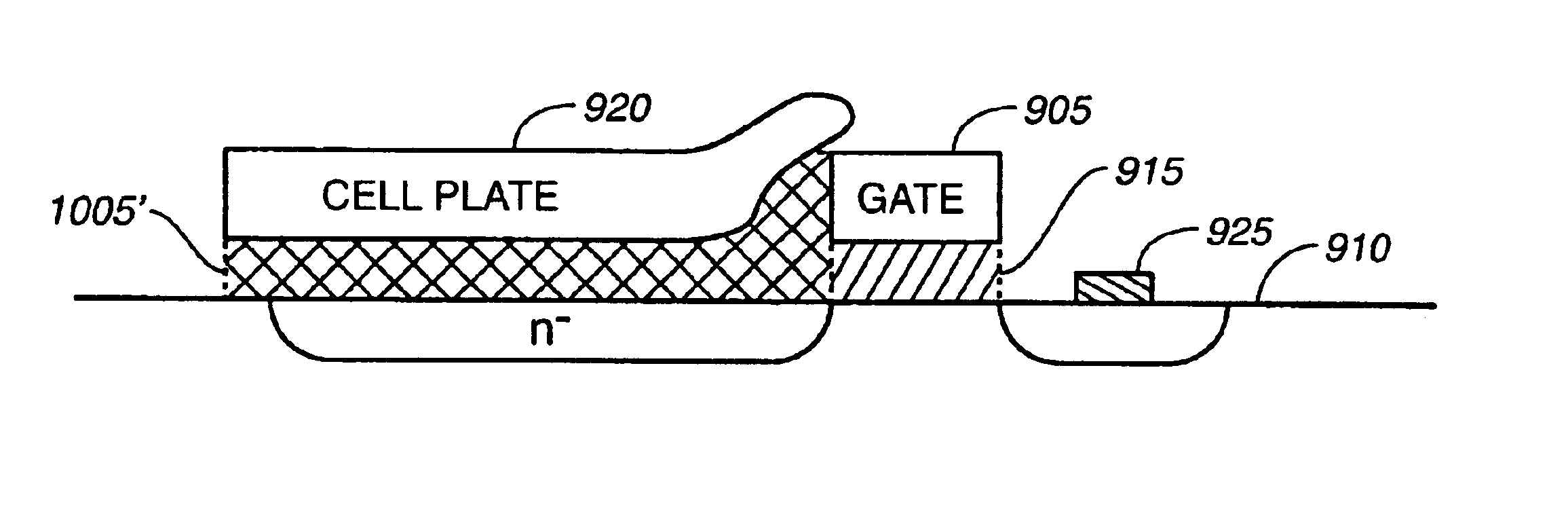

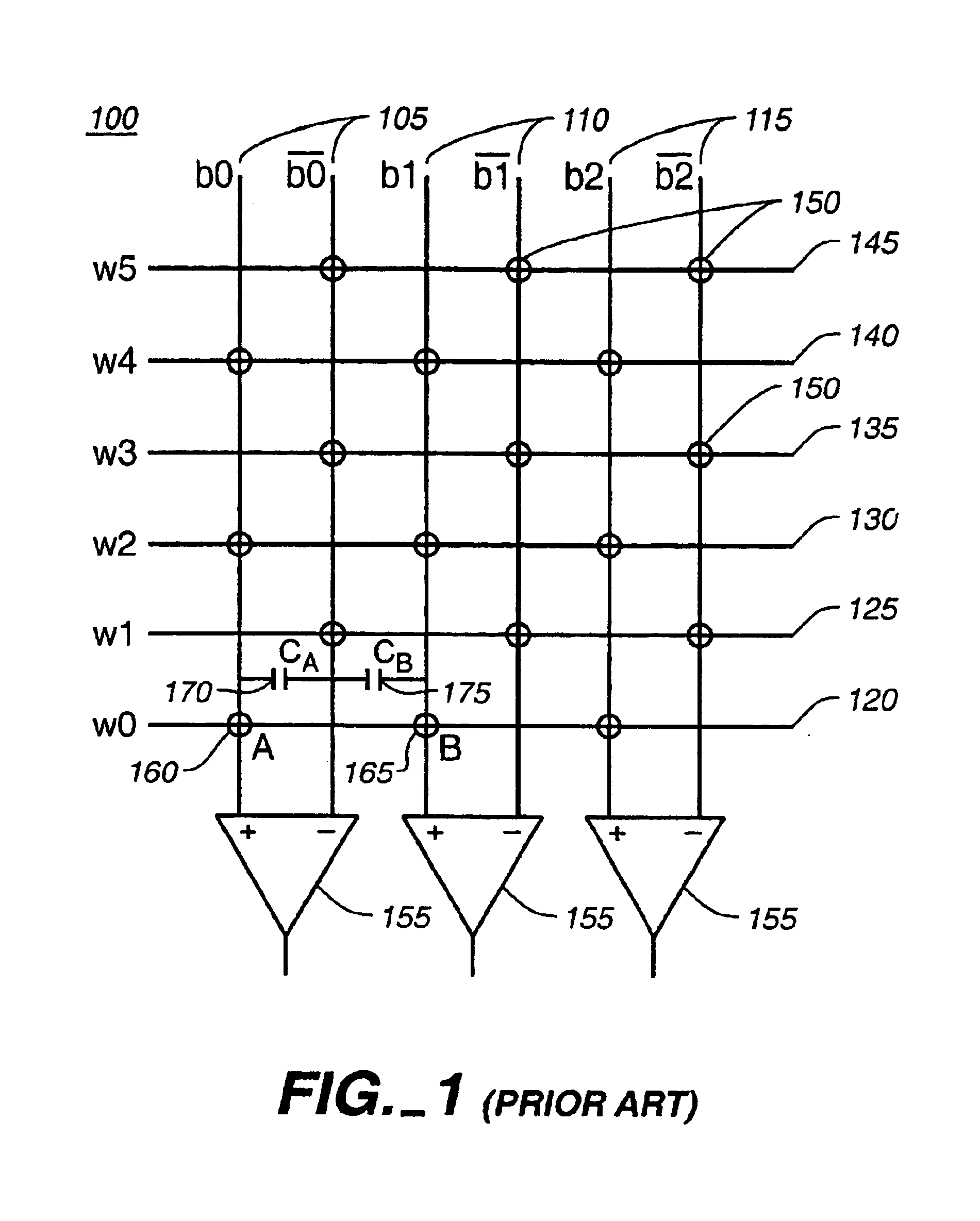

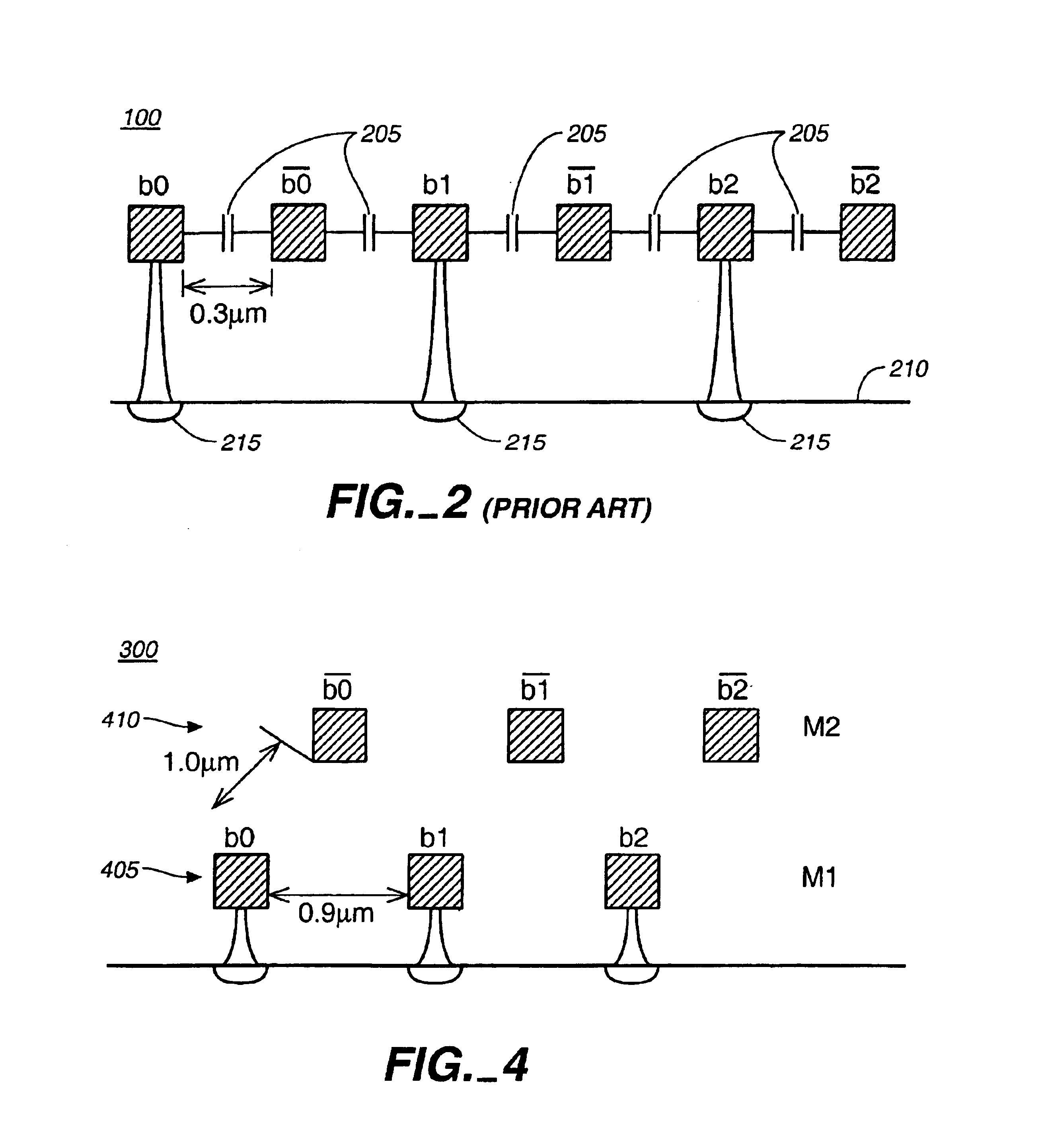

Logic process DRAM

InactiveUS6947324B1Line capacitance is decreasedReduce areaTransistorSolid-state devicesCapacitanceBit line

Owner:MARVELL ASIA PTE LTD

Semiconductor-device manufacturing method, semiconductor-device manufacturing program and semiconductor-device manufacturing system

InactiveUS20090183132A1Intensively manageEasy to manageSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceCapacitance

Owner:SONY CORP

Forming method of lead-acid battery electrode plate transplantation

ActiveCN1794491ALead-acid accumulator electrodesSecondary cells charging/dischargingCapacitanceCharge and discharge

Owner:ZHEJIANG NARADA POWER SOURCE CO LTD +1

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap