Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

42results about "Pulse automatic control" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

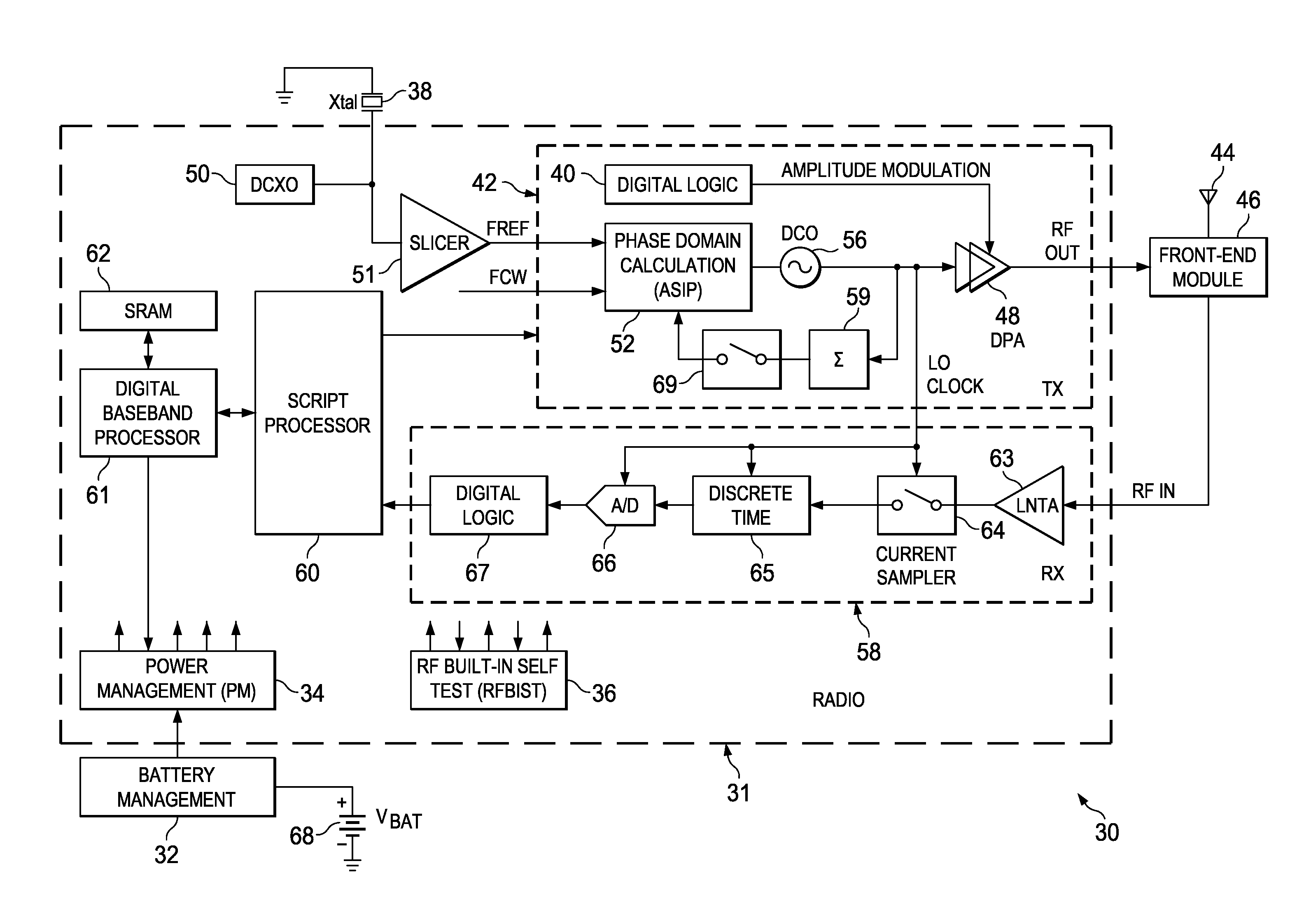

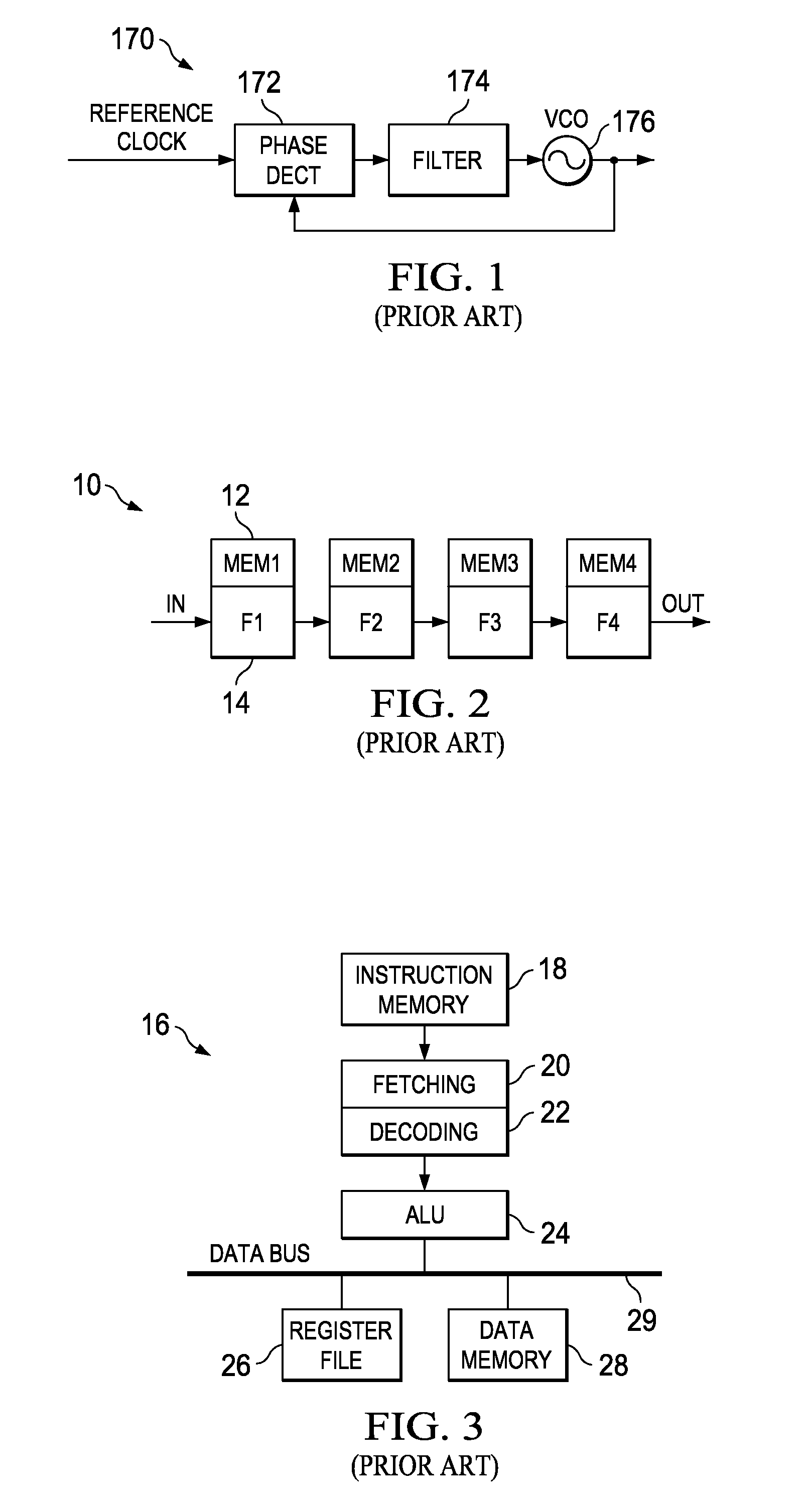

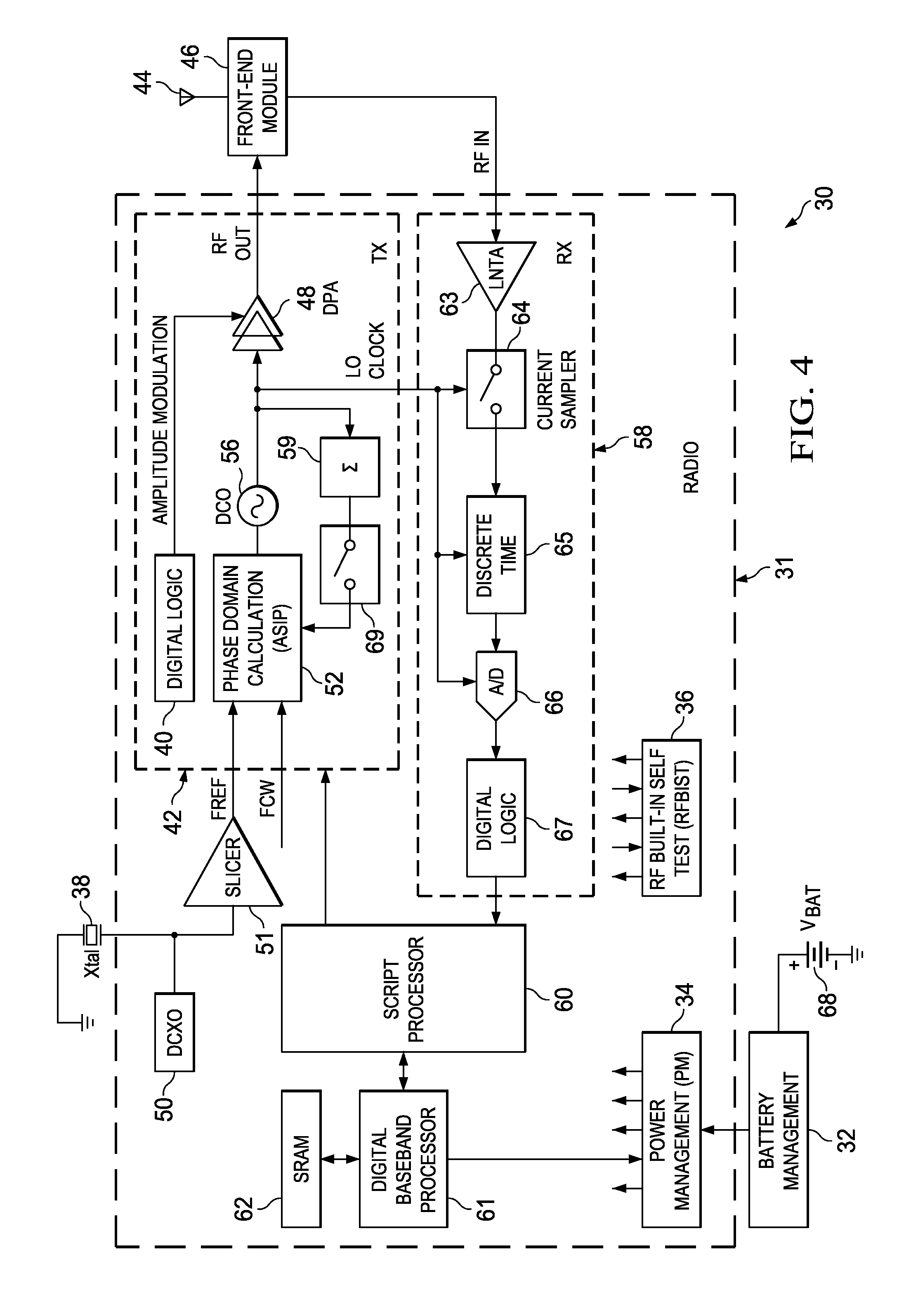

Computation parallelization in software reconfigurable all digital phase lock loop

ActiveUS20090070568A1Easy to reconfigureReduce per cycle current transientPulse automatic controlGeneral purpose stored program computerData stream processingTime-sharing

Owner:TEXAS INSTR INC

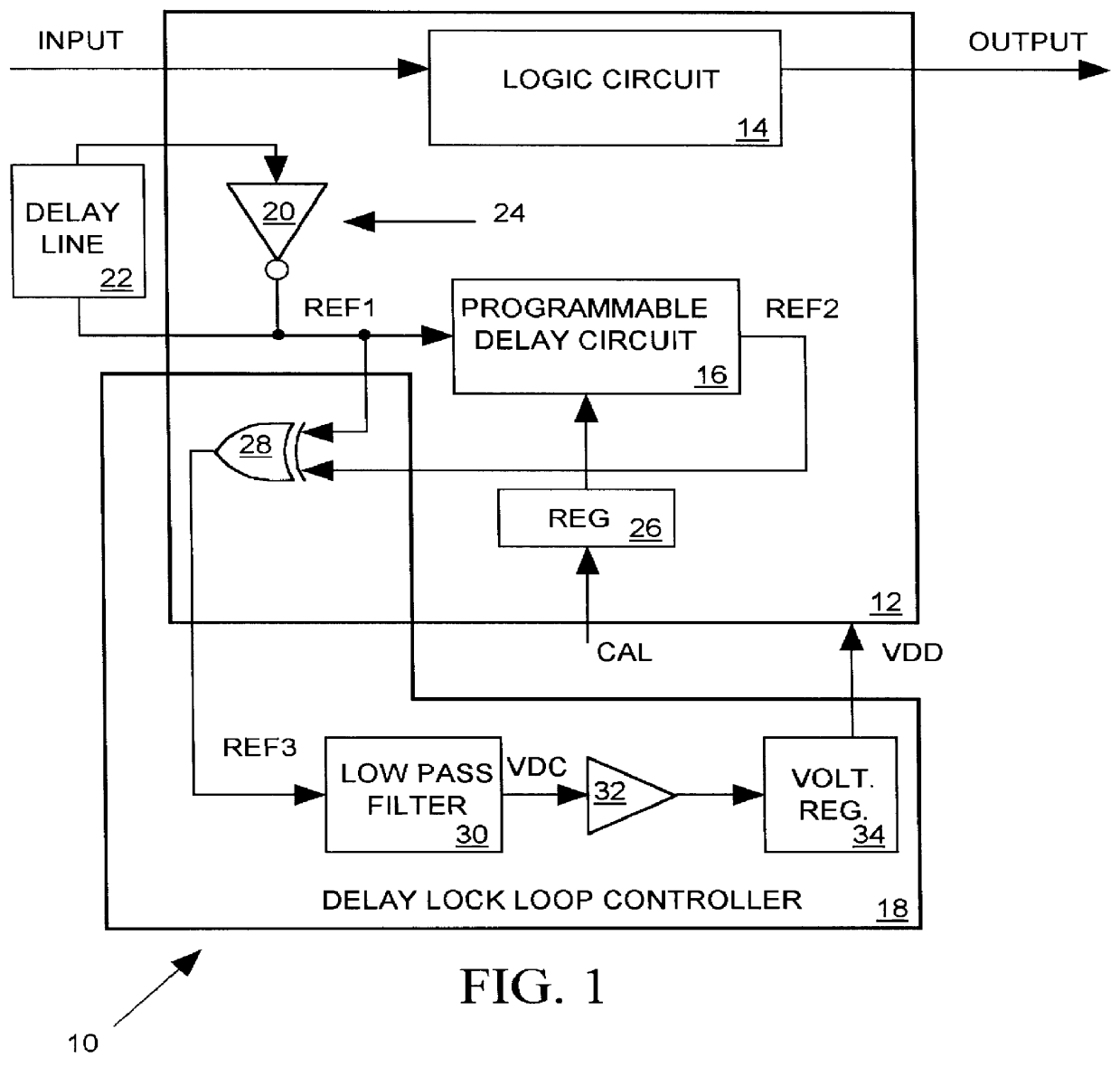

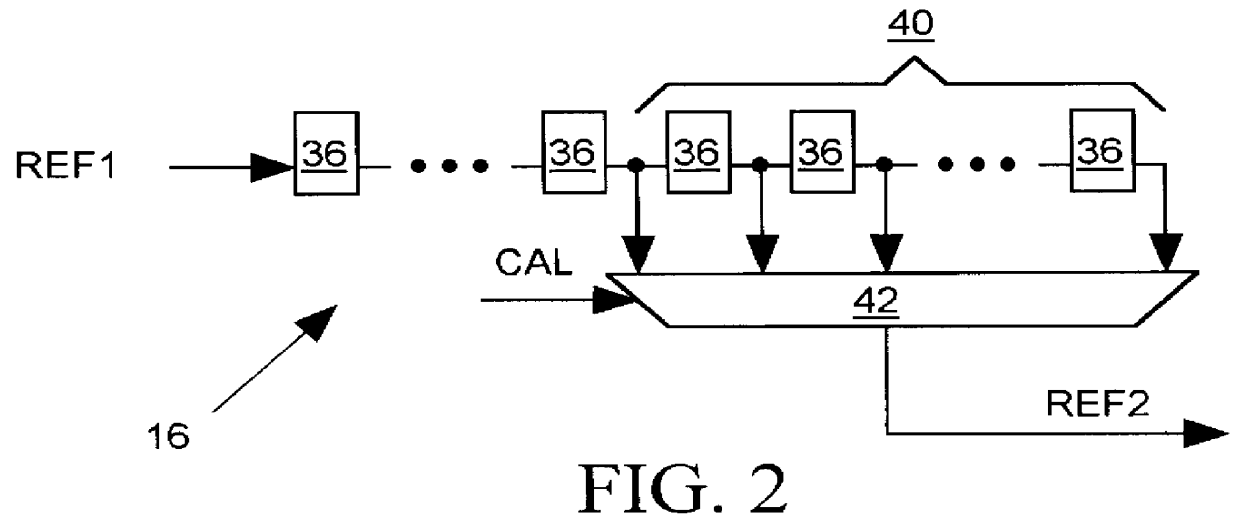

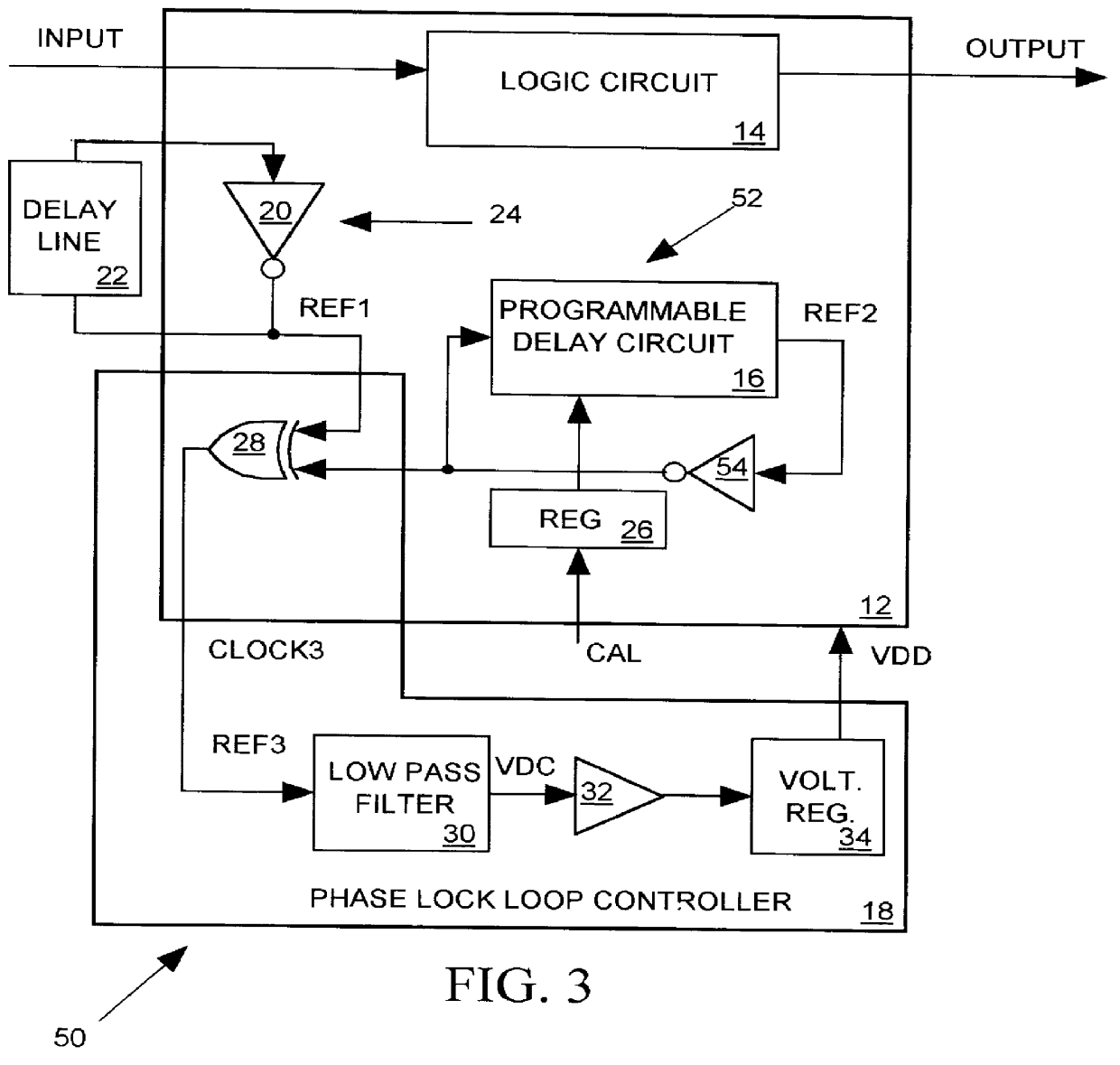

Delay stabilization system for an integrated circuit

InactiveUS6157231AEasy to adjustPrecise processReliability increasing modificationsPulse automatic controlPhase differenceEngineering

Owner:CREDENCE SYSTEMS

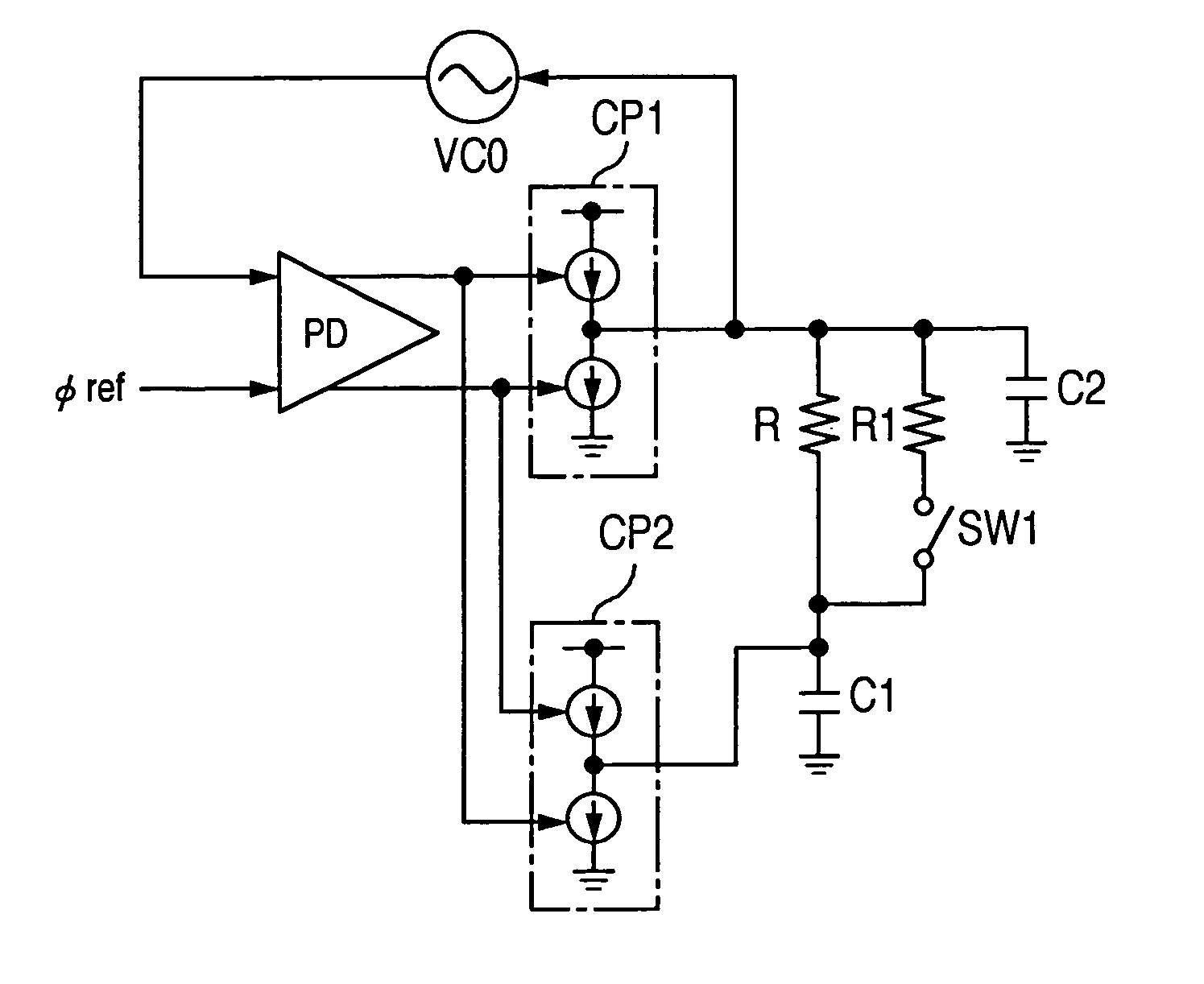

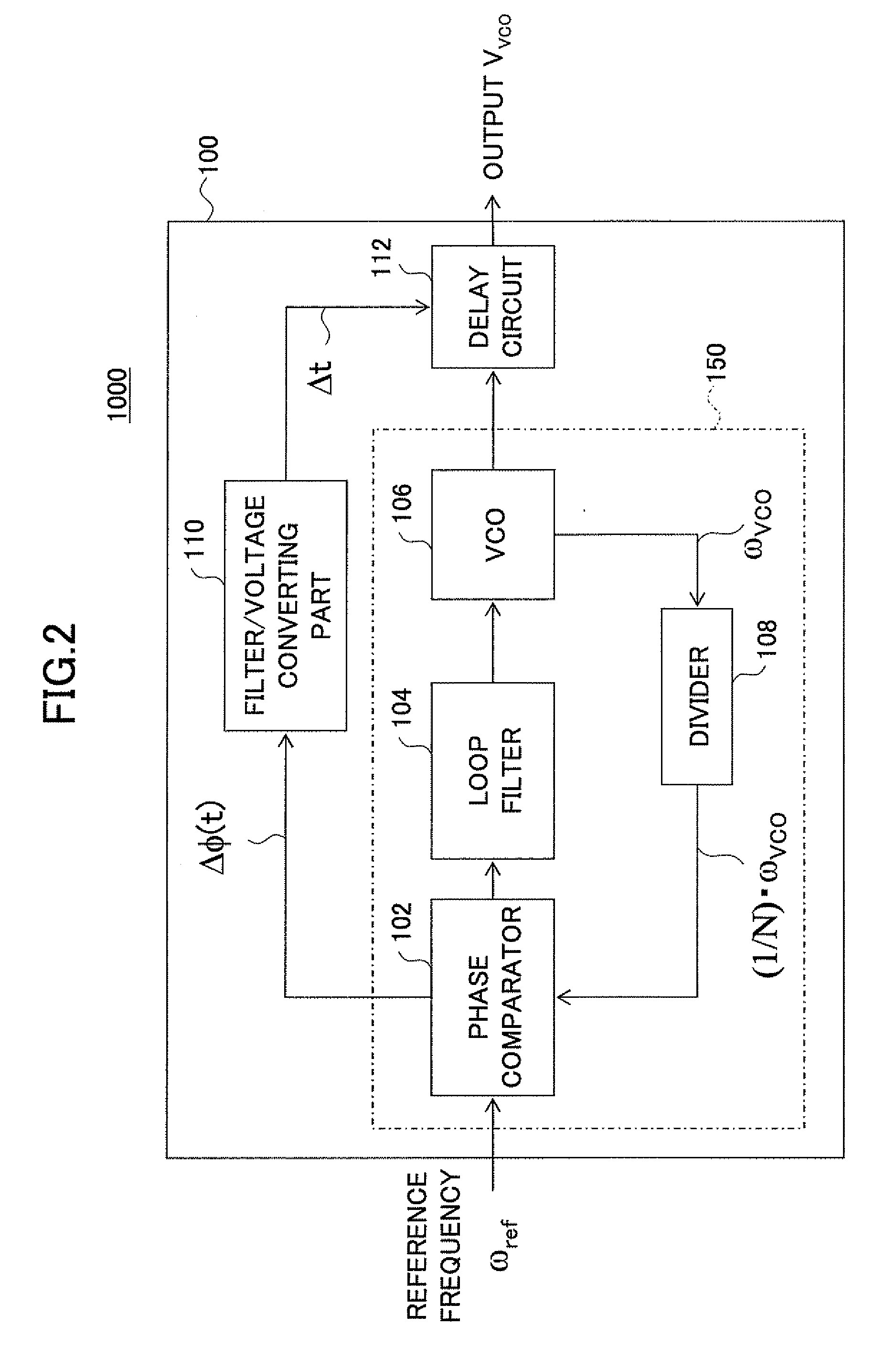

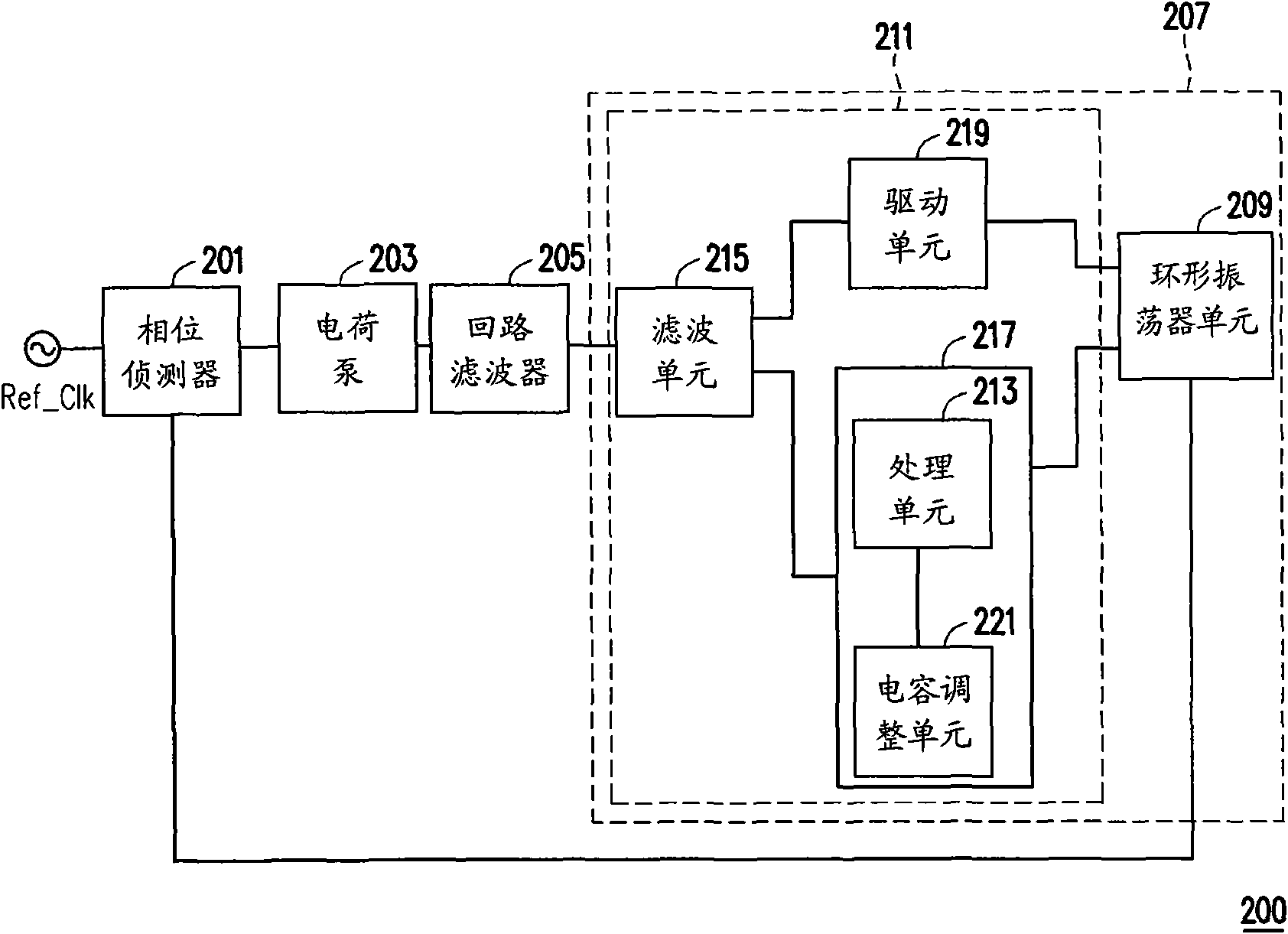

Semiconductor integrated circuit having built-in PLL circuit

ActiveUS20050134391A1Avoid mistakesEliminate needPulse automatic controlAngle demodulation by phase difference detectionCapacitanceEngineering

Owner:RENESAS ELECTRONICS CORP +1

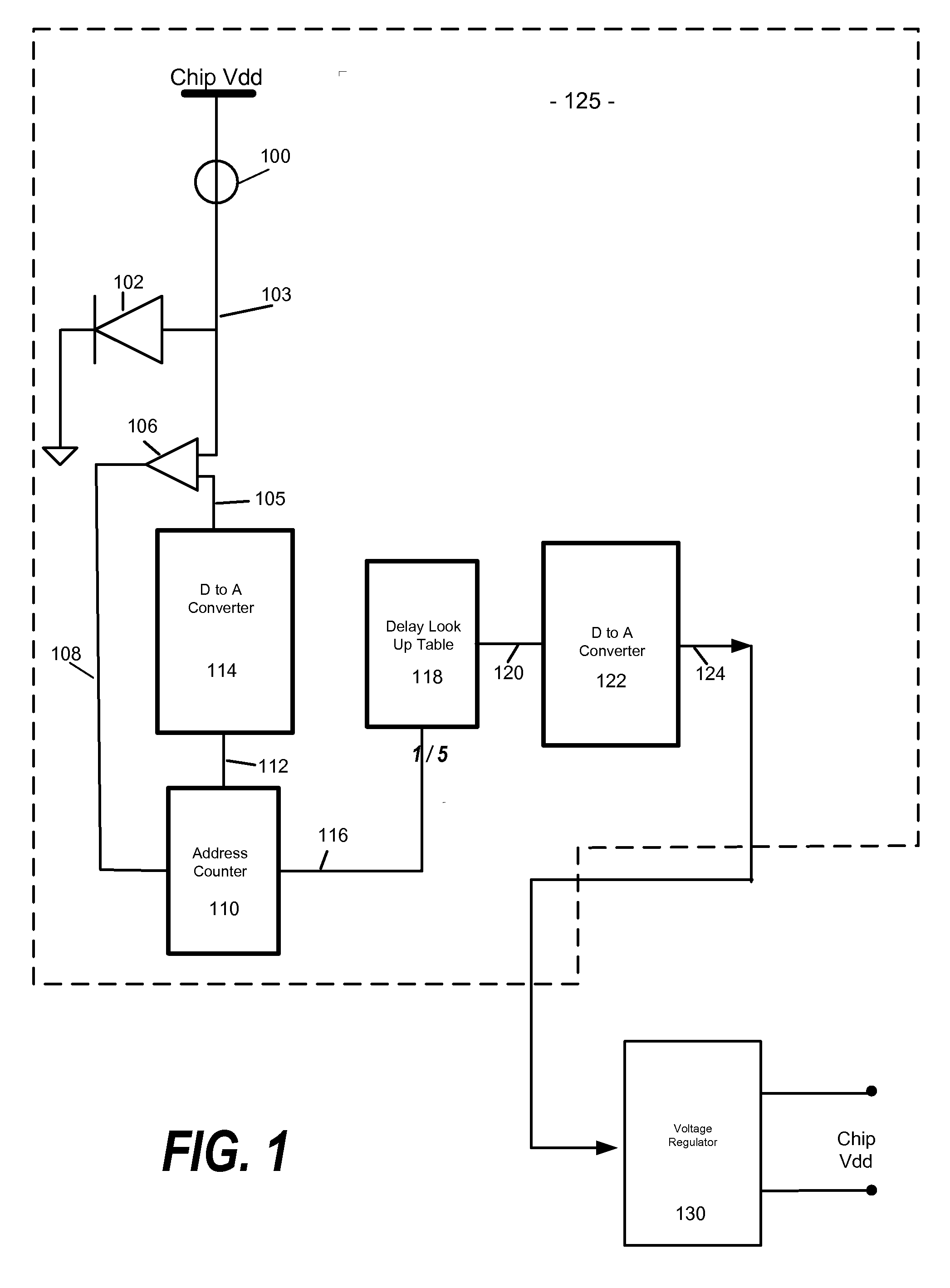

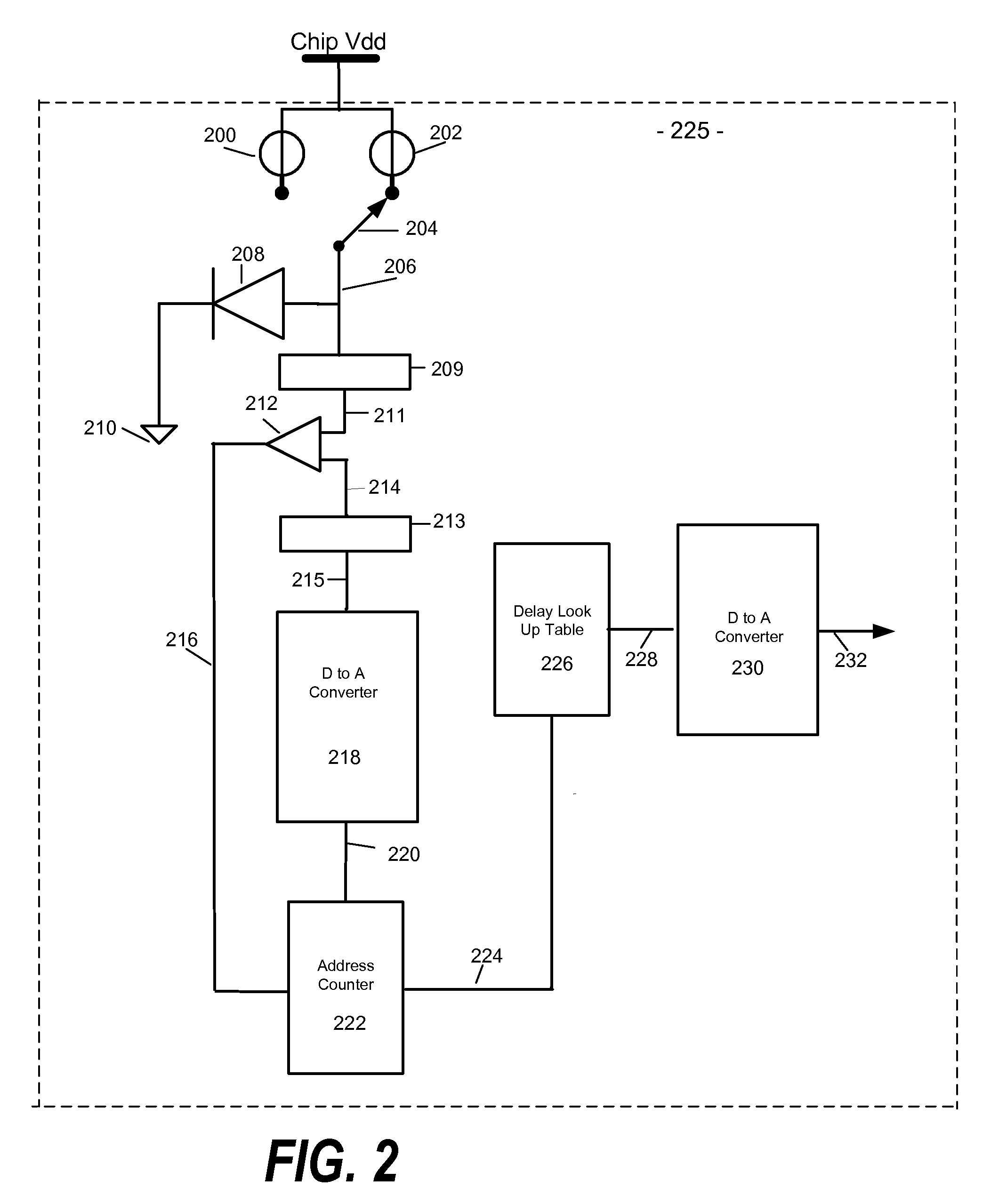

On-Chip Adaptive Voltage Compensation

ActiveUS20080186001A1Thermometer detailsPulse automatic controlVoltage regulationIntegrated circuit layout

Owner:IBM CORP

Linear burst mode synchronizer for passive optical networks

ActiveUS20080022143A1Improves synchronized jitter performanceImprove Timing MarginPulse automatic controlSynchronisation signal speed/phase controlFiberTiming margin

Owner:REALTEK SINGAPORE PTE LTD

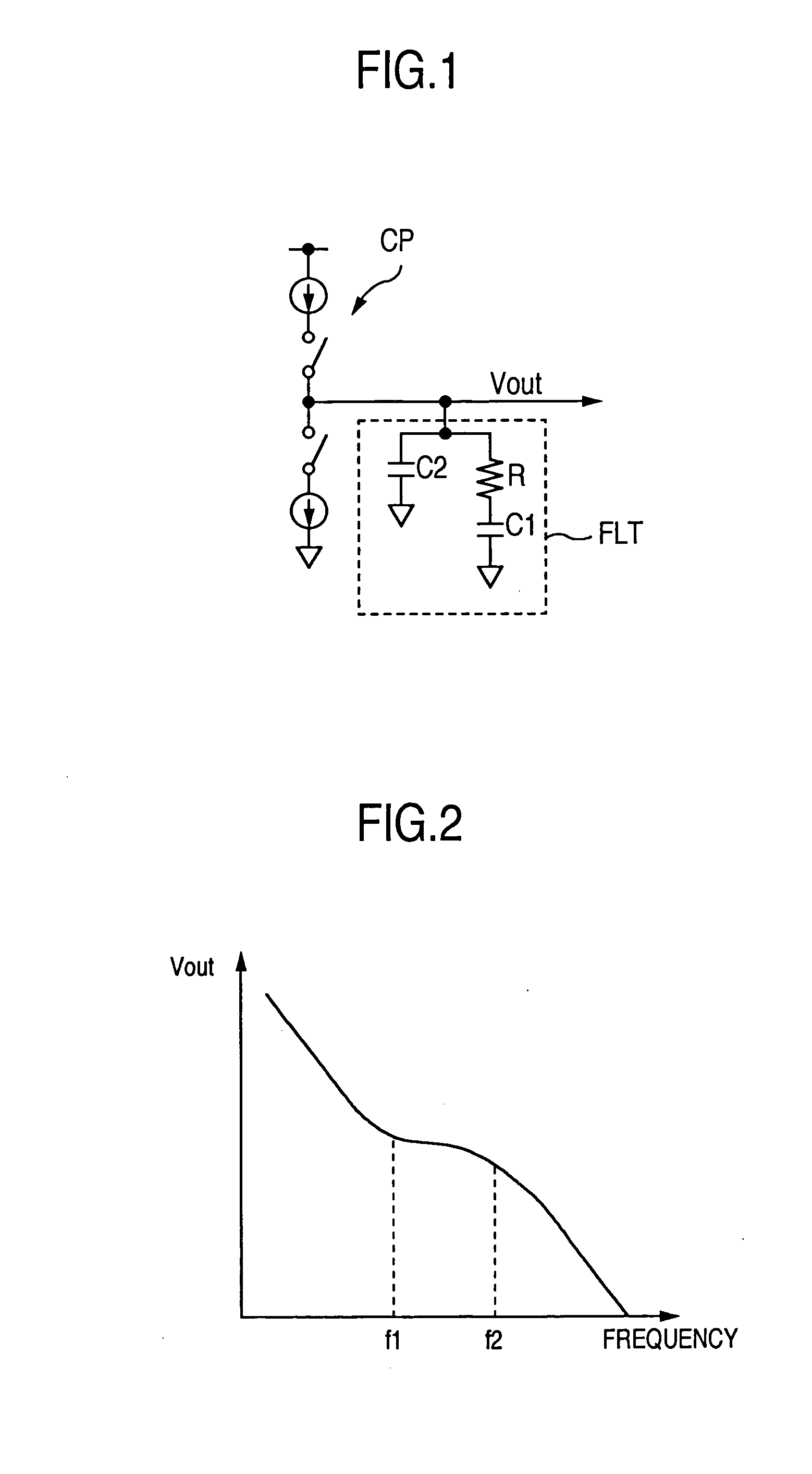

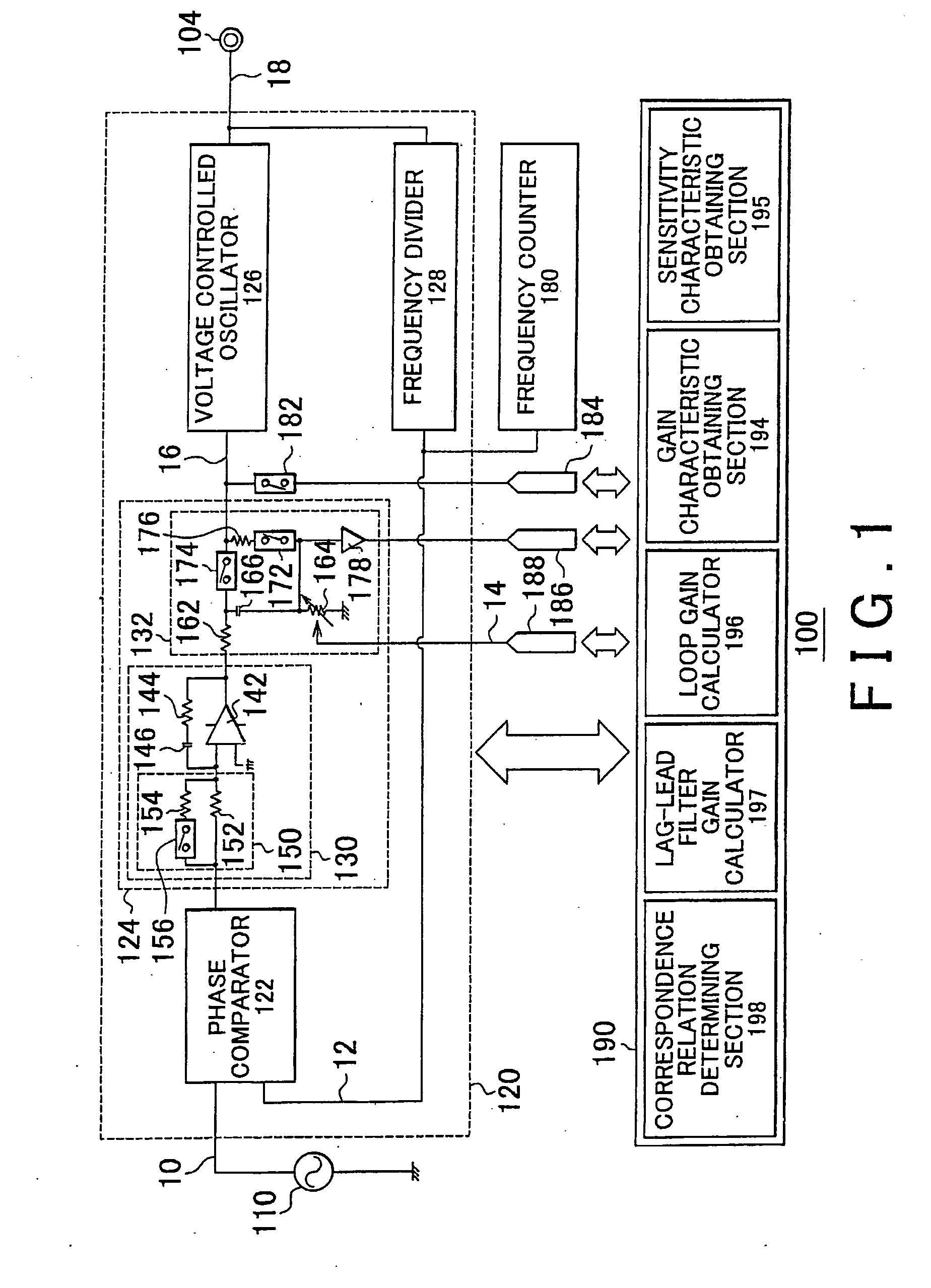

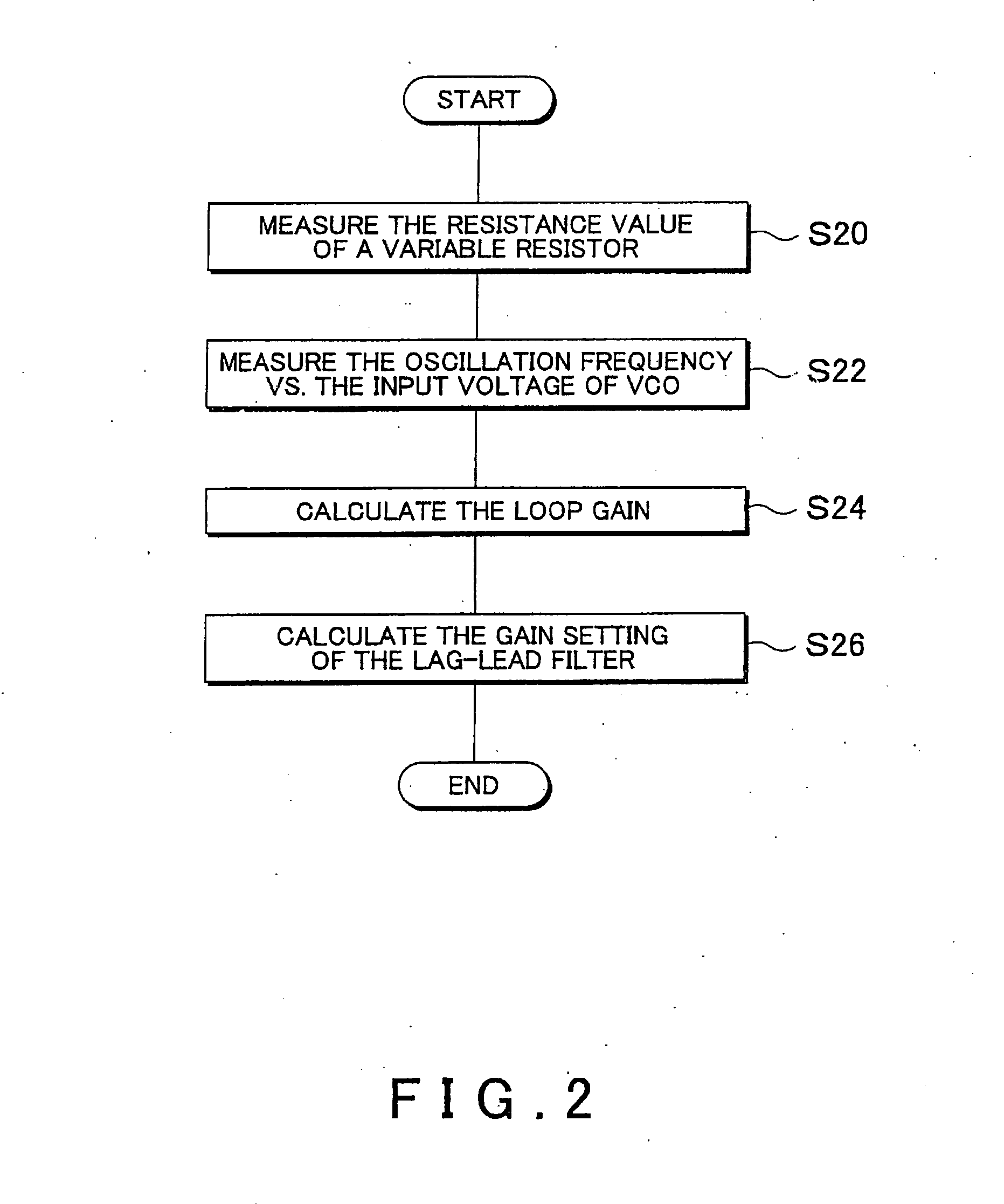

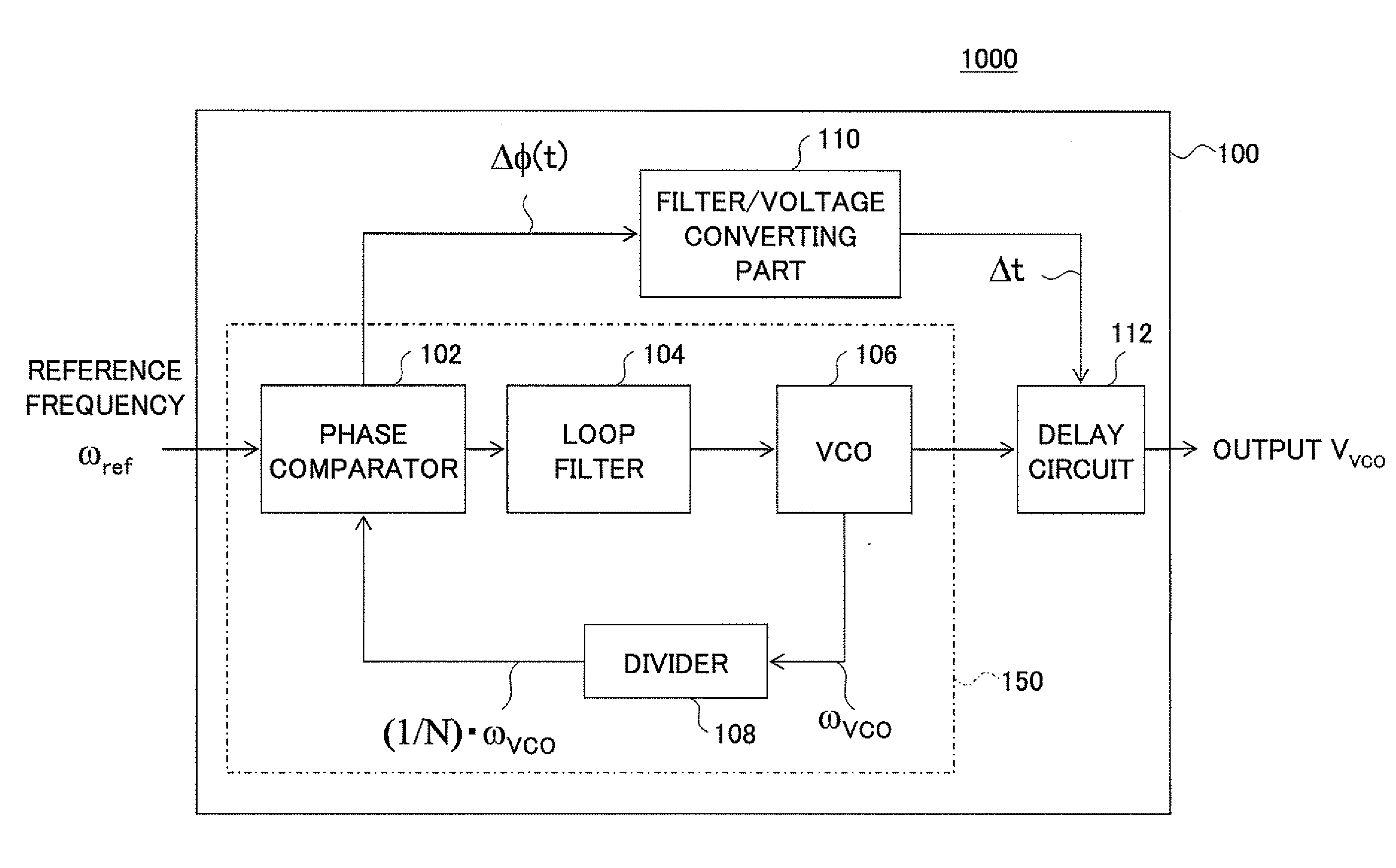

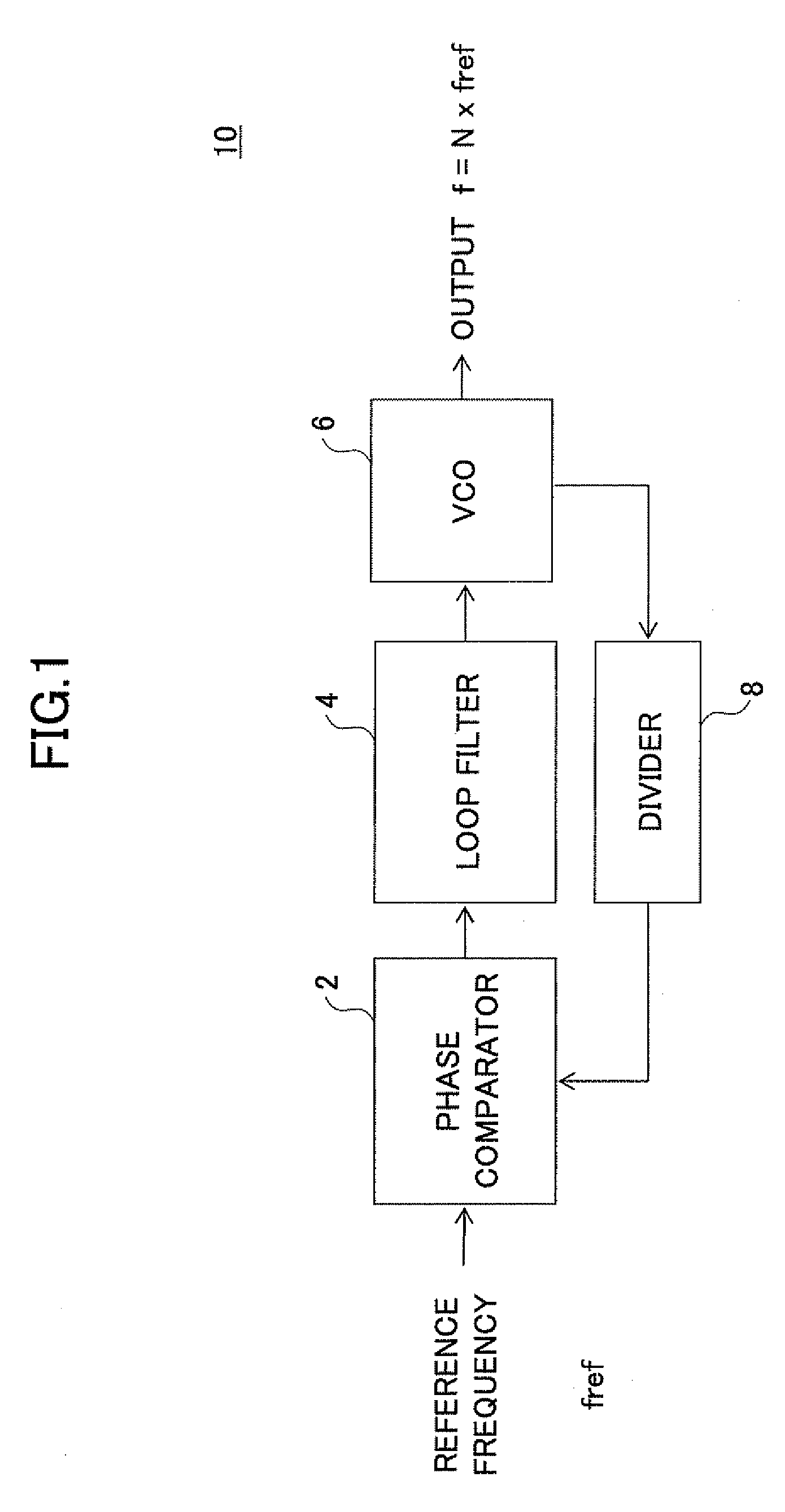

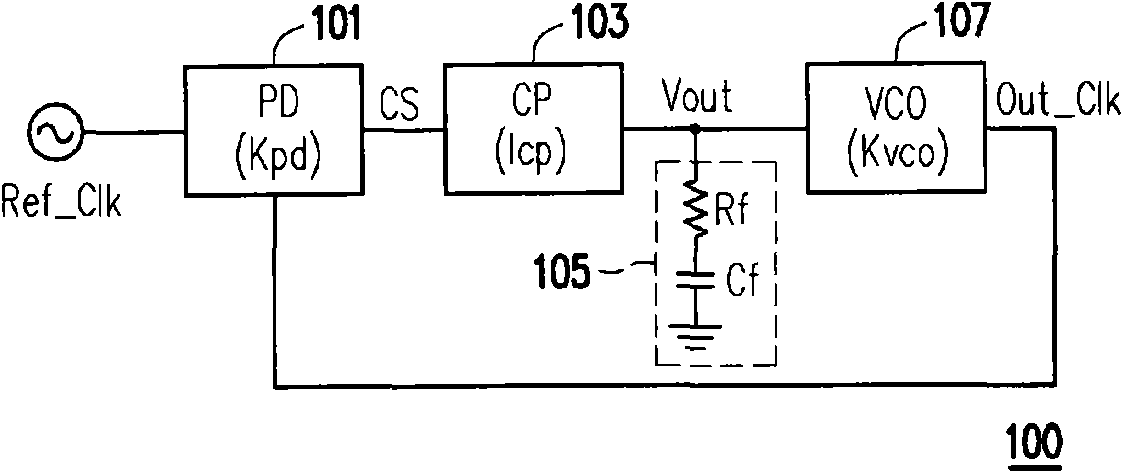

Oscillator and a tuning method of a loop bandwidth of a phase-locked-loop

InactiveUS20090302908A1Multiple-port networksPulse automatic controlFrequency oscillationLoop bandwidth

Owner:ADVANTEST CORP

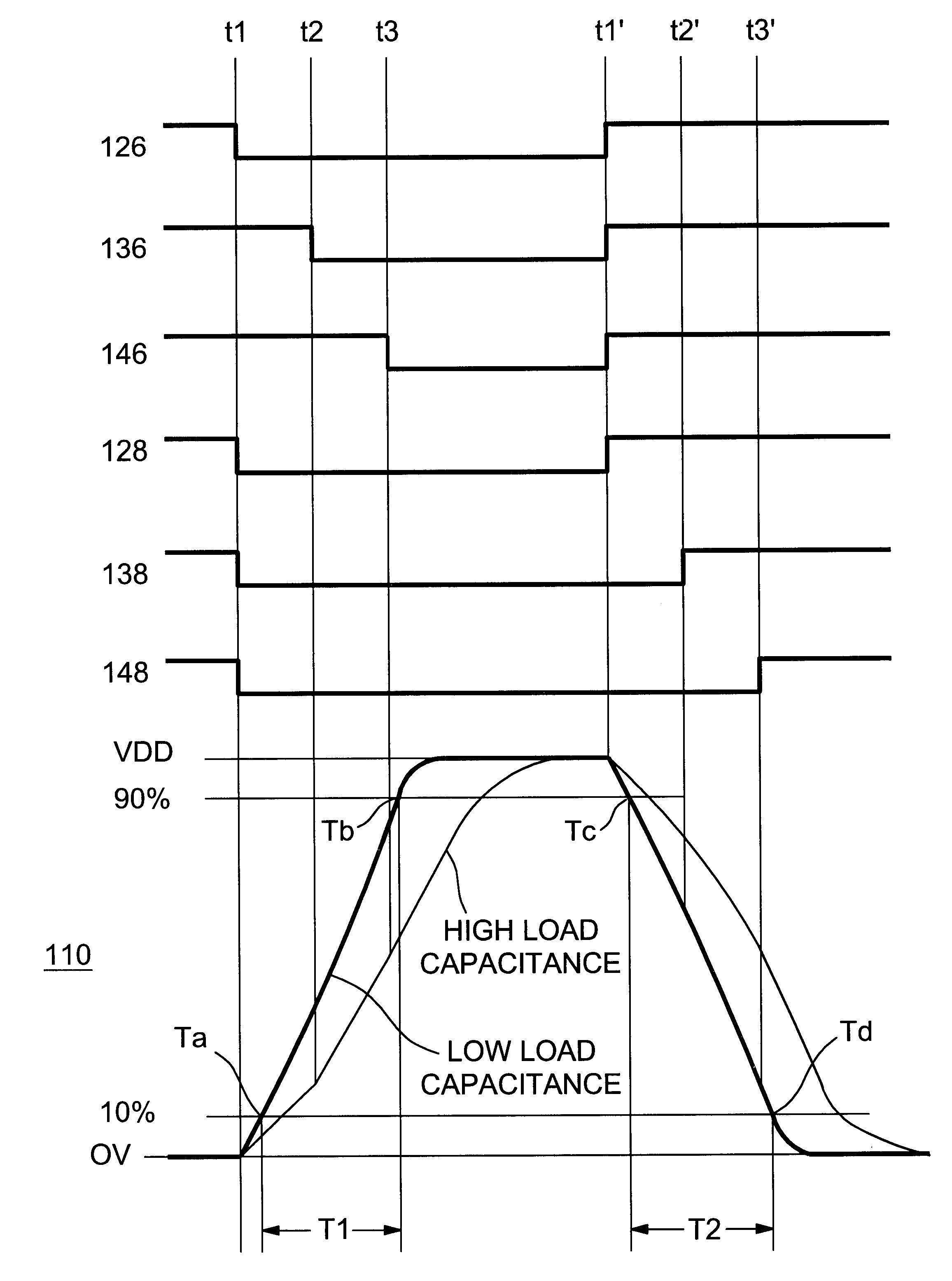

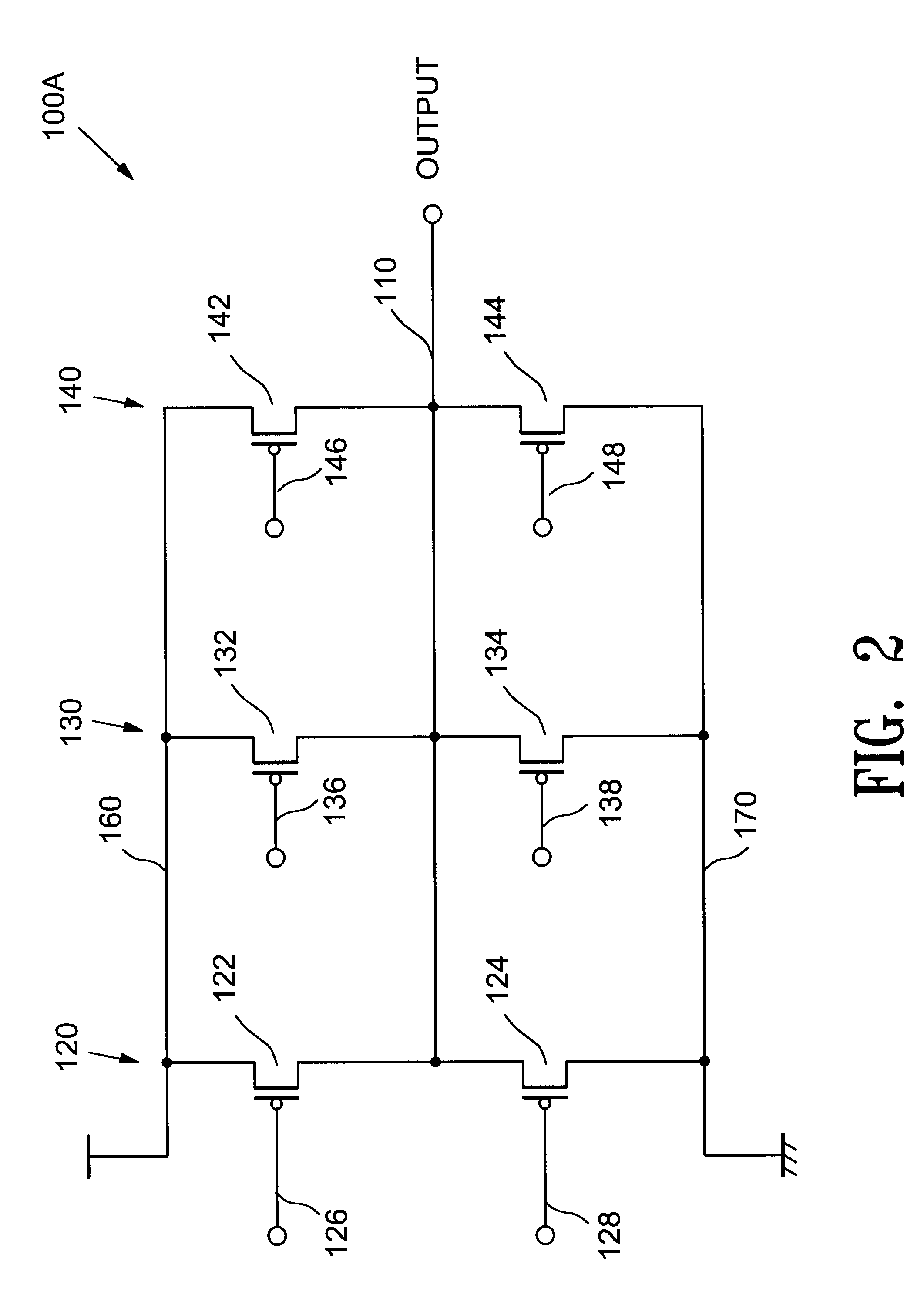

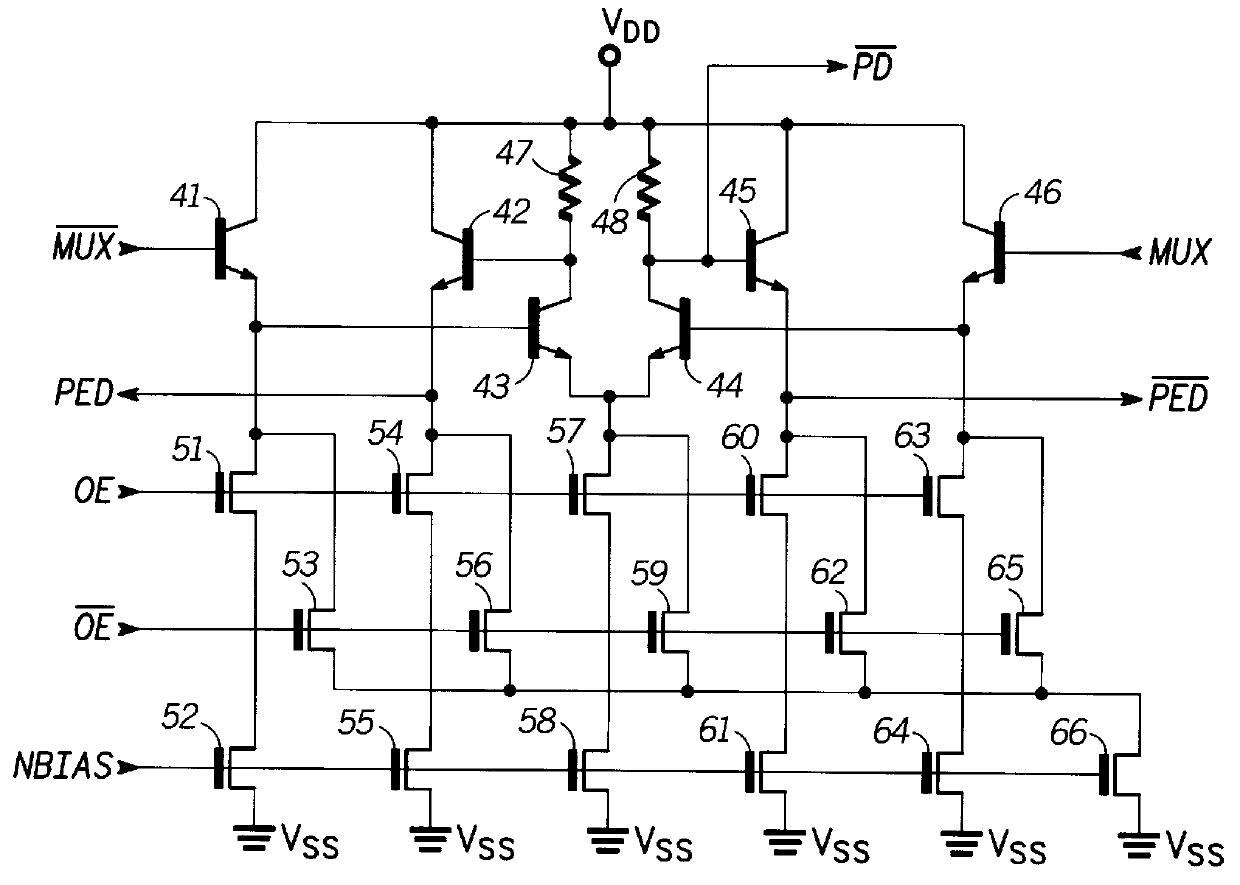

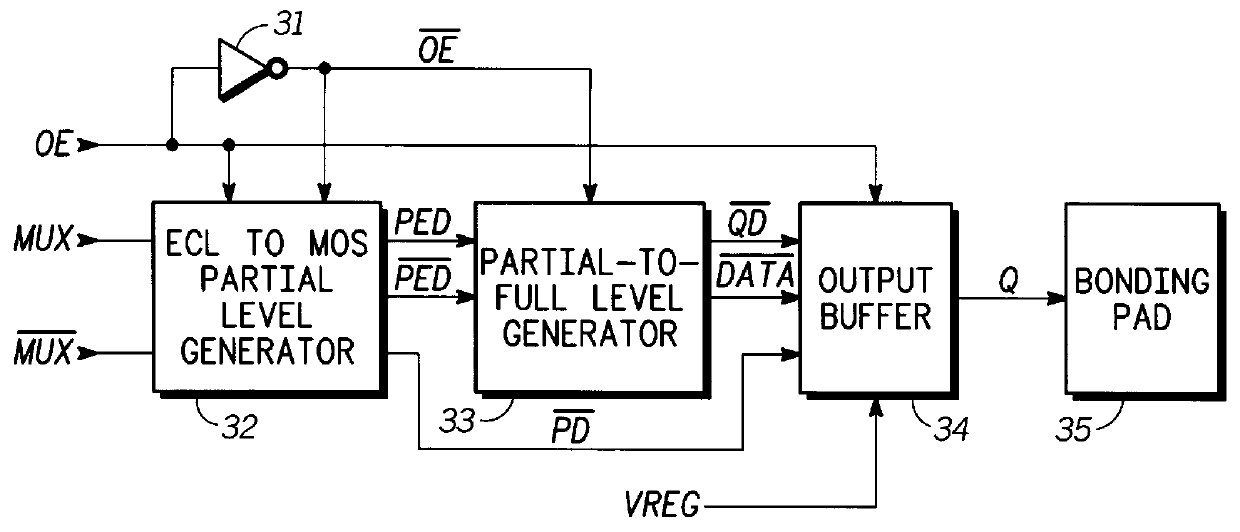

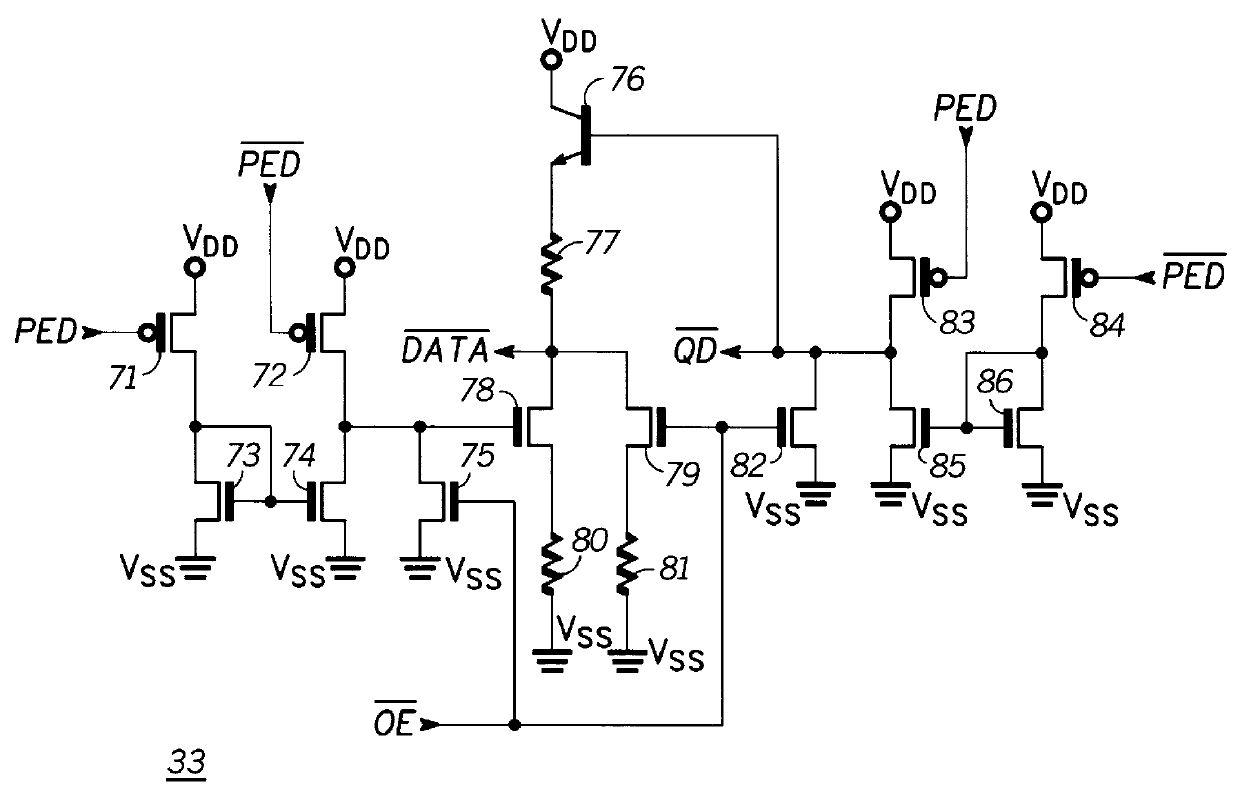

Output buffer having a plurality of switching devices being turned on successively at shorter time intervals to achieve increasing drive capability using a predriver

InactiveUS6578156B1Pulse automatic controlLogic circuits coupling/interface using field-effect transistorsData bufferGround line

Owner:SEIKO EPSON CORP

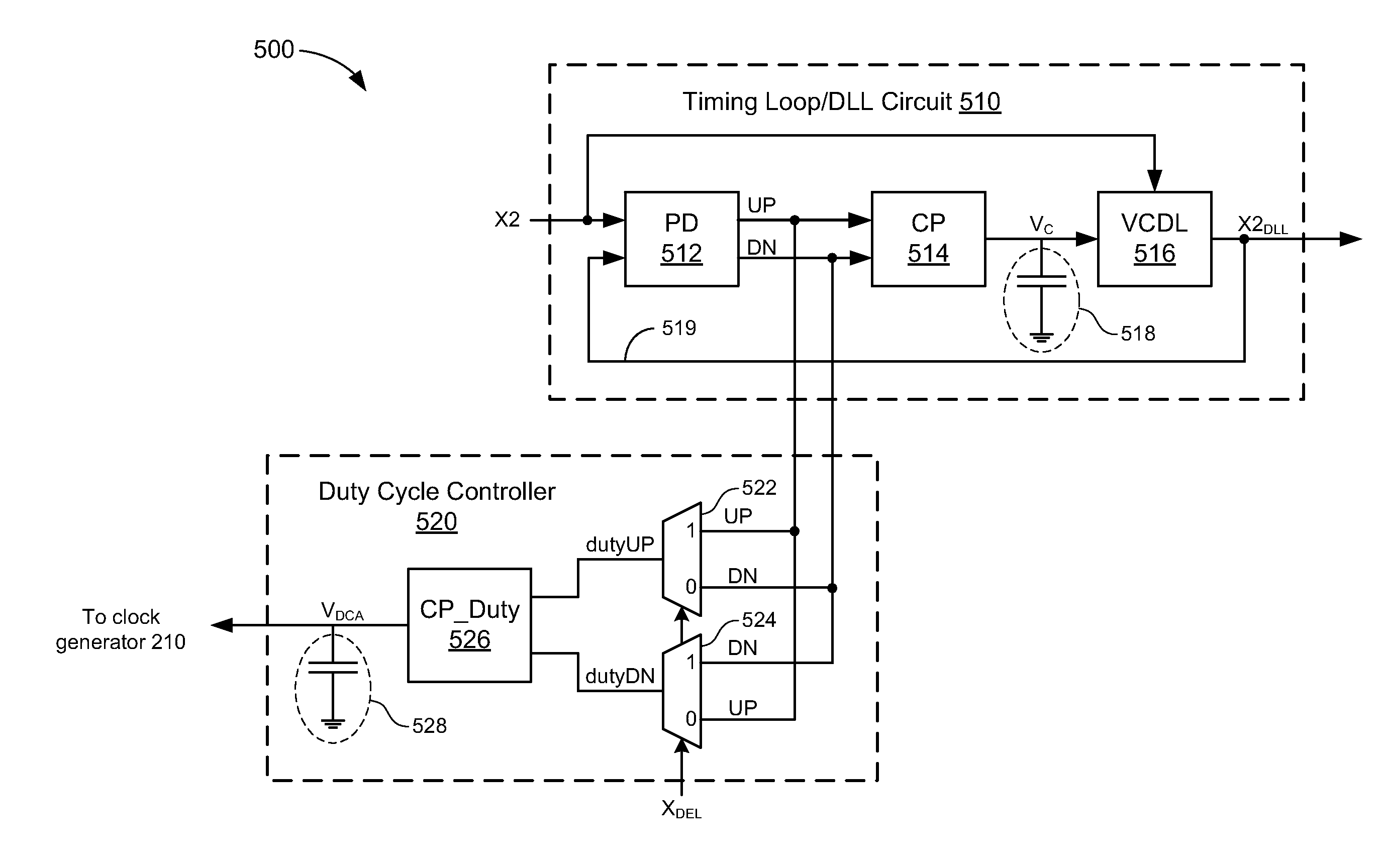

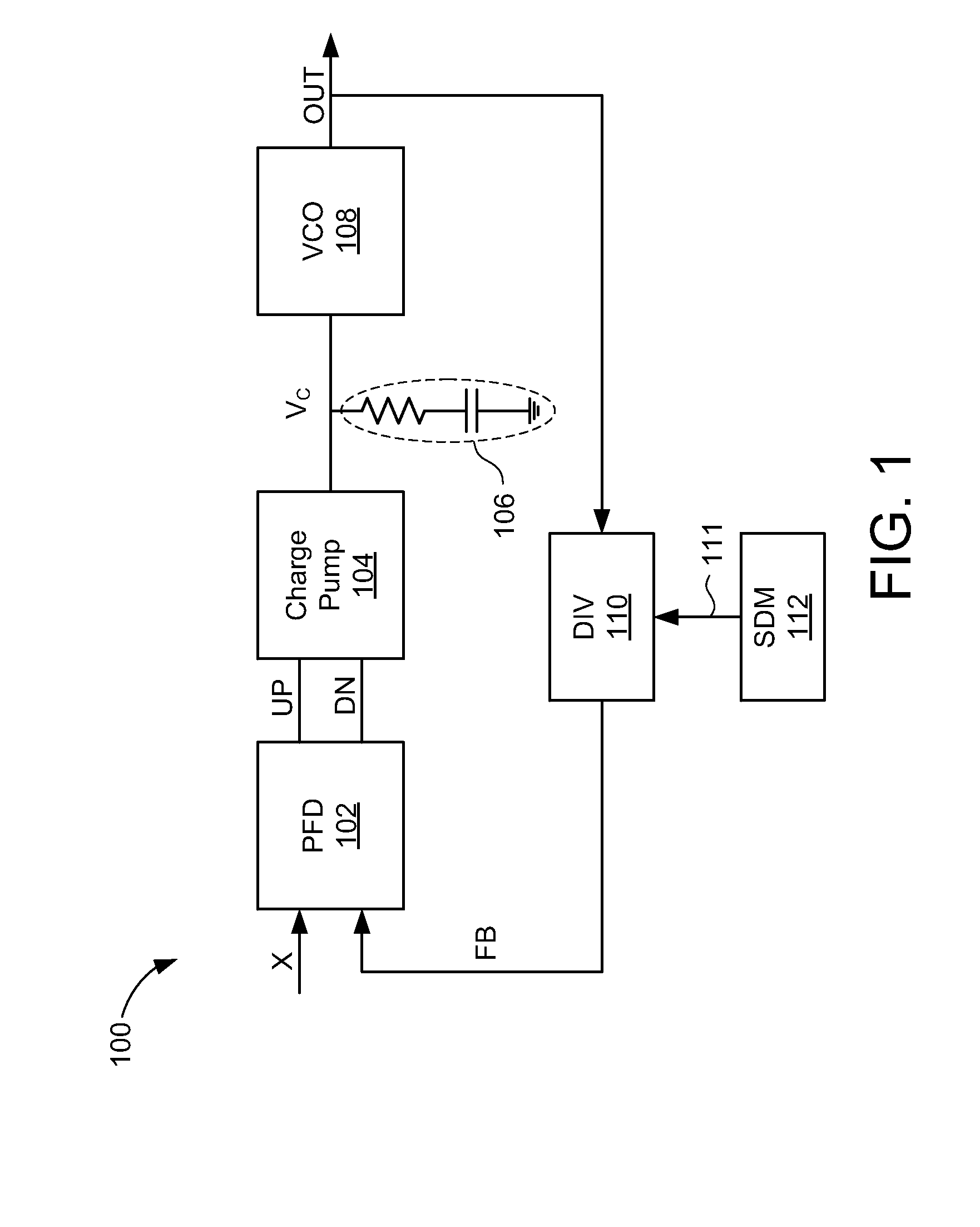

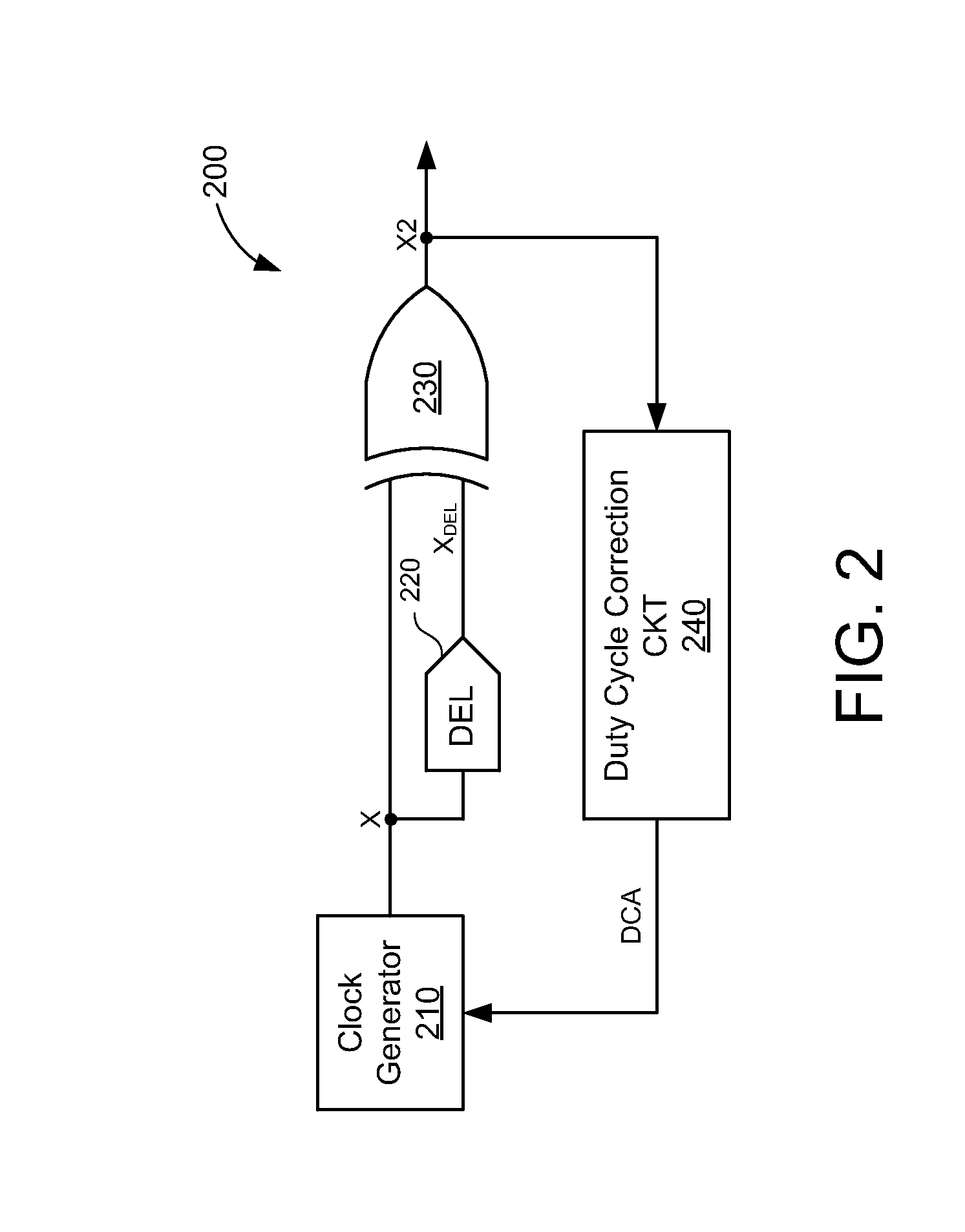

Method and apparatus for generating a reference signal for a fractional-n frequency synthesizer

ActiveUS20140340132A1Synthesizer output phase noiseSettling fastPulse automatic controlFrequency multiplierClock generator

Owner:QUALCOMM INC

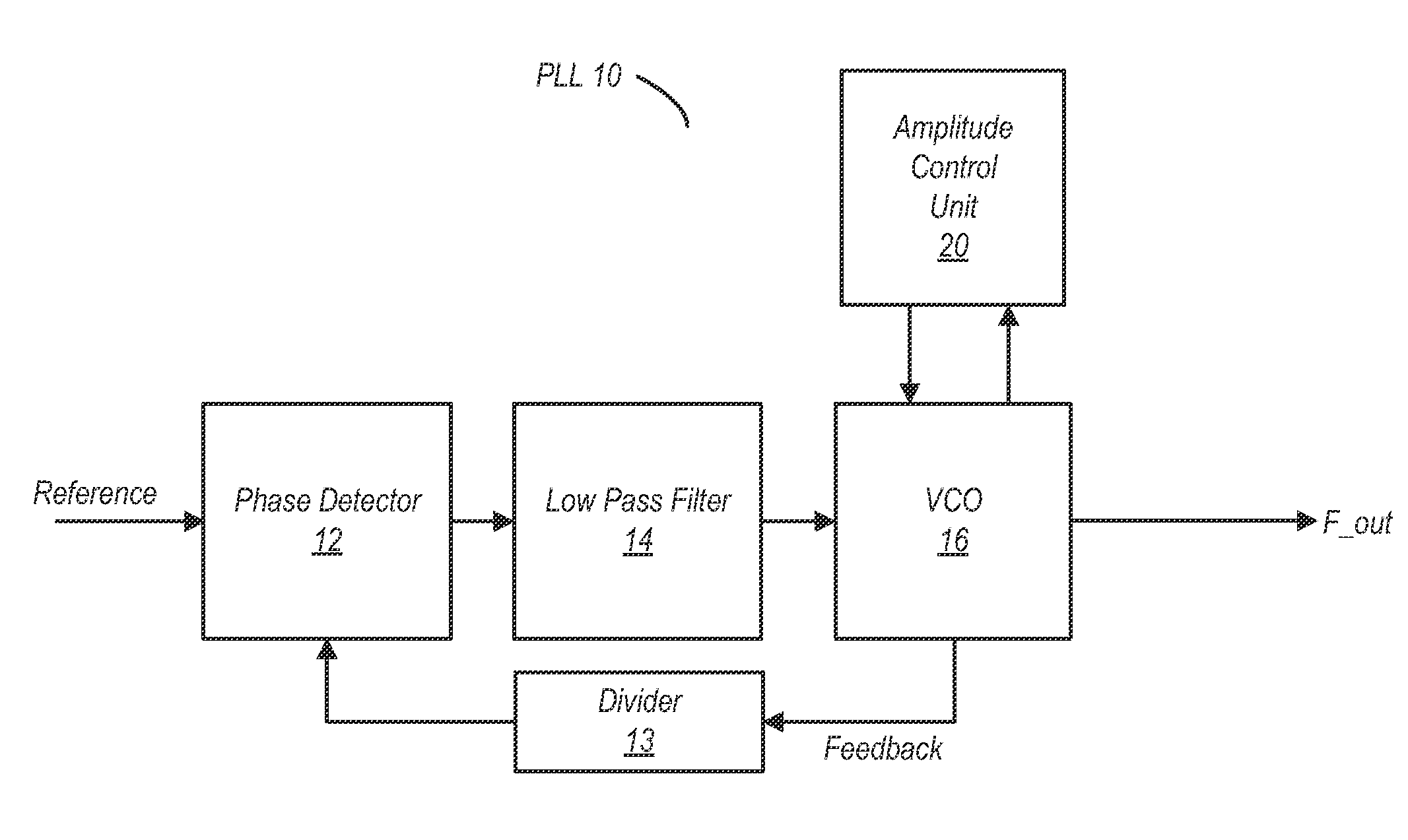

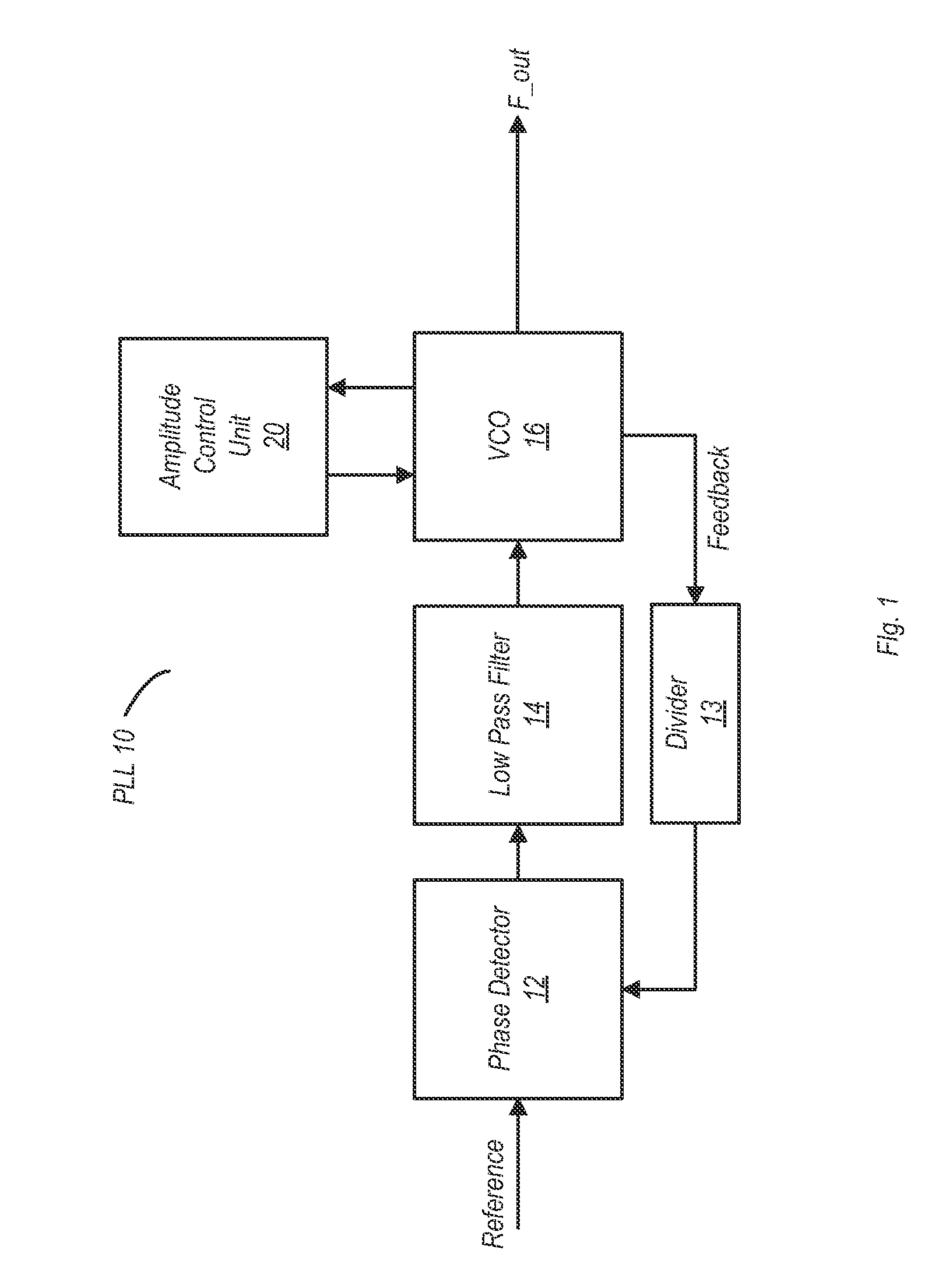

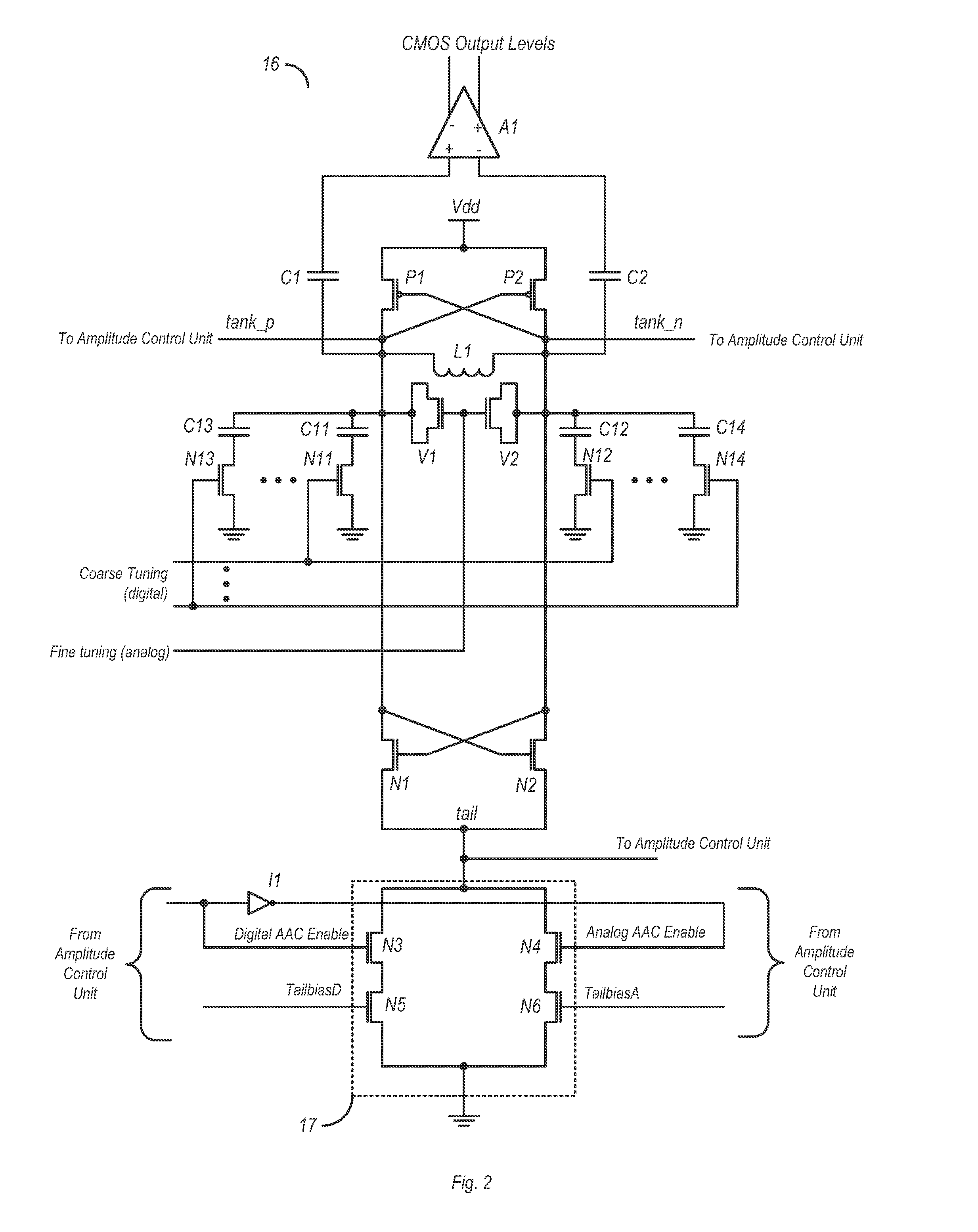

Automatic amplitude control for voltage controlled oscillator

ActiveUS20110304407A1Pulse automatic controlOscillations generatorsVIT signalsVoltage controlled ring oscillator

Owner:ADVANCED MICRO DEVICES INC

DLL circuit

InactiveUS7020228B2Reduce power consumptionPulse automatic controlDigital storageDelay-locked loopPhase relationship

A DLL (delay locked loop) circuit for outputting a phase lock signal having a predetermined phase relationship with an input signal. The DLL circuit has: a functional block having a constant-current source; and bias generator for generating a constant current source bias signal for controlling the constant current source of the functional block, the bias generator comprising a bias control which changes the bias signal according to the frequency of the input signal.

Owner:LONGITUDE SEMICON S A R L

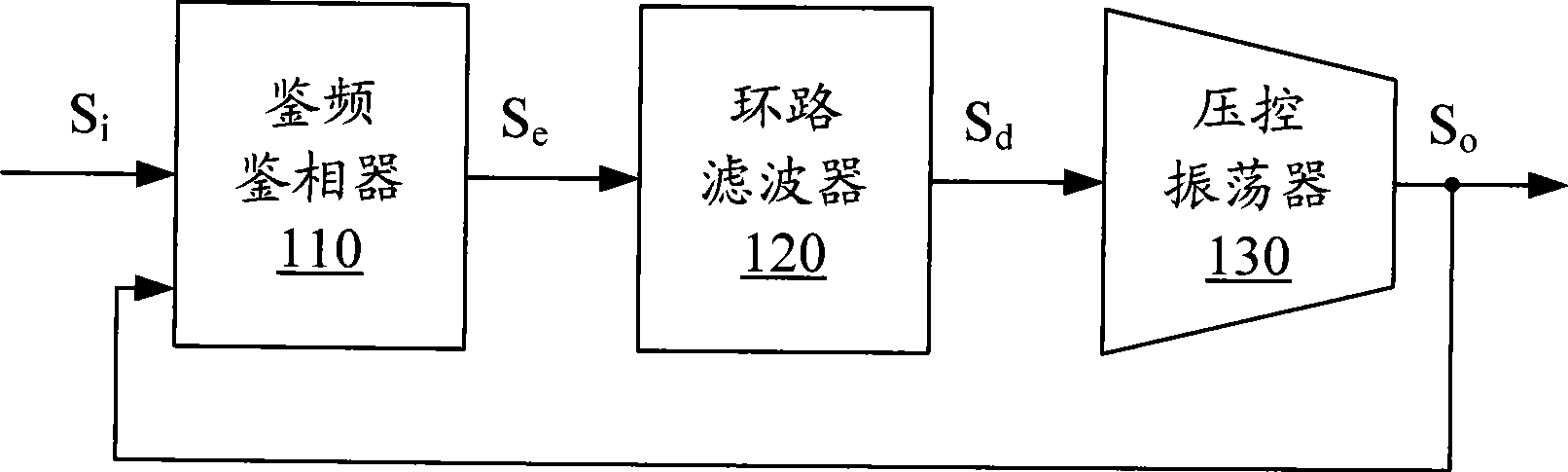

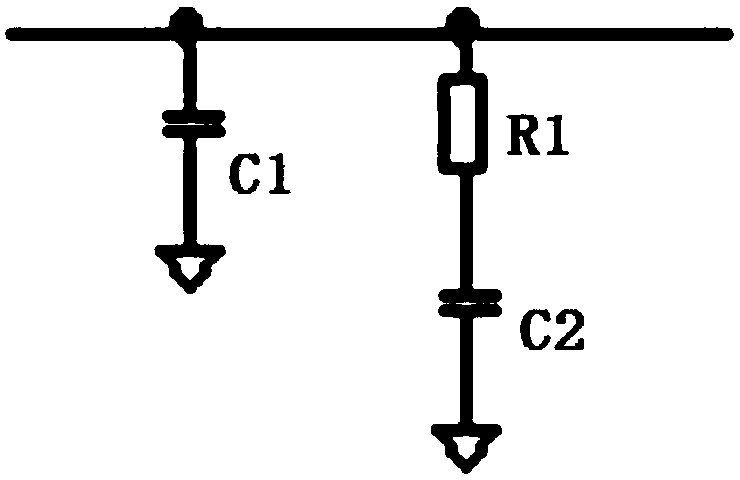

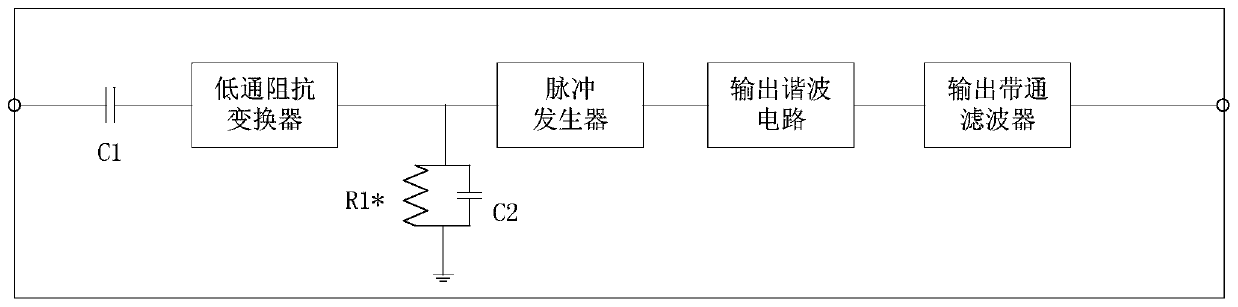

Frequency synthesis system for enhancing spectrum purity of direct digital frequency synthesizer

InactiveCN101847992AReduce noiseImprove output signal spurious indexPulse automatic controlFrequency spectrumClock rate

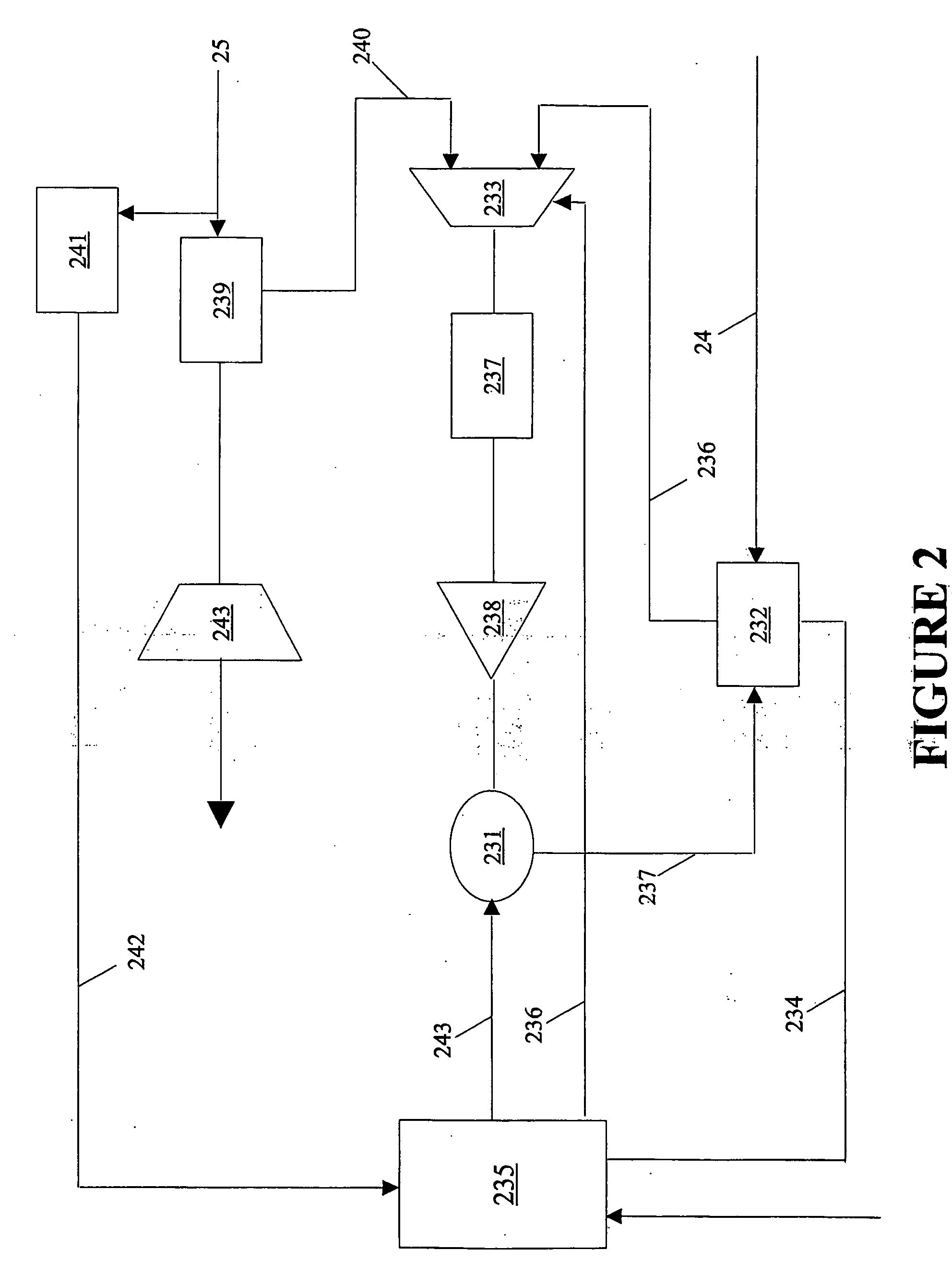

The invention relates to a frequency synthesis system for enhancing spectrum purity of a direct digital frequency synthesizer, which comprises a crystal oscillator, a phase-locked loop module (PLL), a direct digital frequency synthesis module (DDS), a filter module and a central processing unit, wherein the system uses the phase-locked loop module (PLL) to provide a variable clock for the direct digital frequency synthesis module (DDS), and the clock frequency of the variable clock provided by the phase-locked loop module (PLL) is an integral multiple of the frequency of the output signal. By changing the clock frequency of the direct digital frequency synthesizer, the noise generated in the quantization process is minimized, thereby improving the stray indexes of the output signal and enhancing the spectrum purity of the output signal.

Owner:NANJING GUORUI ANTAIXIN TECH

Square-law clamping circuit

InactiveUS6031408APulse automatic controlComputing operations for logarithmic/exponential functionsVoltage referenceInput/output

Owner:MOTOROLA INC

Power system, power module therein and method for fabricating power module

ActiveUS20130214842A1Reduce voltage spikesPulse automatic controlConversion constructional detailsElectrical conductorDevice material

A power system, a power module therein and a method for fabricating power module are disclosed herein. The power module includes a first and a second common pins, and a first and a second bridge arms. The first and the second common pins are symmetrically disposed at one side of a substrate. The first bridge arm includes a first and a second semiconductor devices, and the first and the second semiconductor devices are connected to each other through the first common pin and disposed adjacently. The second bridge arm includes a third and a fourth semiconductor devices, and the third and the fourth semiconductor devices are connected to each other through the second common pin and disposed adjacently. The first and the third semiconductor devices are disposed symmetrically, and the second and the fourth semiconductor devices are disposed symmetrically.

Owner:DELTA ELECTRONICS INC

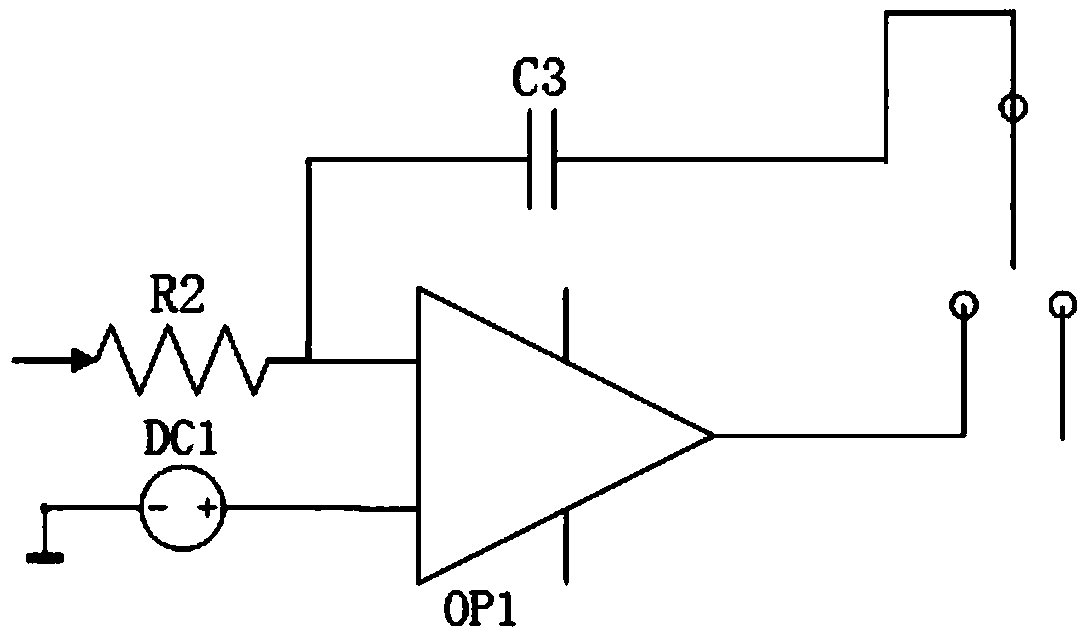

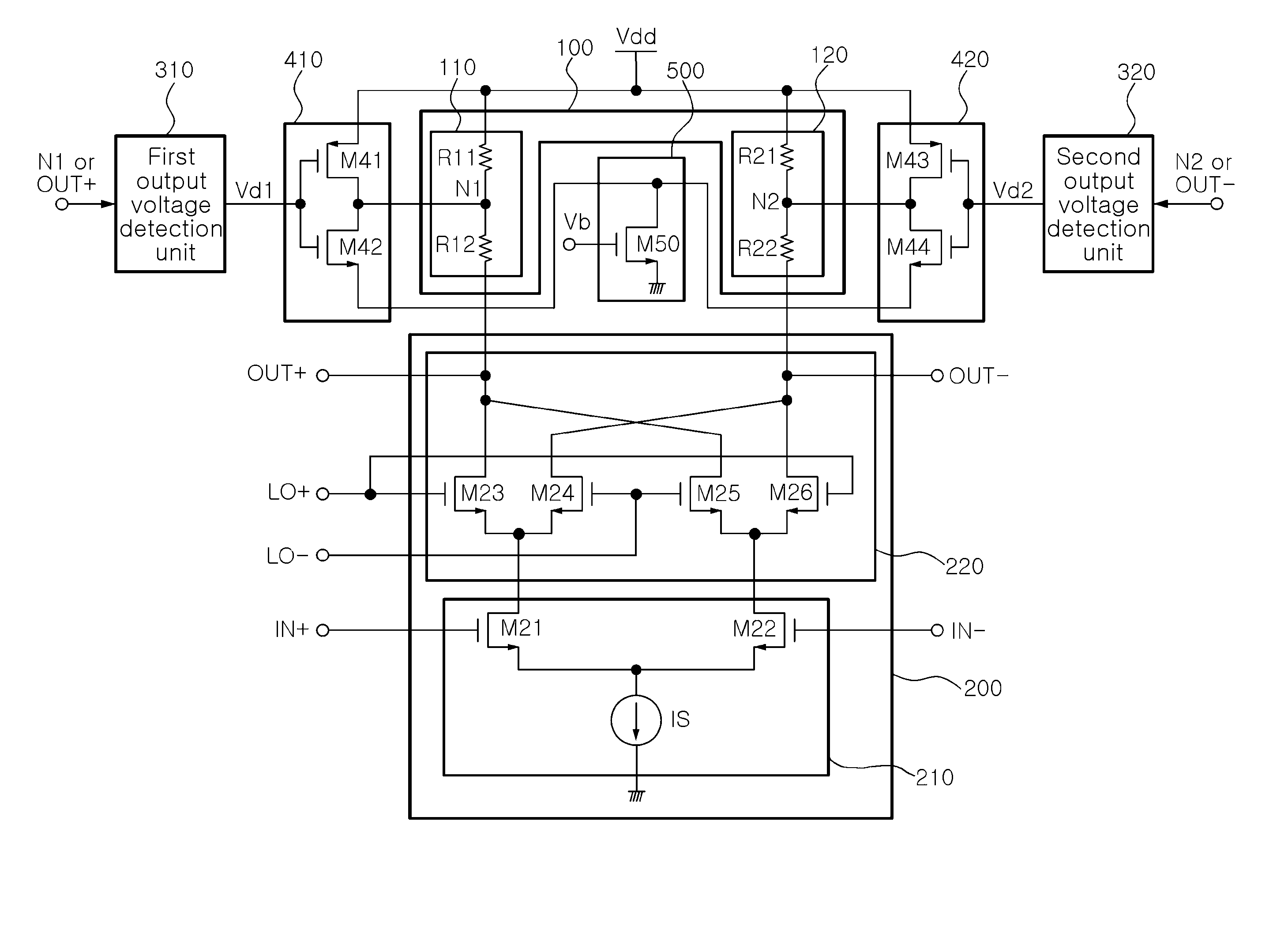

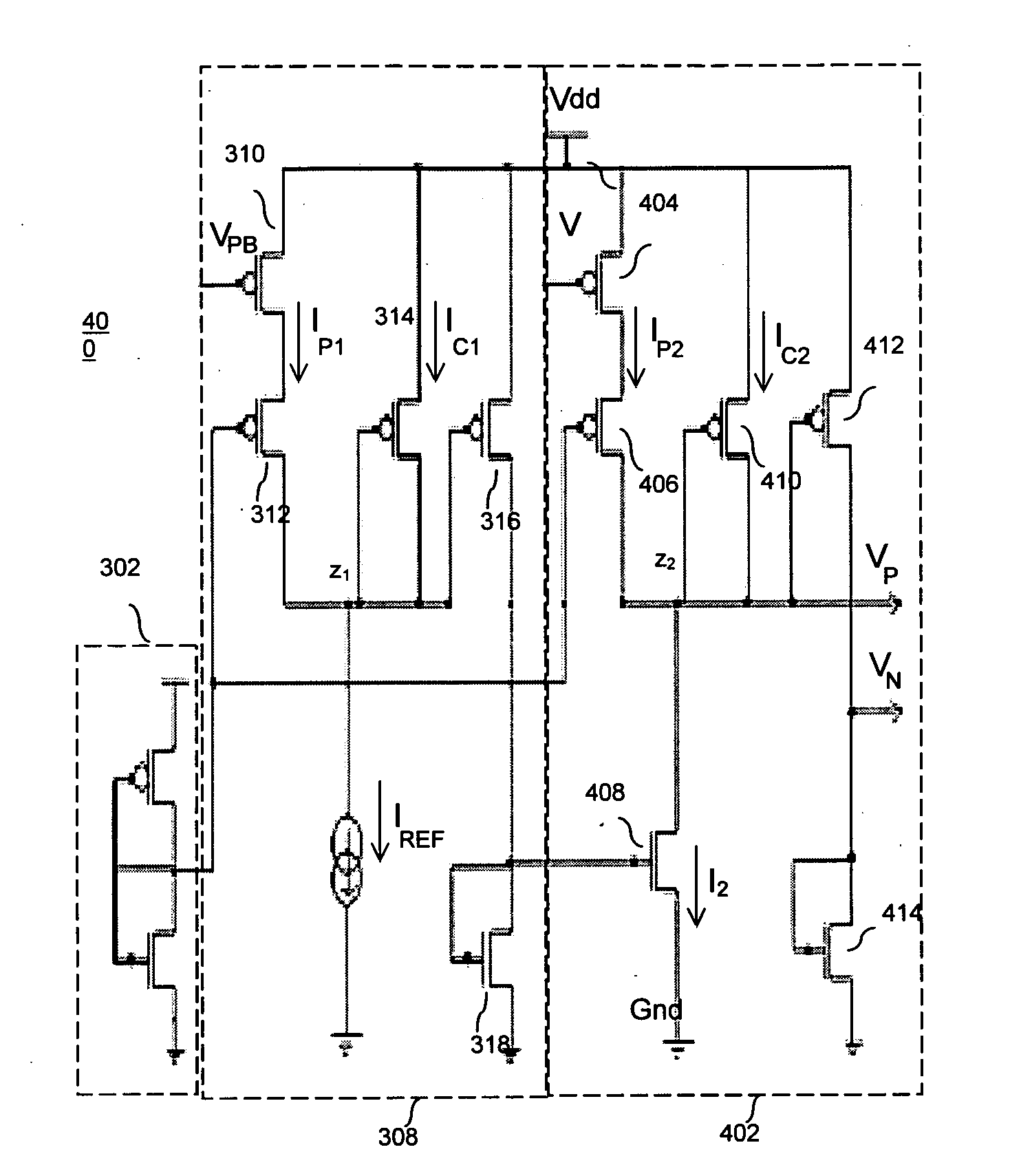

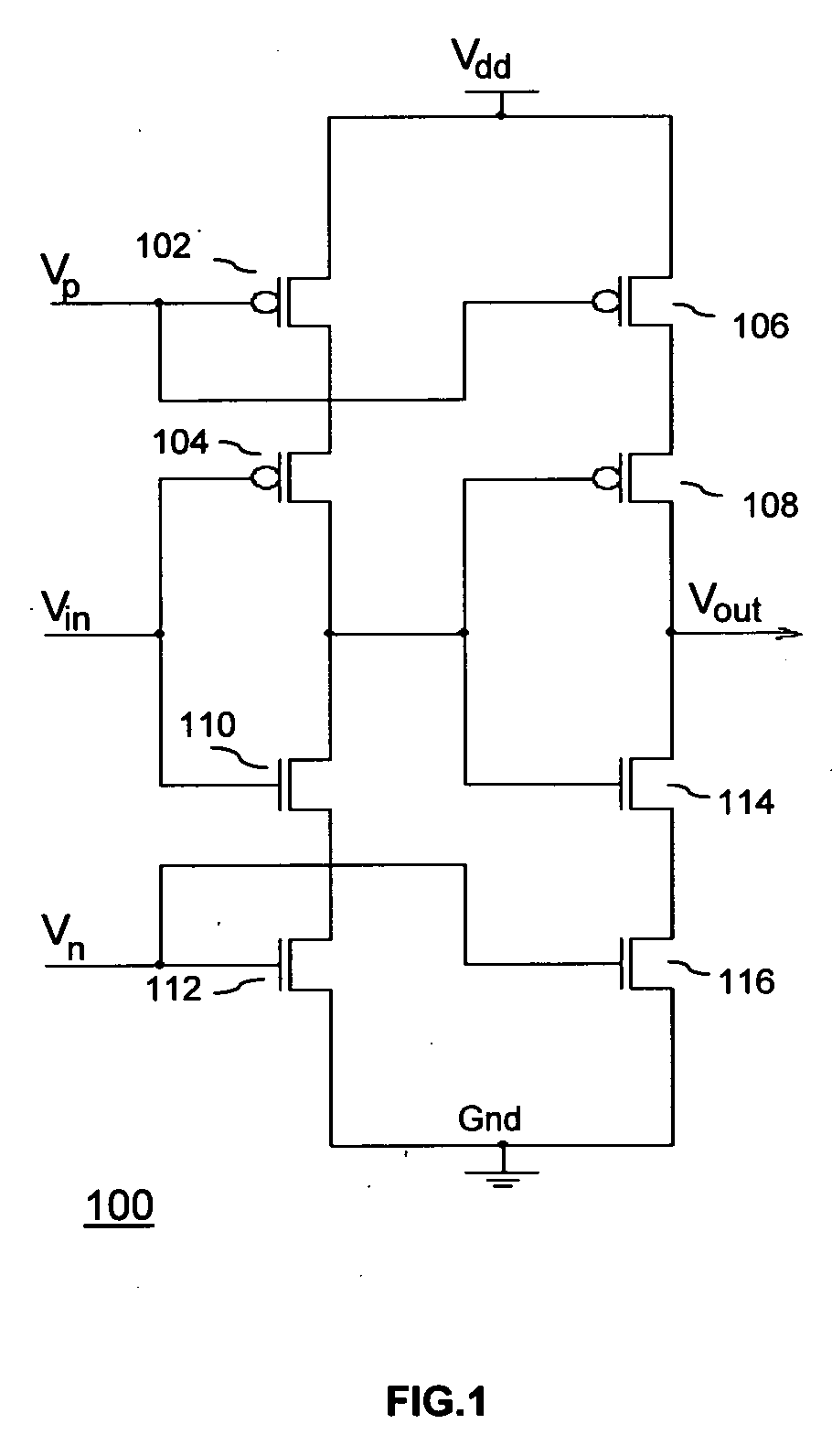

Apparatus and circuit for amplifying baseband signal

ActiveUS20130154741A1Reduce power consumptionCharge amplifiersPulse automatic controlSignal qualityAudio power amplifier

An operational amplifier circuit is provided. The operational amplifier circuit includes a differential amplifier of a cascade structure and a switched-capacitor type Common-Mode FeedBack (CMFB) circuit. The differential amplifier amplifies a difference between two input signals to output an anode output voltage and a negative output voltage. The switched-capacitor type CMFB circuit averages the anode output voltage and the negative output voltage of the differential amplifier, compares the average voltage with a reference voltage to generate a feedback signal based on a result of the comparison, and provides the feedback signal to the differential amplifier. Therefore, power consumption is reduced and a battery use time of a wireless terminal can be extended. Also, since an operational amplifier gain of each analog filter terminal is not negatively affected, a Direct Current (DC) offset is reduced, thereby improving signal quality.

Owner:SAMSUNG ELECTRONICS CO LTD

Test method for step response performance of phase-locked loop system

InactiveCN101498761AAvoid elicitingEasy to operateElectronic circuit testingPulse automatic controlEngineeringStep response

Owner:北京芯汇中秀电子技术有限公司

Delay phase-locked loop and method for improving accuracy of delay phase-locked loop

ActiveCN104124964AHigh precisionIncrease layout areaPulse automatic controlPhase differenceMiddle phase

The invention provides a delay phase-locked loop and a method for improving the accuracy of the delay phase-locked loop, wherein the accuracy of the delay phase-locked loop is at least doubled on the premise of increasing a domain area and power consumption as little as possible. The delay phase-locked loop comprises a DLL delay chain, wherein the DLL delay chain comprises a DLL coarse tuning chain and a DLL fine tuning chain. The delay phase-locked loop is characterized in that a middle phase generator used for generating the middle phase of the odd clock and the even clock of an input clock signal is arranged between the DLL coarse tuning chain and the DLL fine tuning chain. The method for improving the accuracy of the delay phase-locked loop comprises is generating two clock signals which are an odd-even clock and a middle clock, through the even clocks and the odd clocks of two input clock signals, wherein the phase difference of the odd-even clock and the middle clock is one half of the phase difference of the even clock and the odd clock.

Owner:XI AN UNIIC SEMICON CO LTD

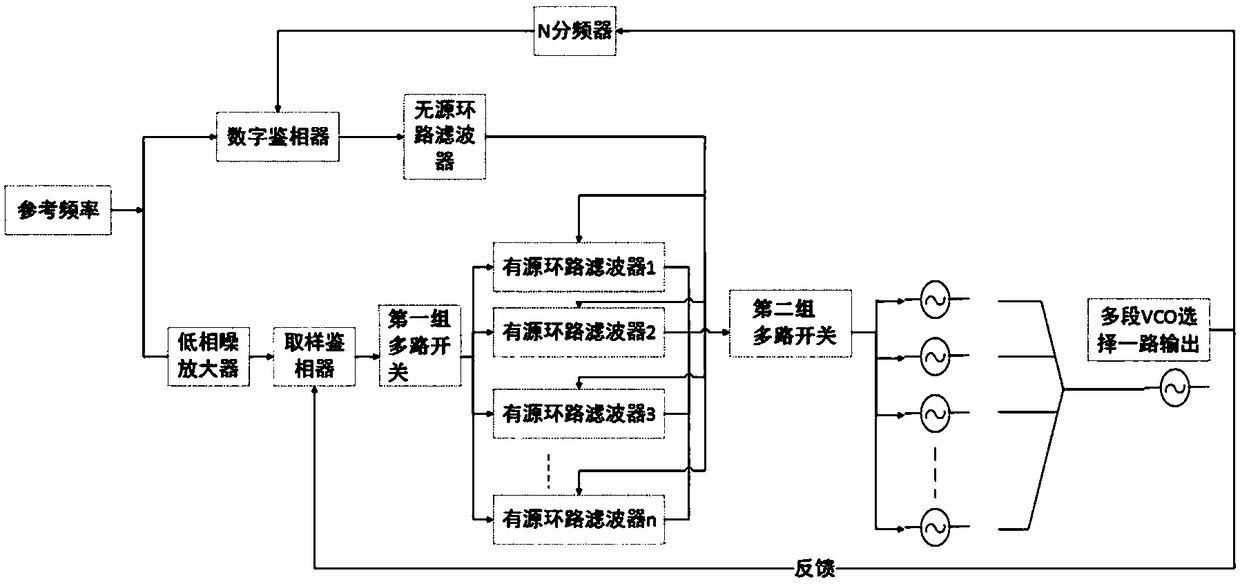

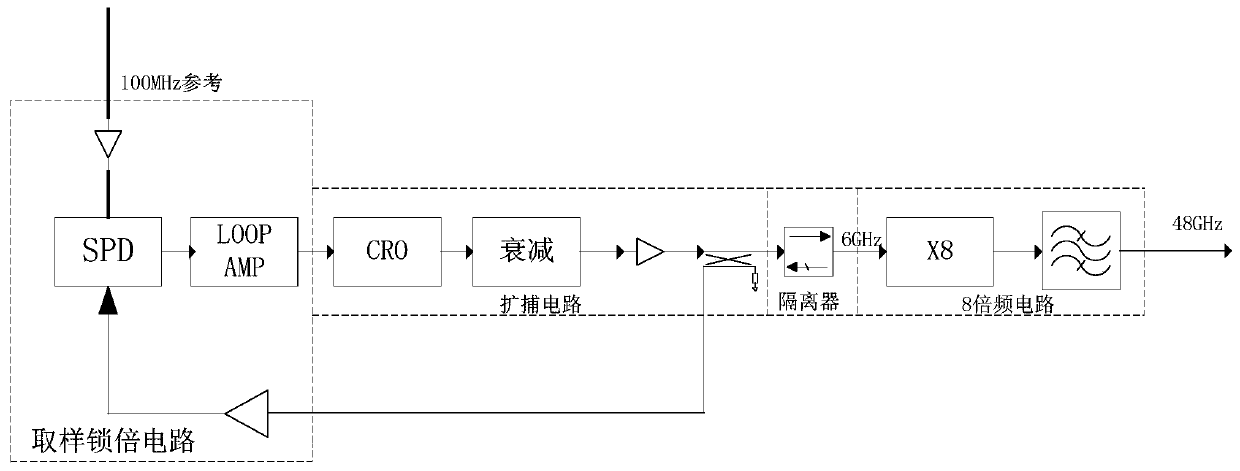

A low phase noise broadband microwave frequency source circuit

ActiveCN109088634AReduce phase noiseAchieve the effect of low phase noisePulse automatic controlLoop filterPhase detector

Owner:SOUTHEAST UNIV

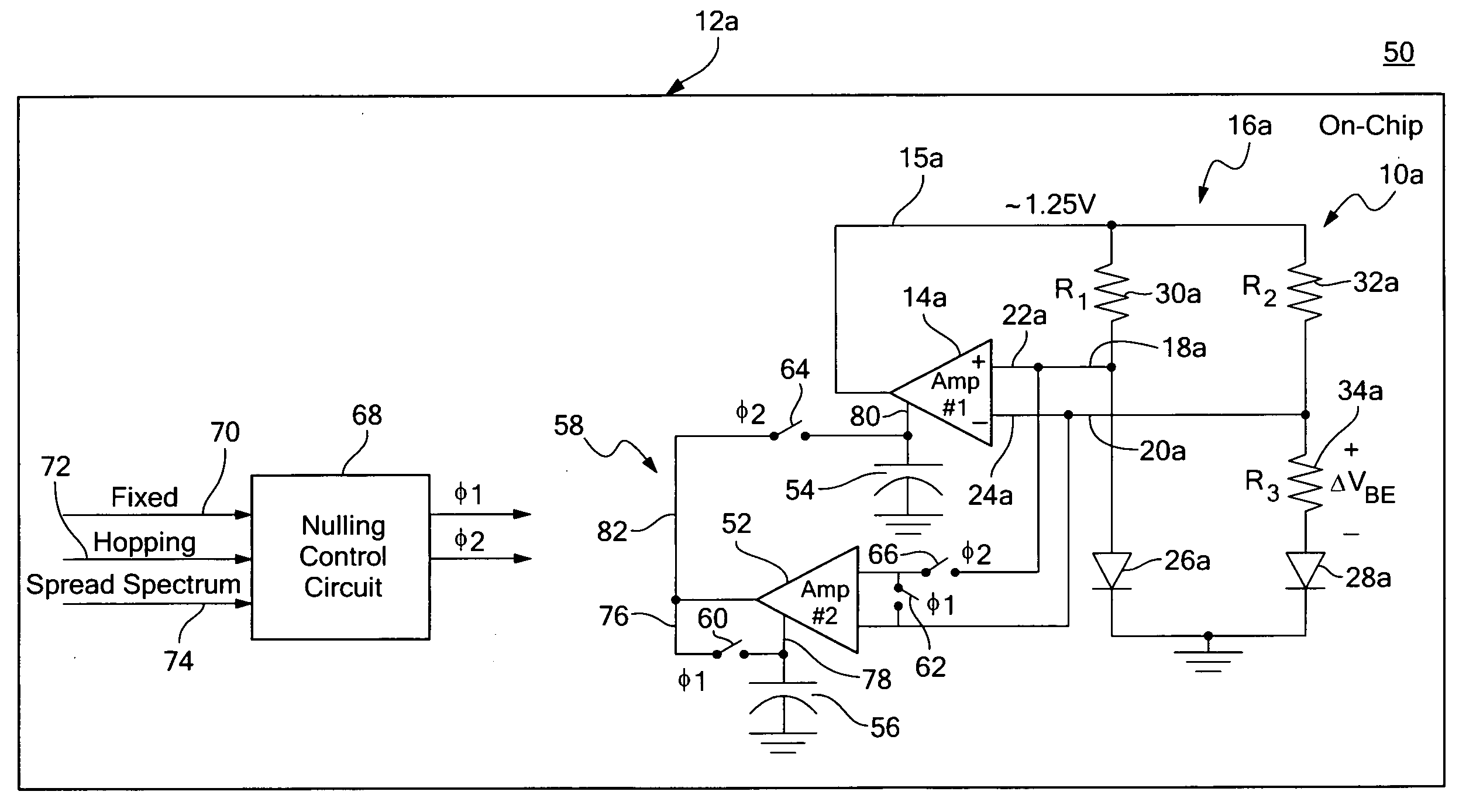

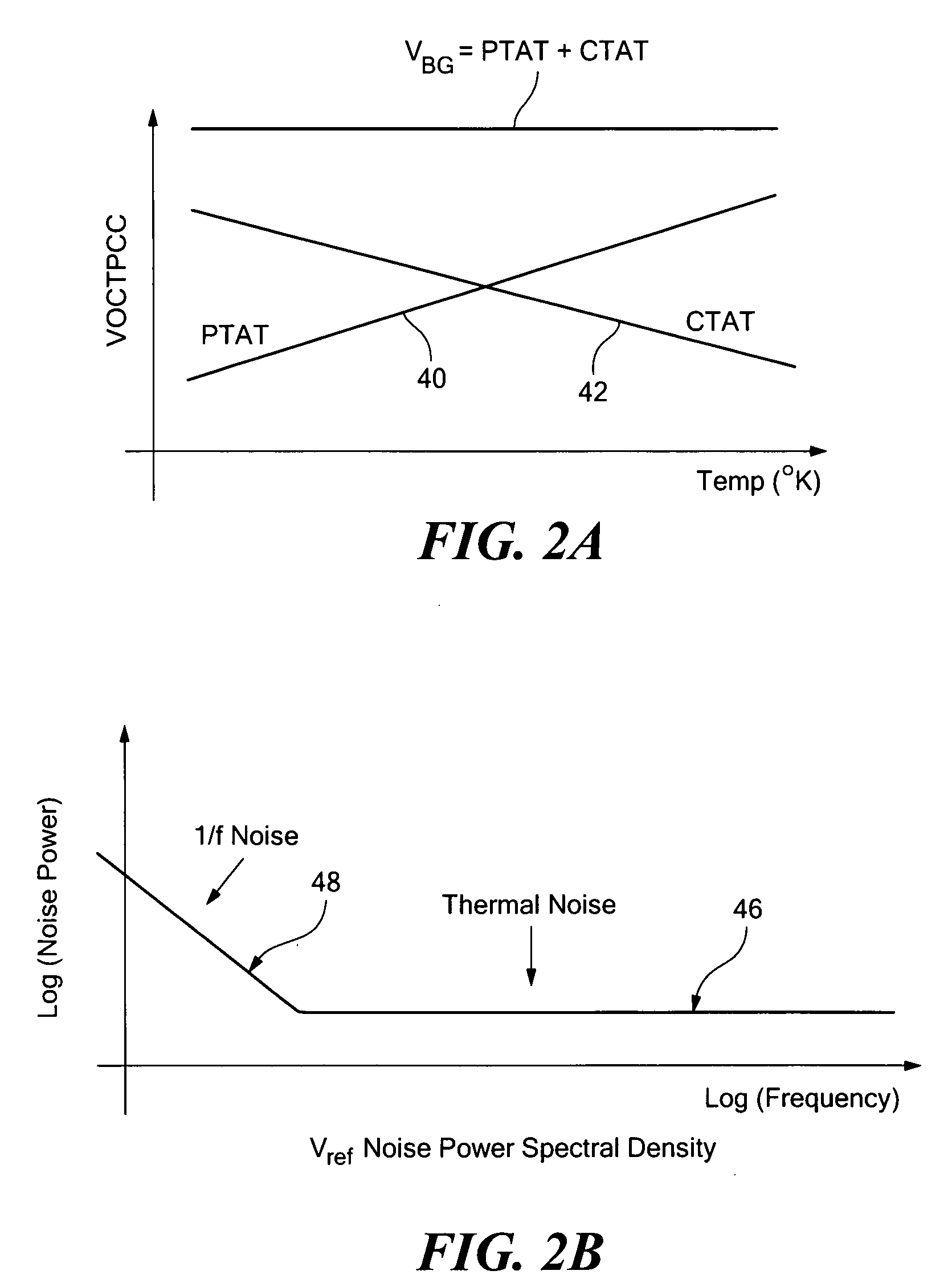

Auto-nulled bandgap reference system and strobed bandgap reference circuit

ActiveUS20080079413A1Eliminate the problemReduce voltage offsetPulse automatic controlPulse shapingVoltageEngineering

Owner:ANALOG DEVICES INC

Phase and/or frequency detector, phase-locked loop and operation method for the phase-locked loop

ActiveUS8461890B1Extended maintenance periodSolve the real problemPulse automatic controlControl signalEngineering

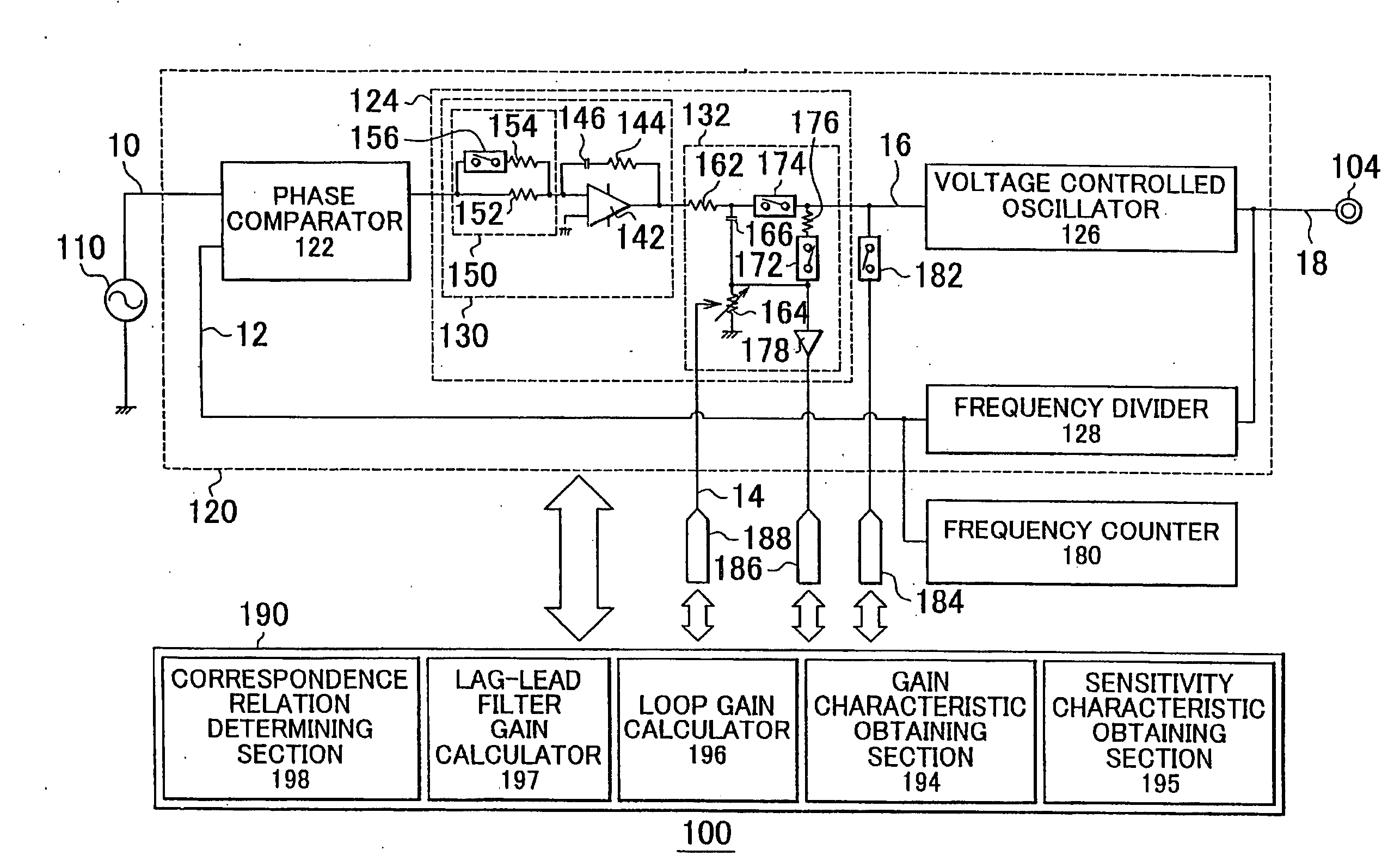

The present invention provides a phase and / or frequency detector, a PLL and an operation method for the PLL. The phase and / or frequency detector comprises two flip-flops, a logic gate, a control circuit and a delay circuit. The clock-input terminals of the two flip-flops receive a reference signal and a frequency-divided signal respectively. The logic gate receives signals outputted from the data-output terminals of the two flip-flops. The control circuit is configured for generating a corresponding delay control signal according to an oscillating frequency of an oscillating signal outputted from the PLL. The delay circuit is configured for altering a prolonged period according to the delay control signal to output a reset signal to the reset terminals of the two flip-flops.

Owner:UNITED MICROELECTRONICS CORP

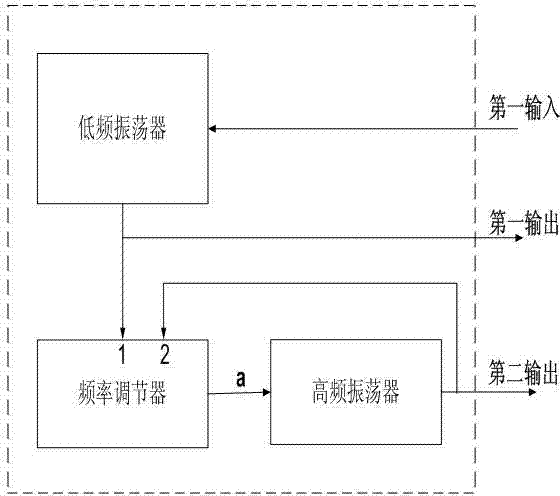

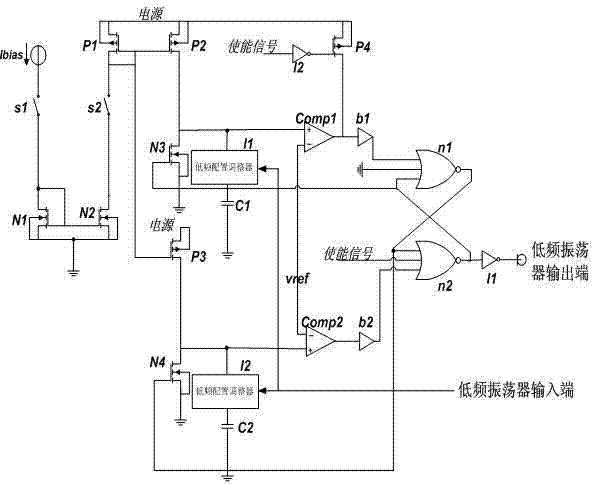

Method for outputting high-precision and high-frequency clock signals and oscillating circuit

ActiveCN103888138ASimple structureAccurate reference frequencyPulse automatic controlEngineeringLow-frequency oscillation

Owner:合肥健天电子有限公司

Phase lock oscillator and wireless communications device including phase lock oscillator

InactiveUS20090179708A1Eliminate the problemPulse automatic controlSingle output arrangementsVoltagePhysics

Owner:FUJITSU LTD

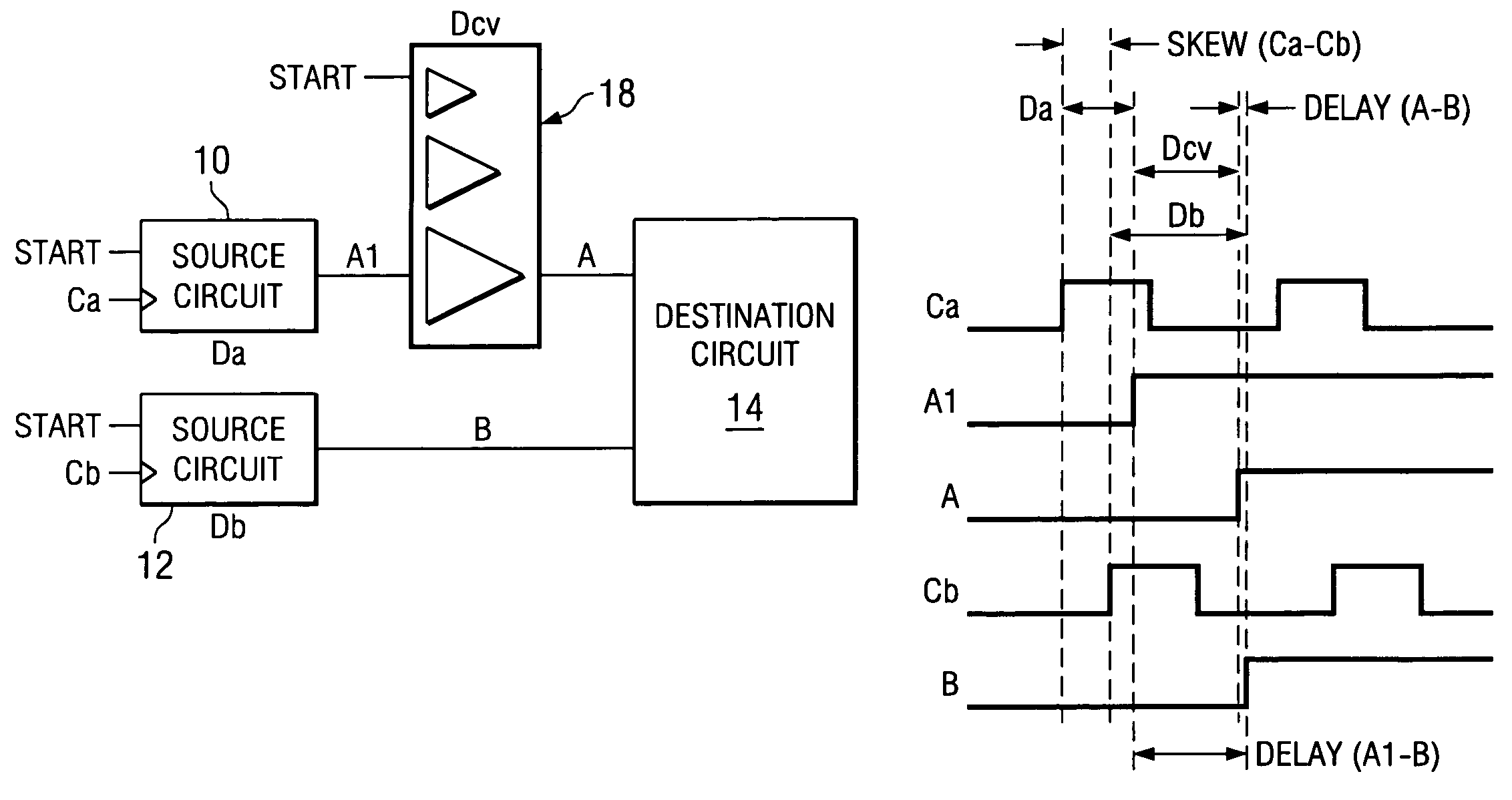

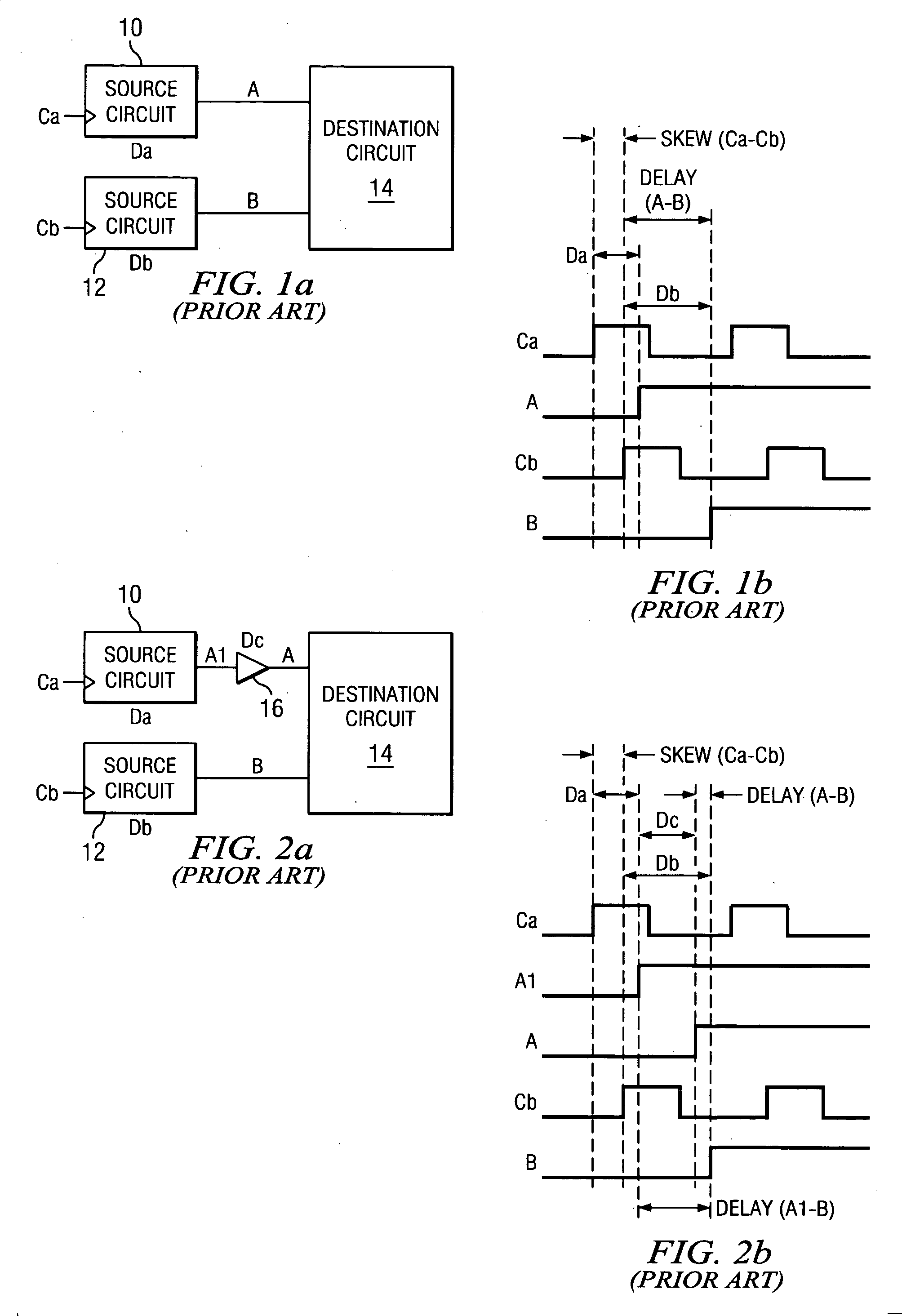

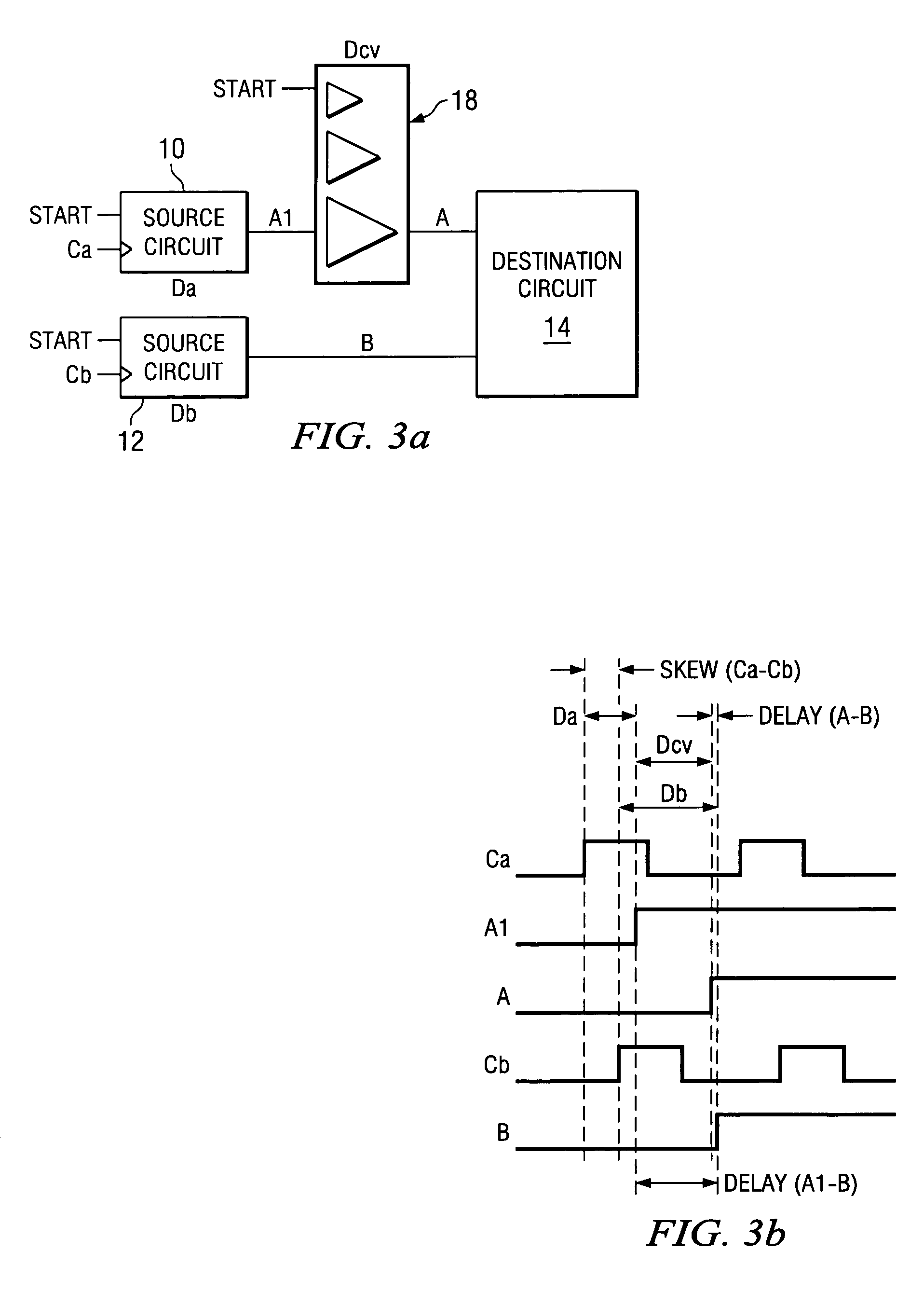

Circuitry for reducing the skew between two signals

ActiveUS20050040862A1Delay minimizationPulse automatic controlVoltage-current phase angleComputer scienceIntegrated circuit

Owner:TEXAS INSTR INC

Phase locked loop and voltage controlled oscillator

Owner:PHISON ELECTRONICS

Semiconductor integrated circuit device with power-on reset circuit for detecting the operating state of an analog circuit

A semiconductor integrated circuit device operates using a first power supply and a second power supply differing from the first power supply in voltage. The semiconductor integrated circuit device includes a first detecting circuit which detects that the first power supply has exceeded a specific voltage, a second detecting circuit which detects that the second power supply has exceeded a specific voltage, and a check circuit which checks the operating state of an analog circuit carrying out an analog operation using the first power supply and outputs a control signal indicating whether the analog circuit is operating properly. The detecting level of the first detecting circuit is determined on the basis of the control signal. A power-on reset signal is output according to the result of the detection at the first and second detecting circuits.

Owner:KK TOSHIBA

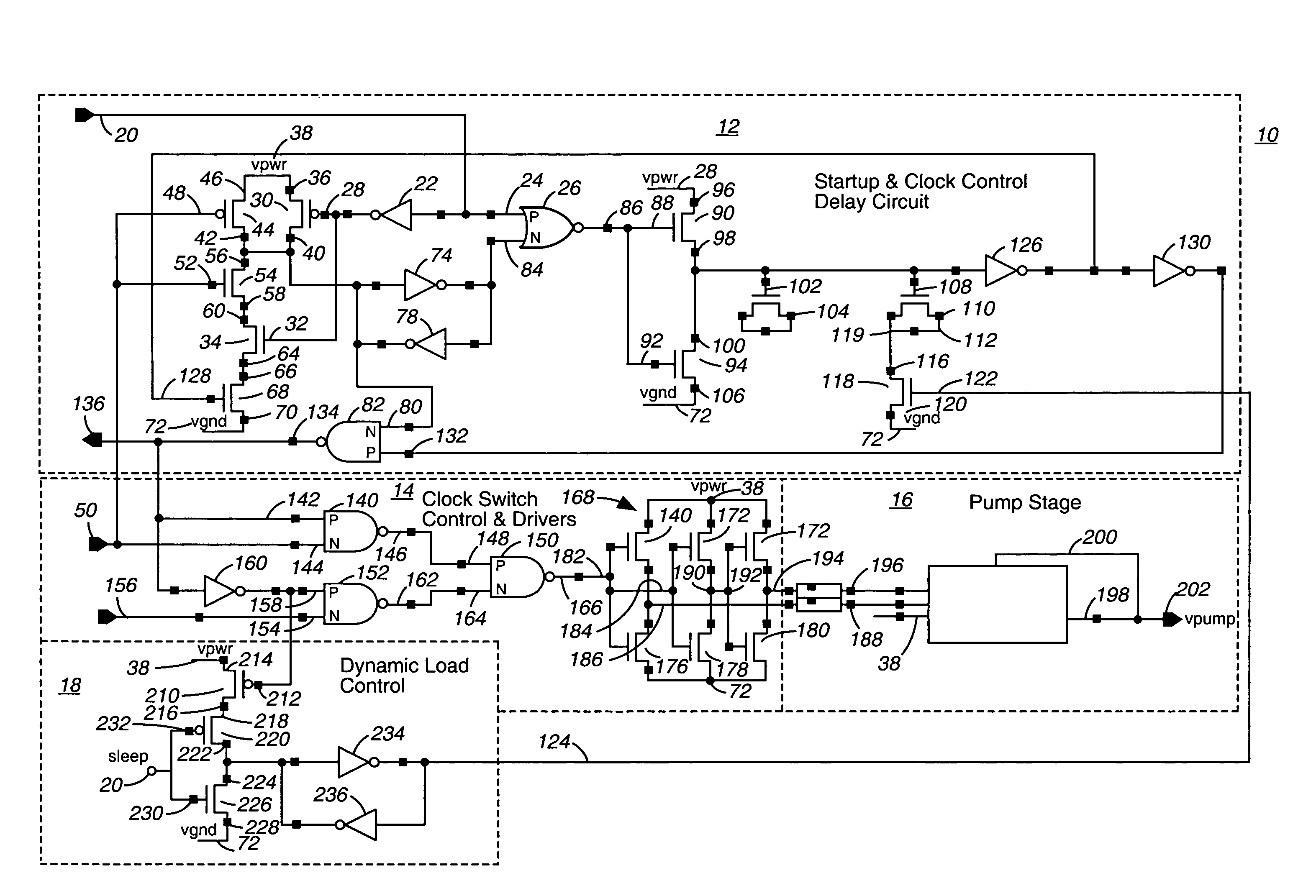

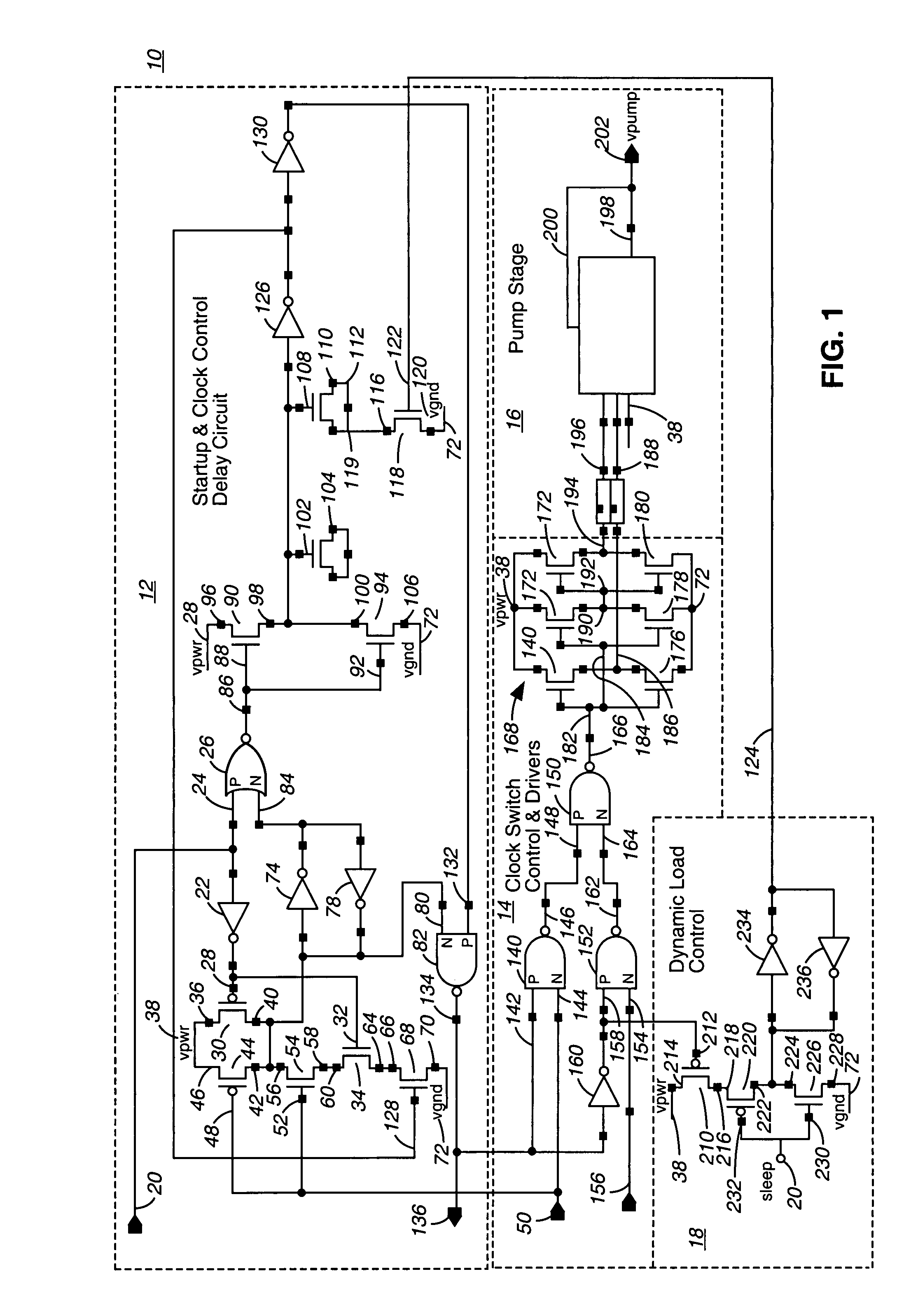

Charge pump control circuit and method

ActiveUS7671664B1Fast boosted output voltageReduce power consumptionPulse automatic controlDc-dc conversionDriver circuitCapacitance

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

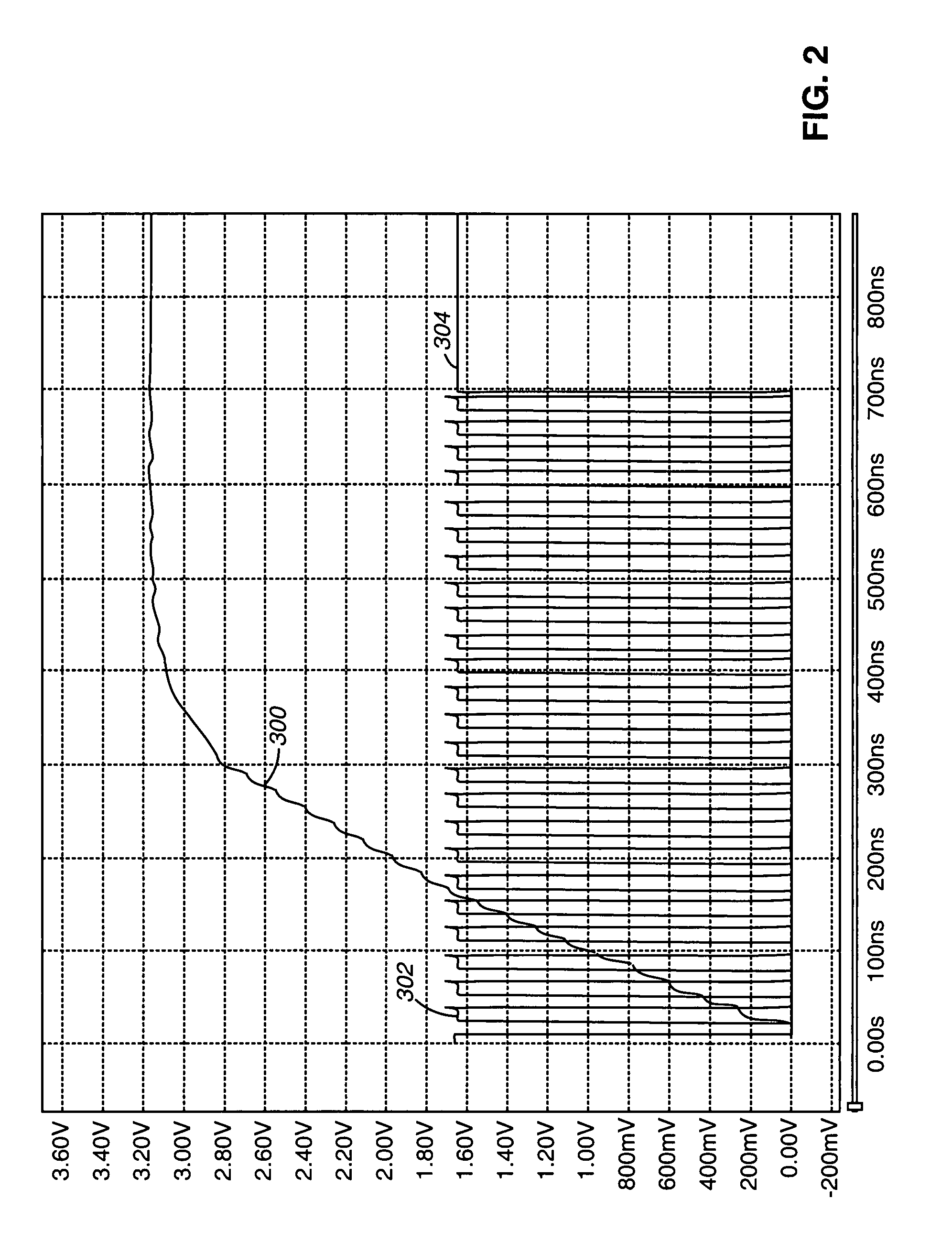

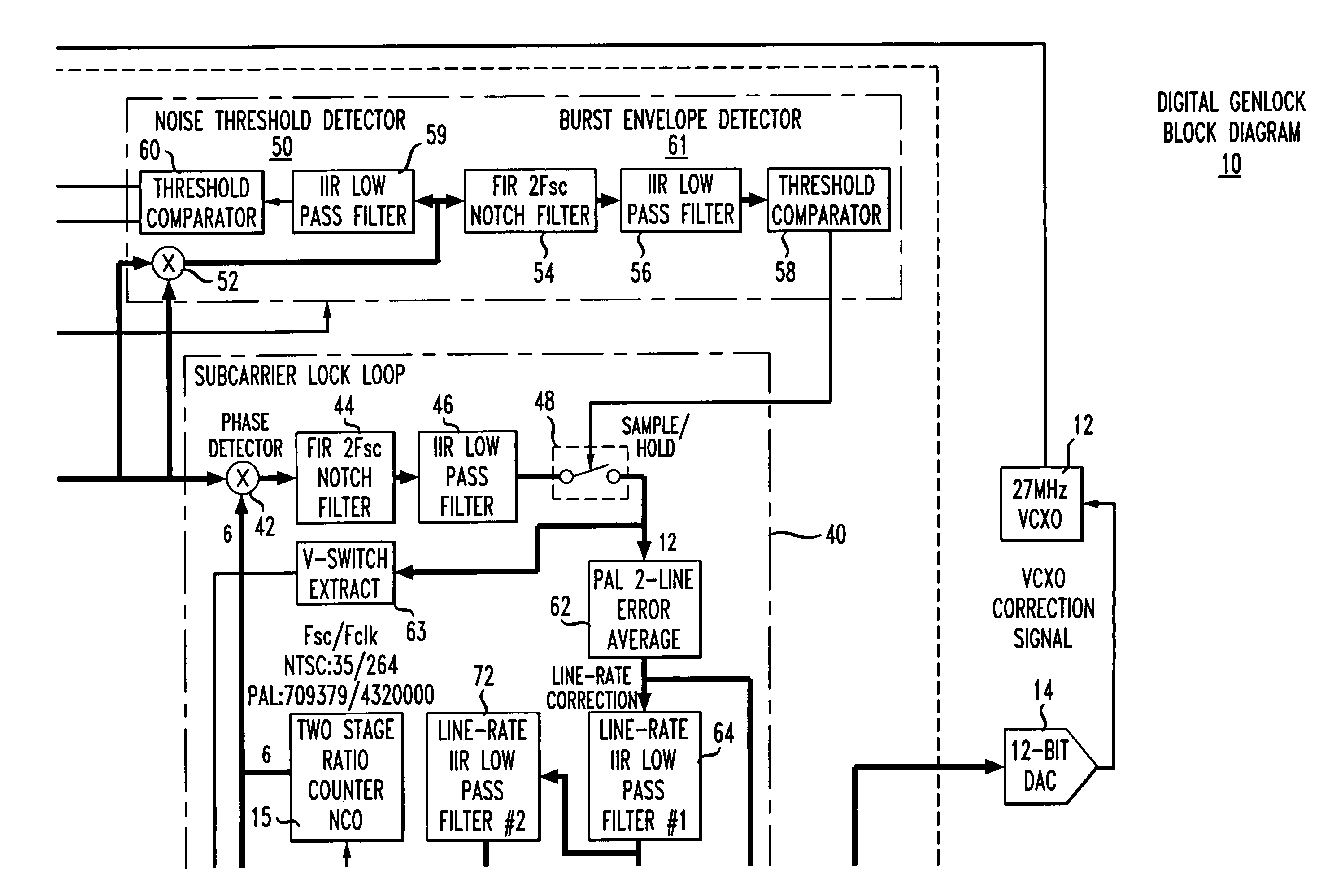

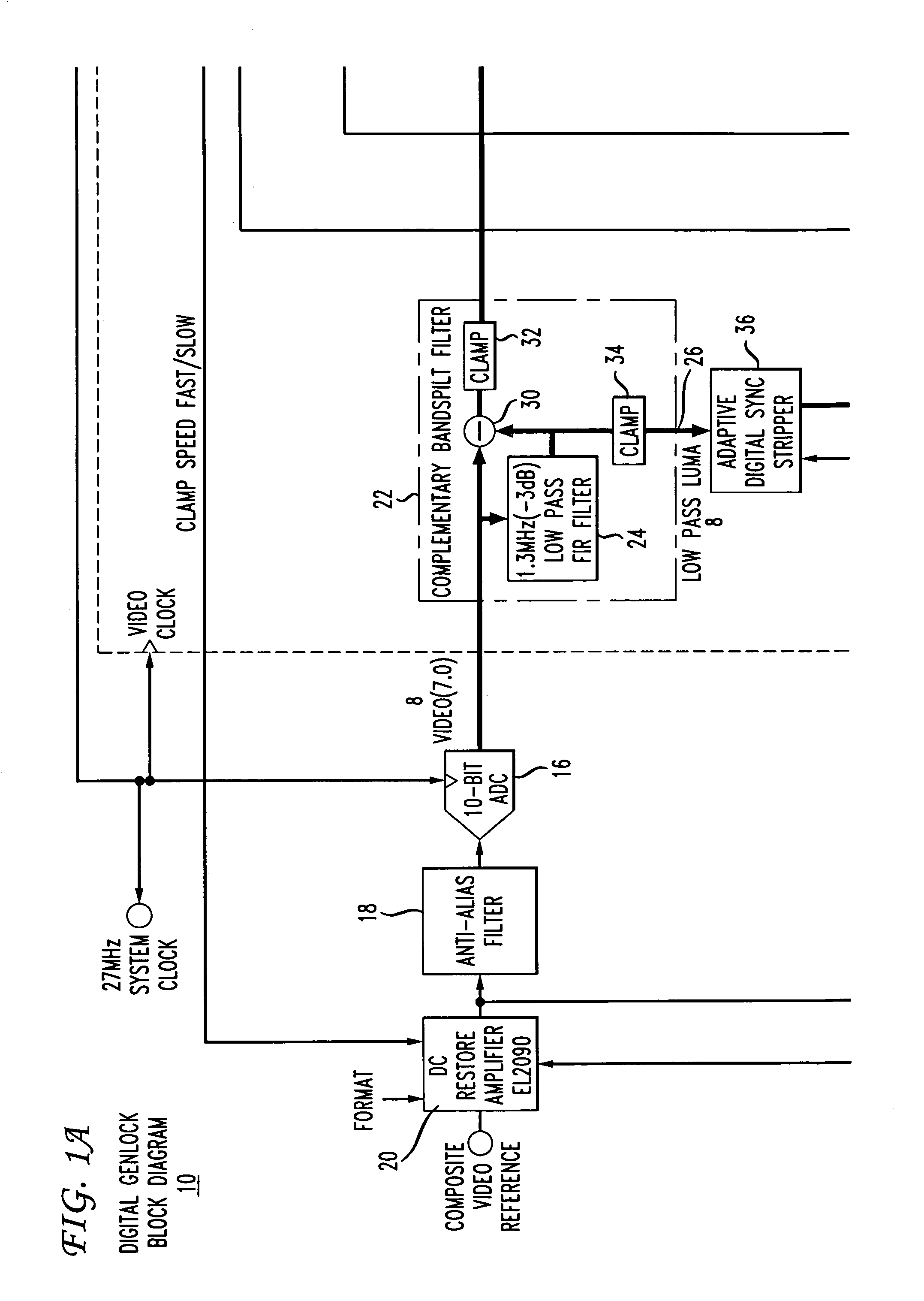

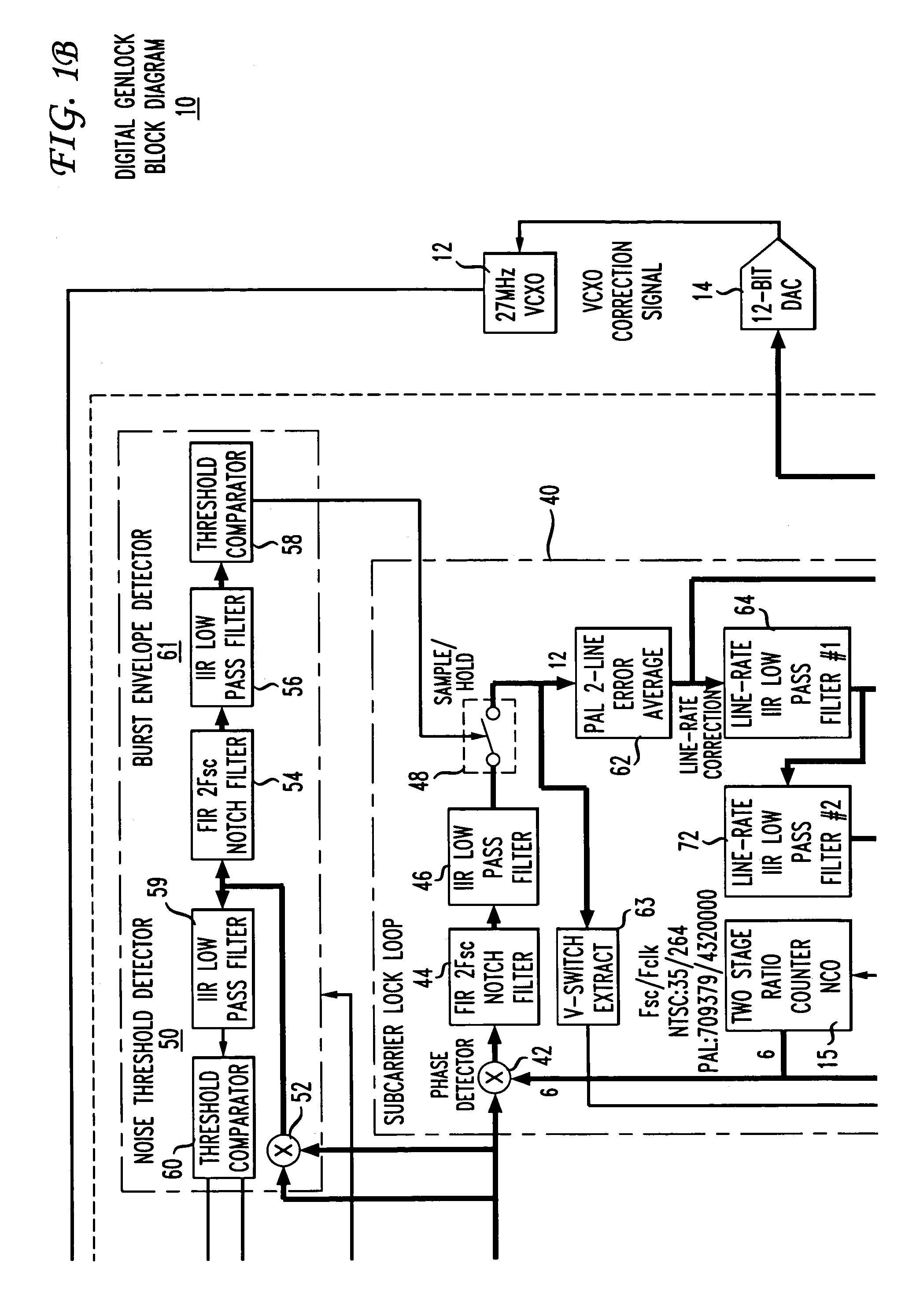

Digital synchronizing generator

InactiveUS7268825B2Television system detailsPulse automatic controlCarrier signalDigital controlled oscillator

Owner:GRASS VALLEY U S

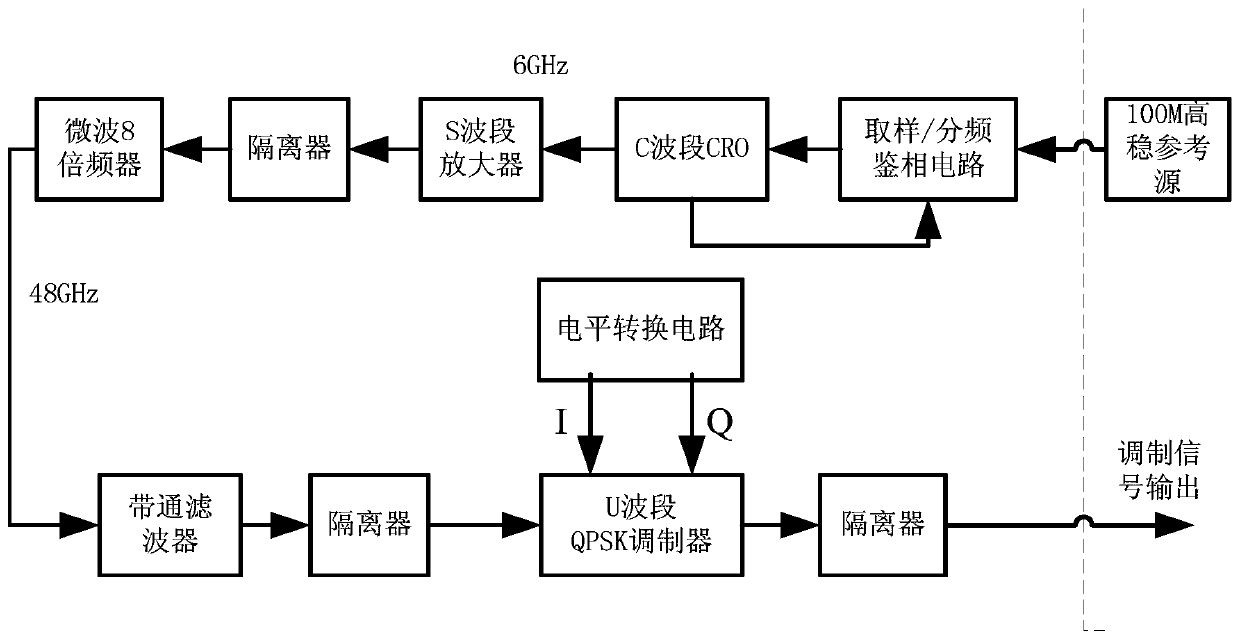

U-band microwave direct modulation system

ActiveCN110830040APulse automatic controlPhase-modulated carrier systemsCarrier signalFrequency band

Owner:XIAN INSTITUE OF SPACE RADIO TECH

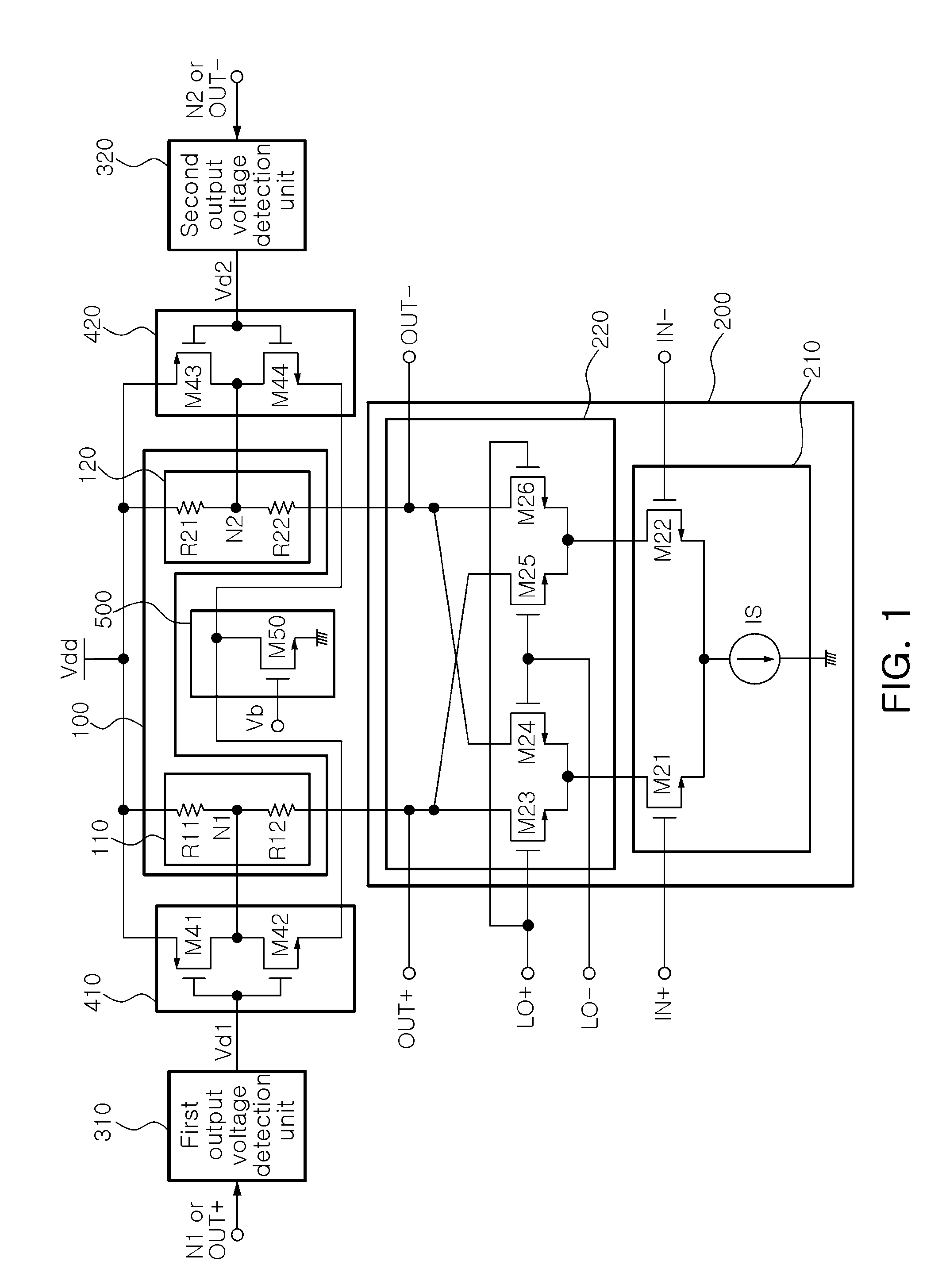

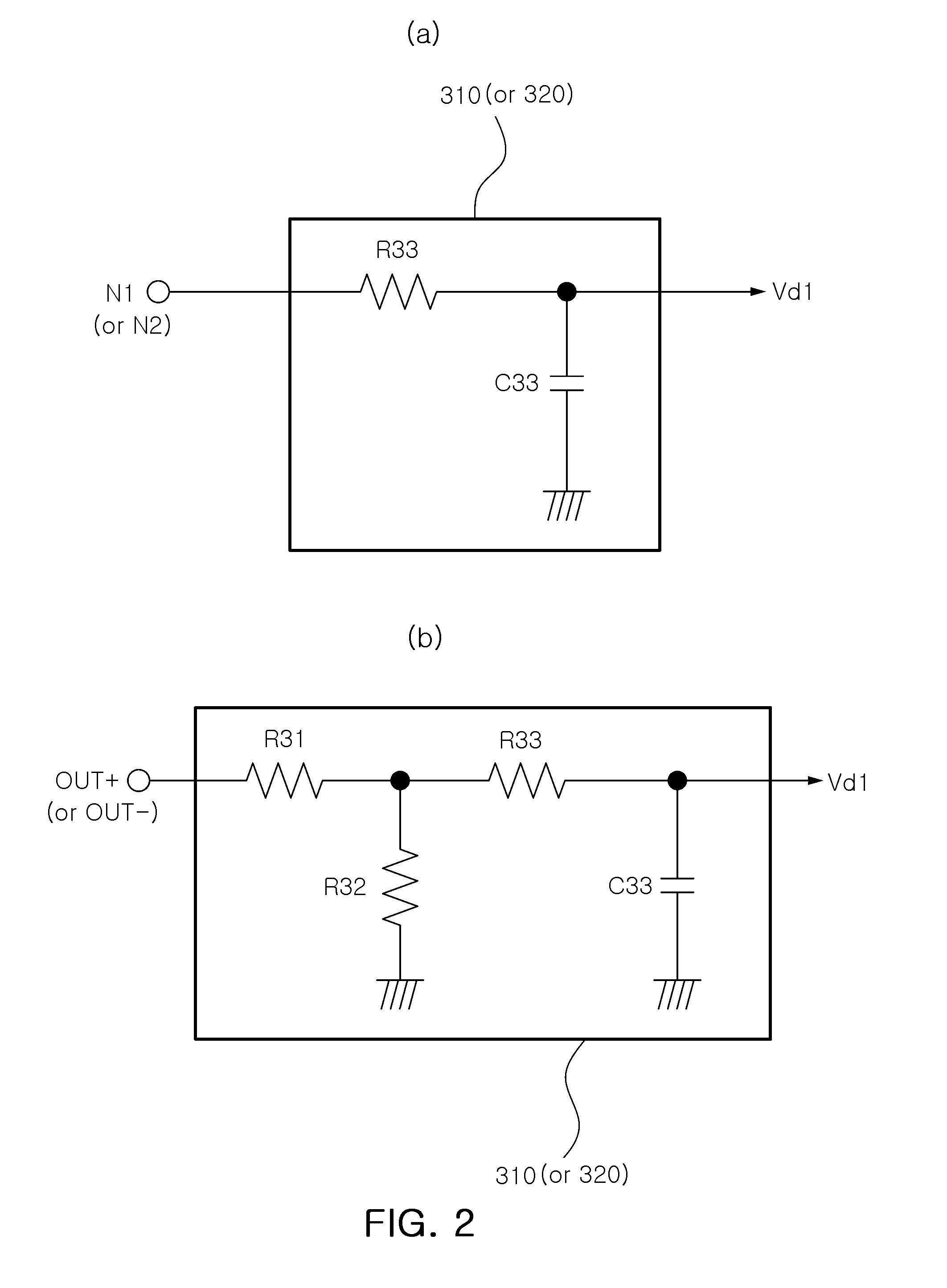

Mixer with differential DC offset cancellation function

InactiveUS20110037507A1Improve linearityModulation transference by semiconductor devices with minimum 2 electrodesPulse automatic controlPower flowFrequency mixer

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

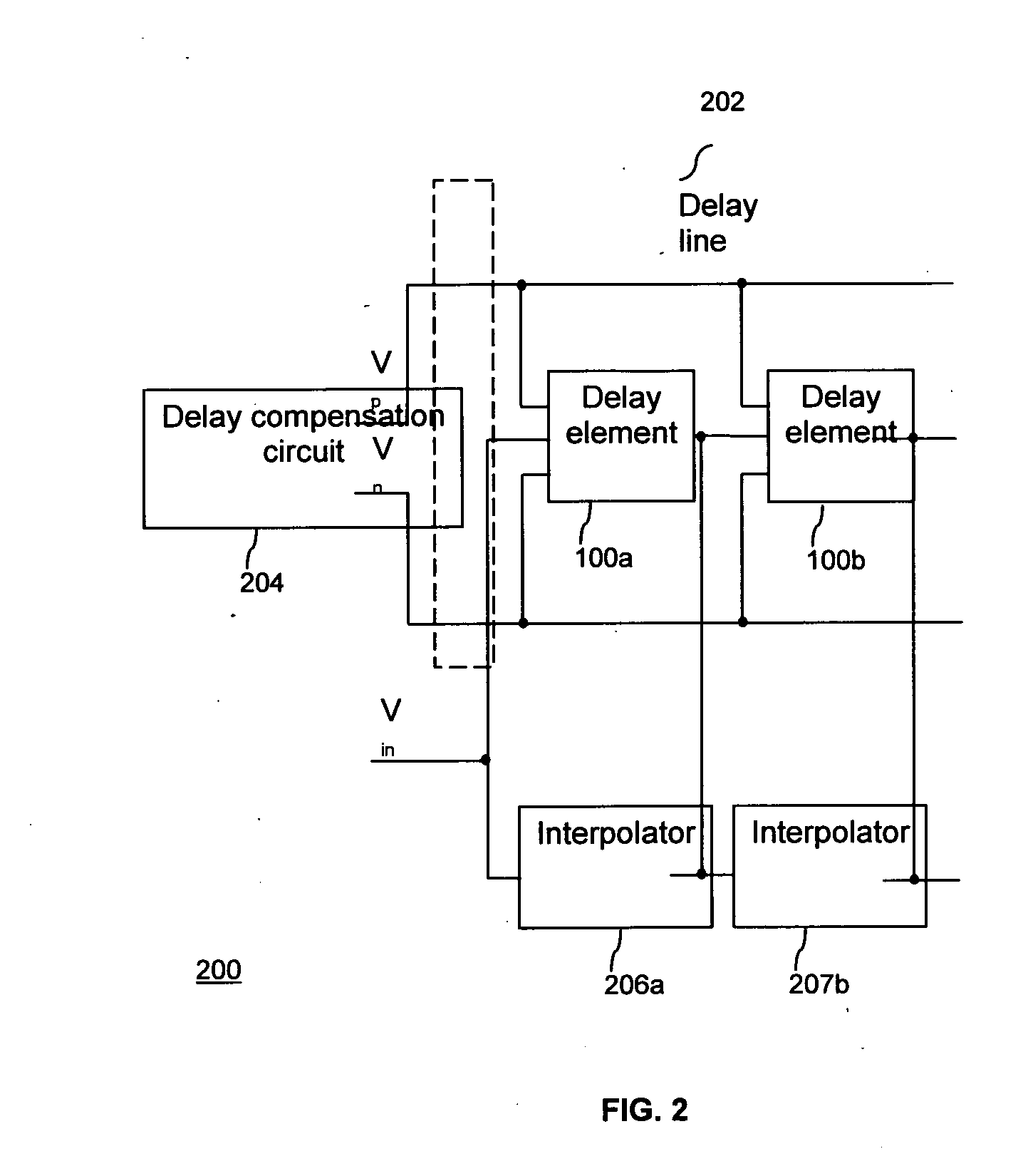

Method and system for open loop compensation of delay variations in a delay line

InactiveUS20110204958A1Low powerPulse automatic controlElectronic switchingReference currentEngineering

Owner:KPIT TECH LTD

Birefringent laser self-mixing Doppler velocity measurement method

InactiveCN111722244AIncrease the measurable rangeHigh precisionPulse automatic controlElectromagnetic wave reradiationBirefringent crystalPrism

The invention discloses a birefringent laser self-mixing Doppler velocity measurement method, which is based on a self-mixing interference effect of a large-frequency-difference birefringent double-frequency He-Ne laser, and comprises the steps of firstly, detecting the same moving target by utilizing two orthogonal polarization laser modes generated by the laser, and generating self-mixing interference at the same time; if a user wants to obtain self-mixing interference signals of two orthogonal polarization laser modes, separately detecting the two modes at a detection end of the system by using a Wollaston polarization splitting prism, carrying out independent detection by using two photoelectric detectors to obtain Doppler frequency shift mixing signals, extracting difference frequencyitems in the mixing signals, and finally, calculating the actual movement speed of a target by utilizing the linear relation between Doppler frequency shift and speed. According to the invention, themeasurable range of the self-mixing interference speed measurement technology is effectively expanded, and the optical carrier microwave frequency mainly depends on a birefringent crystal element ofthe laser cavity, so that the stability is very high, and the speed measurement precision is remarkably improved.

Owner:NANJING FOREST POLICE COLLEGE

Popular searches

Memory systems Specific program execution arrangements Complex mathematical operations Input/output processes for data processing Volume/mass flow measurement Thermometers using electric/magnetic elements Using electrical means Power supply for data processing Electric variable regulation Solid-state devices

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap