Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

47results about "Read-only memories" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

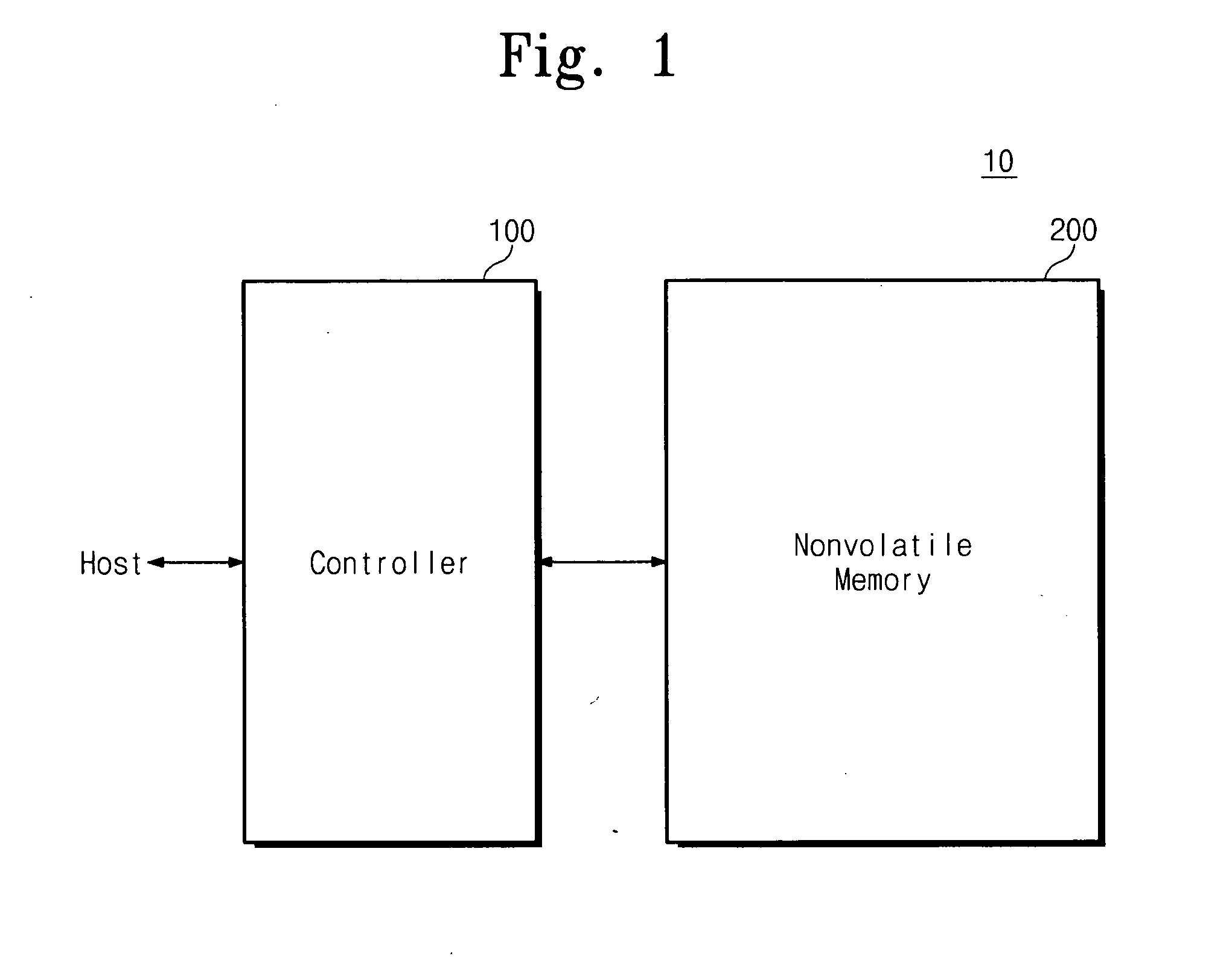

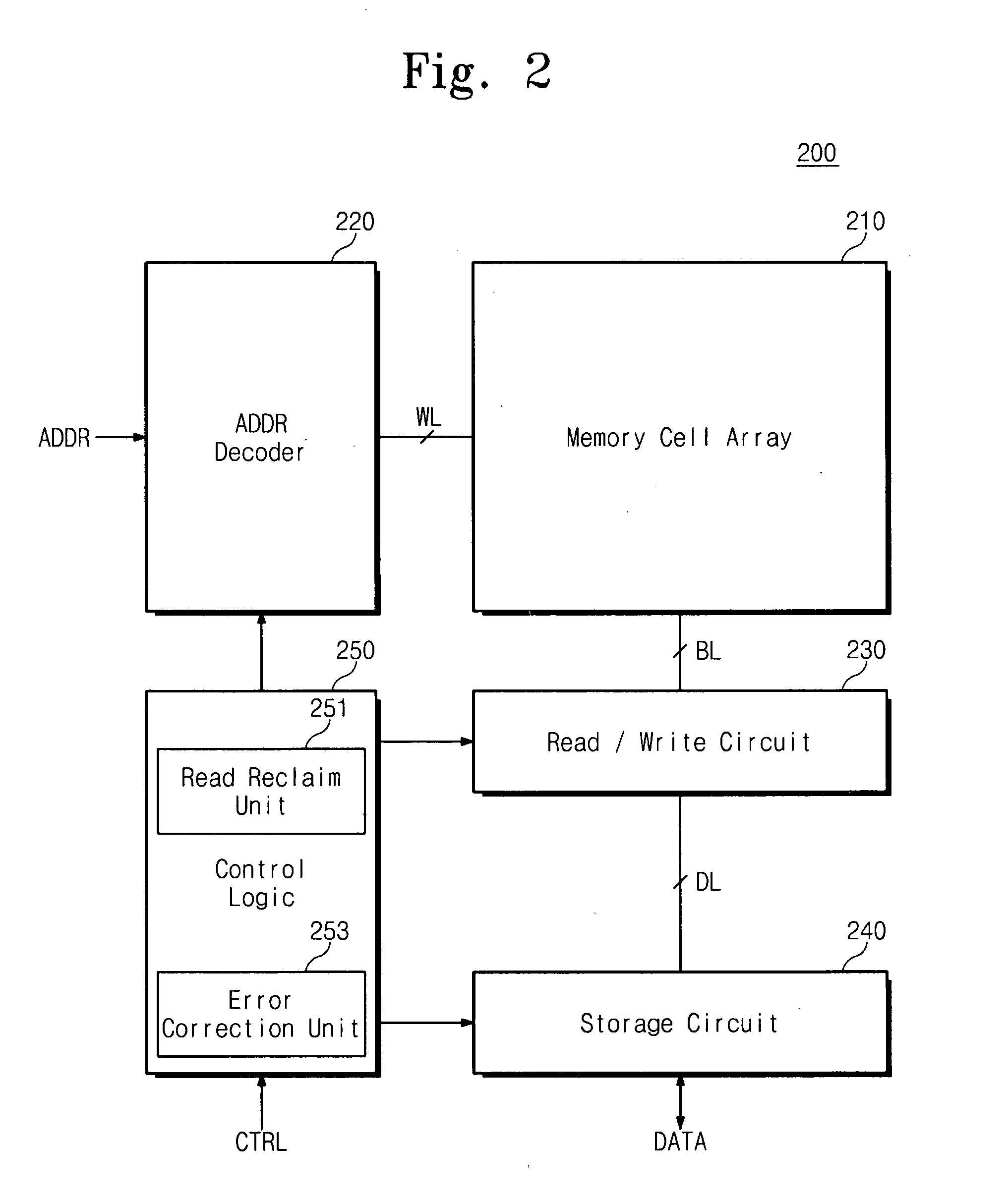

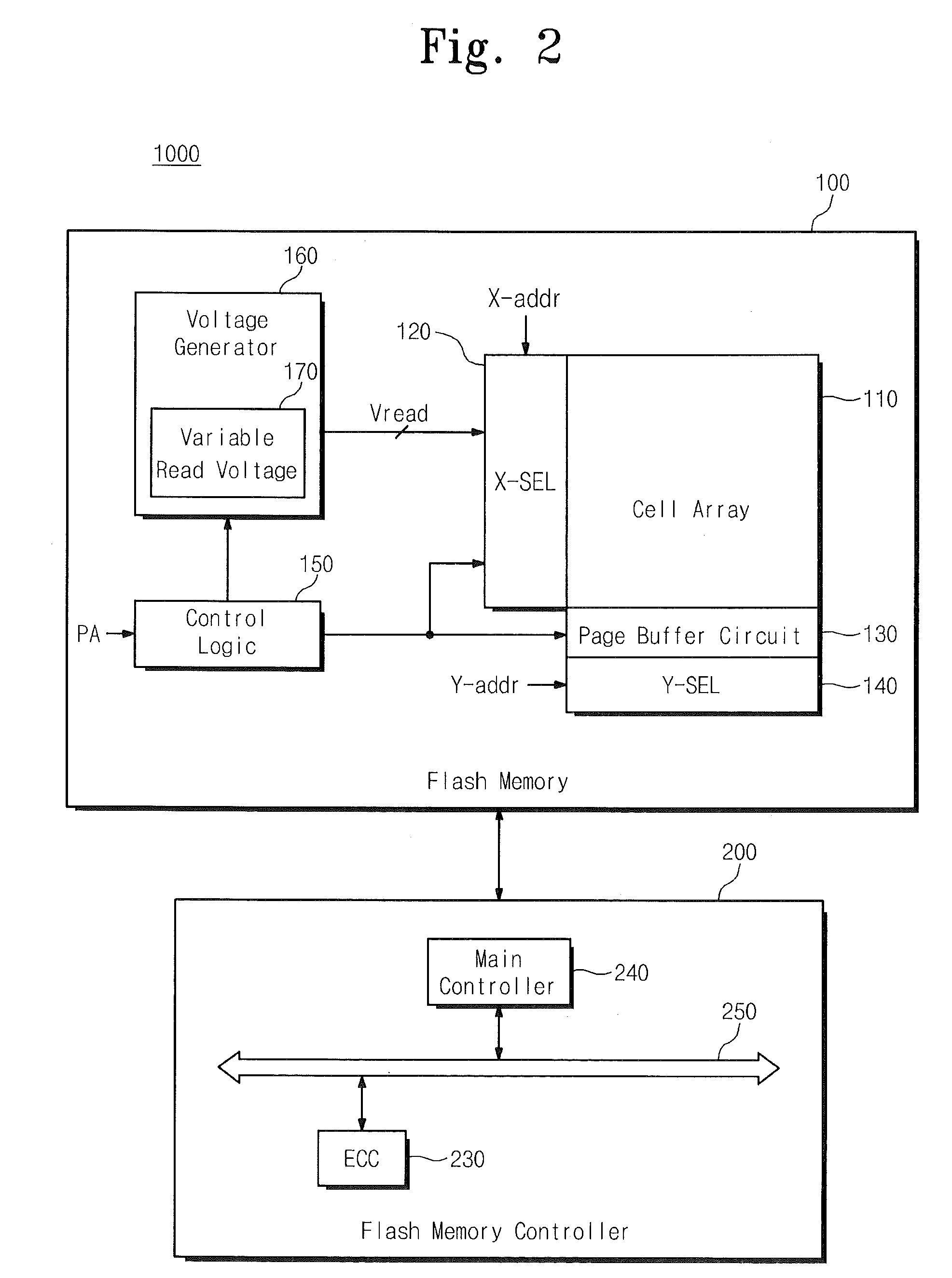

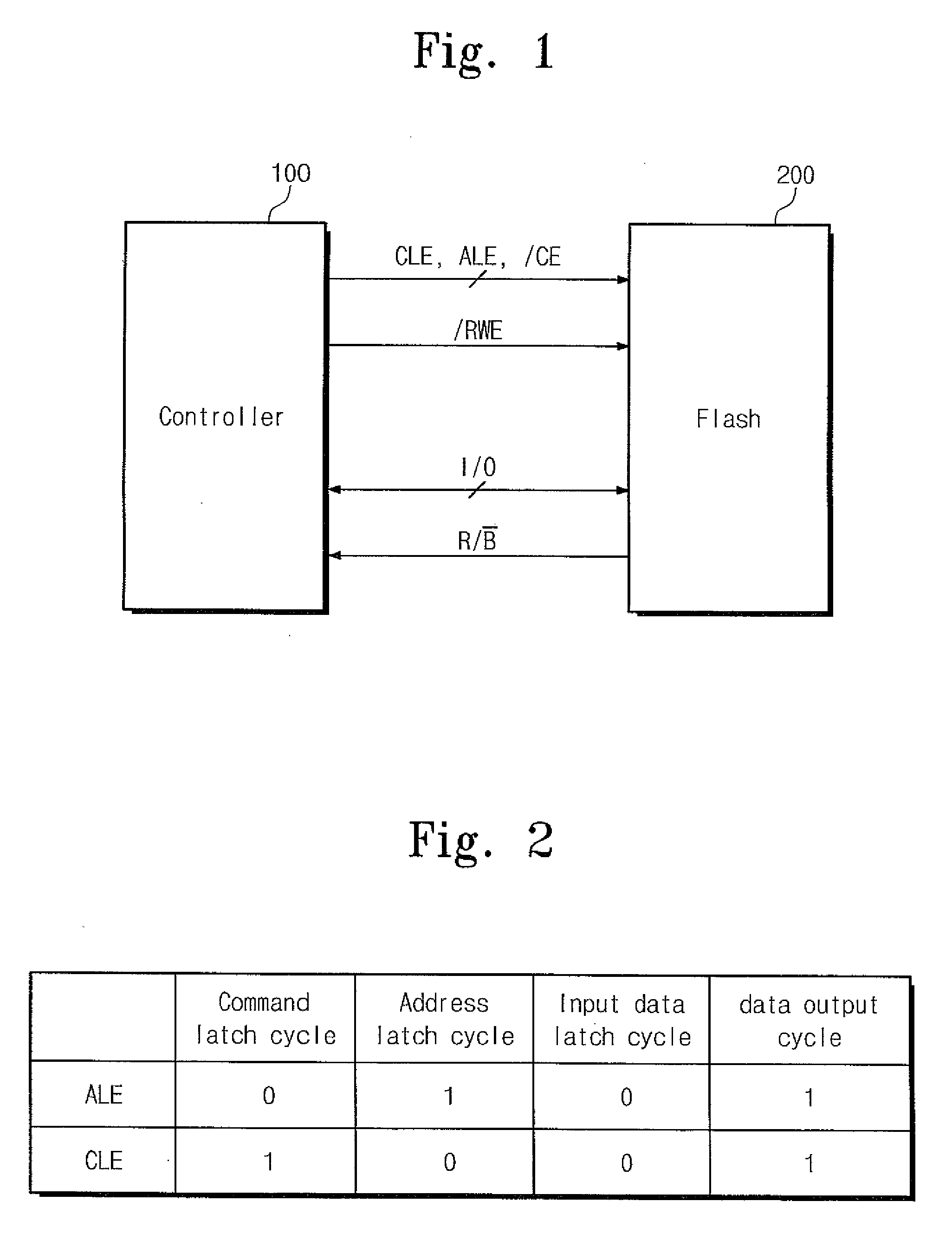

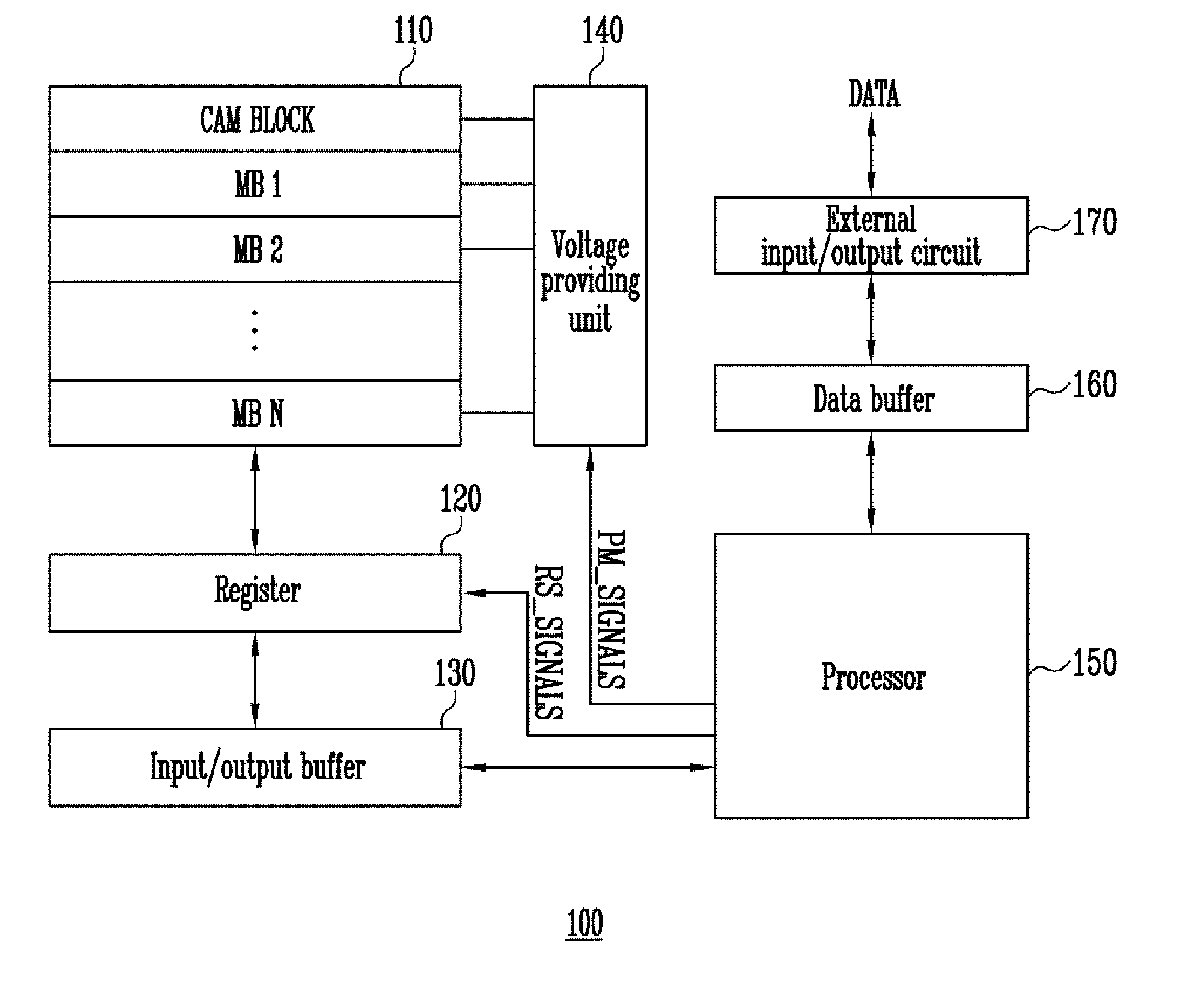

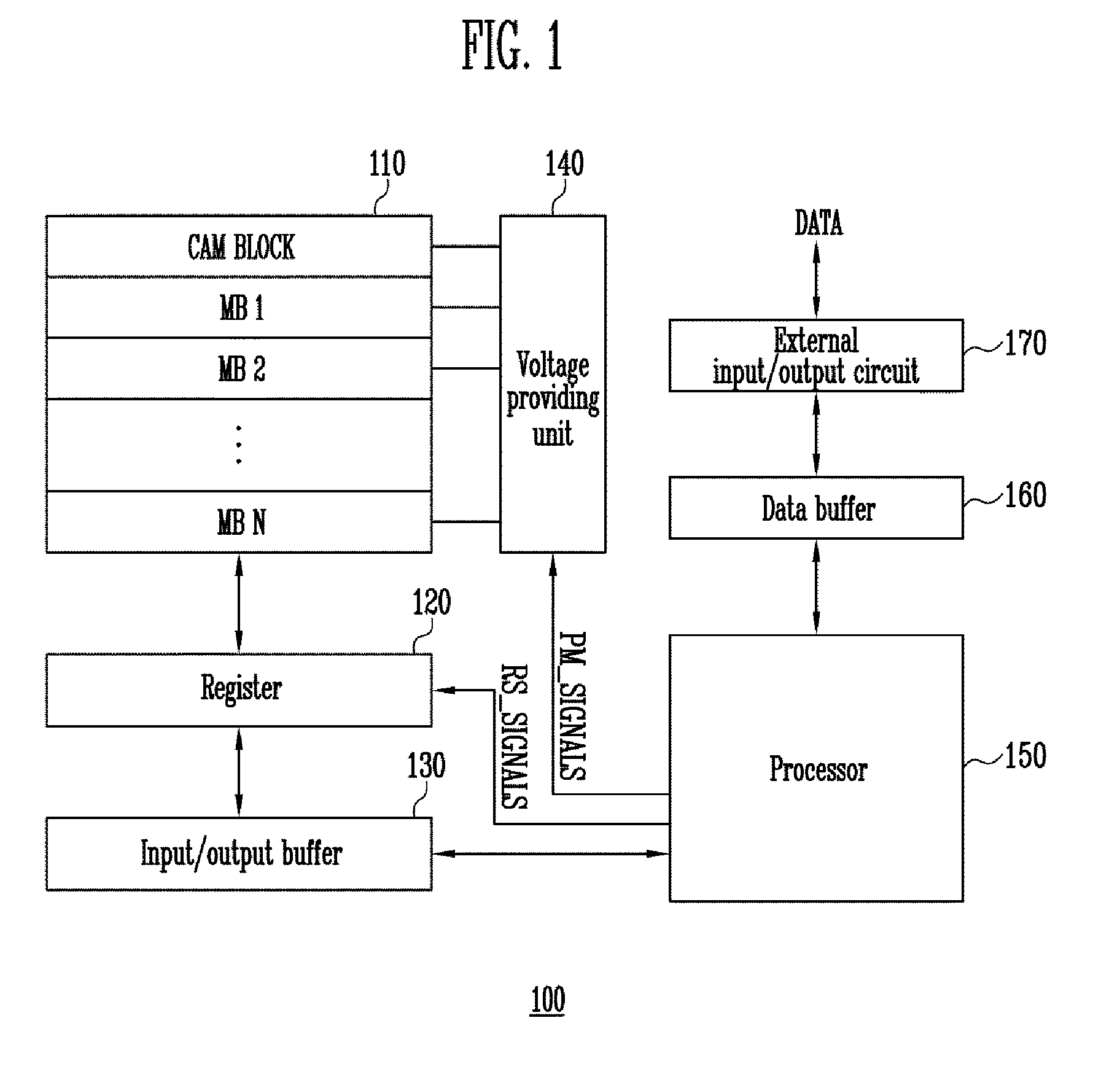

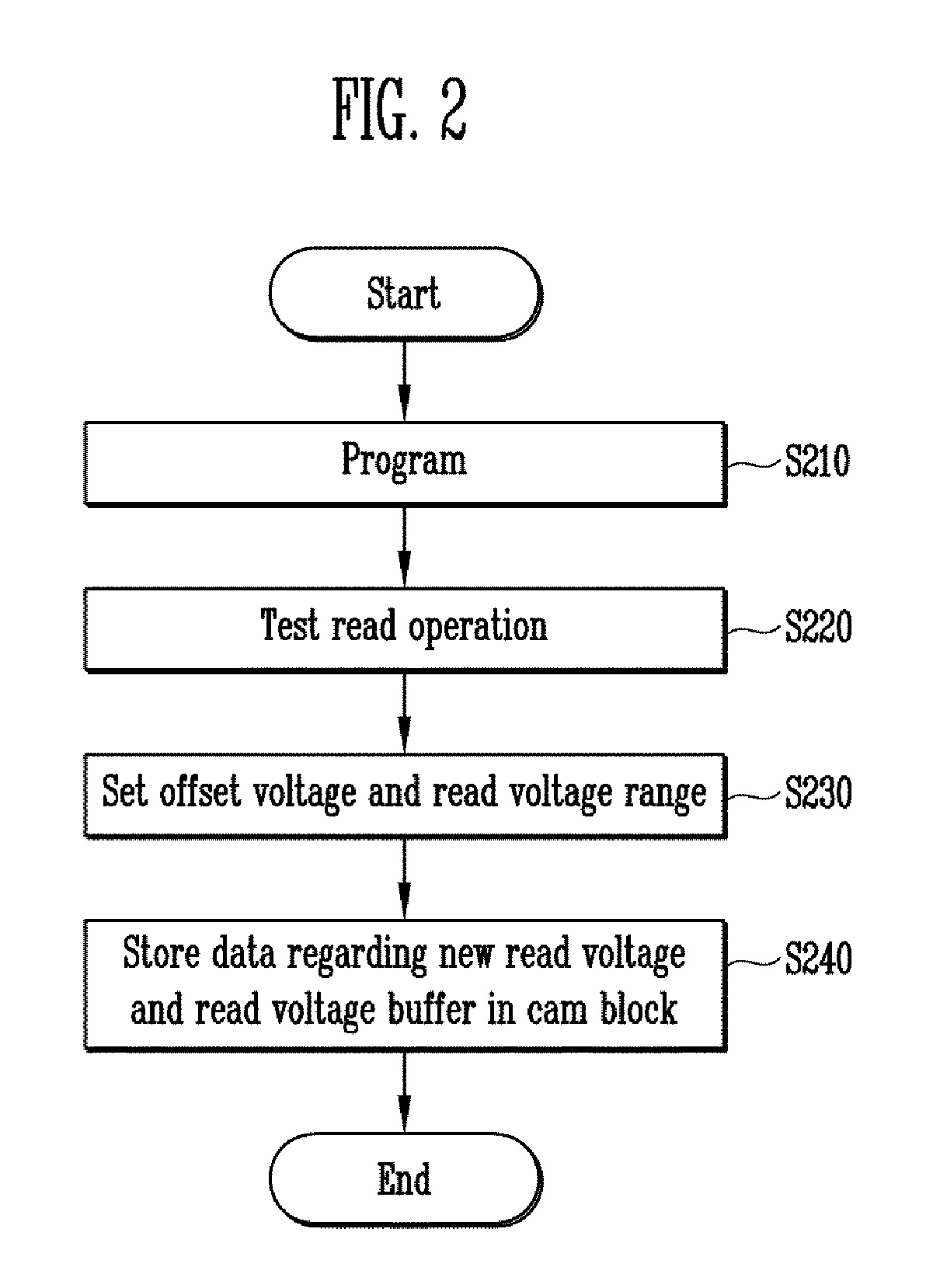

Nonvolatile memory device, method of operating nonvolatile memory device and memory system including nonvolatile memory device

Owner:SAMSUNG ELECTRONICS CO LTD

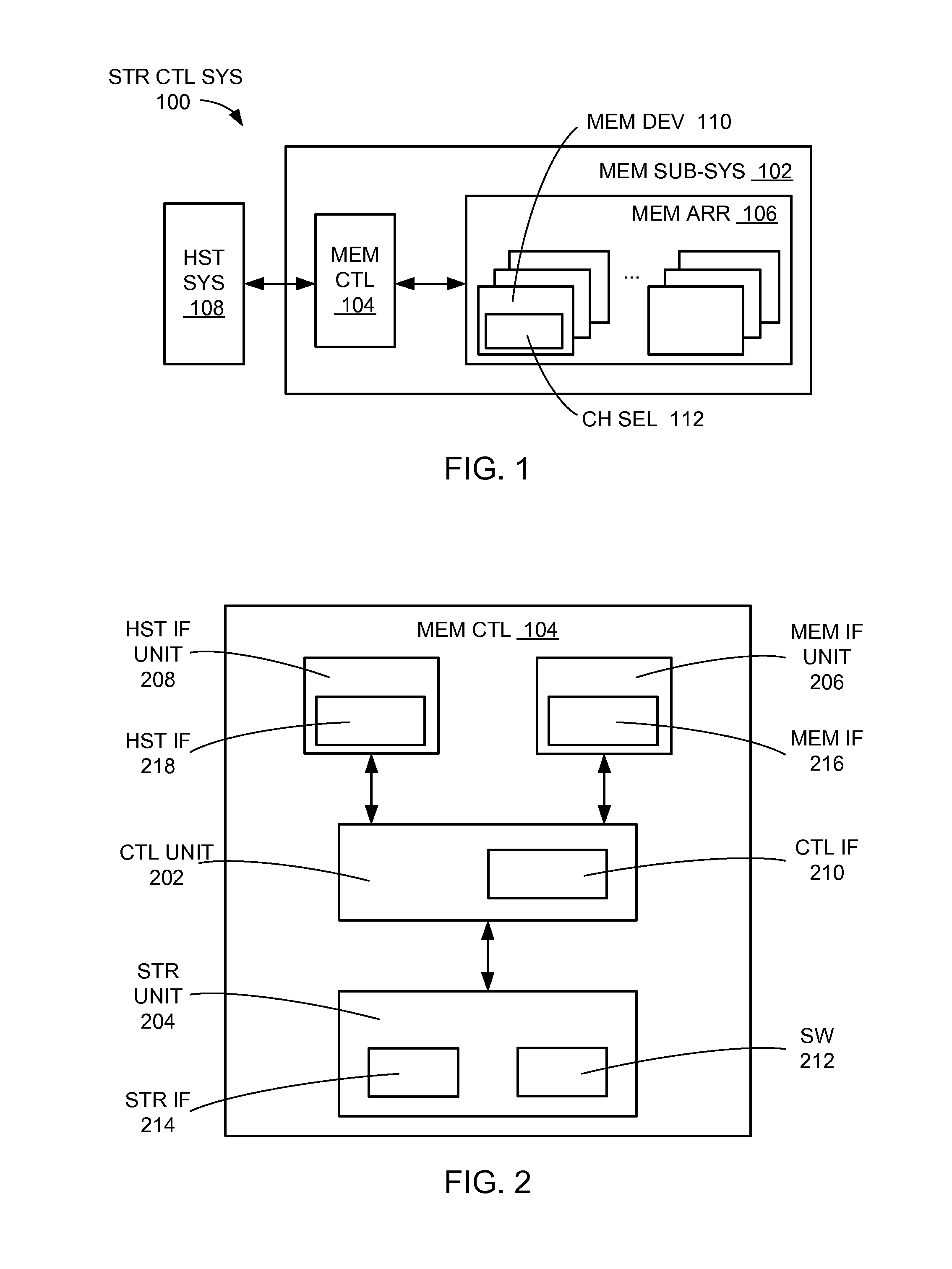

Storage control system with data management mechanism and method of operation thereof

Owner:SANDISK TECH LLC

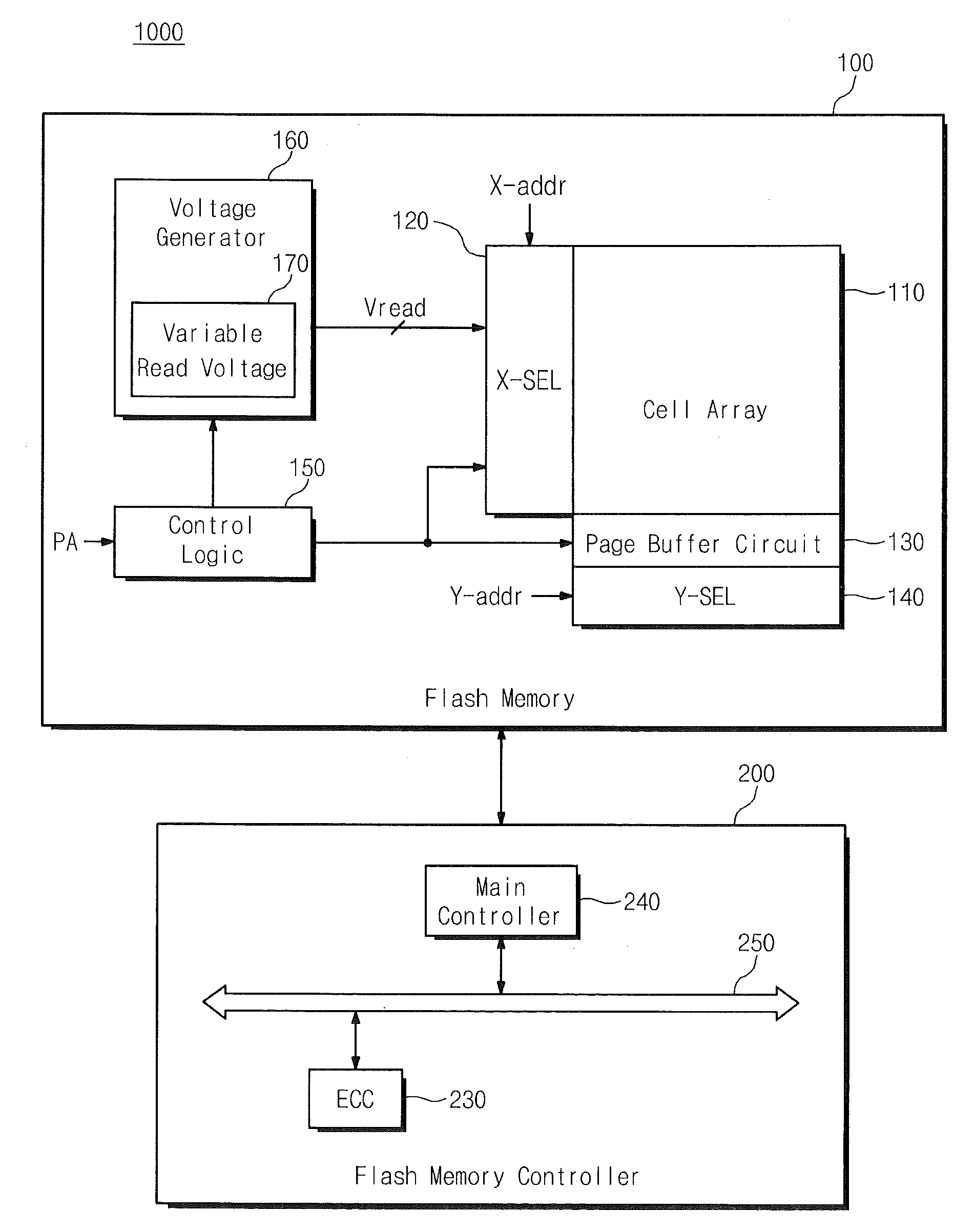

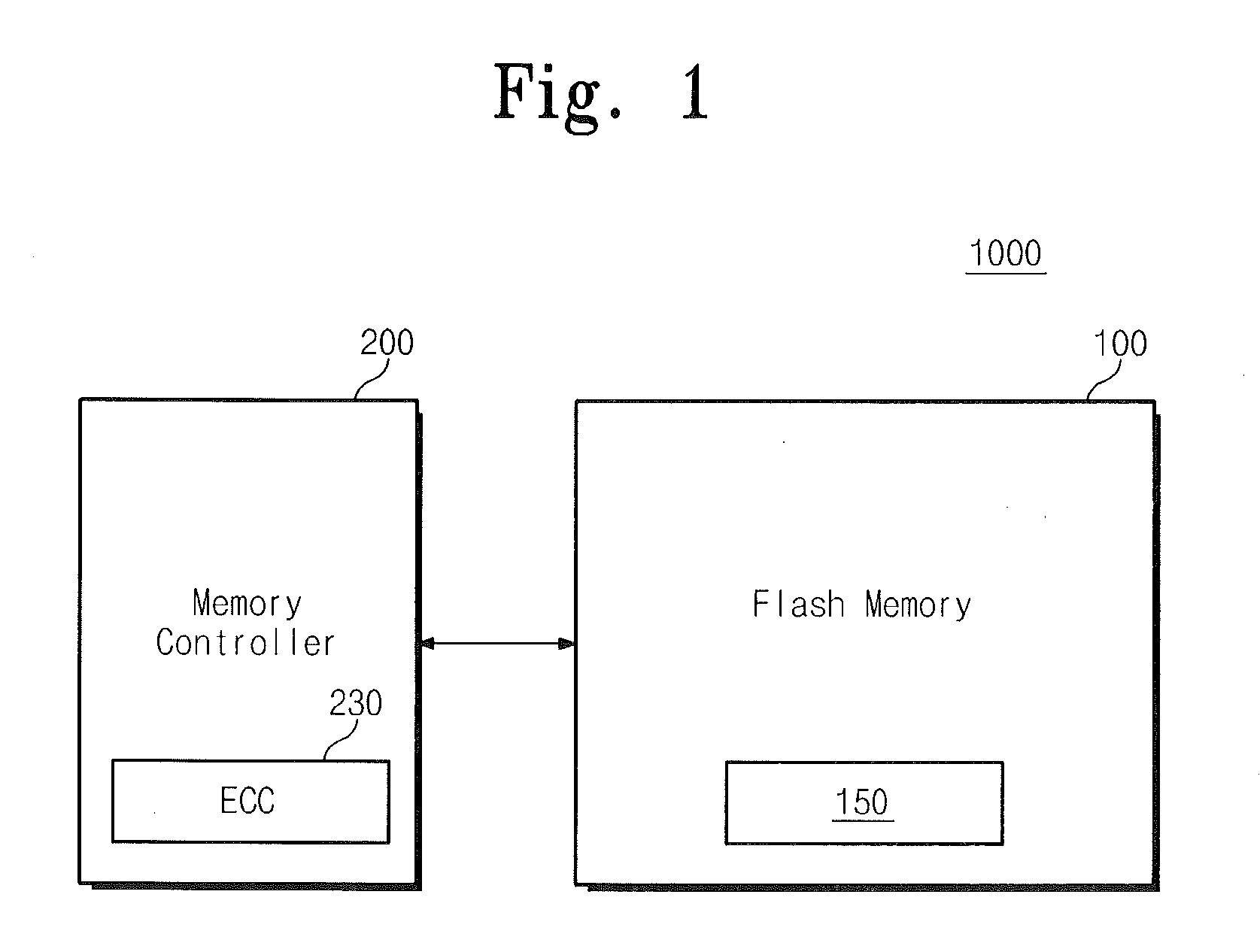

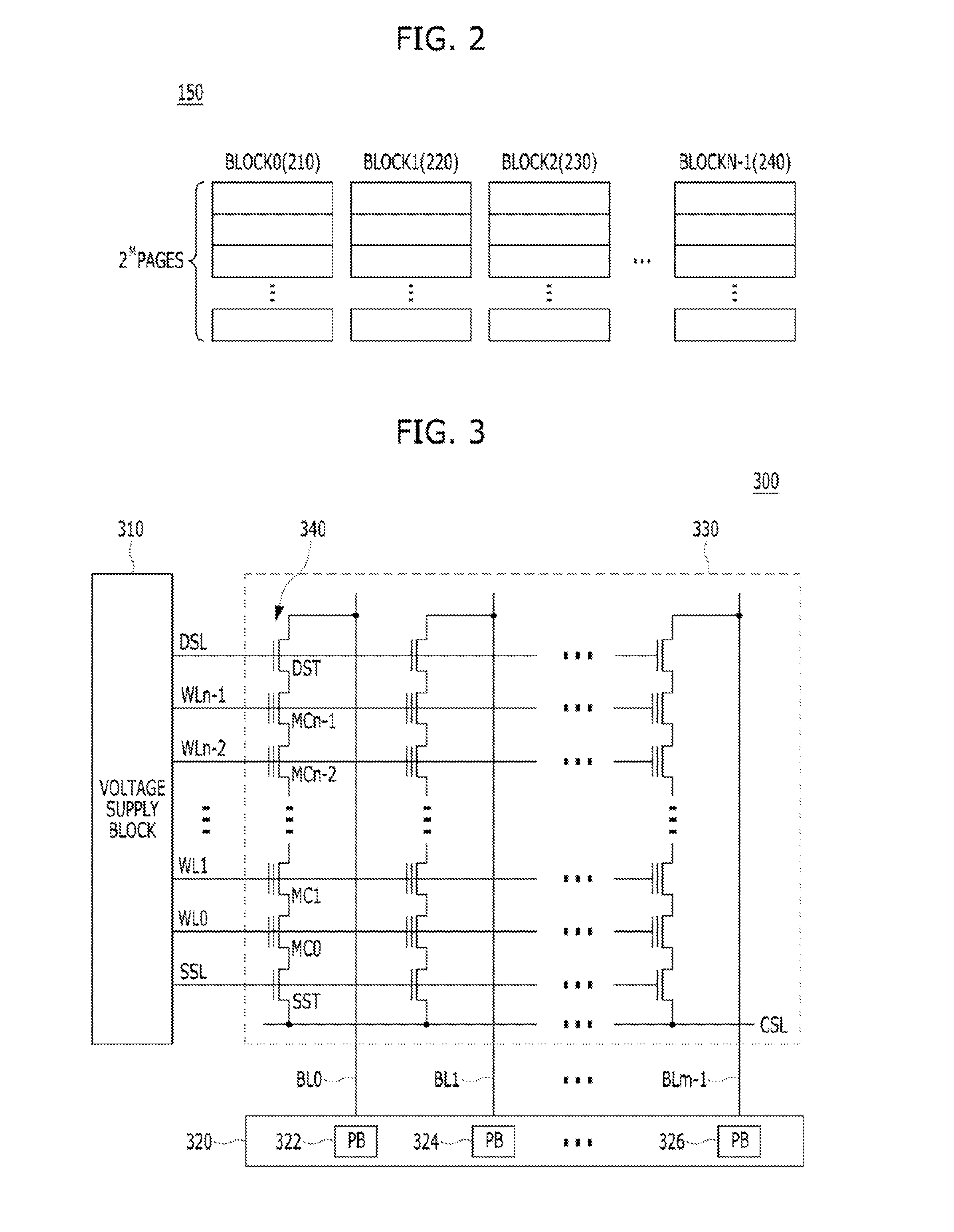

Flash Memory Devices Having Multi-Bit Memory Cells Therein with Improved Read Reliability

ActiveUS20110197015A1Increase in chip sizeEnhanced informationCode conversionRead-only memoriesData valueIntegrated circuit

Owner:SAMSUNG ELECTRONICS CO LTD

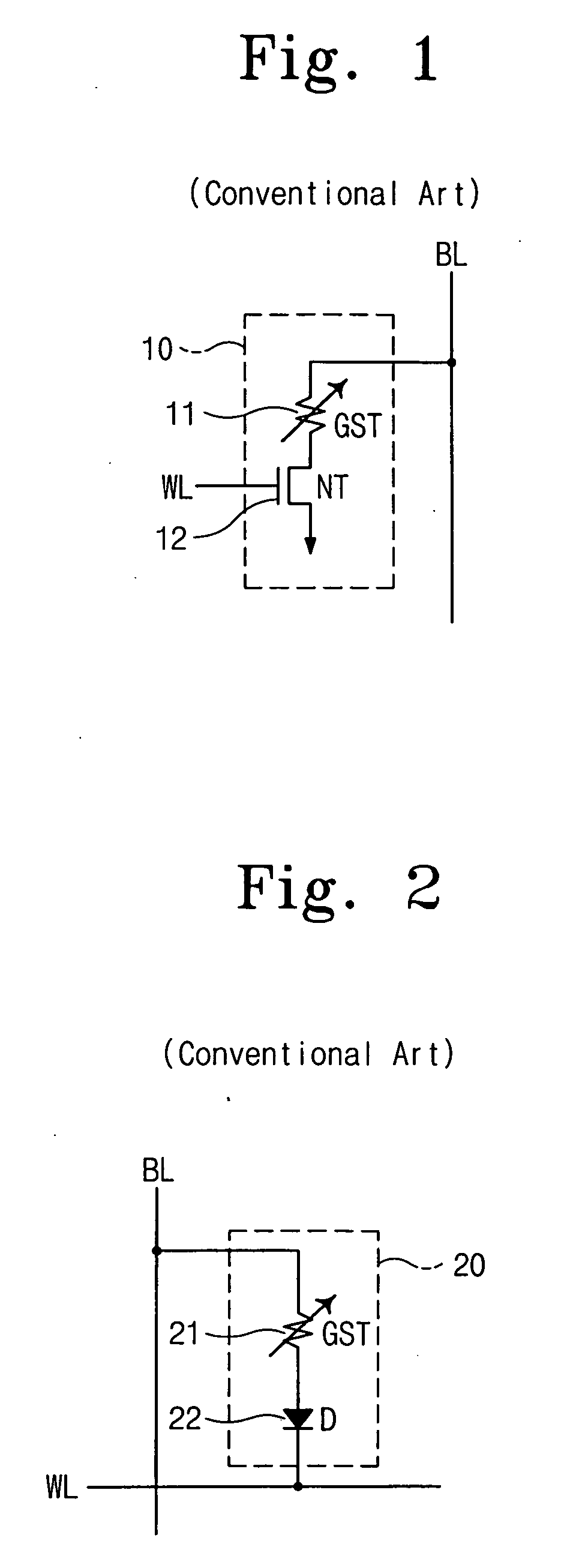

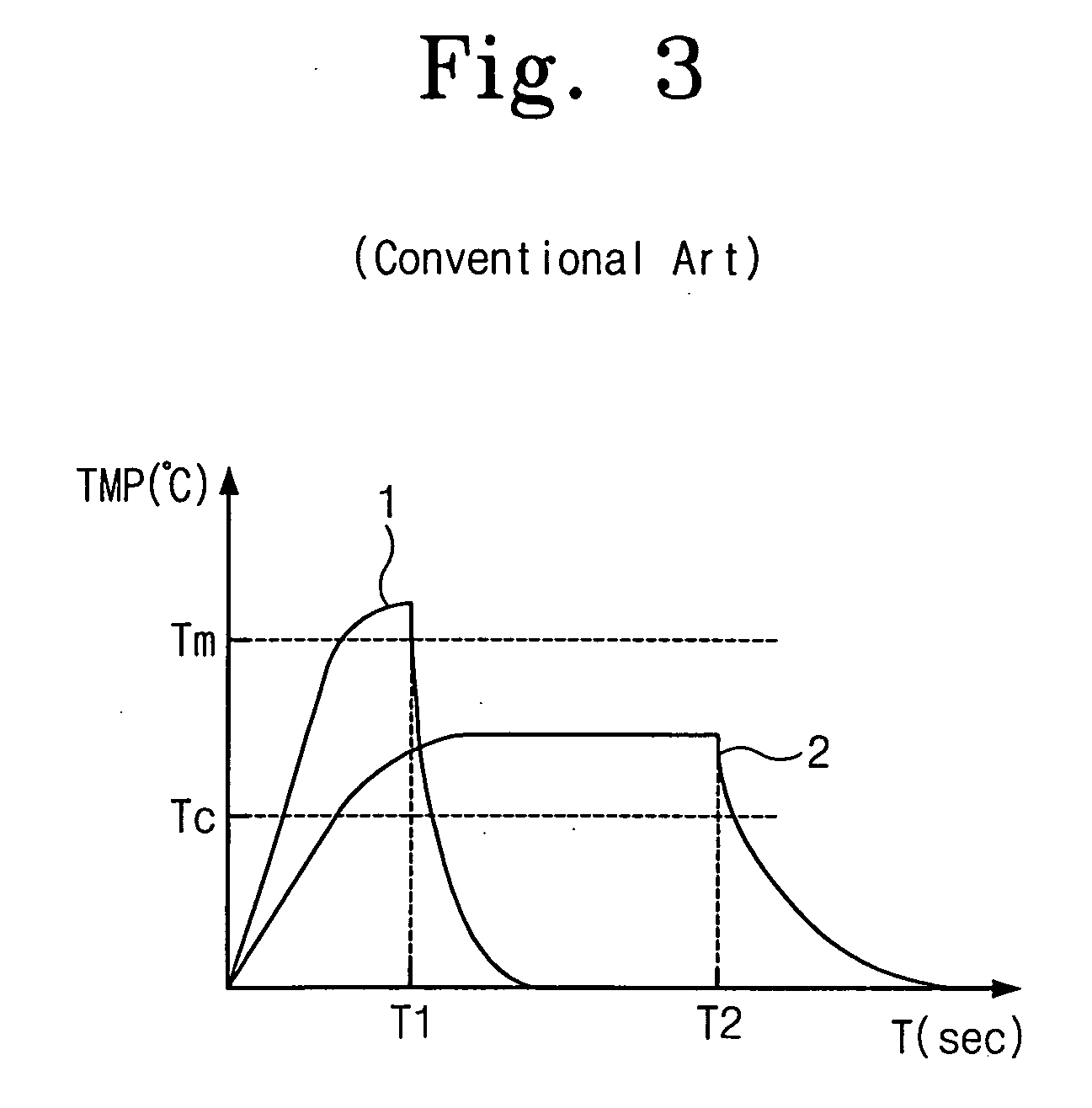

Phase change memory device and method of programming the same

Owner:SAMSUNG ELECTRONICS CO LTD

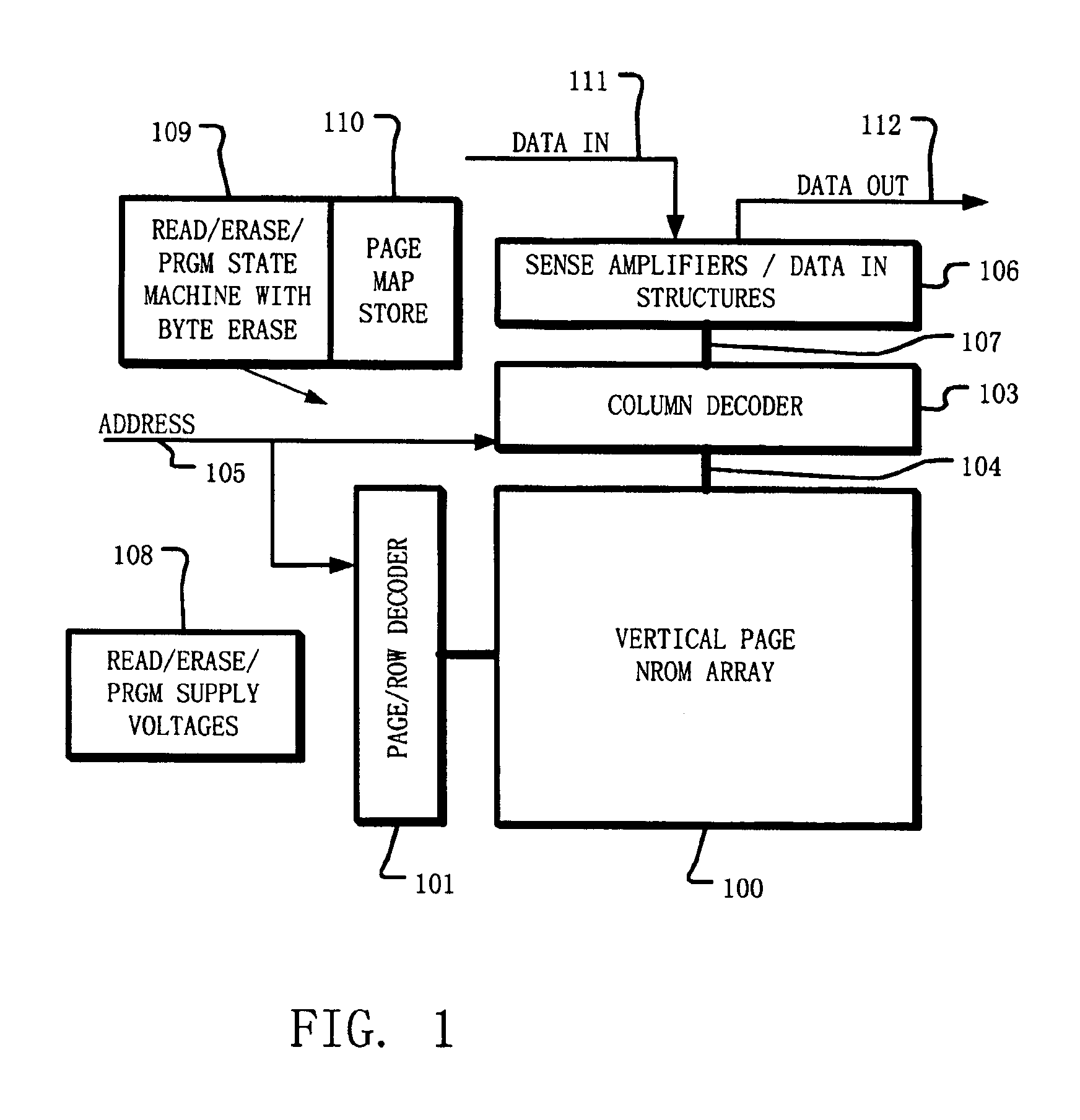

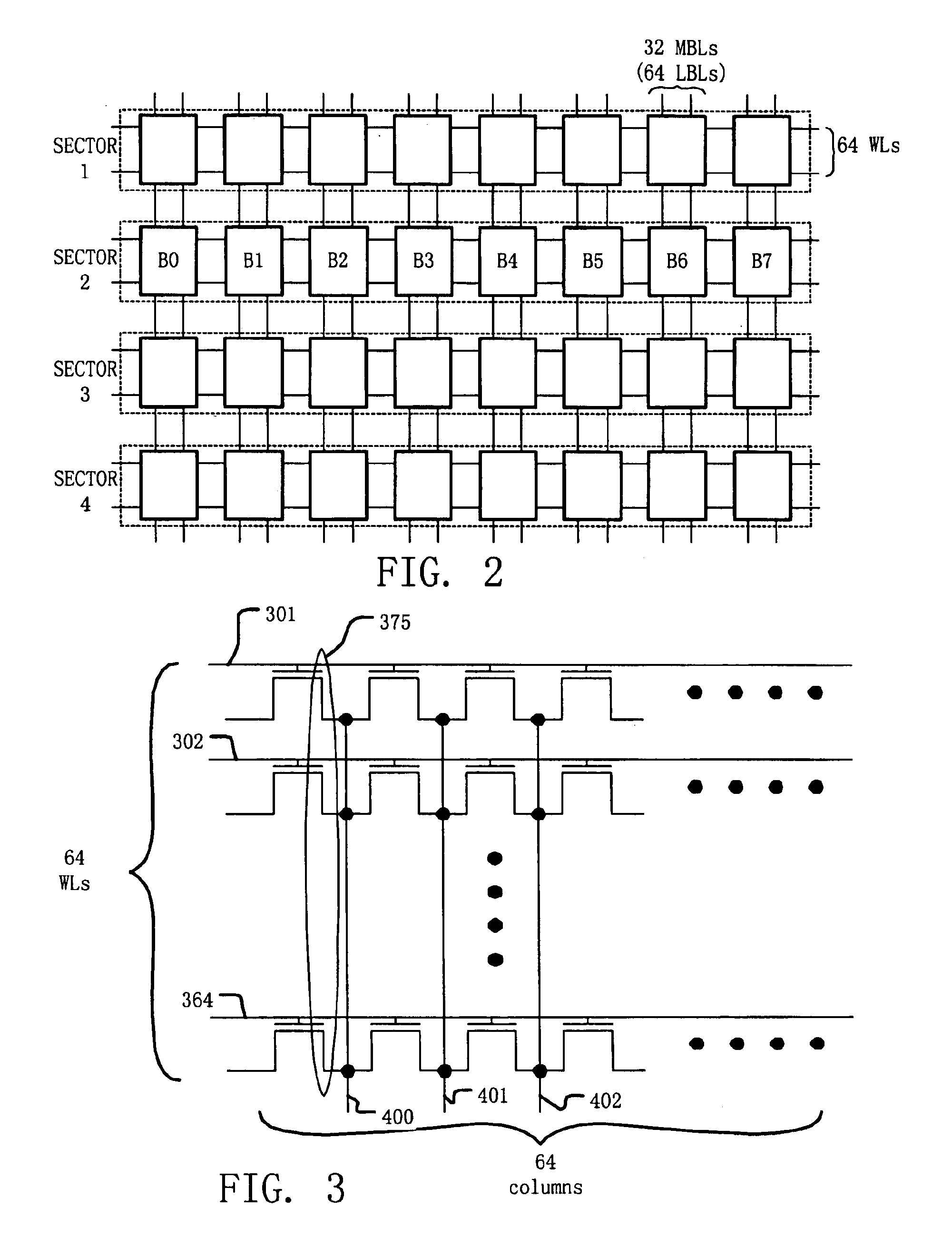

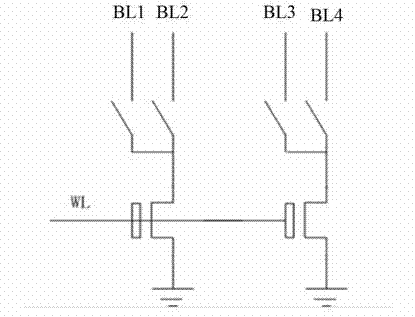

Flash memory device with byte erase

Owner:MACRONIX INT CO LTD

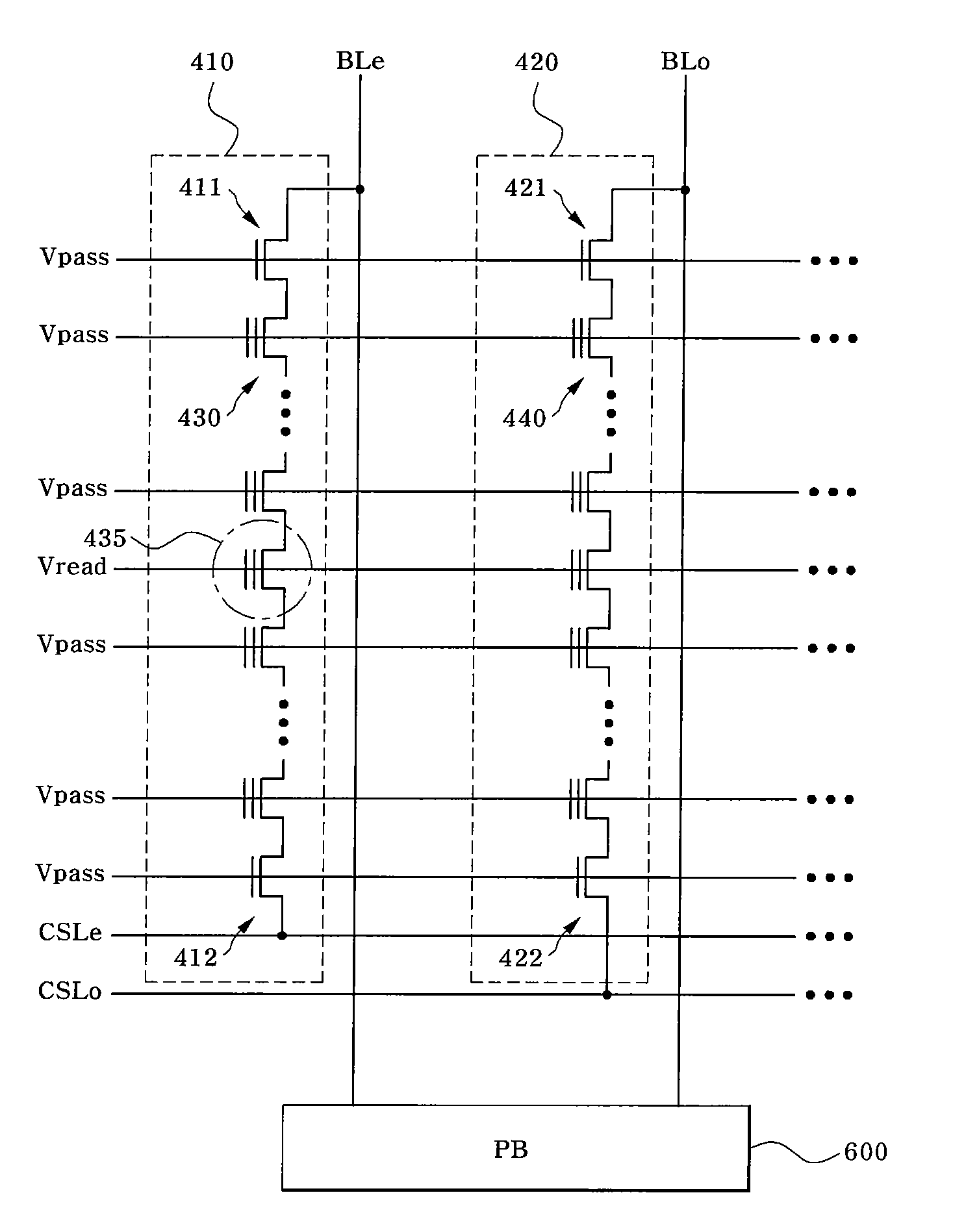

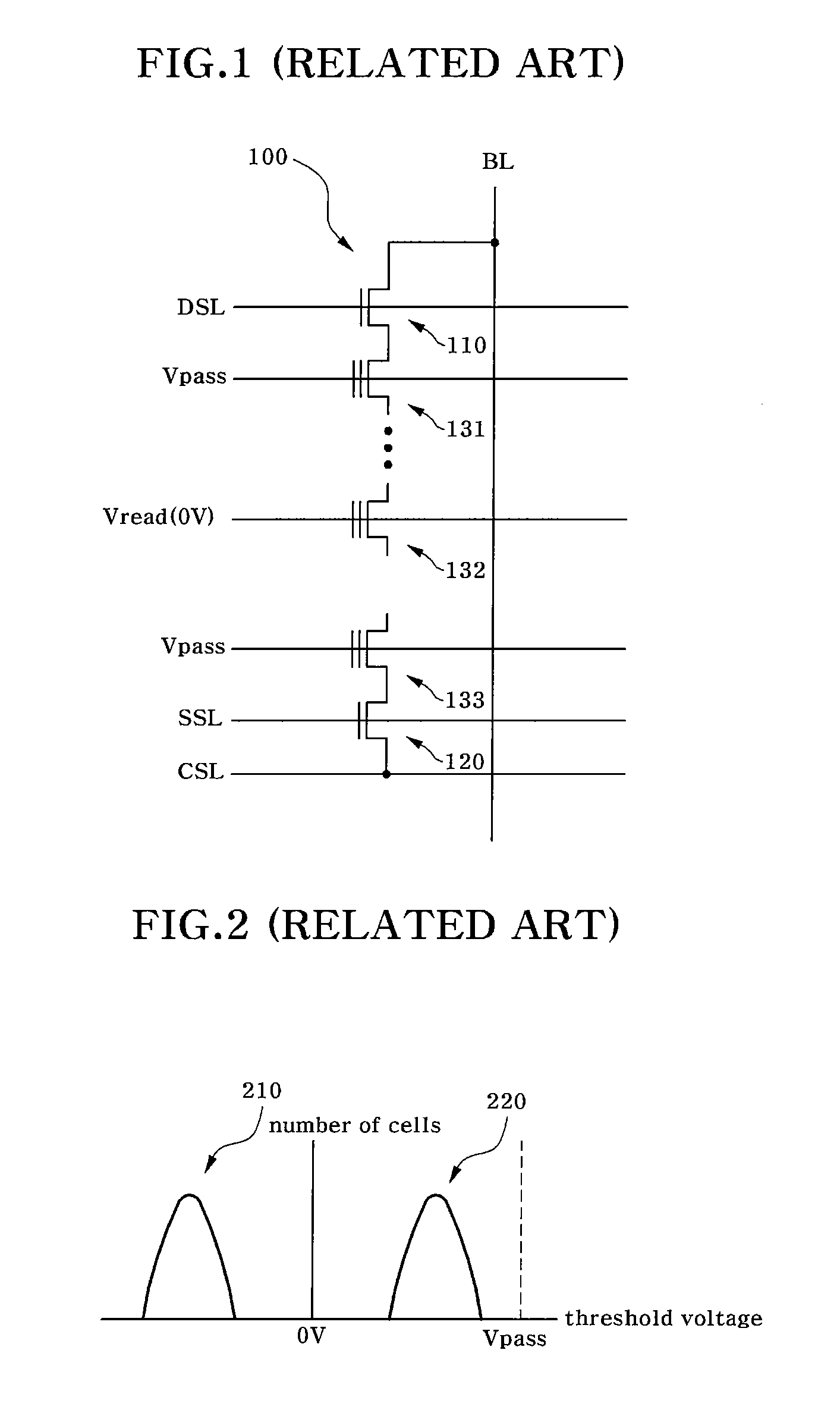

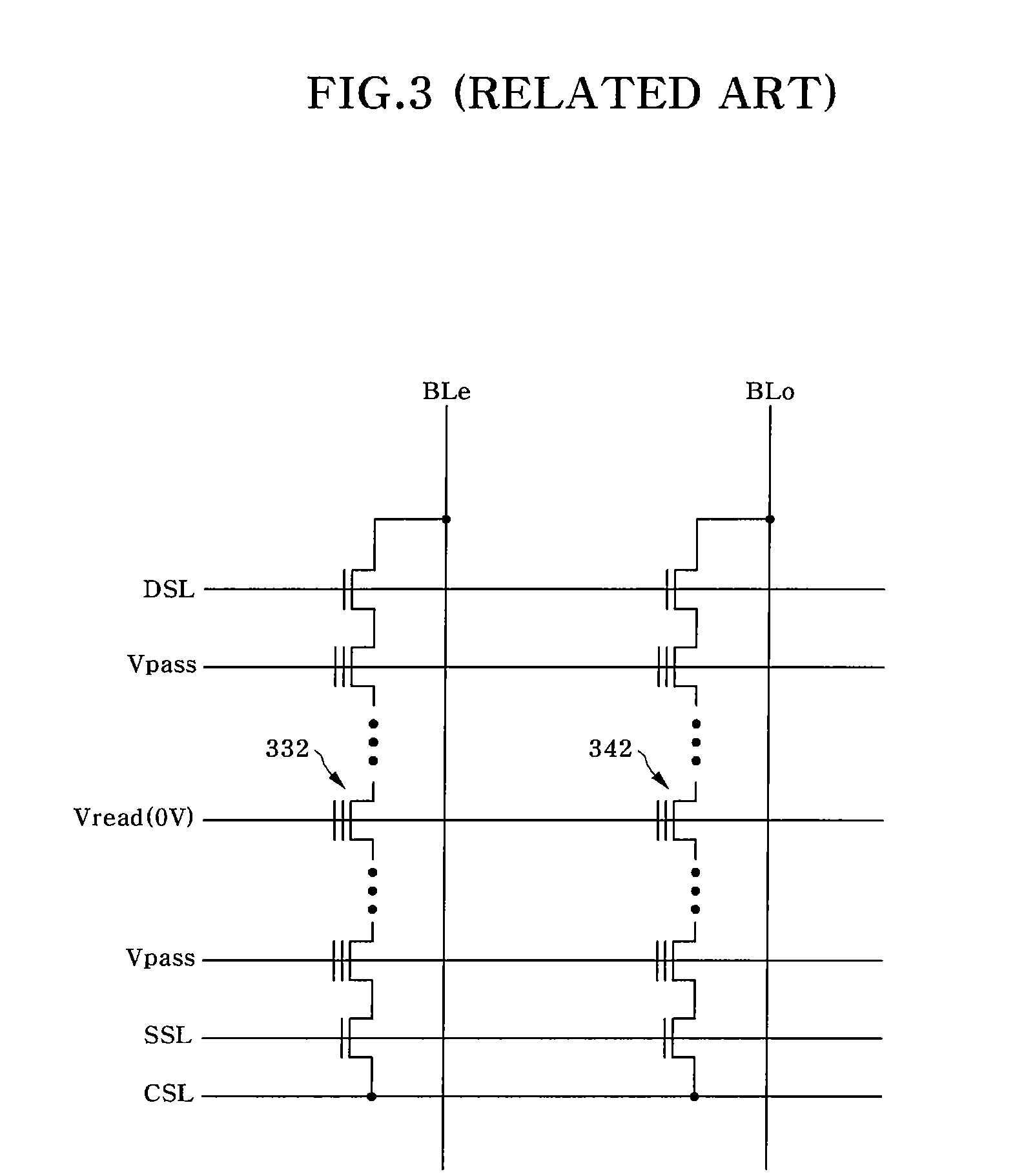

Method for reading NAND flash memory device using self-boosting

Owner:SK HYNIX INC

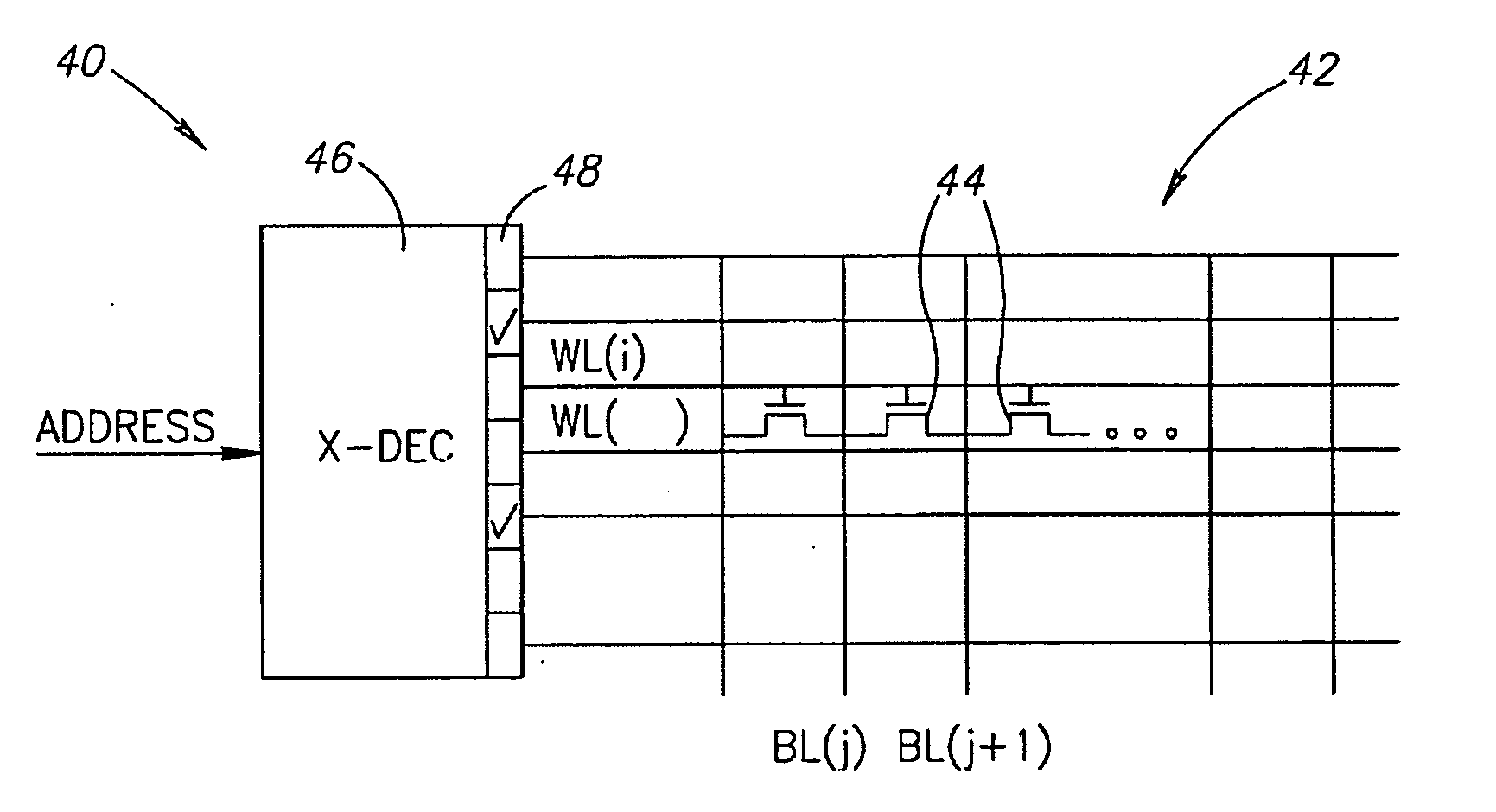

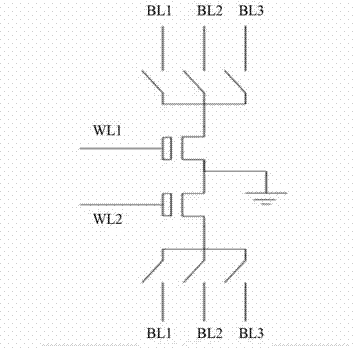

Apparatus for dividing bank in flash memory

InactiveUS6963502B2Shorten the lengthImprove the sense of speedRead-only memoriesDigital storageComputer sciencePage buffers

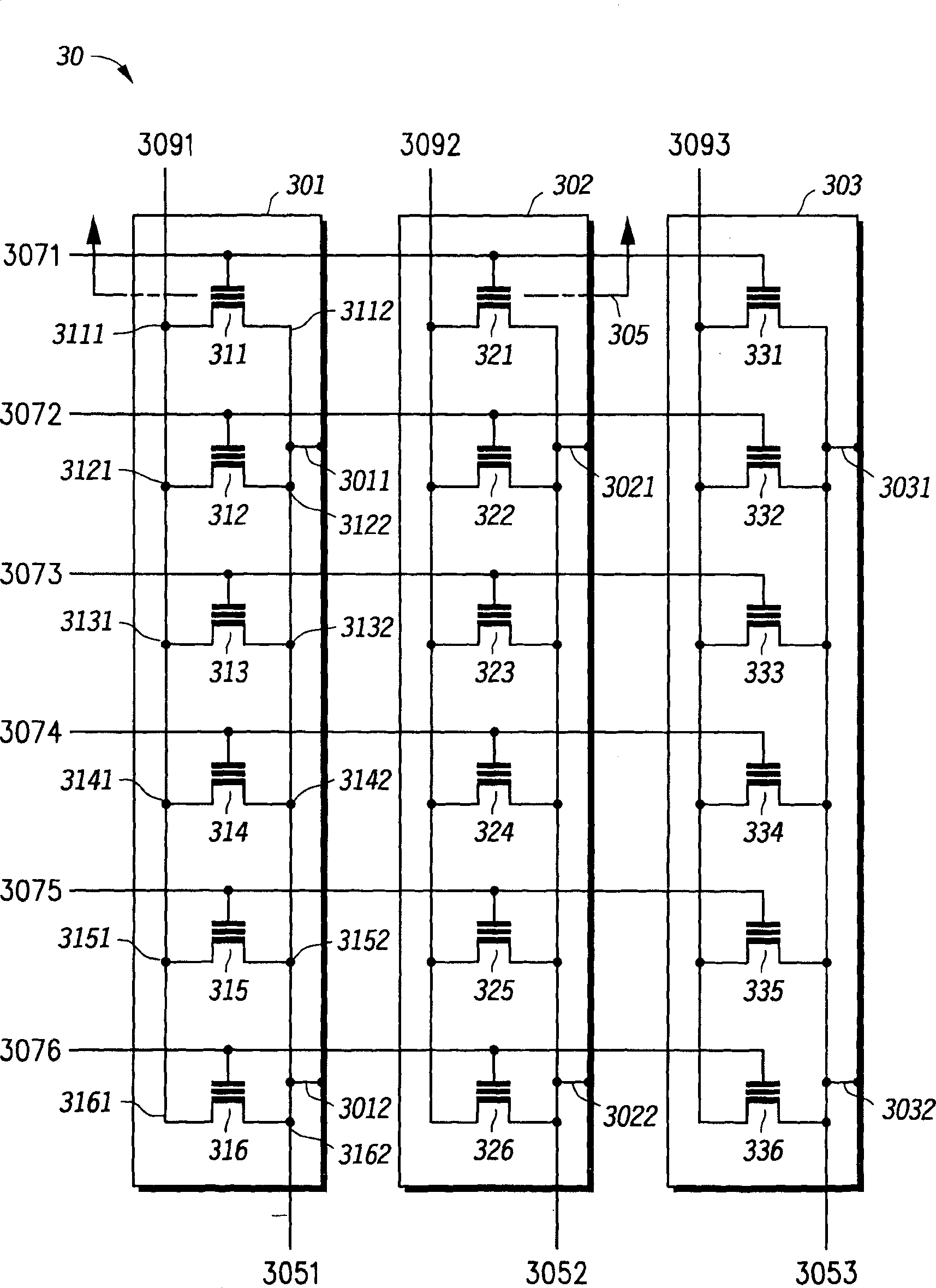

The present invention relates to an apparatus for dividing a bank in a flash memory. A block of the flash memory is divided into two banks and each page buffer is located between the two banks to share an input / output line. Therefore, it is possible to shorten the length of a bit line, improve a data sensing rate, and allow one bank to perform one operation while the other bank performs a read, write or erase operation.

Owner:SK HYNIX INC

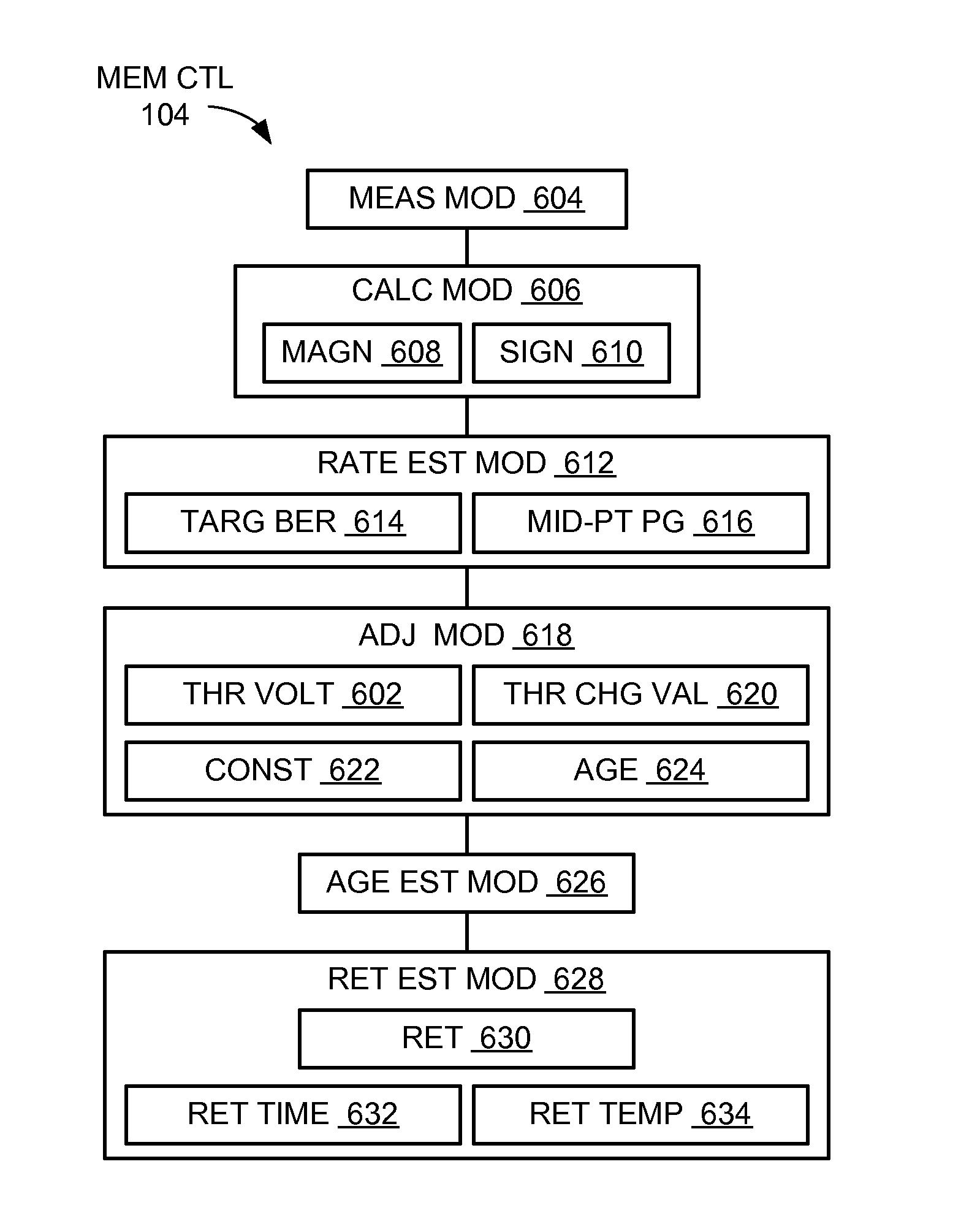

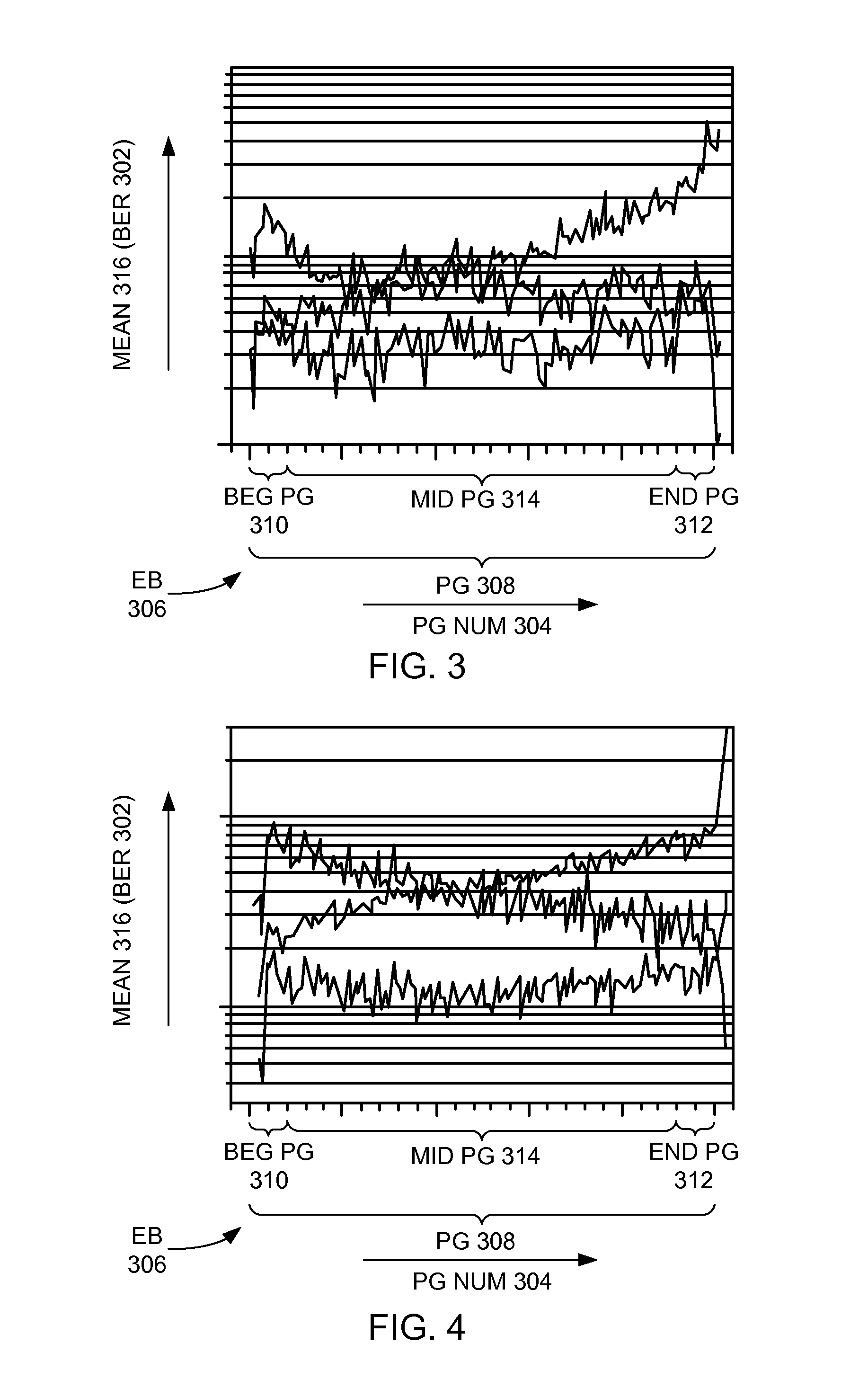

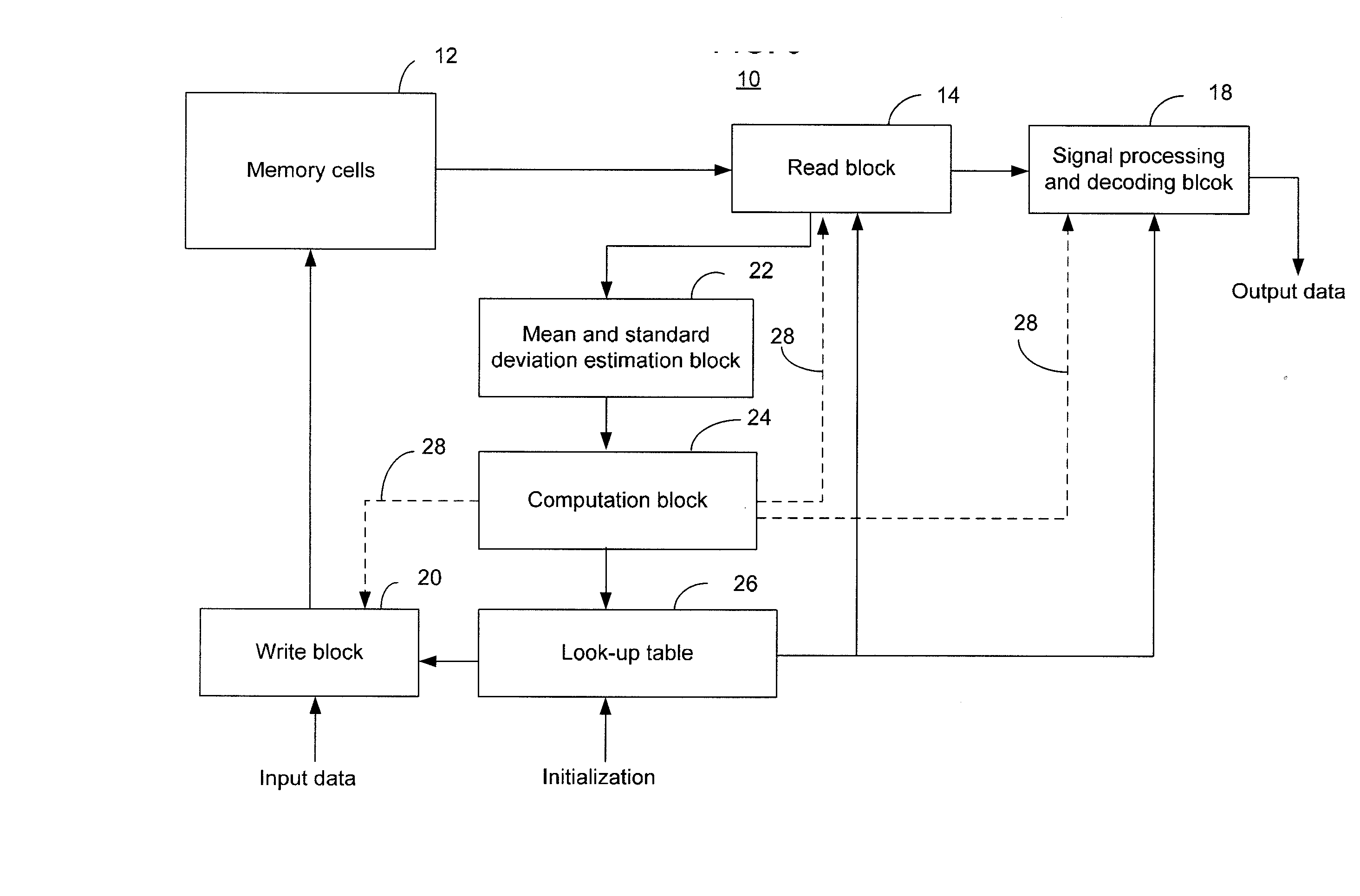

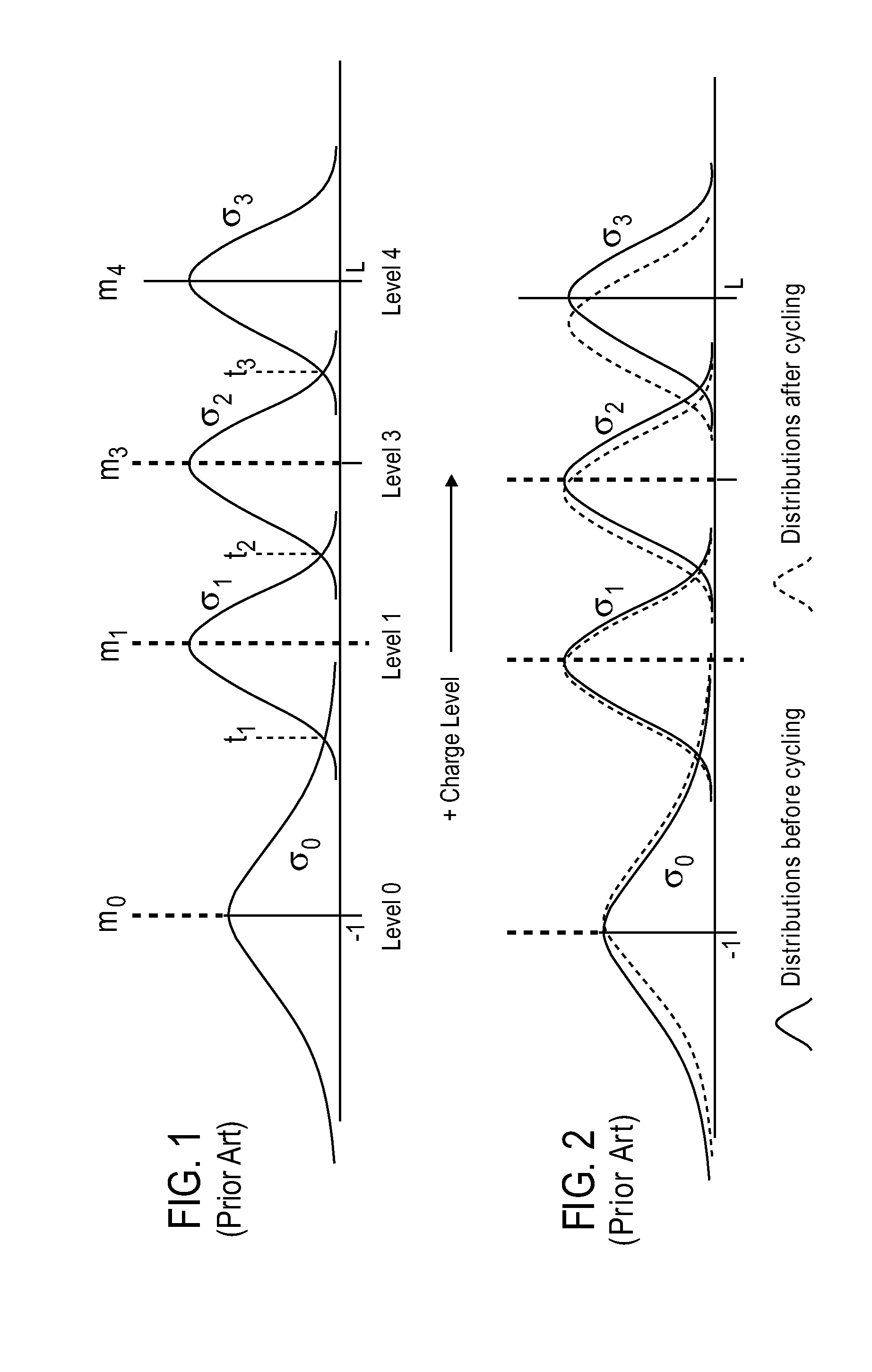

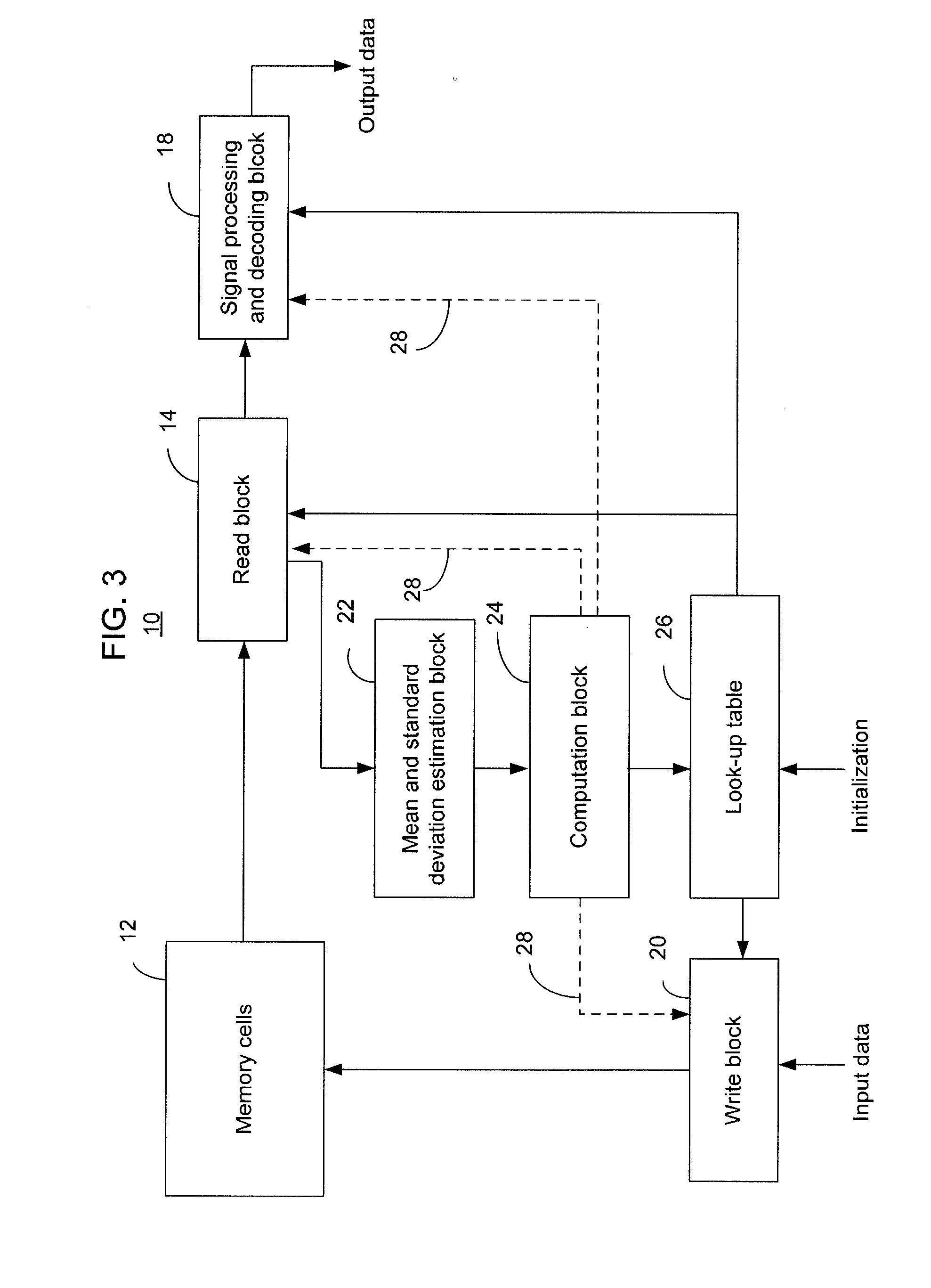

Adaptive read and write systems and methods for memory cells

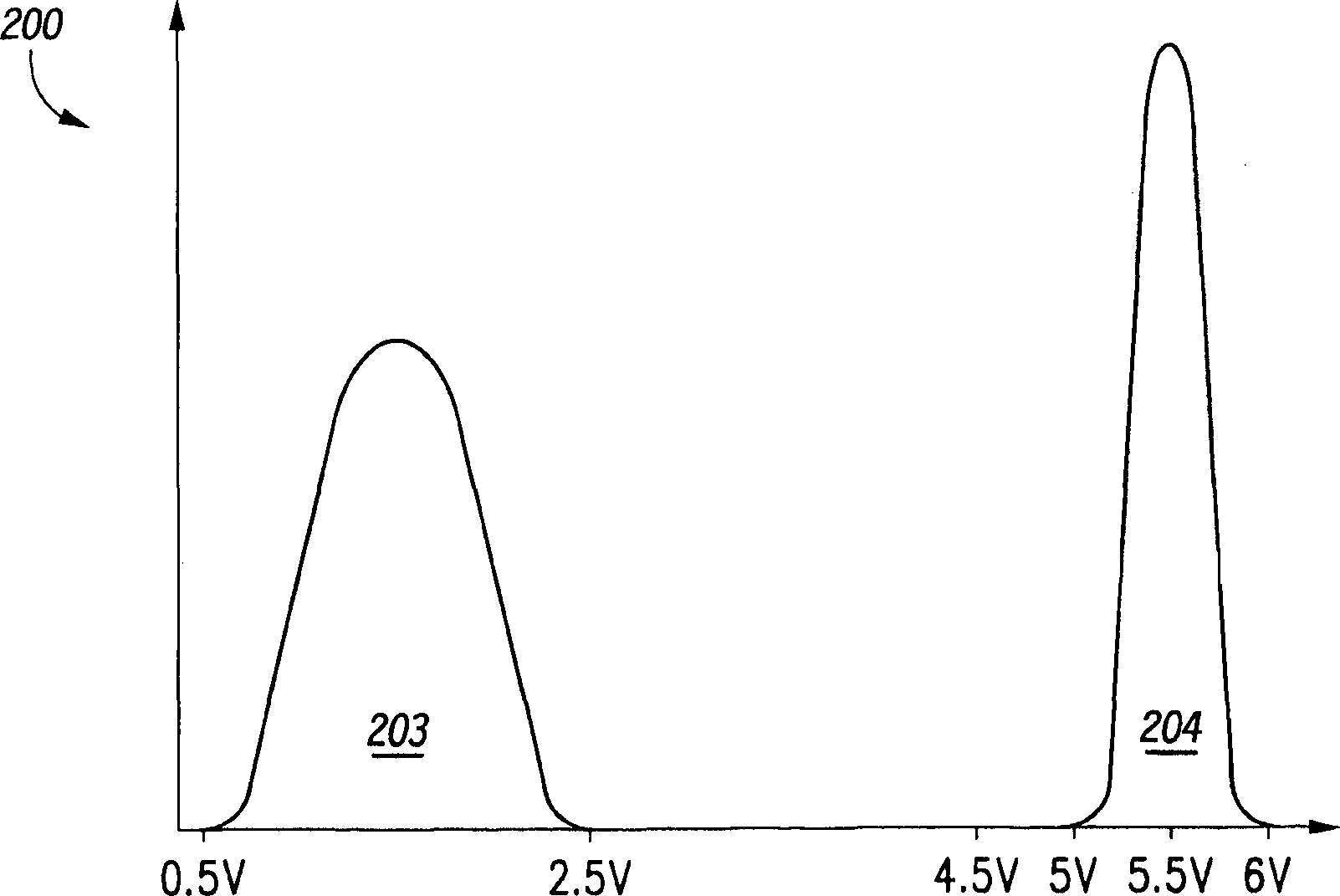

ActiveUS20080106936A1Facilitate writing and readingRead-only memoriesDigital storageSelf adaptiveThreshold voltage

Adaptive memory read and write systems and methods are described herein that adapts to changes to threshold voltage distributions of memory cells as of result of, for example, the detrimental affects of repeated cycling operations of the memory cells. The novel systems may include at least multi-level memory cells, which may be multi-level flash memory cells, and a computation block operatively coupled to the multi-level memory cells. The computation block may be configured to compute optimal or near optimal mean and detection threshold values based, at least in part, on estimated mean and standard deviation values of level distributions of the multi-level memory cells. The optimal or near optimal mean and detection threshold values computed by the computation block may be subsequently used to facilitate writing and reading, respectively, of data to and from the multi-level memory cells.

Owner:MARVELL ASIA PTE LTD

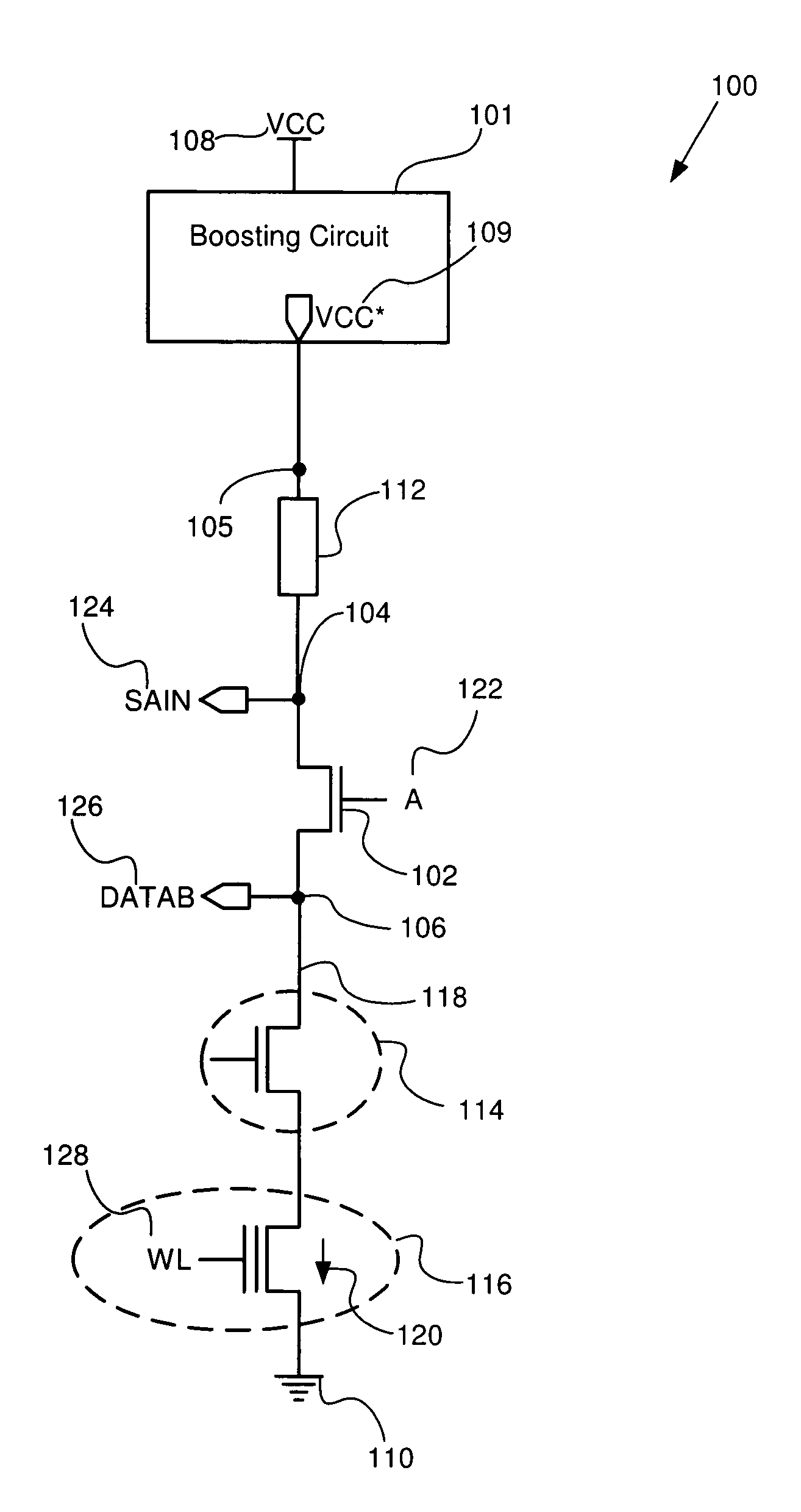

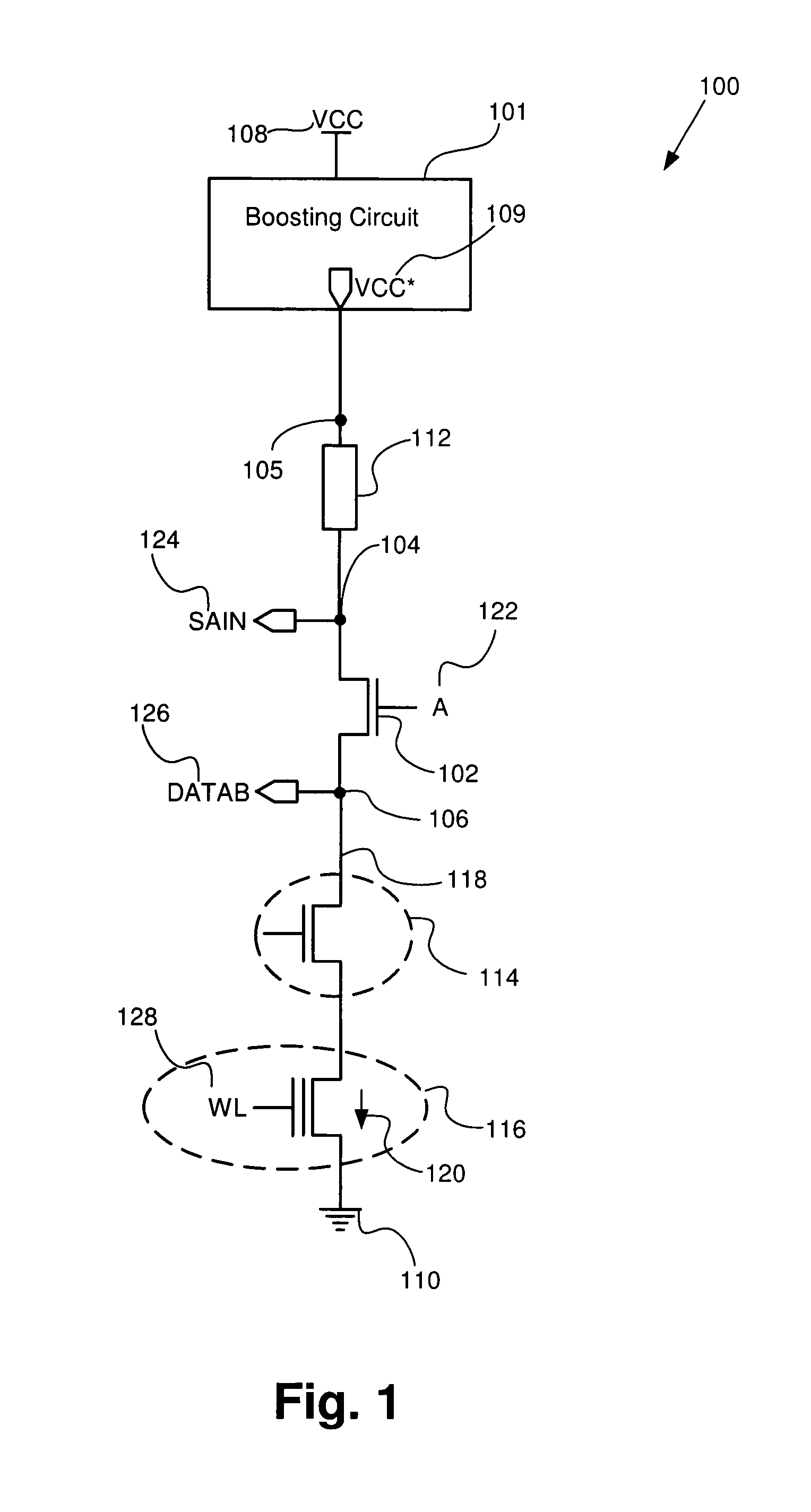

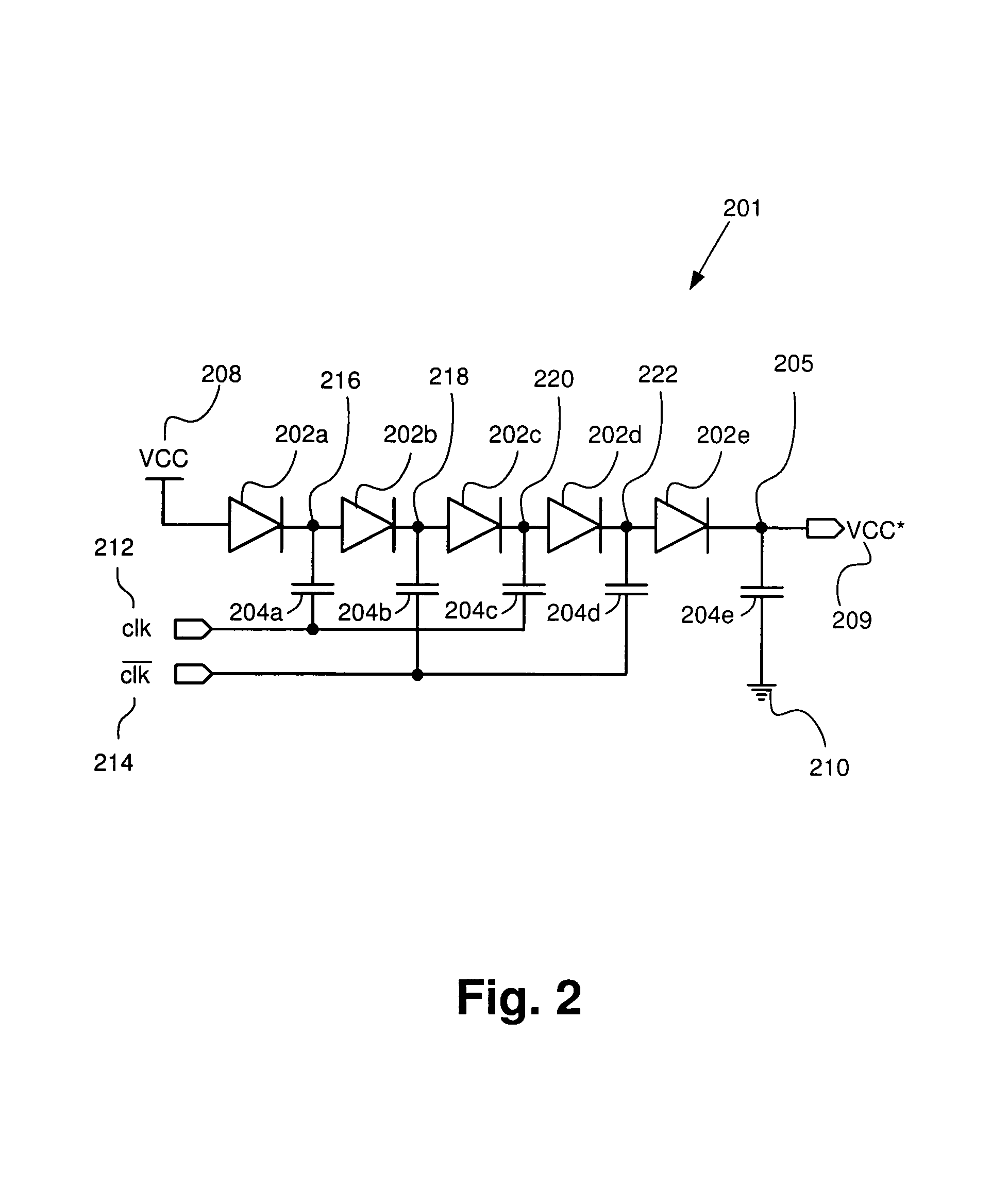

High-voltage switch with low output ripple for non-volatile floating-gate memories

A high-voltage switch has a high-voltage input terminal, receiving a high voltage, and an output terminal. A pass transistor, having a control terminal, is connected between the high-voltage input terminal and the output terminal. The output of a voltage-multiplying circuit of the charge-pump type is connected to the control terminal. The voltage-multiplying circuit is of a symmetrical type, has first and second charge-storage means, receiving a clock signal of a periodic type, and has a first circuit branch and a second circuit branch, which are symmetrical to one another and operate in phase opposition with respect to the clock signal.

Owner:MICRON TECH INC

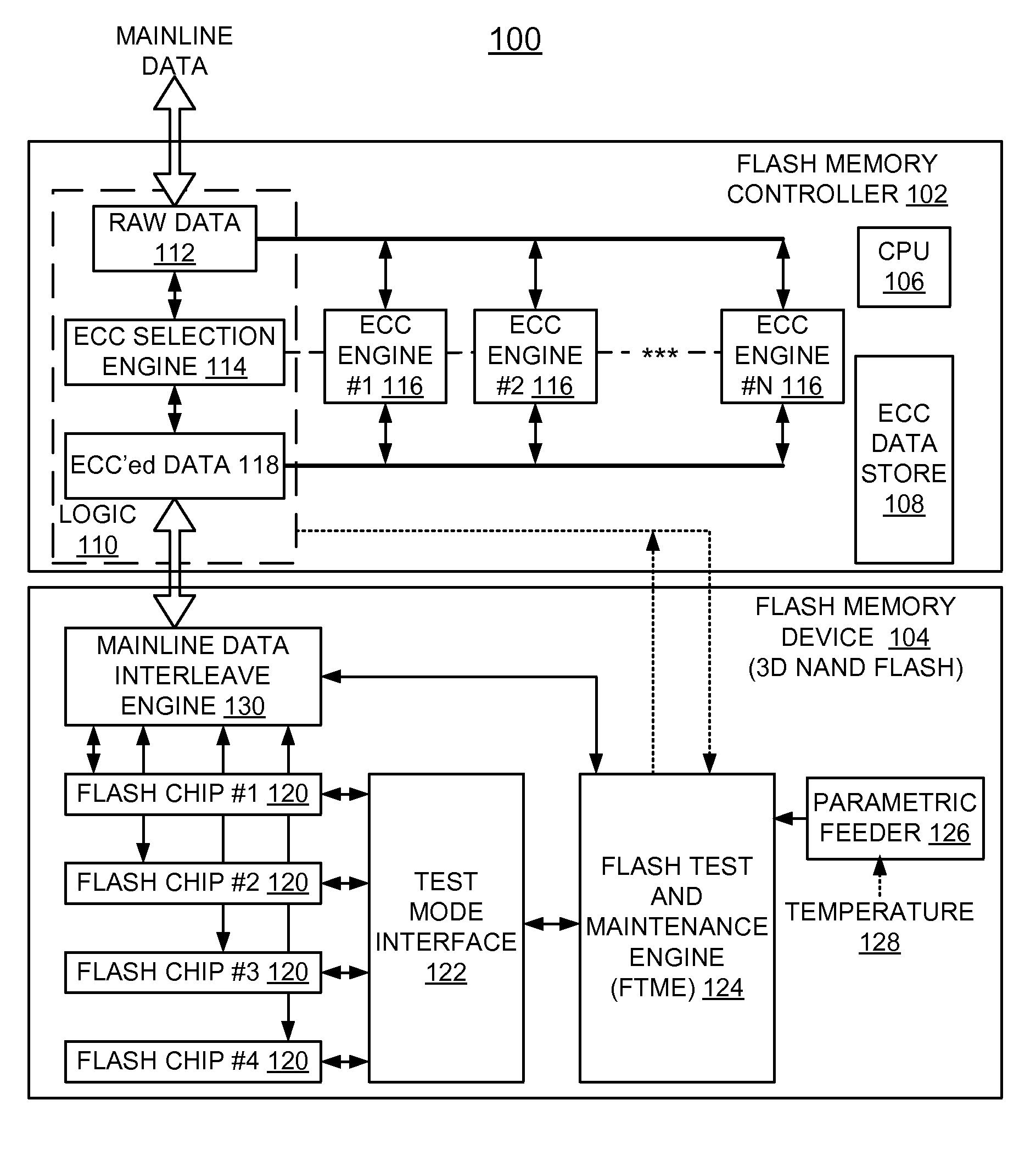

Implementing ecc control for enhanced endurance and data retention of flash memories

InactiveUS20150199232A1Improve enduranceImprove data retentionCode conversionRead-only memoriesMemory controllerData retention

Owner:IBM CORP

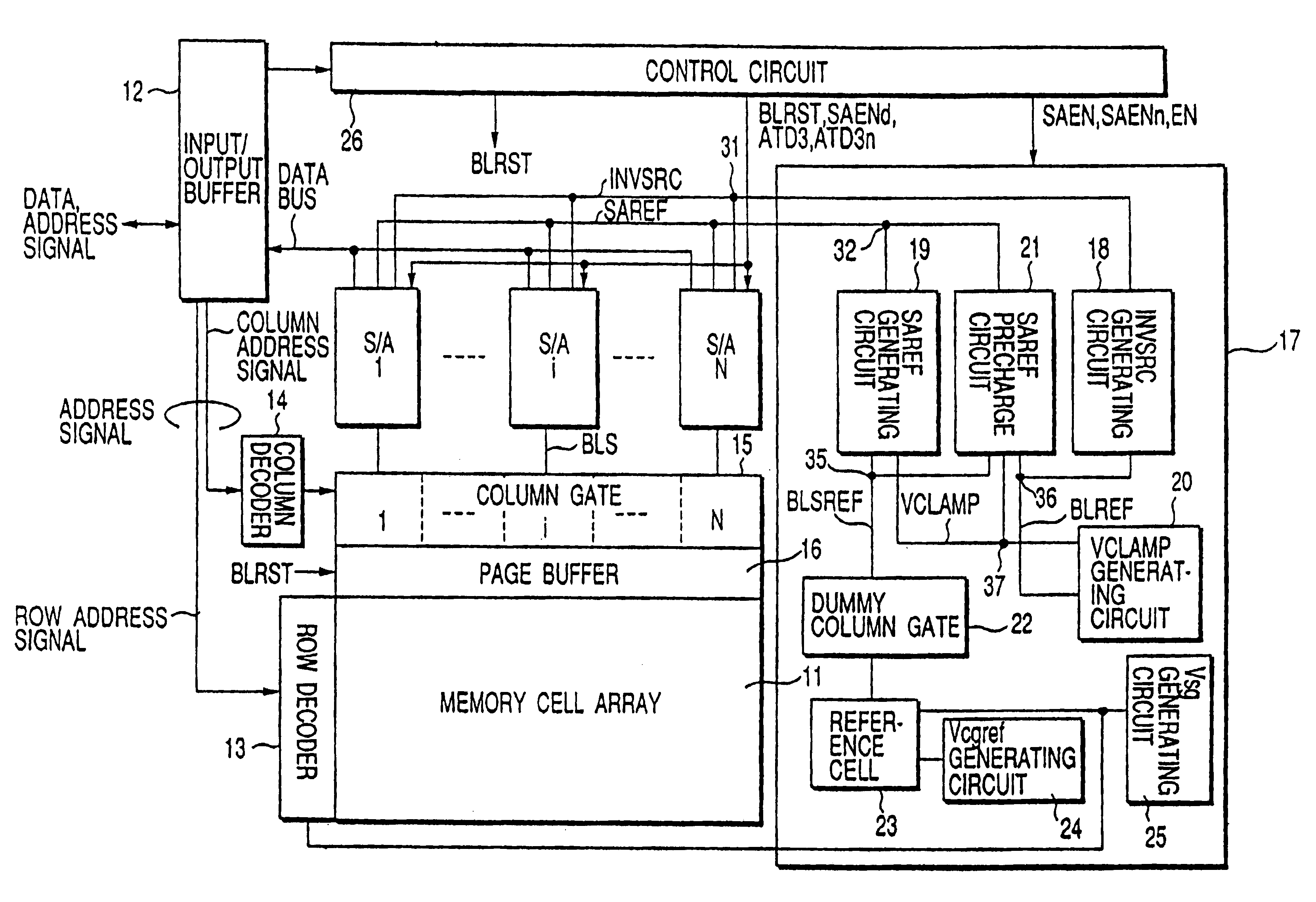

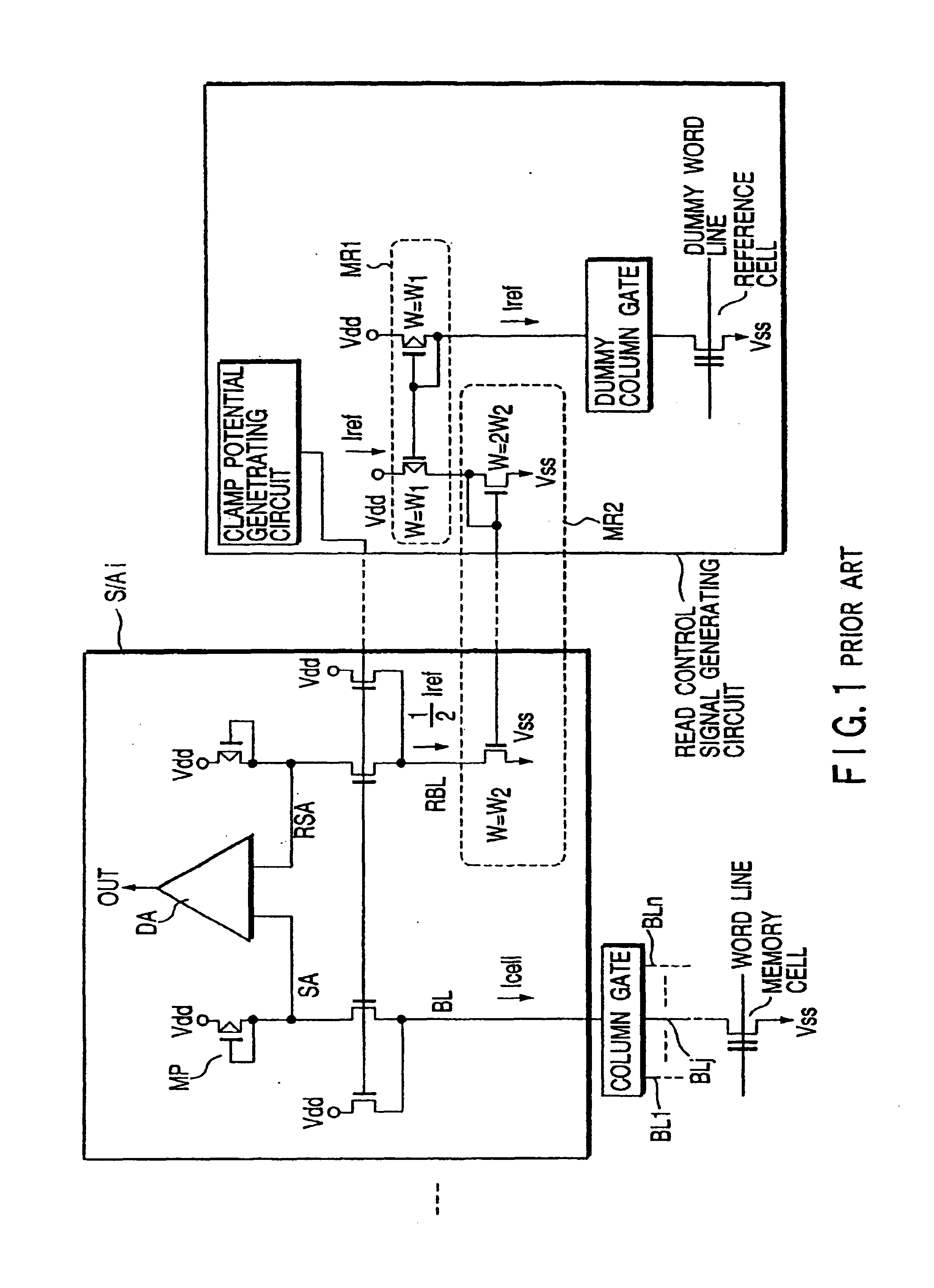

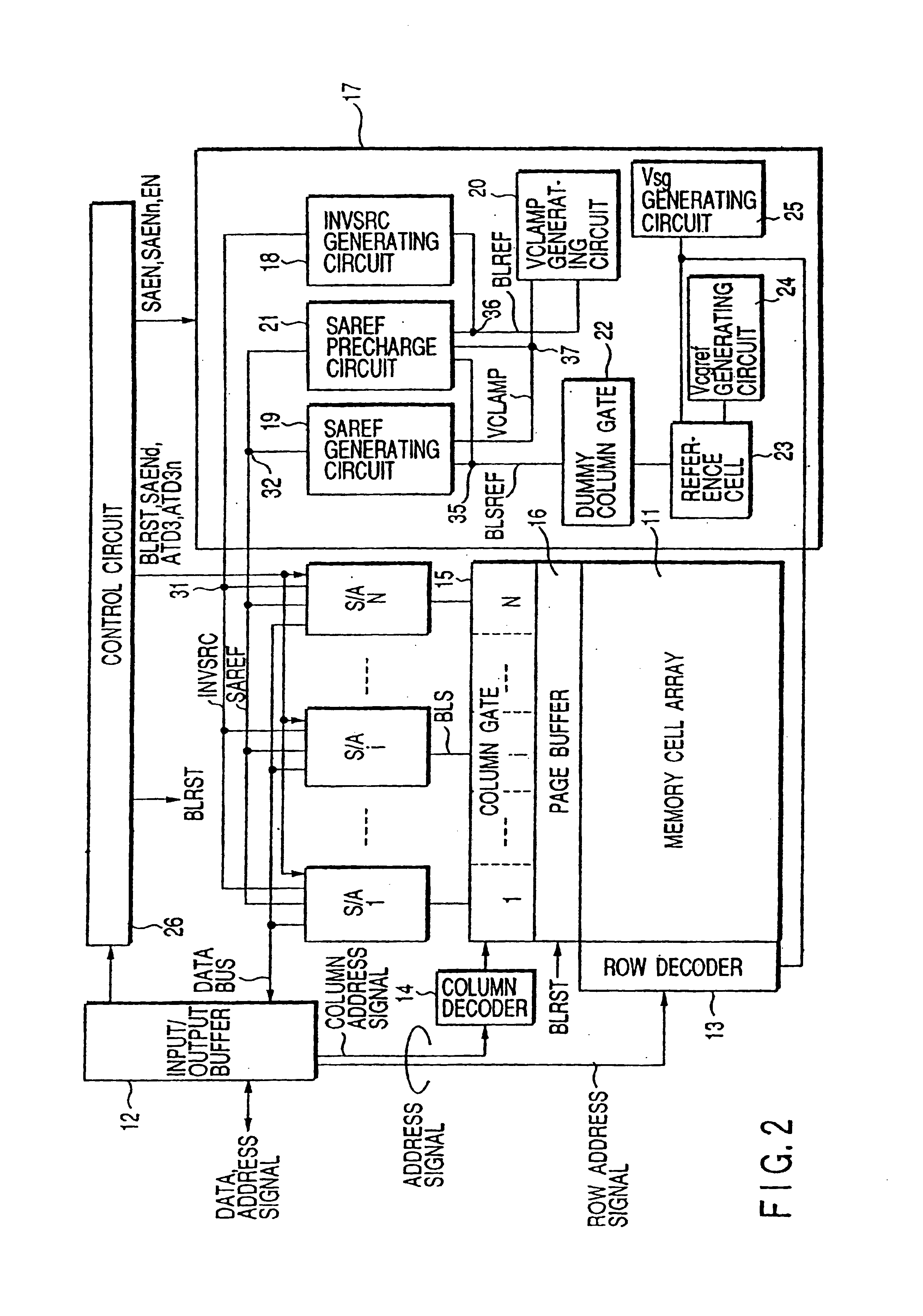

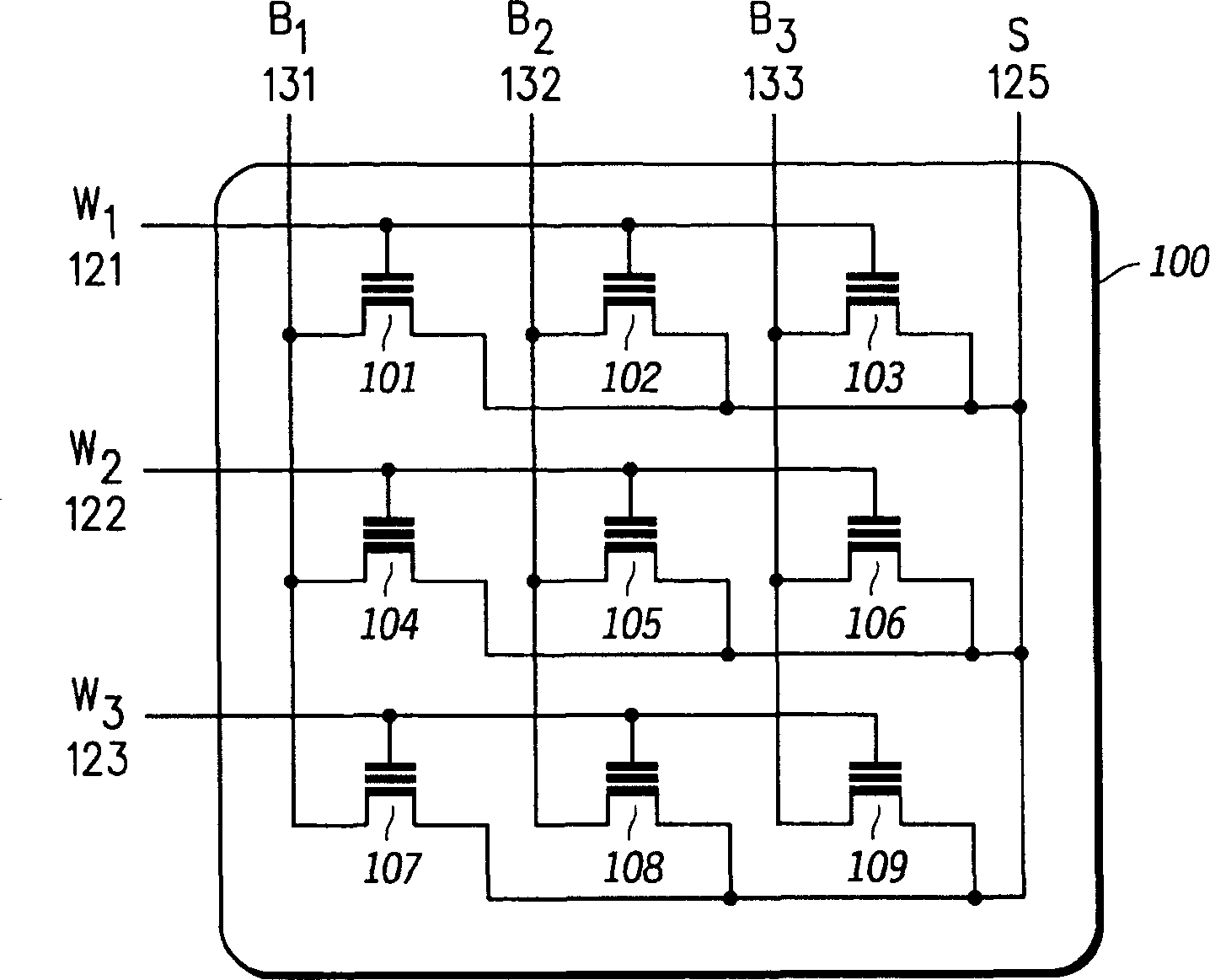

Read circuit of nonvolatile semiconductor memory

InactiveUS6845047B2Total current dropPerforming readRead-only memoriesDigital storageBit lineComputer architecture

Owner:KK TOSHIBA

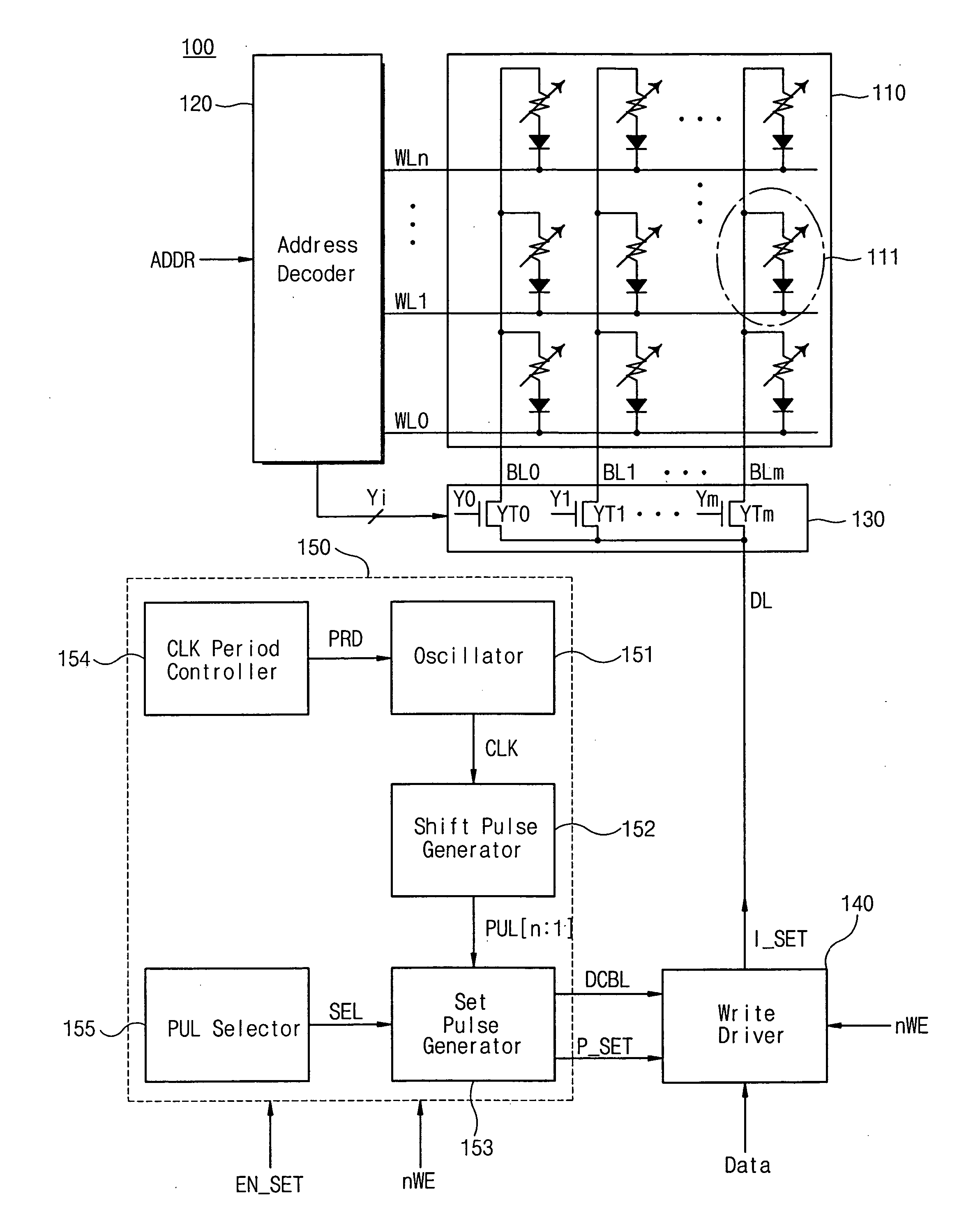

Resistance variable memory device performing program and verification operation

A variable resistance memory device includes: a memory cell array comprising a plurality of memory cells, a pulse shifter shifting a plurality of program pulses to generate a plurality of shifted program pulses, a write and verification driver receiving the plurality of shifted program pulses to provide a program current that varies with the plurality of shifted program pulses to the plurality of memory cells, and control logic providing the plurality of program pulses to the pulse shifter and the write and verification driver during a program / verification operation, such at least two write data bits are programmed to the memory cell array in parallel during the program / verification operation.

Owner:SAMSUNG ELECTRONICS CO LTD

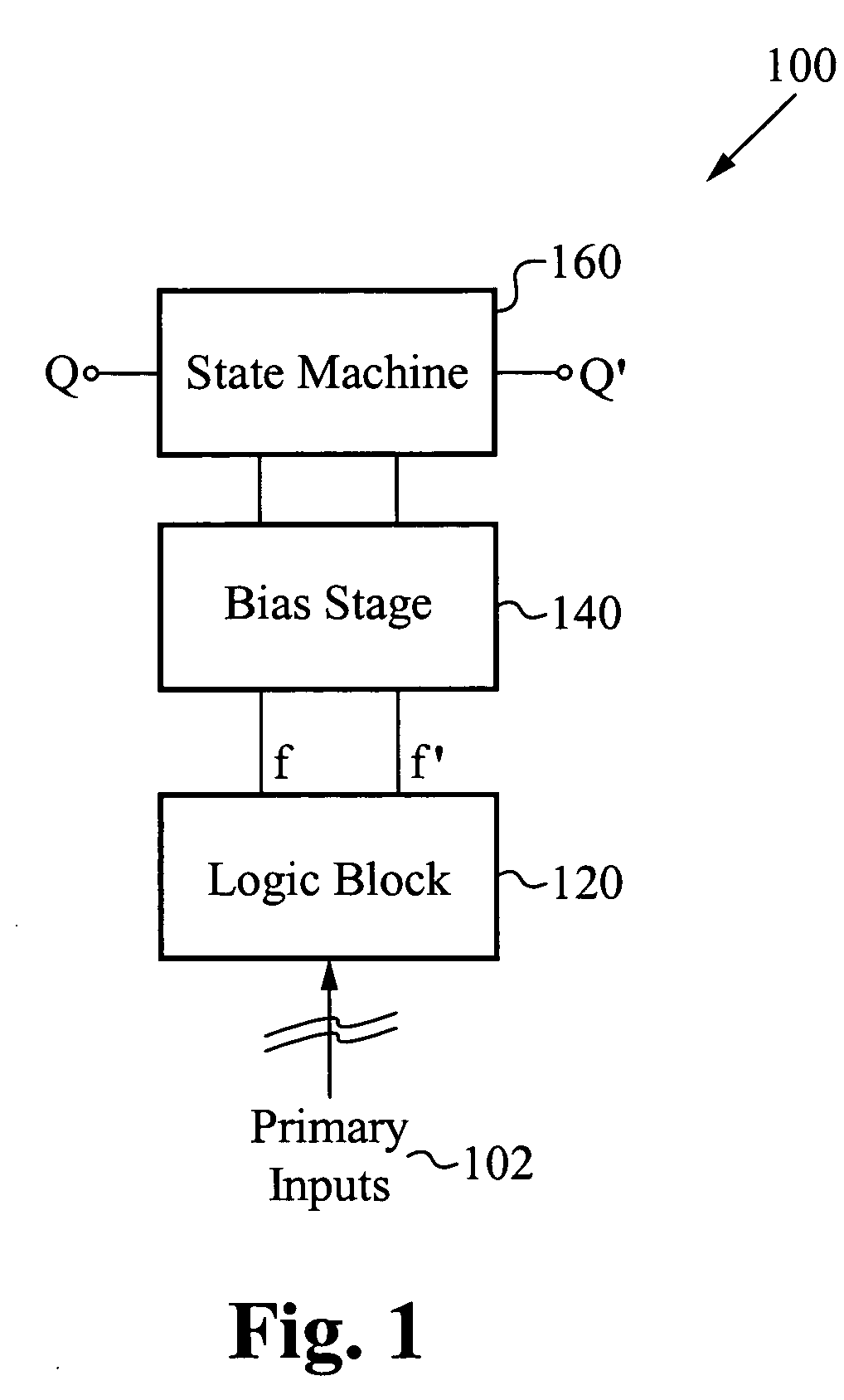

Radiation tolerant combinational logic cell

InactiveUS20070109865A1Increase energy levelReduce sensitivityRead-only memoriesDigital storageCMOSData set

Owner:IDAHO UNIV OF +1

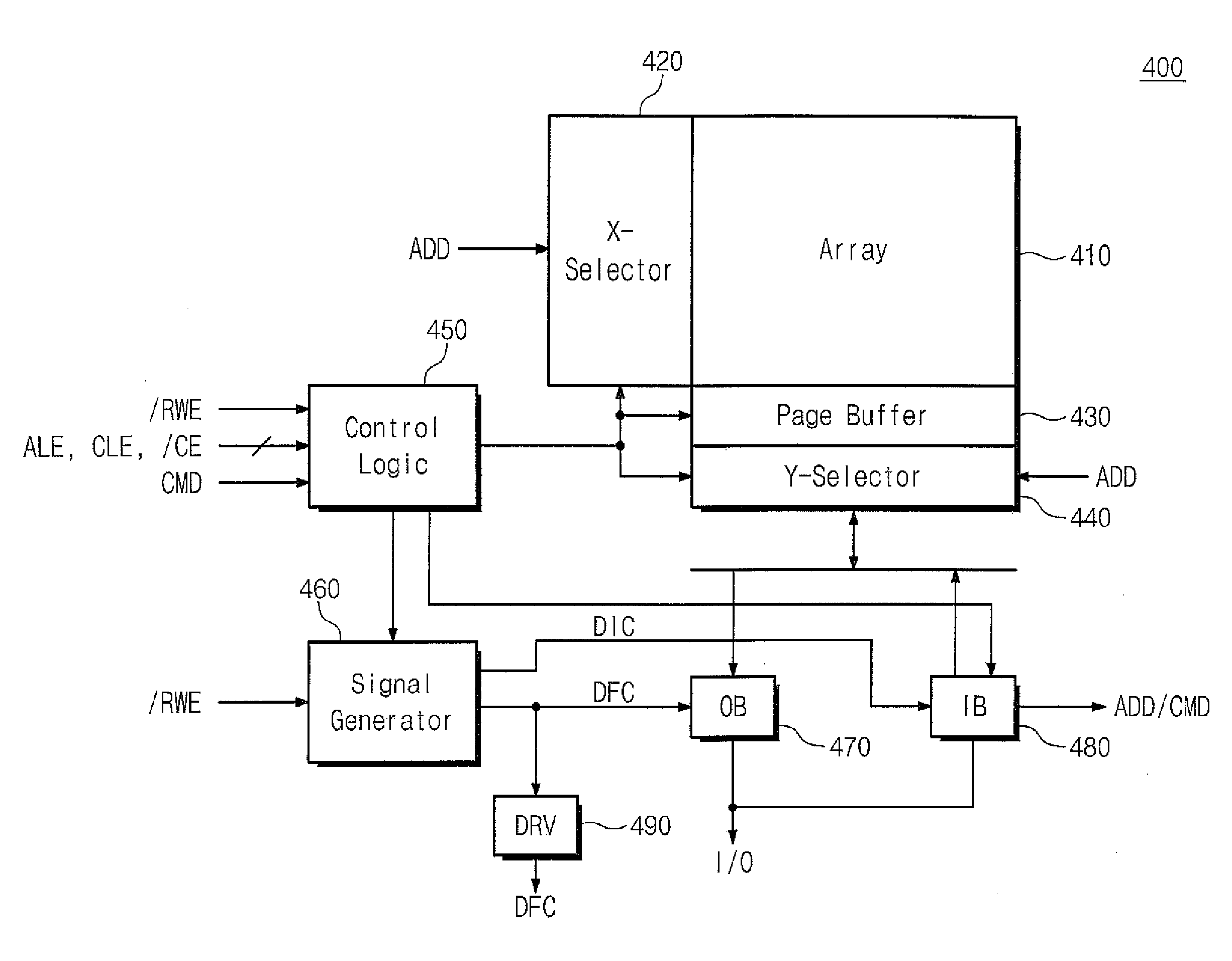

Flash memory device and flash memory system including the same

InactiveUS20090213659A1High frequencyReduce in quantityRead-only memoriesDigital storageSignal generatorComputer science

Owner:SAMSUNG ELECTRONICS CO LTD

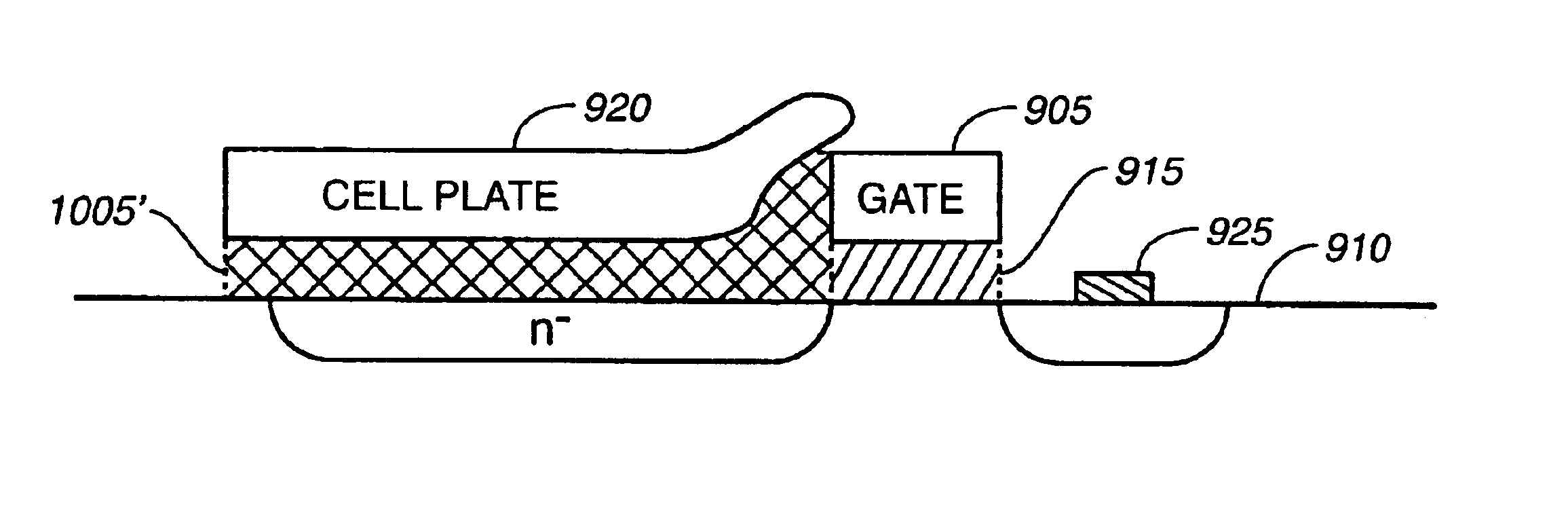

Logic process DRAM

InactiveUS6947324B1Line capacitance is decreasedReduce areaTransistorSolid-state devicesCapacitanceBit line

Owner:MARVELL ASIA PTE LTD

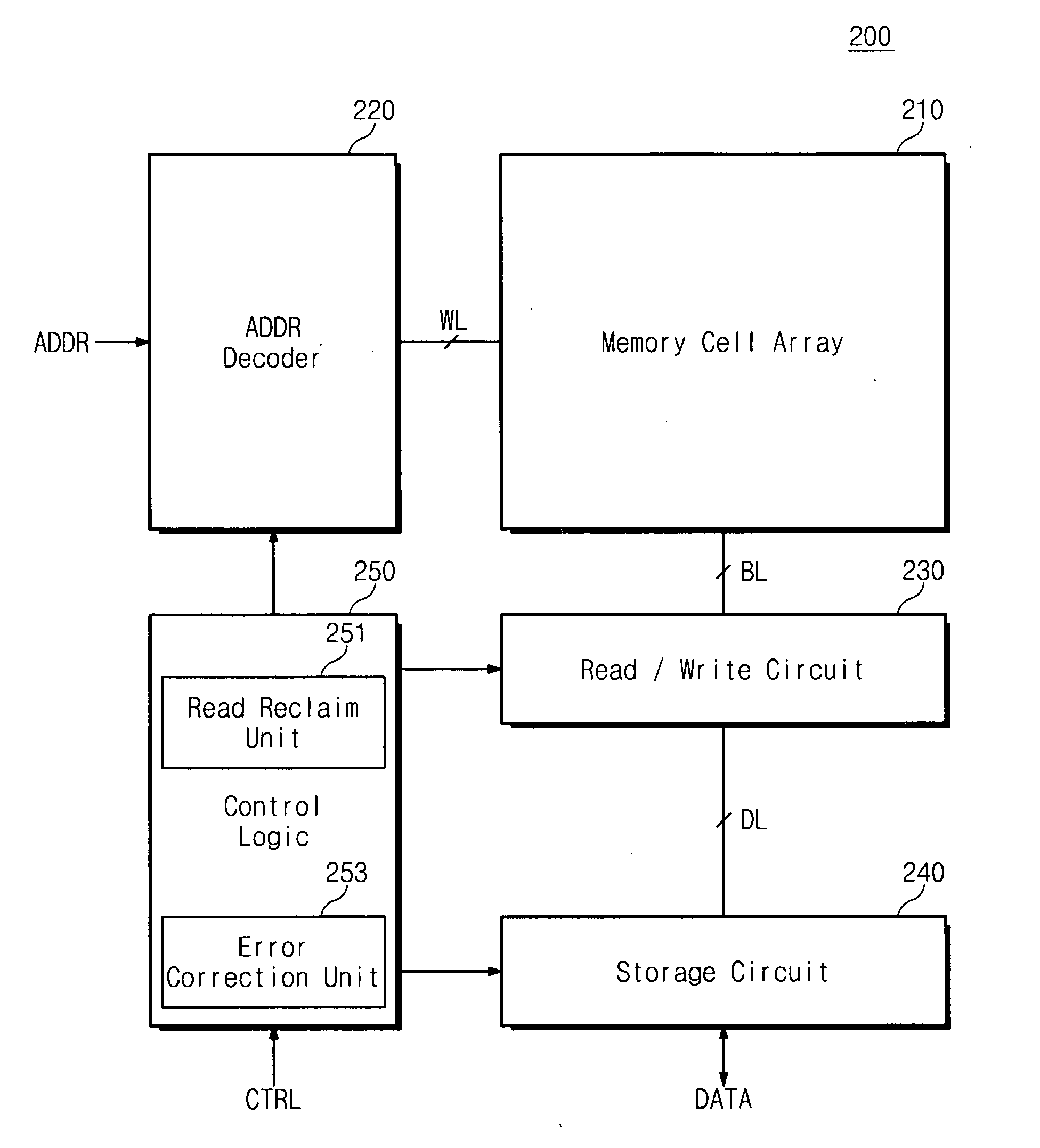

Nonvolatile memory system and data recovery method thereof

InactiveUS20160124805A1High data reliabilityMinimizing deteriorationRead-only memoriesRedundant data error correctionReading levelMemory controller

Owner:SK HYNIX INC

Non-volatile memory device and operating method thereof

InactiveUS20130159798A1Improve operational accuracyRead-only memoriesFunctional testingStorage cellPeripheral

Owner:SK HYNIX INC

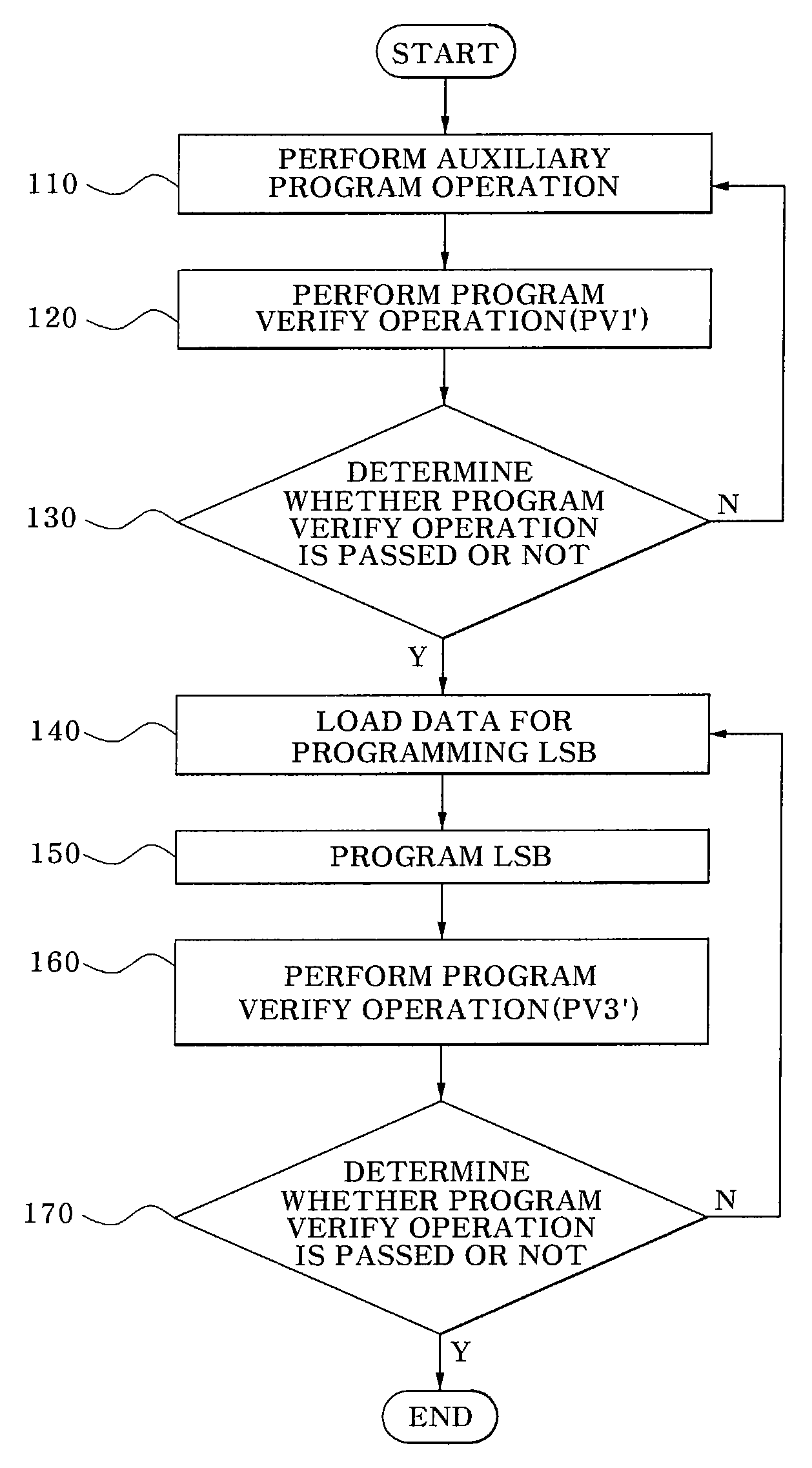

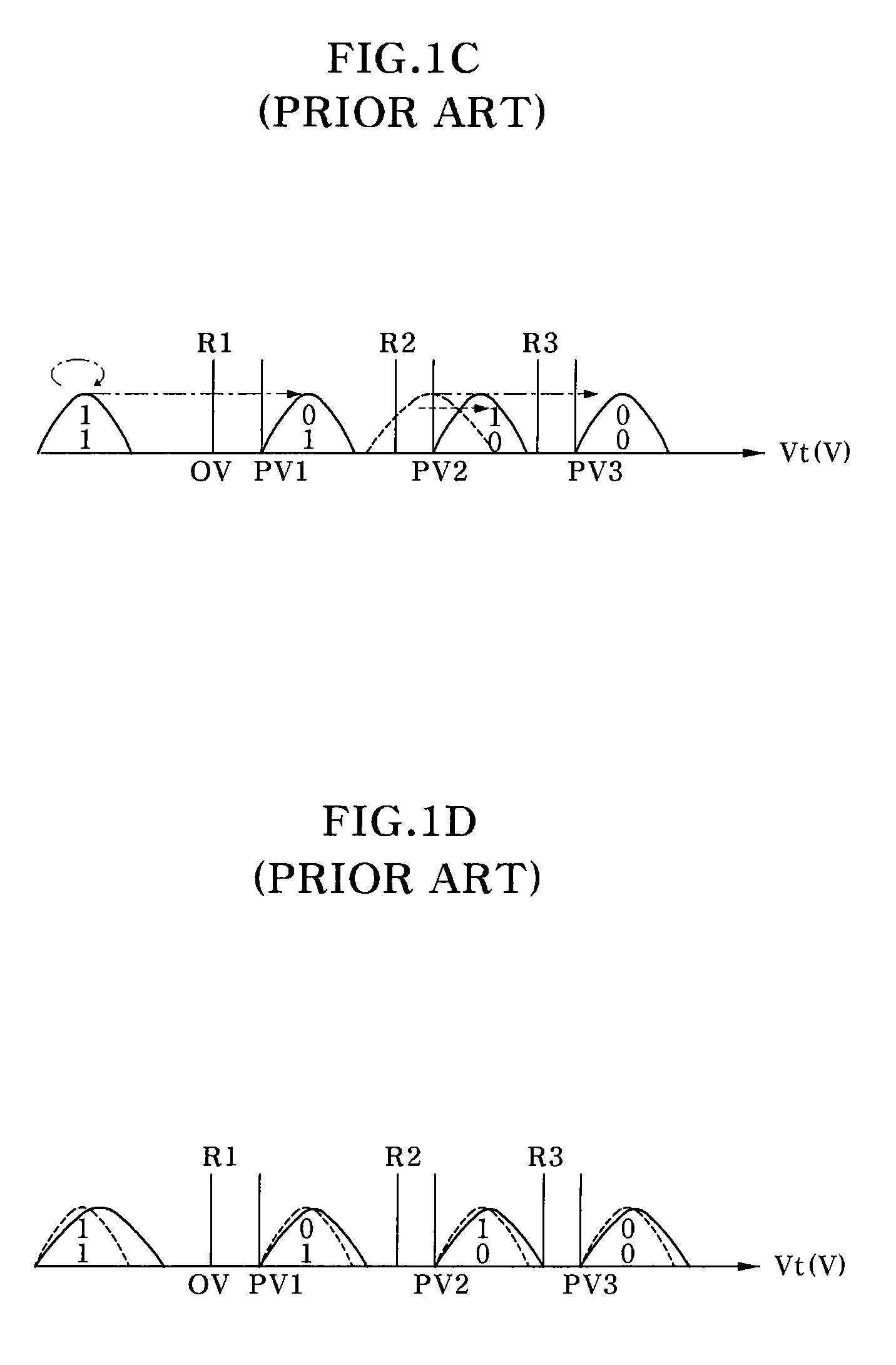

Method for programming multi-level cell flash memory device

ActiveUS20090003055A1Interference minimizationRead-only memoriesDigital storageSensing dataThreshold voltage

Owner:SK HYNIX INC

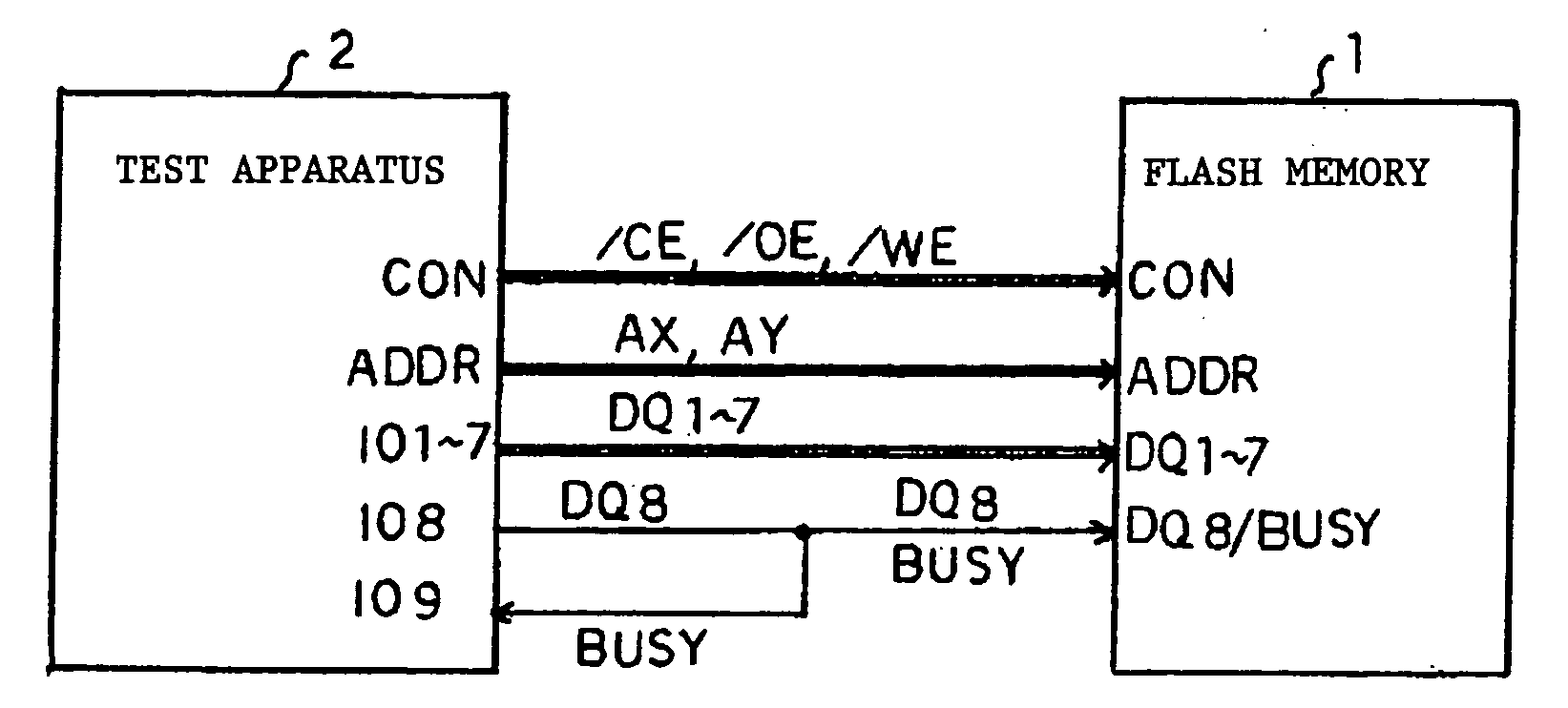

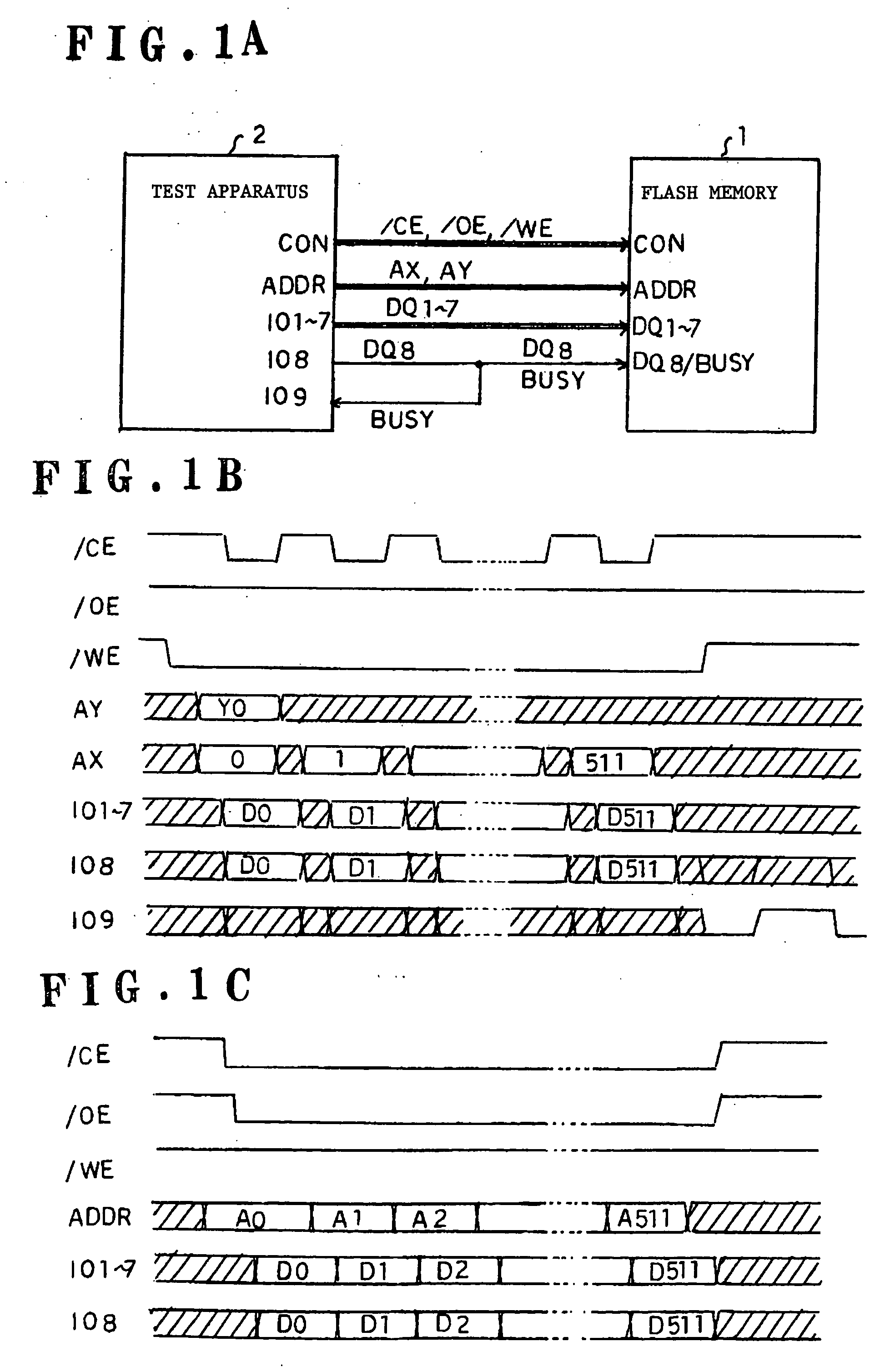

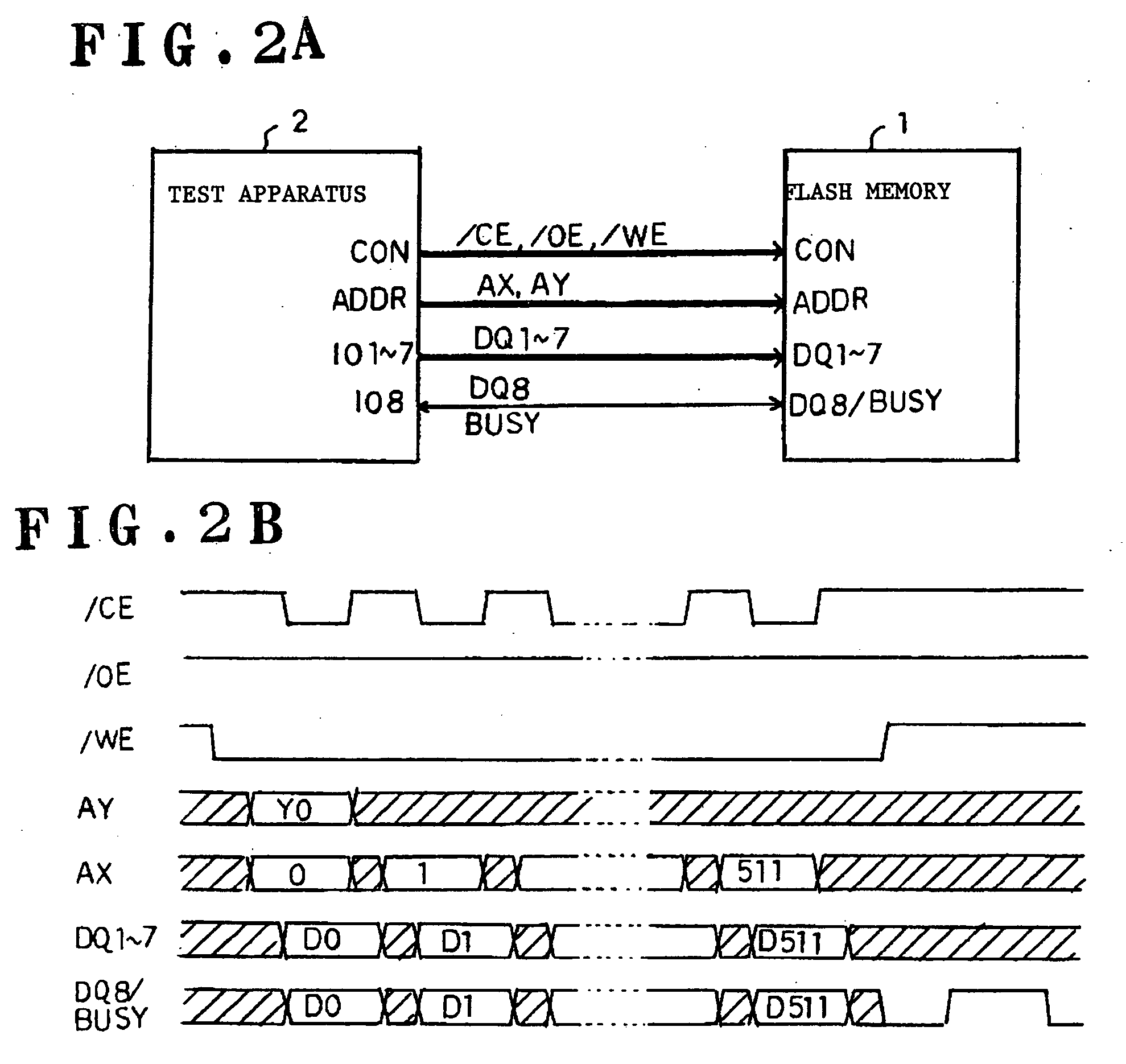

Test method for nonvolatile memory

InactiveUS20060048023A1Simple processSimple methodRead-only memoriesDigital storageData terminalComputer terminal

Owner:LAPIS SEMICON CO LTD

Circuit and technique for accurately sensing low voltage flash memory devices

Owner:MONTEREY RES LLC

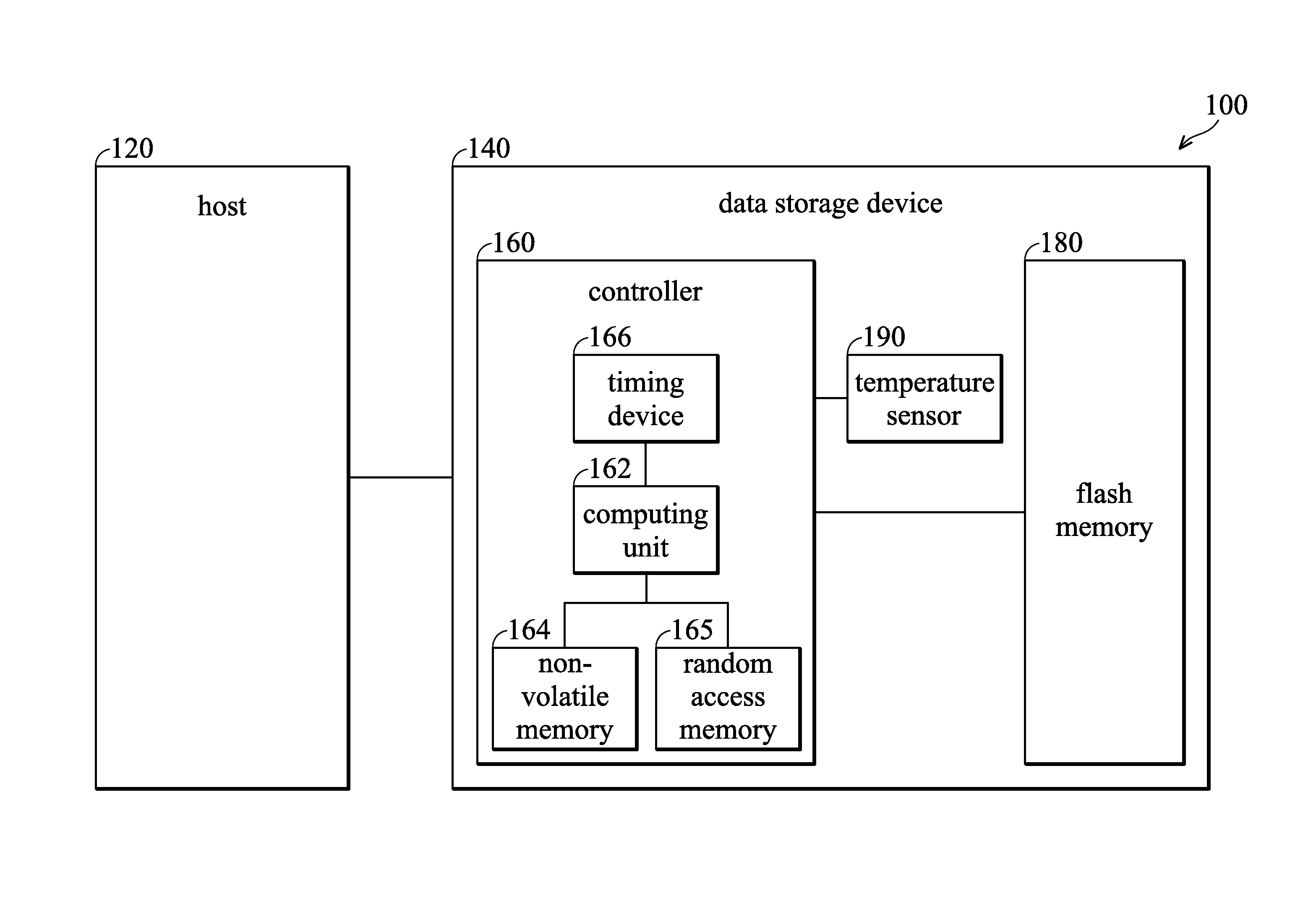

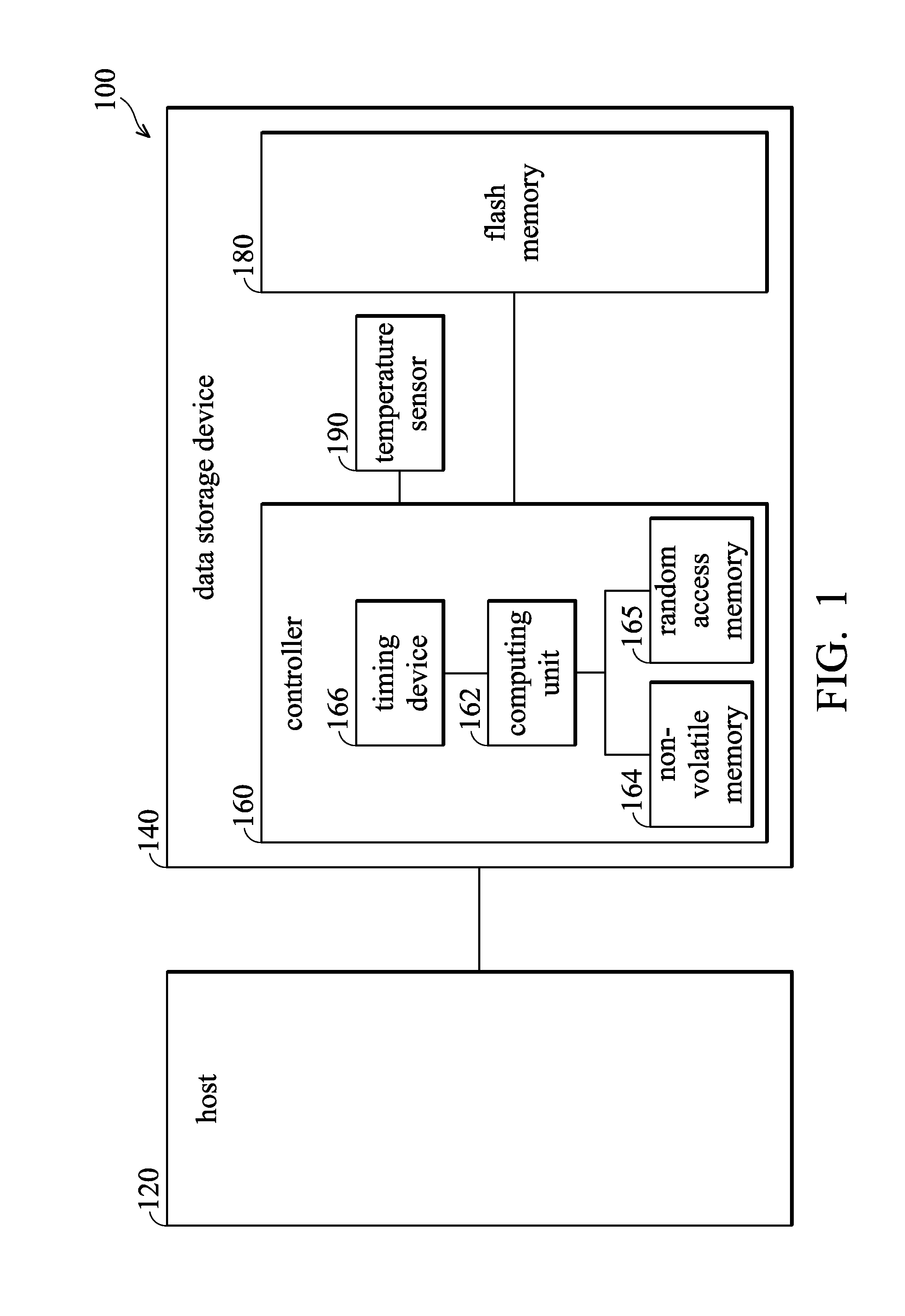

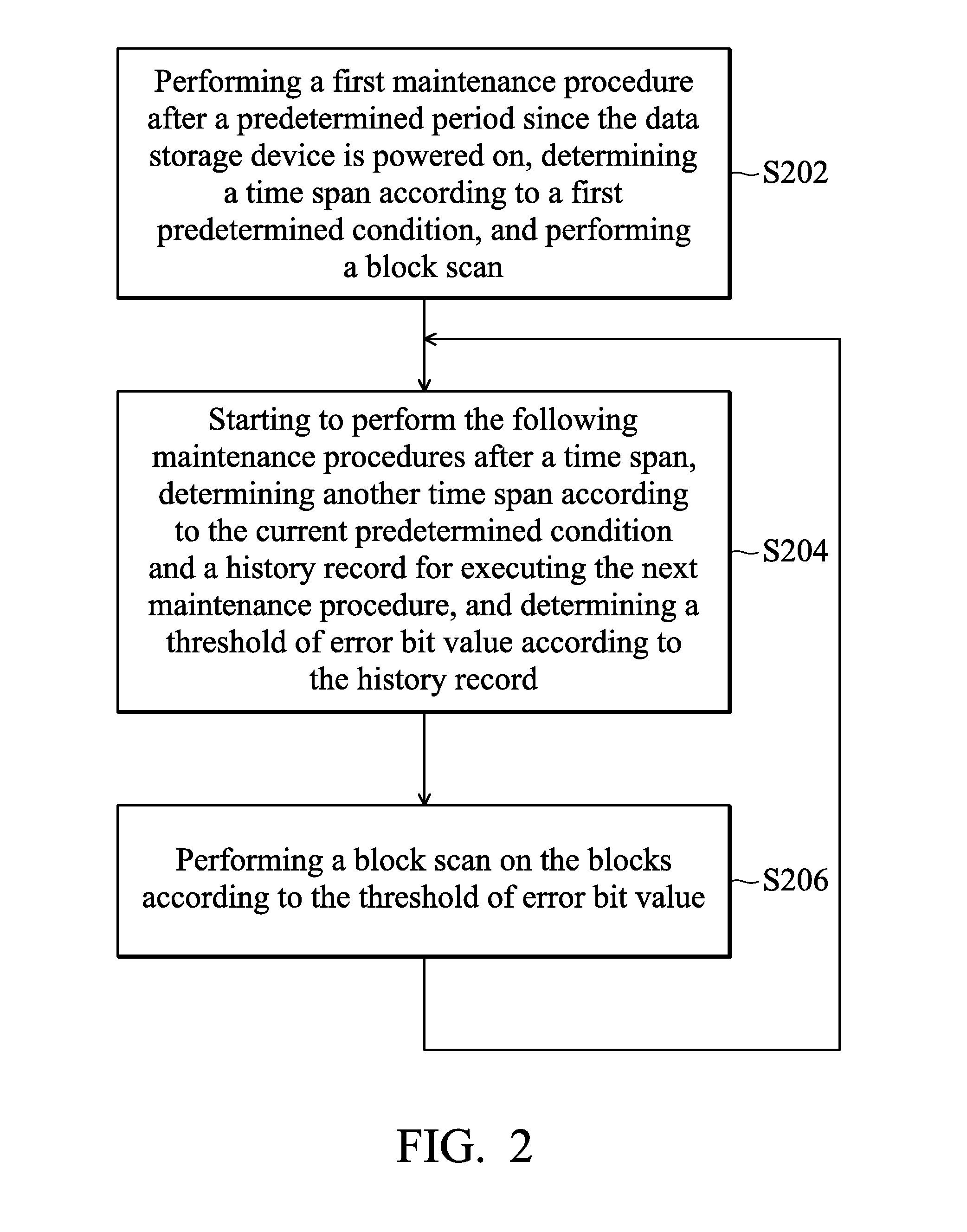

Data Storage Device and Data Maintenance Method Thereof

Owner:SILICON MOTION INC (TW)

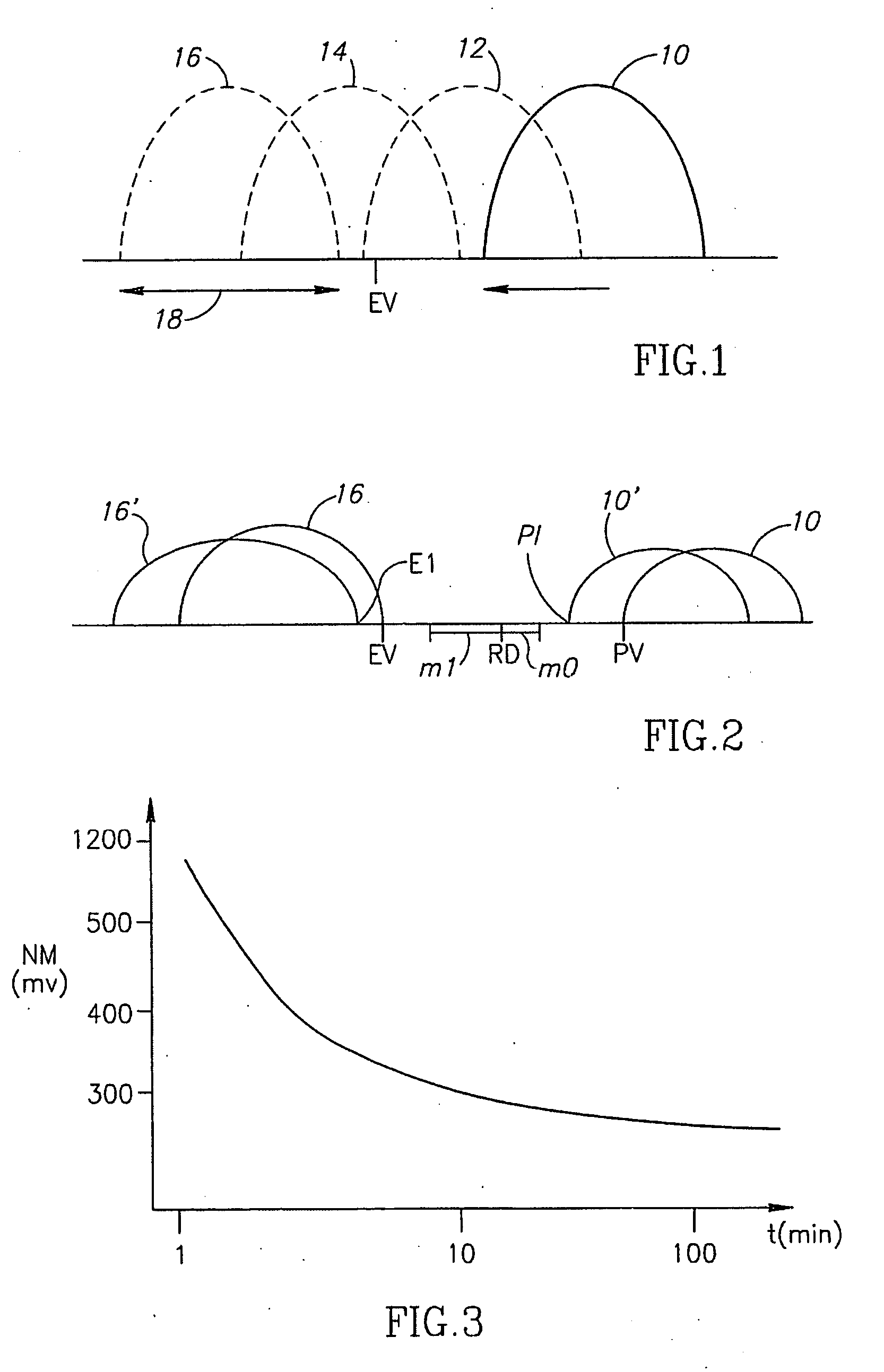

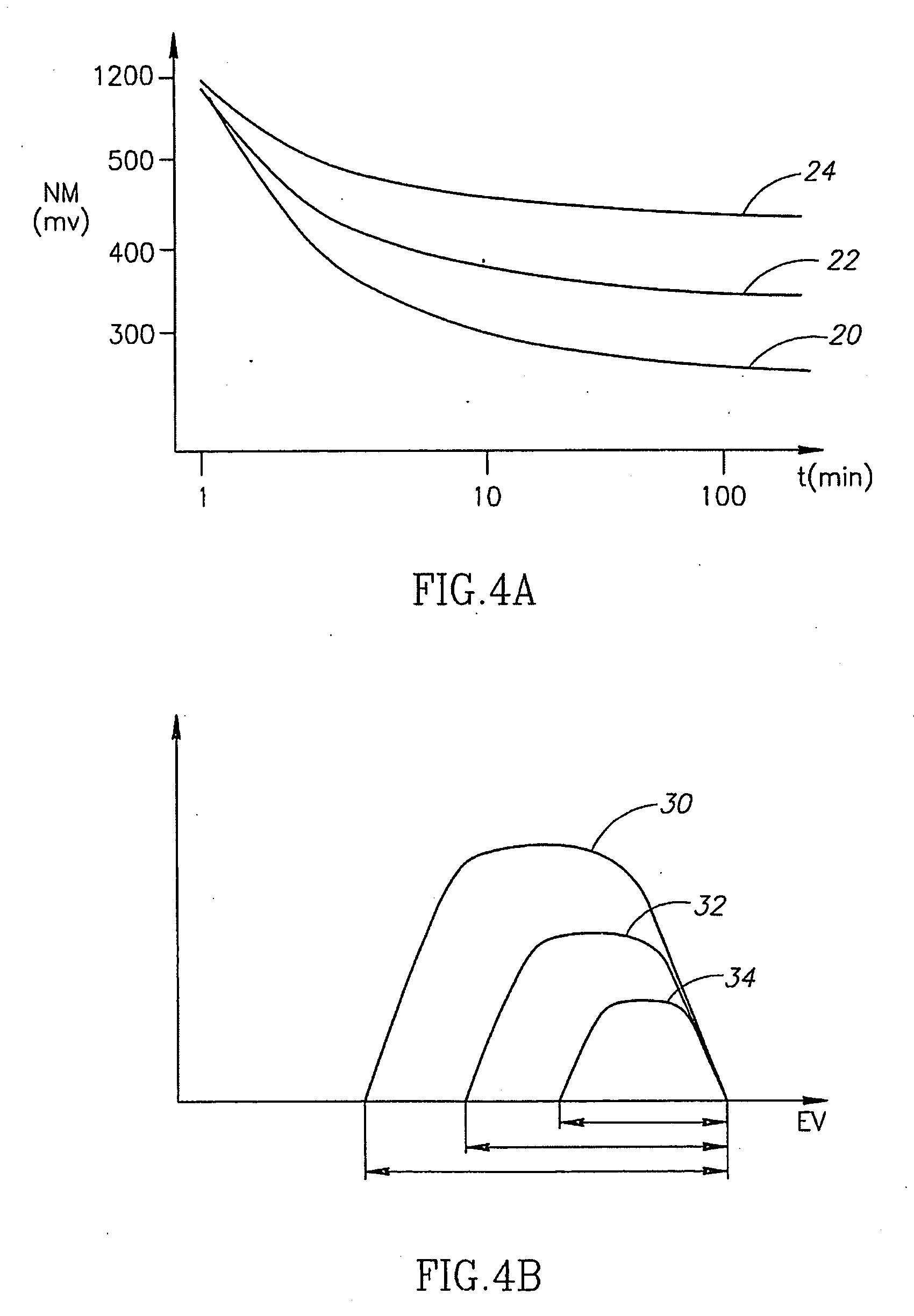

Method of erasing non-volatile memory cells

Owner:SAIFUN SEMICON

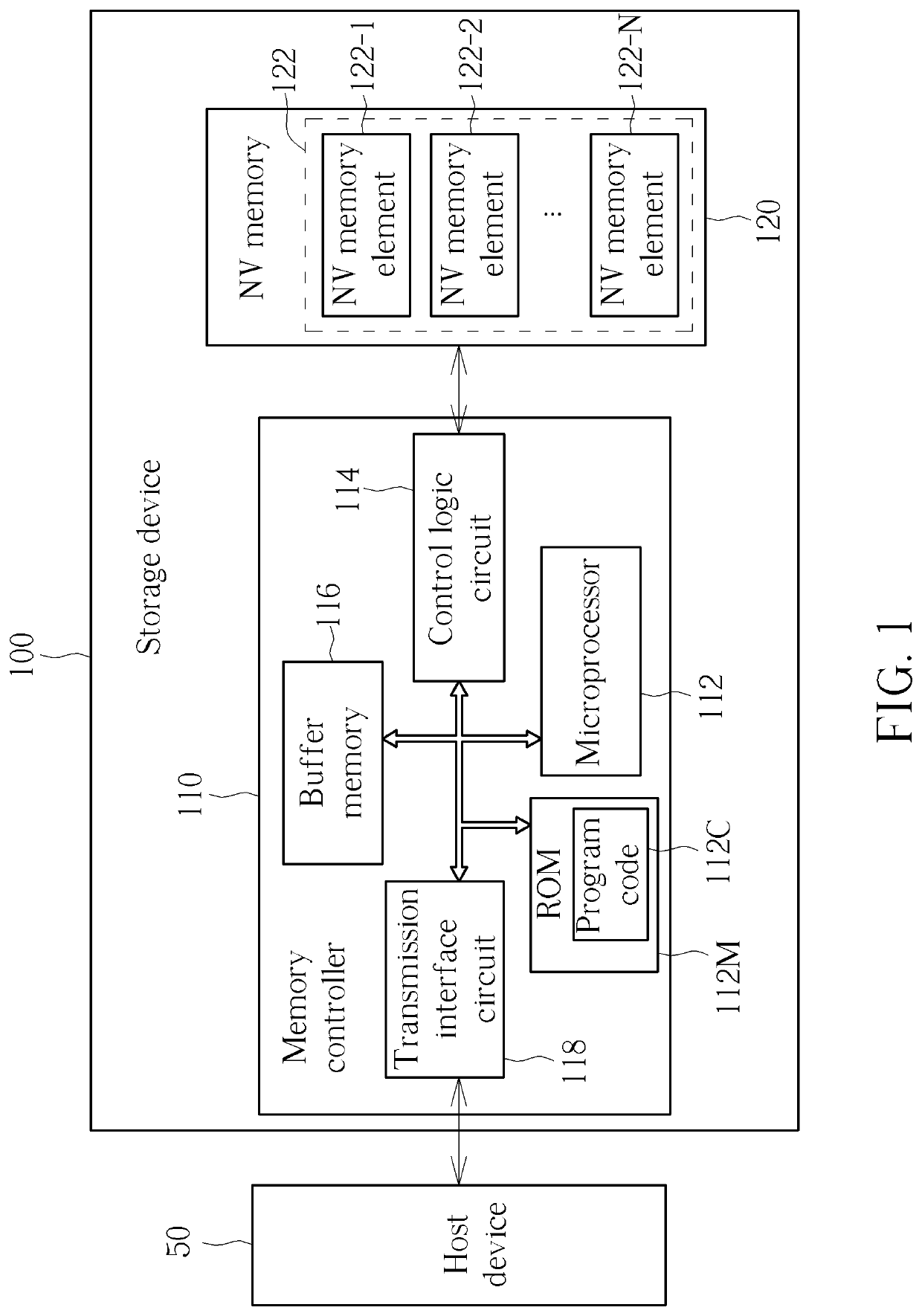

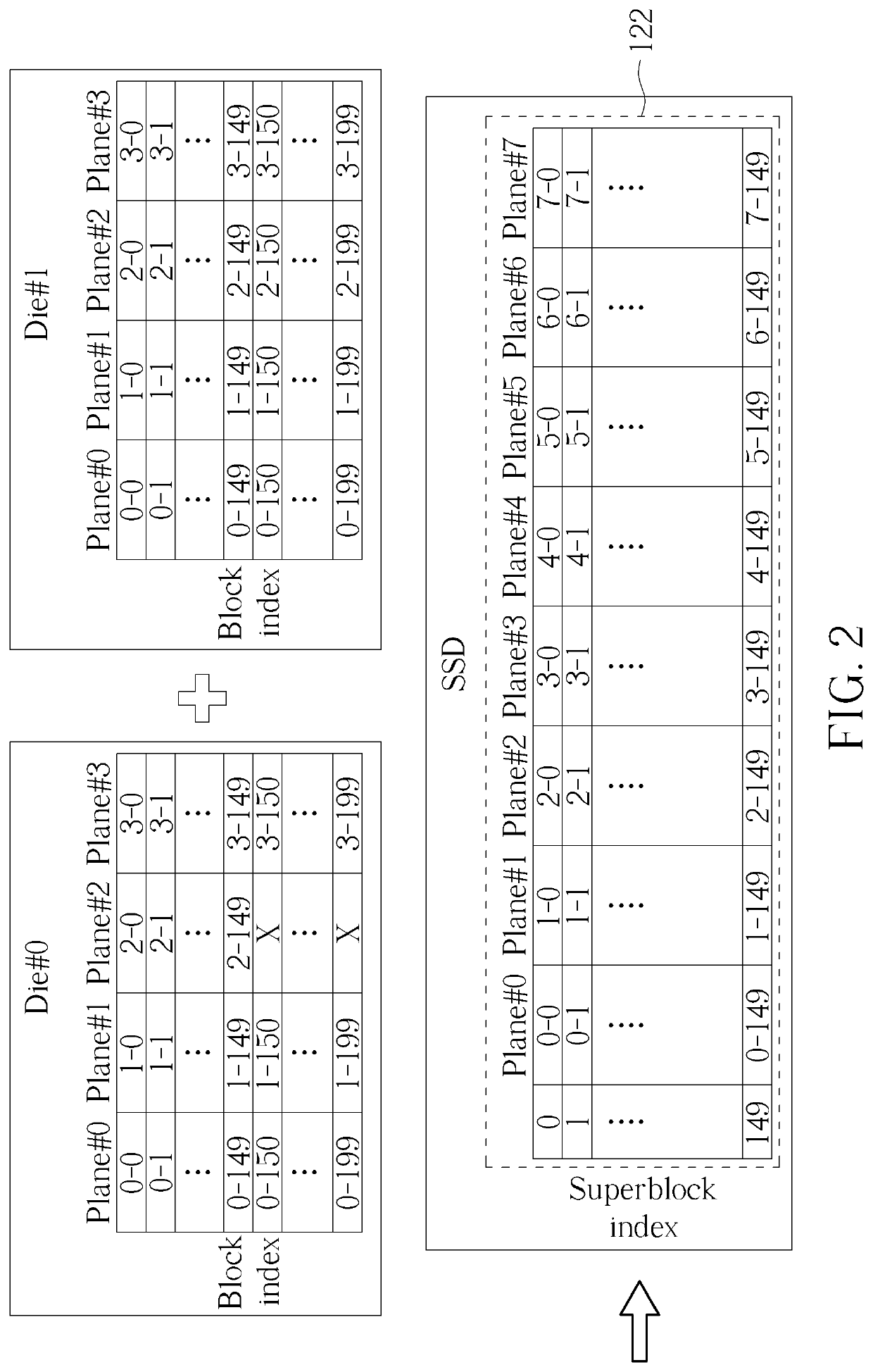

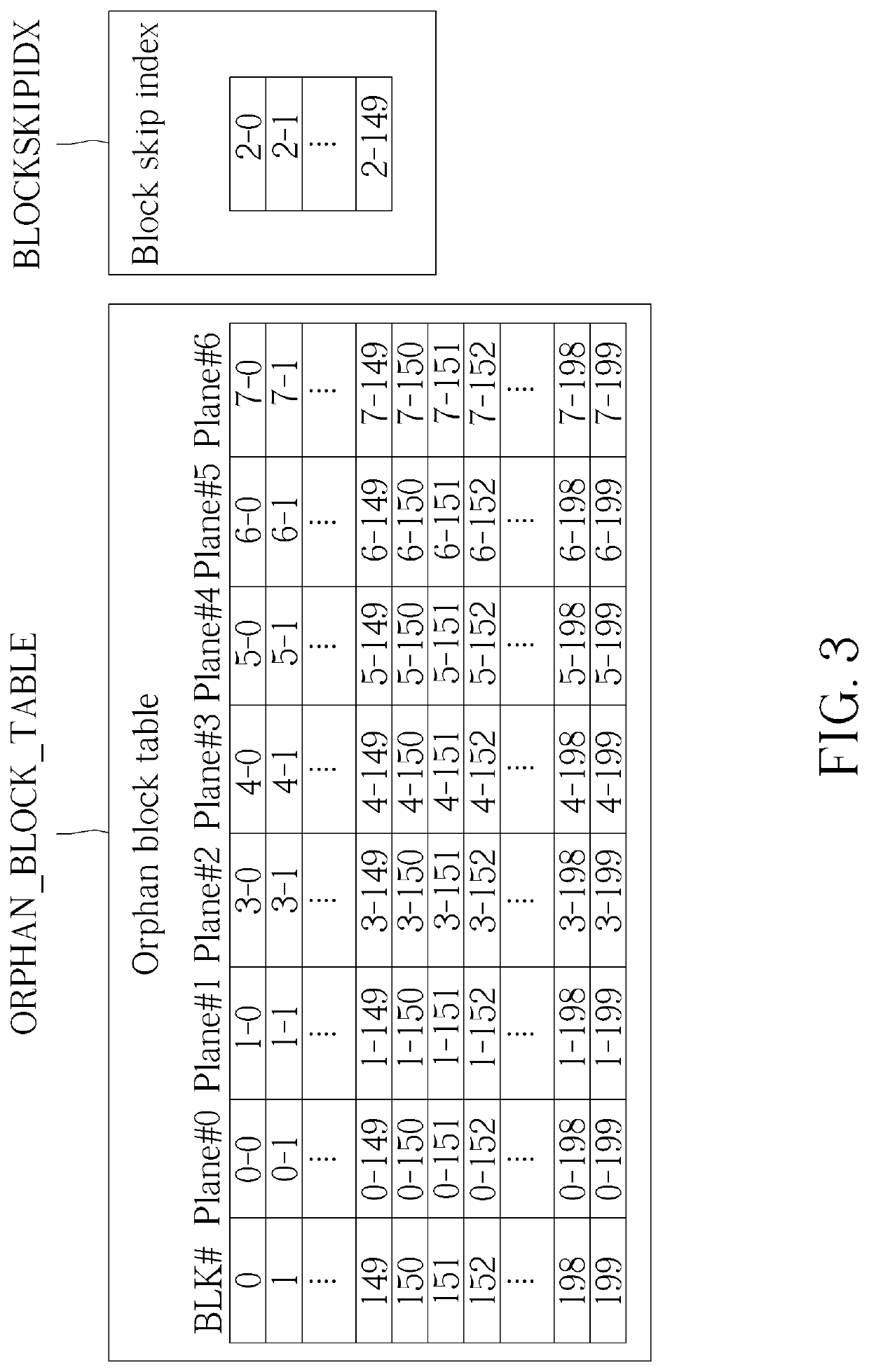

Unbalanced plane management method, associated data storage device and controller thereof

ActiveUS20200285393A1Improve efficiencyIncrease costMemory architecture accessing/allocationInput/output to record carriersParallel computingData store

Owner:SILICON MOTION INC (TW)

ROM (Read Only Memory) and layout thereof

Owner:苏州兆芯半导体科技有限公司

Semiconductor integrated circuit device with power-on reset circuit for detecting the operating state of an analog circuit

A semiconductor integrated circuit device operates using a first power supply and a second power supply differing from the first power supply in voltage. The semiconductor integrated circuit device includes a first detecting circuit which detects that the first power supply has exceeded a specific voltage, a second detecting circuit which detects that the second power supply has exceeded a specific voltage, and a check circuit which checks the operating state of an analog circuit carrying out an analog operation using the first power supply and outputs a control signal indicating whether the analog circuit is operating properly. The detecting level of the first detecting circuit is determined on the basis of the control signal. A power-on reset signal is output according to the result of the detection at the first and second detecting circuits.

Owner:KK TOSHIBA

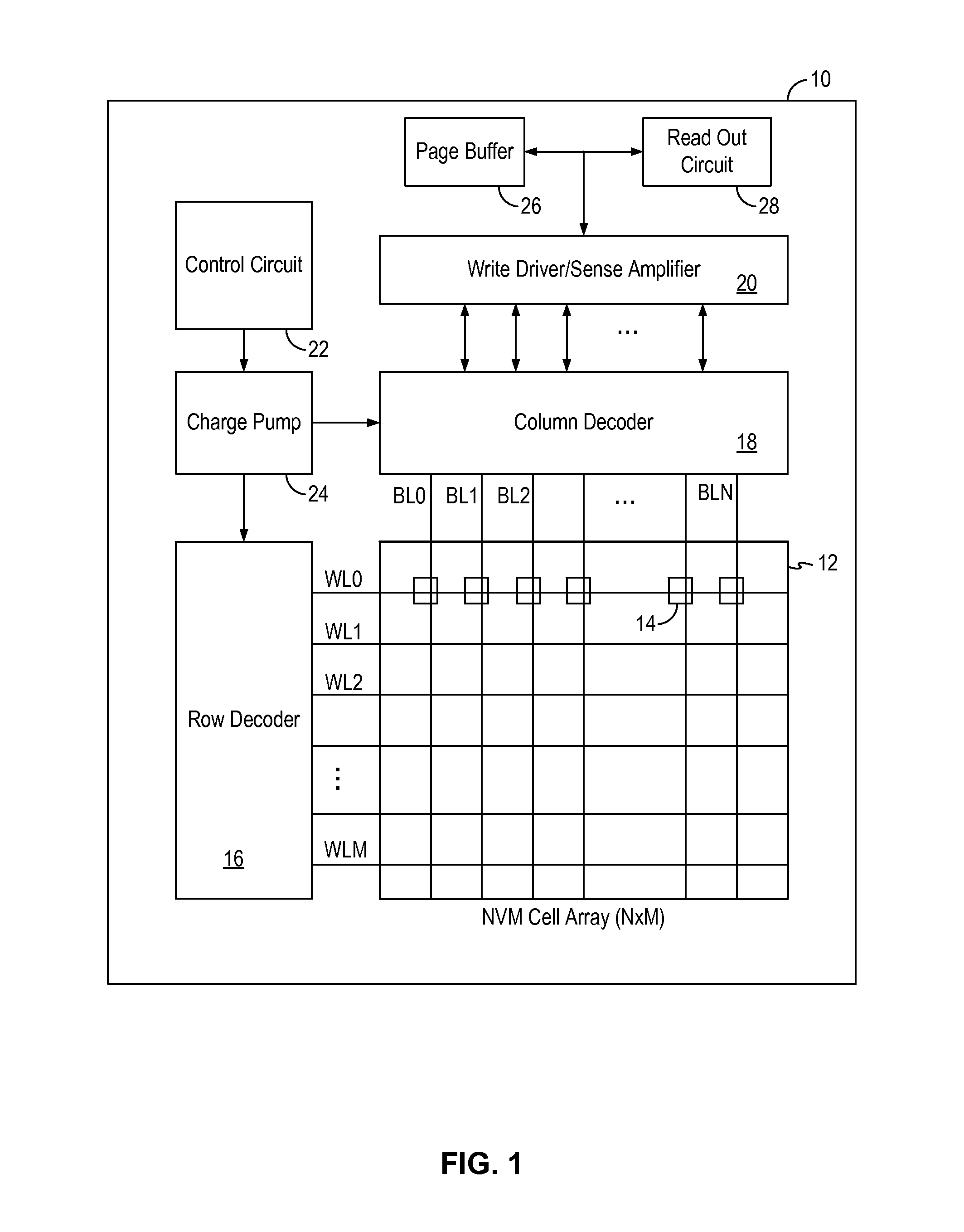

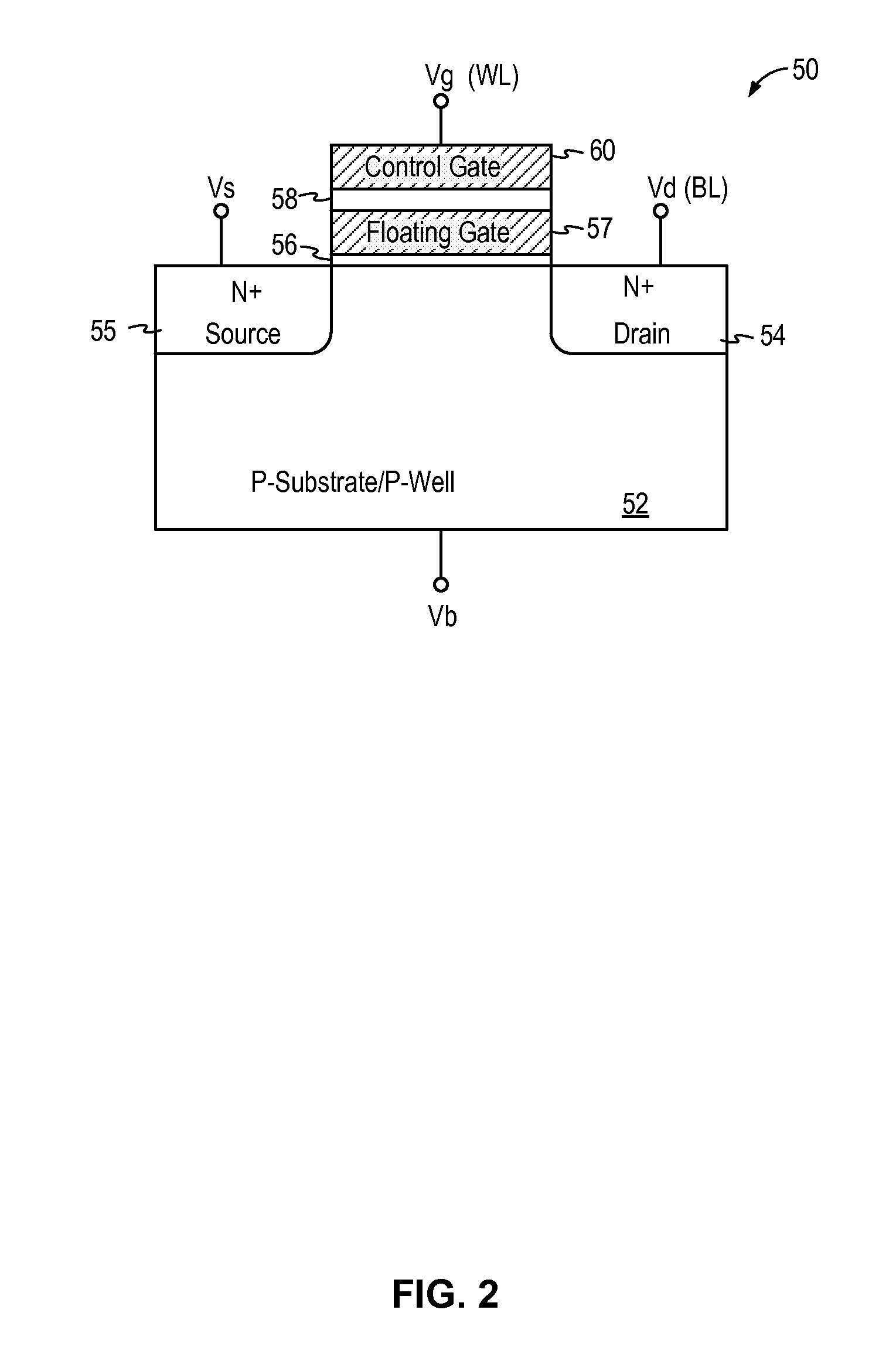

Non-volatile memory, method of manufacture, and method of programming

Owner:FREESCALE SEMICON INC

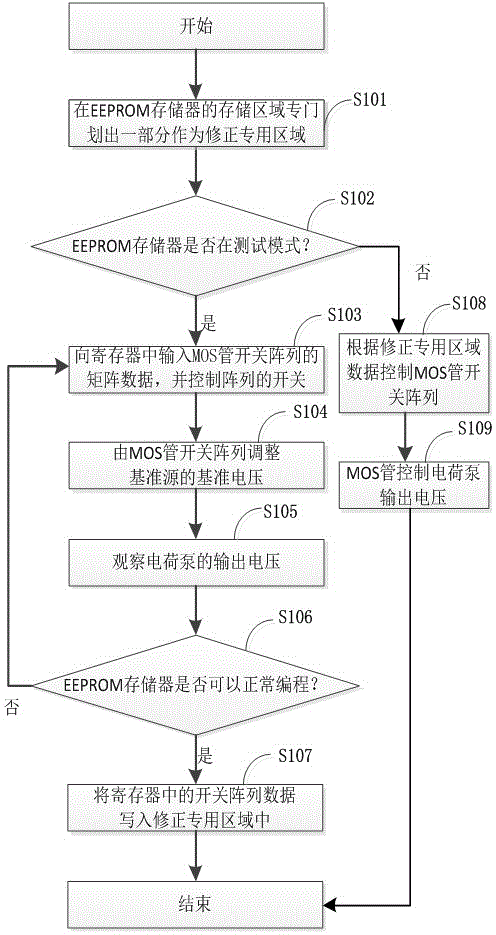

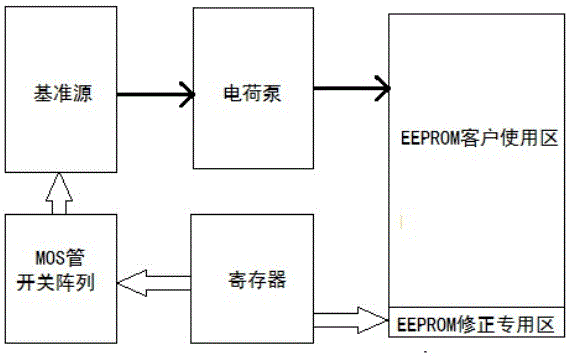

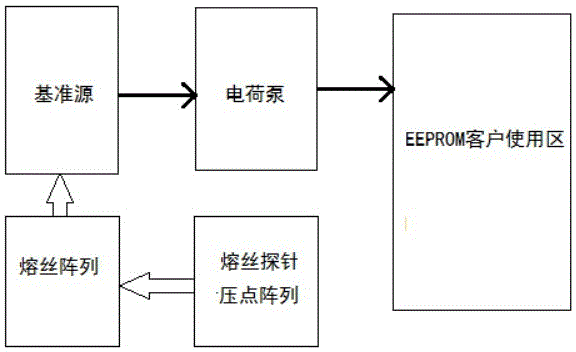

Booster circuit and method for improving programming accuracy of EEPROM

Owner:深圳市航顺芯片技术研发有限公司

Abridged erase verify method for flash memory

Owner:INTEGRATED SILICON SOLUTION

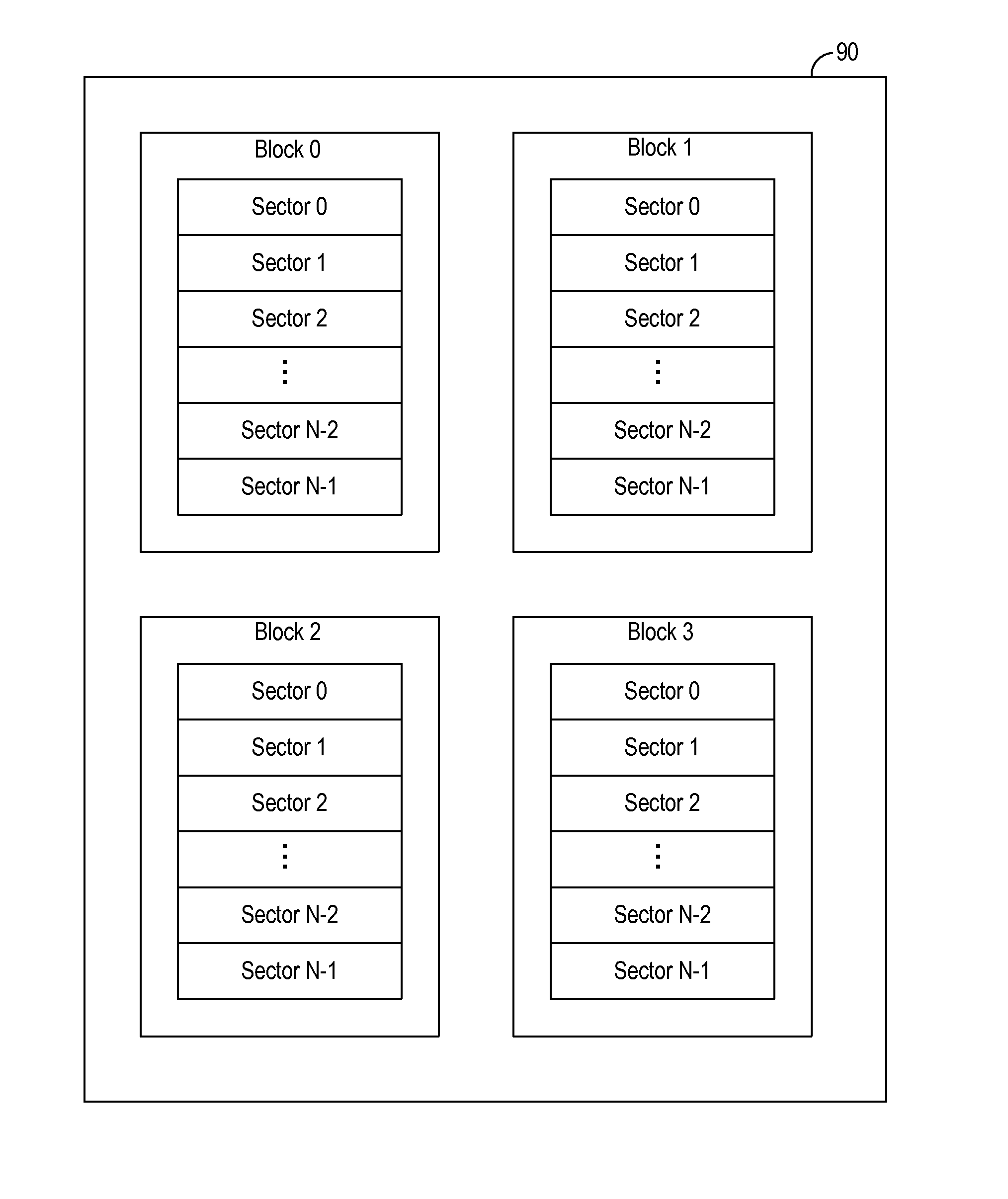

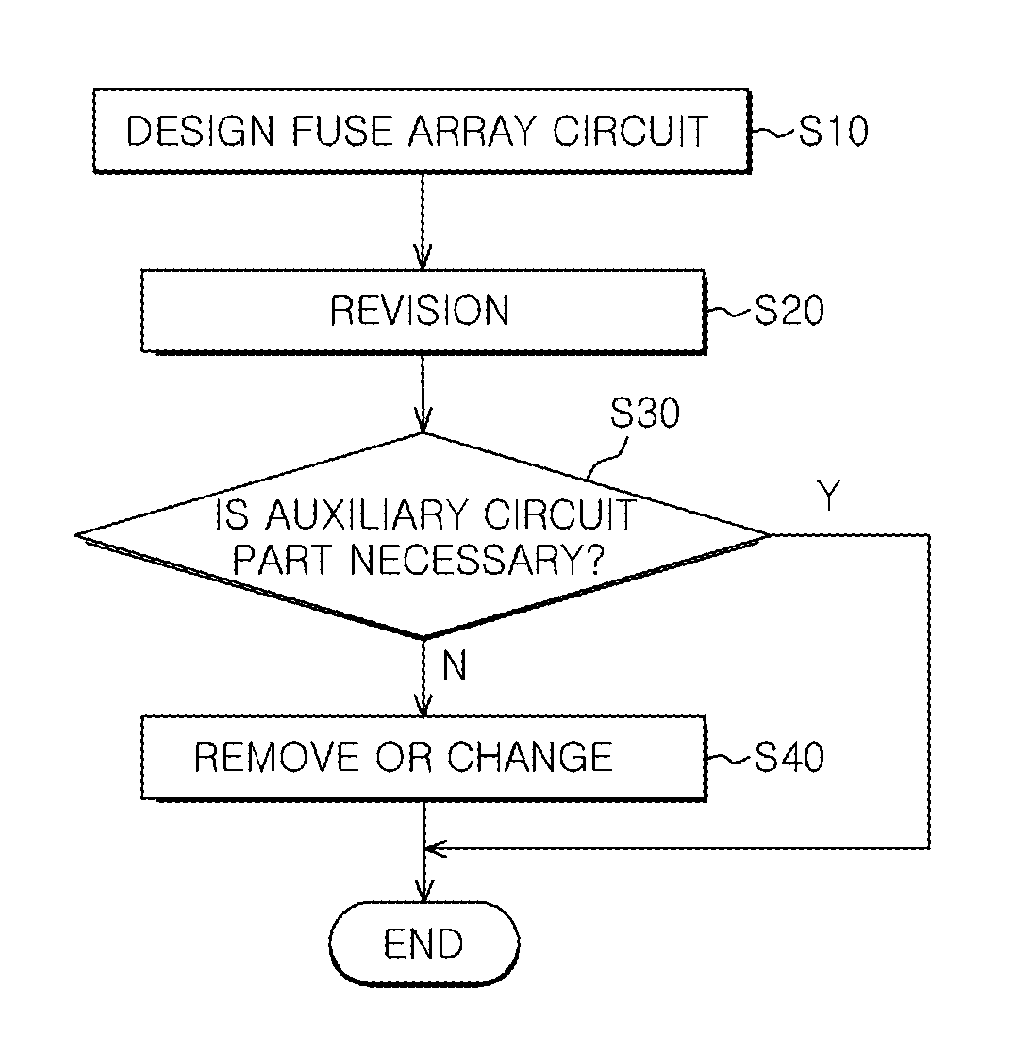

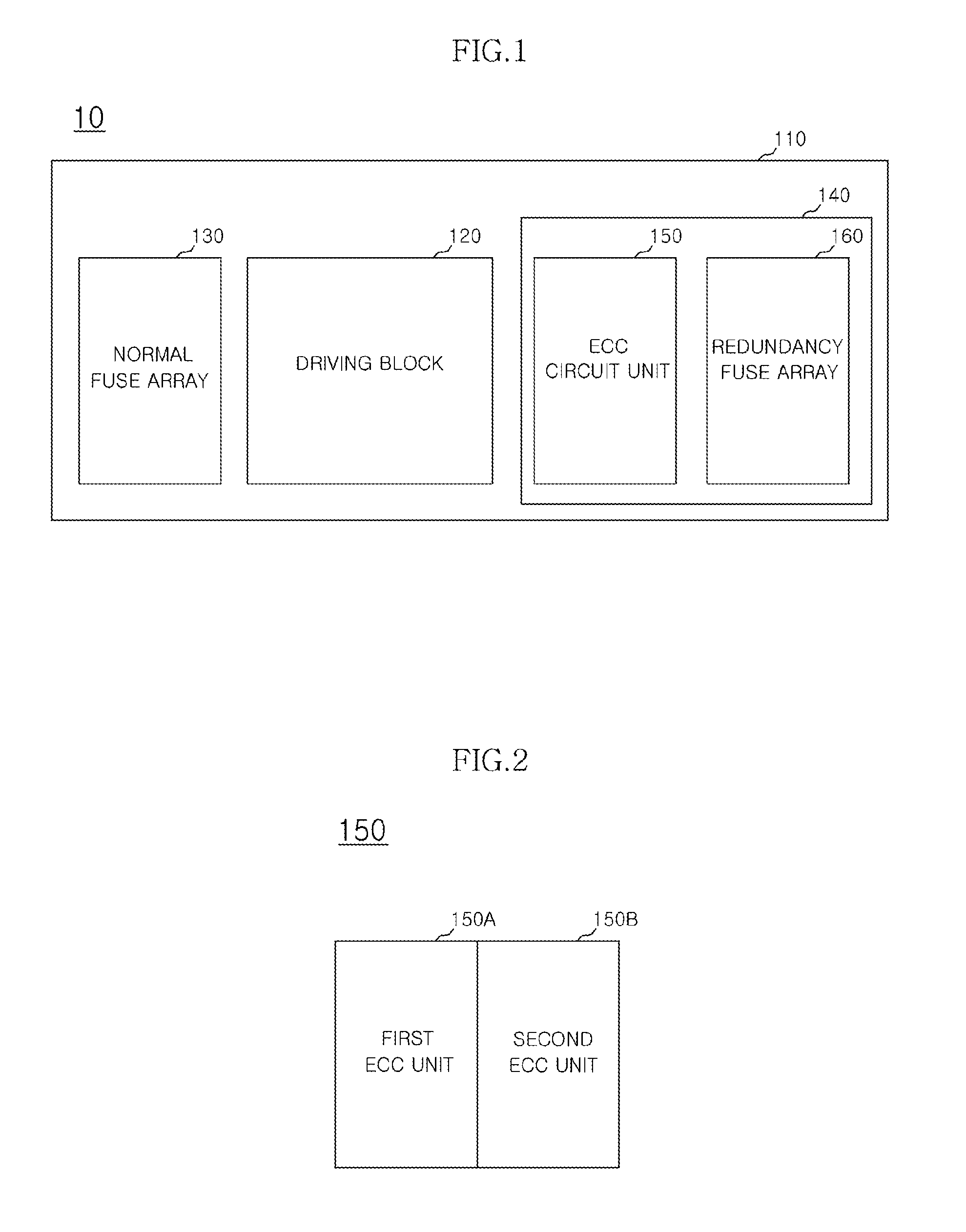

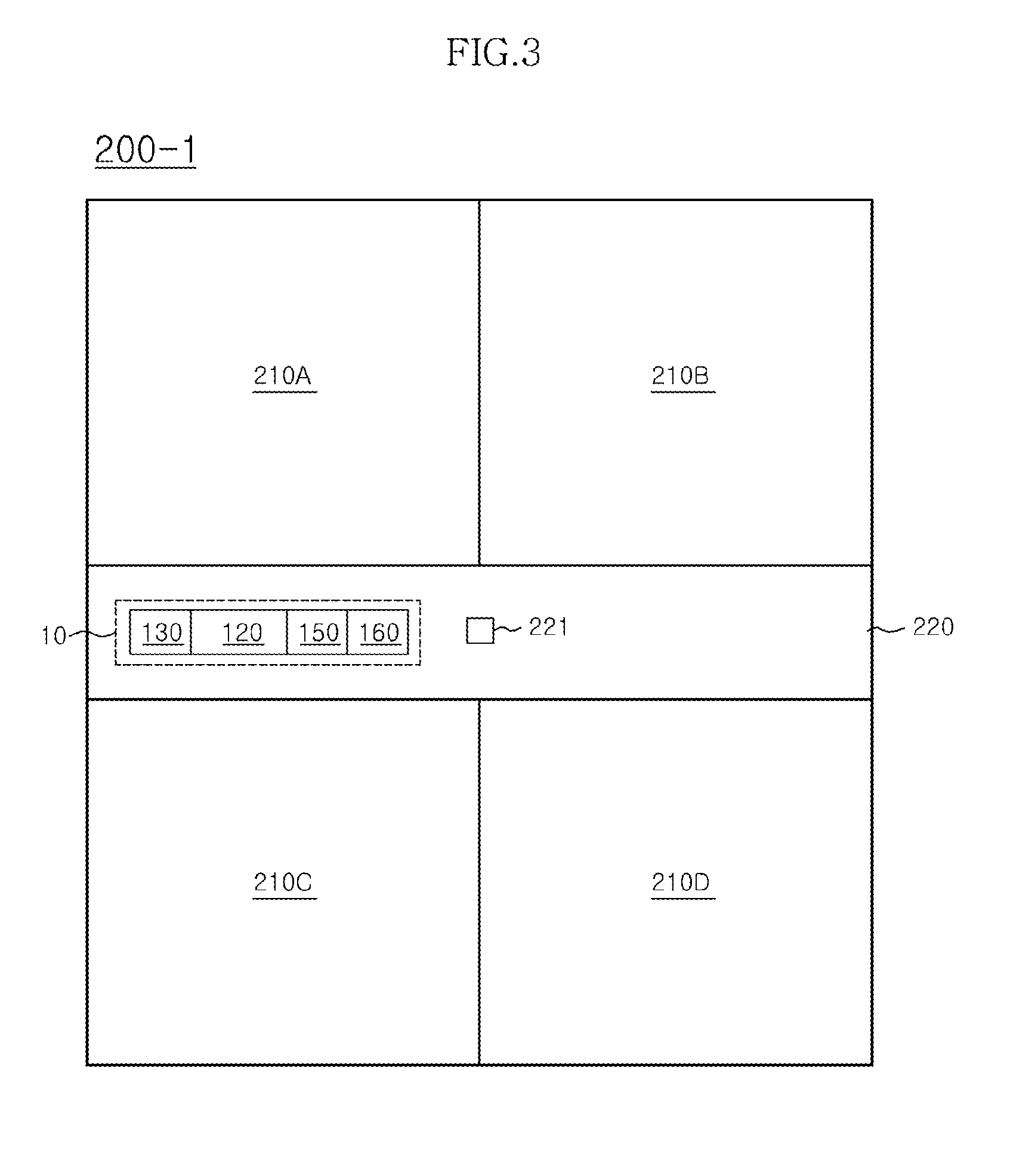

E-fuse array circuit and semiconductor memory apparatus having the same

Owner:SK HYNIX INC

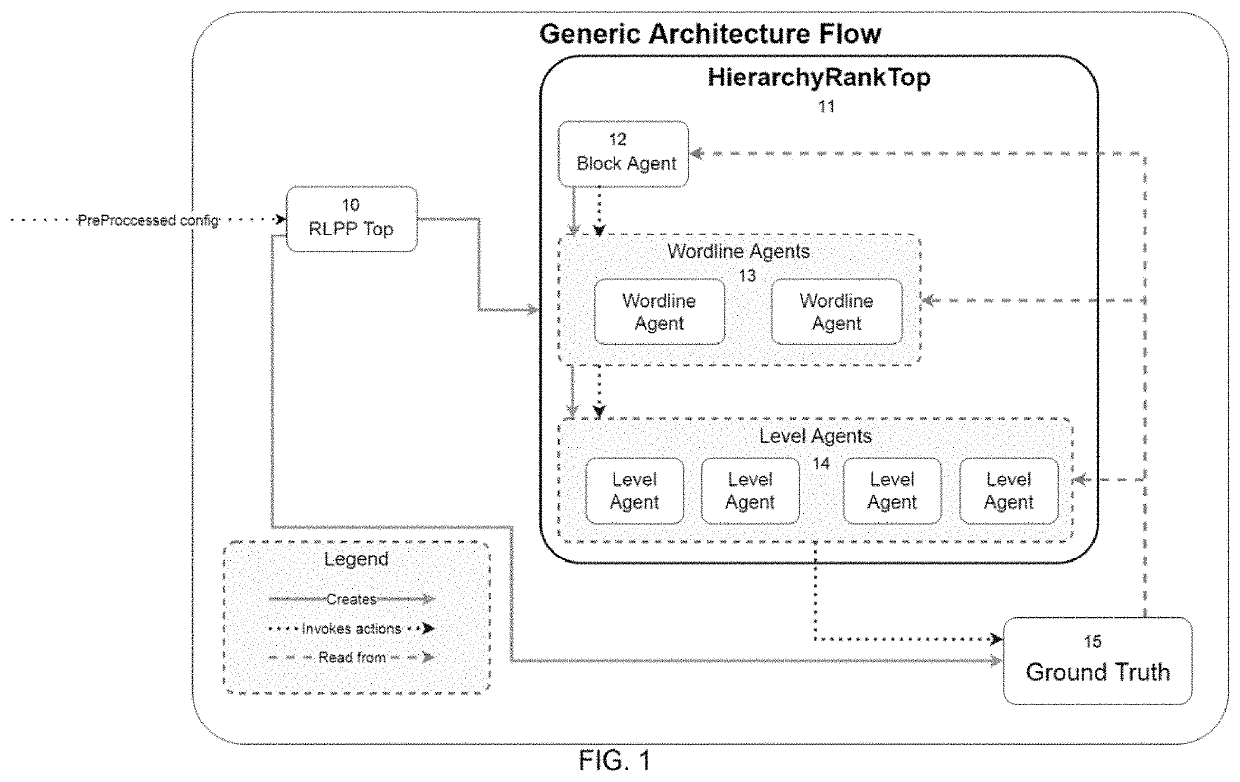

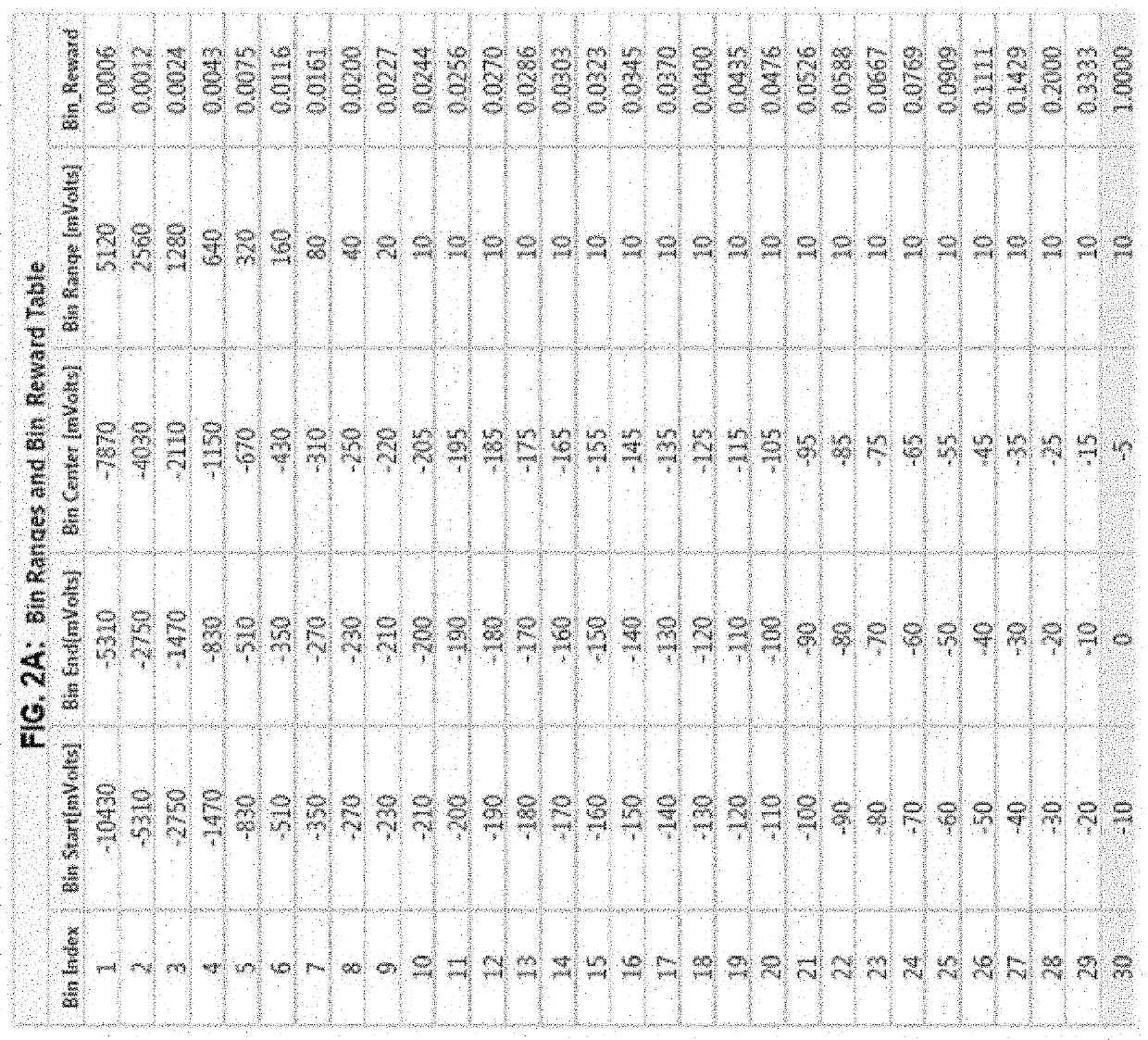

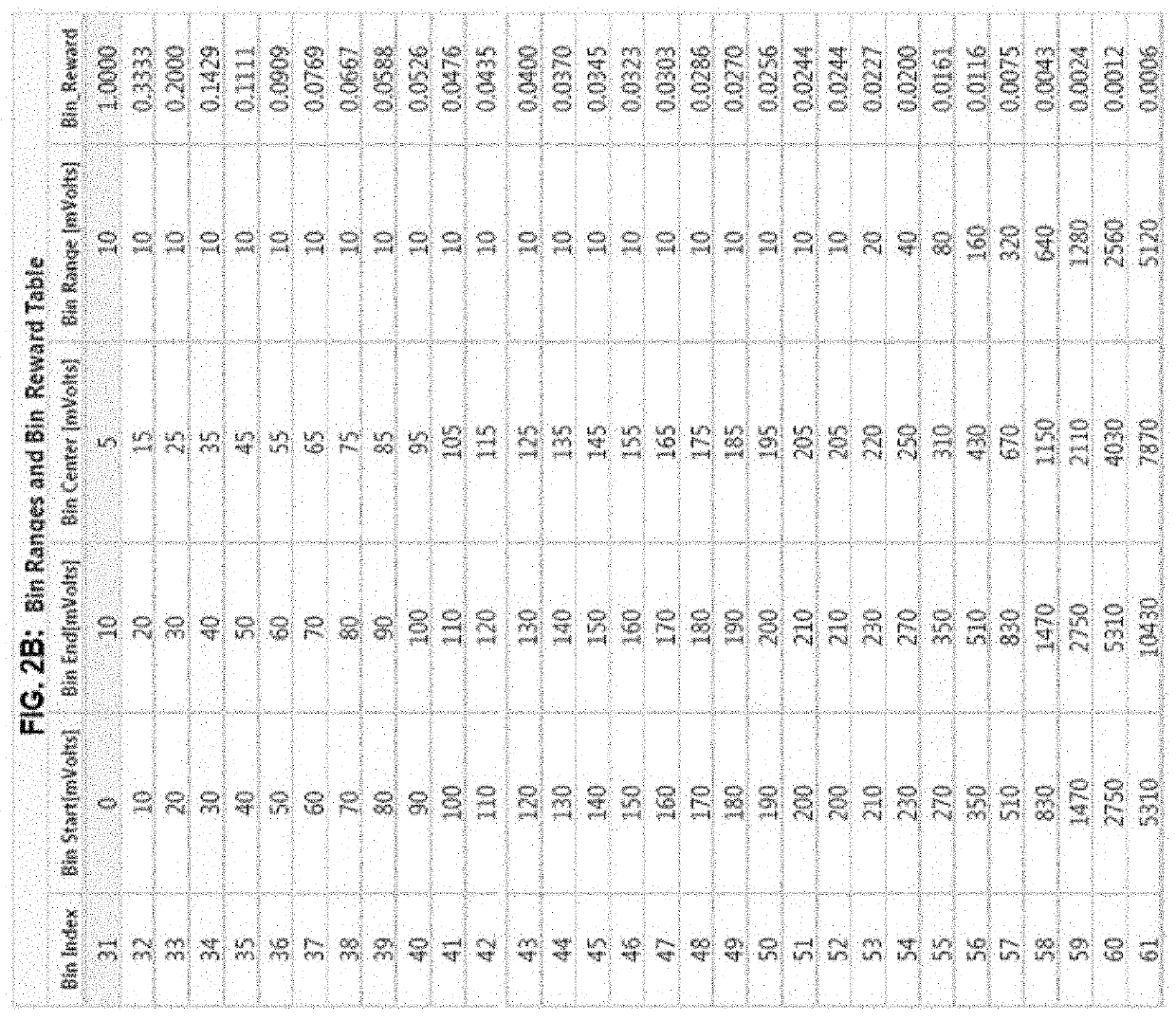

Reinforcement learning pulse programming

ActiveUS20210103806A1Mathematical modelsRead-only memoriesElectrical and Electronics engineeringAlgorithm

Owner:SAMSUNG ELECTRONICS CO LTD

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap