Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

45results about "Code conversion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

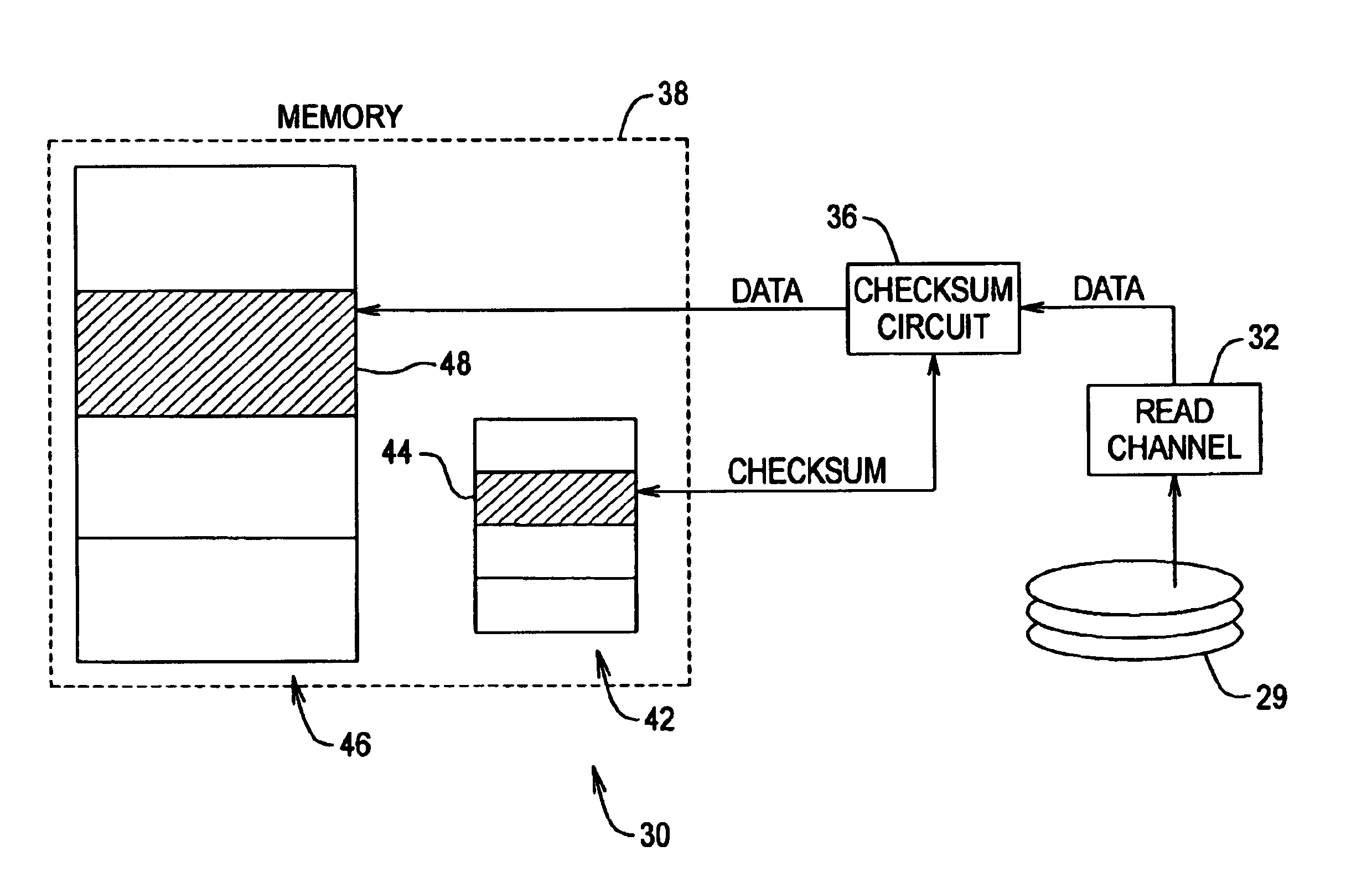

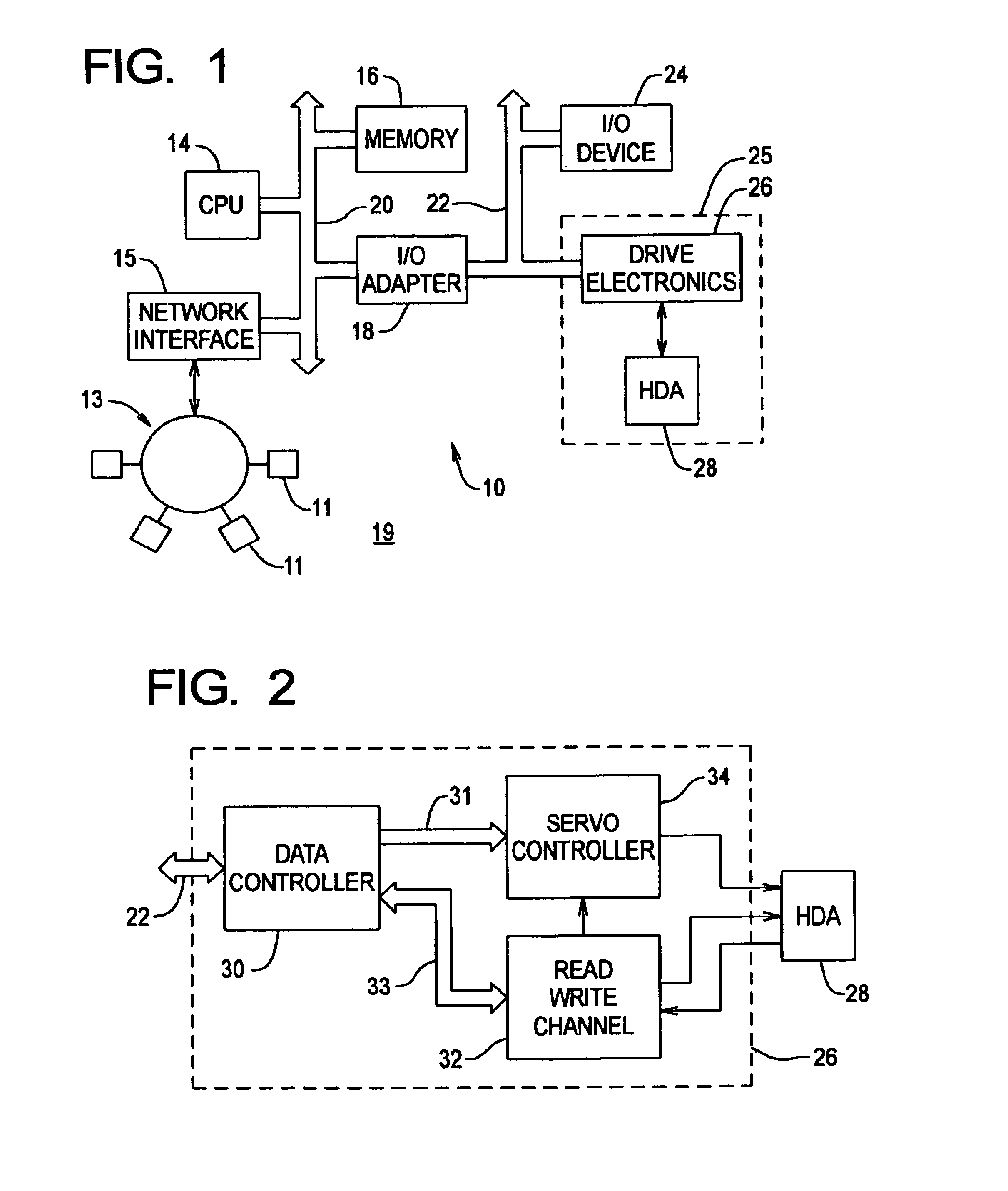

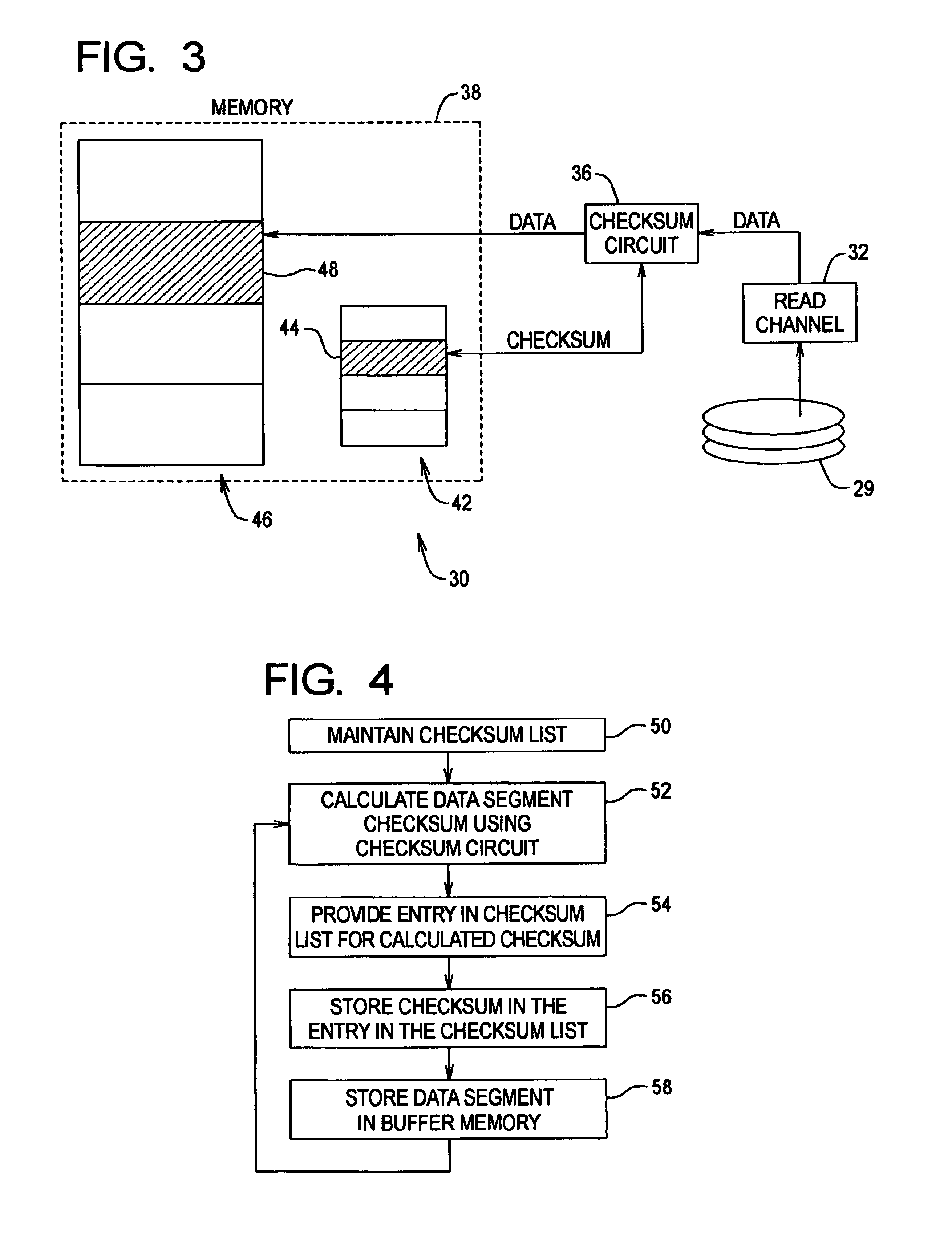

Data checksum method and apparatus

InactiveUS6964008B1Reduces memory bandwidth consumedReduce data transferCode conversionCoding detailsChecksumData store

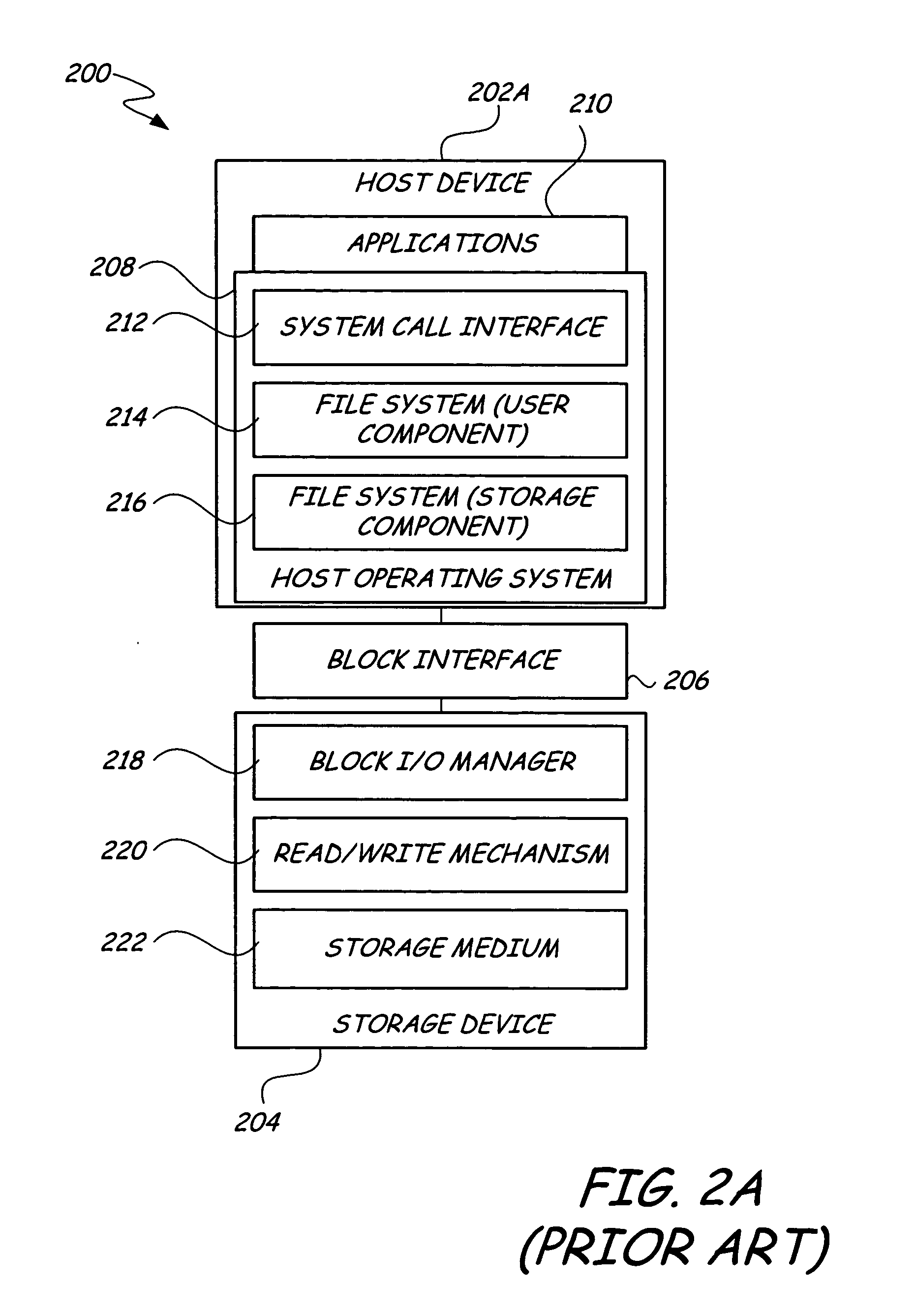

A method and apparatus for generating checksum values for data segments retrieved from a data storage device for transfer into a buffer memory, is provided. A checksum list is maintained to contain checksum values, wherein the checksum list includes a plurality of entries corresponding to the data segments stored in the buffer memory, each entry for storing a checksum value for a corresponding data segment stored in the buffer memory. For each data segment retrieved from the storage device: a checksum value is calculated for that data segment using a checksum circuit; an entry in the checksum list corresponding to that data segment is selected; the checksum value is stored in the selected entry in the checksum list; and that data segment is stored in the buffer memory. Preferably, the checksum circuit calculates the checksum for each data segment as that data segment is transferred into the buffer memory.

Owner:MAXTOR

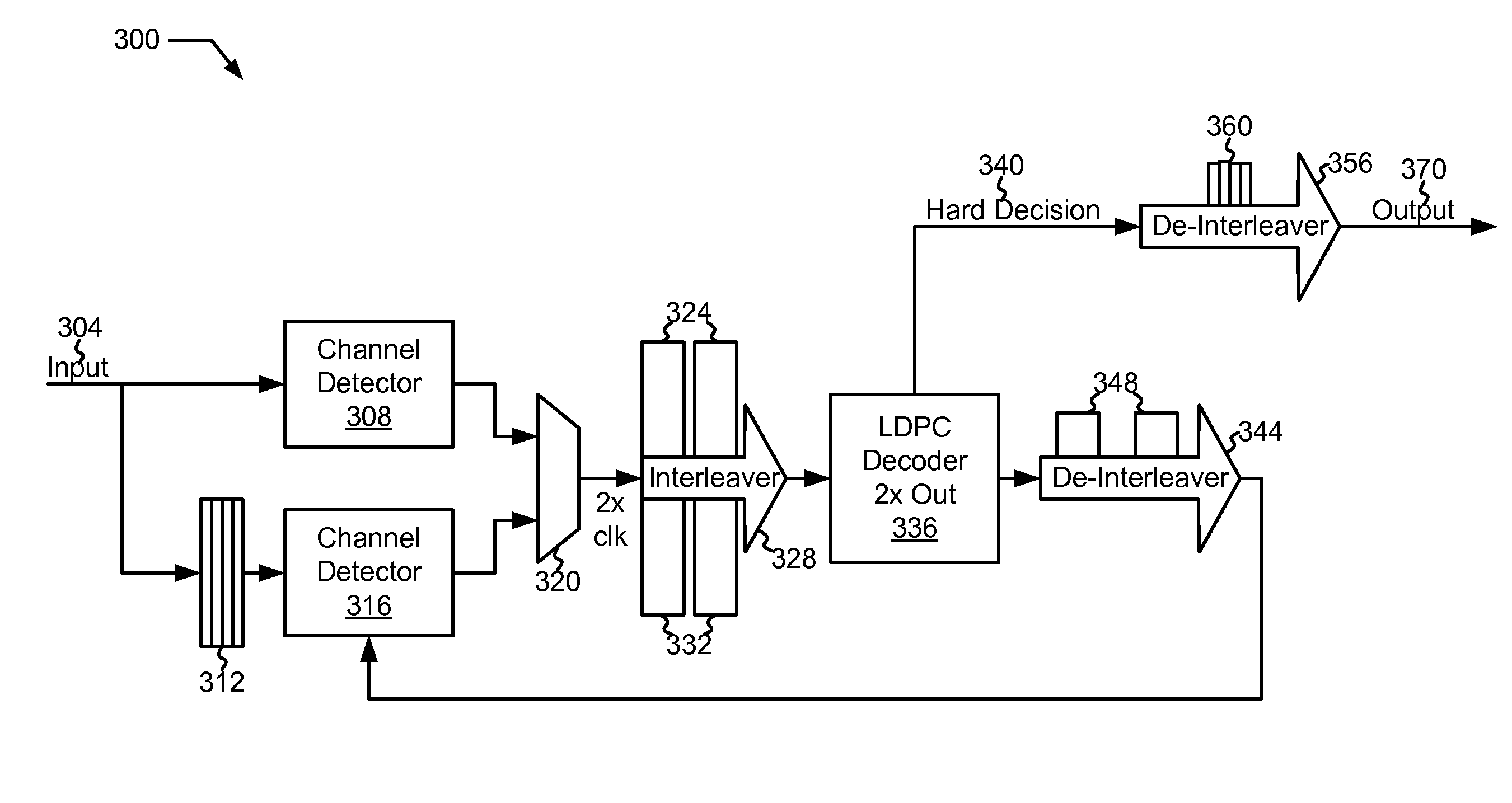

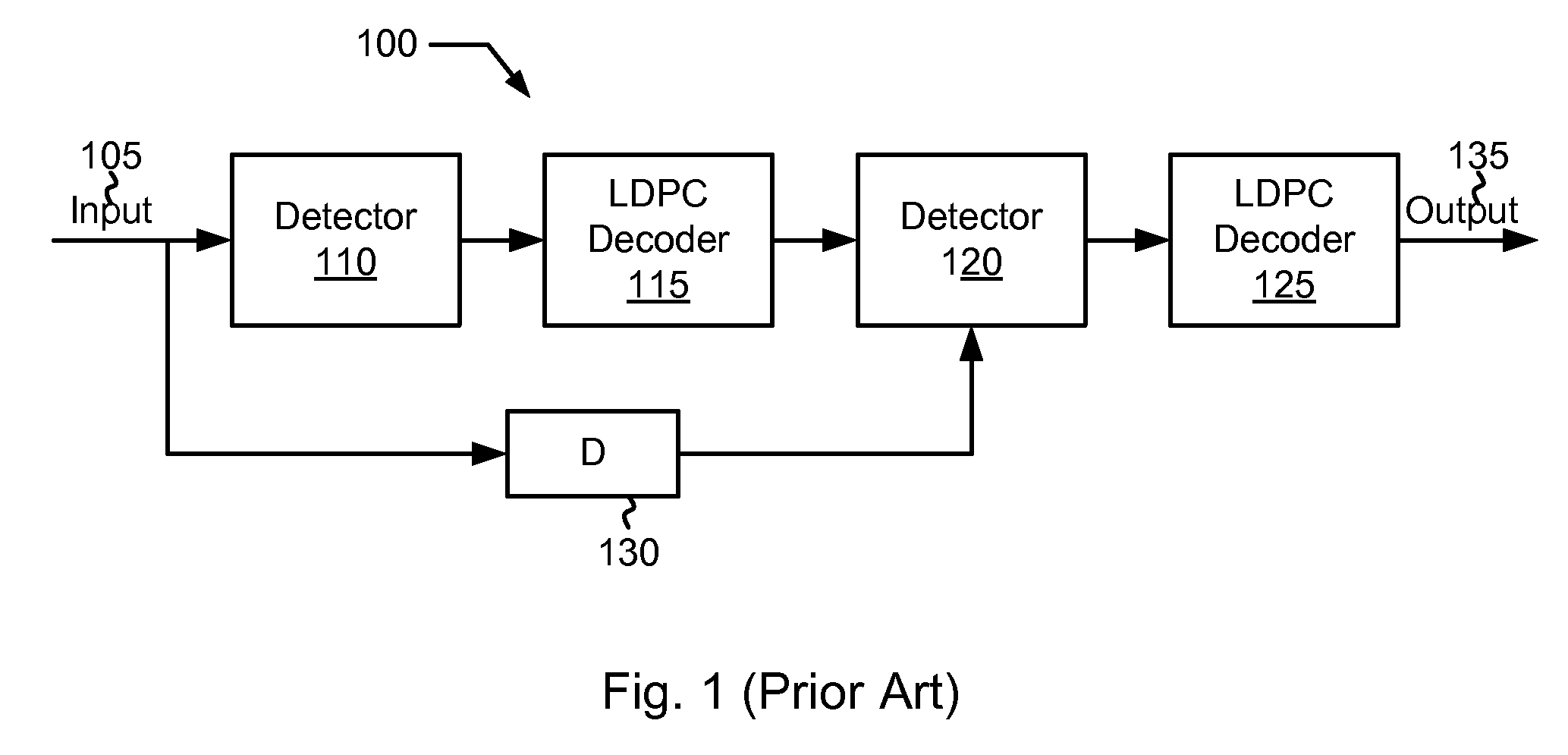

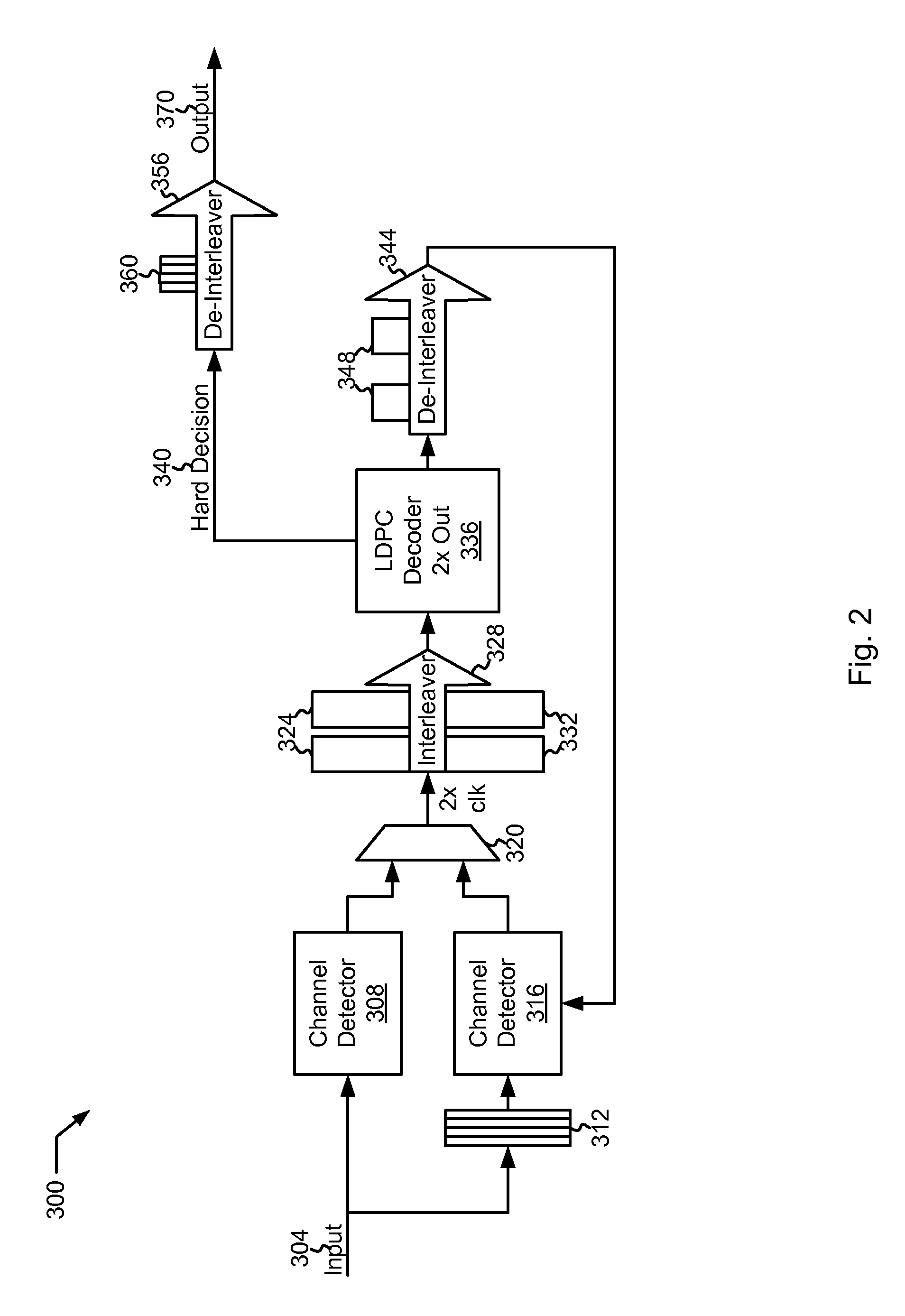

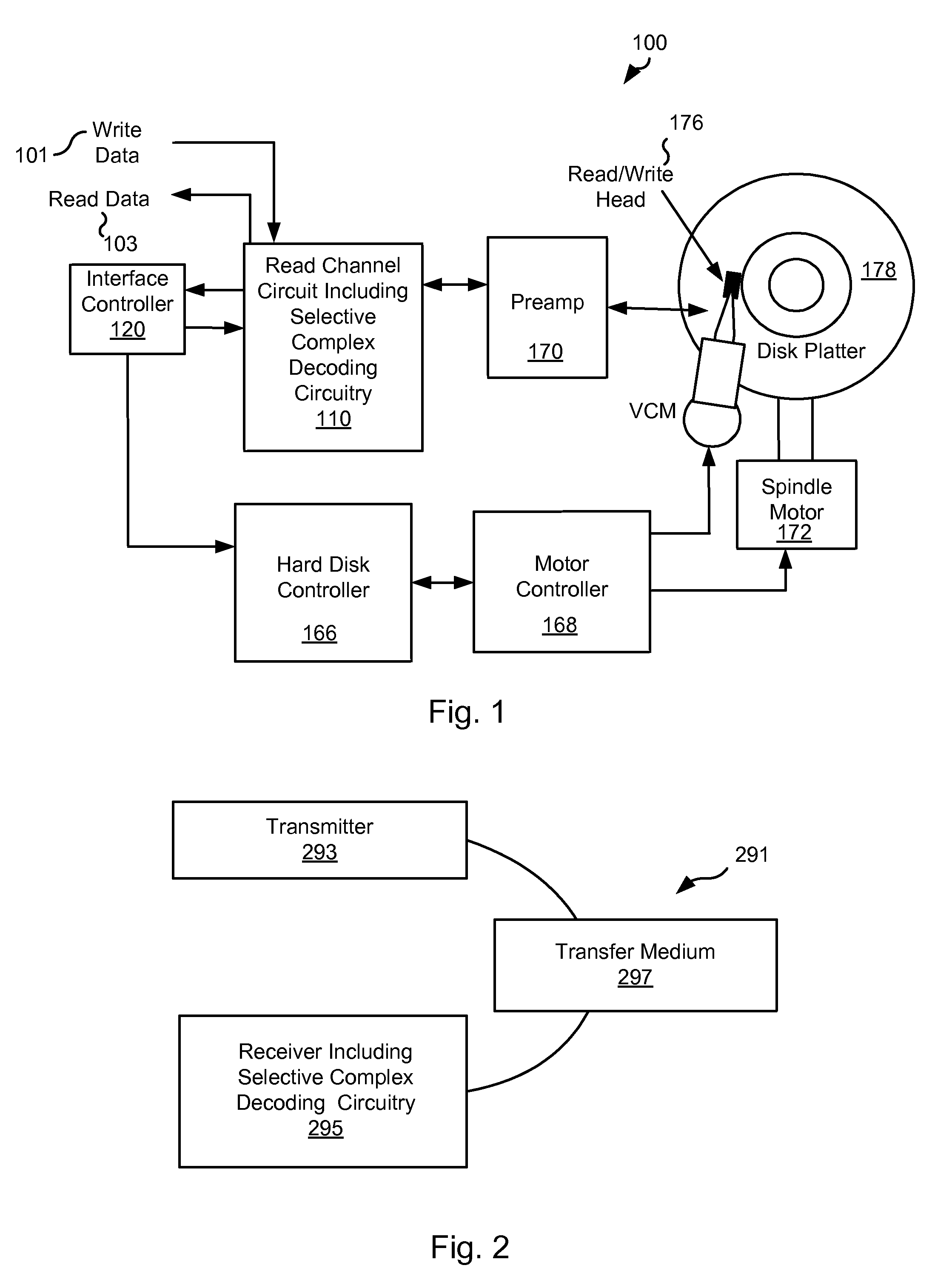

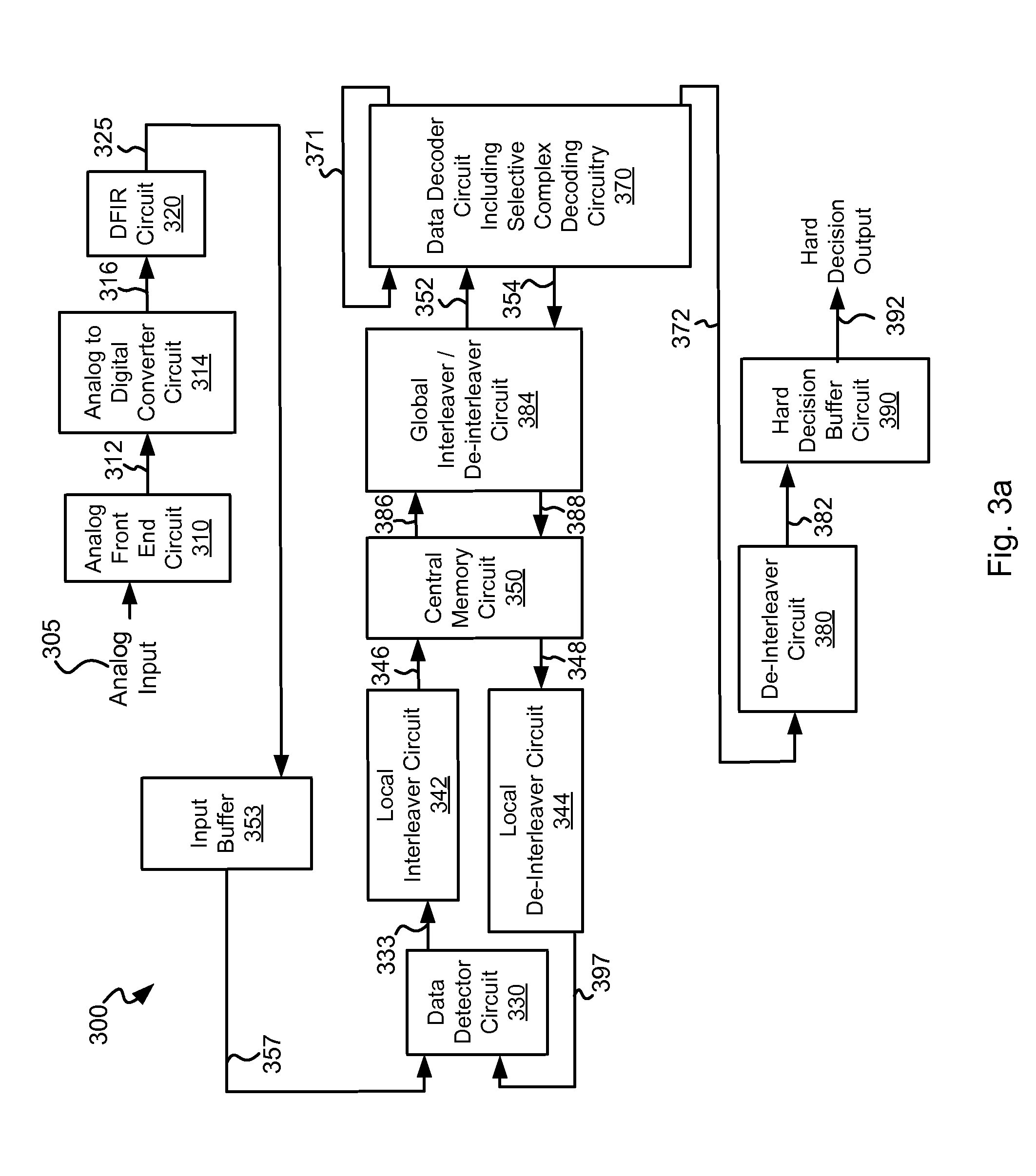

Power Reduced Queue Based Data Detection and Decoding Systems and Methods for Using Such

Owner:AVAGO TECH INT SALES PTE LTD

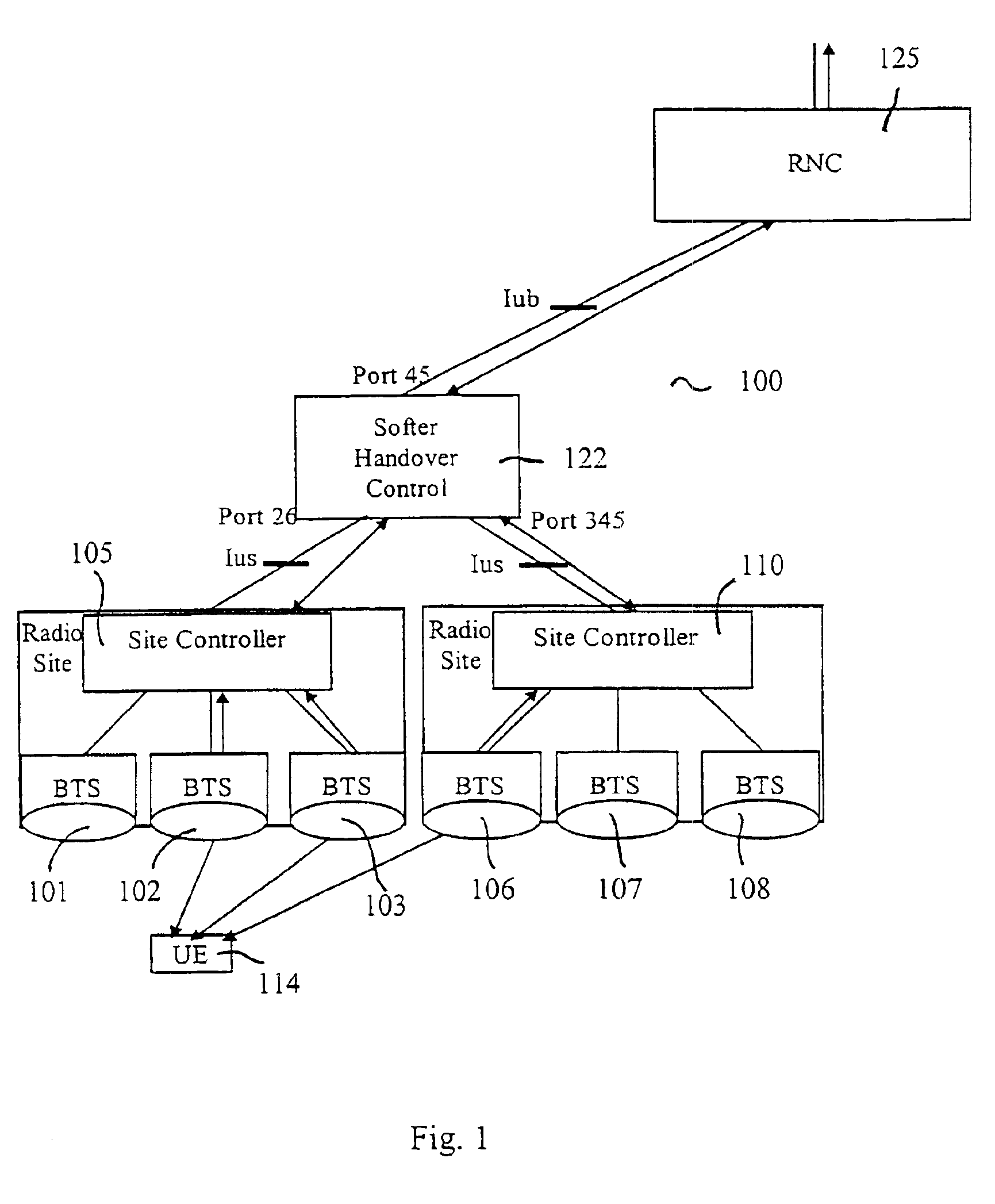

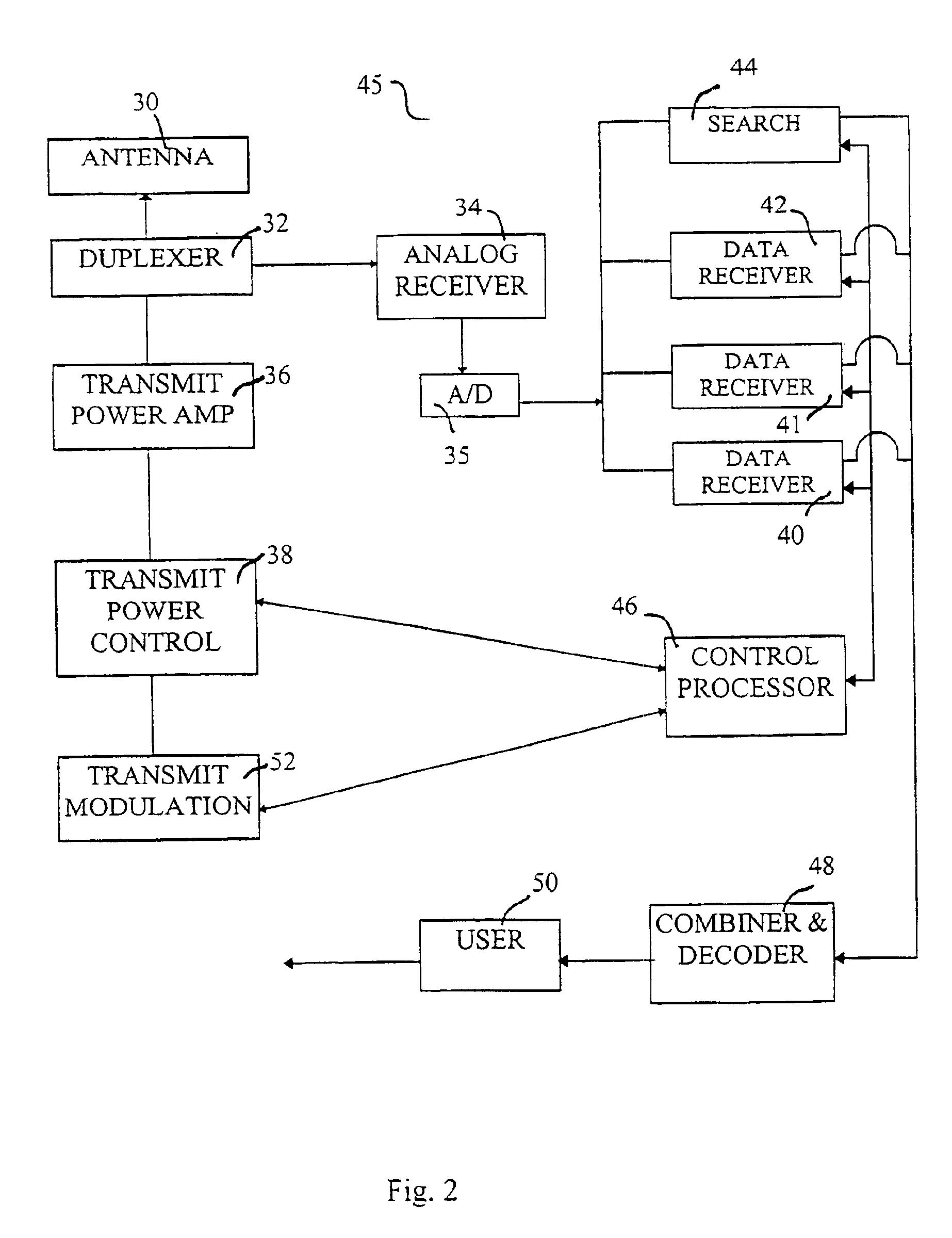

Method and apparatus for providing high quality transmissions in a telecommunications system

InactiveUS6868520B1Error correction/detection using convolutional codesCode conversionForward error correctionMobile radio

Owner:WSOU INVESTMENTS LLC

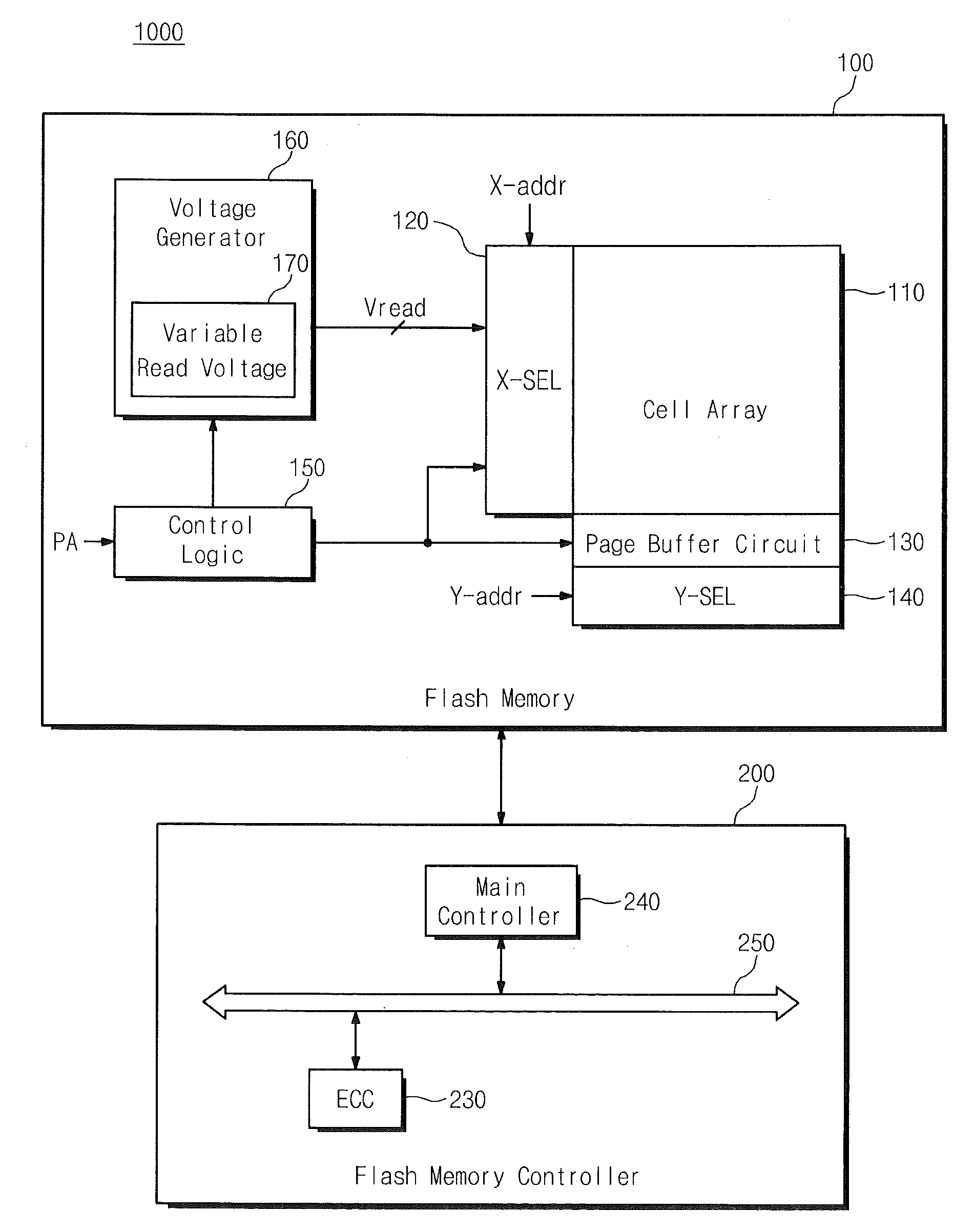

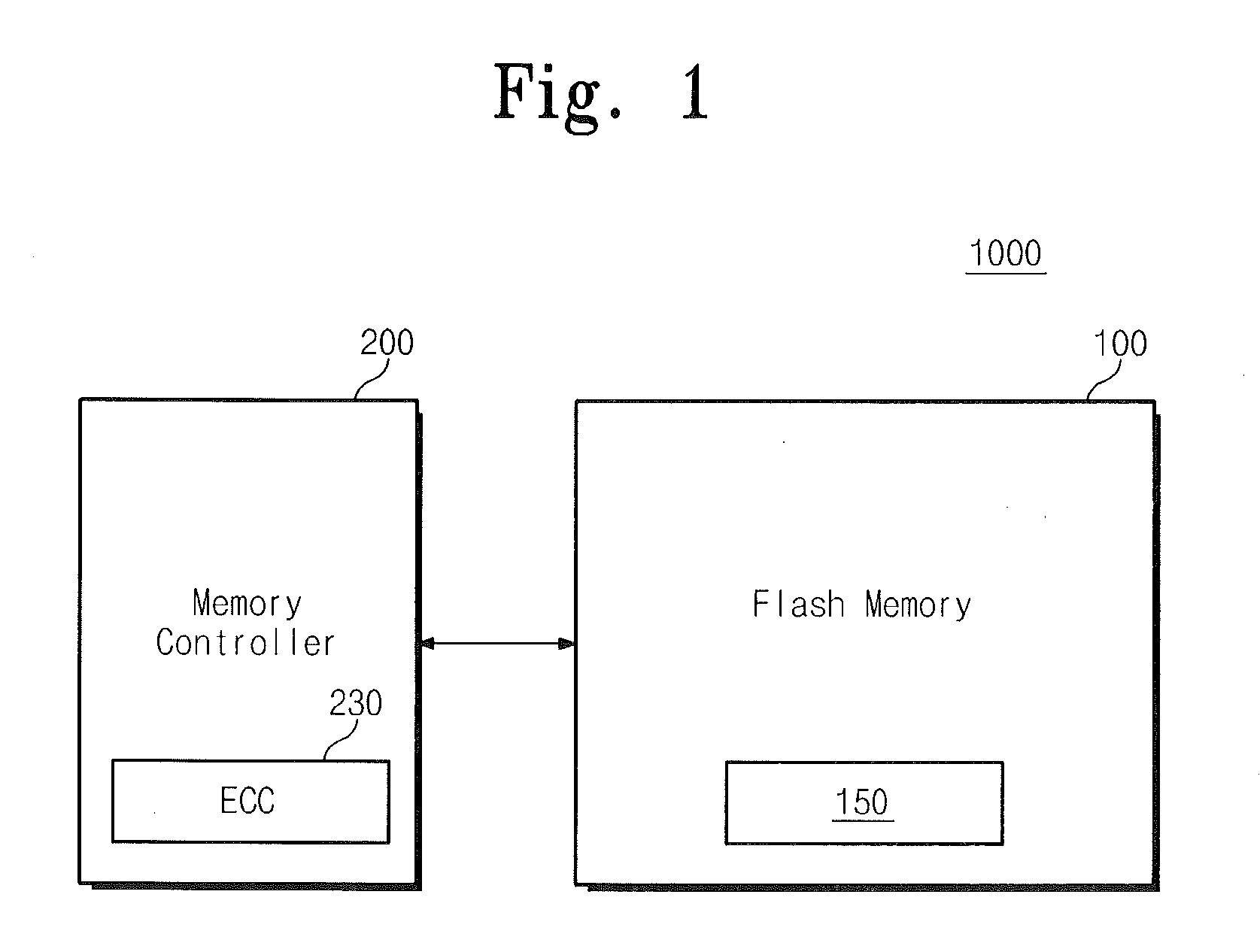

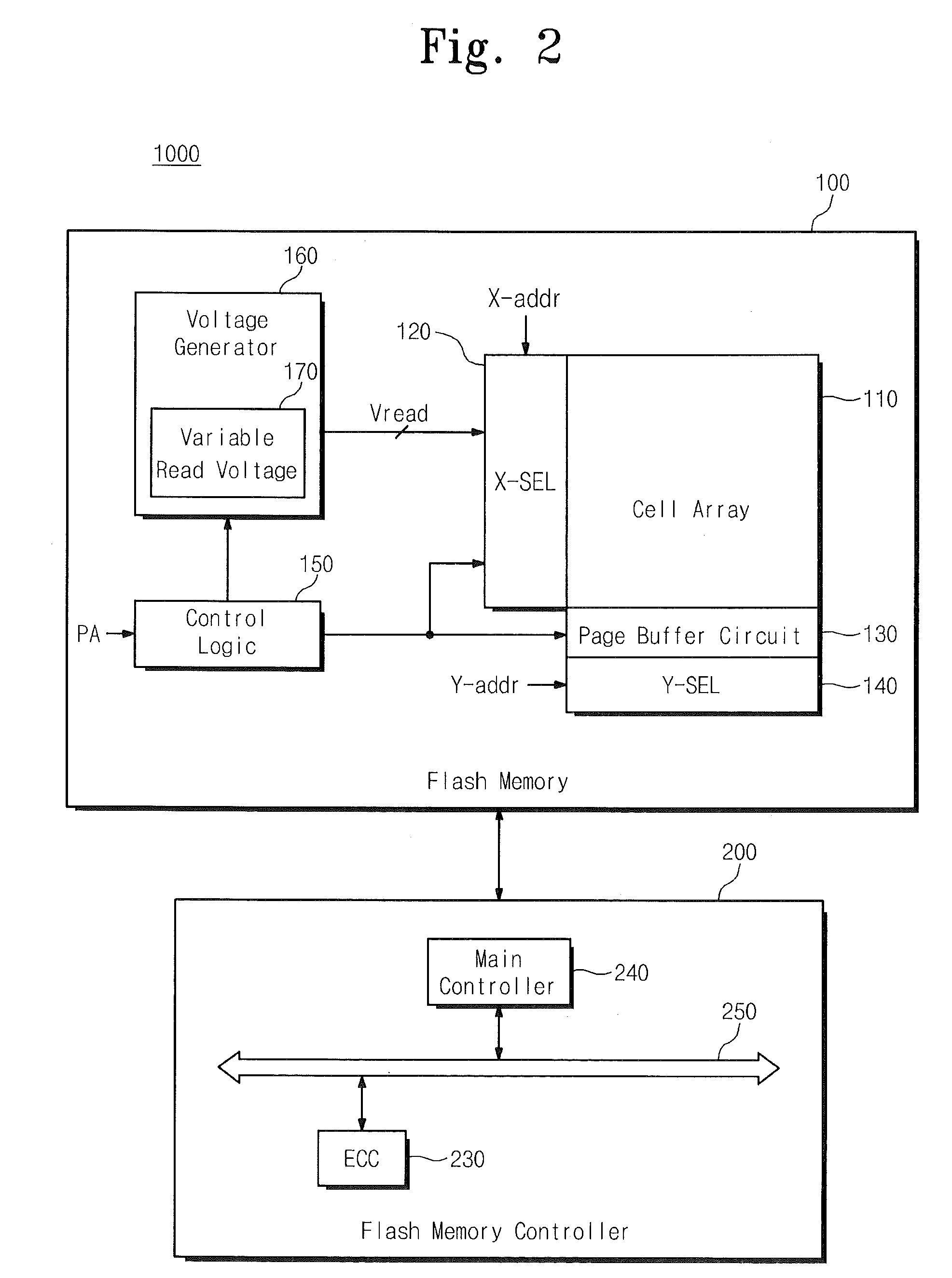

Flash Memory Devices Having Multi-Bit Memory Cells Therein with Improved Read Reliability

ActiveUS20110197015A1Increase in chip sizeEnhanced informationCode conversionRead-only memoriesData valueIntegrated circuit

Owner:SAMSUNG ELECTRONICS CO LTD

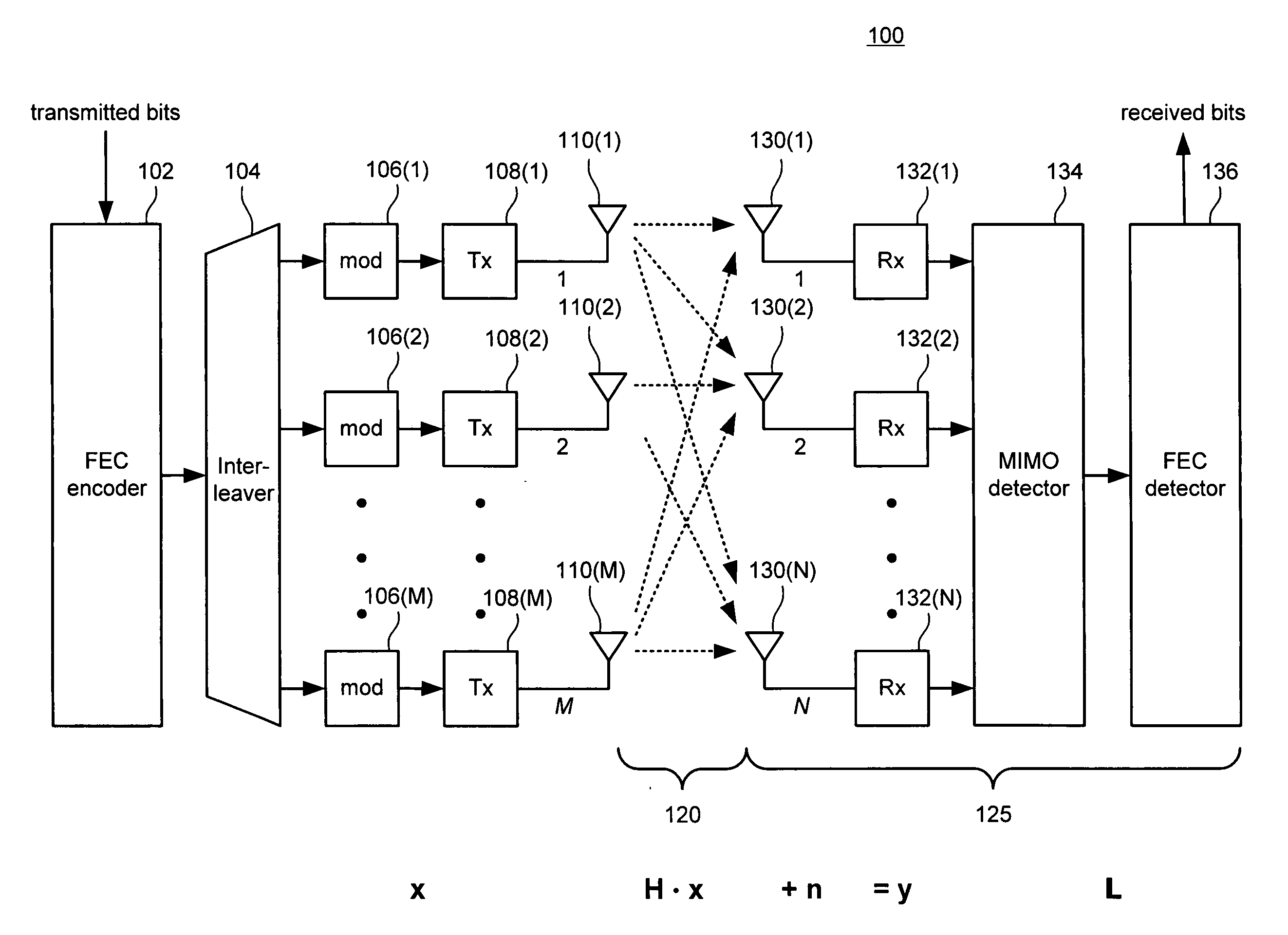

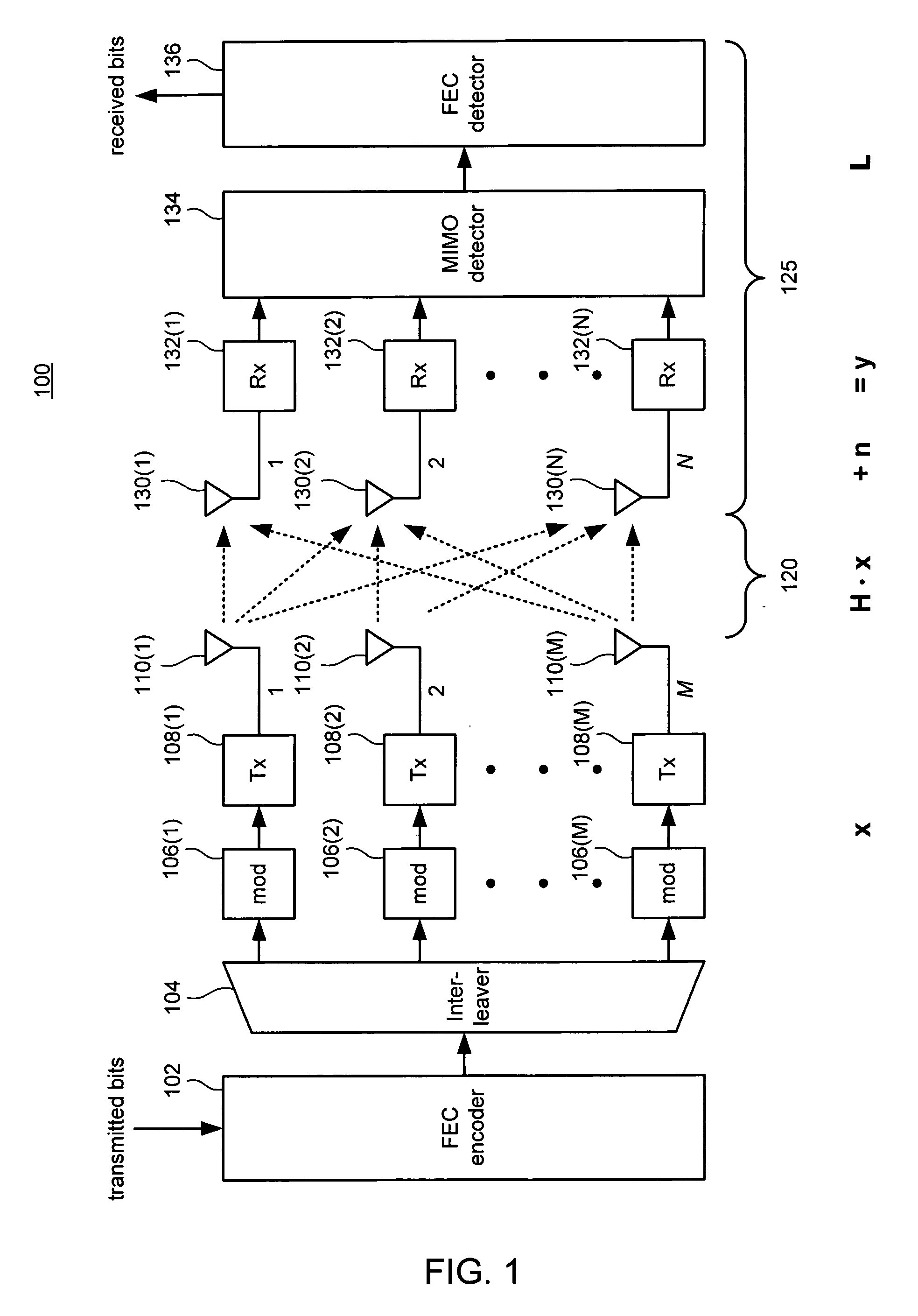

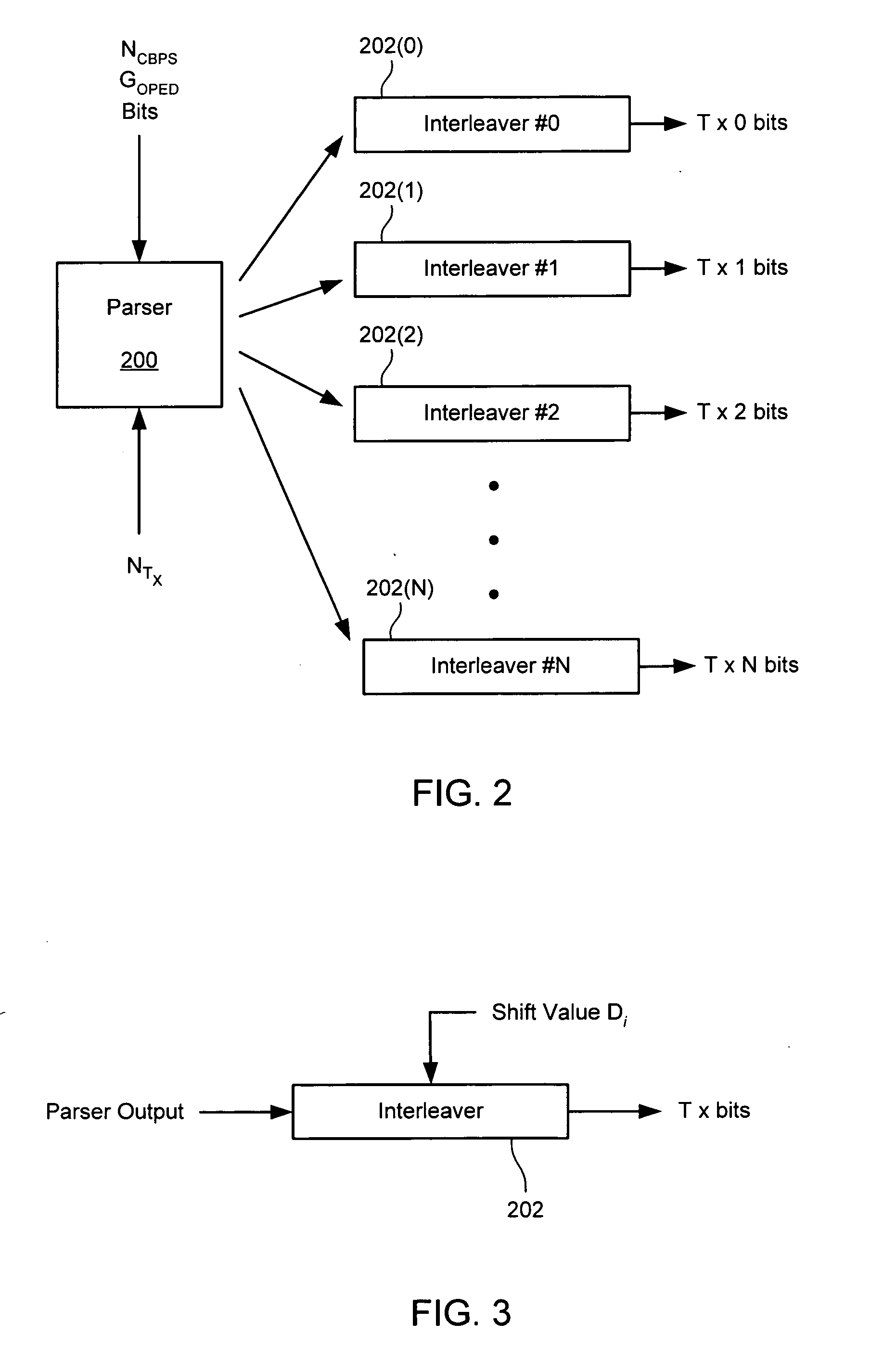

Advanced MIMO interleaving

Owner:QUALCOMM INC

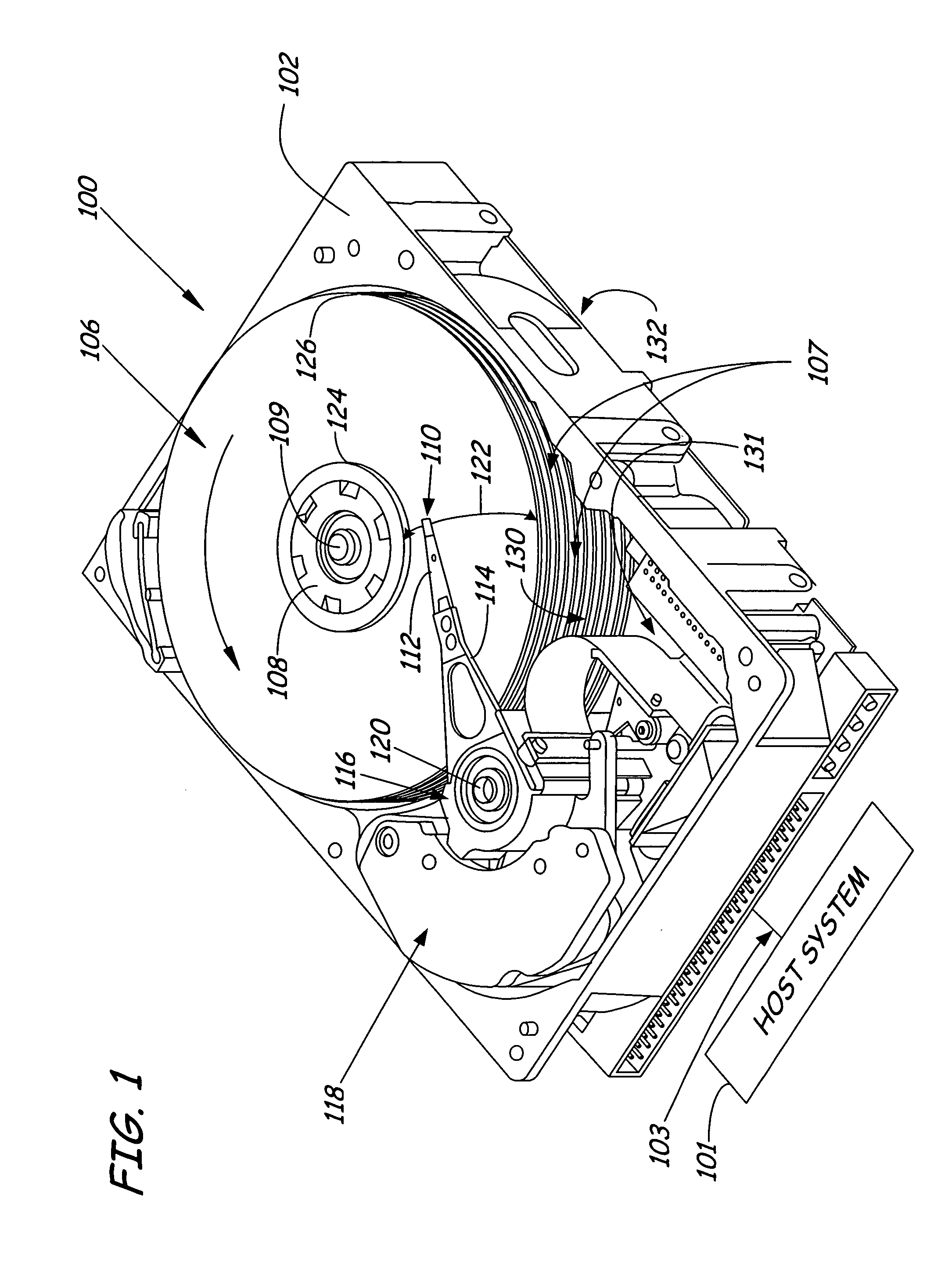

Redundancy for storage data structures

Owner:SEAGATE TECH LLC

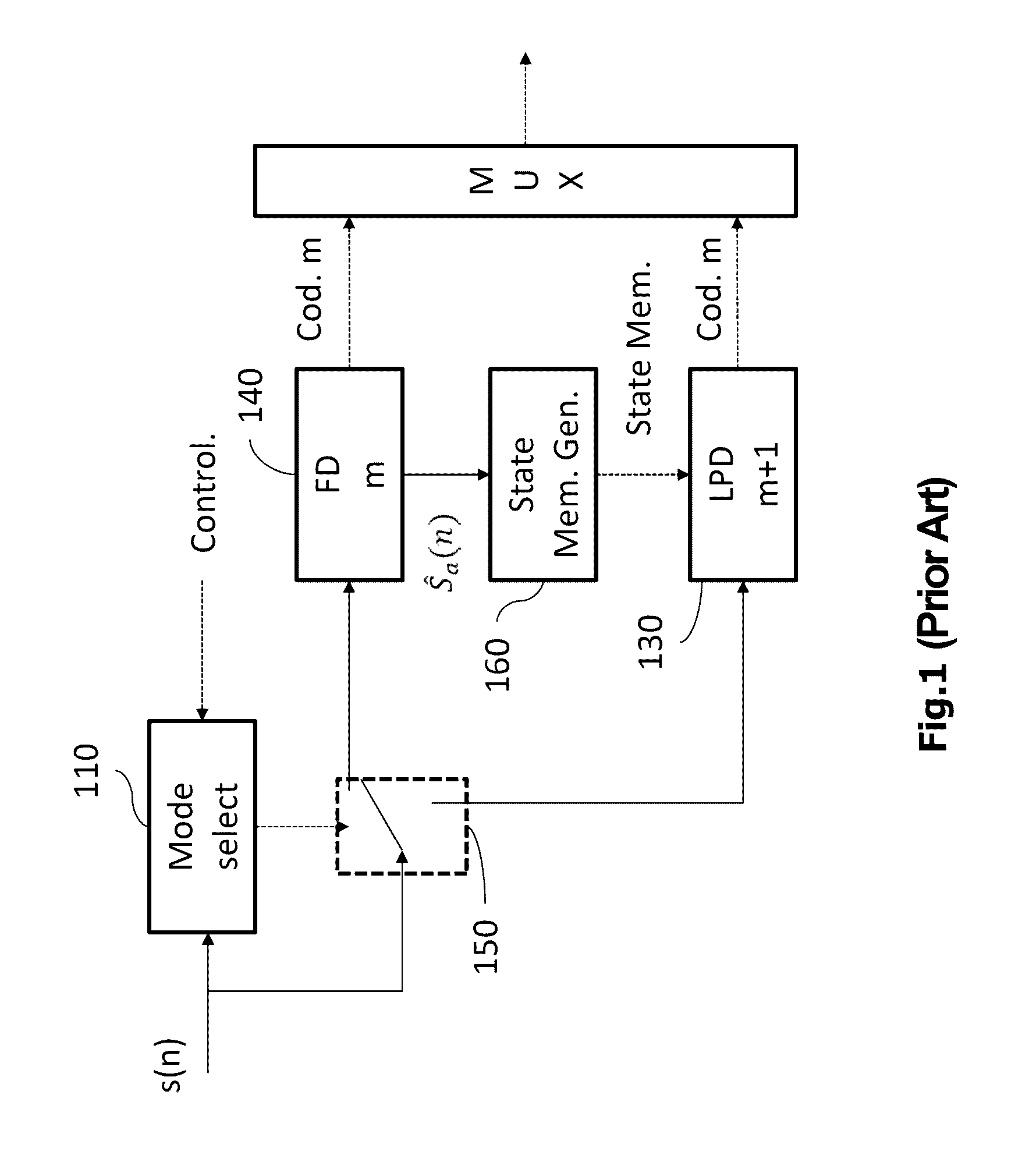

Device and Method for Graduated Encoding of a Multichannel Audio Signal Based on a Principal Component Analysis

Owner:FRANCE TELECOM SA

Acceleration of bitstream decoding

ActiveUS7286066B1Improve performanceReduce the number of executionsCode conversionParallel computingExecution unit

Described are methods and systems for variable length decoding. A first execution unit executes a first single instruction that optionally reverses the order of bits in an encoded bitstream. A second execution unit executes a second single instruction that extracts a specified number of bits from the bitstream produced by the first execution unit. A third execution unit executes a third single instruction that identifies a number of consecutive zero bit values at the head of the bitstream produced by the first execution unit. The outputs of the first, second and third execution units are used in a process that decodes the encoded bitstream.

Owner:NVIDIA CORP

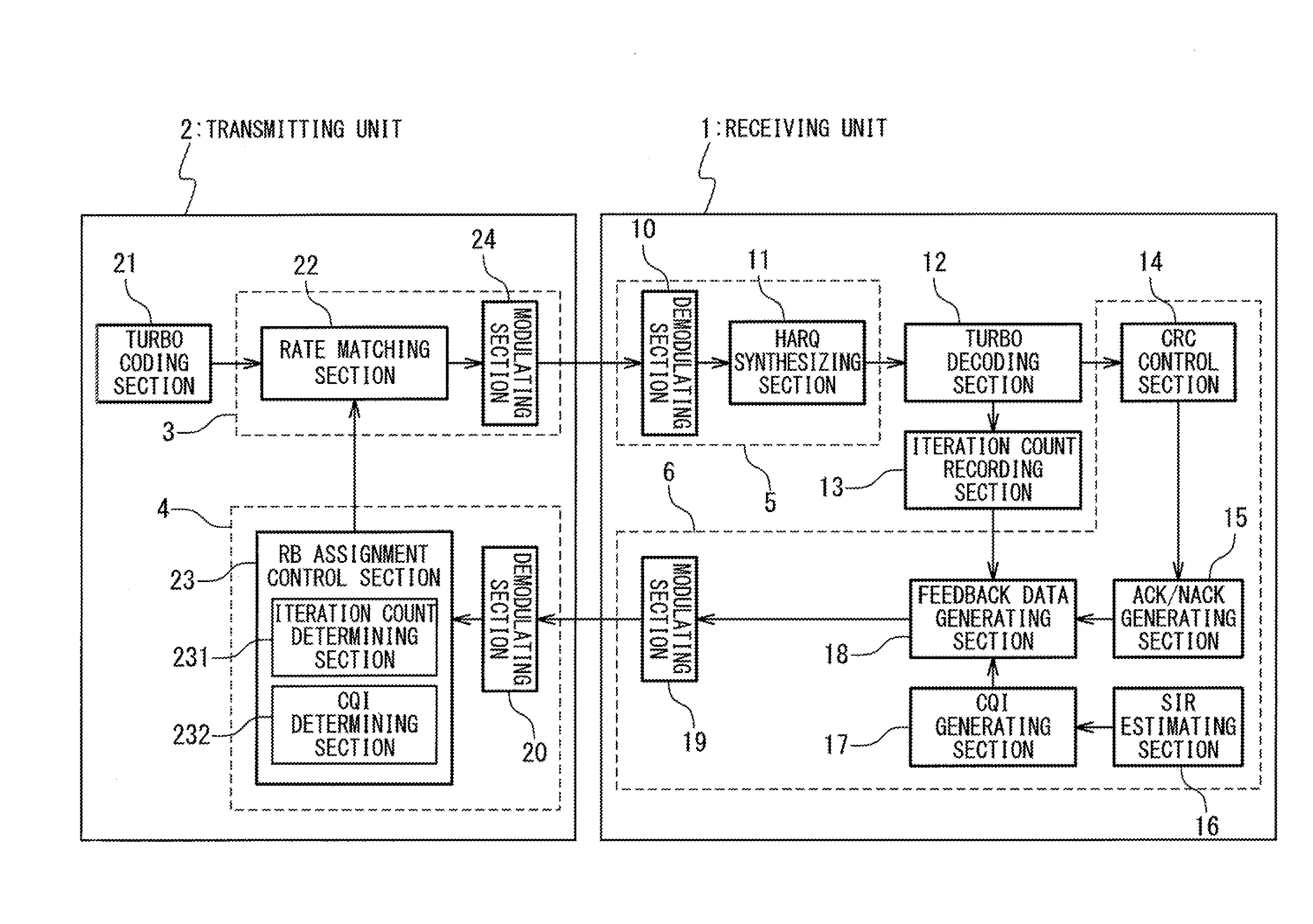

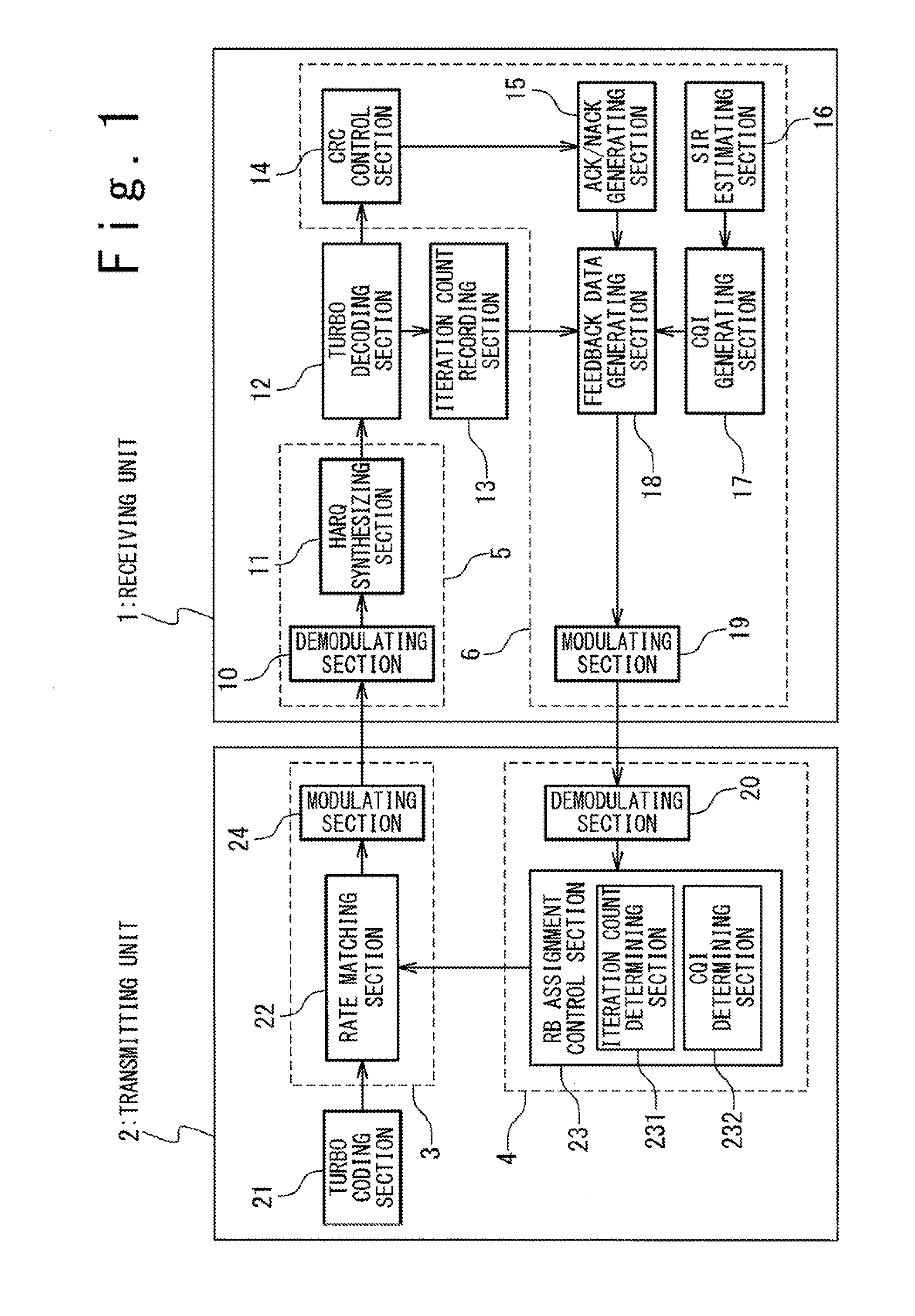

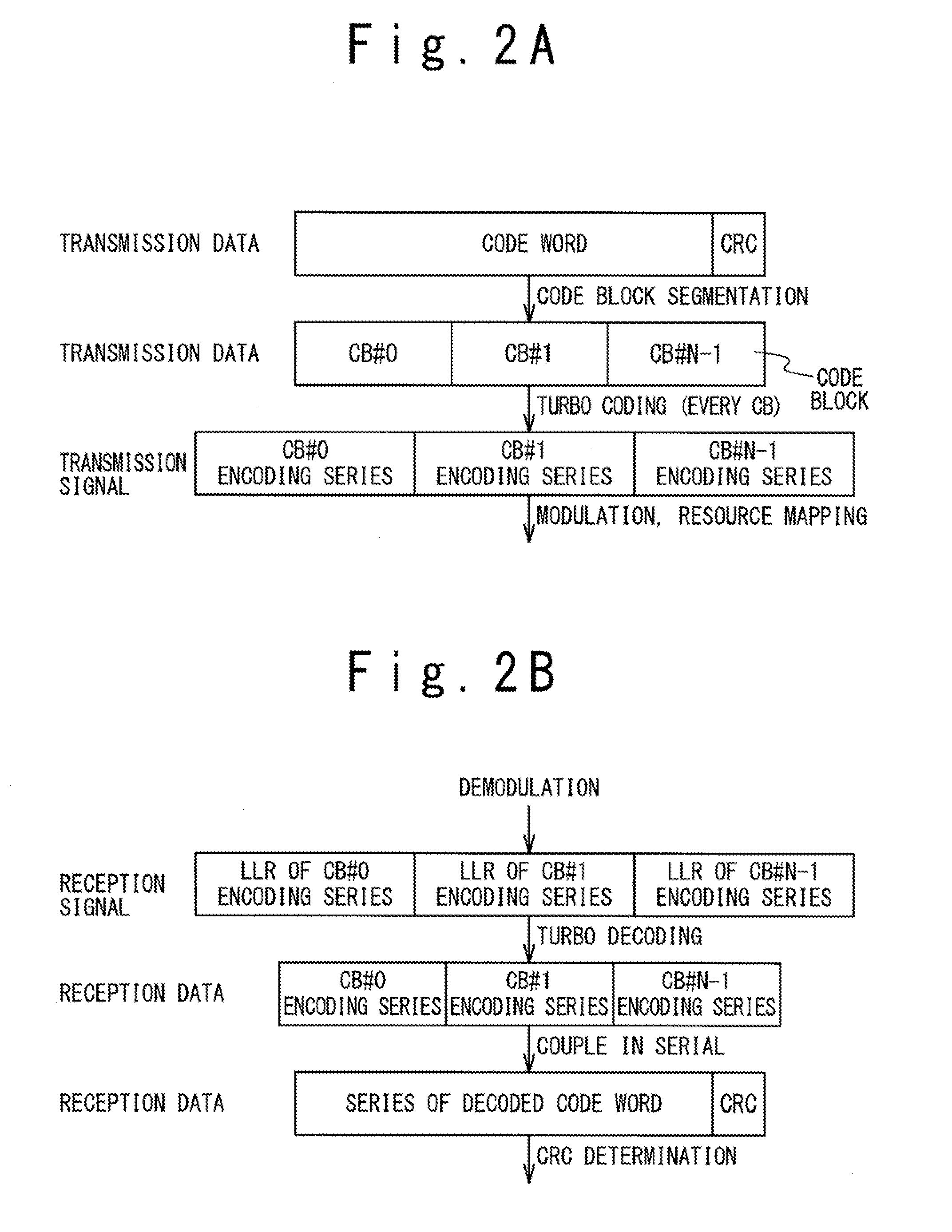

Multicarrier mobile communication system

ActiveUS20110004799A1Retransmission can be increasedRetransmission efficiency is not goodError prevention/detection by using return channelCode conversionCoding blockComputer hardware

Owner:NEC CORP

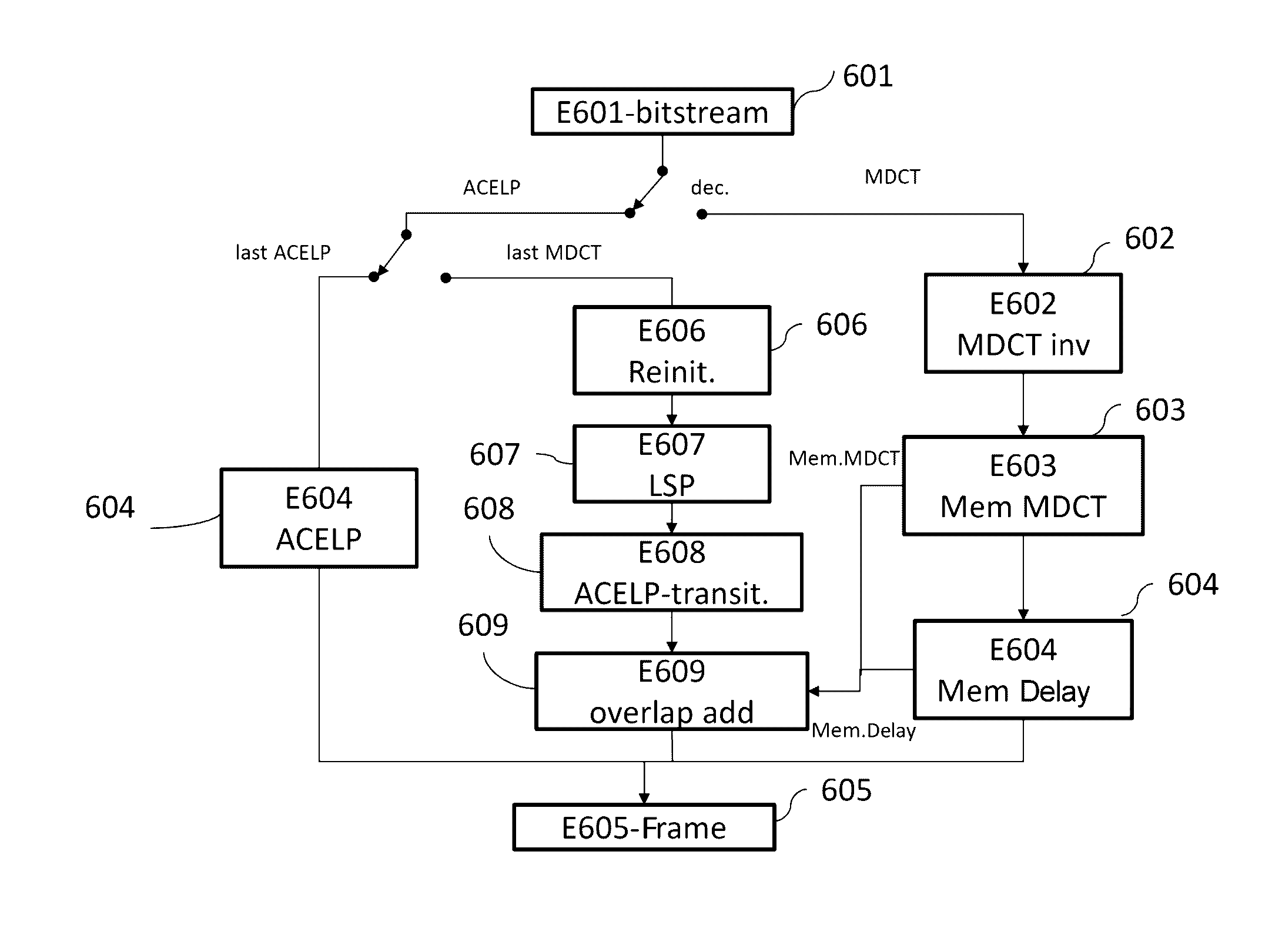

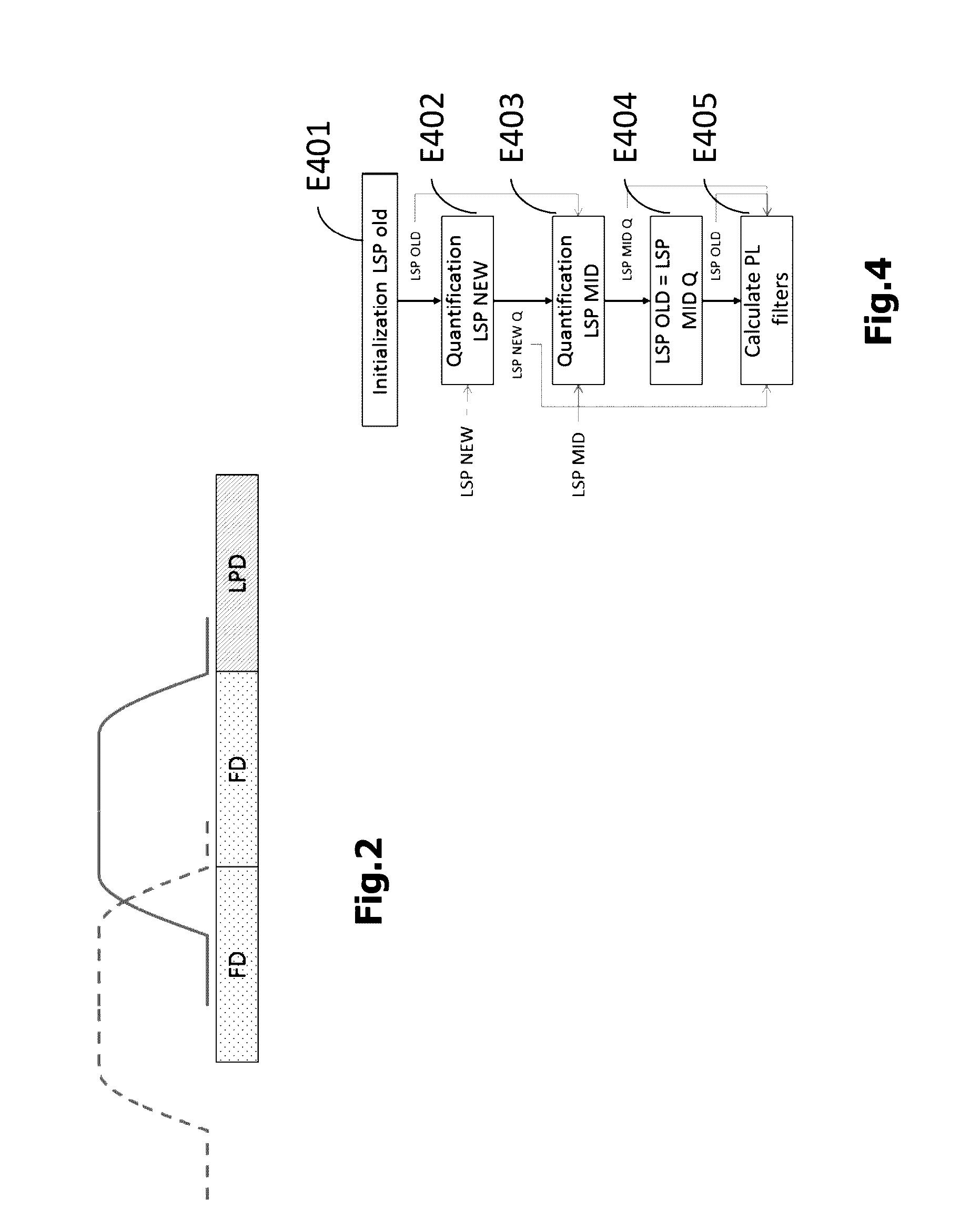

Transition from a transform coding/decoding to a predictive coding/decoding

ActiveUS20160293173A1Reduce complexityEasy to implementCode conversionSpeech analysisLinear predictive codingDigital audio signals

Owner:ORANGE SA (FR)

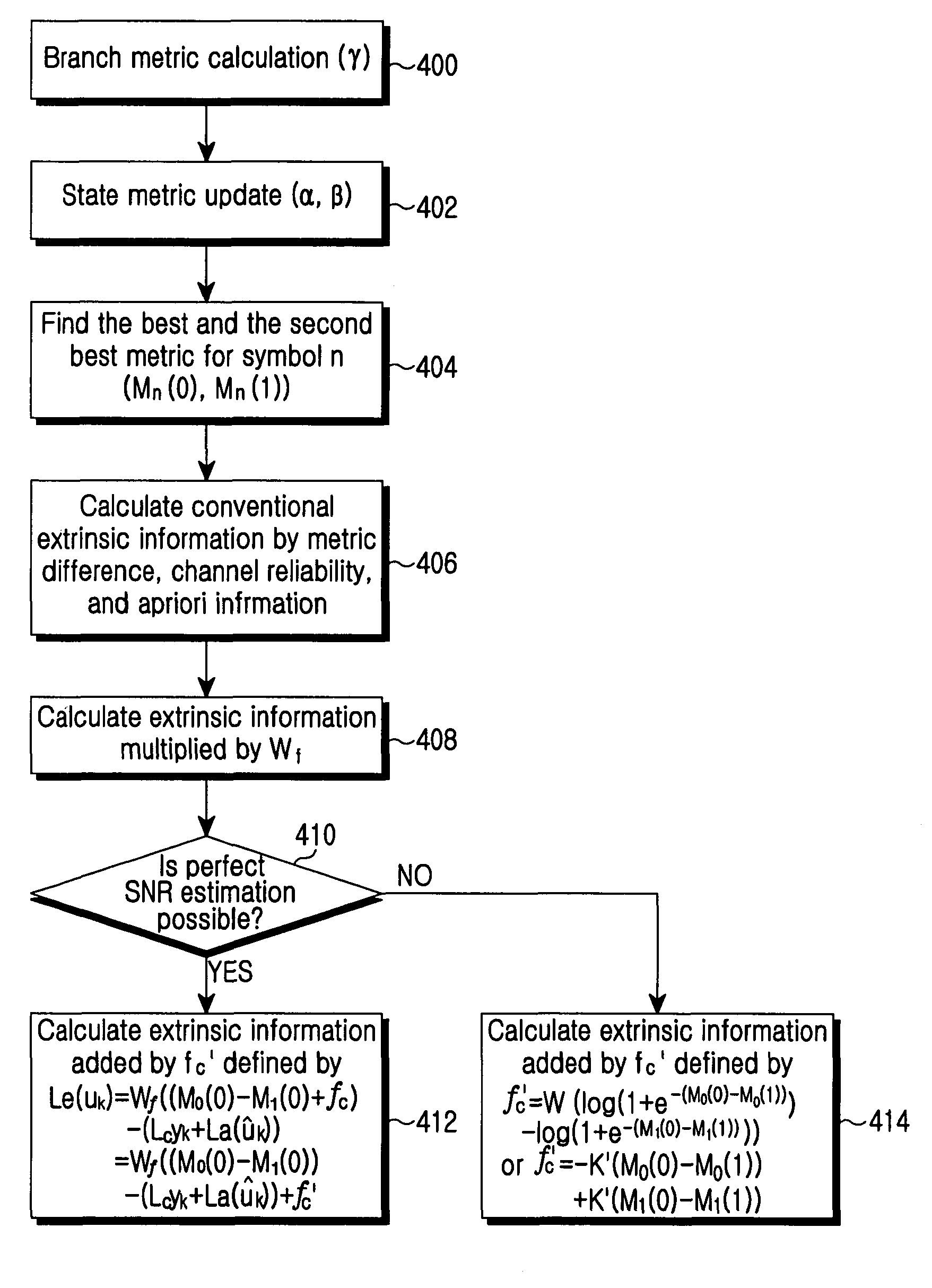

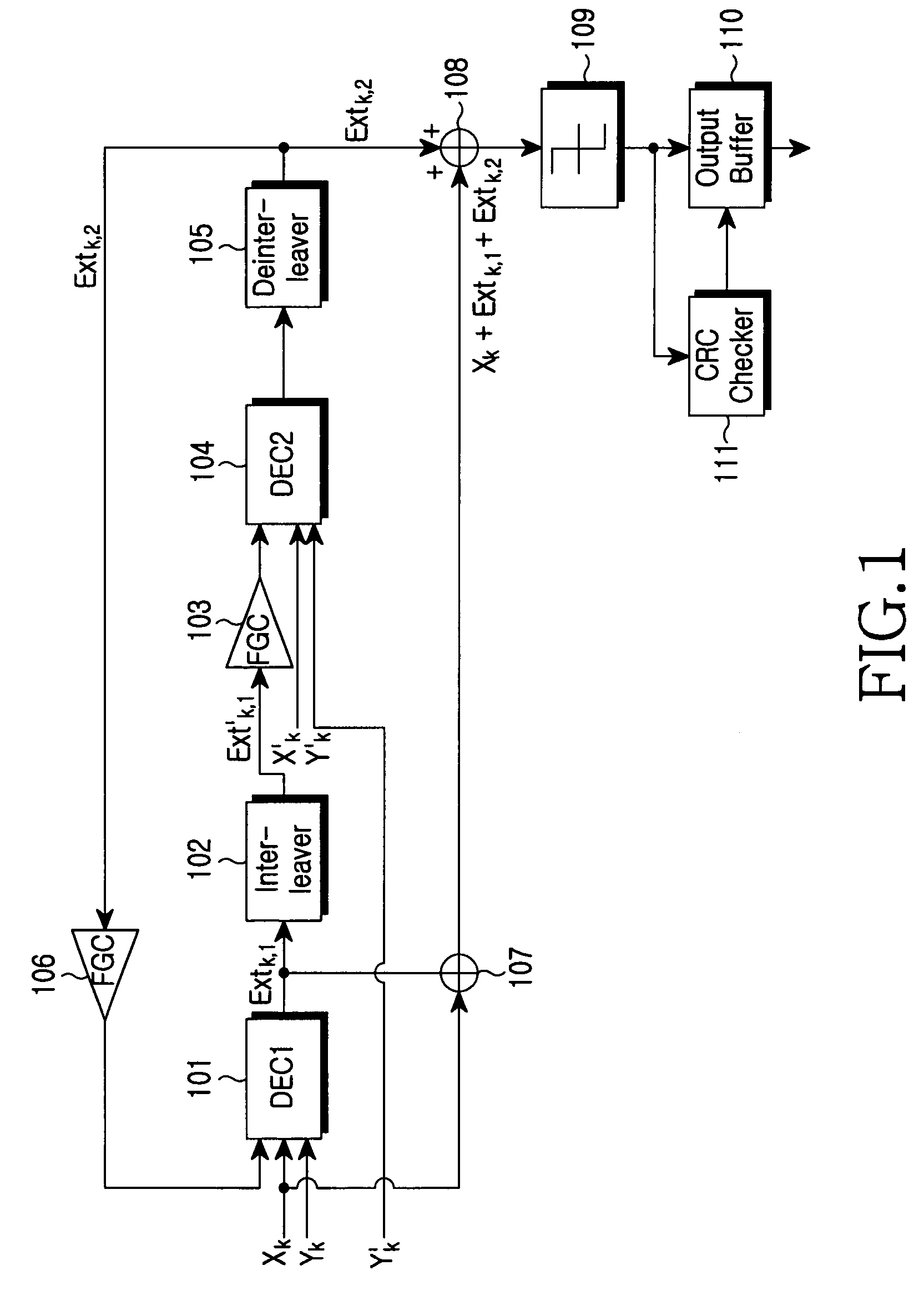

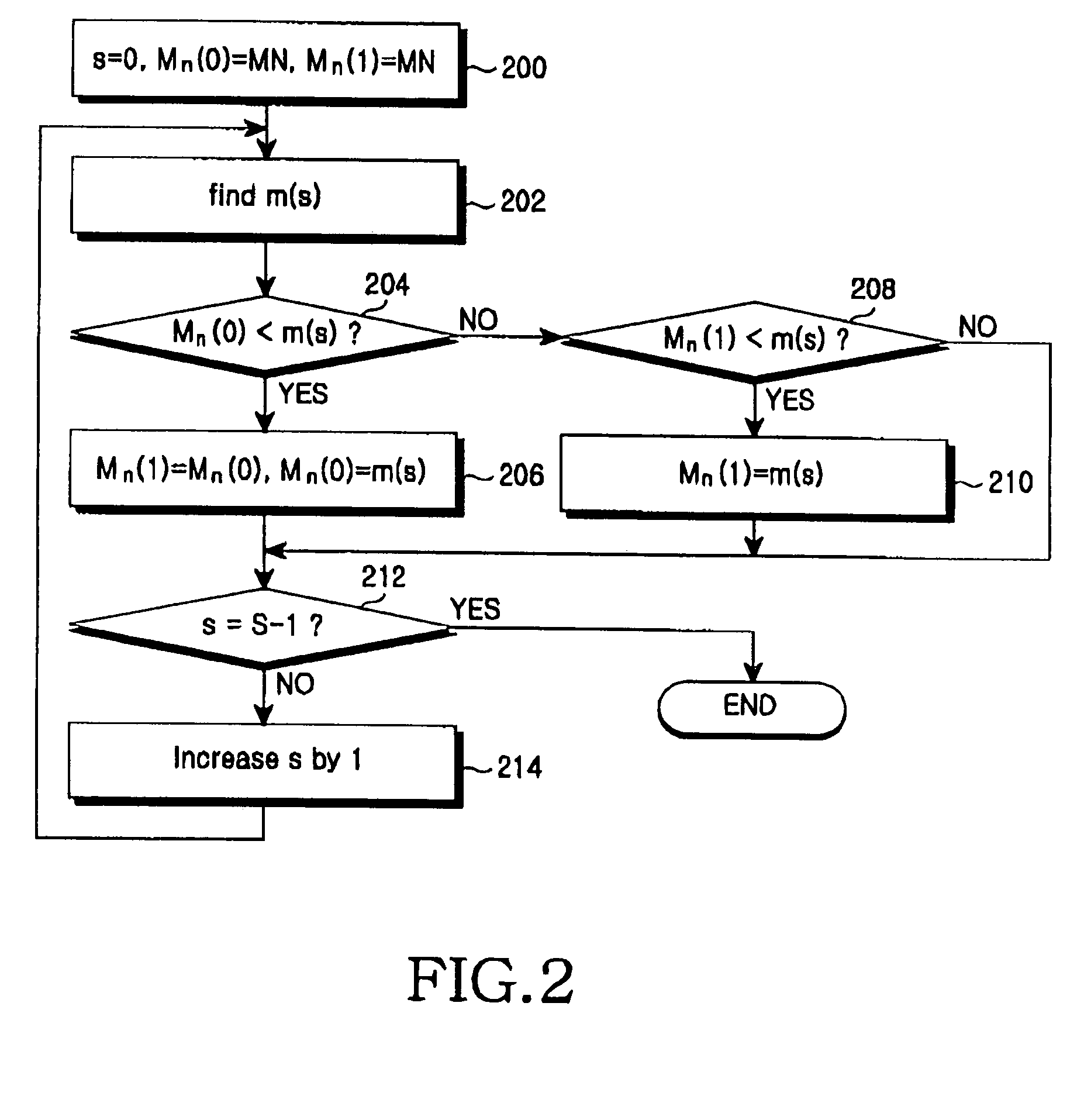

Apparatus and method for reducing Bit Error Rates (BER) and Frame Error Rates (FER) using turbo decoding in a digital communication system

ActiveUS7032156B2Improve performanceLess complexData representation error detection/correctionError preventionCommunications systemBinary multiplier

Owner:SAMSUNG ELECTRONICS CO LTD

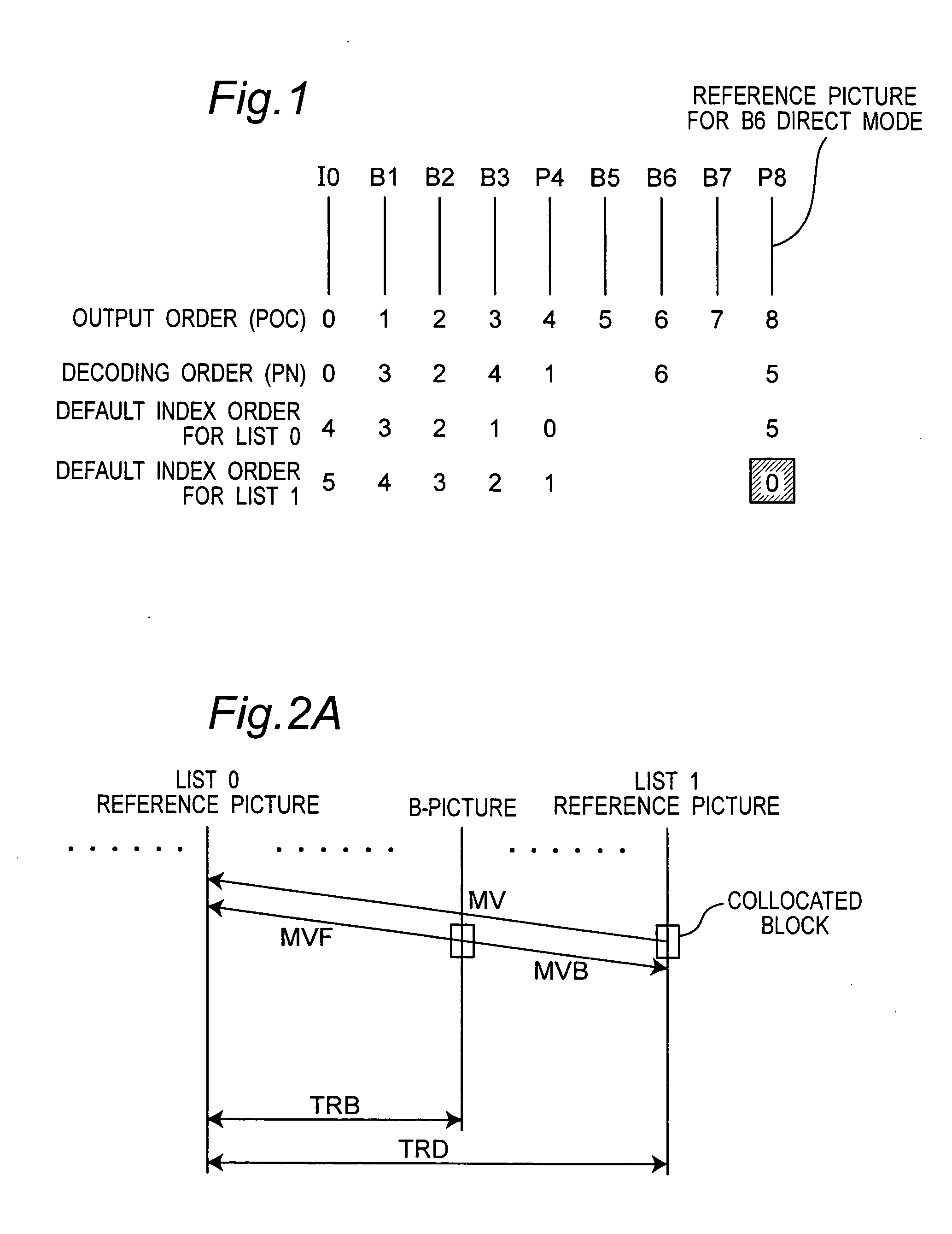

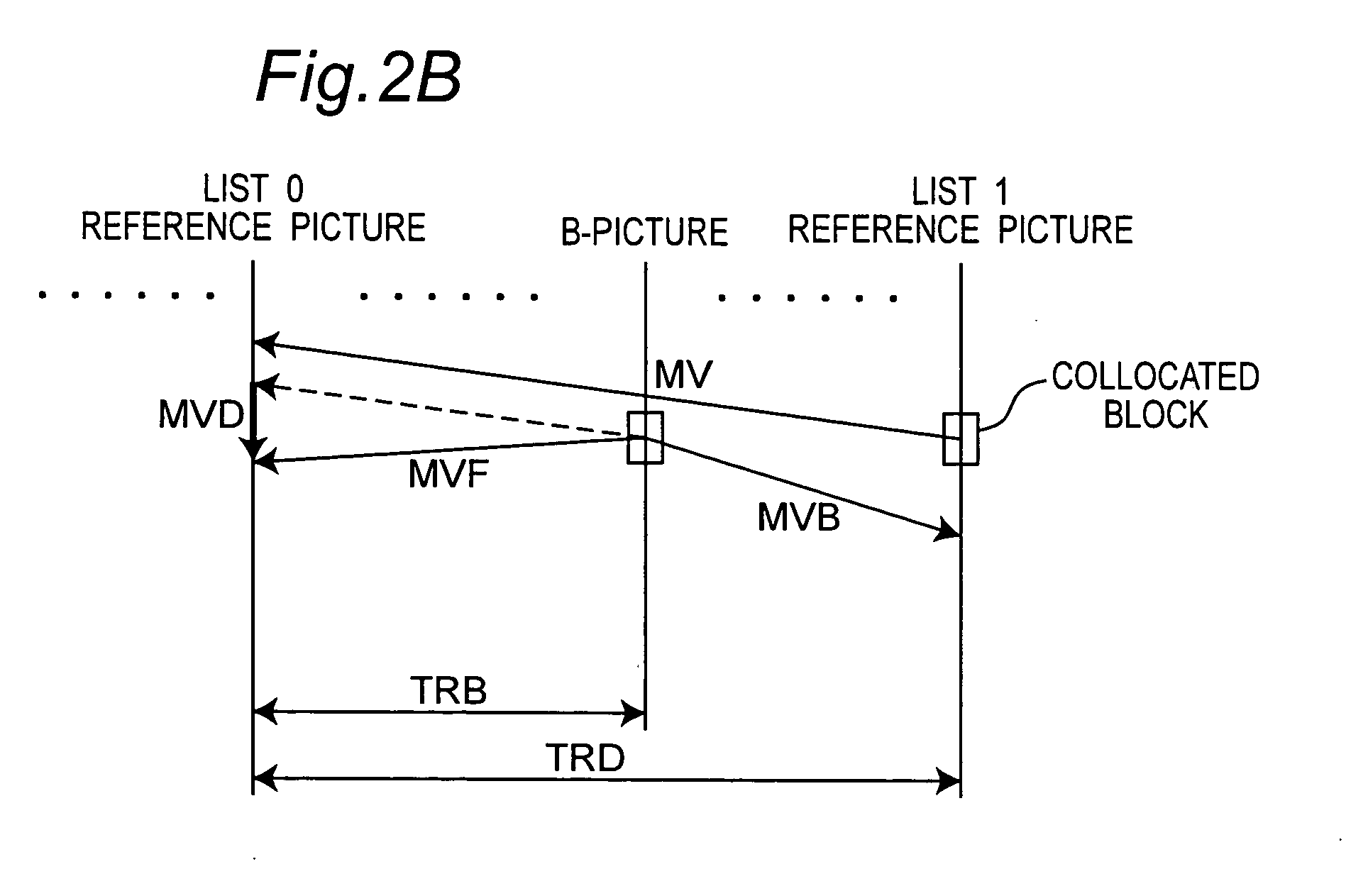

Method for calculating a direct mode motion vector for a bi-directionally predictive-picture

InactiveUS20070019731A1Simpler and few operationReduces number of operation operationalColor television with pulse code modulationColor television with bandwidth reductionMotion vectorComputer science

Owner:PANASONIC CORP

Techniques for operating semiconductor devices

Owner:IBM CORP

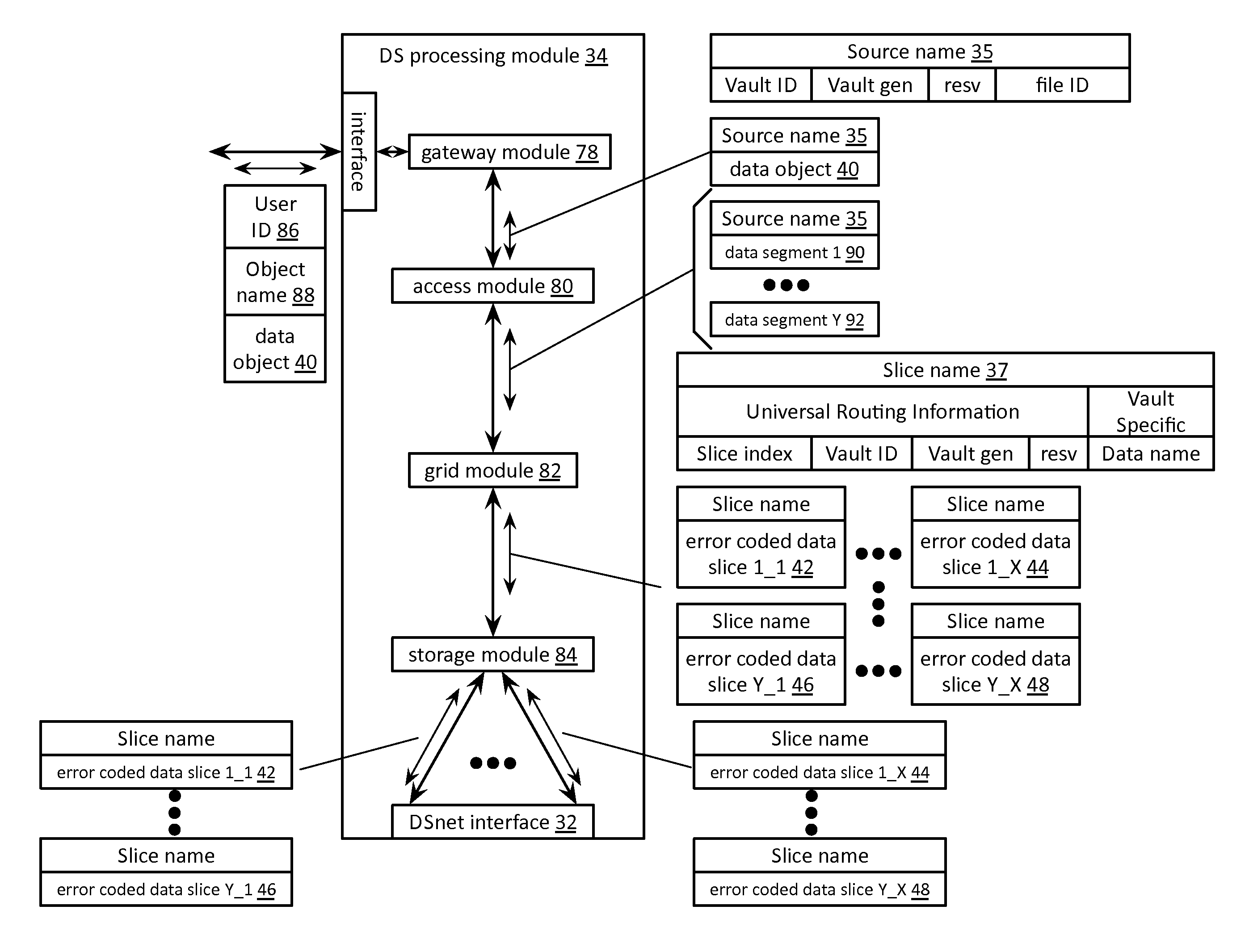

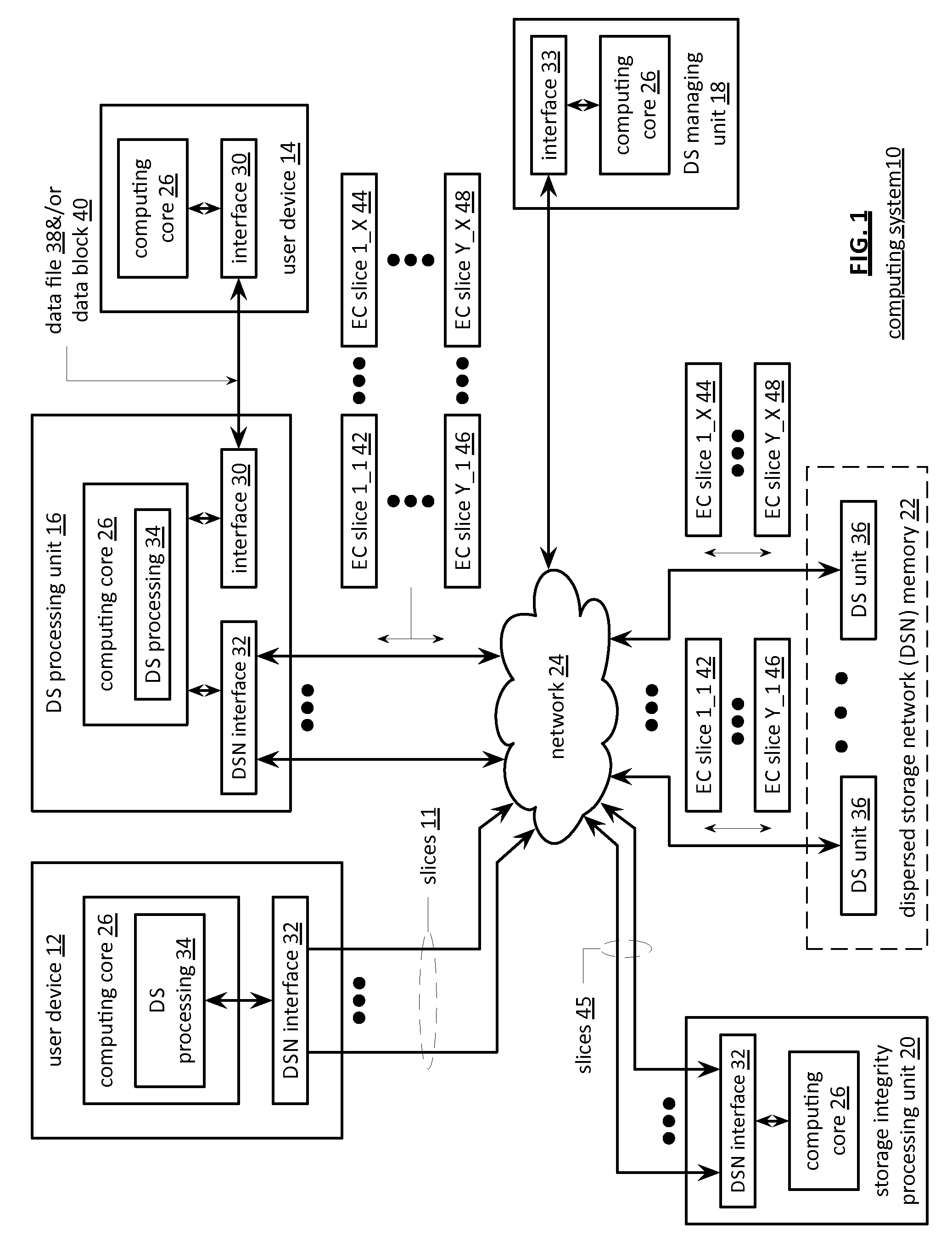

Prioritized deleting of slices stored in a dispersed storage network

Owner:PURE STORAGE

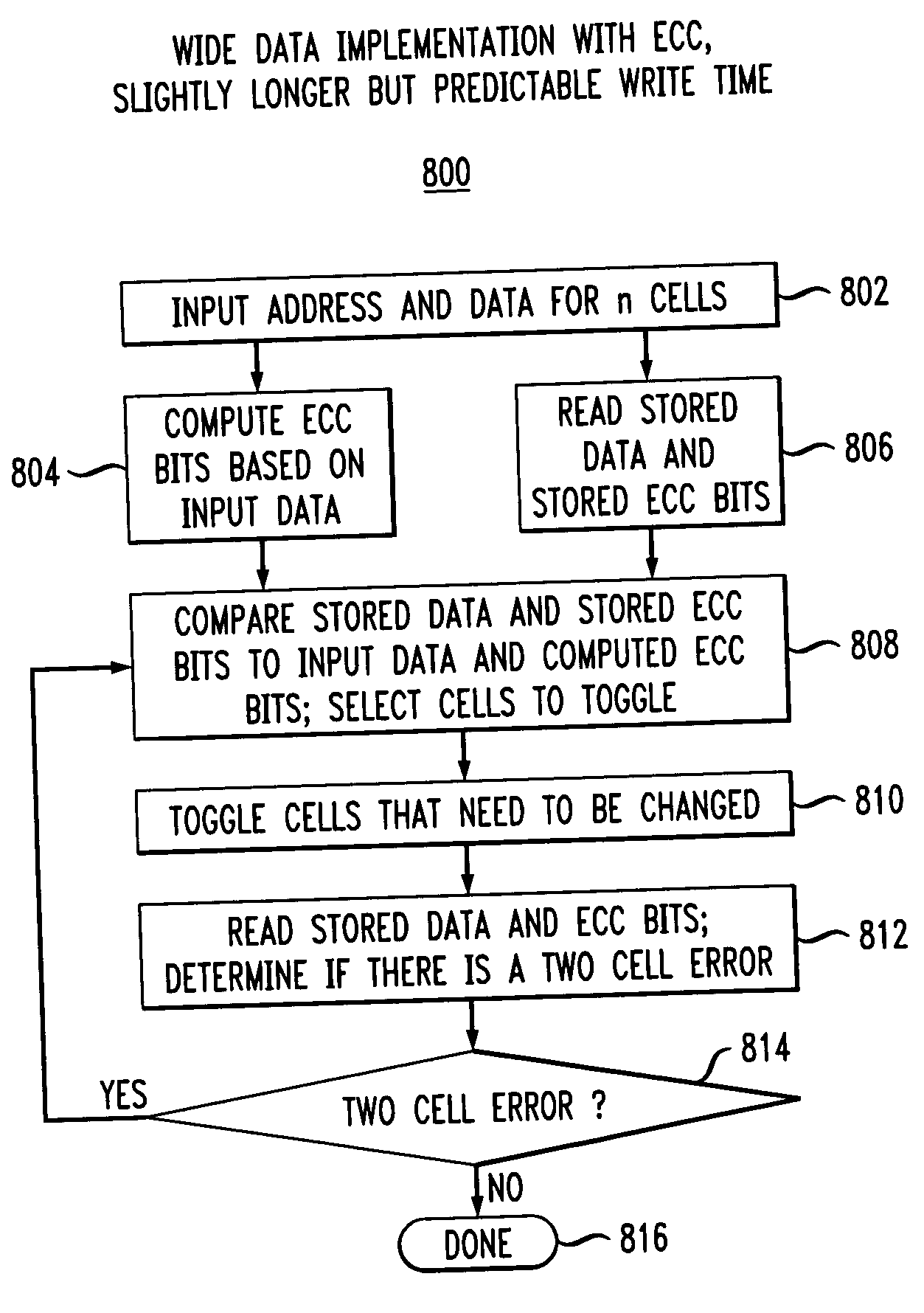

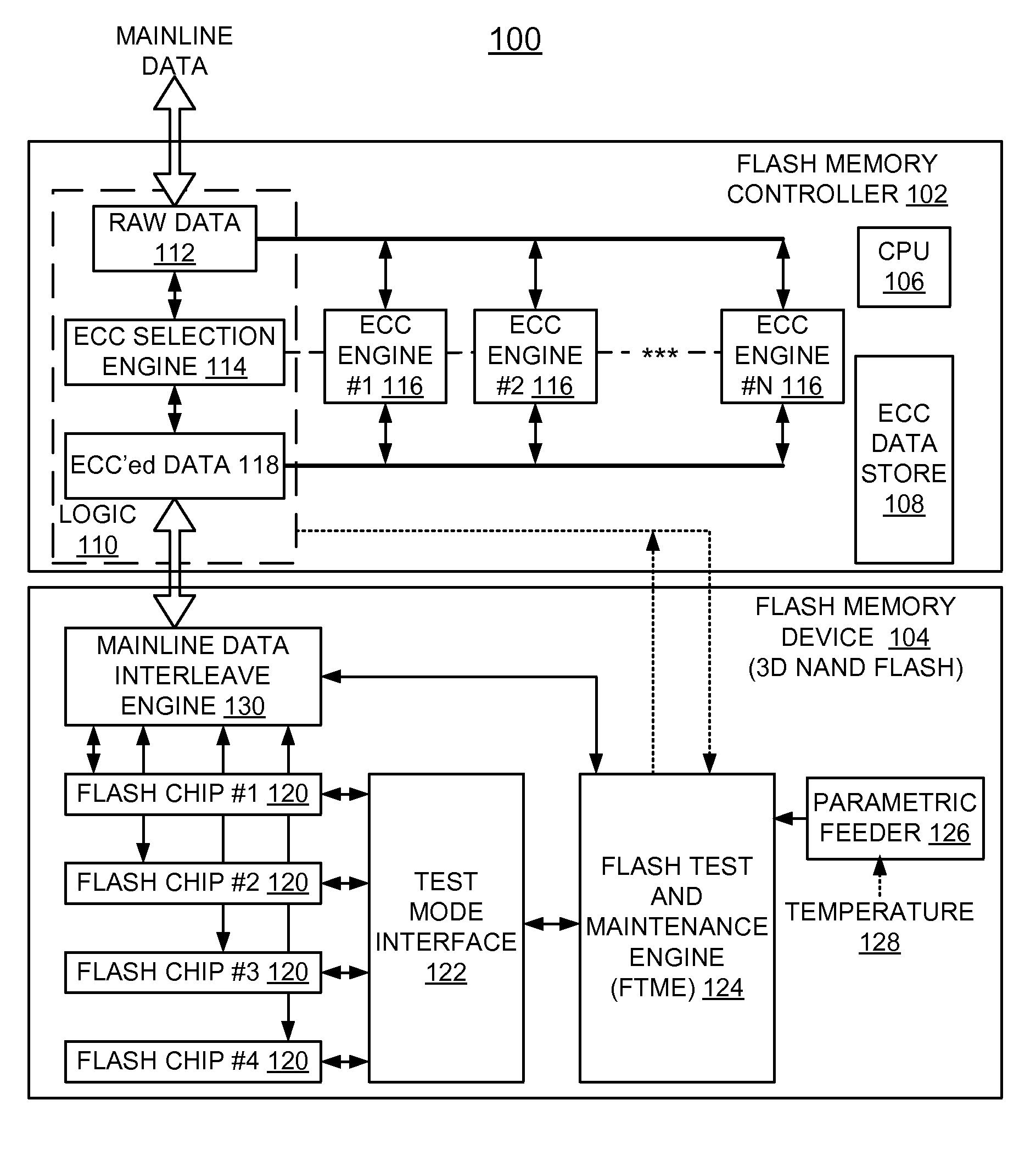

Implementing ecc control for enhanced endurance and data retention of flash memories

InactiveUS20150199232A1Improve enduranceImprove data retentionCode conversionRead-only memoriesMemory controllerData retention

Owner:IBM CORP

Methods for scaling encoded data without requiring knowledge of the encoding scheme

ActiveUS20050179567A1Pulse modulation television signal transmissionEncryption apparatus with shift registers/memoriesComputer hardwareData segment

Methods for scaling (e.g., transcoding) data are described. A sequence of encoded data is accessed. The encoded data are organized according to an encoding scheme that was used to encode the data. A value for a scalable attribute is ascertained. The scalable attribute identifies how the encoded data are to be scaled. A reference to segments of encoded data associated with the scalable attribute is accessed. The reference is beyond the syntax of the encoding scheme. The reference is used to locate the segments in the sequence of encoded data. The segments are found without requiring knowledge by the device of the encoding scheme. A scaled version of the encoded data is created using the segments.

Owner:HEWLETT PACKARD DEV CO LP

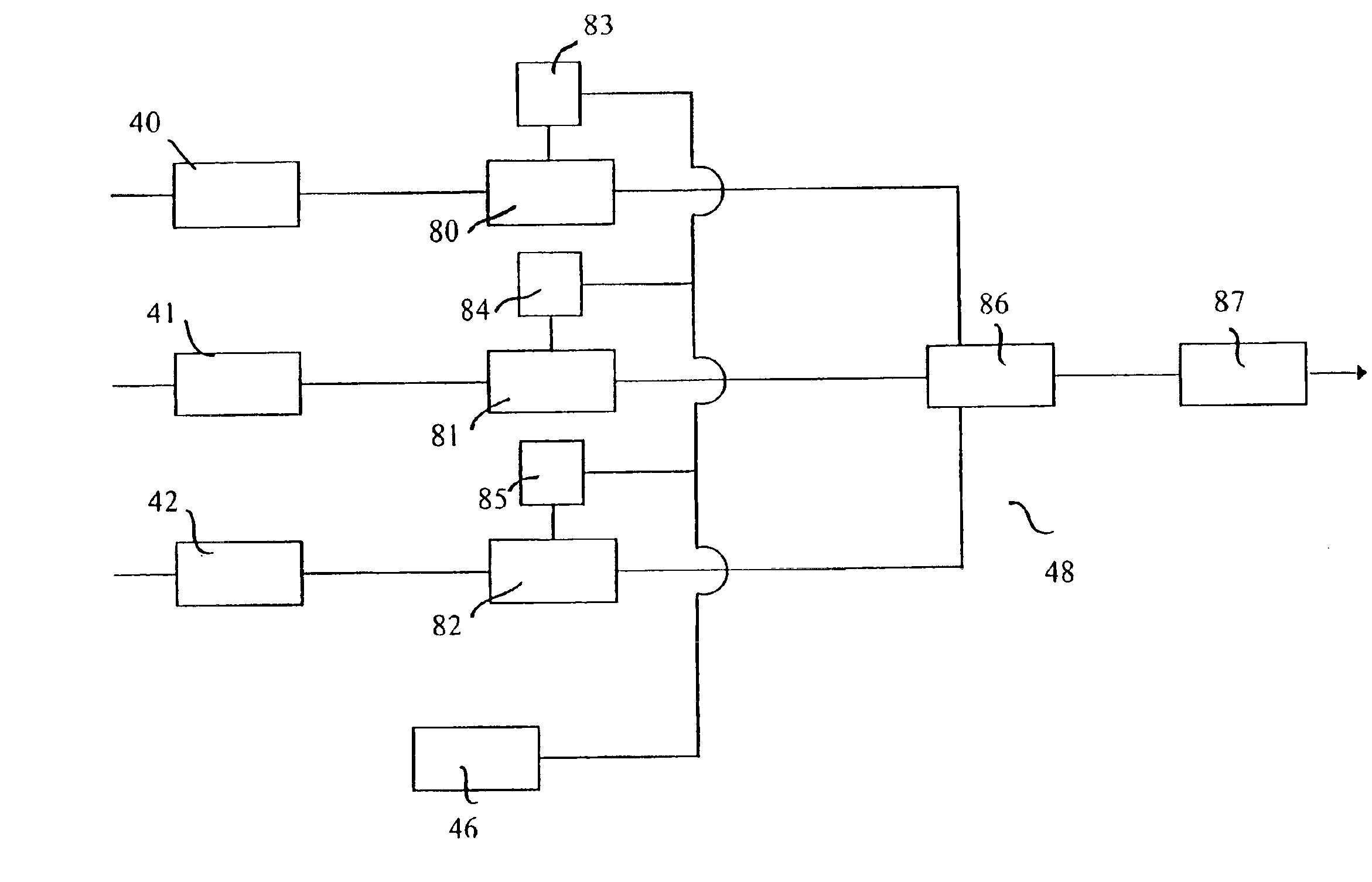

High-speed module, device and method for decoding a concatenated code

InactiveUS7219291B2Improve throughputImprove performanceCode conversionError correction/detection by combining multiple code structuresComputer moduleCode word

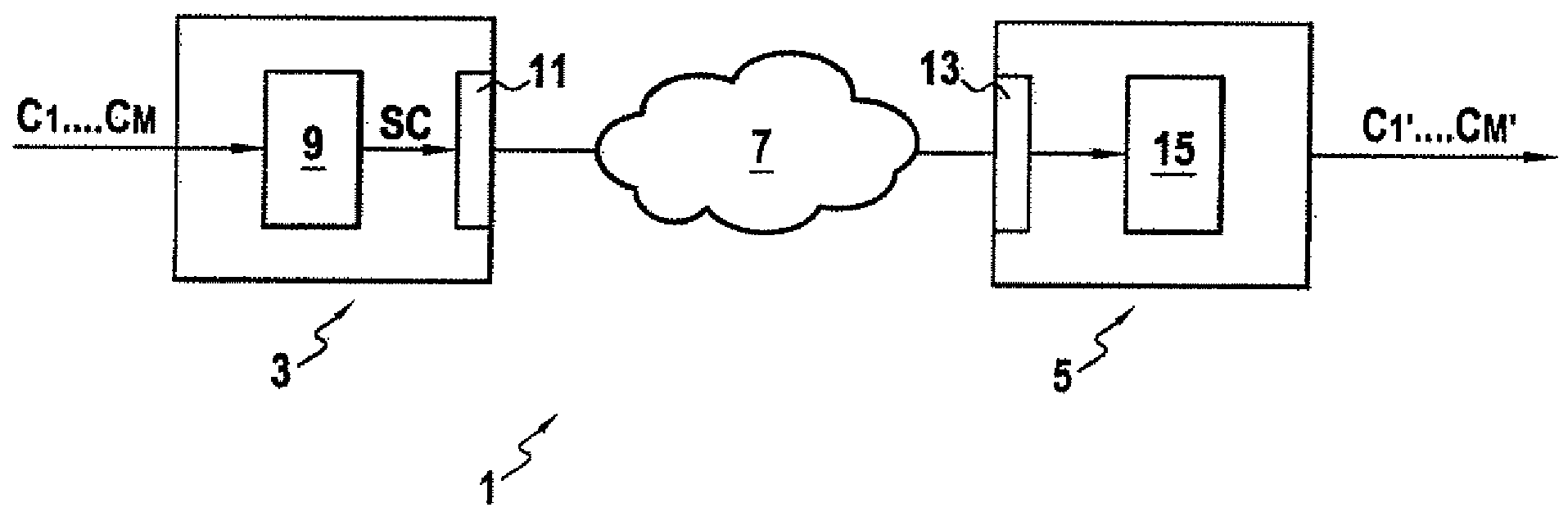

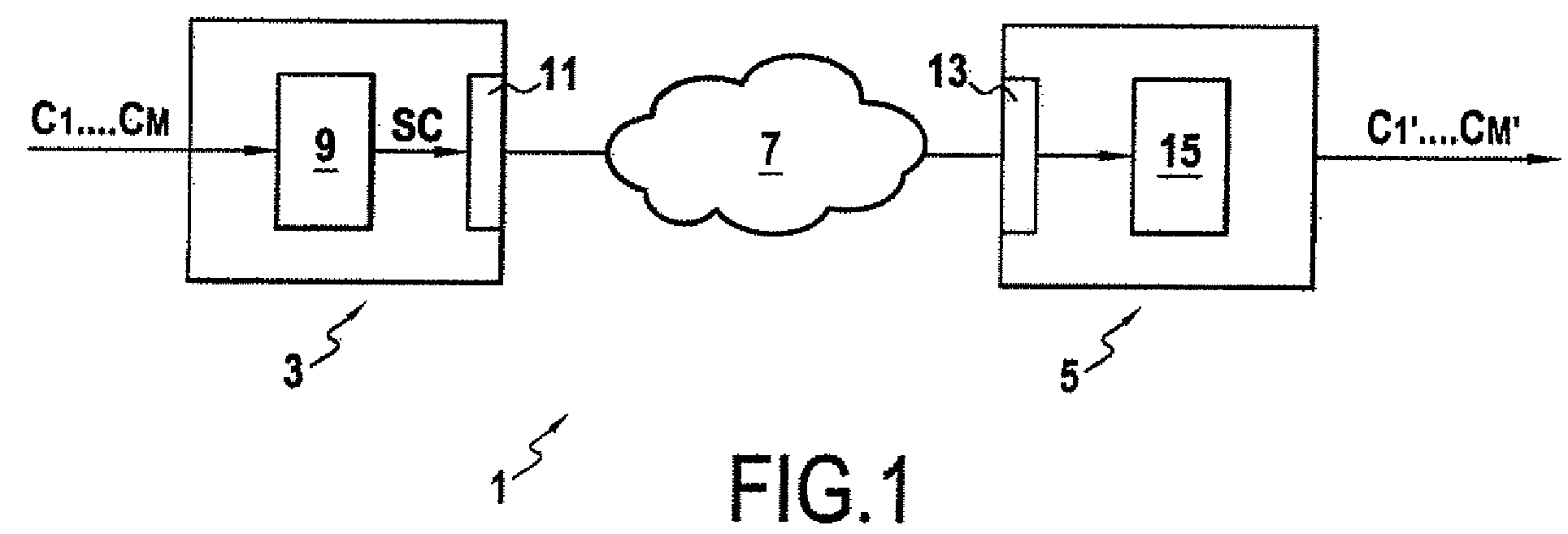

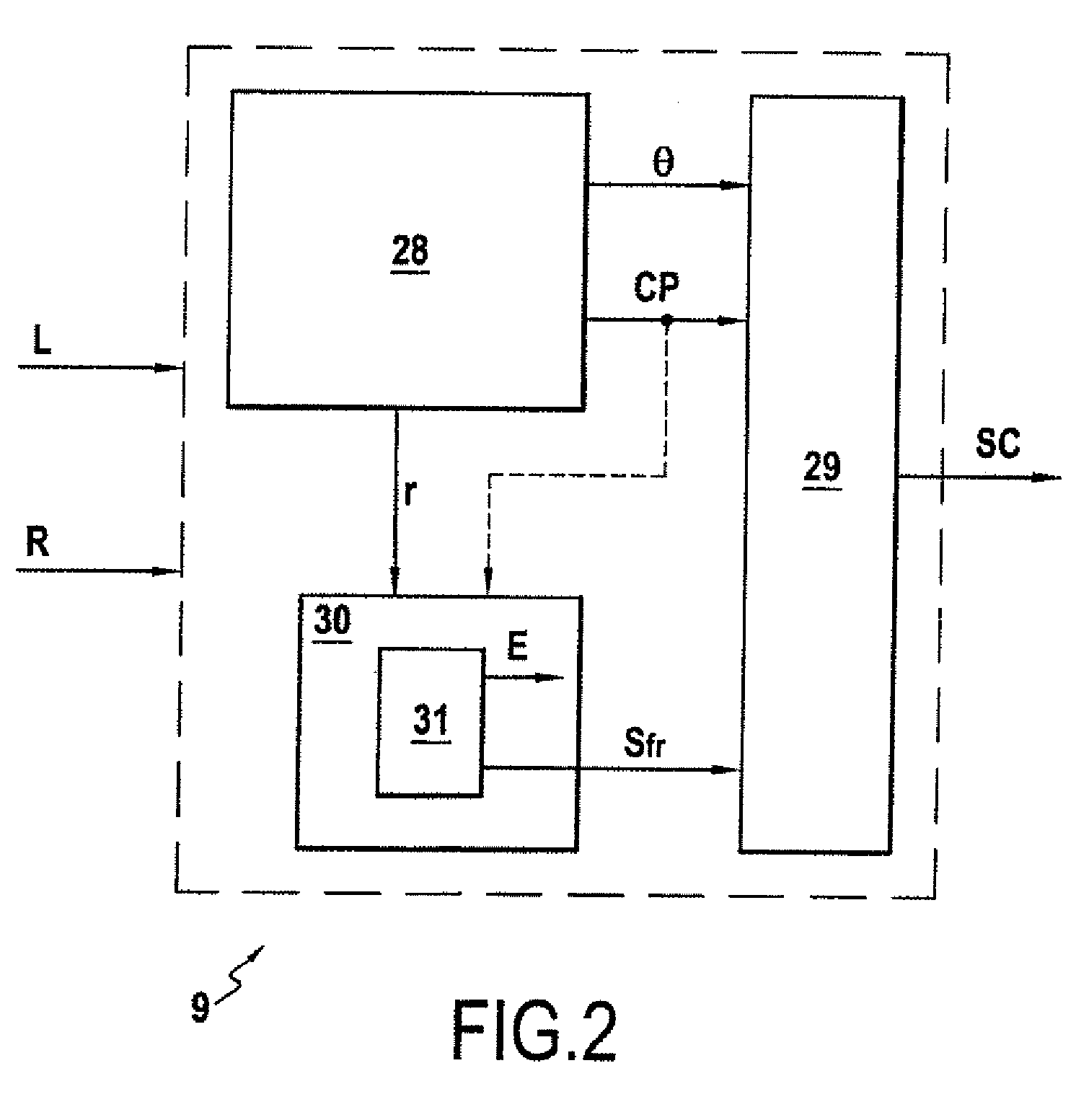

The invention concerns a module for decoding a concatenated code, corresponding at least to two elementary codes C1 and C2, using storage means (81, 83, 90, 111, 113) wherein are stored samples of data to be decoded, comprising at least two elementary decoders (821, 822, . . . 82m) of at least one of the elementary codes, the elementary decoders associated with one of the elementary codes simultaneously processing, in parallel separate code words contained in the storage means.

Owner:FRANCE TELECOM SA +1

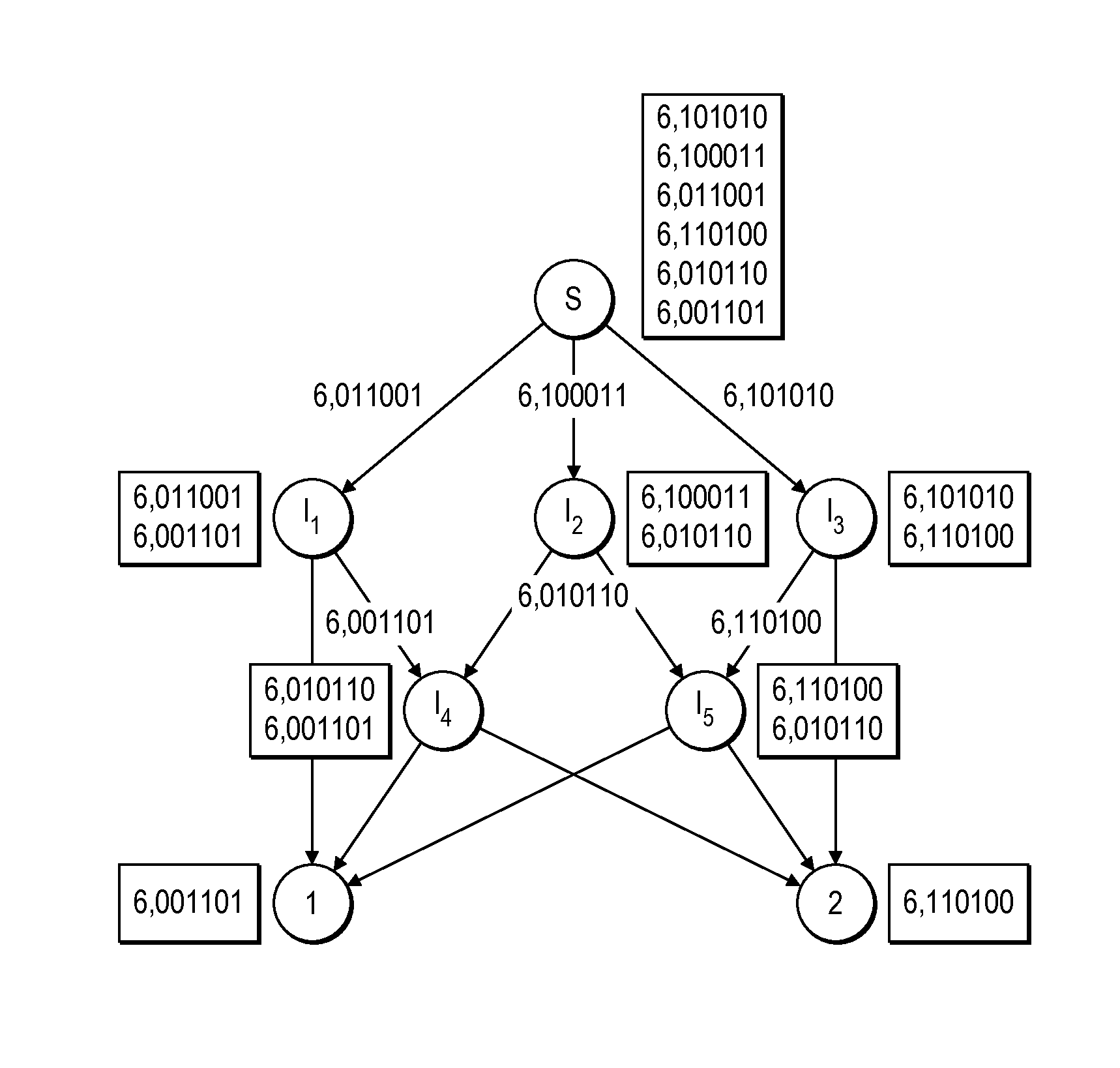

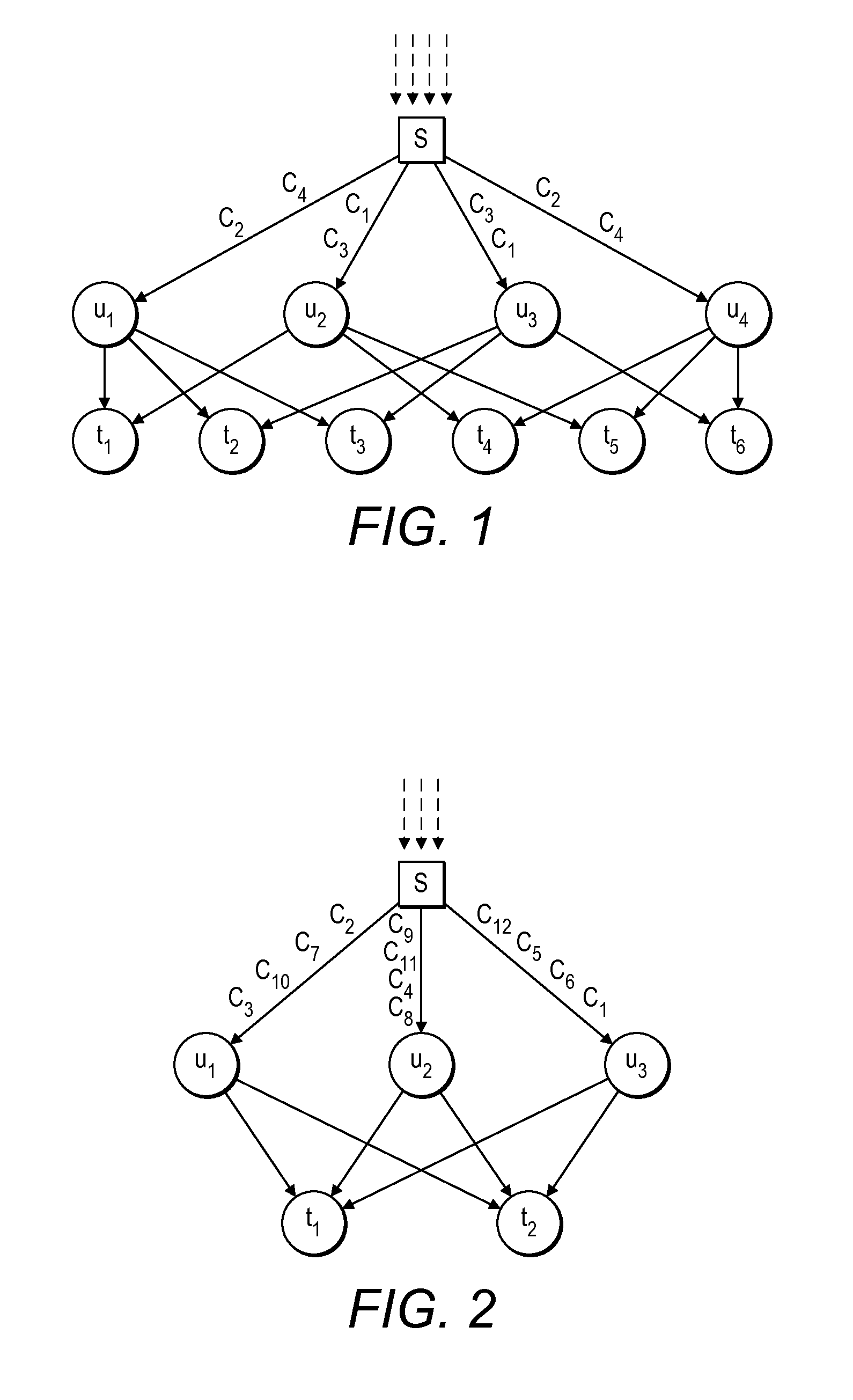

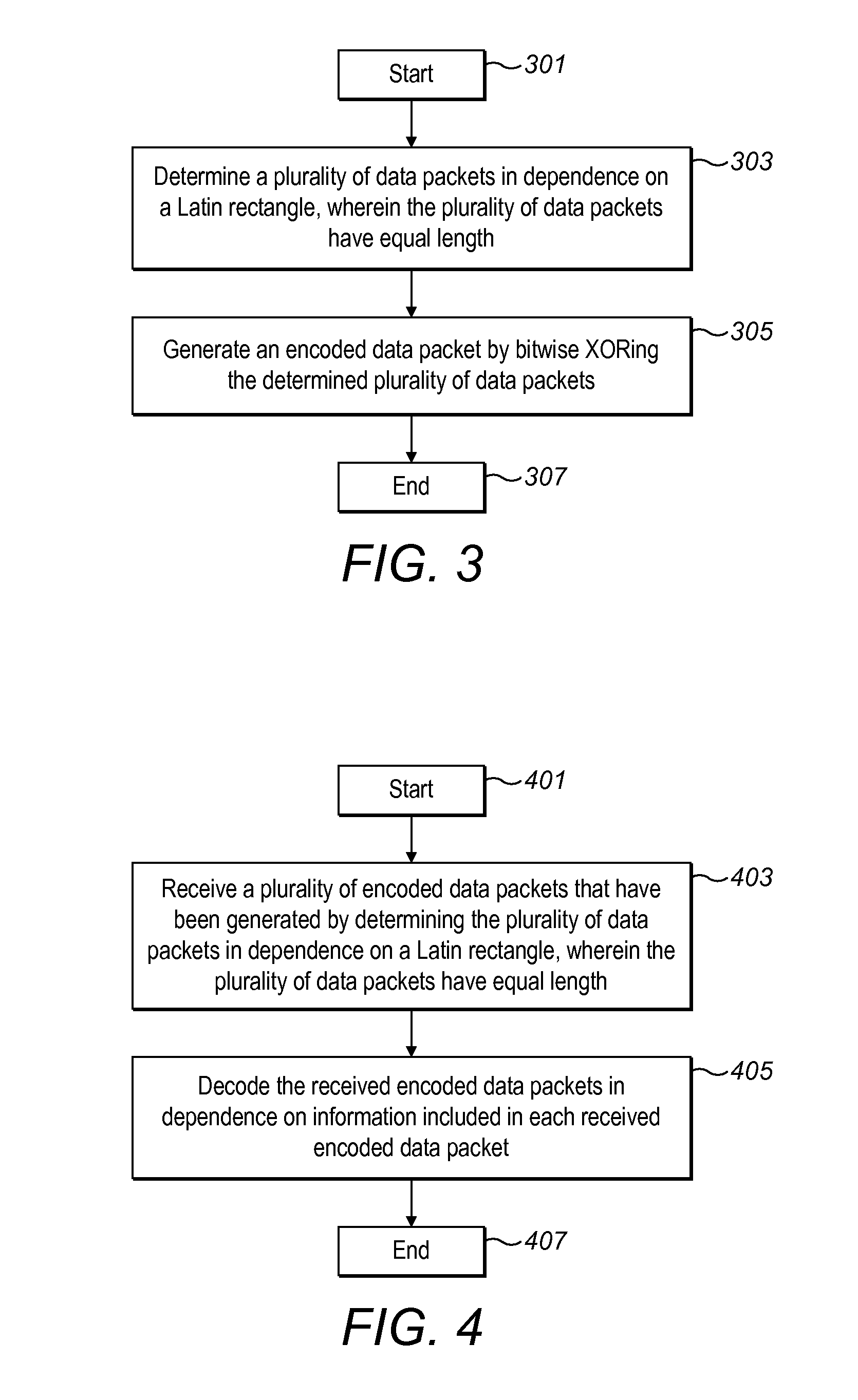

Network coding over gf(2)

InactiveUS20160373210A1Improve efficiencyImprove securityCode conversionCoding detailsComputer networkAlgorithm

Owner:MEMOSCALE AS

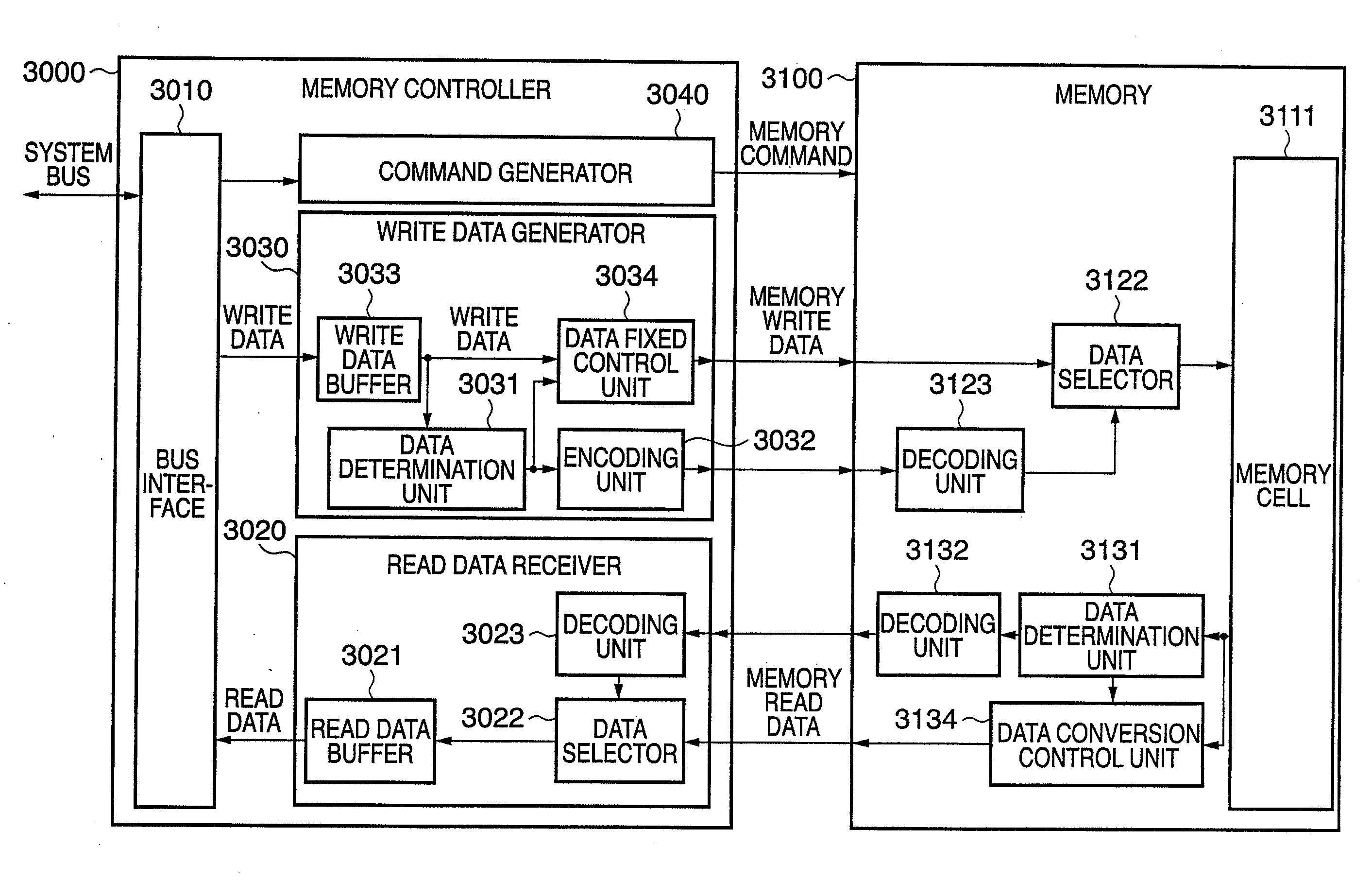

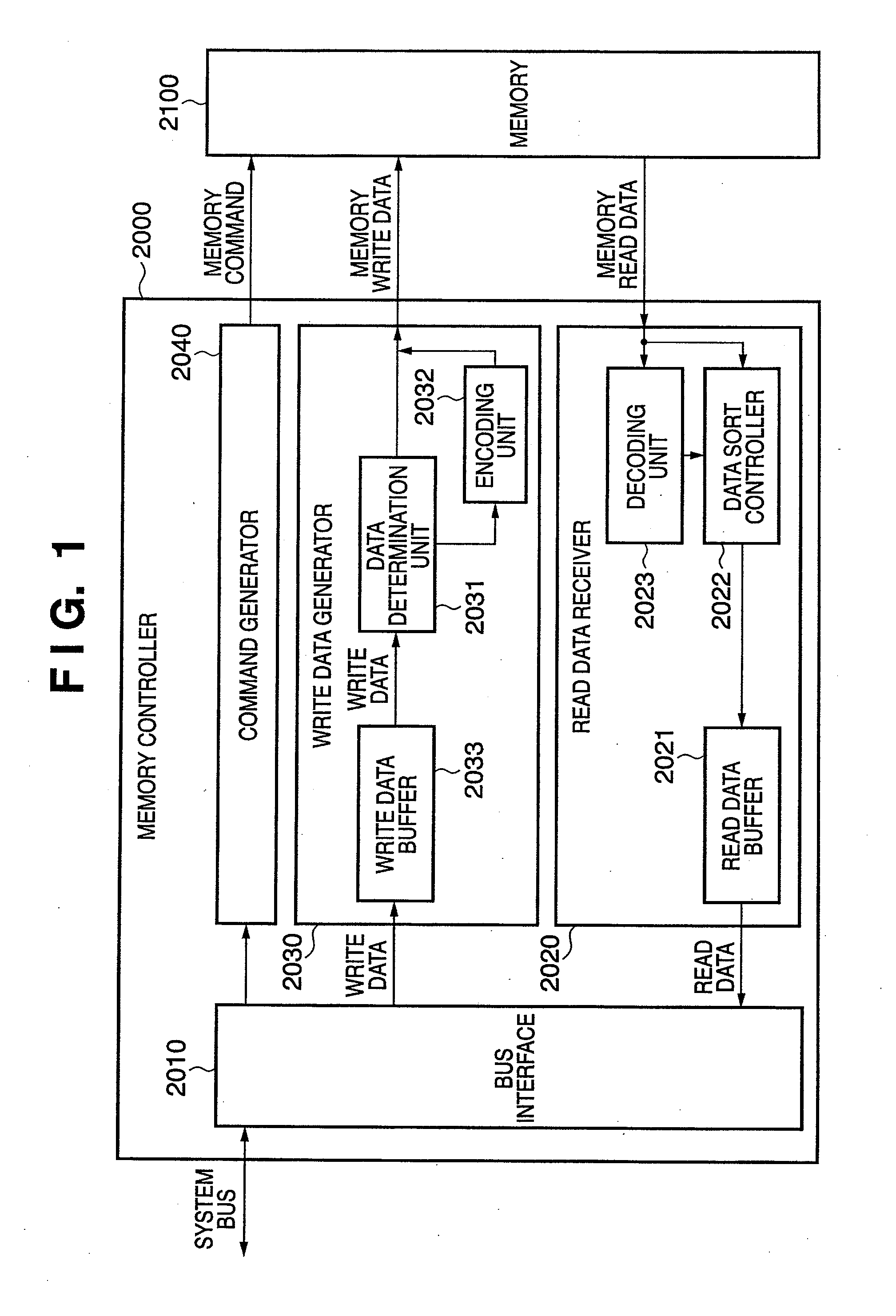

Non-volatile memory system and method with variable error correcting capability

InactiveCN101499325ARealize the ability to adjust and correct errorsOptimal error correction configurationCode conversionStatic storageComputer moduleBus interface

The invention discloses a nonvalatile memory system with variable error correcting capability, which comprises a system bus interface module, an RS encoder, an RS decoder, an NAND read-write time sequence generator and an error correcting capability configuration module. The error correcting capability configuration module carries out order input and error correcting information feedback with outside world through the bus interface module. The error correcting capability configuration module carries out error correcting capability configuration to the RS encoder and the RS decoder respectively in accordance with instructions and outputs feedback information obtained from the RS encoder and the RS decoder respectively through the bus interface module. The system takes both speed and error correcting capacity into consideration, thus realizing the error correcting capacity adjustment in various environments so as to obtain the best error correcting configuration.

Owner:ARKMICRO TECH

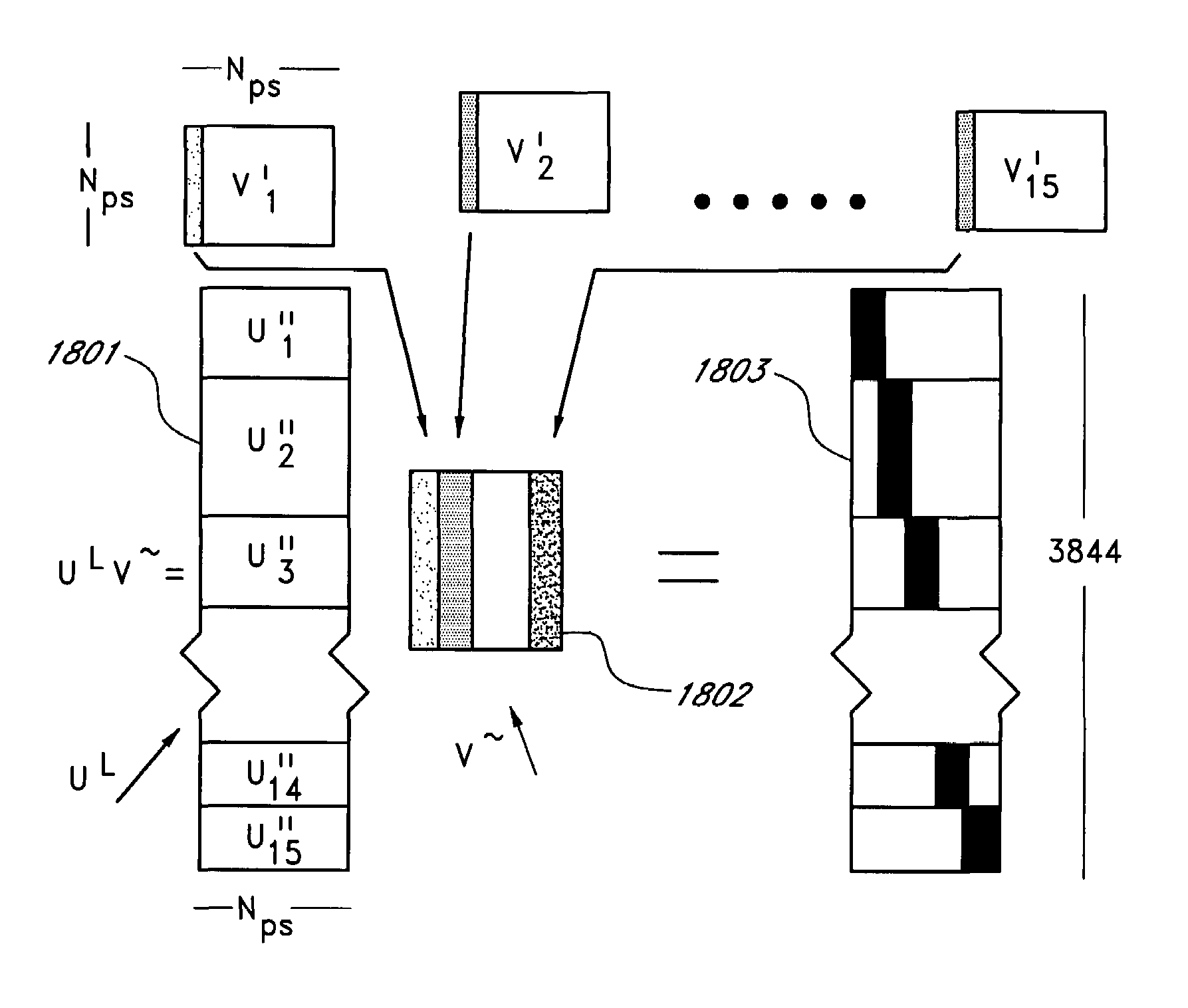

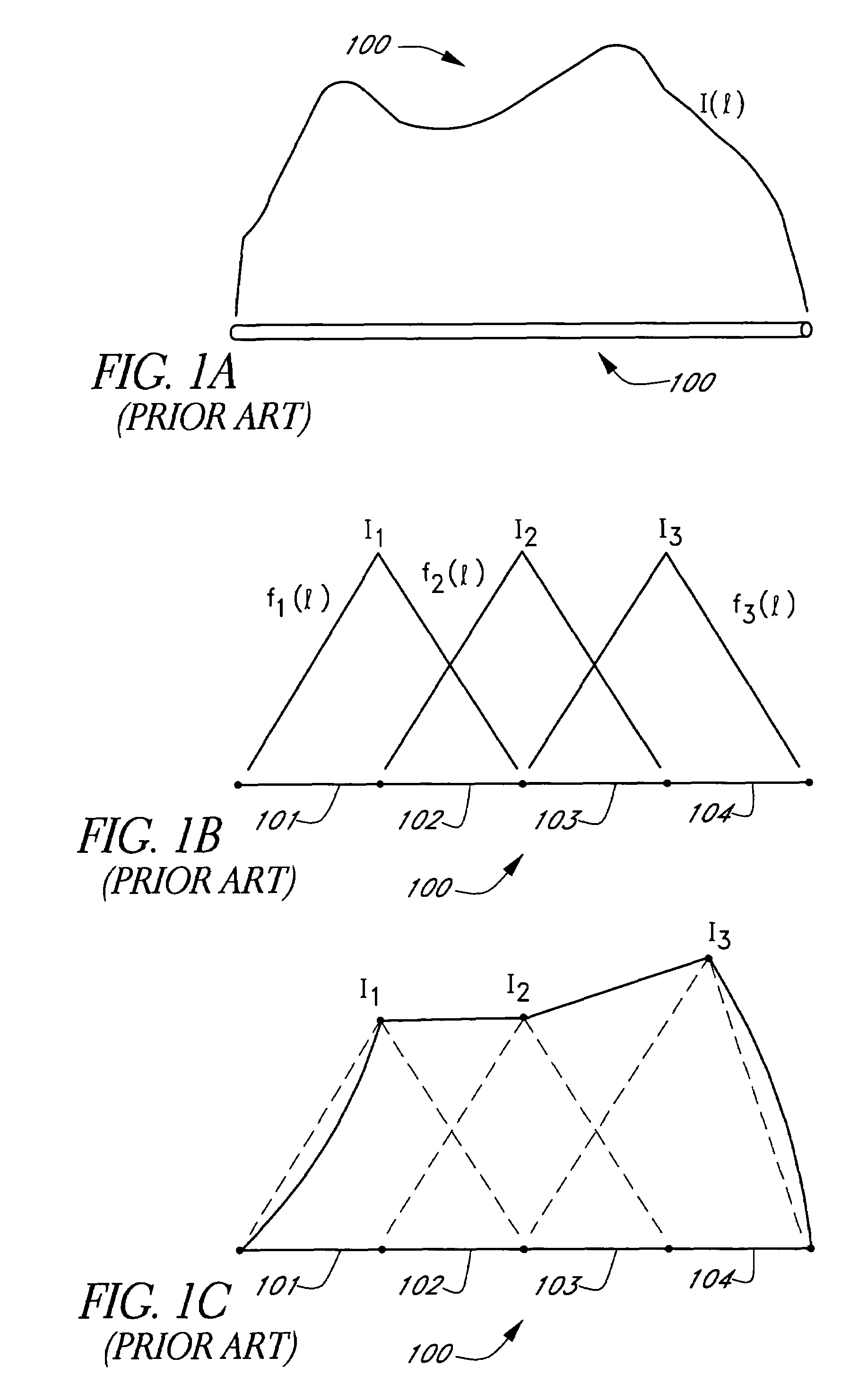

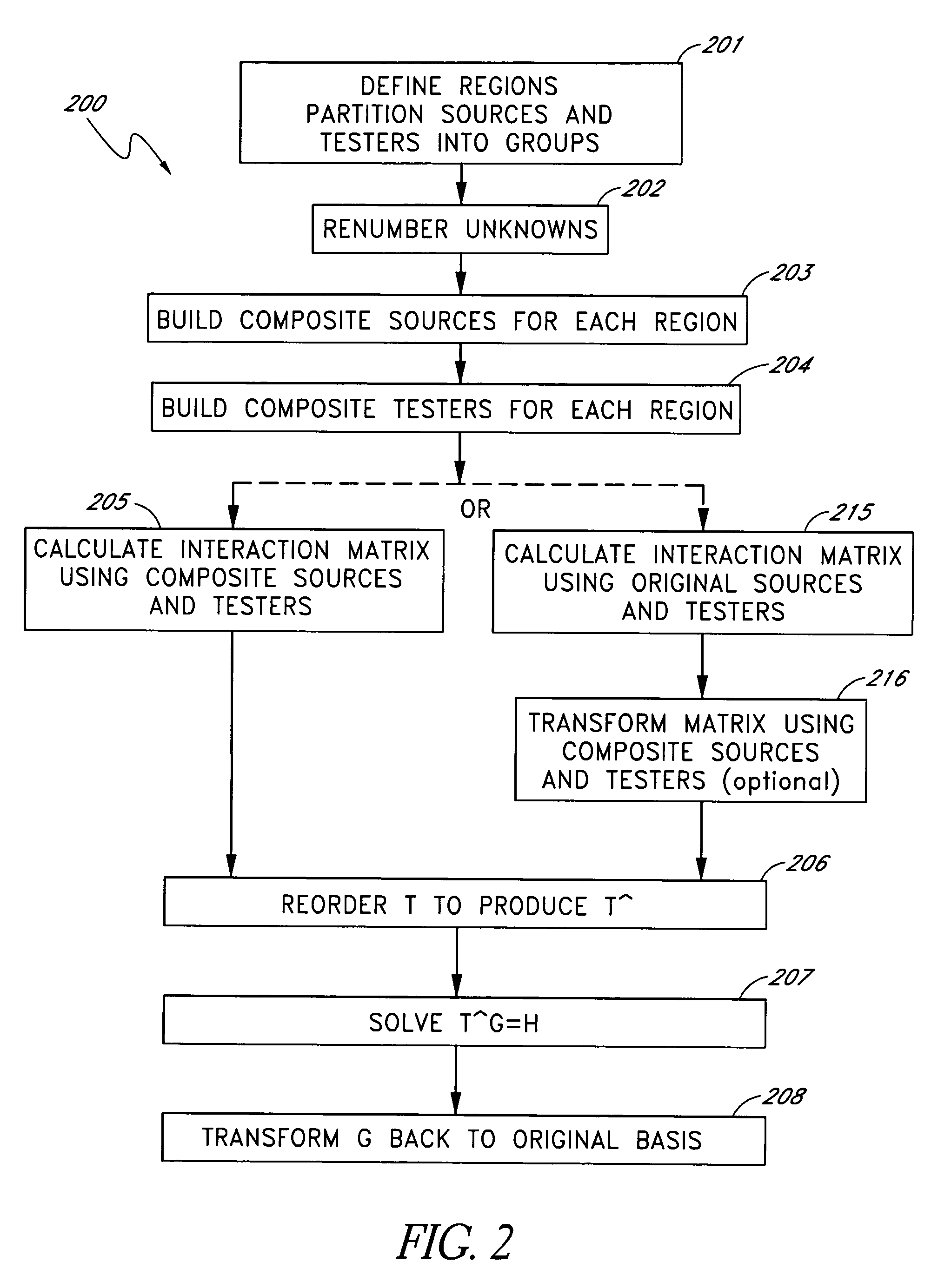

Compression of interaction data using directional sources and/or testers

InactiveUS7720651B2High strengthEasy to optimizeAnalogue computers for electric apparatusCode conversionTester deviceComputer science

Owner:CANNING FRANCIS X

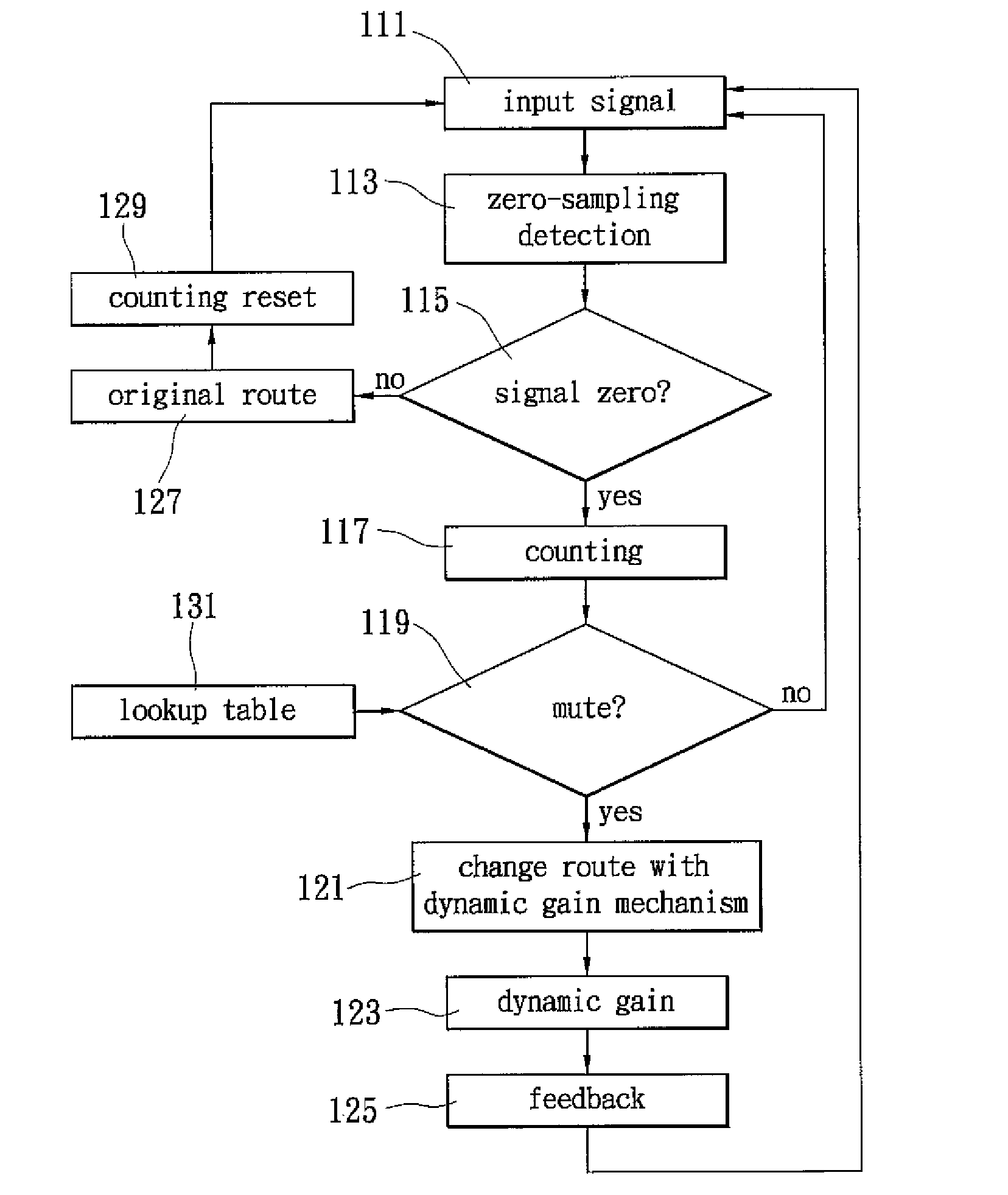

Apparatus and method for minimizing quantization noise as muting

InactiveUS20090238379A1Suppression of POP noiseCode conversionTransmission noise suppressionEngineeringAudio frequency

Owner:ALICORP

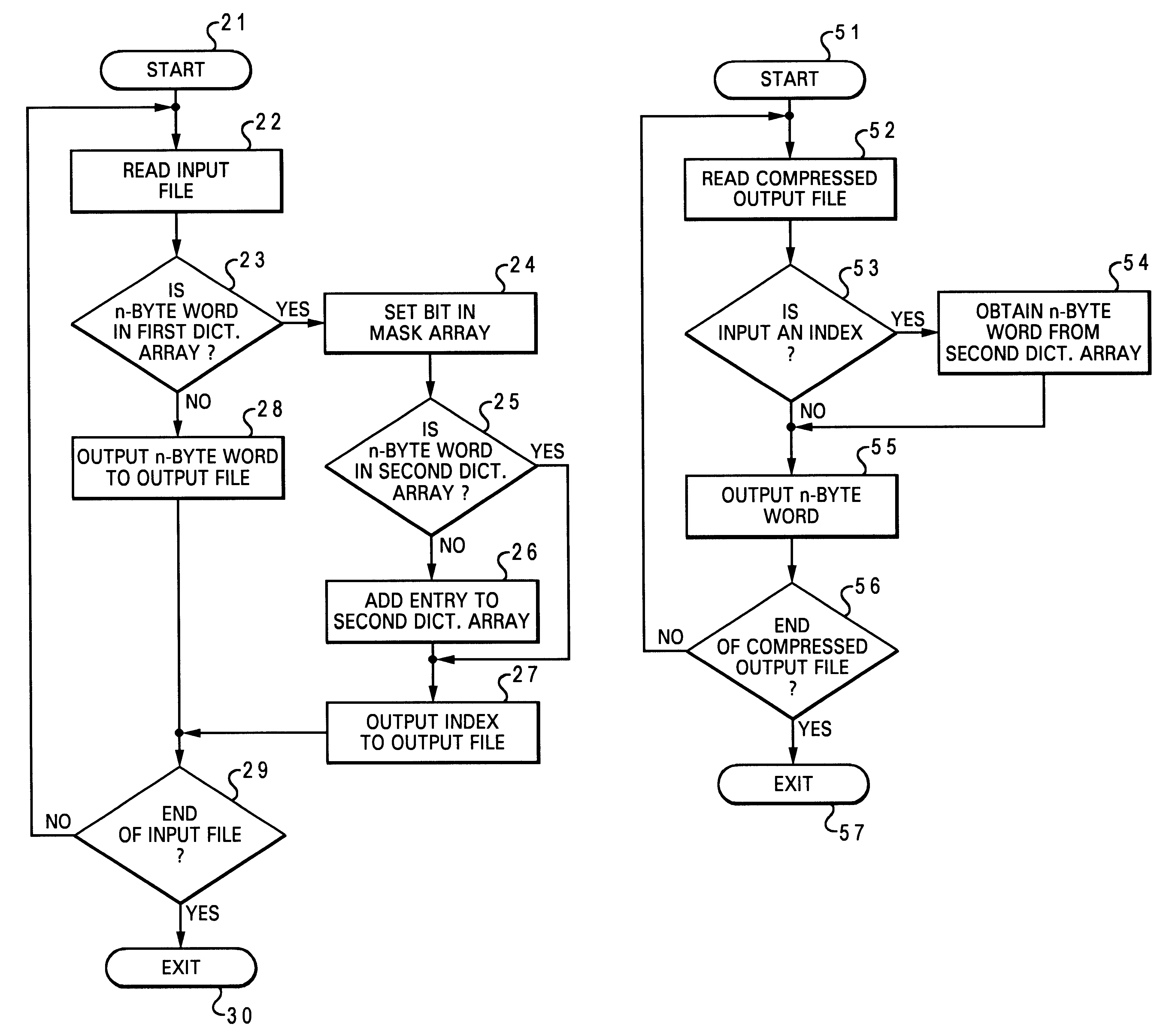

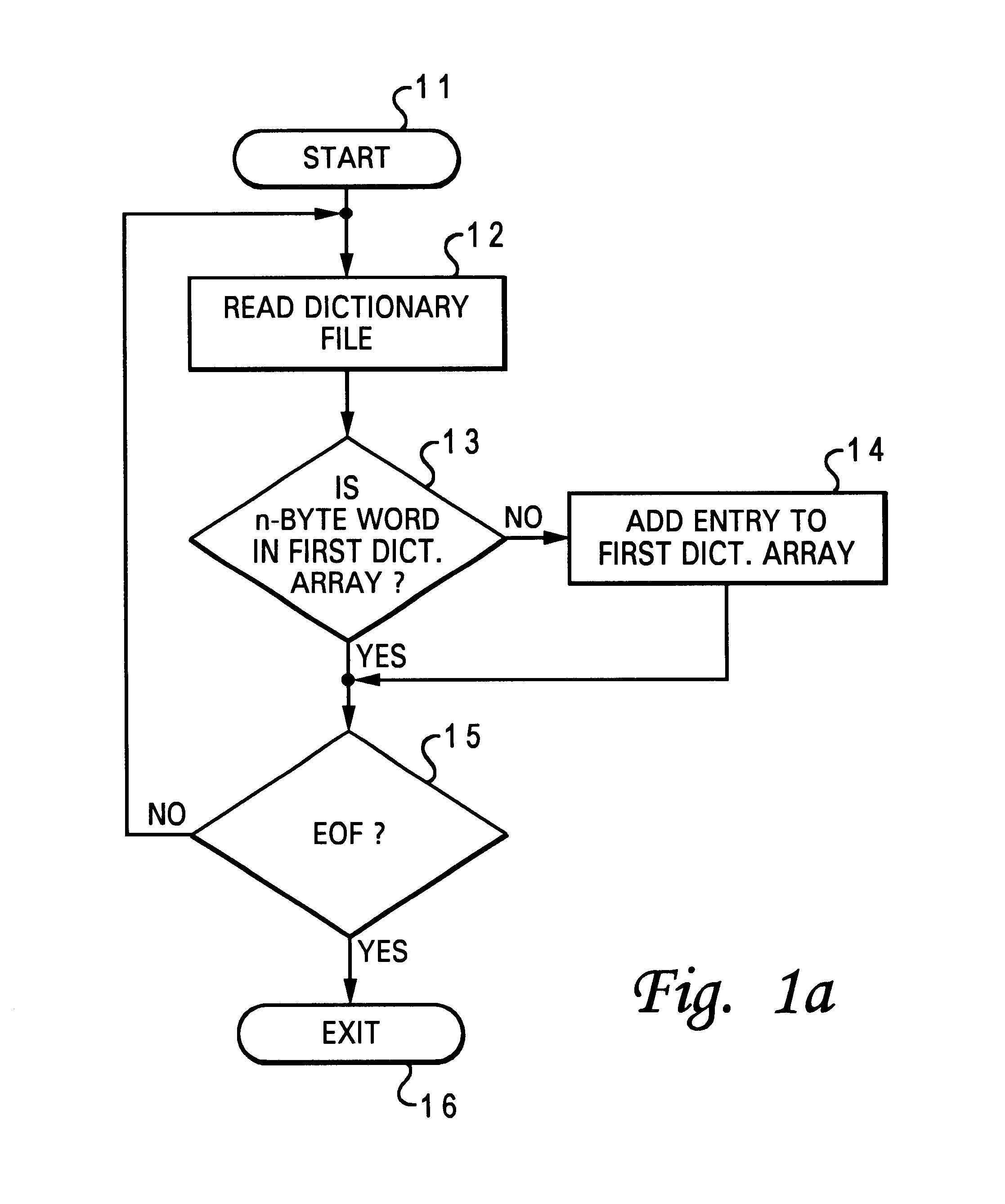

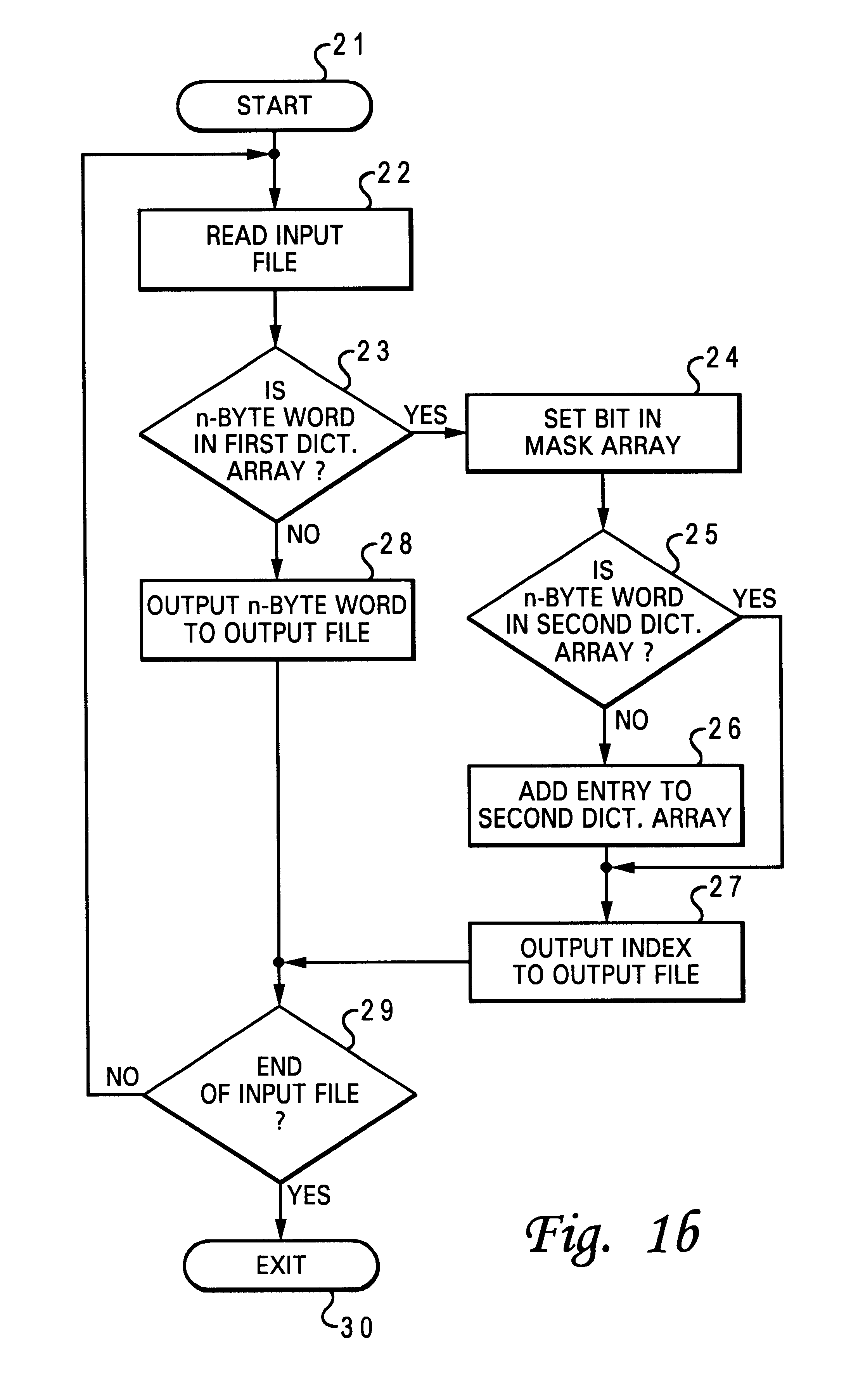

Selective data compression

Owner:DIALOGIC NETWORKS (ISRAEL) LTD

Systems and Methods Selective Complexity Data Decoding

Owner:AVAGO TECH INT SALES PTE LTD

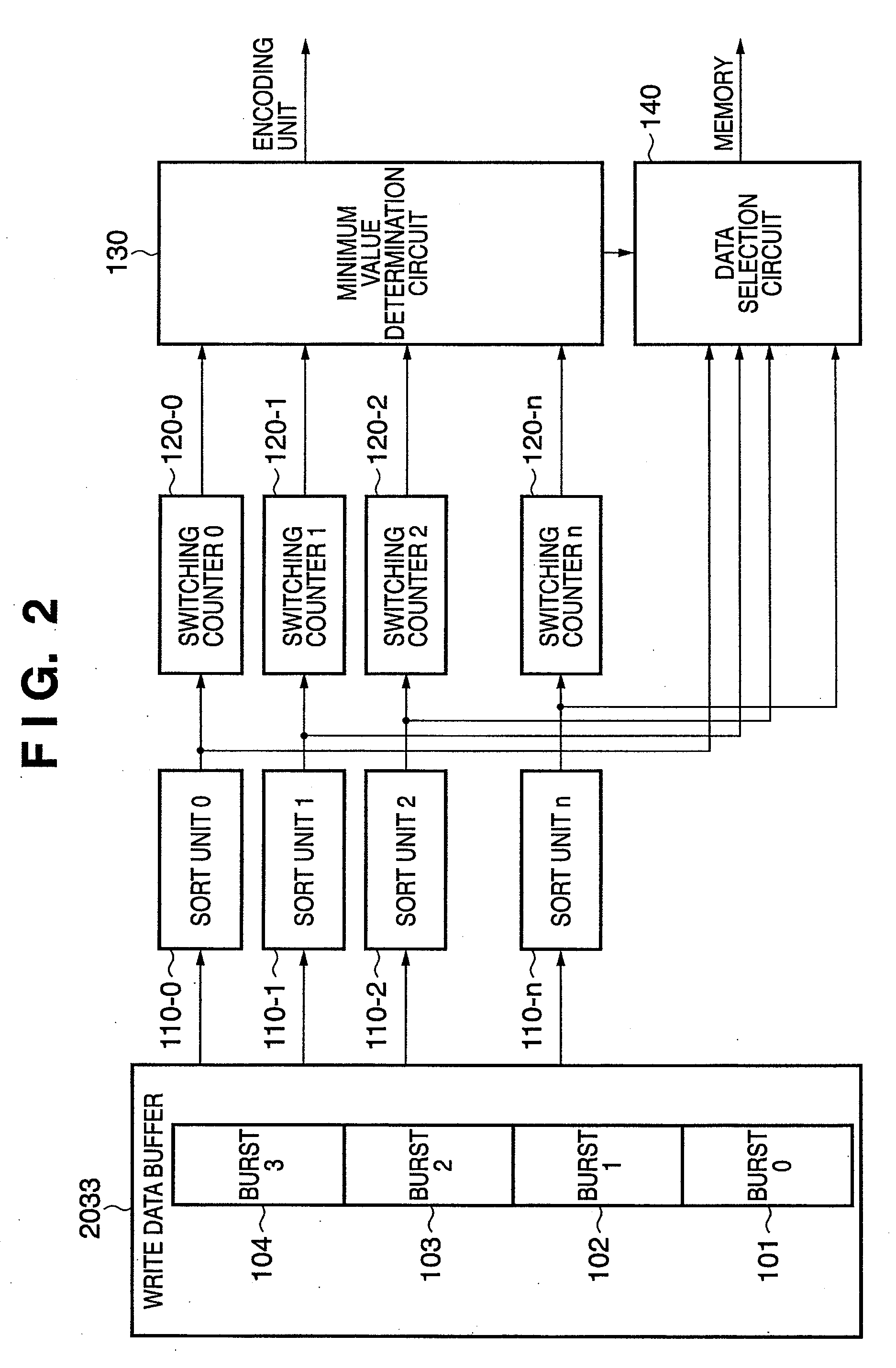

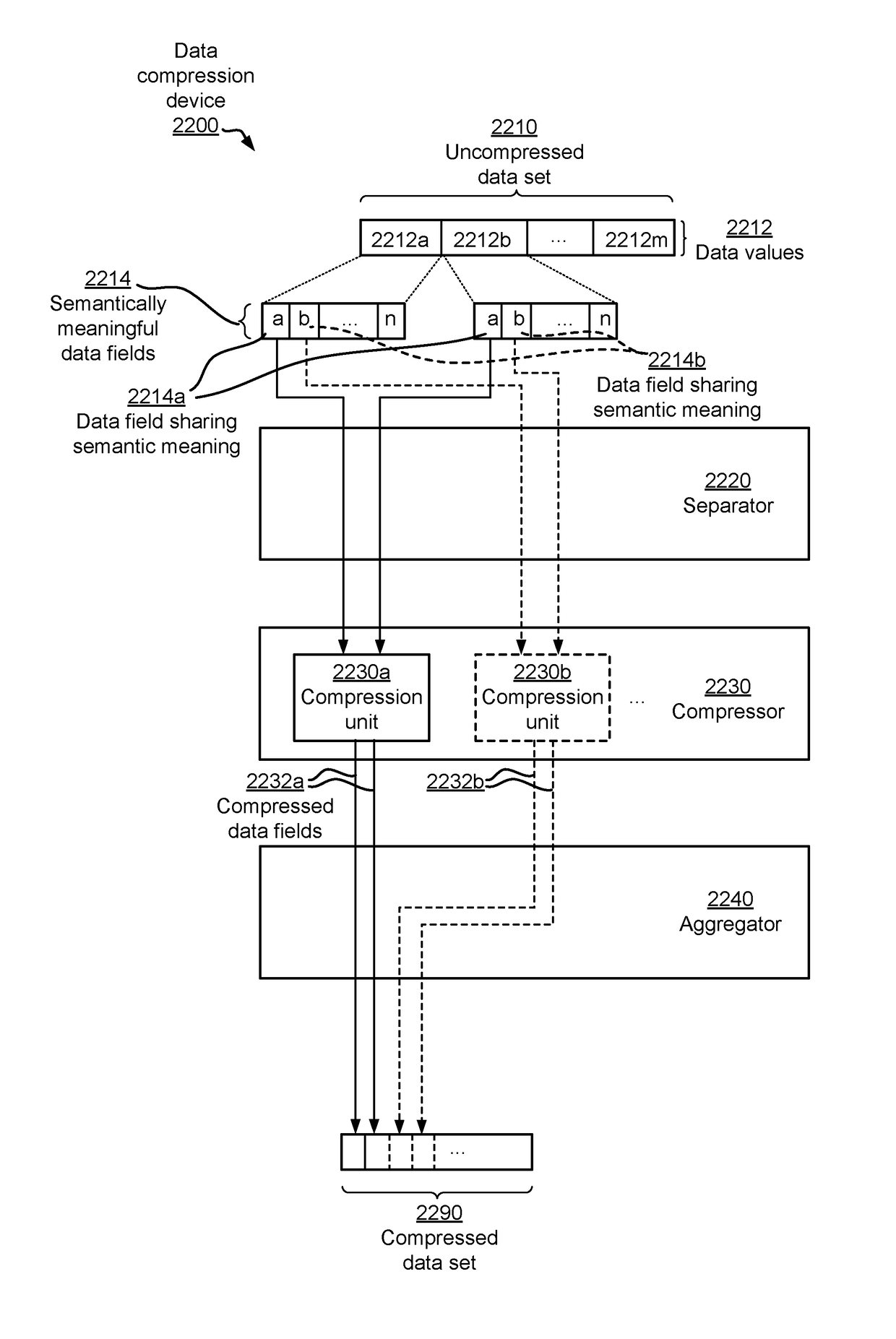

Methods, devices and systems for data compression and decompression

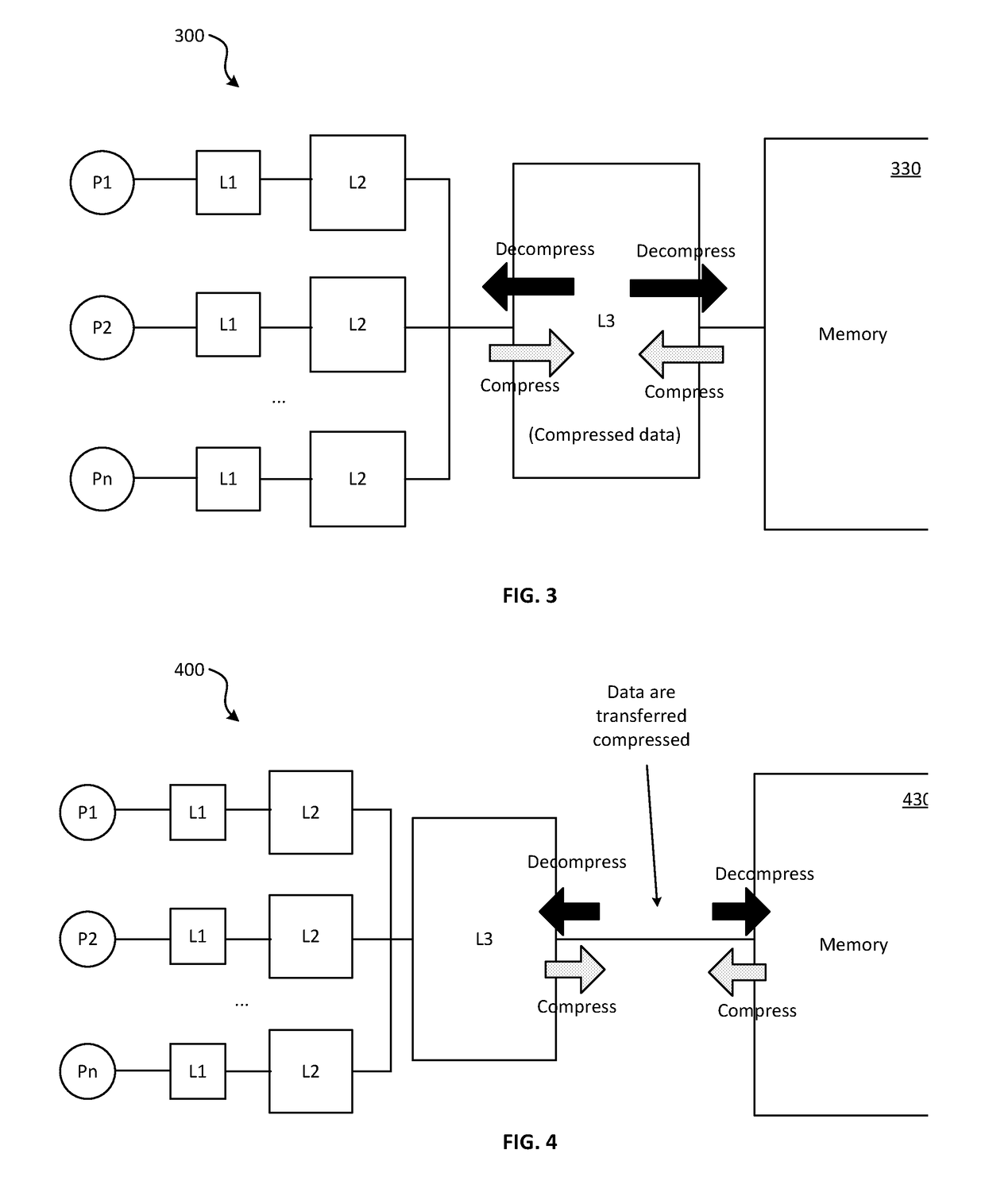

ActiveUS20180143770A1Accelerate decompressionImprove compression efficiencyInput/output to record carriersCode conversionData compressionData field

Owner:ZEROPOINT TECH AB

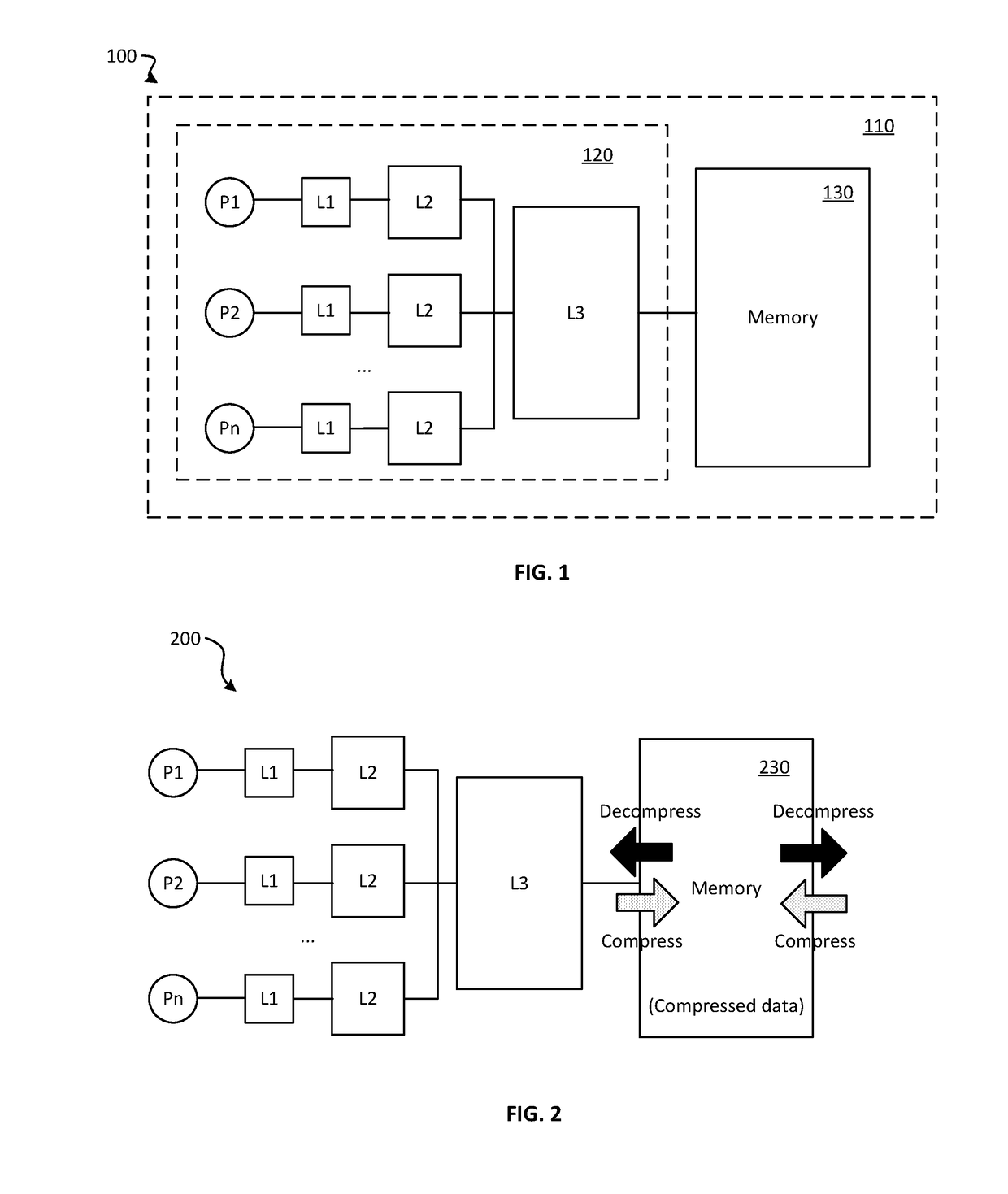

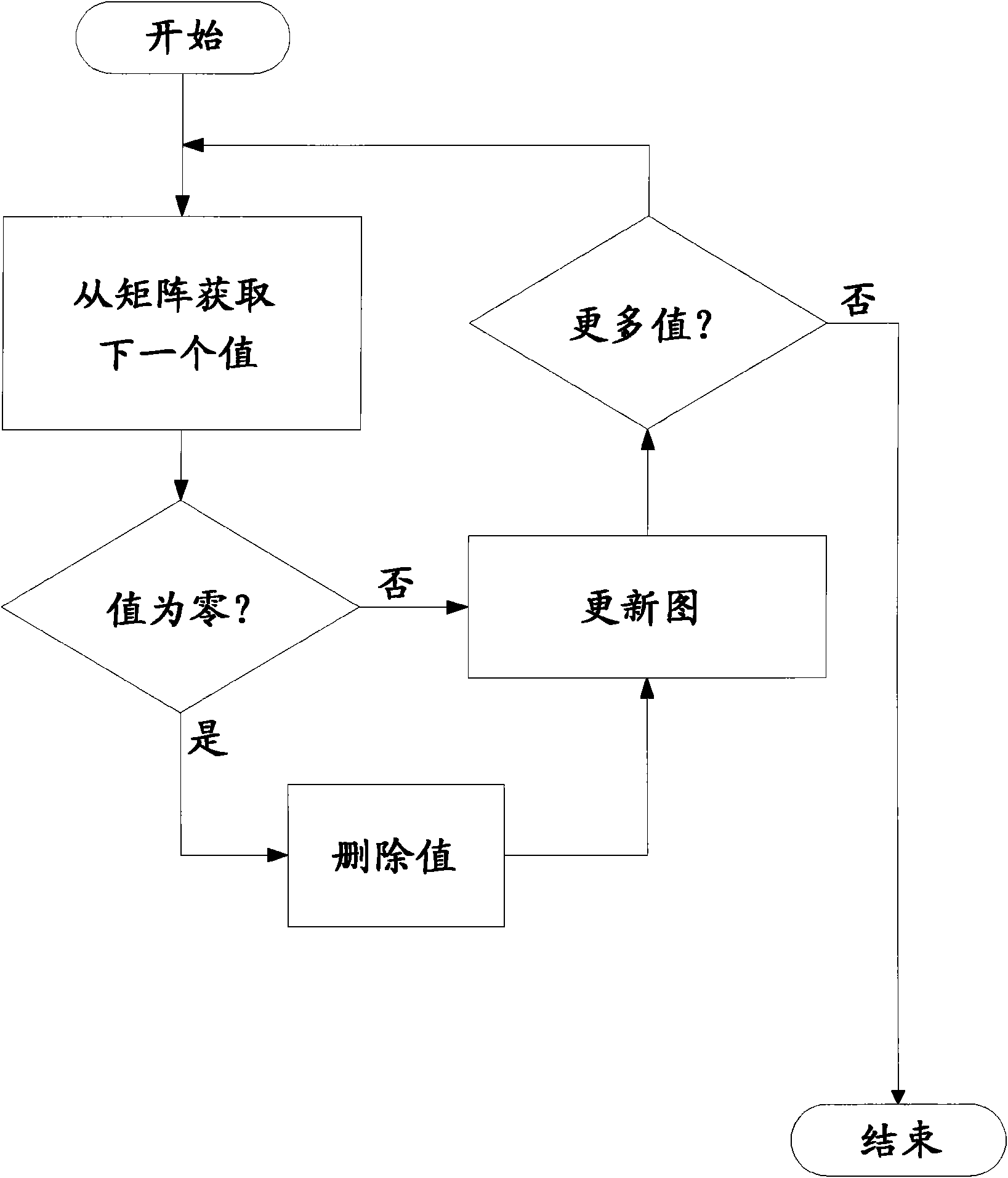

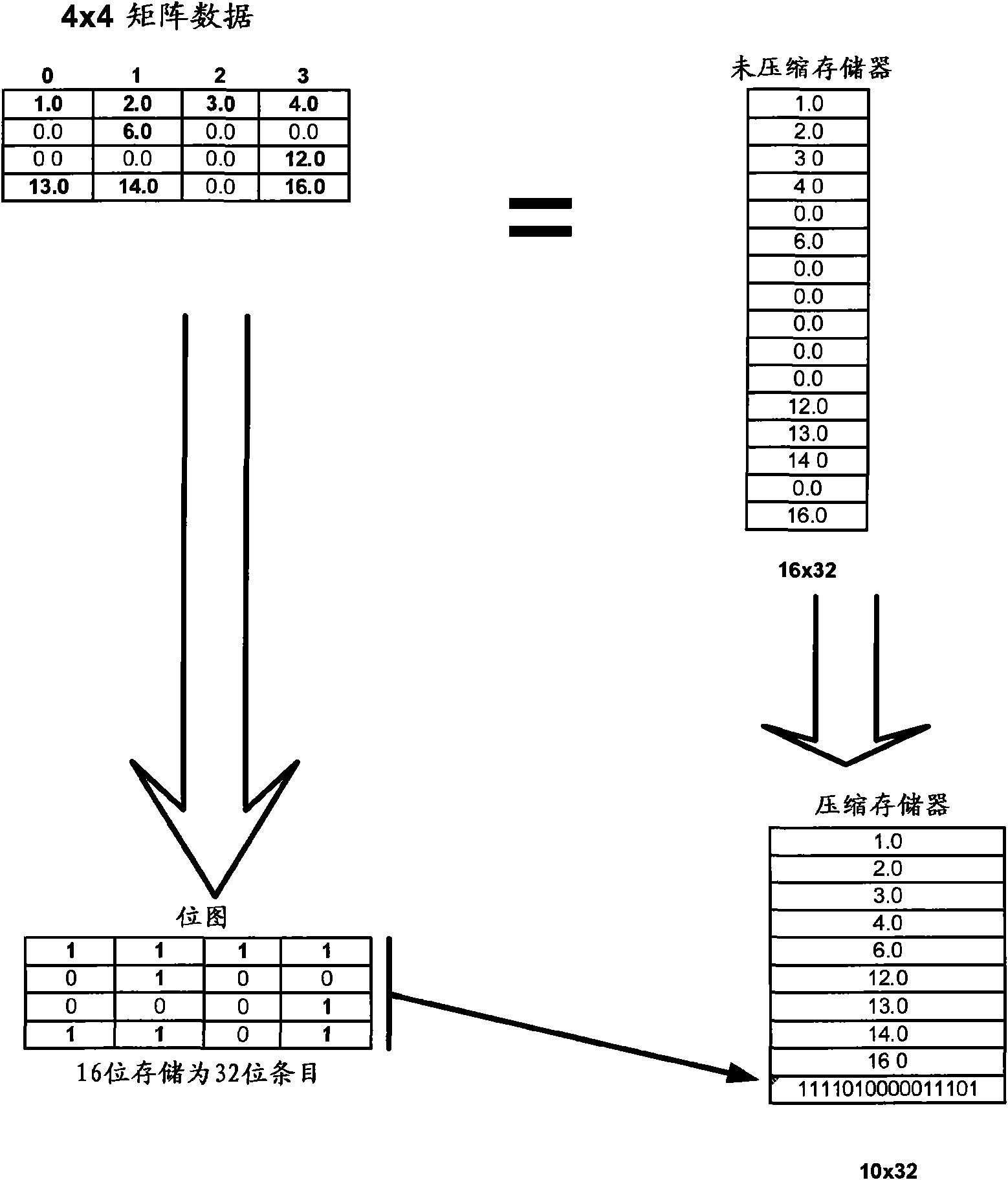

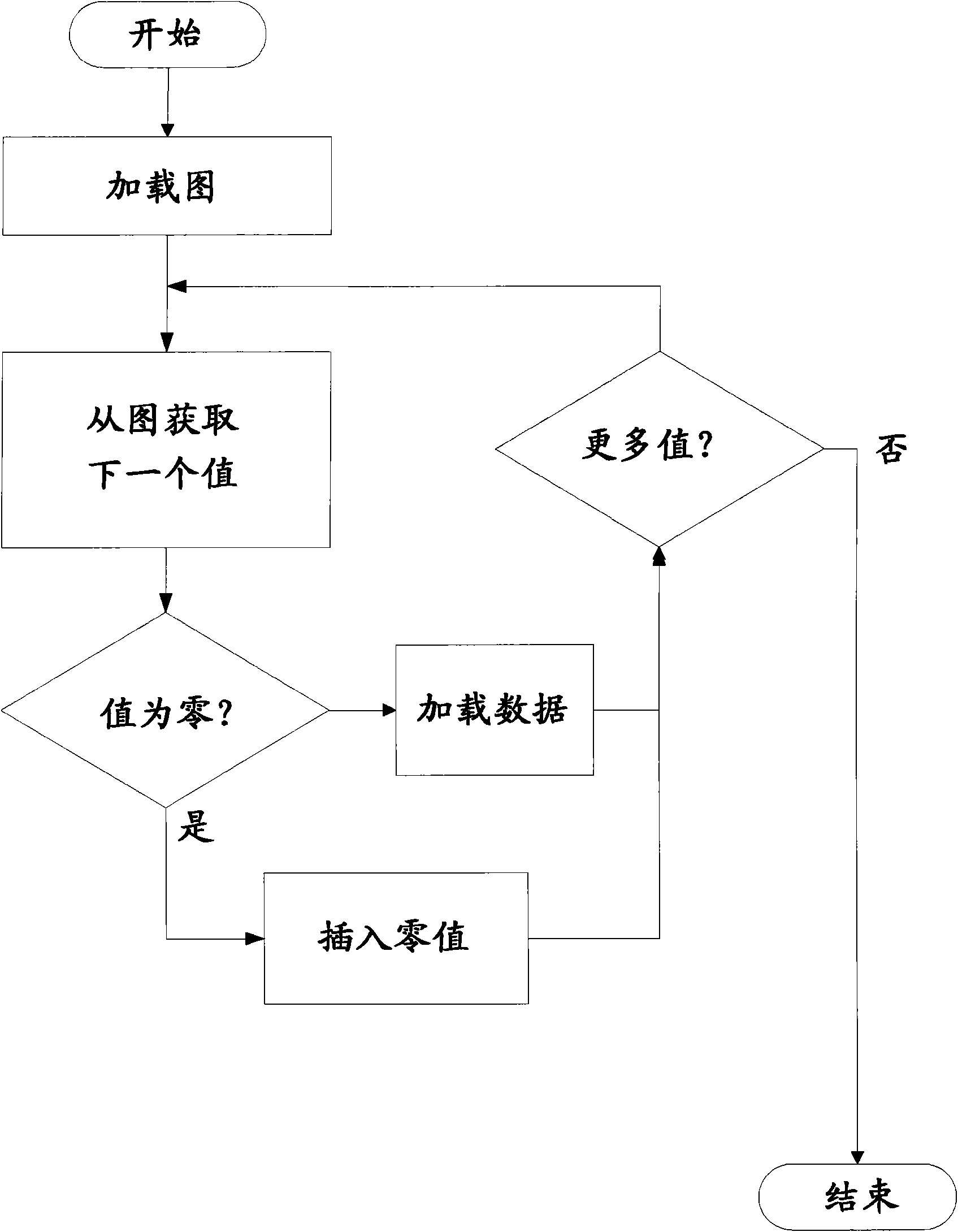

A circuit for compressing data and a processor employing same

The present application addresses a fundamental problem in the design of computing systems, that of minimising the cost of memory access. This is a fundamental limitation on the design of computer systems as regardless of the memory technology or manner of connection to the processor, there is a maximum limitation on how much data can be transferred between processor and memory in a given time, this is the available memory bandwidth and the limitation of compute power by available memory bandwidth is often referred to as the memory-wall. The solution provided creates a map of a data structureto be compressed, the map representing the locations of non-trivial data values in the structure (e.g. non-zero values) and deleting the trivial data values from the structure to provide a compressedstructure.

Owner:LINEAR ALGEBRA TECH LTD

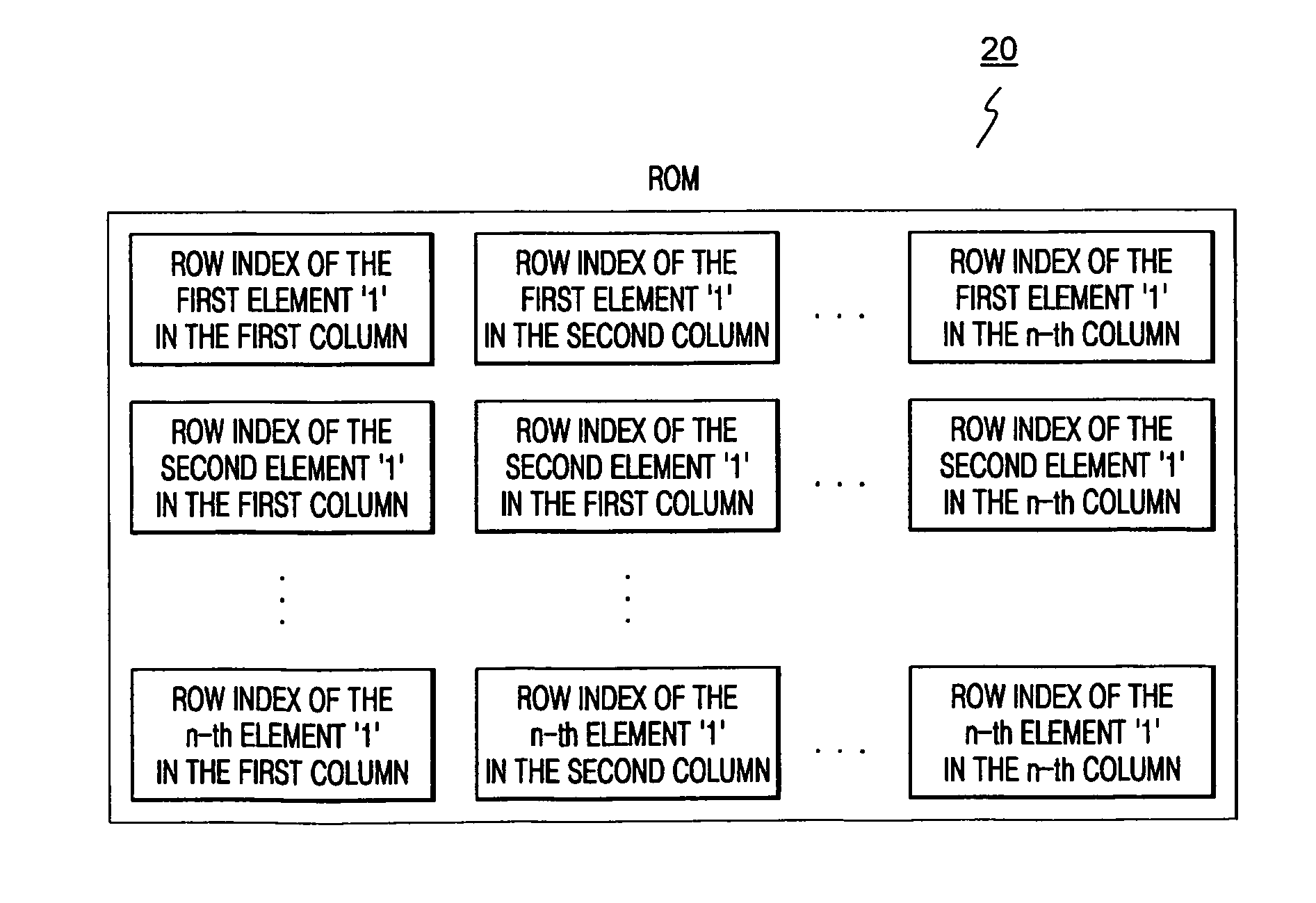

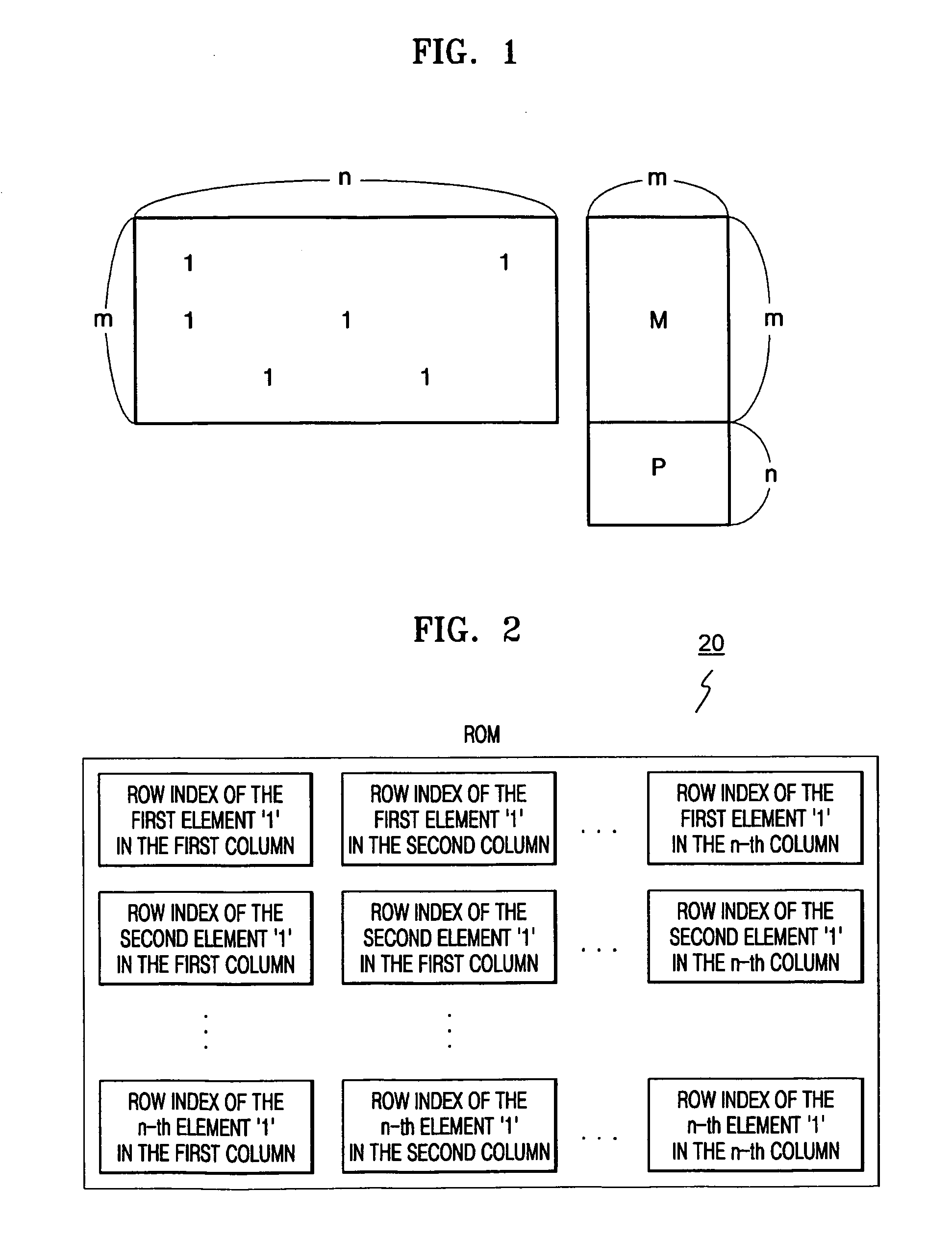

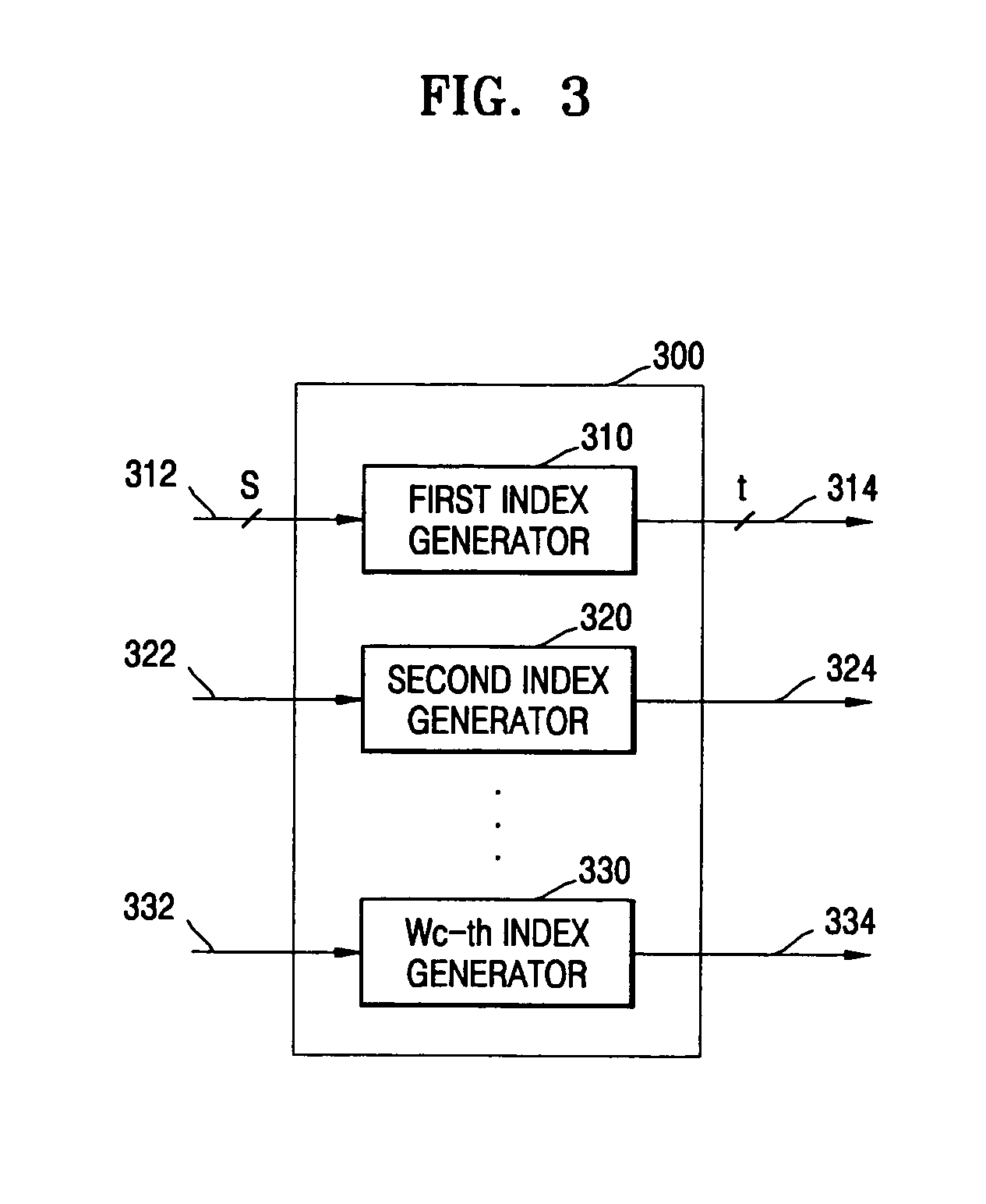

Methods and apparatus for constructing low-density parity check (LDPC) matrix

InactiveUS20060031745A1Large amount of cuttingCode conversionError correction/detection using multiple parity bitsParity-check matrixMatrix method

Owner:SAMSUNG ELECTRONICS CO LTD

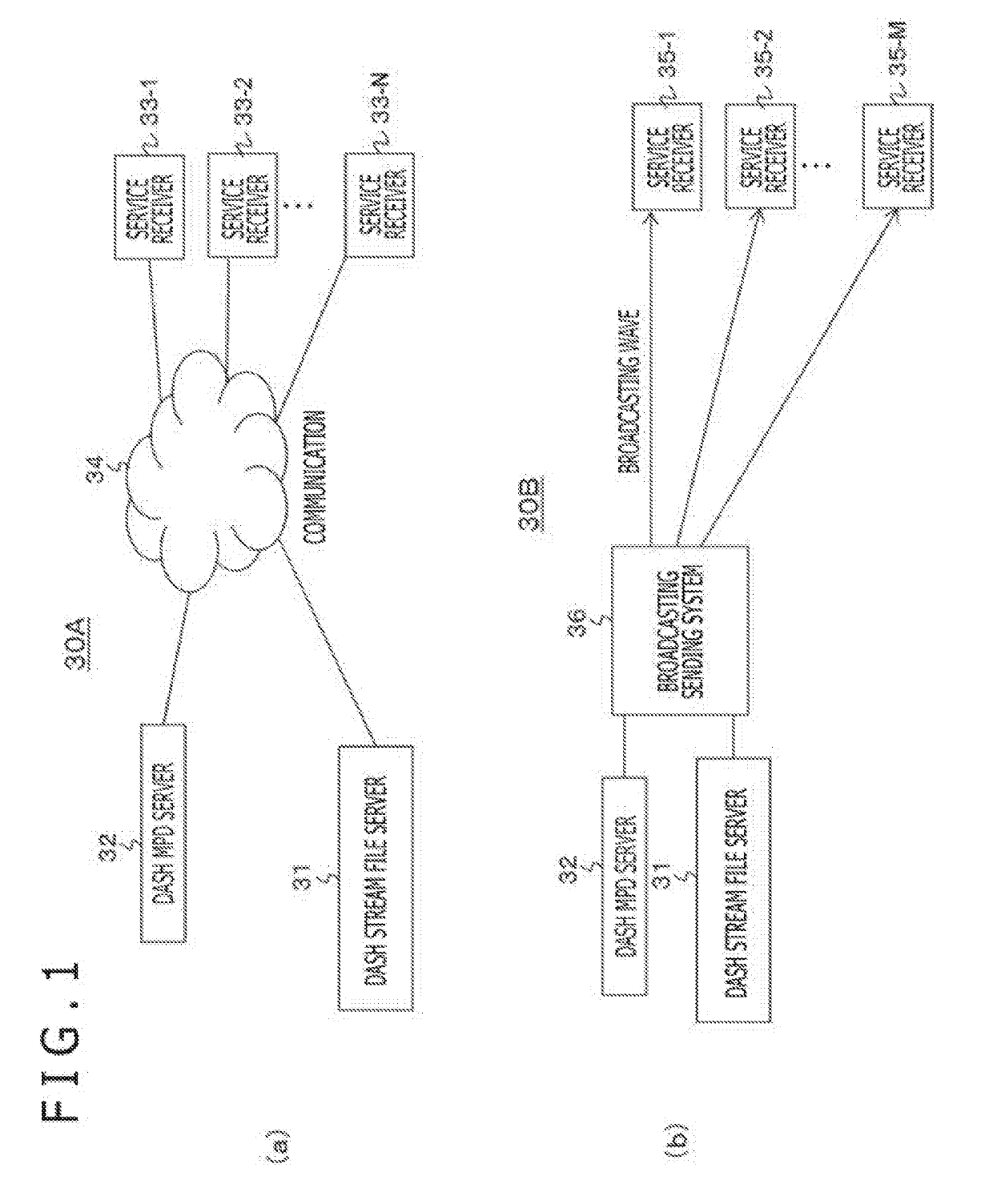

Transmission apparatus, transmission method, reception apparatus, and reception method

ActiveUS20190116386A1Backward compatibility is satisfactorilyIncrease frame rateCode conversionSelective content distributionHigh definitionComputer graphics (images)

Owner:SONY CORP

OFDM (Orthogonal Frequency Division Multiplexing) ultra wide band system compressed sampling method based on compressed sensing

InactiveCN106209111ACompressed sampling implementationStrong anti-noise abilityCode conversionObservation matrixWide band

The invention relates to an OFDM (Orthogonal Frequency Division Multiplexing) ultra wide band system compressed sampling method based on compressed sensing, belongs to the technical field of wireless communication, and aims at providing an optimization parallel segmented compressed sensing (OPSCS) scheme based on a Hadamard matrix according to an established segmented observation model, for a high-speed sampling problem of an OFDM ultra wide band system. The method is technically characterized in that a segmented observation matrix of any dimension is established by employing the Hadamard matrix, multiple ways of orthogonal or quasiorthogonal observing sequences are obtained, and a restricted isometry property is improved; and through adoption of a simplified orthogonal matching pursuit algorithm, iterative operation is avoided. According to the method, compressed sampling of the OFDM ultra wide band system is effectively realized, moreover, the method has the advantage of high noise immunity, and the system performance superior to that realized through adoption of existing compressed sampling and even Nyquist rate sampling can be realized.

Owner:TIANJIN POLYTECHNIC UNIV

Popular searches

Memory systems Multi-frequency code systems Record information storage Special data processing applications Redundant operation error correction Wireless communication Picture reproducers using cathode ray tubes Picture reproducers using projection devices Digital video signal modification Transmission

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap