Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

49 results about "Device material" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor devices are electronic components that exploit the electronic properties of semiconductor materials, principally silicon, germanium, and gallium arsenide, as well as organic semiconductors. Semiconductor devices have replaced thermionic devices (vacuum tubes) in most applications.

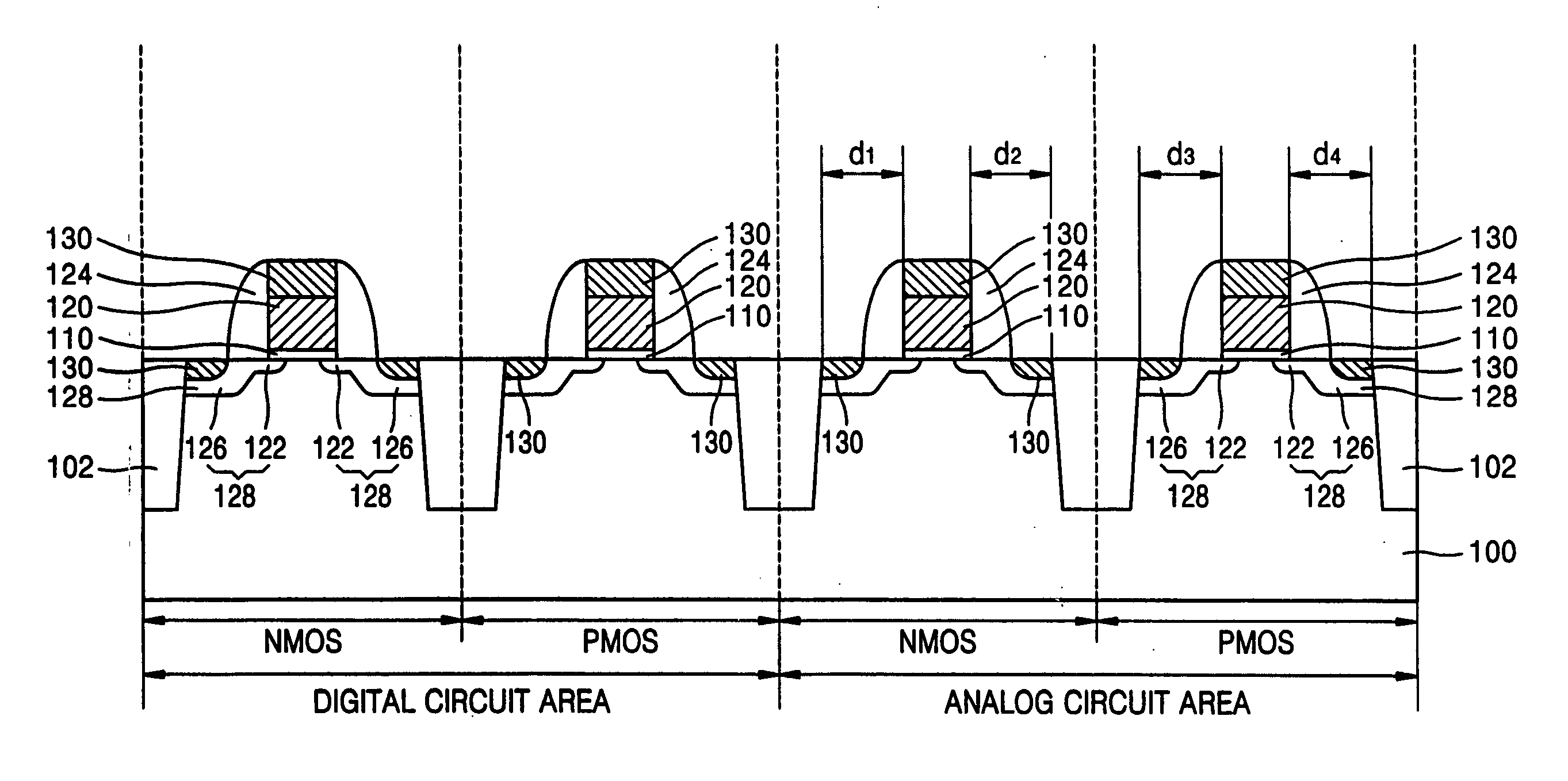

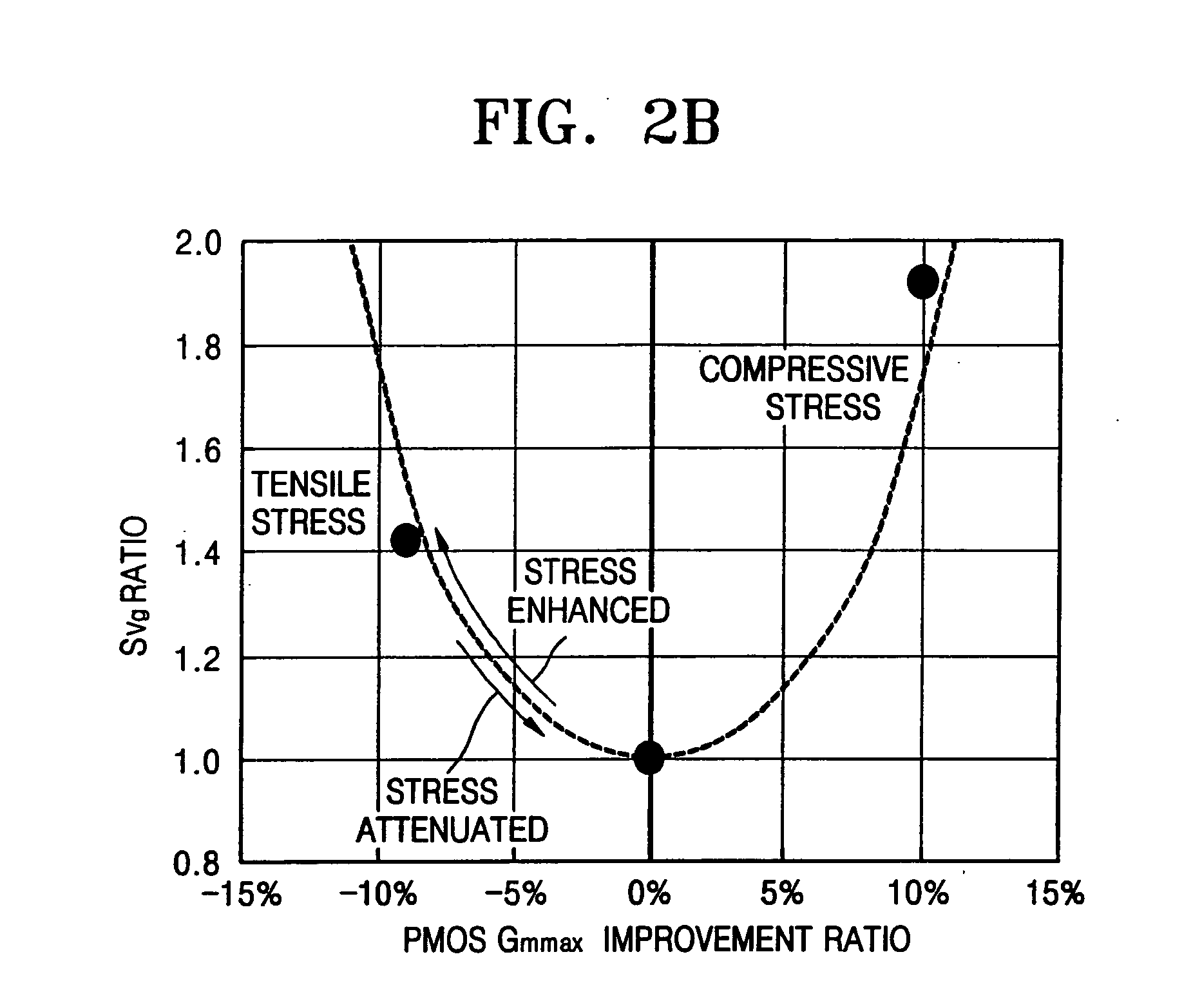

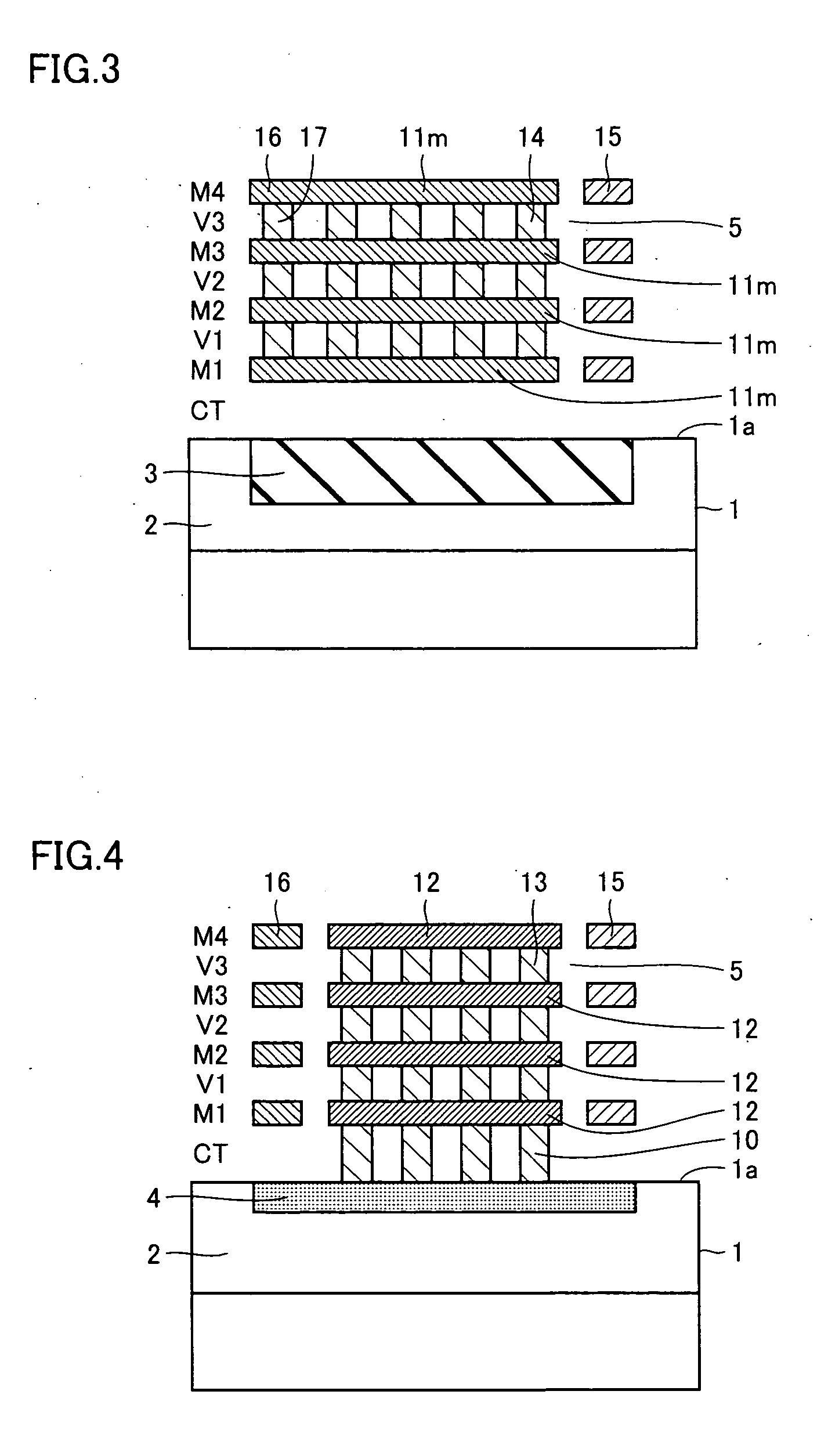

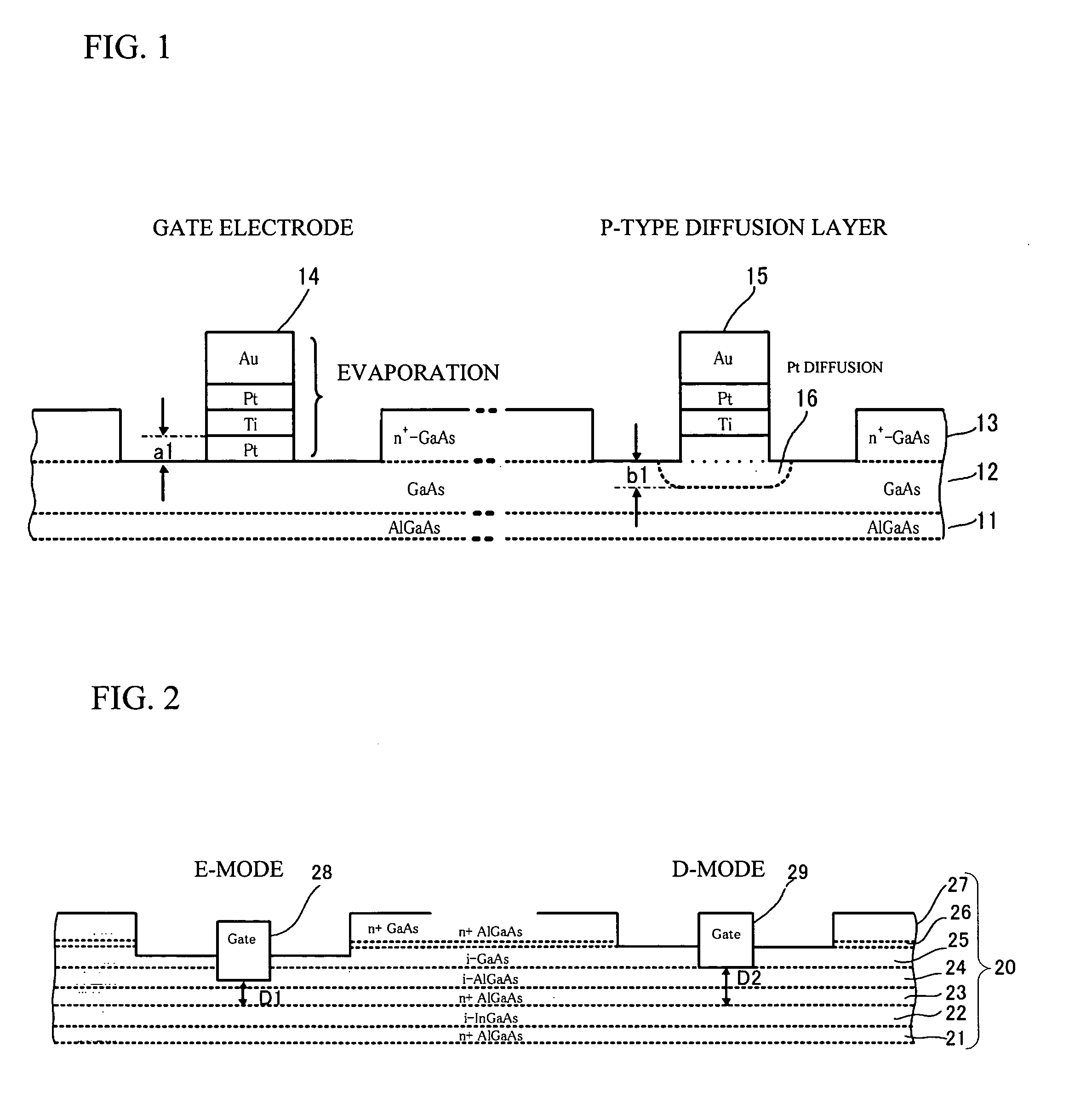

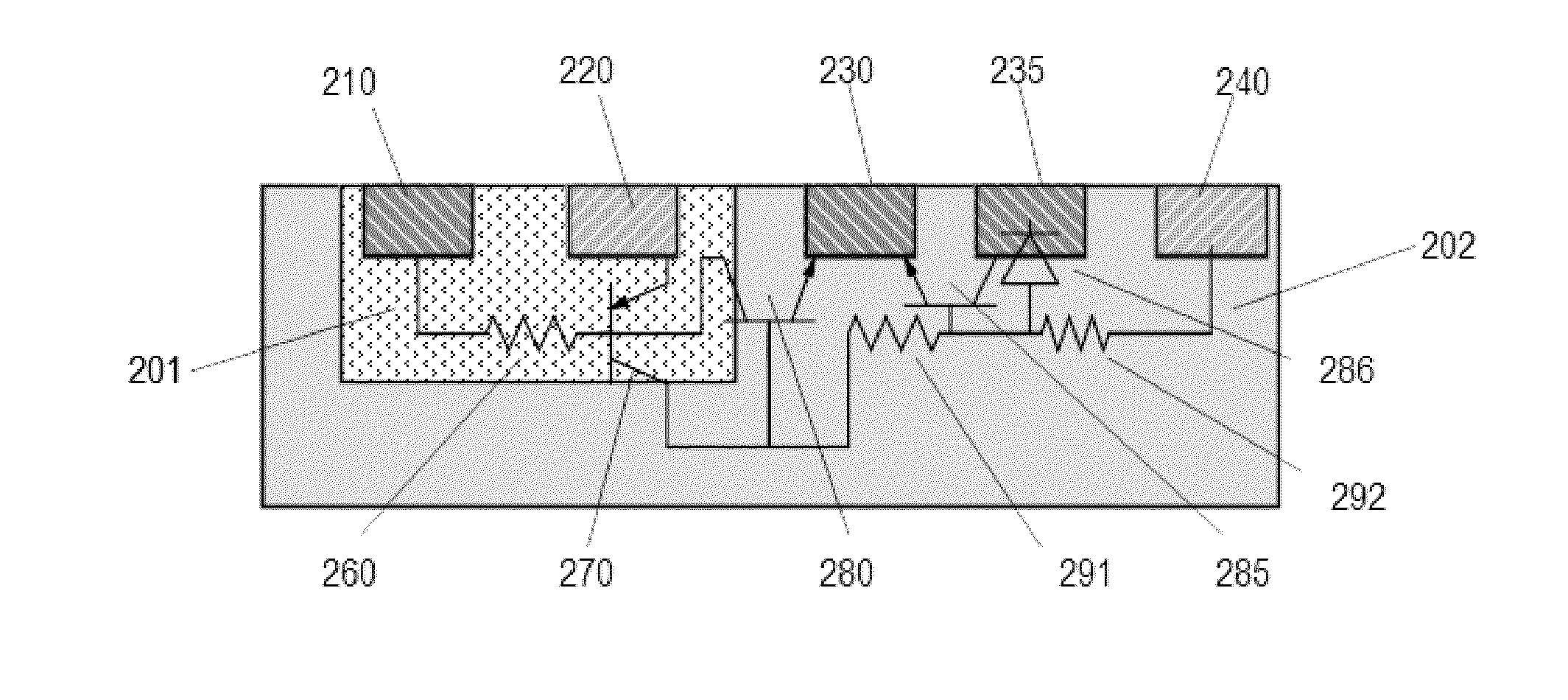

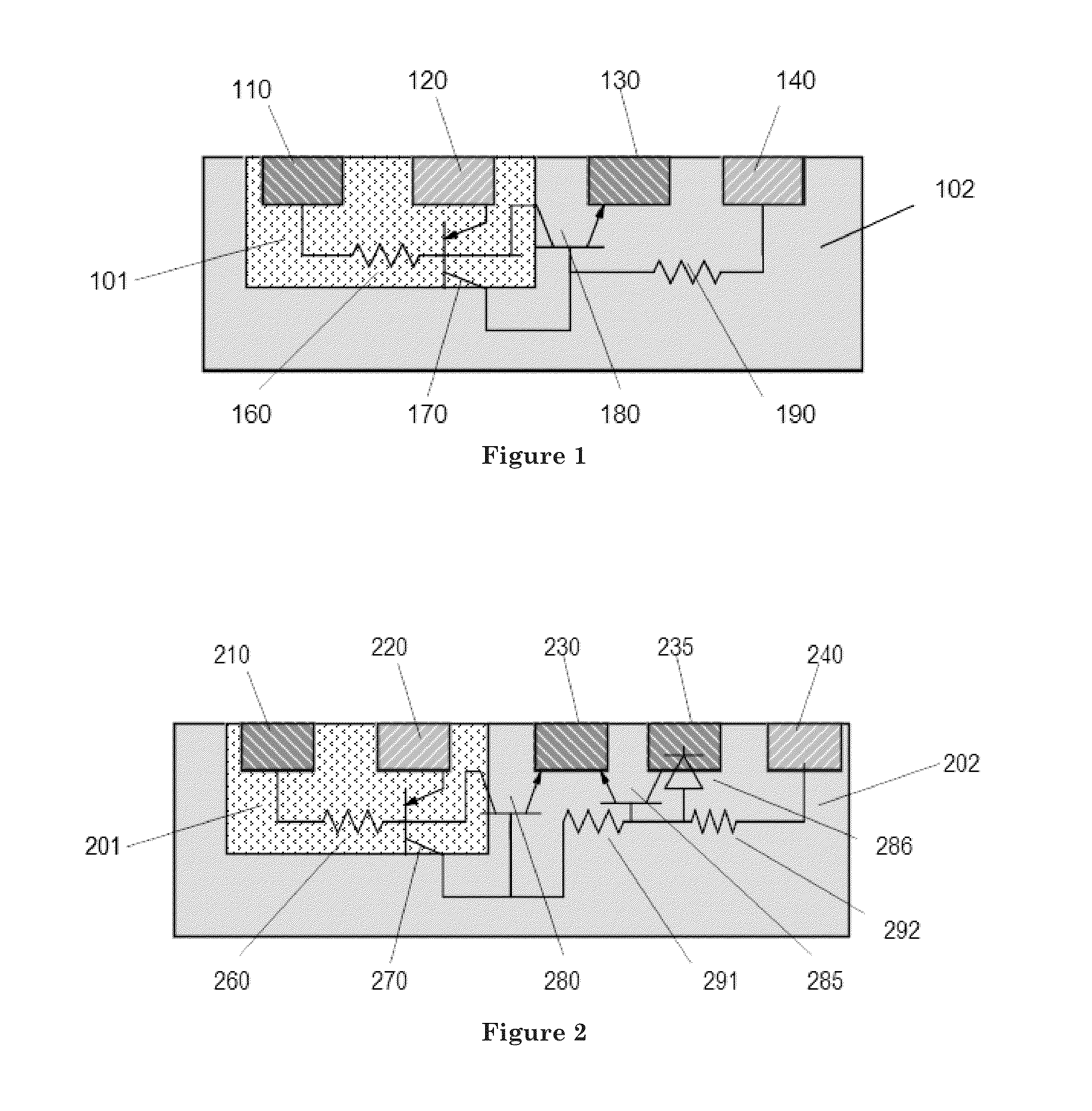

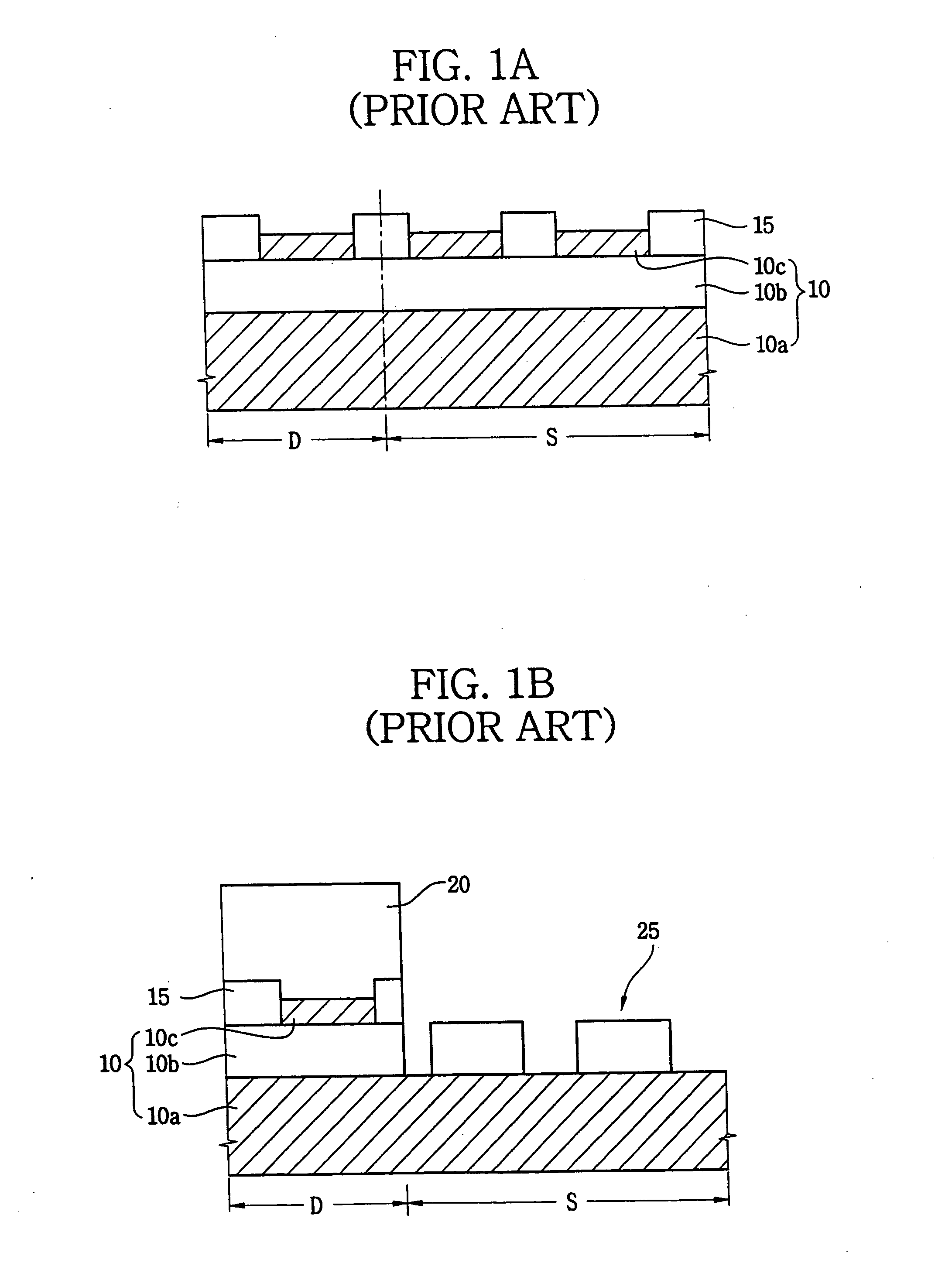

Low noise and high performance LSI device, layout and manufacturing method

ActiveUS20050218455A1Improve device performanceReduce the impactTransistorSolid-state devicesLow noiseLow speed

Owner:SAMSUNG ELECTRONICS CO LTD

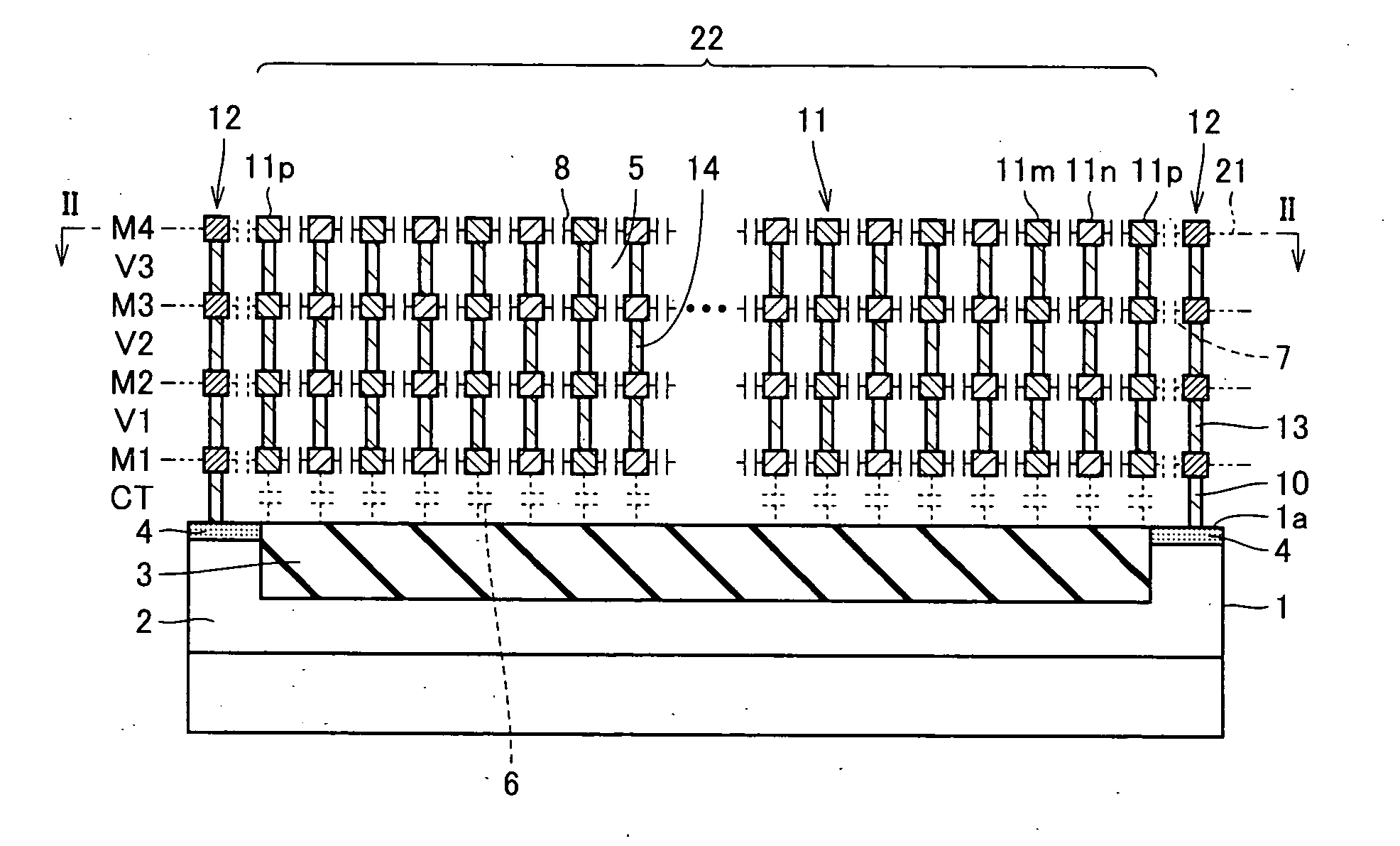

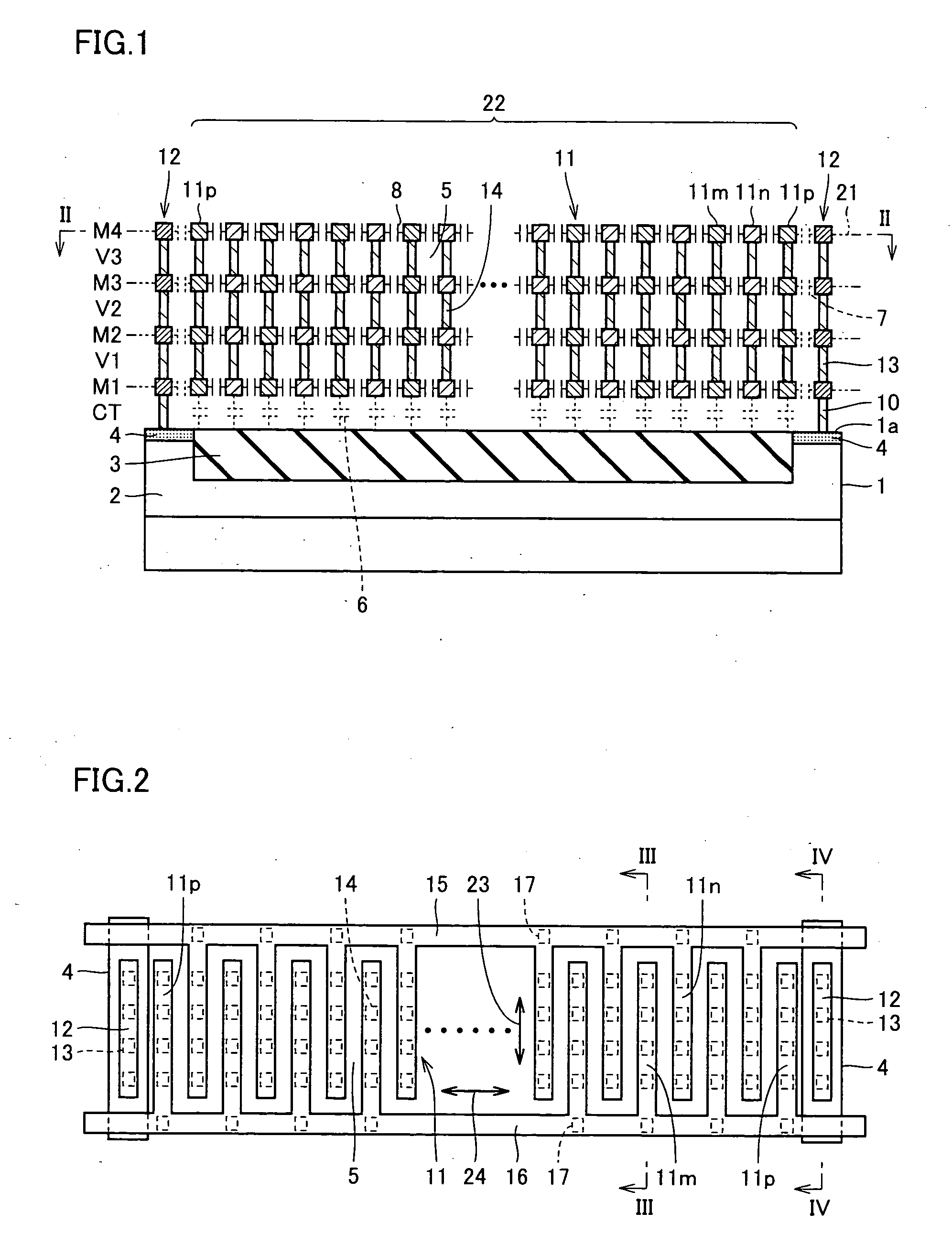

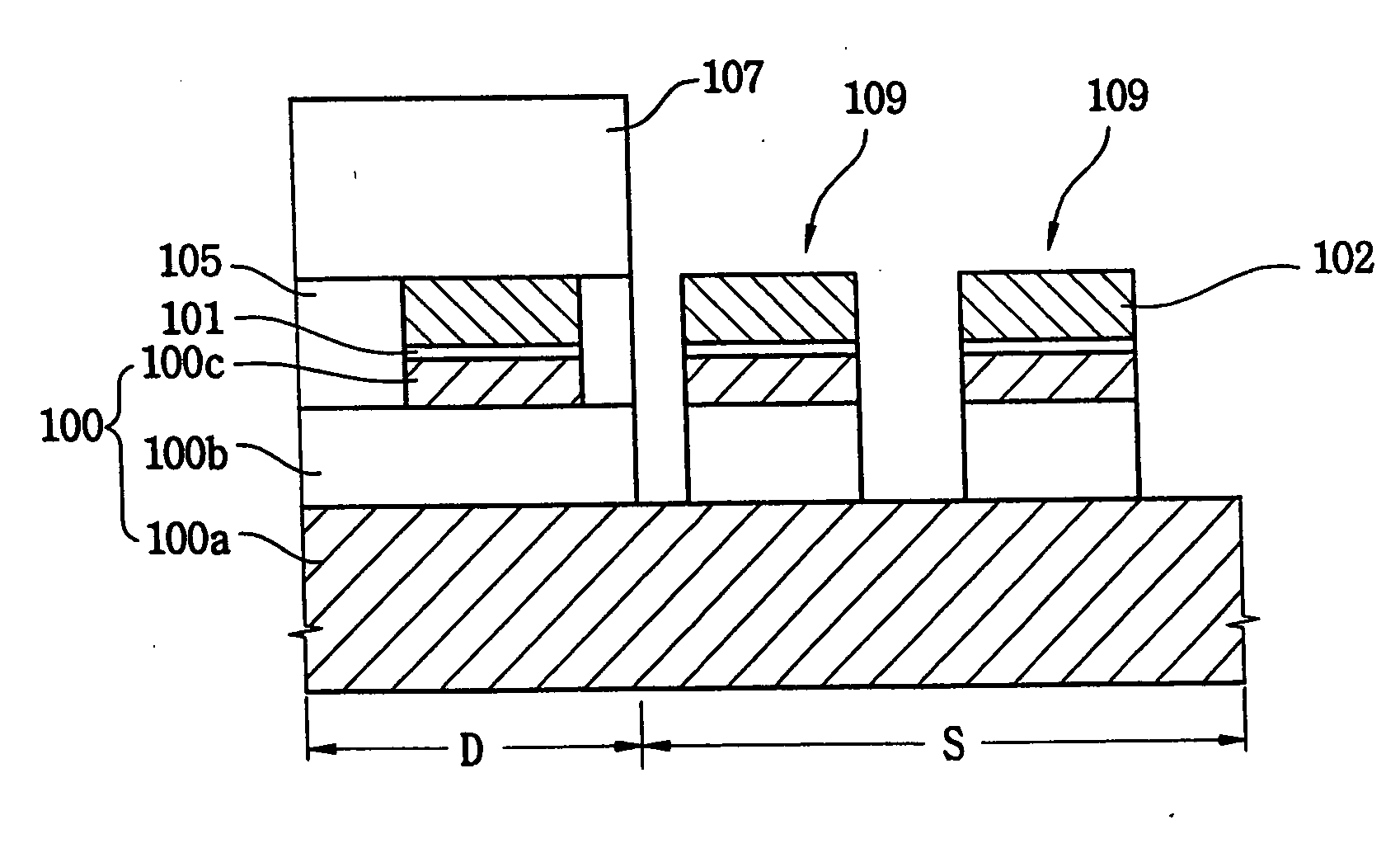

Semiconductor device

ActiveUS20050145987A1Reduce distractionsDesired characteristicTransistorSemiconductor/solid-state device detailsCapacitanceDevice material

Owner:RENESAS ELECTRONICS CORP +1

Semiconductor device and method of manufacturing the same, circuit board and electronic instrument

InactiveUS6841849B2Not easily oxidizedSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A depression is formed from a first surface of a semiconductor substrate on which is formed an integrated circuit. An insulating layer is provided on the inner surface of the depression. A first conductive portion is provided on the inside of the insulating layer. A second conductive portion is formed on the inside of the insulating layer and over the first conductive portion, of a different material from the first conductive portion. The first conductive portion is exposed from a second surface of the semiconductor substrate opposite to the first surface.

Owner:ADVANCED INTERCONNECT SYST LTD

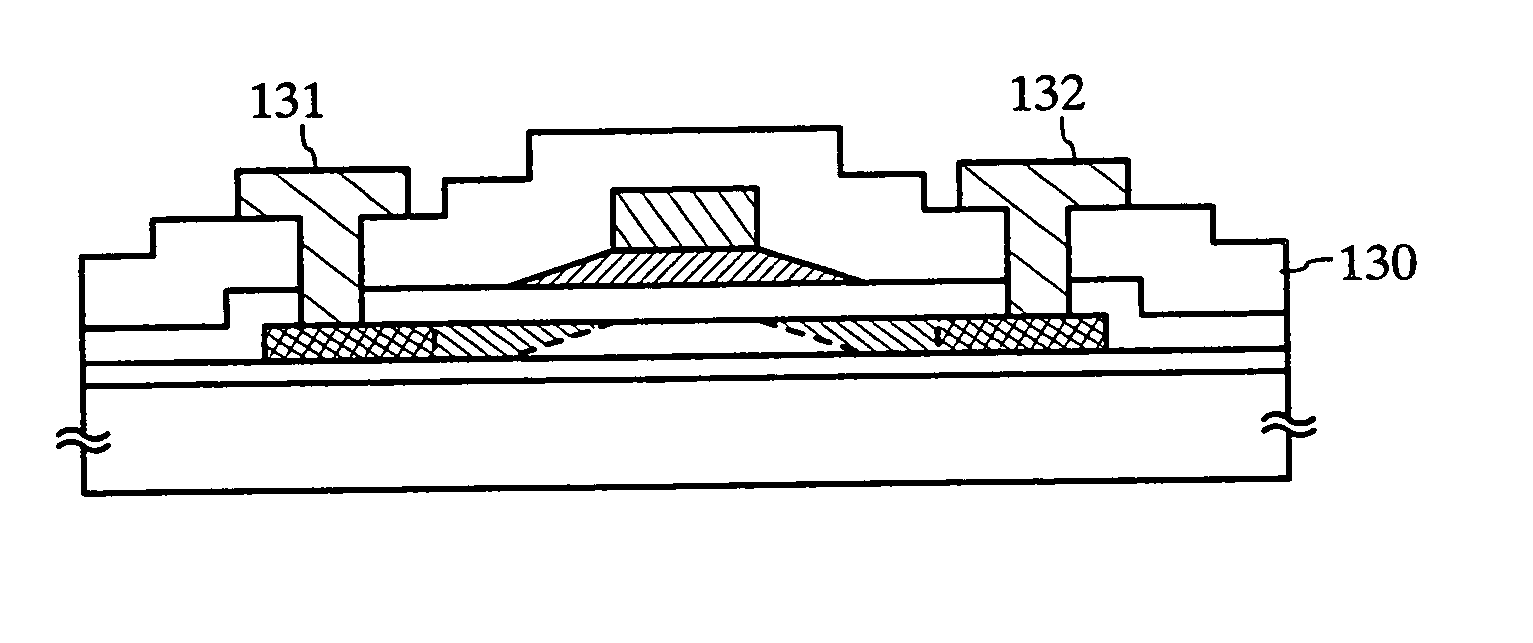

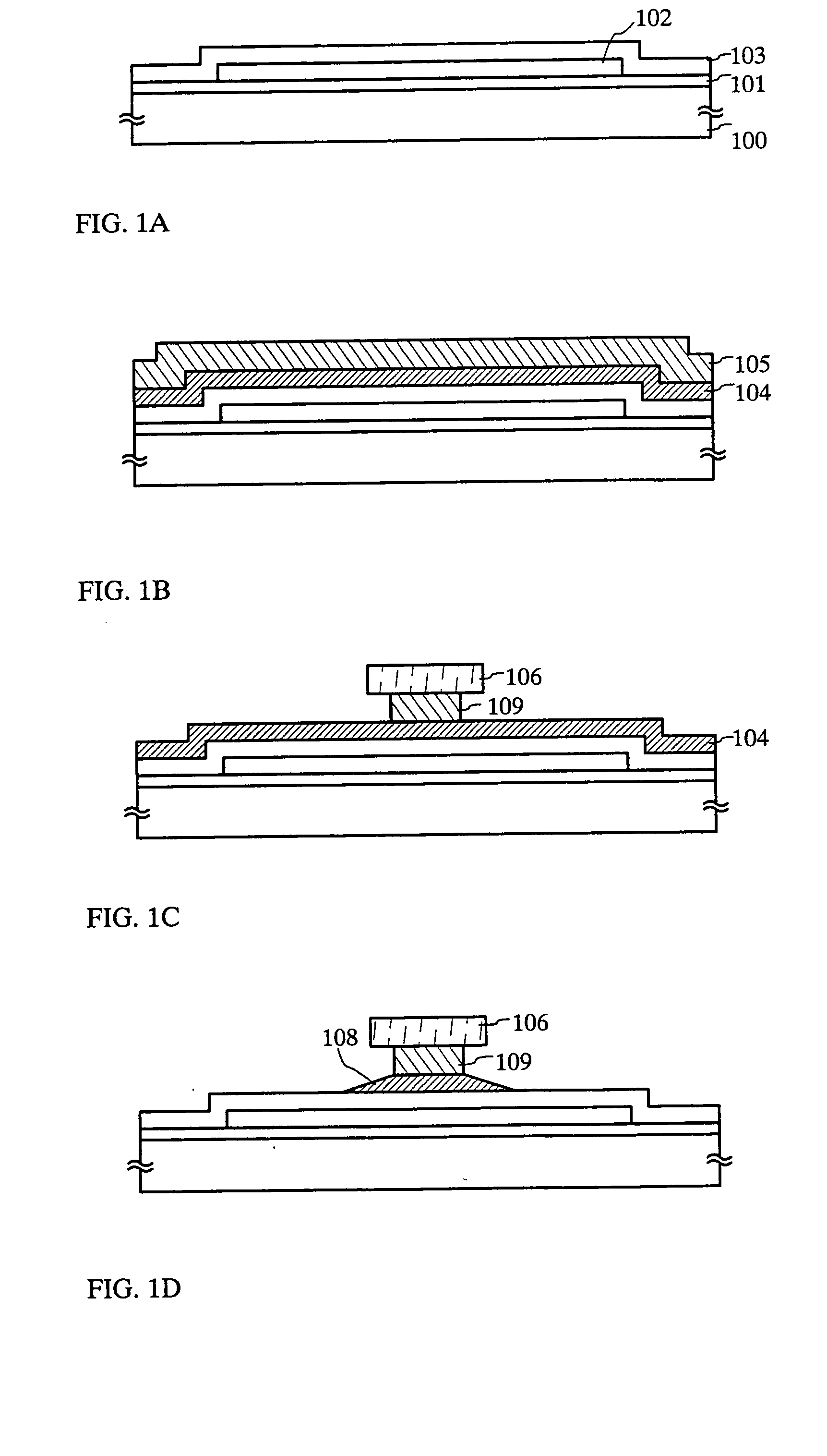

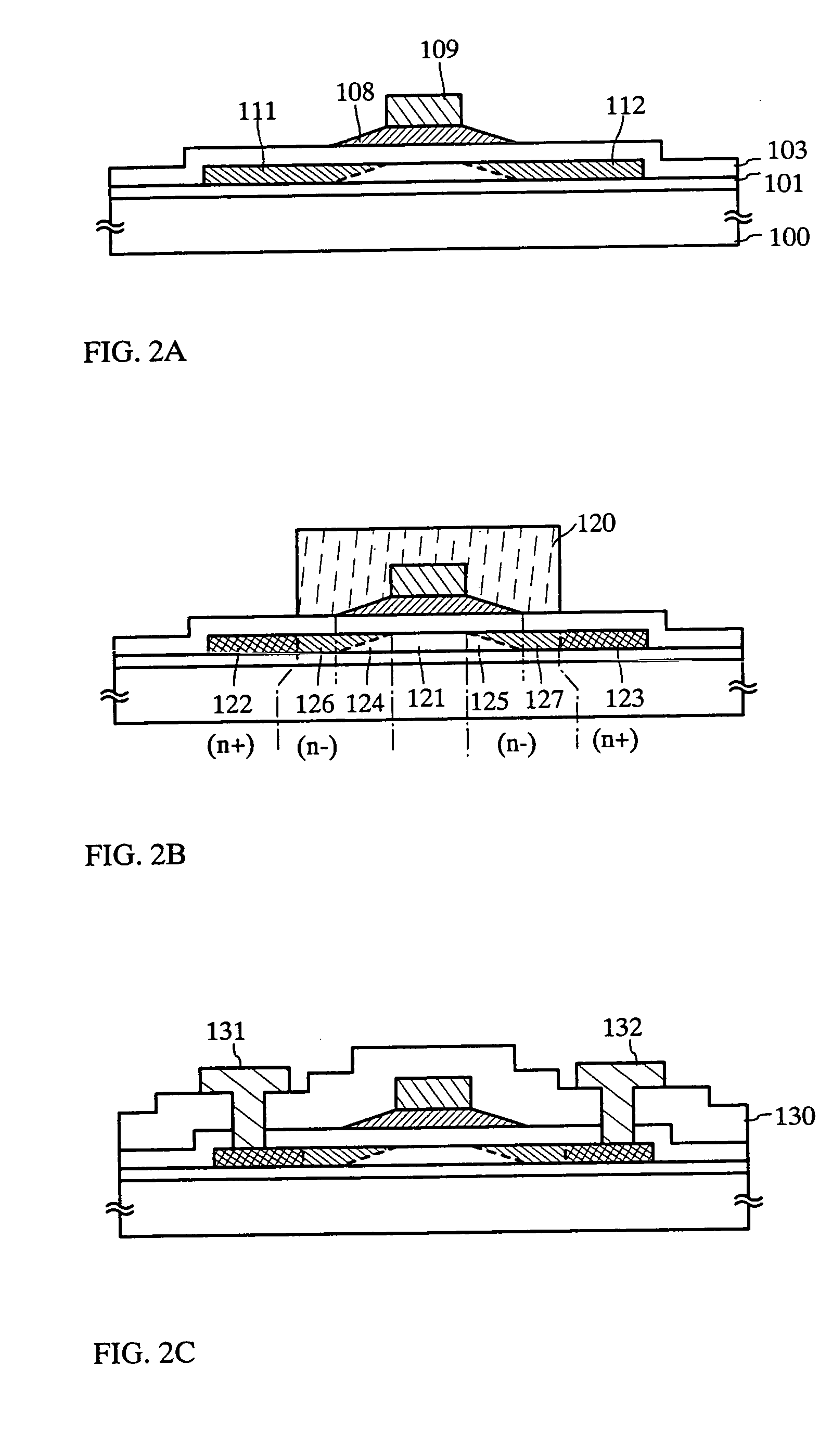

Method of fabricating a semiconductor device

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS20070001308A1High mechanical strengthAvoid failureSemiconductor/solid-state device detailsSolid-state devicesSemiconductorDevice material

Owner:PANASONIC CORP

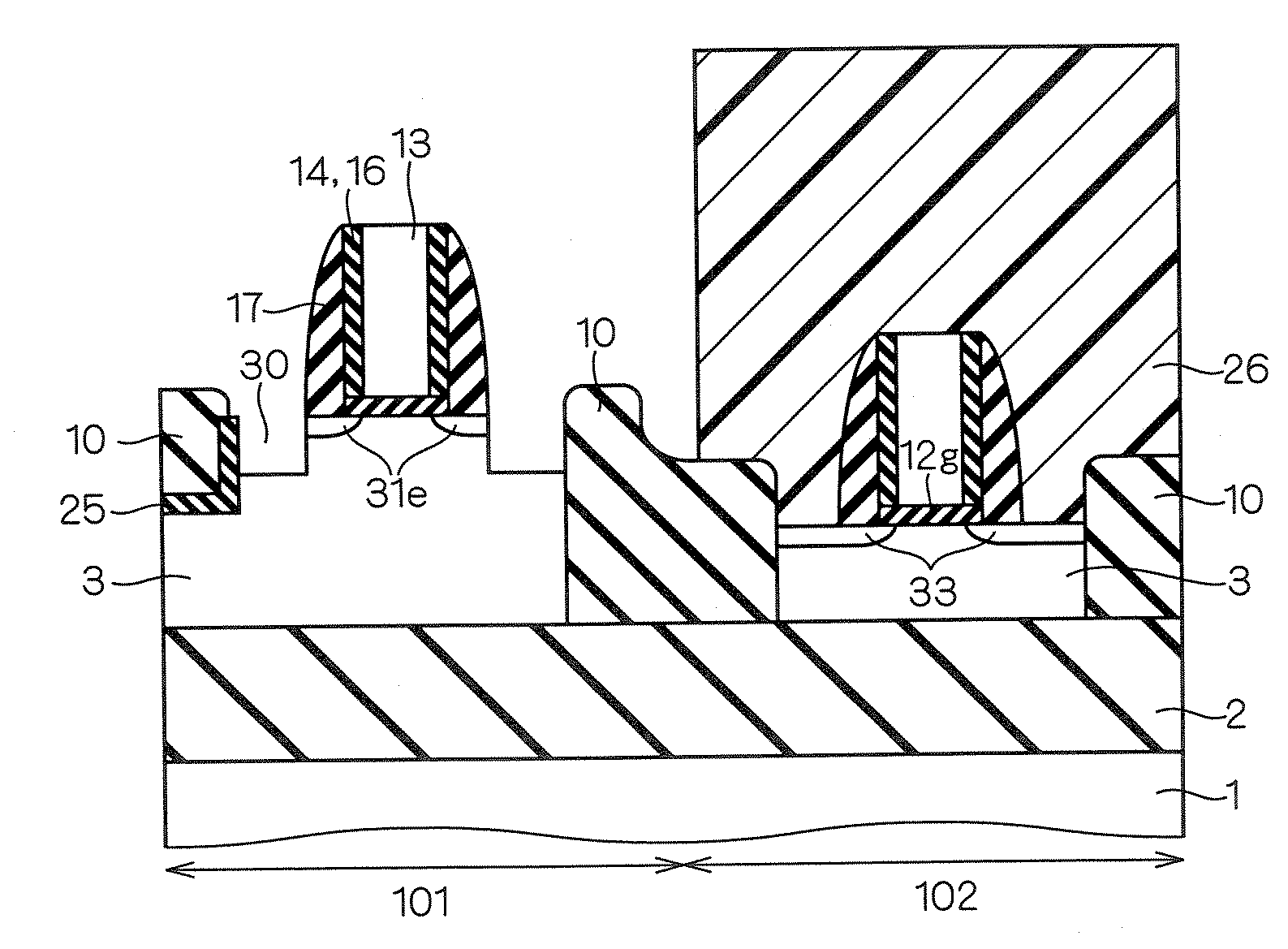

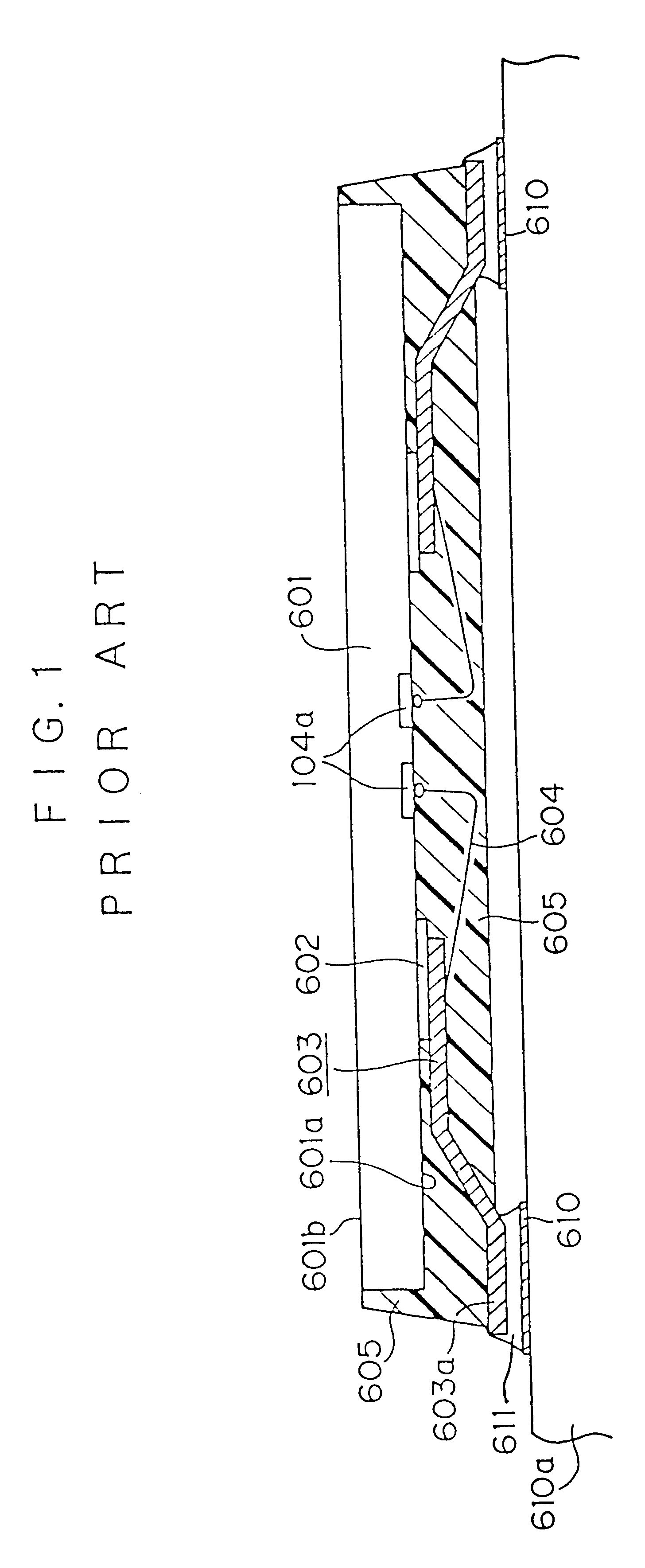

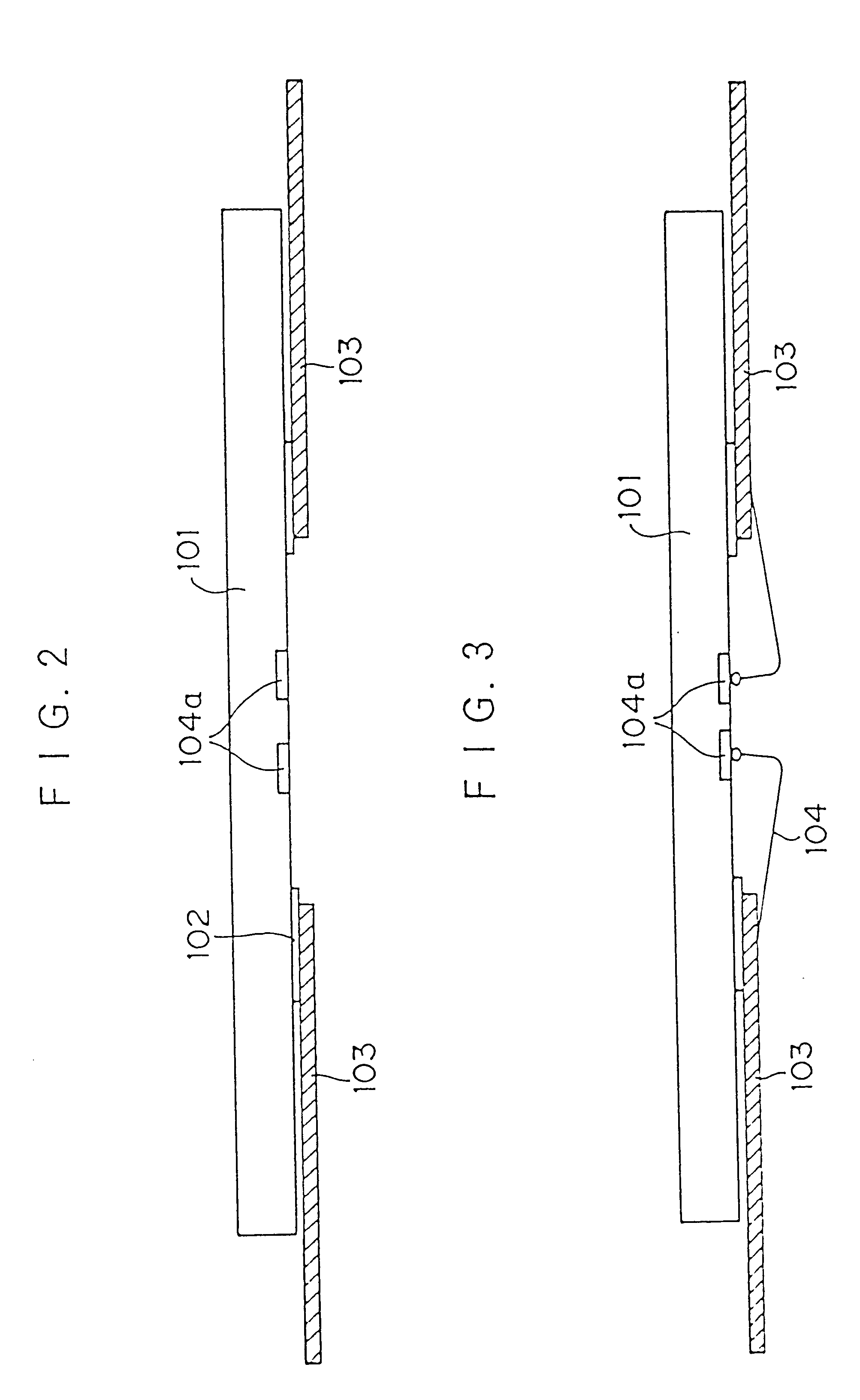

Semiconductor device and manufacturing method for the same

InactiveUS20070176235A1Improve stabilityReduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingBody regionPhysics

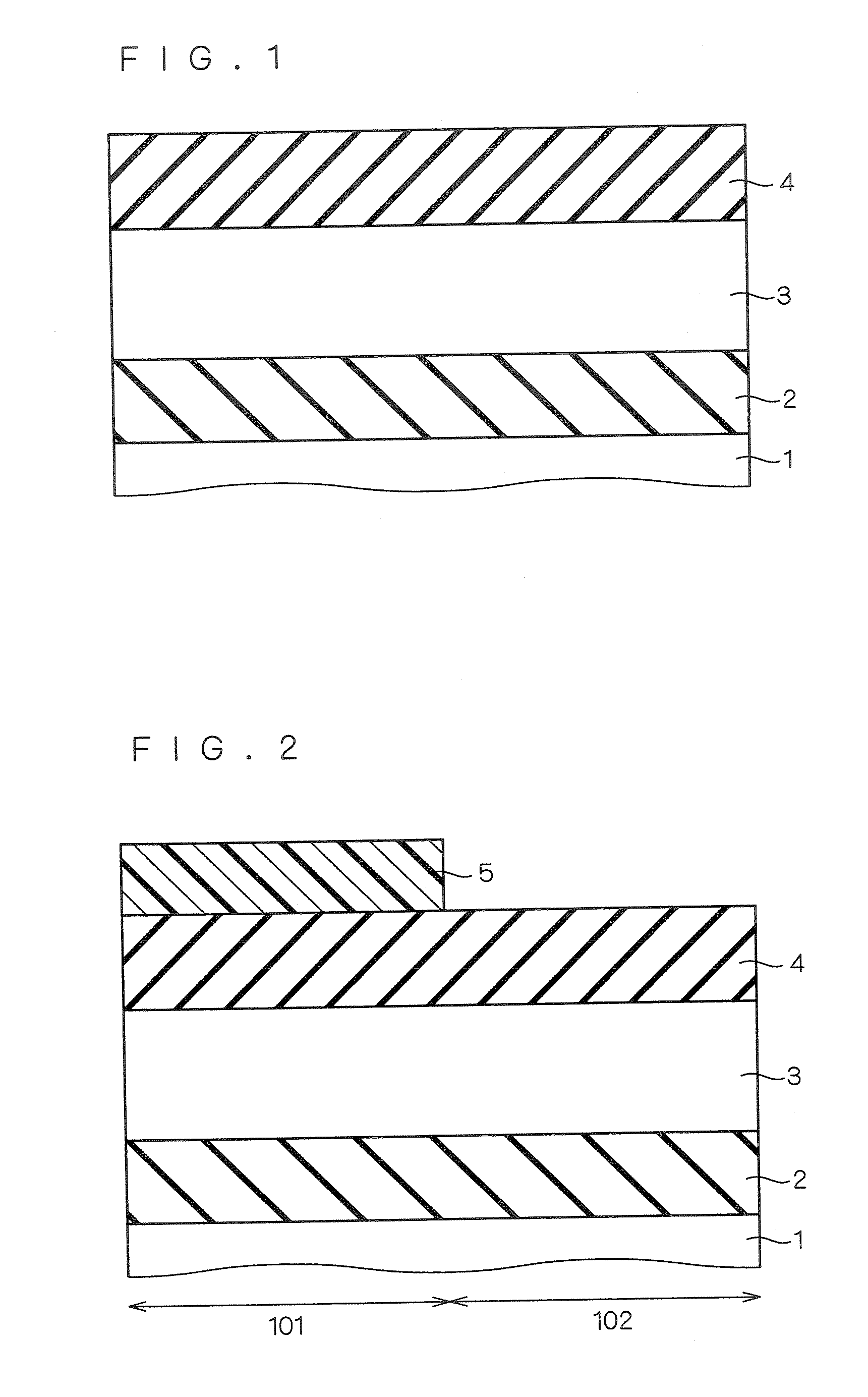

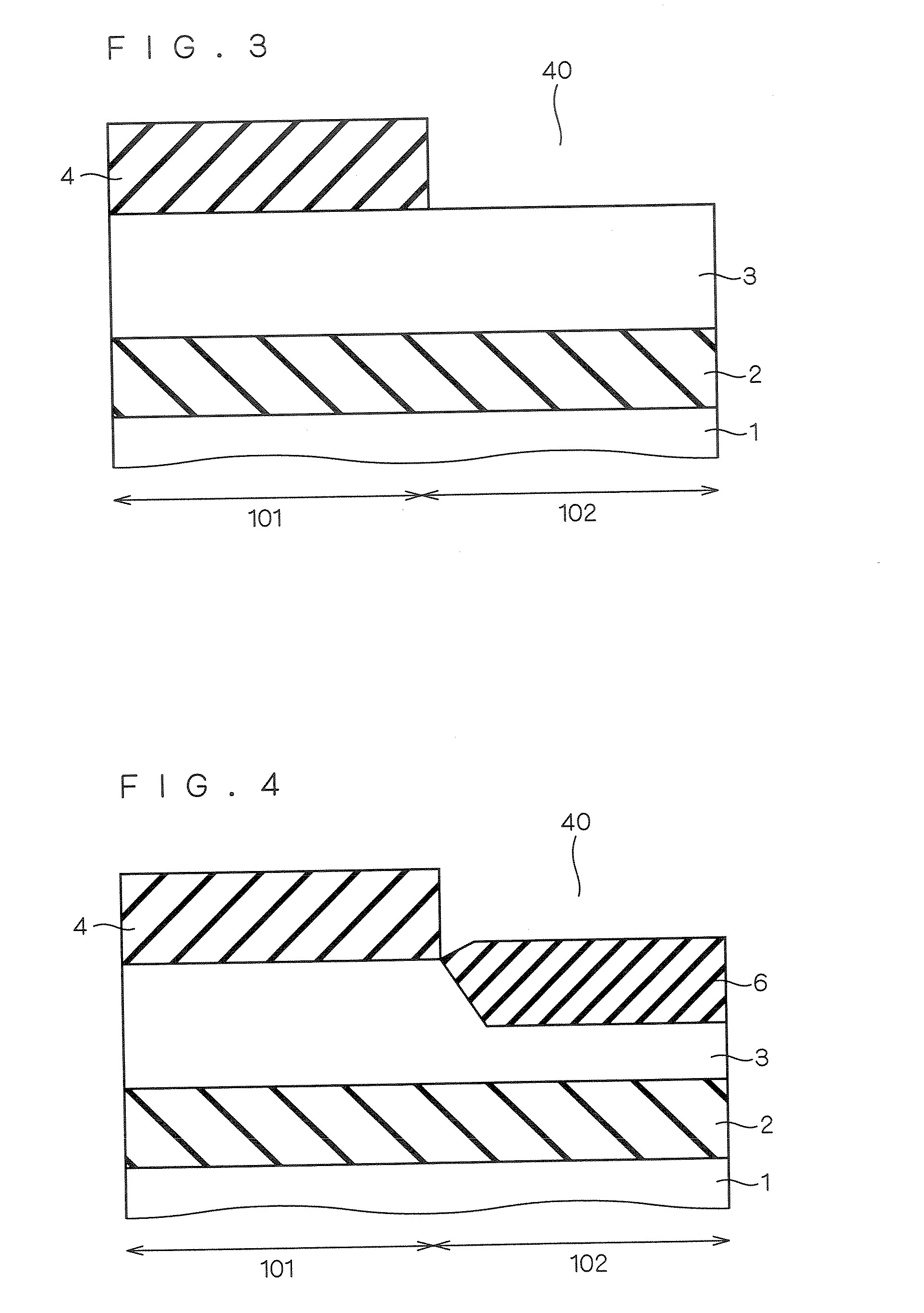

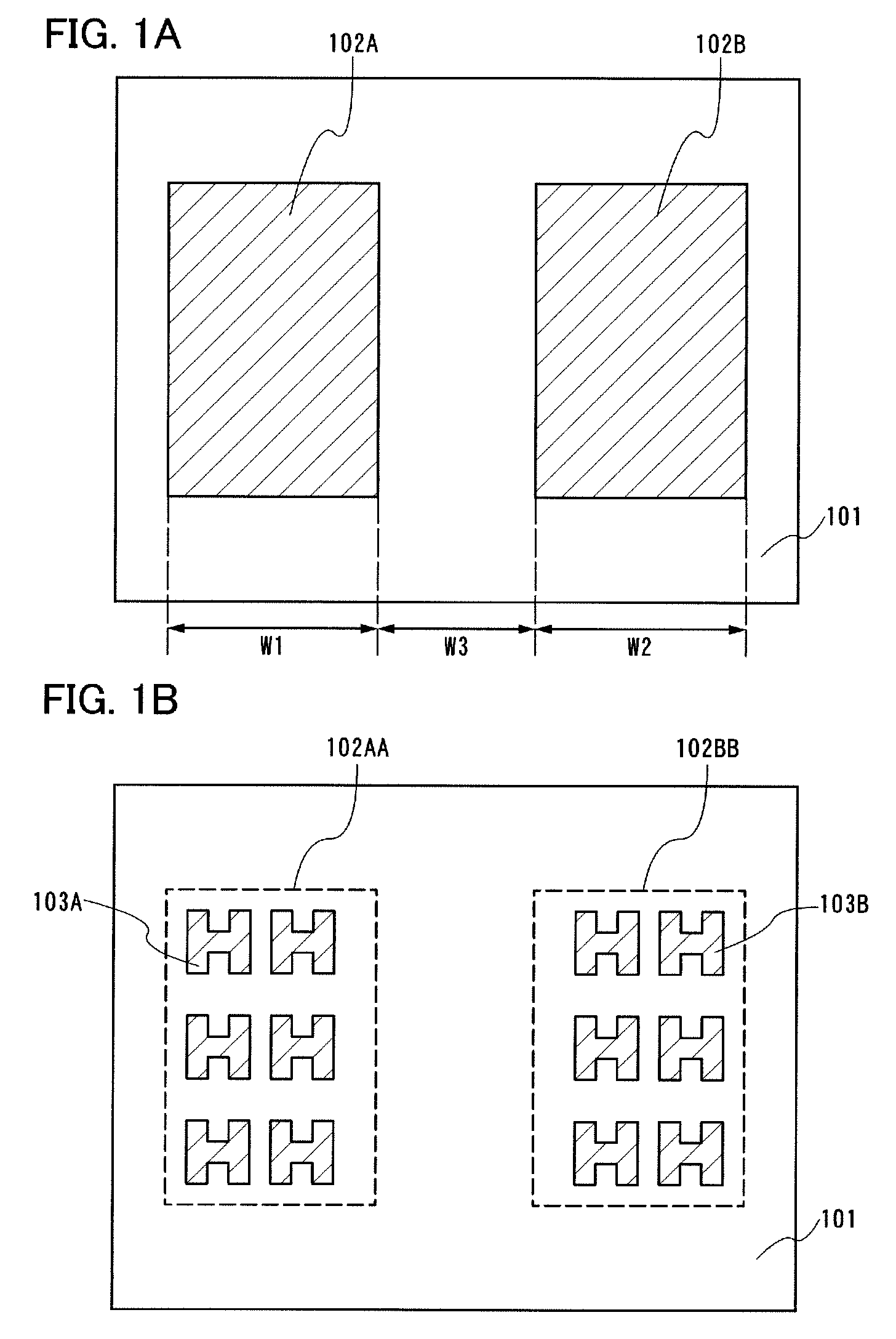

In a semiconductor device, a body thick film transistor and a body thin film transistor having a different body film thickness are formed on the same SOI substrate (silicon support substrate, buried oxide film and silicon layer). The body film is formed to be relatively thick in the body thick film transistor, which has a recess structure where the level of the surface of the source / drain regions is lower than the level of the surface of the body region, and thus, the SOI film in the source / drain regions is formed to be as thin as the SOI film in the body thin film transistor. On the other hand, the entirety of the SOI film is formed to have a relatively thin film thickness in the body thin film transistor. In addition, the source / drain regions are formed to penetrate through the silicon layer.

Owner:RENESAS ELECTRONICS CORP

Method for manufacturing semiconductor device

InactiveUS20090001387A1Easy to operateImprove current characteristicsTransistorSolid-state devicesDevice materialSingle crystal

Owner:SEMICON ENERGY LAB CO LTD

Techniques for operating semiconductor devices

Owner:IBM CORP

Semiconductor device and manufacturing method thereof

InactiveUS20060197230A1Increase capacityEasy to operateTransistorSemiconductor/solid-state device detailsDevice materialConductive materials

A semiconductor device comprises a first insulating film formed over a semiconductor substrate, a second insulating film formed on the first insulating film, a contact plug made of a conductive material vertically penetrating the first and second insulating films and extending on the second insulating film, and a conductor film in contact with the upper surface of the contact plug and part of the second insulating film. This construction makes it possible to form minute via-holes in a mass-production line without increasing parasitic capacity, increasing the number of manufacturing steps, and generating defects.

Owner:FUJITSU SEMICON LTD

Nitride based semiconductor device

ActiveUS20050285125A1Improve efficiencyLow light efficiencyNanoopticsSemiconductor devicesDevice materialQuantum well

The present invention provides a nitride semiconductor device comprising an active layer of a quantum well structure, a first conductive clad layer and a second conductive clad layer. The first conductive clad layer is made of the quaternary nitride semiconductor InAlGaN having a lattice constant equal to or larger than that of the active layer and includes a first nitride semiconductor layer having an energy band gap larger than that of the active layer, a second nitride semiconductor layer having an energy band gap smaller than that of the first nitride semiconductor layer and a third nitride semiconductor layer having an energy band gap larger than that of the second nitride semiconductor layer, sequentially closer to the active layer.

Owner:SAMSUNG ELECTRONICS CO LTD

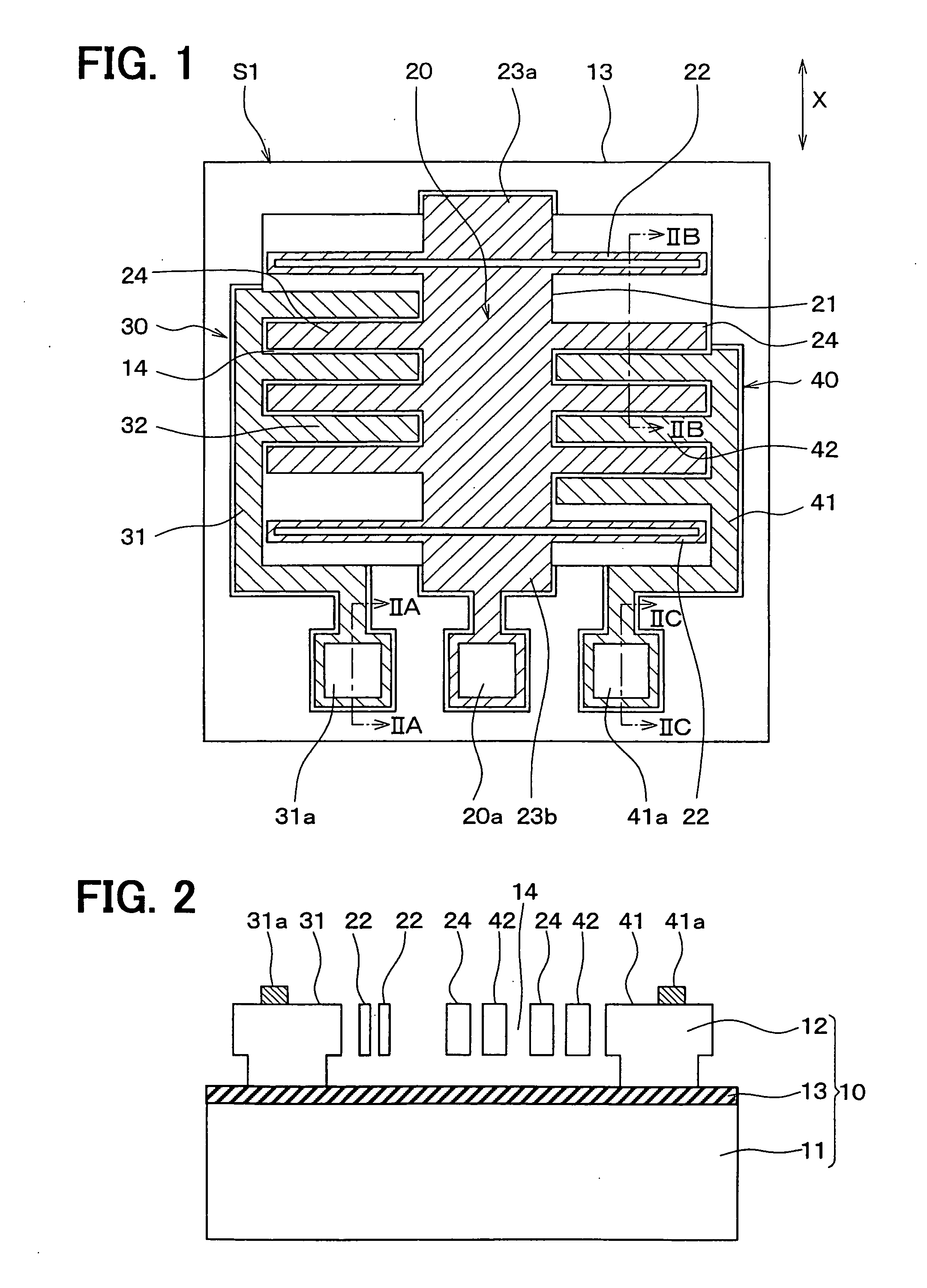

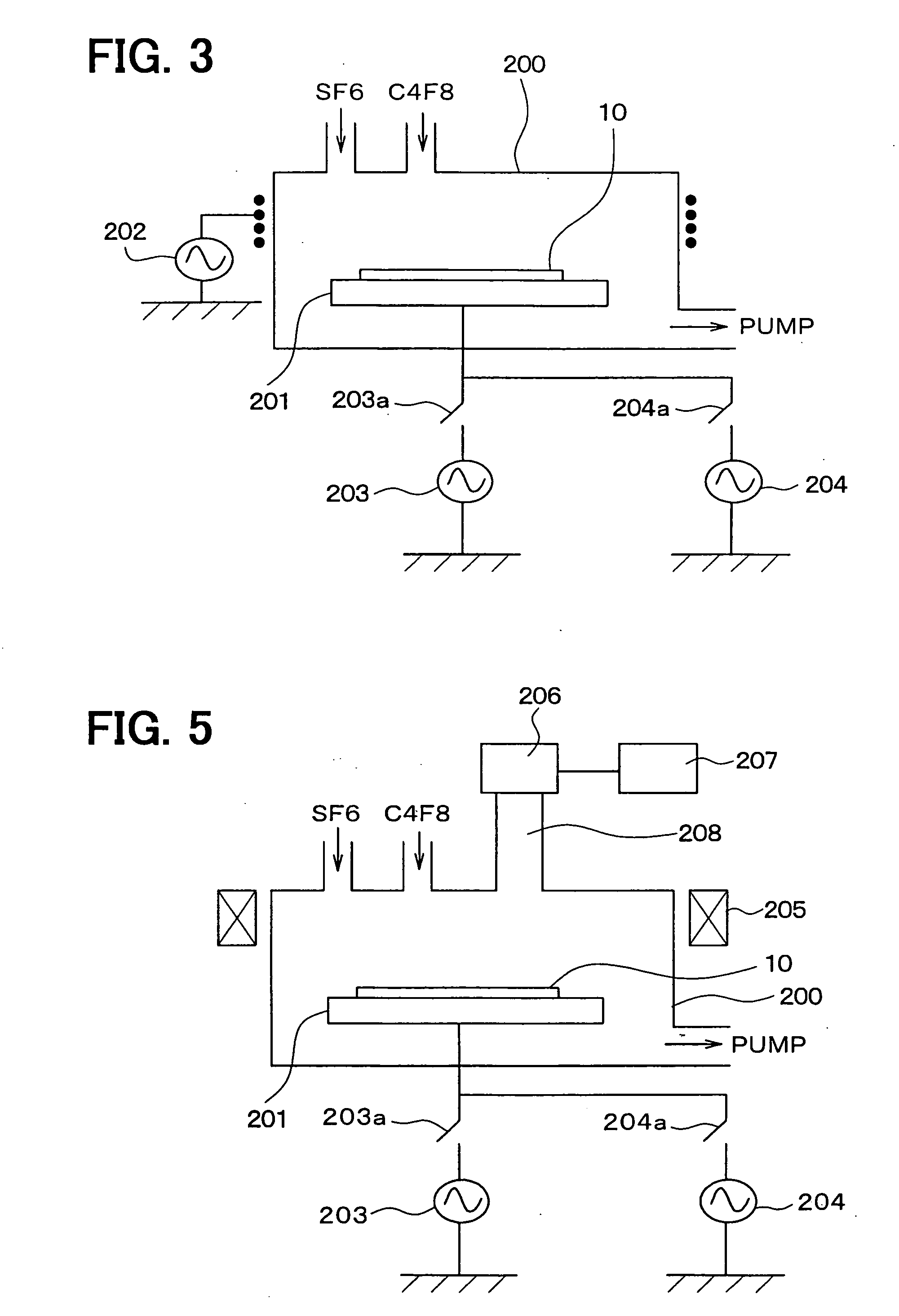

Method for manufacturing movable portion of semiconductor device

ActiveUS20050054153A1Short processing timeEasy to disassembleTransistorDecorative surface effectsInsulation layerDevice material

Owner:DENSO CORP

Method of forming metal interconnect of semiconductor device

InactiveUS20060024941A1Avoid analysisSemiconductor/solid-state device manufacturingMetal interconnectDevice material

Owner:SAMSUNG ELECTRONICS CO LTD

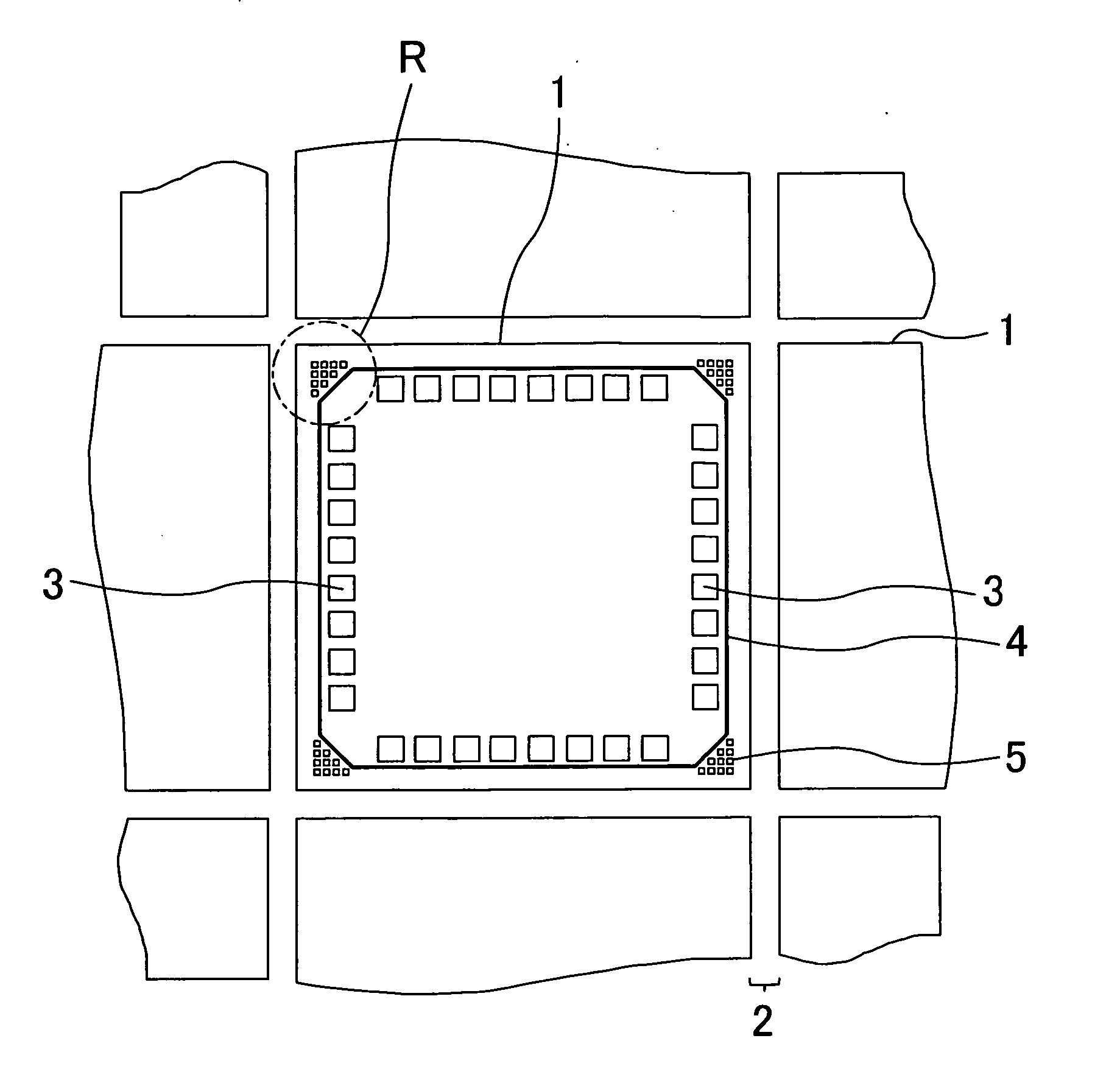

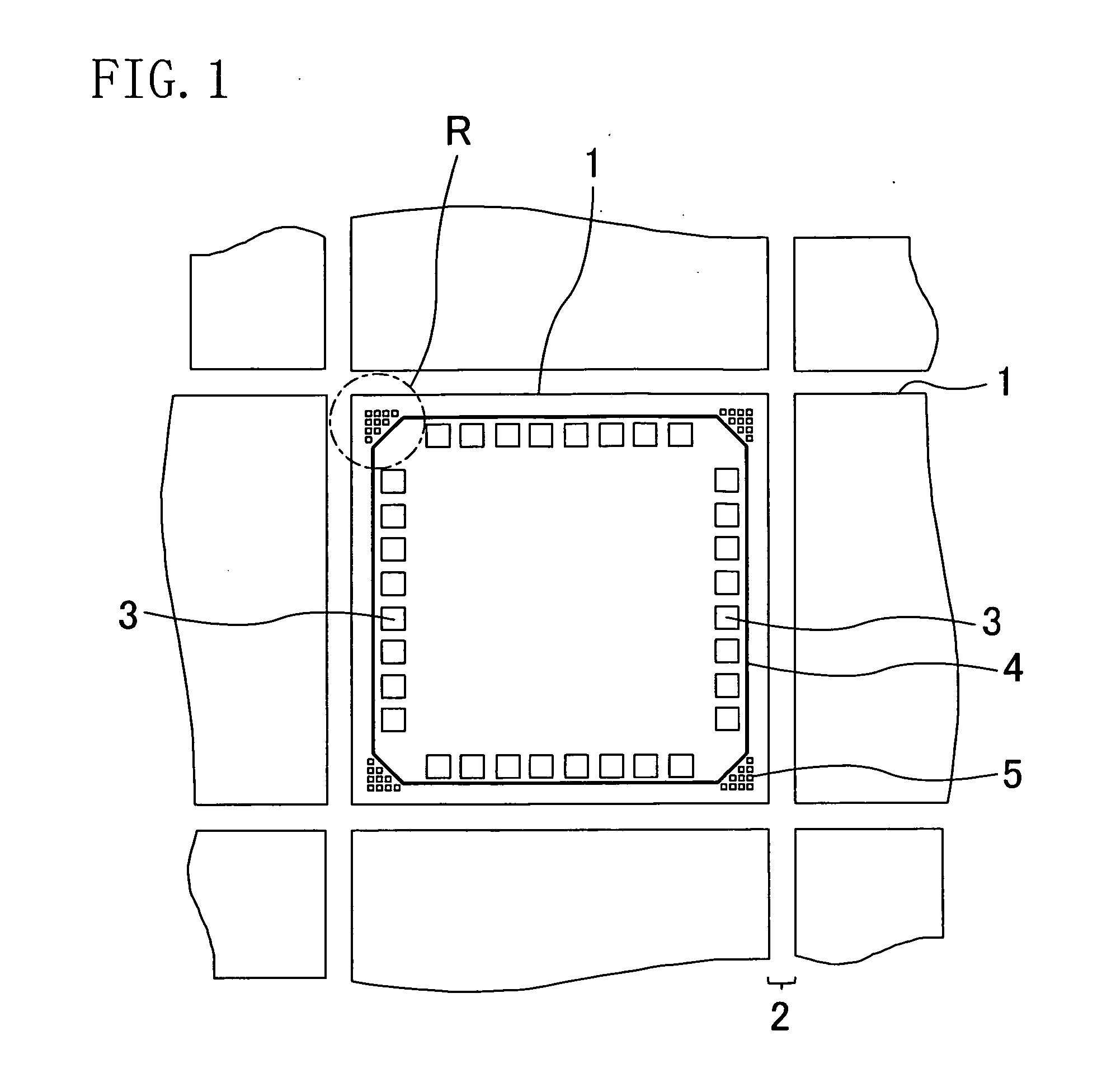

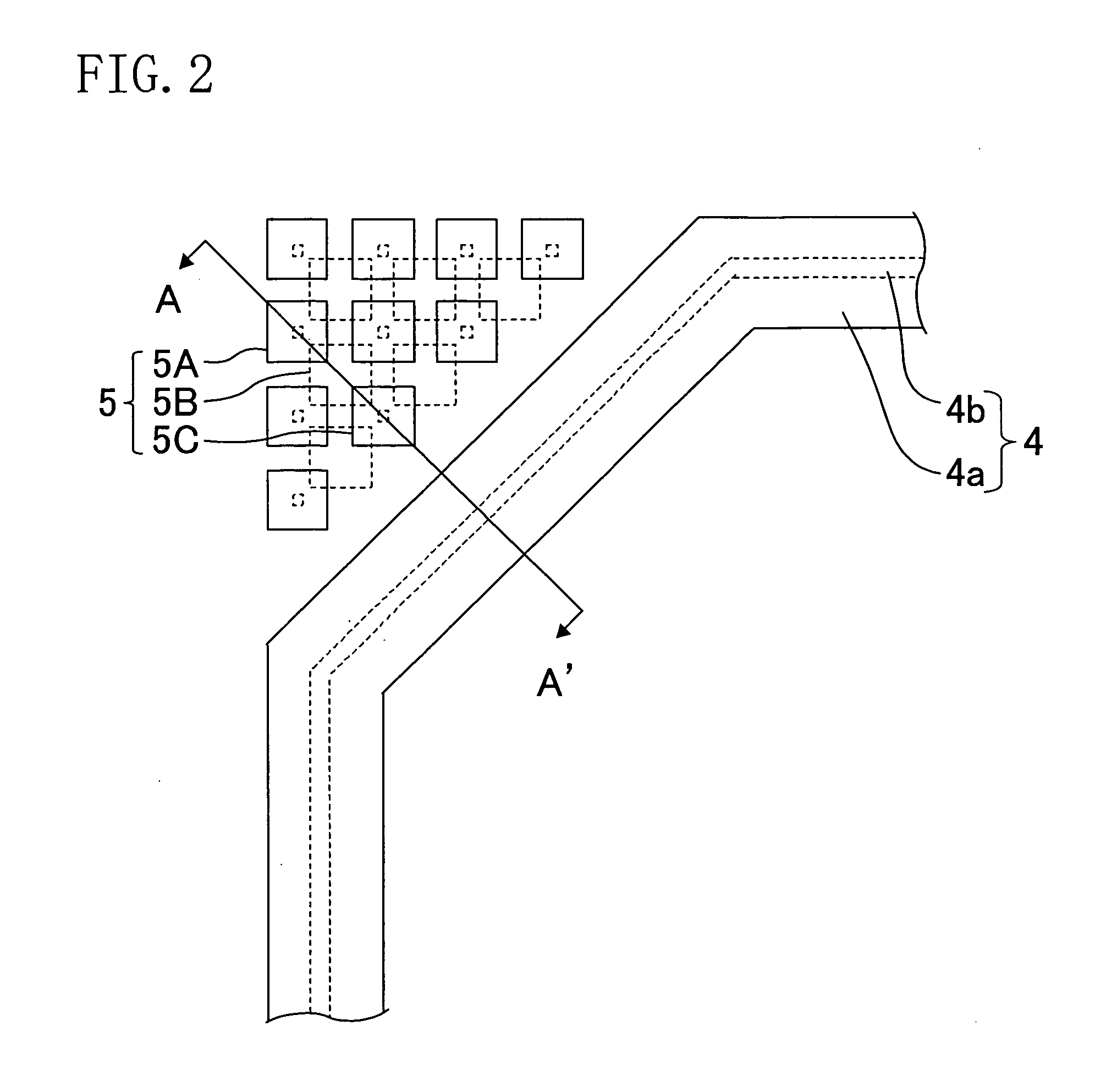

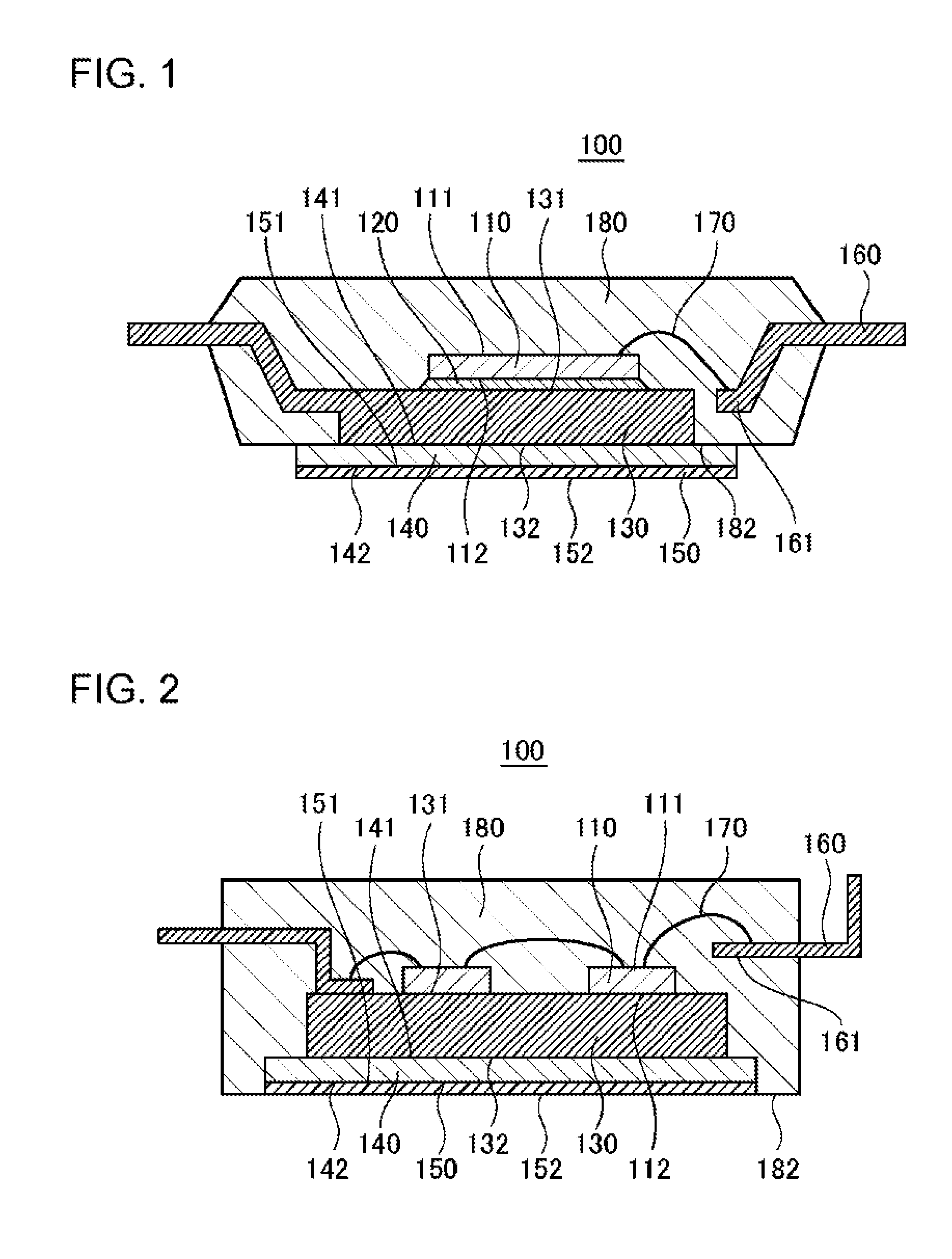

Semiconductor device manufacturing method, semiconductor device, and wiring board

InactiveUS20080174012A1Reduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A semiconductor device manufacturing method includes (a) bonding a first surface of a metal plate to a substrate, (b) forming a plurality of metal posts that are arranged in vertical and lateral directions in a plan view and include a first metal post and a second metal post, by partially etching the metal plate bonded to the substrate from a second surface of the metal plate, (c) fixing an integrated circuit (IC) element to the second surface of the first metal post, (d) coupling the second metal post and a pad terminal of the integrated circuit element via a conductive material, (e) resin-sealing the integrated circuit element, the metal posts, and the conductive material by providing a resin onto the substrate, and (f) removing the substrate from the resin and the first surfaces of the metal posts sealed using the resin.

Owner:SEIKO EPSON CORP

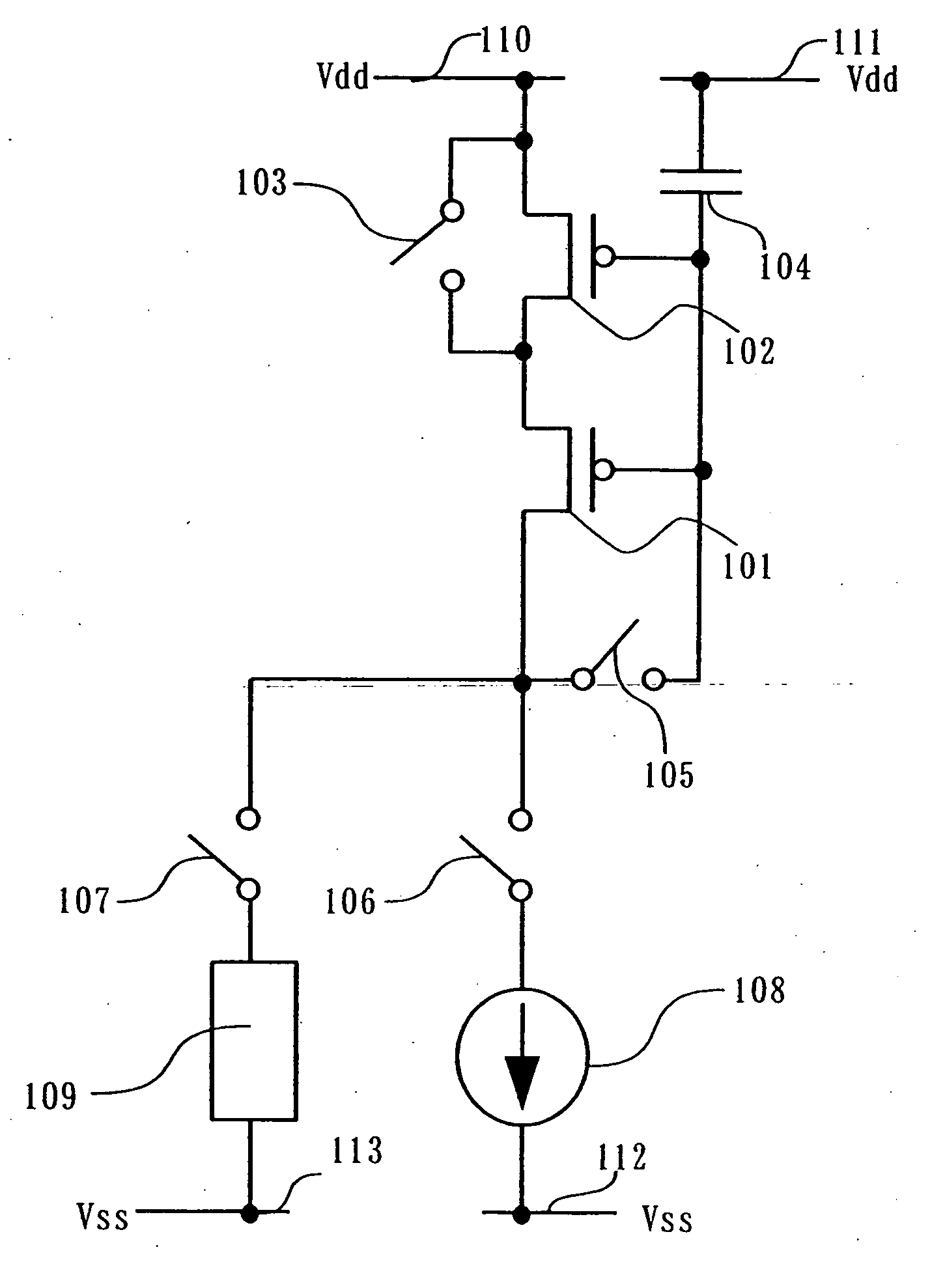

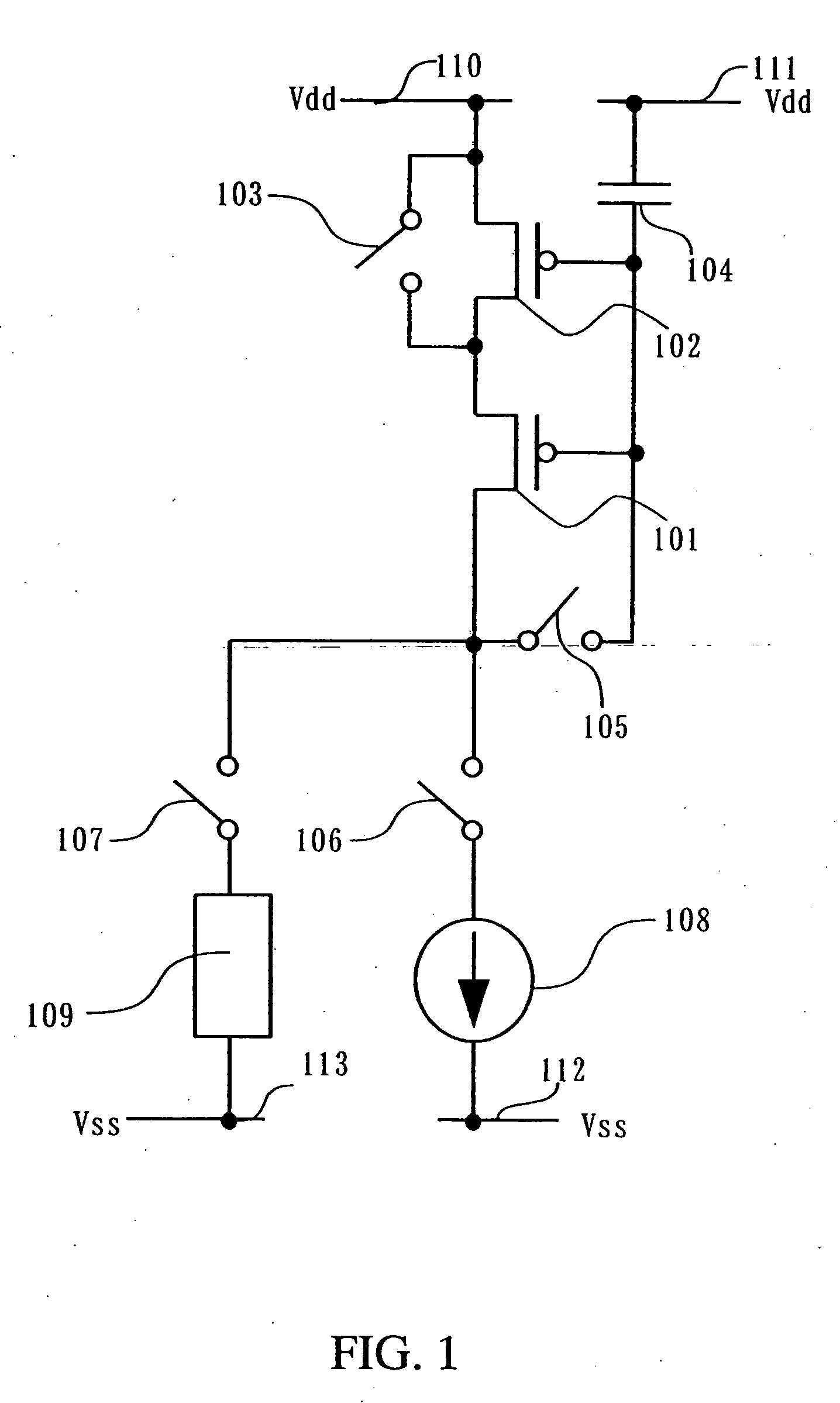

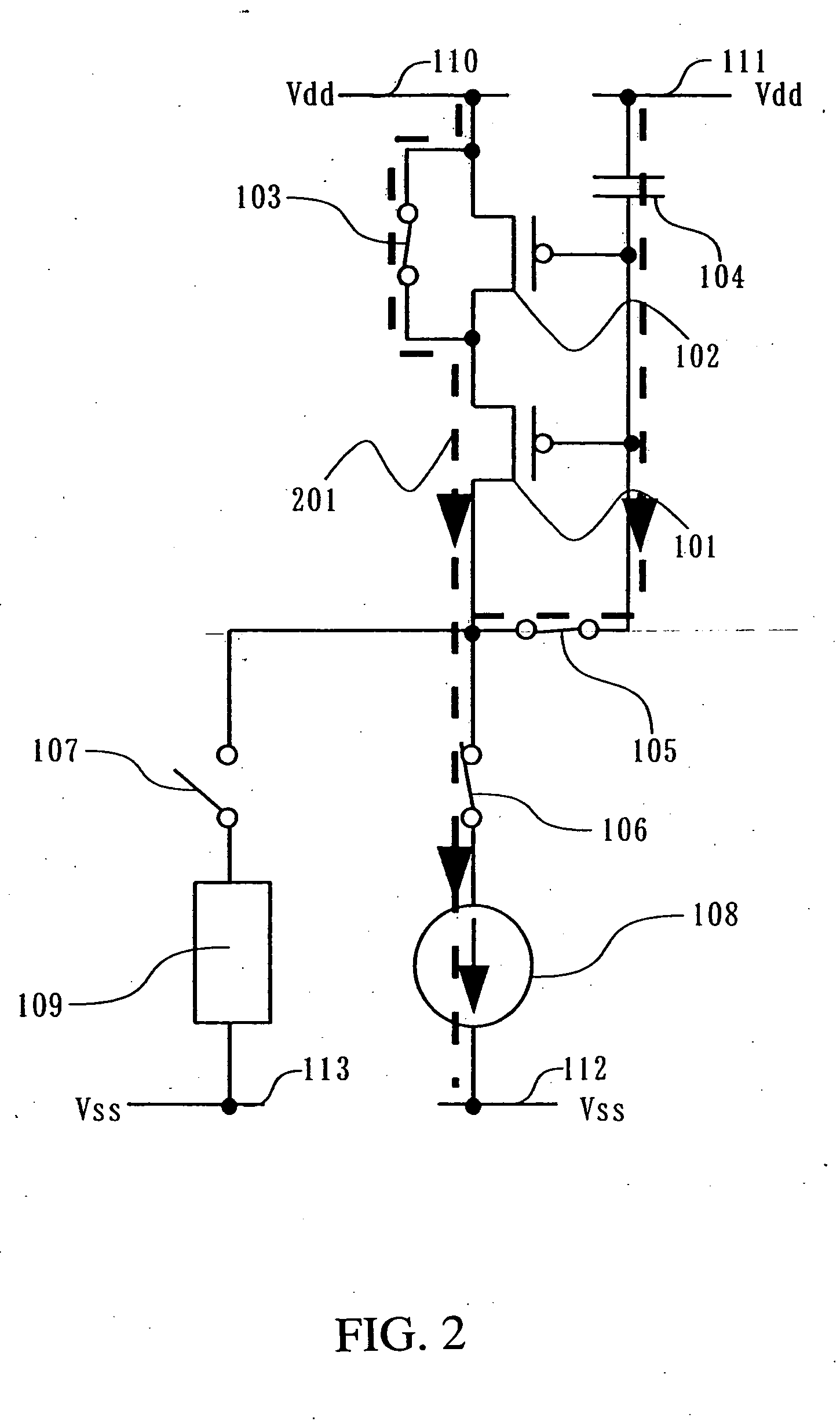

Semiconductor device and display device utilizing the same

InactiveUS20060187730A1High currentLess influenceStatic indicating devicesDigital storageCapacitanceElectrical resistance and conductance

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device having reset function

A semiconductor device comprises a memory cell array, a row control circuit for controlling an access to the memory cell array, and a refresh control circuit for instructing the row control circuit to refresh the memory cell array. After temporarily transiting to a reset state due to an activation of a reset signal, the refresh control circuit instructs to refresh the memory cell array in response to a transition to an initial state due to a de-activation of the reset signal.

Owner:LONGITUDE SEMICON S A R L

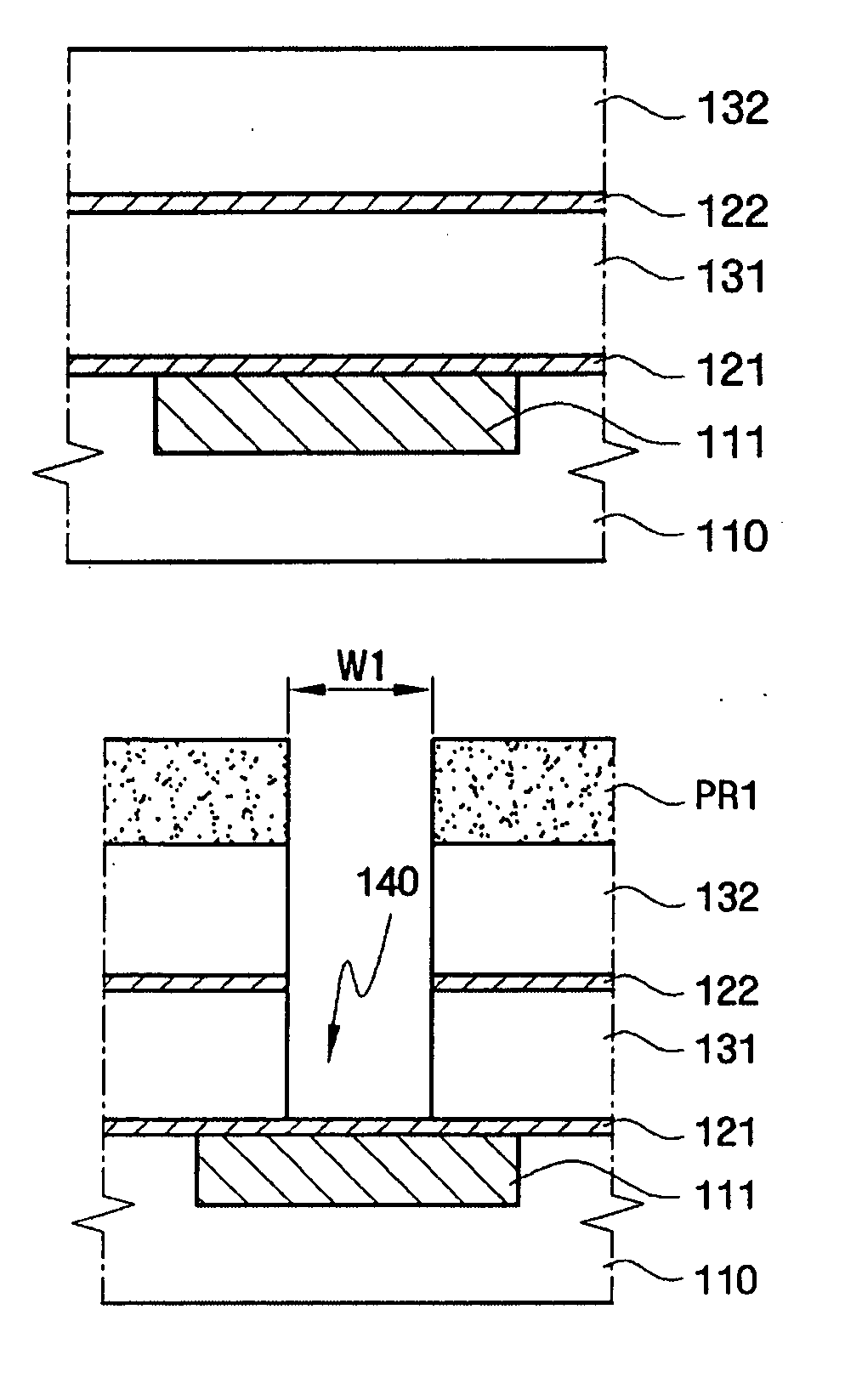

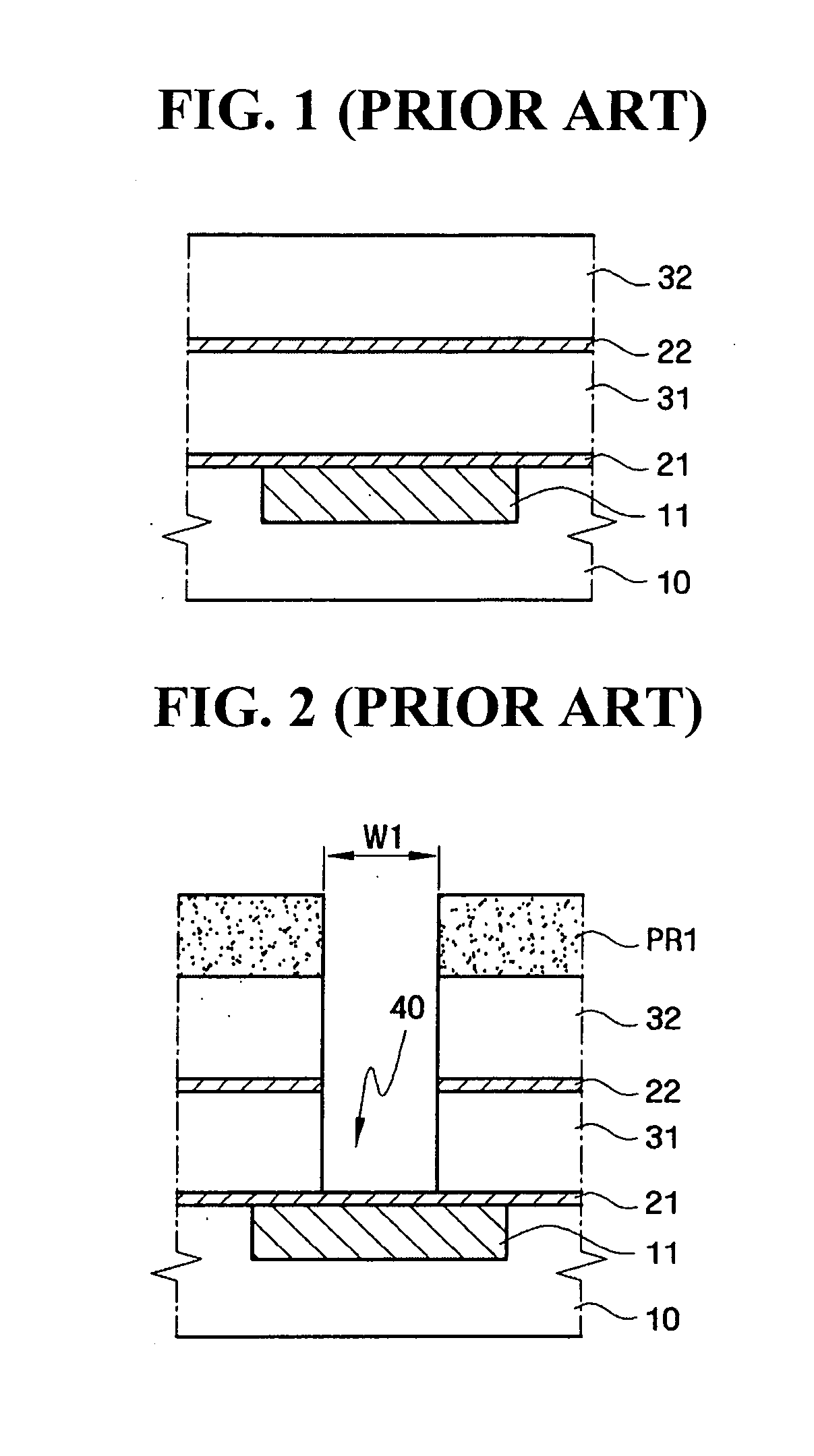

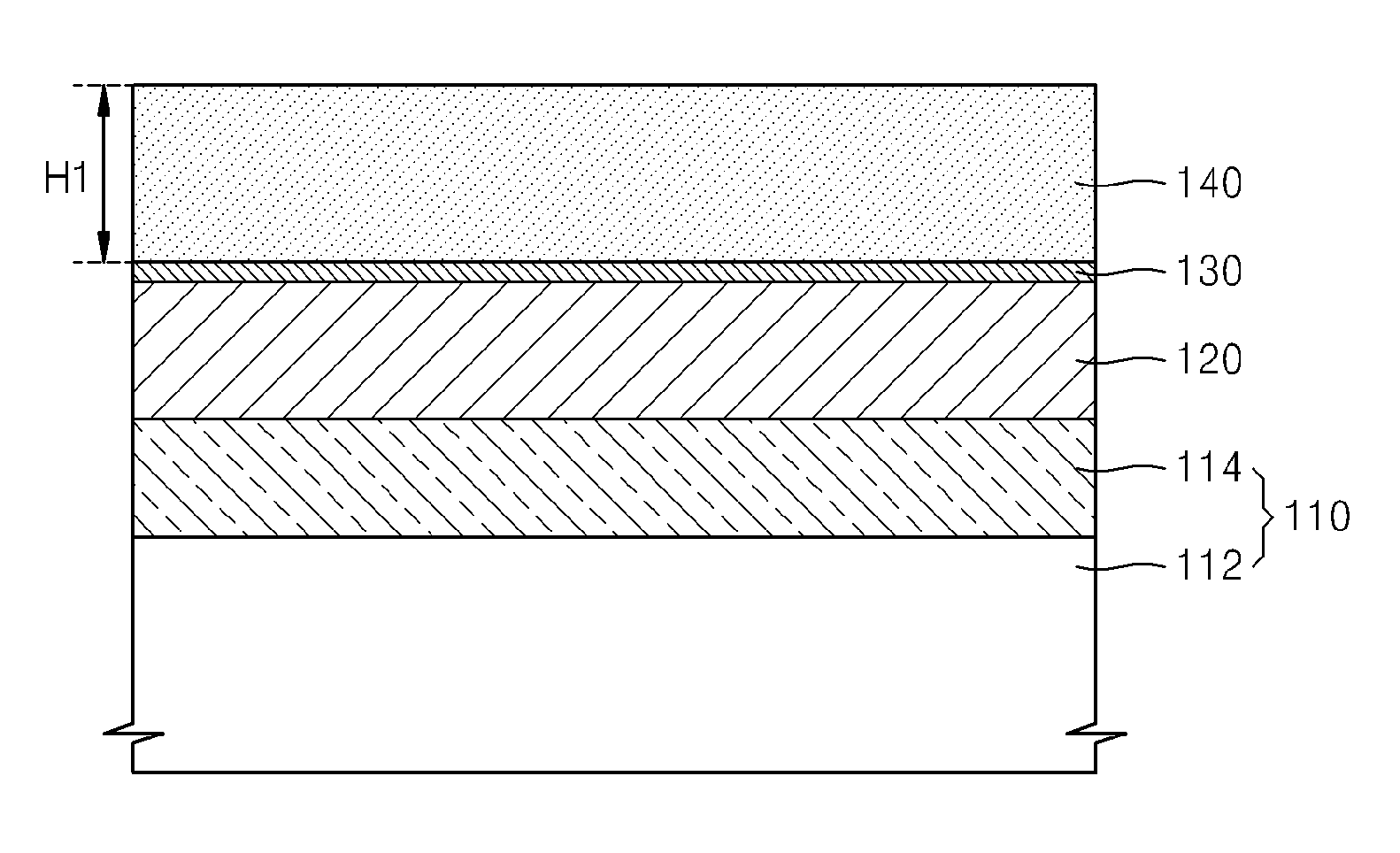

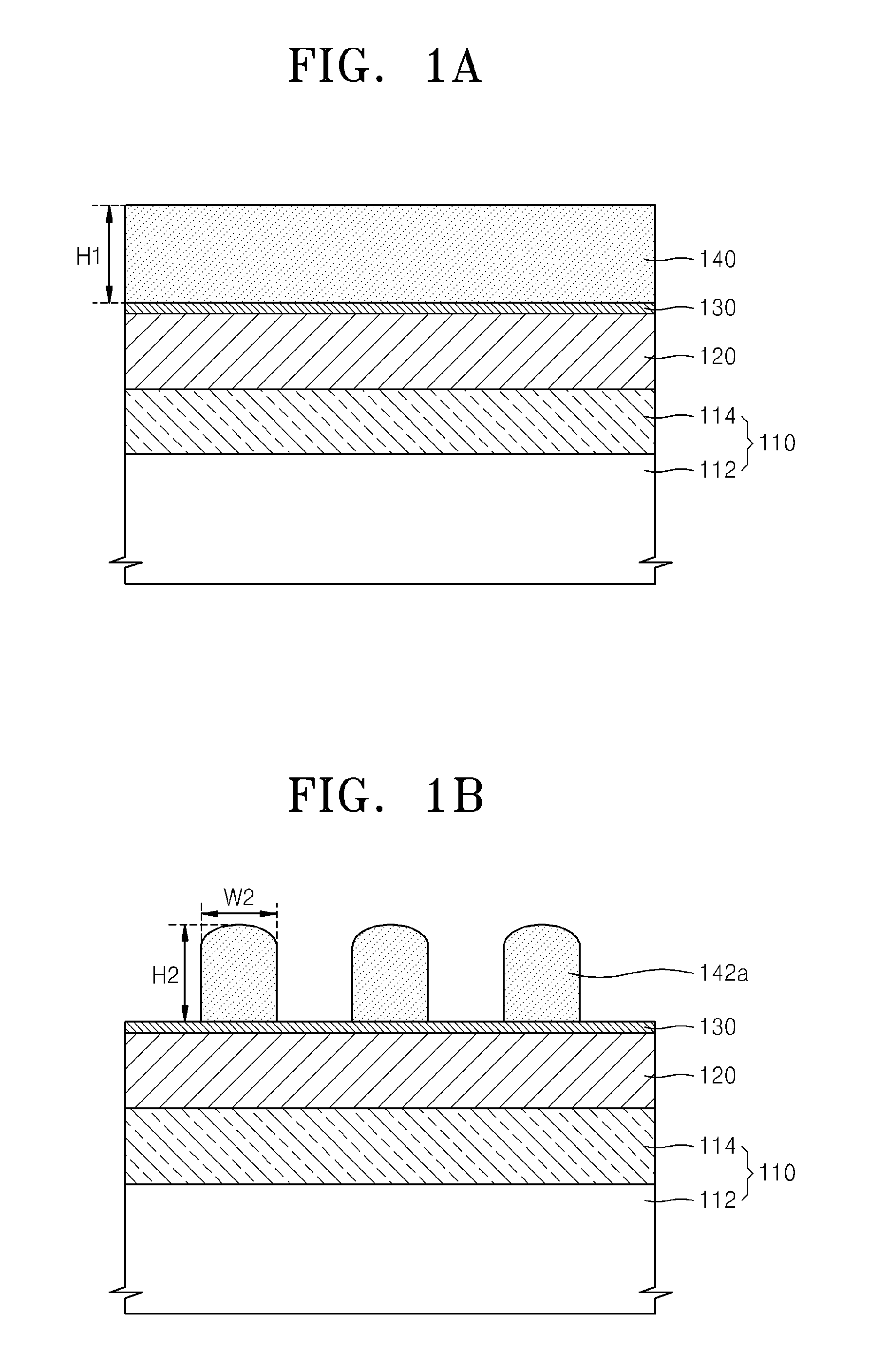

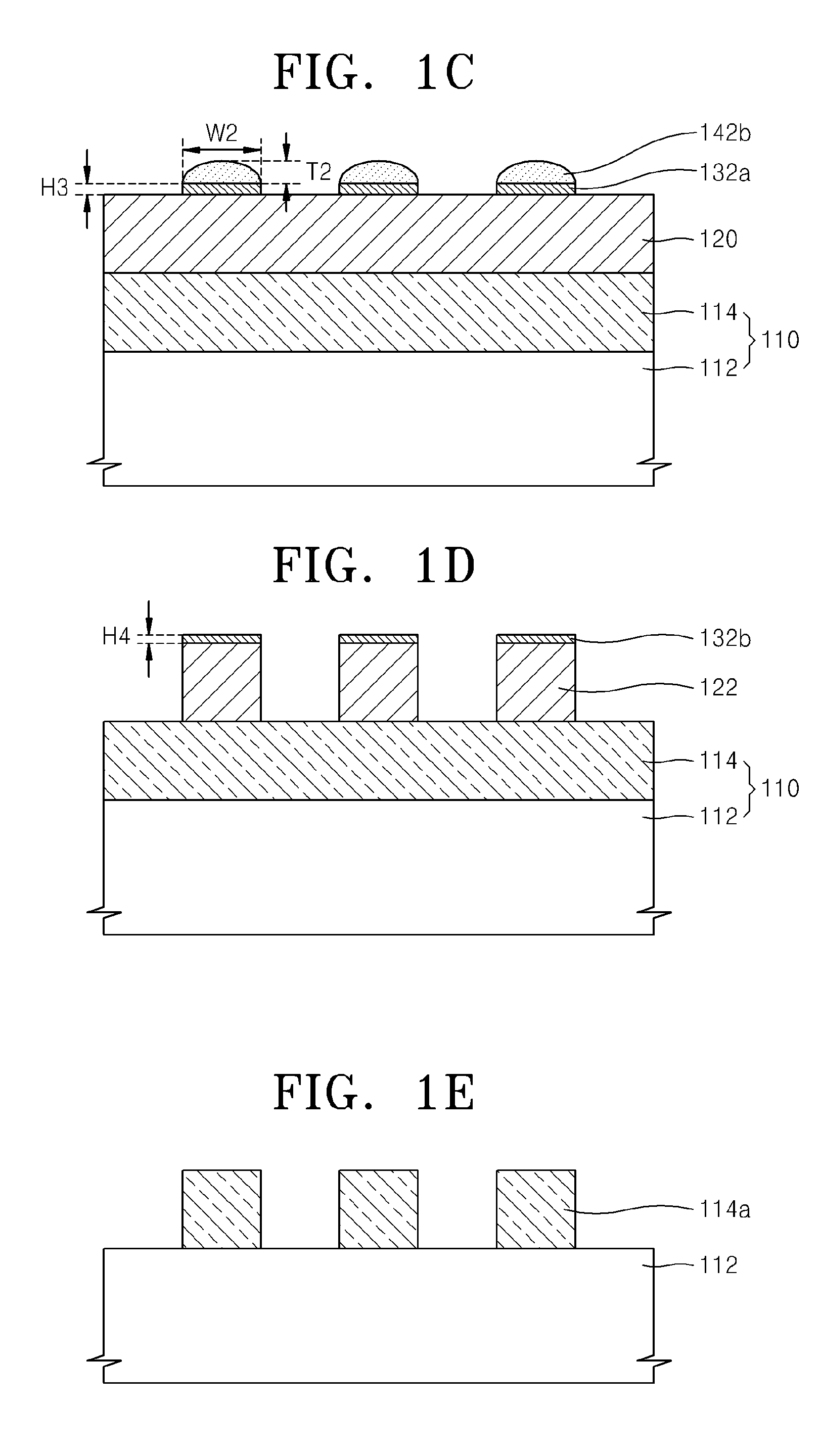

Methods of forming fine patterns and methods of fabricating semiconductor devices

Owner:SAMSUNG ELECTRONICS CO LTD

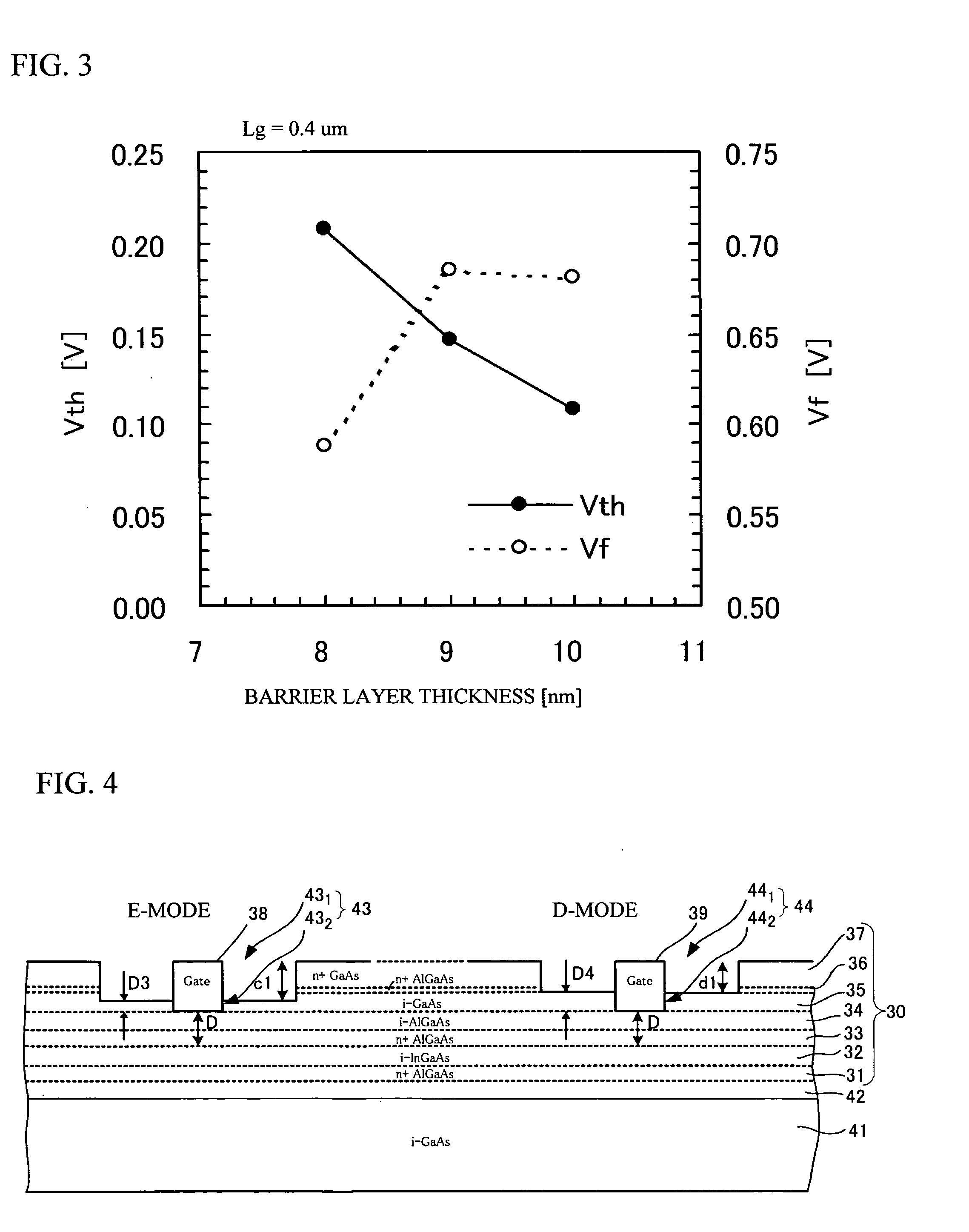

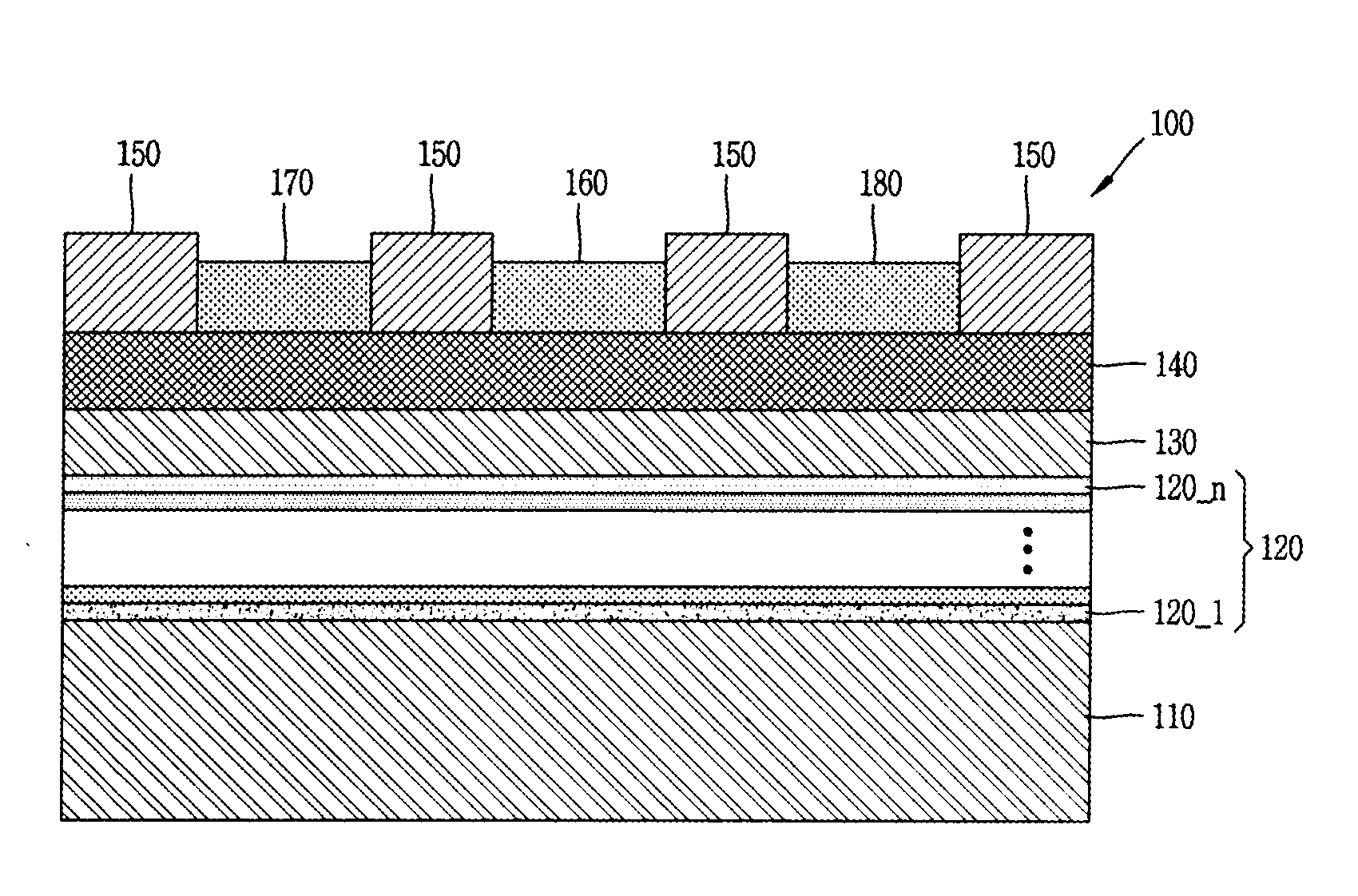

Semiconductor device and manufacturing method of the same

Owner:SUMITOMO ELECTRIC DEVICE INNOVATIONS

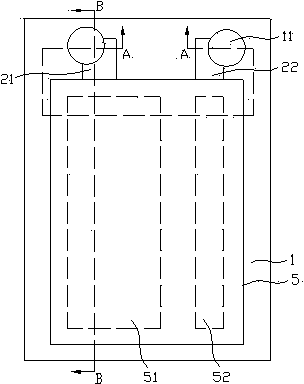

Power system, power module therein and method for fabricating power module

ActiveUS20130214842A1Reduce voltage spikesPulse automatic controlConversion constructional detailsElectrical conductorDevice material

A power system, a power module therein and a method for fabricating power module are disclosed herein. The power module includes a first and a second common pins, and a first and a second bridge arms. The first and the second common pins are symmetrically disposed at one side of a substrate. The first bridge arm includes a first and a second semiconductor devices, and the first and the second semiconductor devices are connected to each other through the first common pin and disposed adjacently. The second bridge arm includes a third and a fourth semiconductor devices, and the third and the fourth semiconductor devices are connected to each other through the second common pin and disposed adjacently. The first and the third semiconductor devices are disposed symmetrically, and the second and the fourth semiconductor devices are disposed symmetrically.

Owner:DELTA ELECTRONICS INC

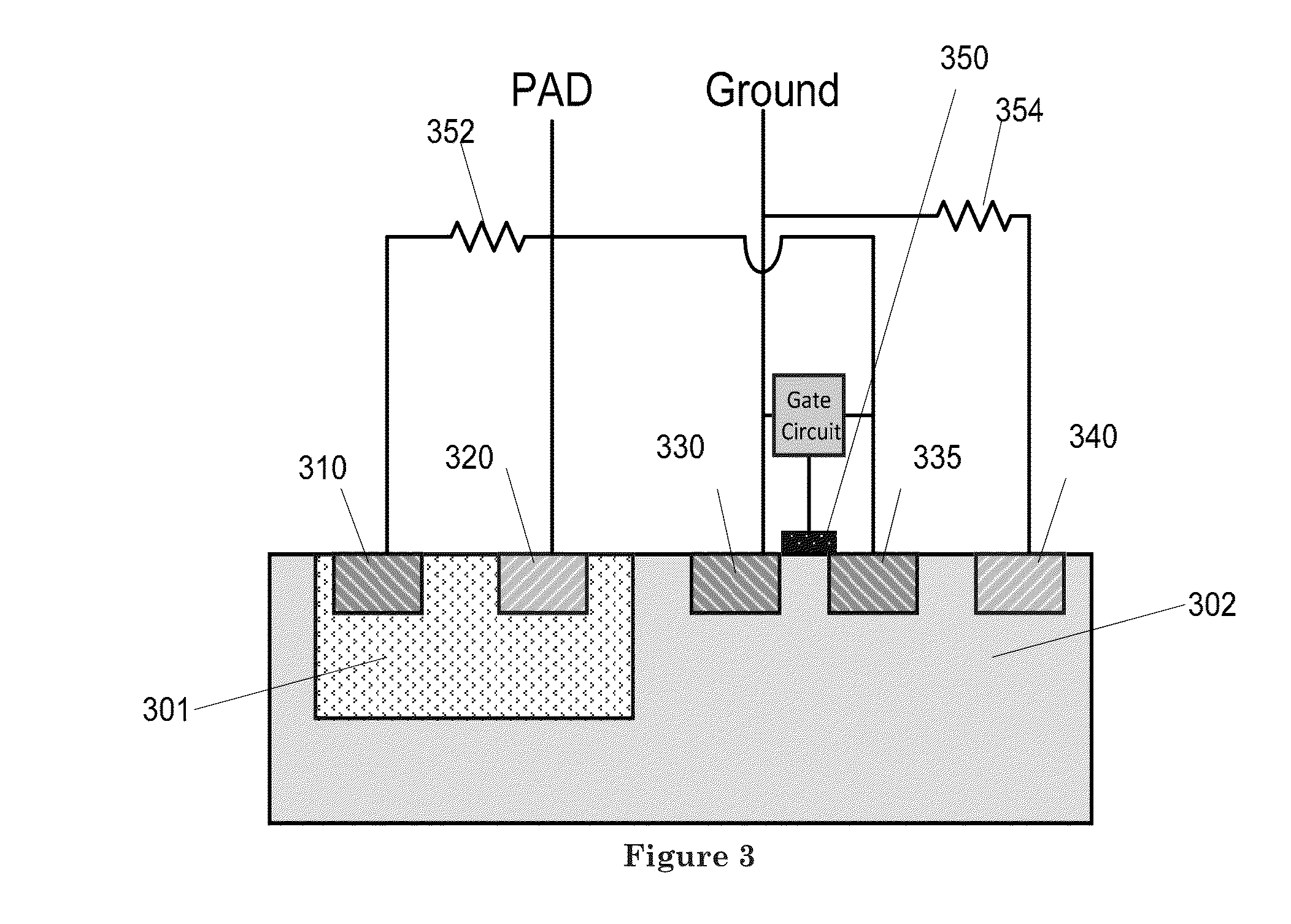

Semiconductor device for electrostatic discharge protection

ActiveUS20150091056A1Speed up triggeringSpeedTransistorSolid-state devicesPower semiconductor deviceDevice material

Owner:SOFICS BVBA

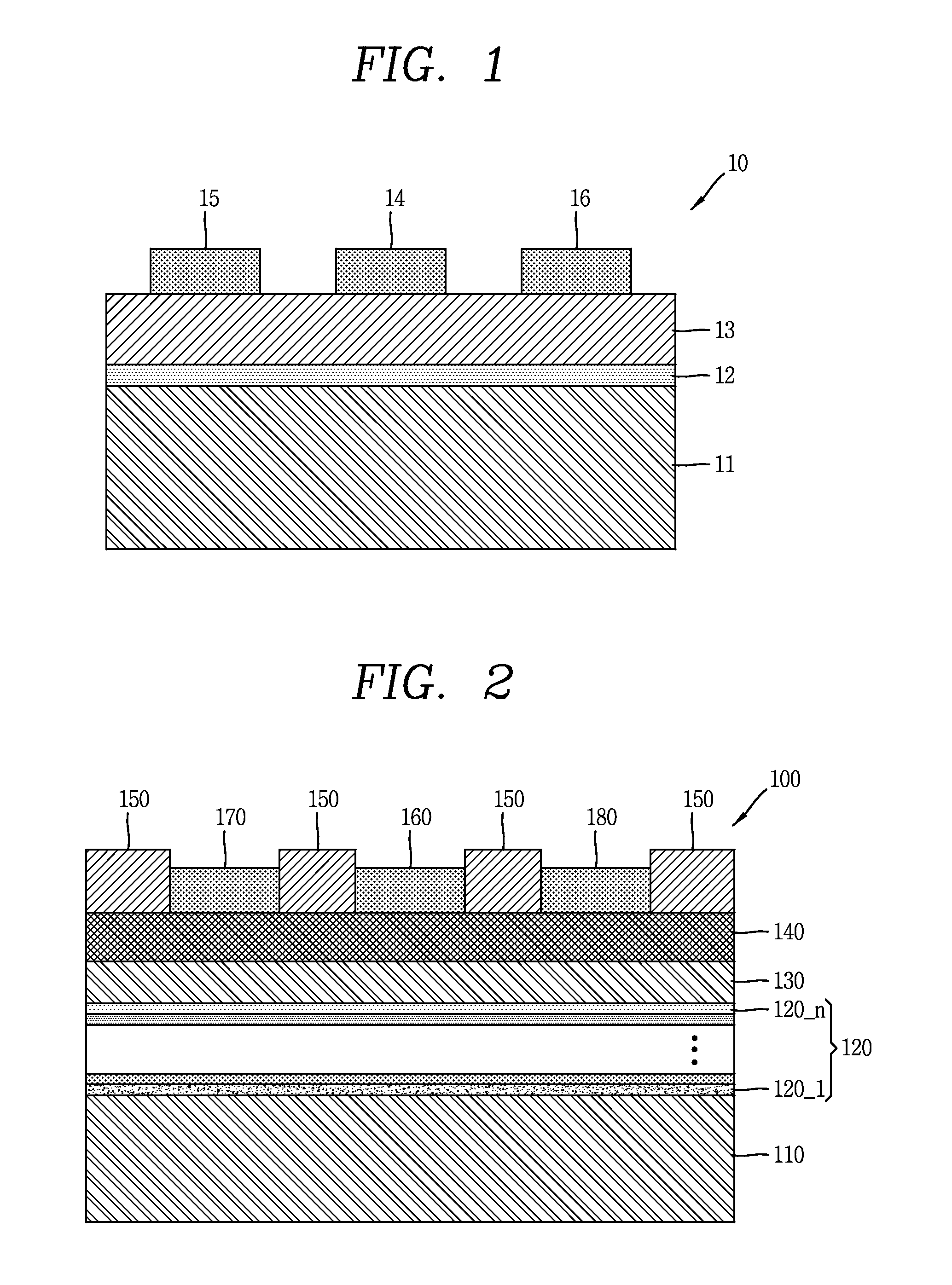

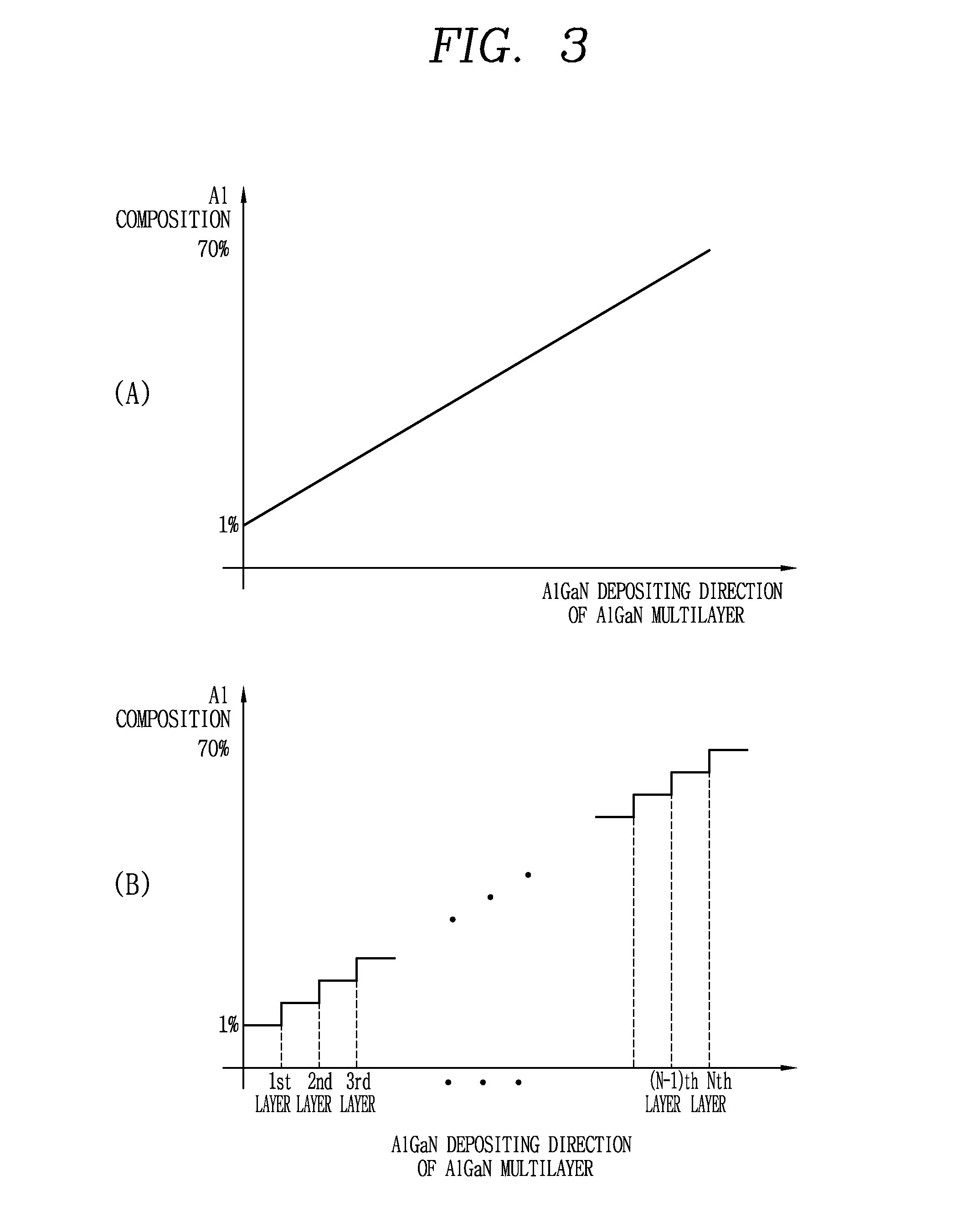

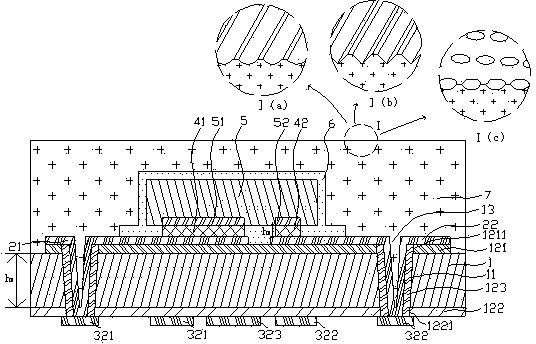

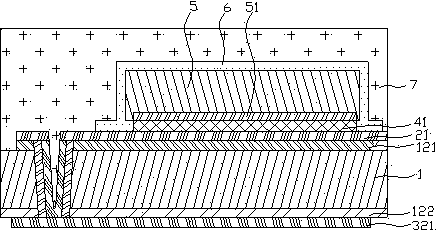

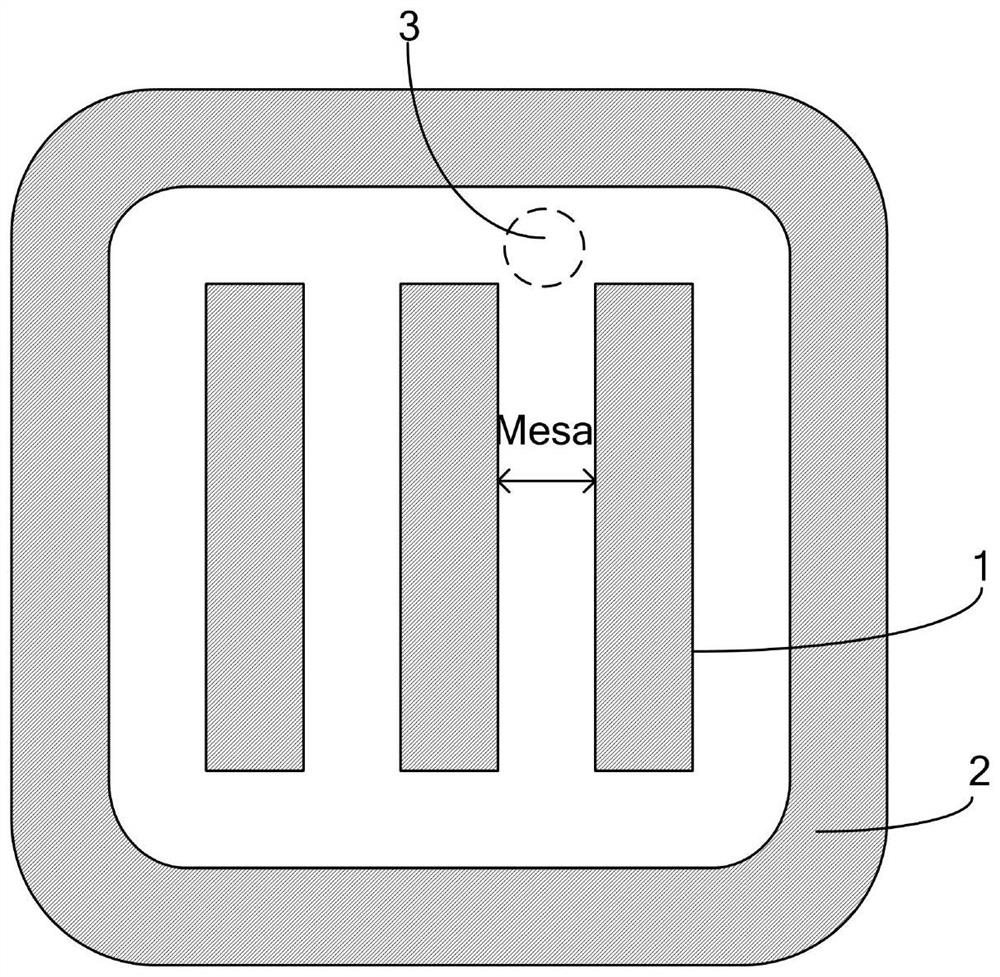

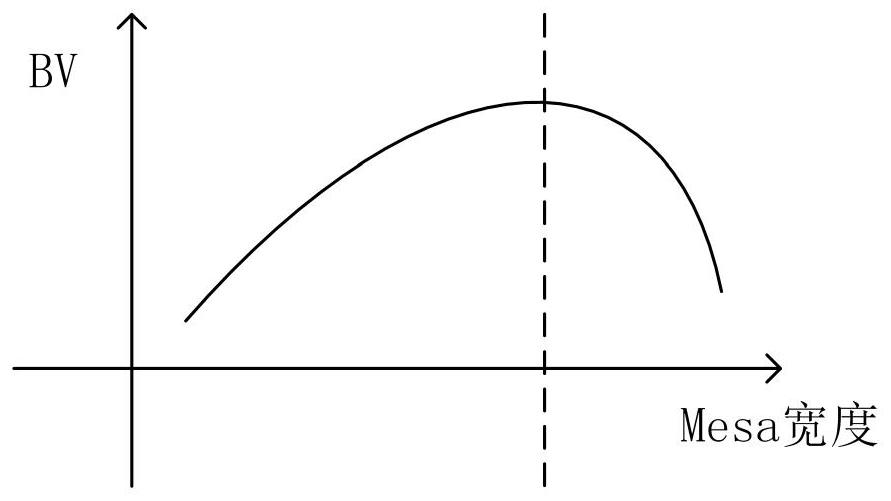

Nitride semiconductor device and fabricating method thereof

ActiveUS20150200257A1Minimized increaseLower breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionDevice material

Owner:LG ELECTRONICS INC

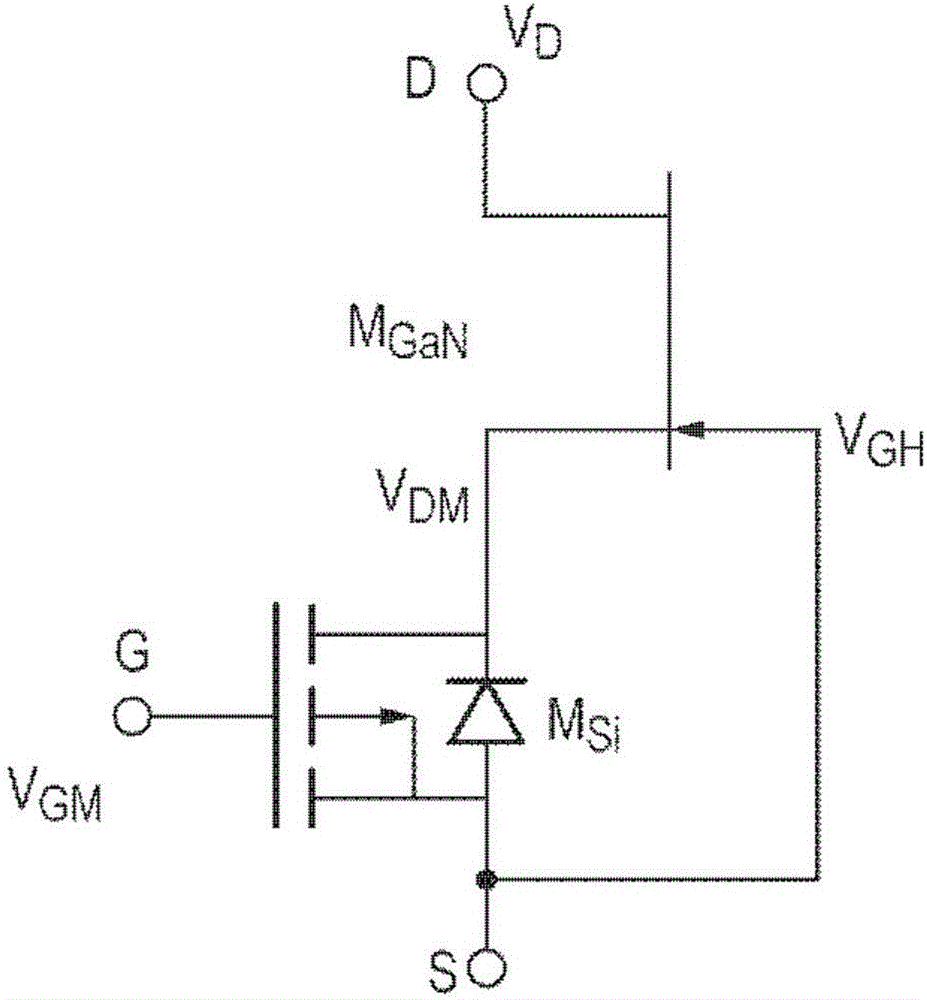

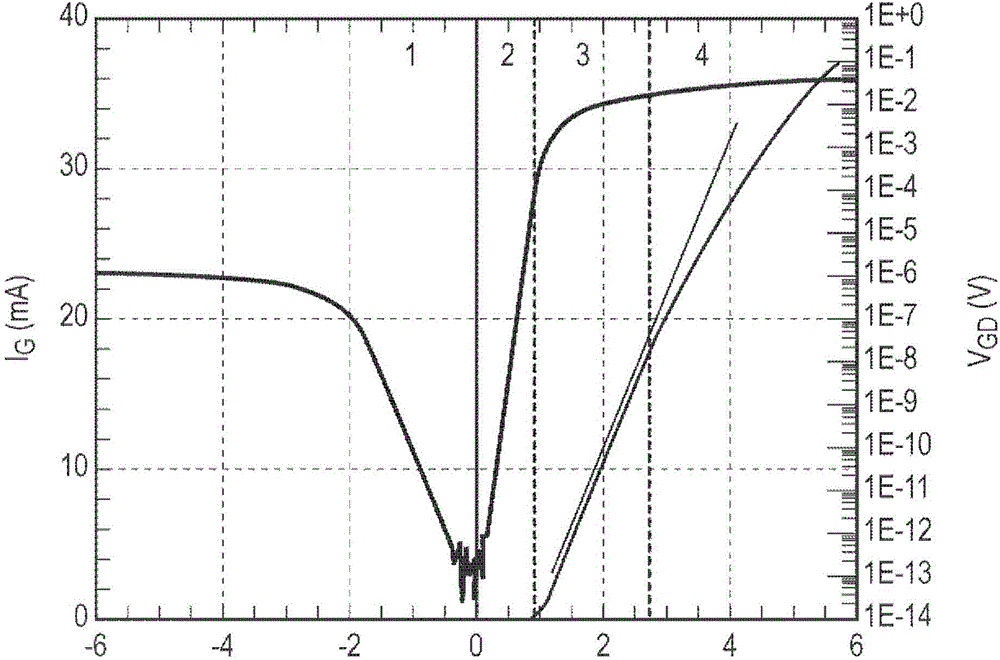

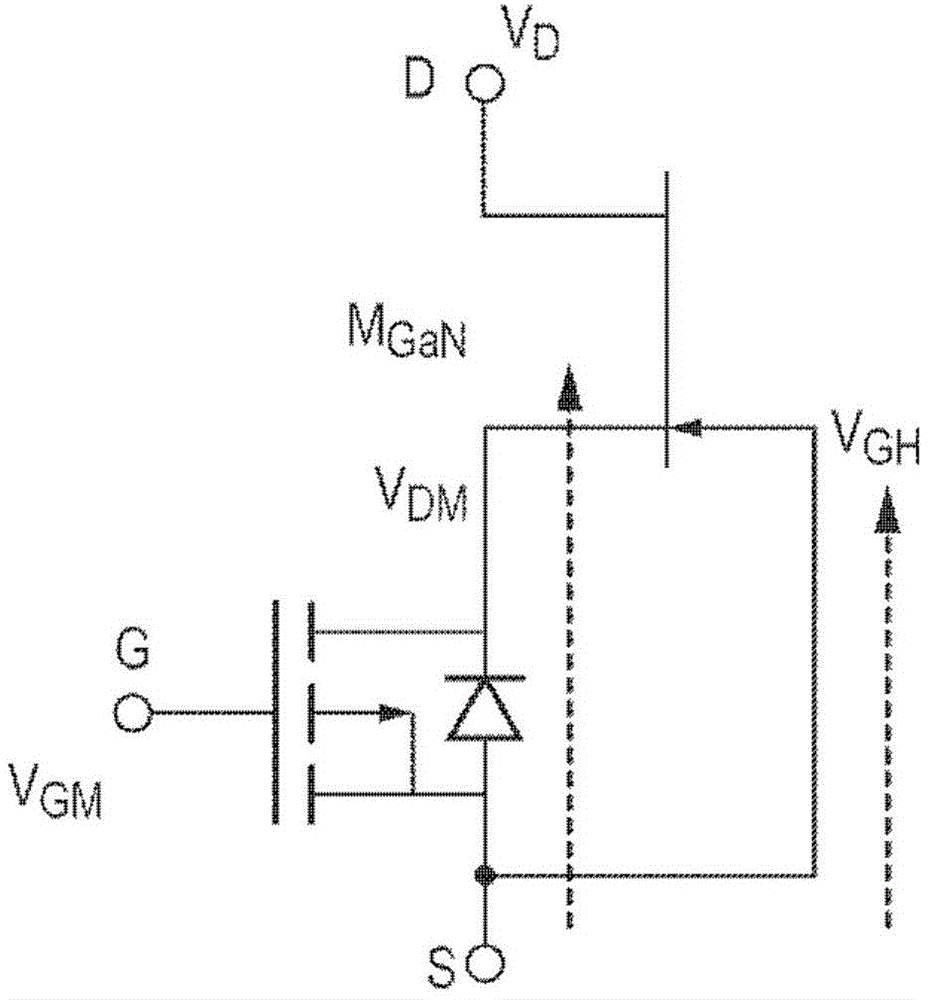

Cascoded semiconductor devices

ActiveCN104104384AReliable reverse operationReduce lossSemiconductor/solid-state device detailsSolid-state devicesDevice materialTransistor circuits

Owner:NEXPERIA BV

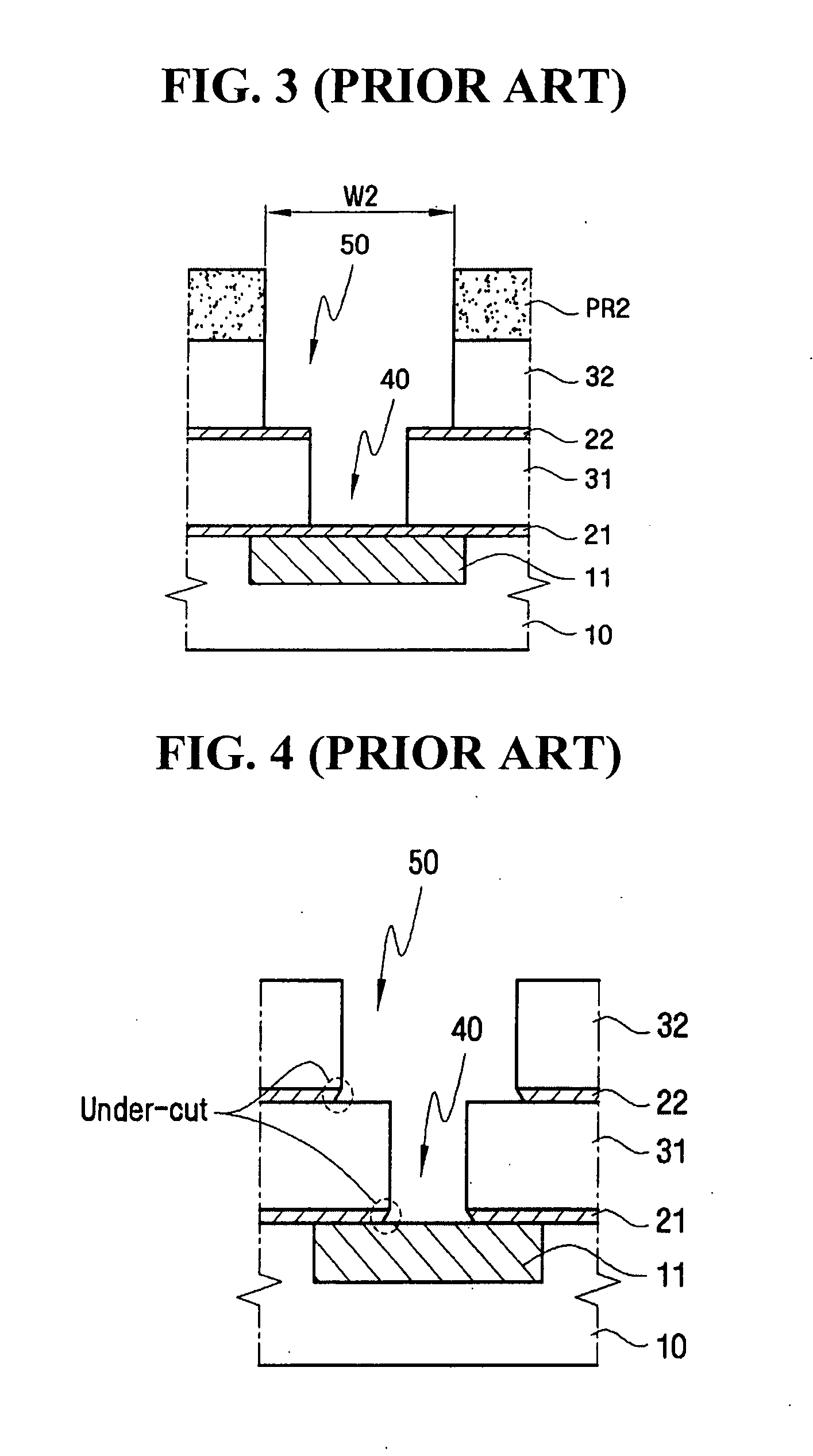

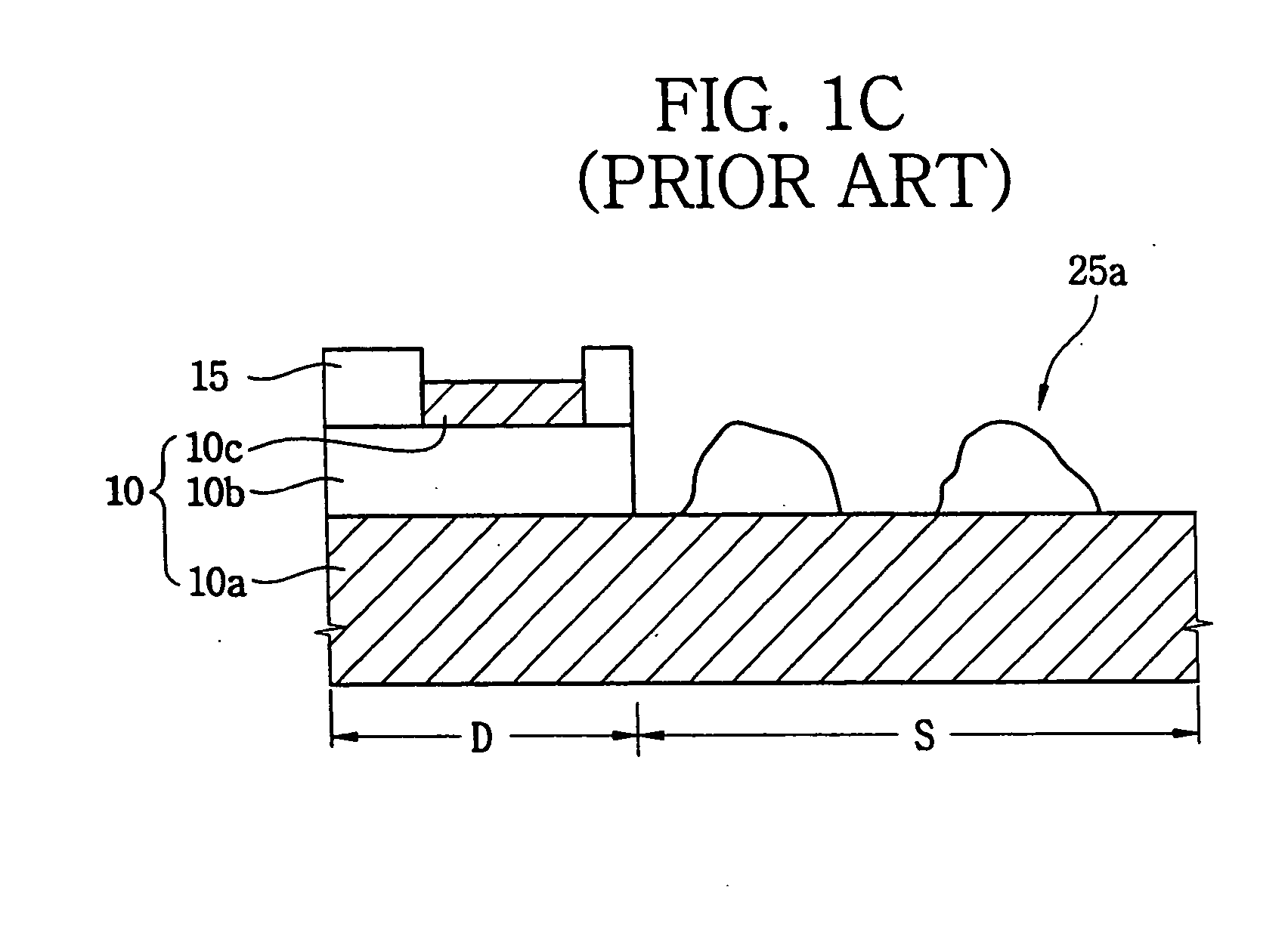

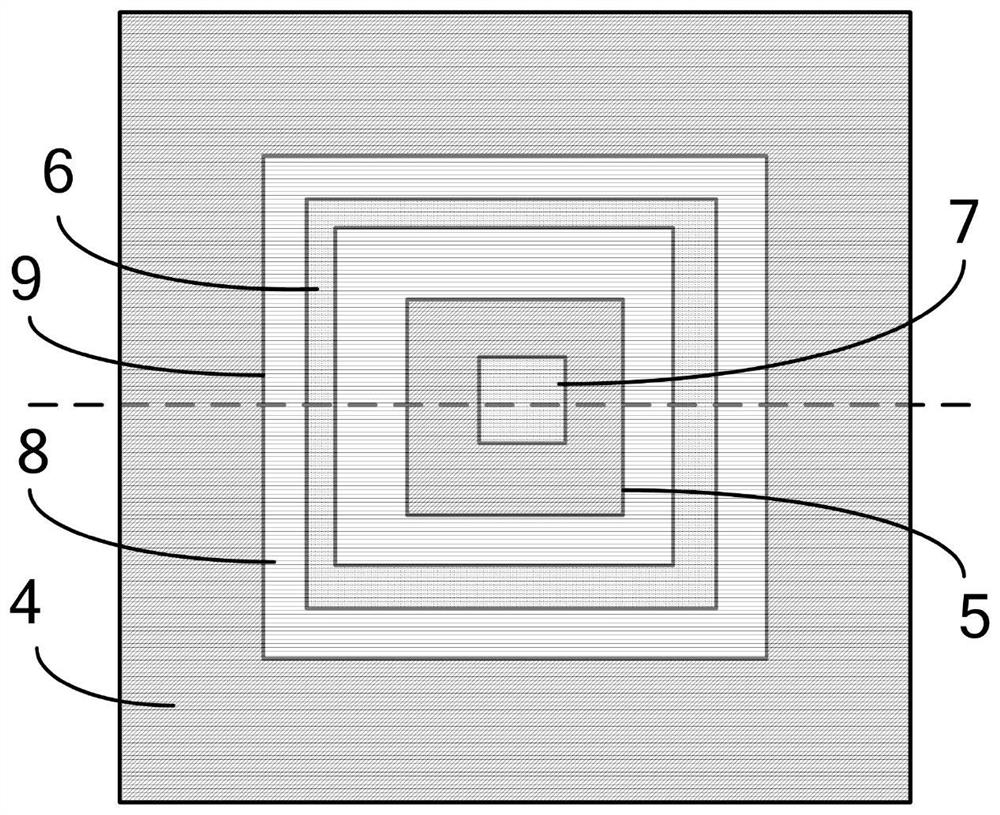

Alignment mark and method for manufacturing a semiconductor device having the same

ActiveUS20050009287A1No damageSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

Owner:SAMSUNG ELECTRONICS CO LTD

Preparation method of Cu2CdSnS4 nanometer crystal

The invention discloses a preparation method of Cu2CdSnS4 nanometer crystal with low cost and high quality. In the method, the high-quality Cu2CdSnS4 nanometer crystal is finally obtained by adding reactant presoma oleamide, copper acetylacetonate, cadmium acetate, tin acetate and sulphur in a reaction flask and then rising the temperature for reaction. The invention has the advantages of simple nanometer crystal preparation method, low-cost used presoma material; and the prepared nanometer crystal particles have good dispersity and favorable crystallinity. The prepared nanometer crystal can be used as thermo-electric device materials.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

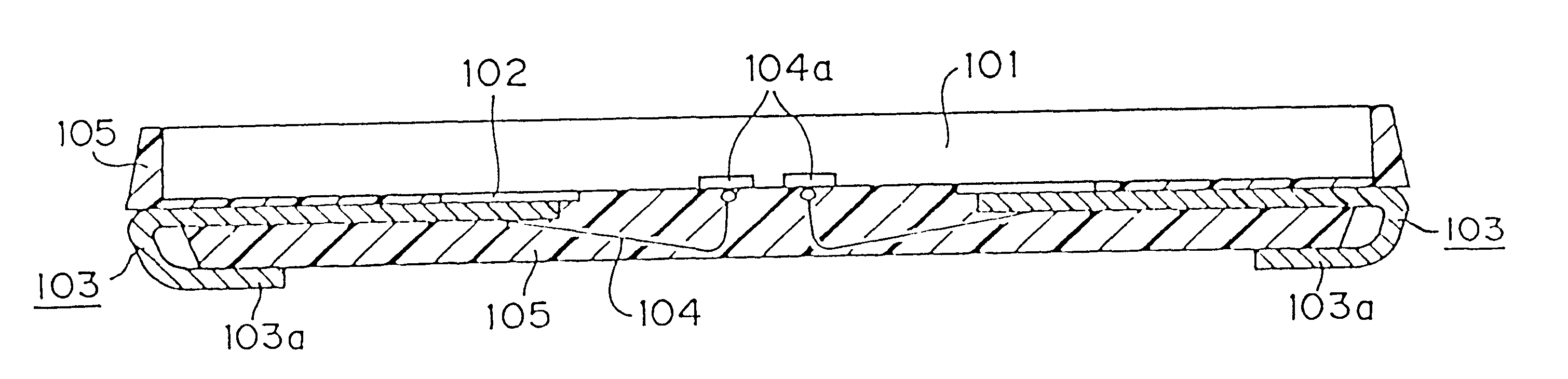

Semiconductor device packaged in plastic package

InactiveUS6181003B1Strong connectionSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor

Owner:OKI ELECTRIC IND CO LTD

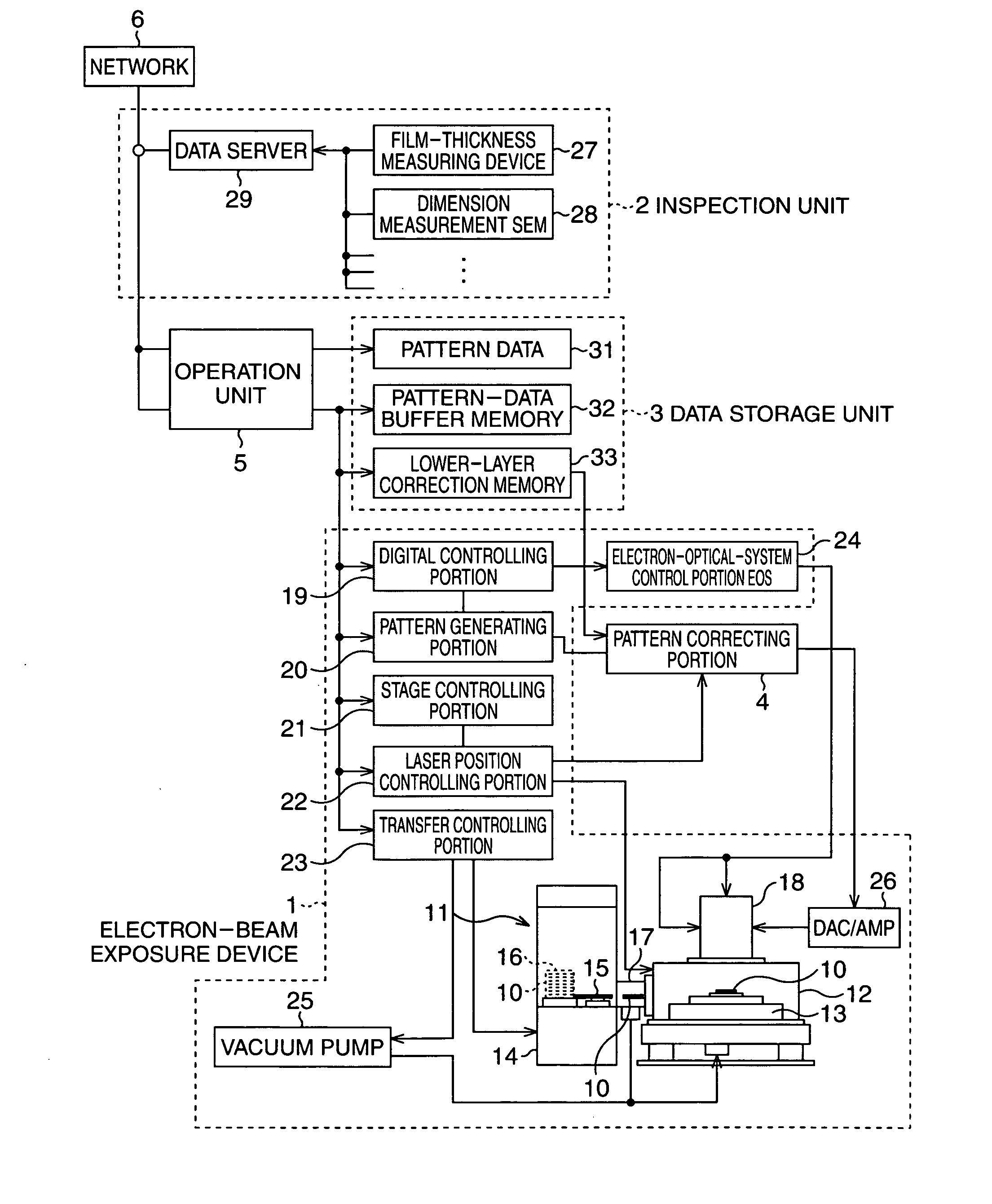

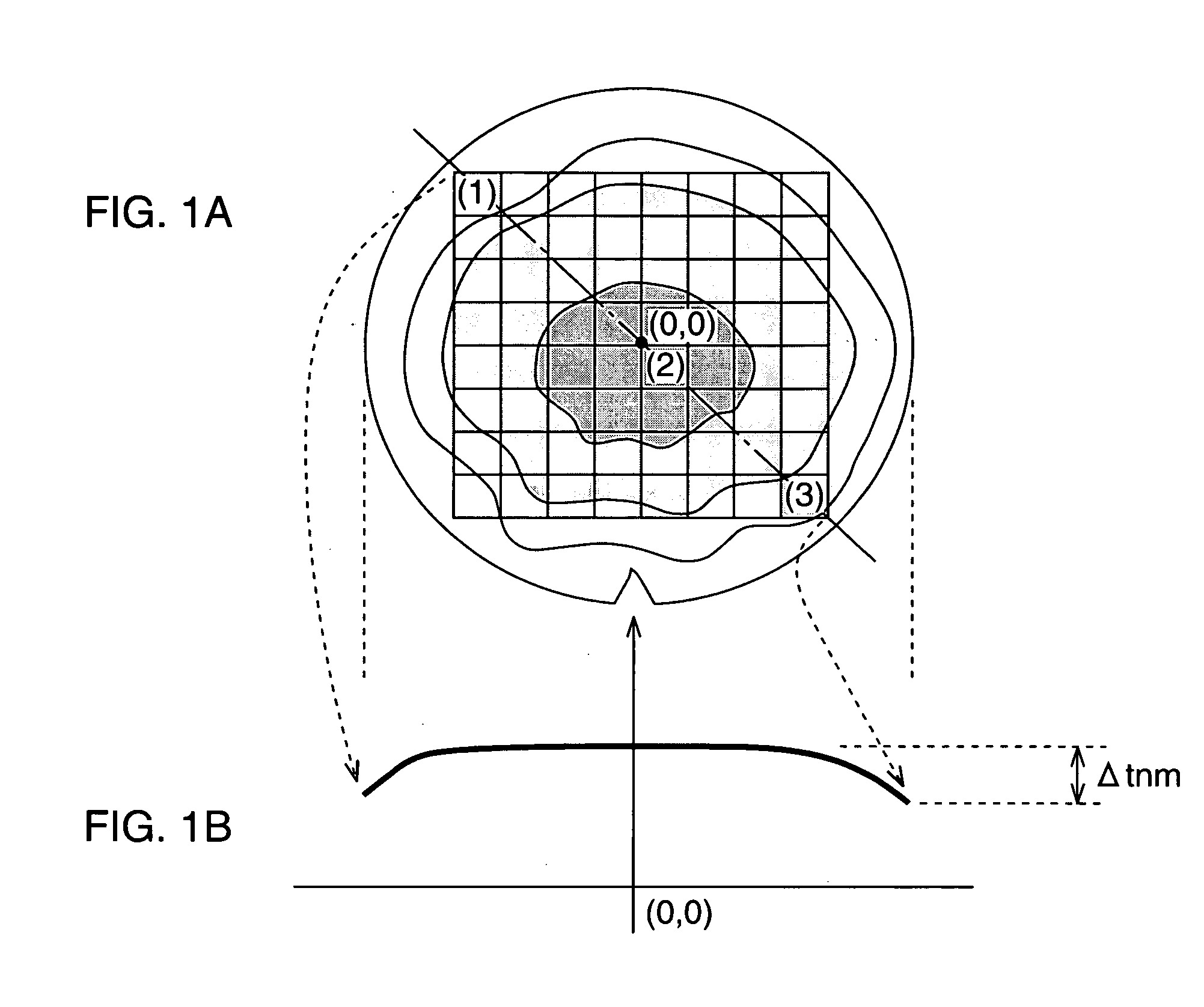

Exposure system, exposure method and semiconductor device manufacturing method

InactiveUS20070070314A1Easy to integrateMinimal restrictionElectric discharge tubesRadiation applicationsResistIn plane

Owner:FUJITSU SEMICON LTD

Thermally conductive sheet and semiconductor device

ActiveUS20170011986A1Improve insulation reliabilitySemiconductor/solid-state device detailsSolid-state devicesDielectric loss factorDevice material

Owner:SUMITOMO BAKELITE CO LTD

Wafer-level packaging method of semiconductor device

ActiveCN104465973ASmall sizeIn line with the trend of miniaturizationSolid-state devicesSemiconductor devicesInsulation layerDevice material

Owner:JIANGYIN CHANGDIAN ADVANCED PACKAGING CO LTD

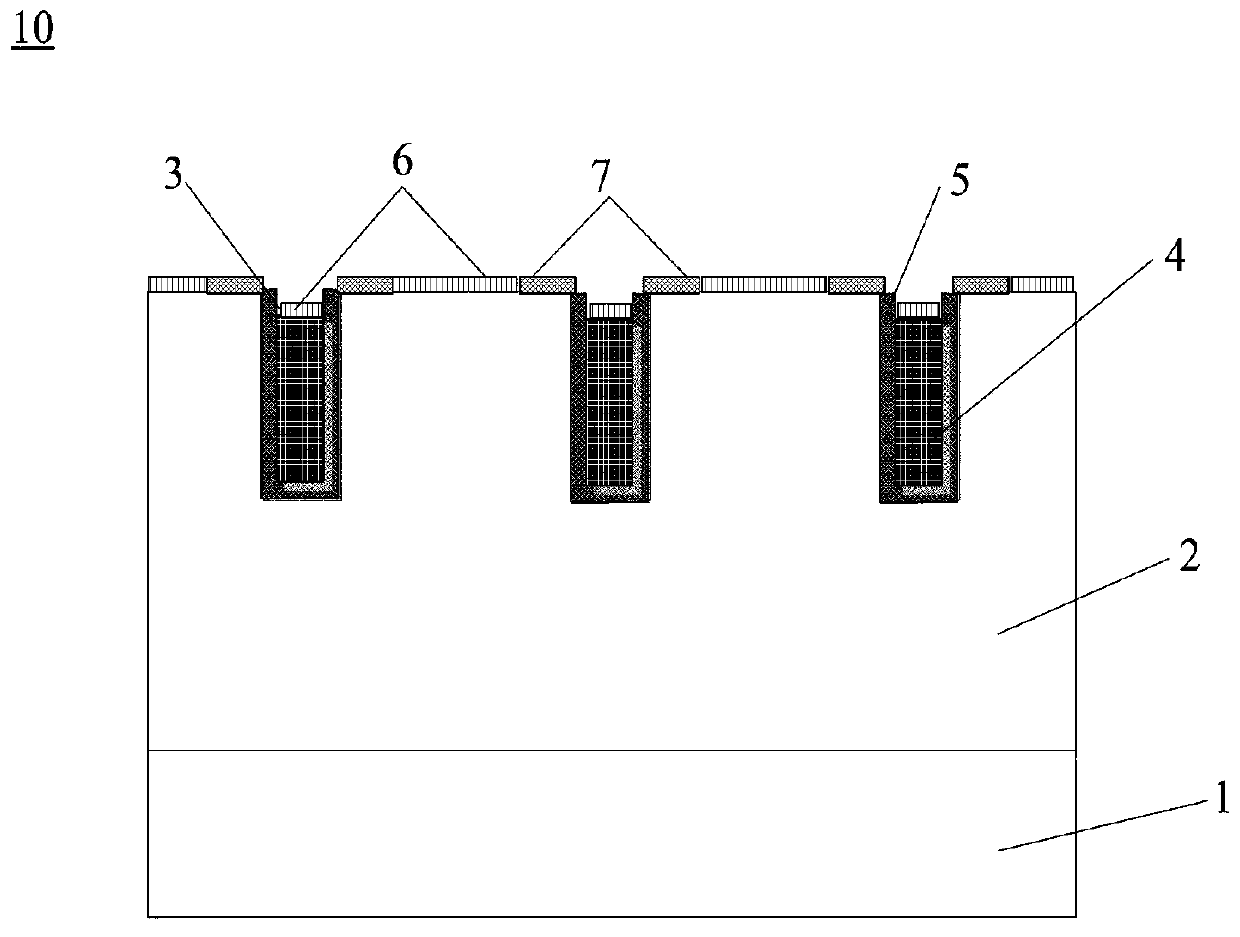

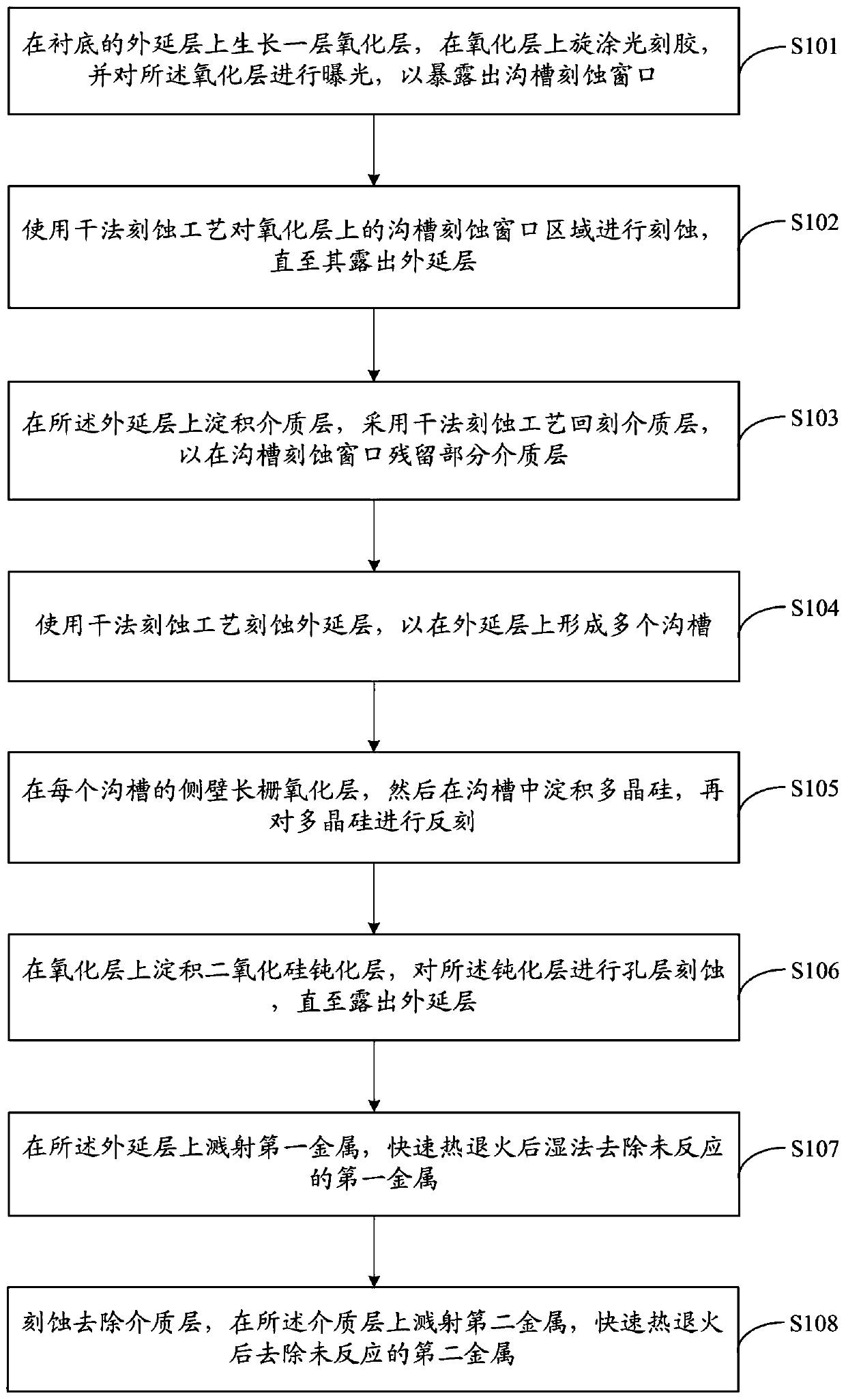

High-reliability SGT device with upper and lower structures

Owner:江苏芯长征微电子集团股份有限公司 +1

Semiconductor device with Schottky metal junction and manufacturing method thereof

PendingCN110931569AReduce leakage currentReduce conduction voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierDevice material

Owner:广微集成技术(深圳)有限公司

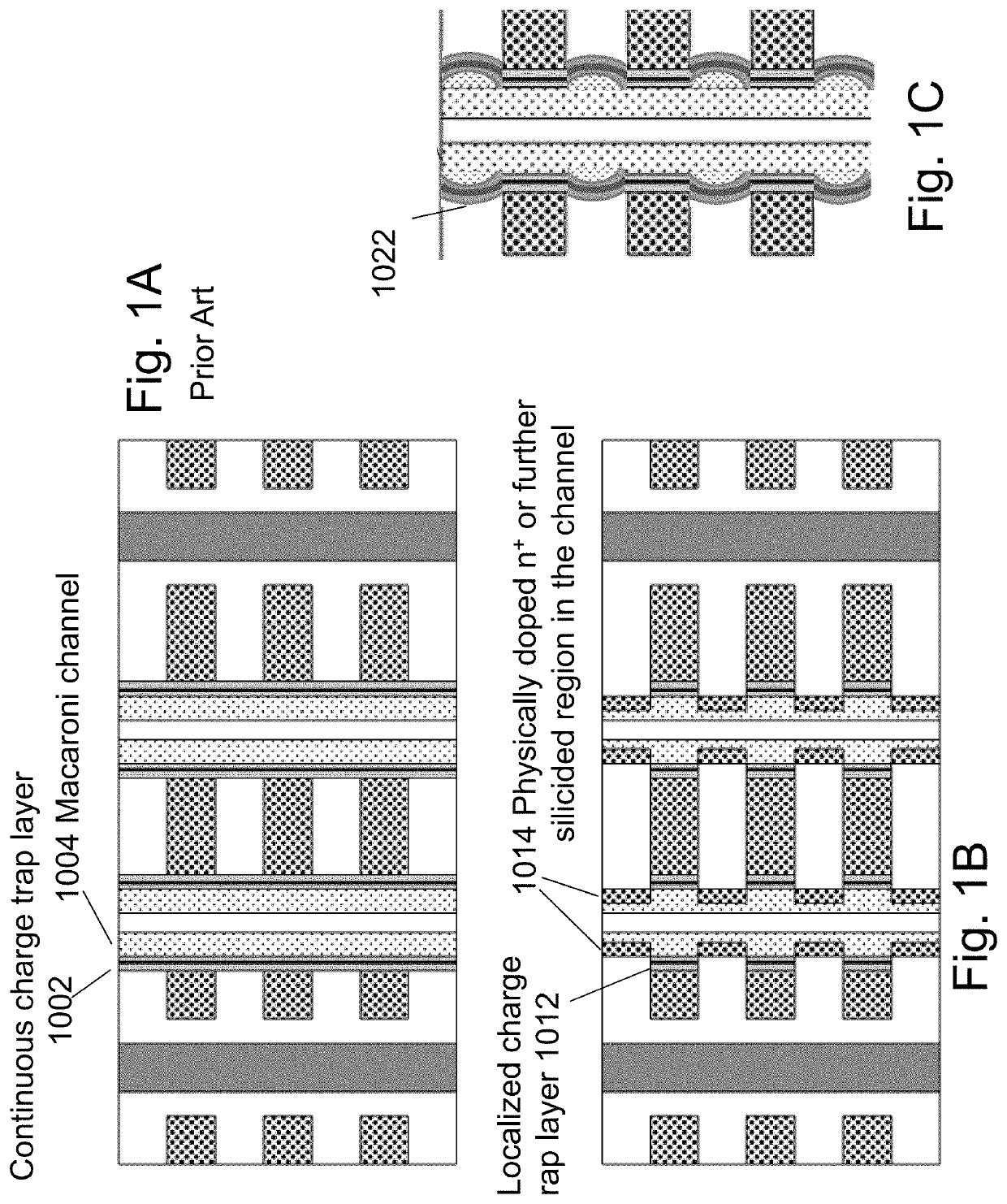

3D memory semiconductor device and structure

Owner:MONOLITHIC 3D

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap