Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

135 results about "Hemt circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Systems and methods for interconnection of multiple FPGA devices

InactiveUS20050256969A1Simple designEnhance intercommunicationDigital computer detailsLogic circuits using elementary logic circuit componentsComputer architectureTransceiver

Application Specific Integrated Circuit (“ASIC”) devices, such as Field Programmable Gate Arrays (“FPGAs”), may be interconnected using serial I / O connections, such as high speed multi-gigabit serial transceiver (“MGT”) connections. For example, serial I / O connections may be employed to interconnect a pair of ASICs to create a high bandwidth, low signal count connection, and in a manner so that any given pair of multiple ASIC devices on a single circuit card may communicate with each other through no more than one serial data communication link connection step. A reconfigurable hardware architecture (“RHA”) may be configured to include a communications infrastructure that uses a high-bandwidth packet router to establish standard communications protocols between multiple interfaces and / or multiple devices that may be present on a single circuit card. Additionally, a communications infrastructure may be established across multiple circuit cards.

Owner:LIONRA TECH LTD +1

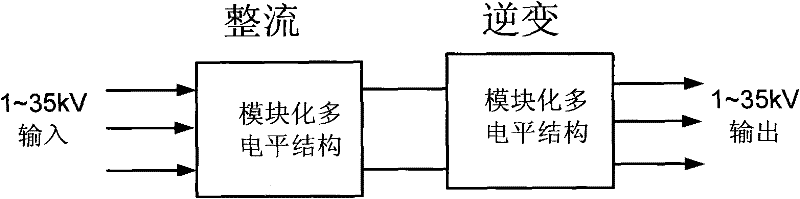

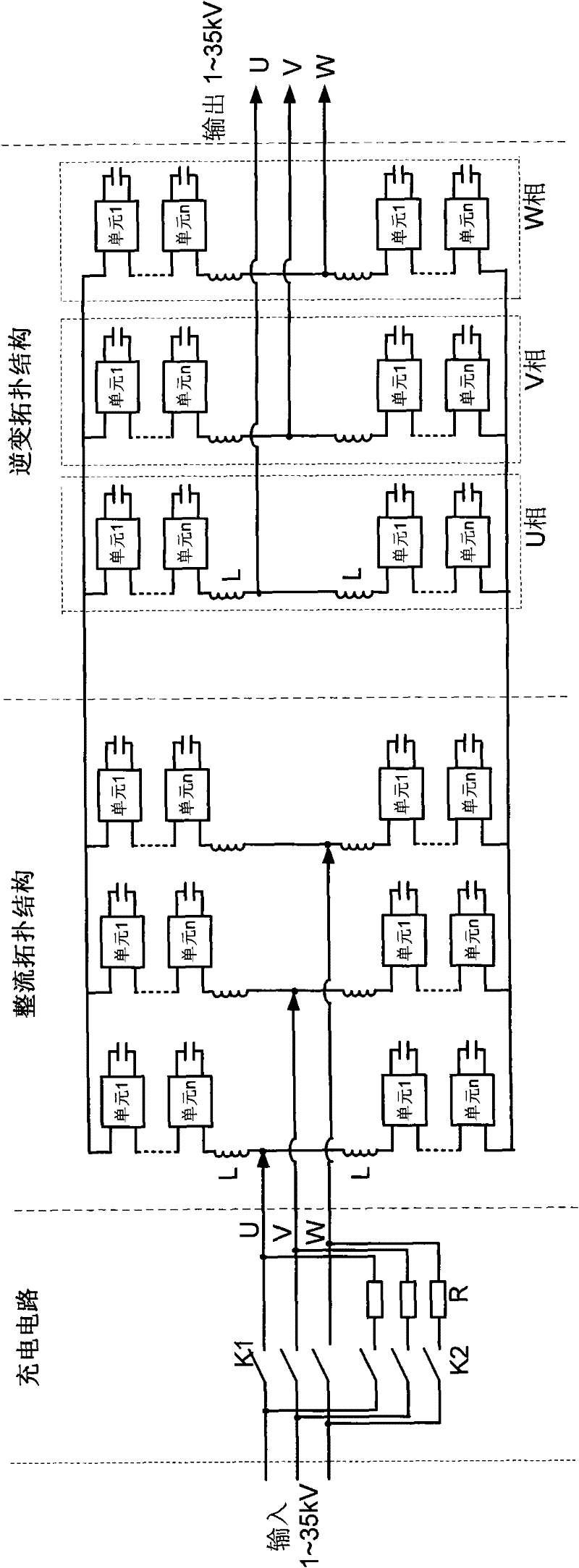

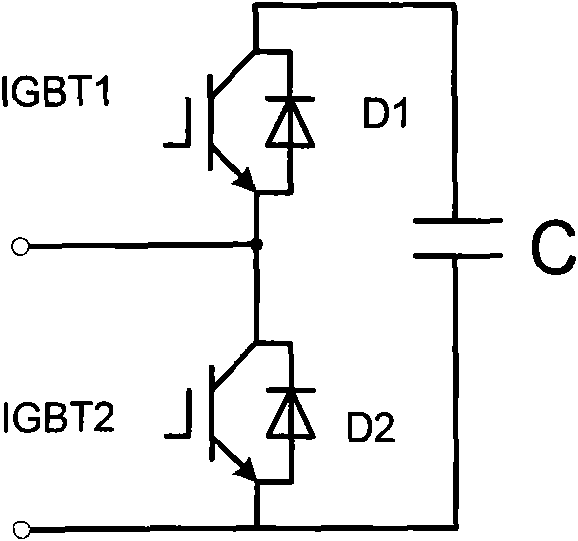

Modular multilevel converter (MMC)-based transformer-free four-quadrant high-voltage variable frequency power supply topological structure

InactiveCN102055347AReduce volumeReduce weightConversion with intermediate conversion to dcDc-ac conversion without reversalPower topologyHemt circuits

Owner:RONGXIN POWER ELECTRONICS

Semiconductor memory device

ActiveUS20090219775A1Reduce and eliminate test timeElectronic circuit testingError detection/correctionHemt circuitsEngineering

Semiconductor memory device includes a cell array including a plurality of unit cells; and a test circuit configured to perform a built-in self-stress (BISS) test for detecting a defect by performing a plurality of internal operations including a write operation through an access to the unit cells using a plurality of patterns during a test procedure carried out at a wafer-level.

Owner:SK HYNIX INC

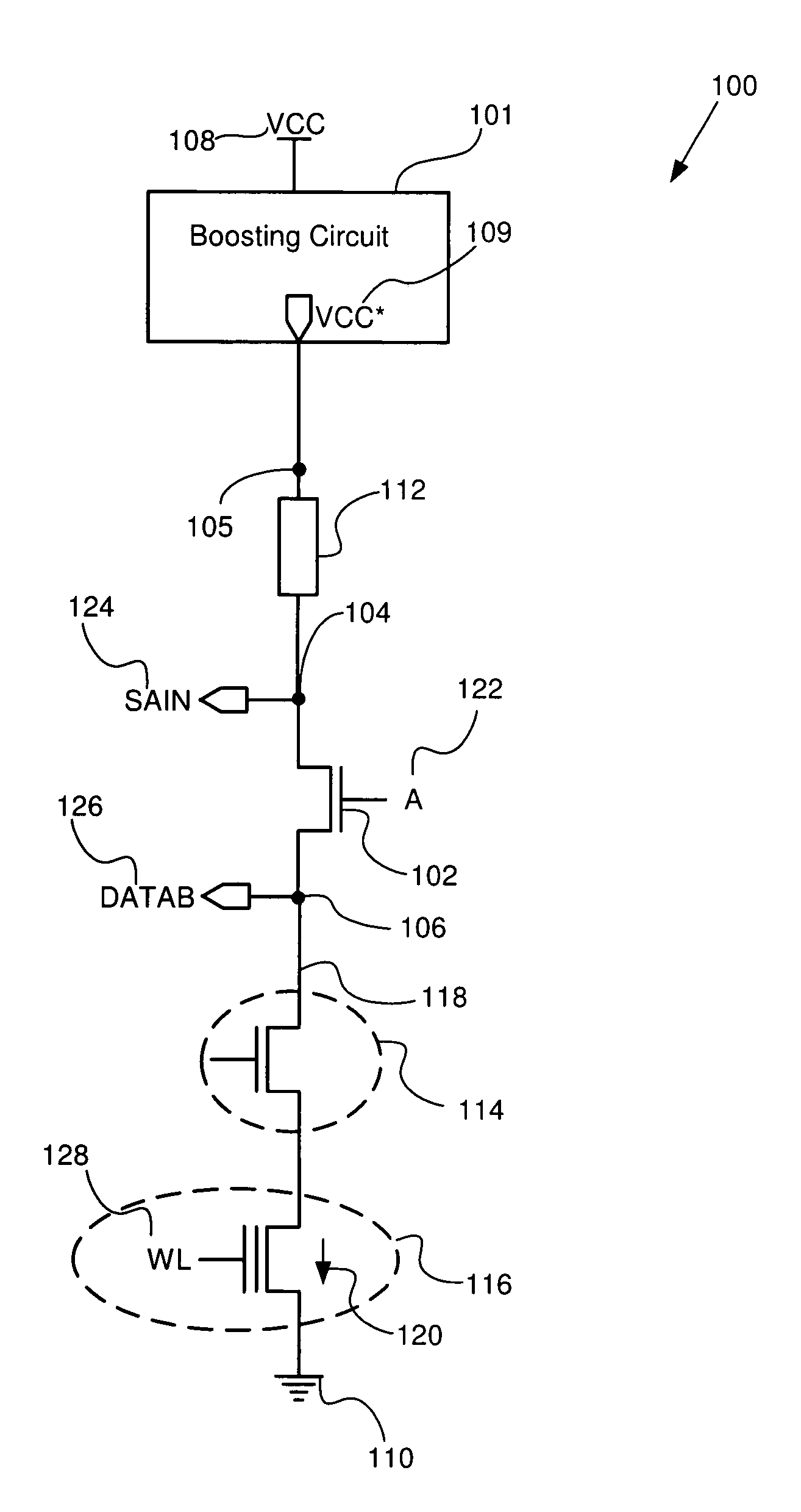

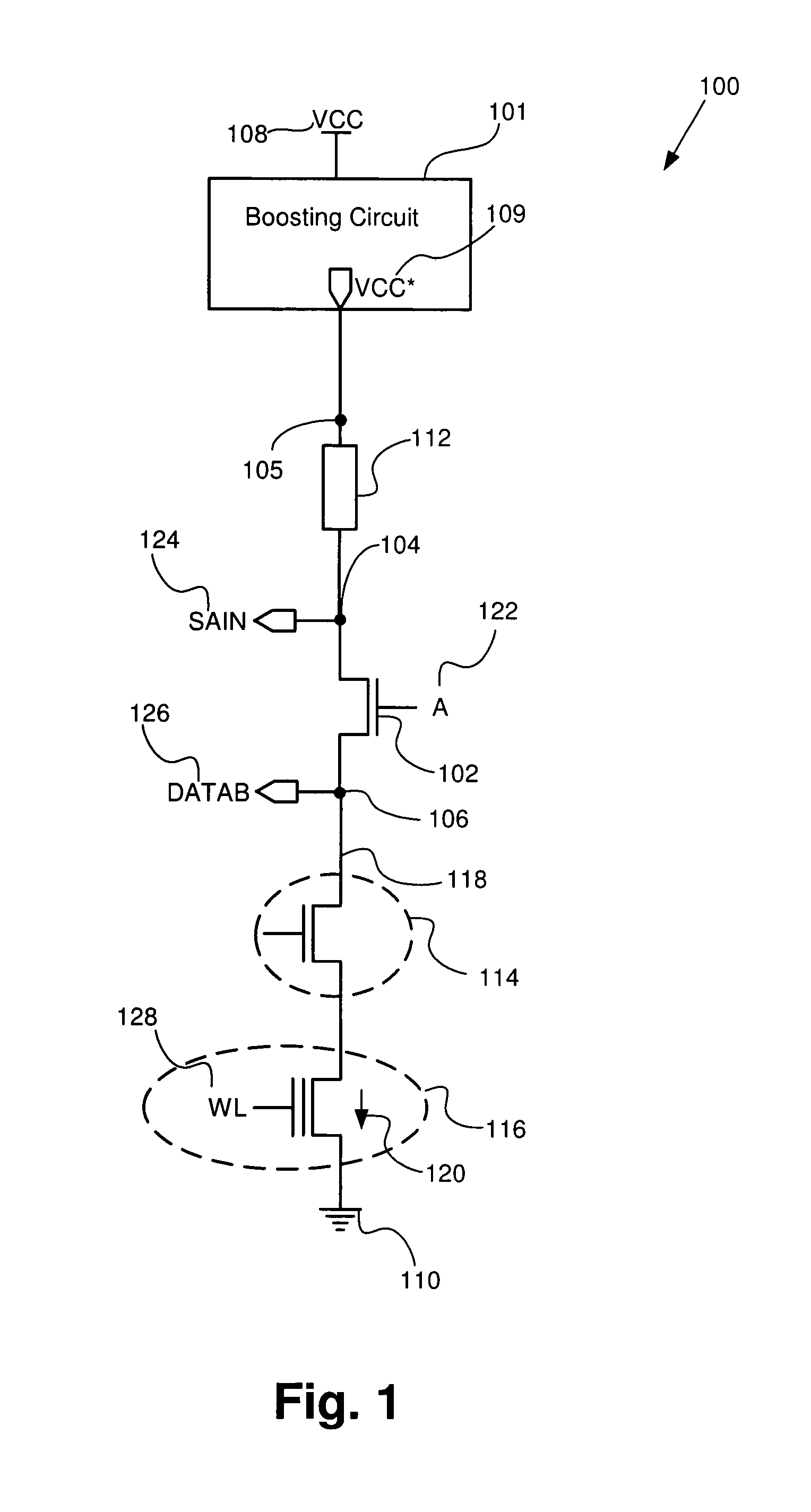

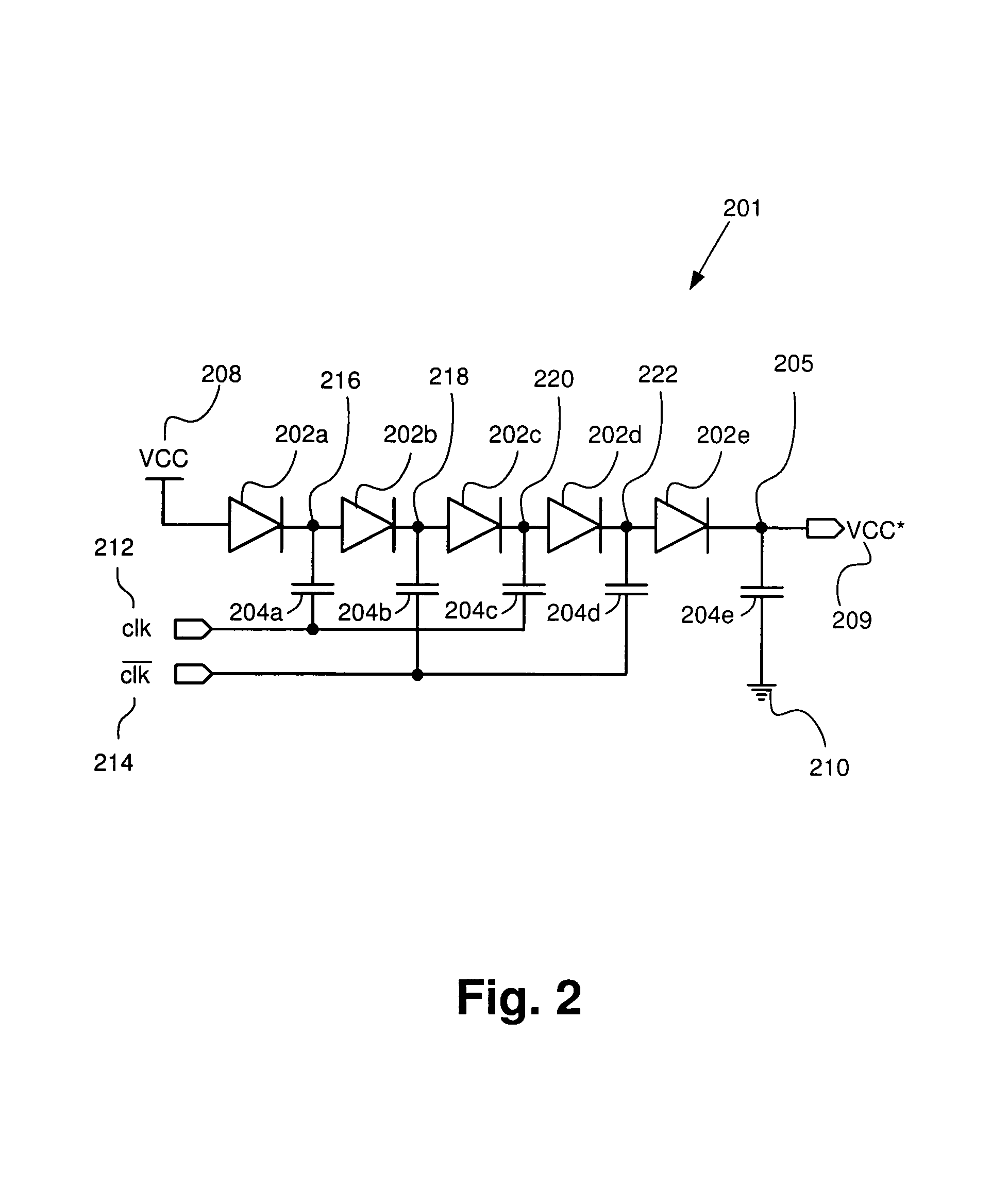

High-voltage switch with low output ripple for non-volatile floating-gate memories

A high-voltage switch has a high-voltage input terminal, receiving a high voltage, and an output terminal. A pass transistor, having a control terminal, is connected between the high-voltage input terminal and the output terminal. The output of a voltage-multiplying circuit of the charge-pump type is connected to the control terminal. The voltage-multiplying circuit is of a symmetrical type, has first and second charge-storage means, receiving a clock signal of a periodic type, and has a first circuit branch and a second circuit branch, which are symmetrical to one another and operate in phase opposition with respect to the clock signal.

Owner:MICRON TECH INC

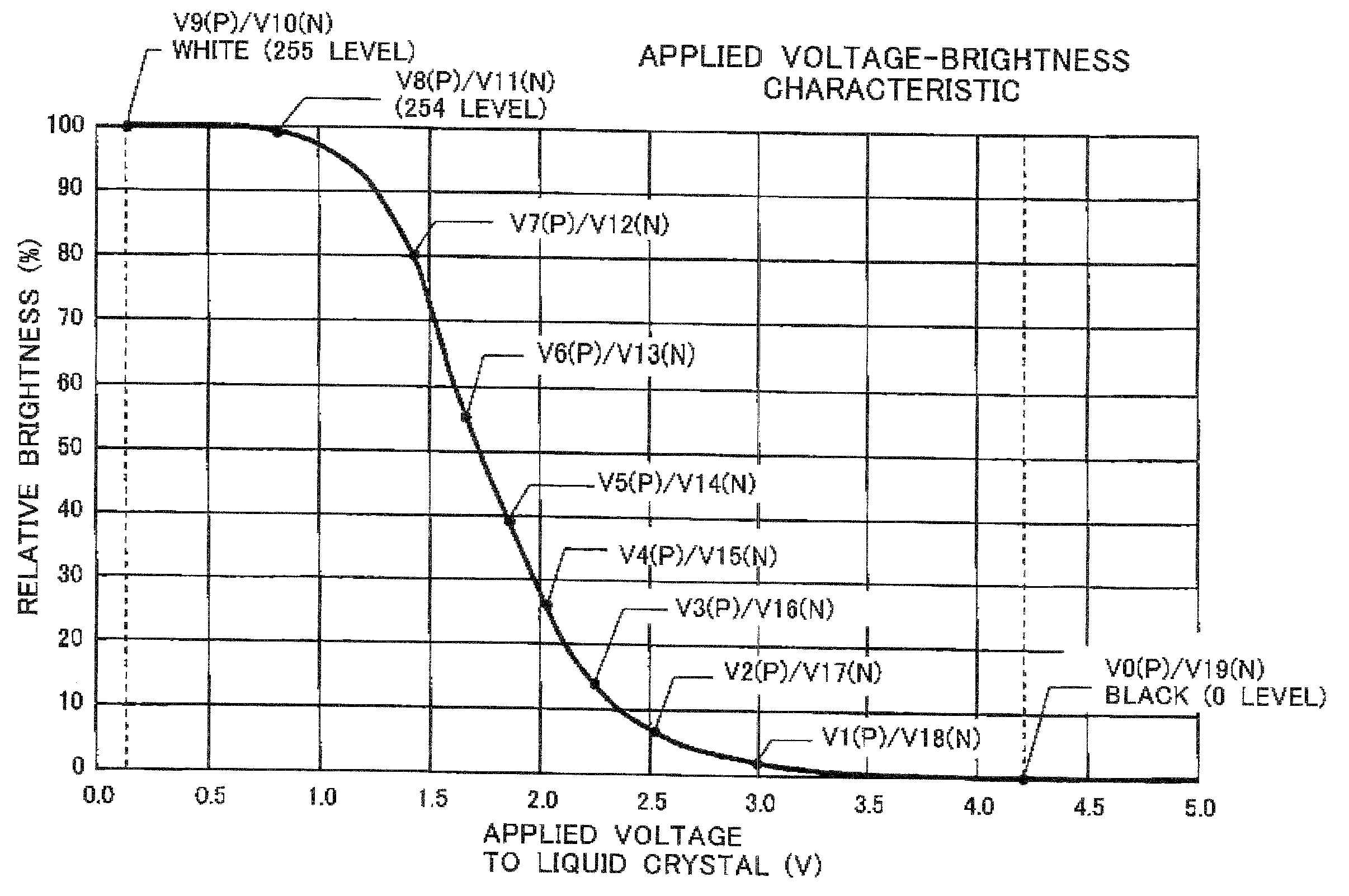

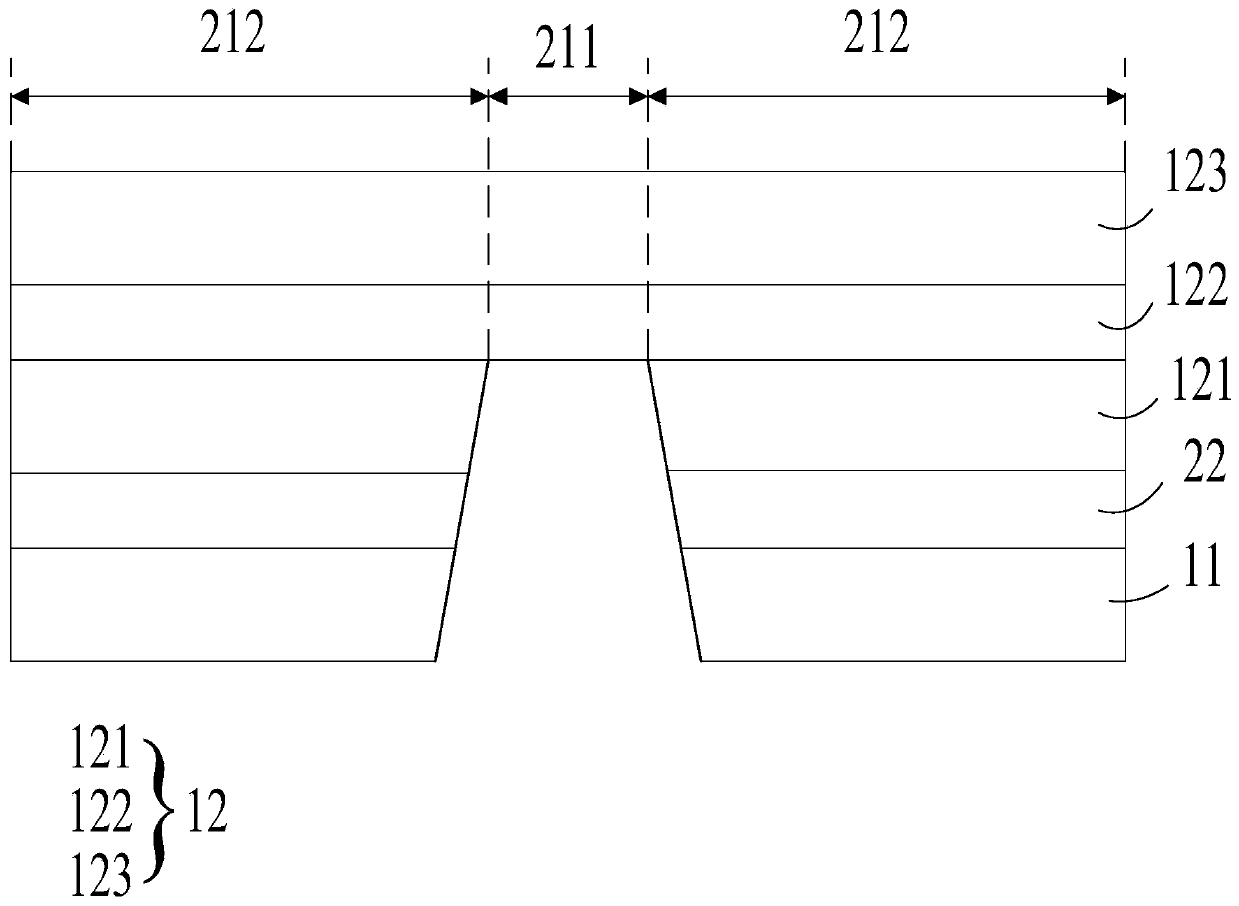

Liquid crystal display device

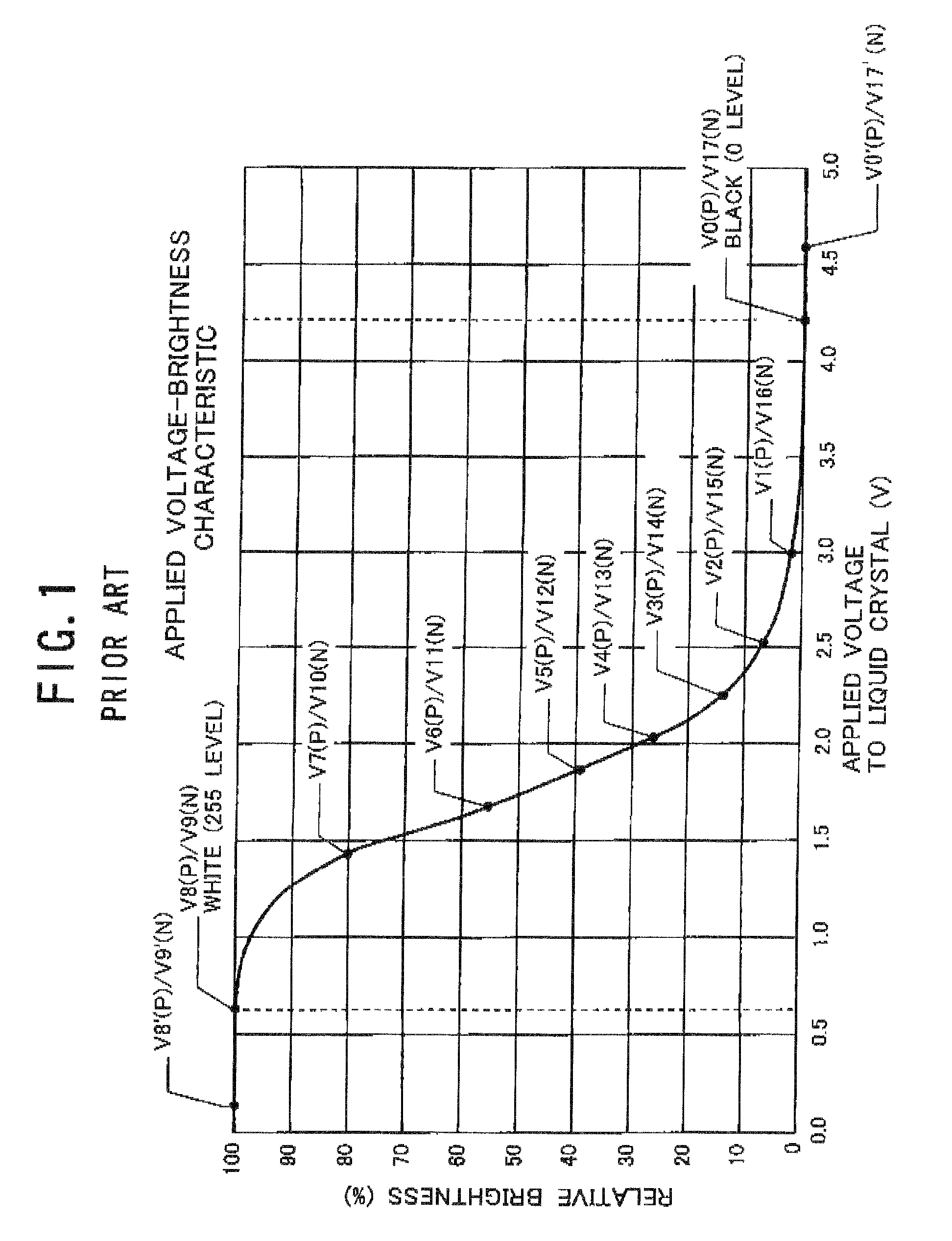

InactiveUS20080259014A1Prevent gray level foldingAvoid complicationsCathode-ray tube indicatorsInput/output processes for data processingLiquid-crystal displayVoltage reference

A liquid crystal display device prevents the gray level folding in at least one of the vicinities of the highest and lowest gray levels while avoiding the complication of the data line driver circuit. The data line driver circuit generates output voltages whose number is equal to a predetermined gray level number M based on reference voltages, and selects one of the output voltages and outputs the selected one to the display section in response to an inputted image signal, thereby displaying images The applied voltage-brightness characteristic of the display section has a zero brightness change region in which the reference voltage corresponding to the highest gray level is located. The reference voltage corresponding to the next lower level to the highest level is set such that the brightness at the next lower level is lower than that at the highest level by a predetermined difference.

Owner:NEC LCD TECH CORP

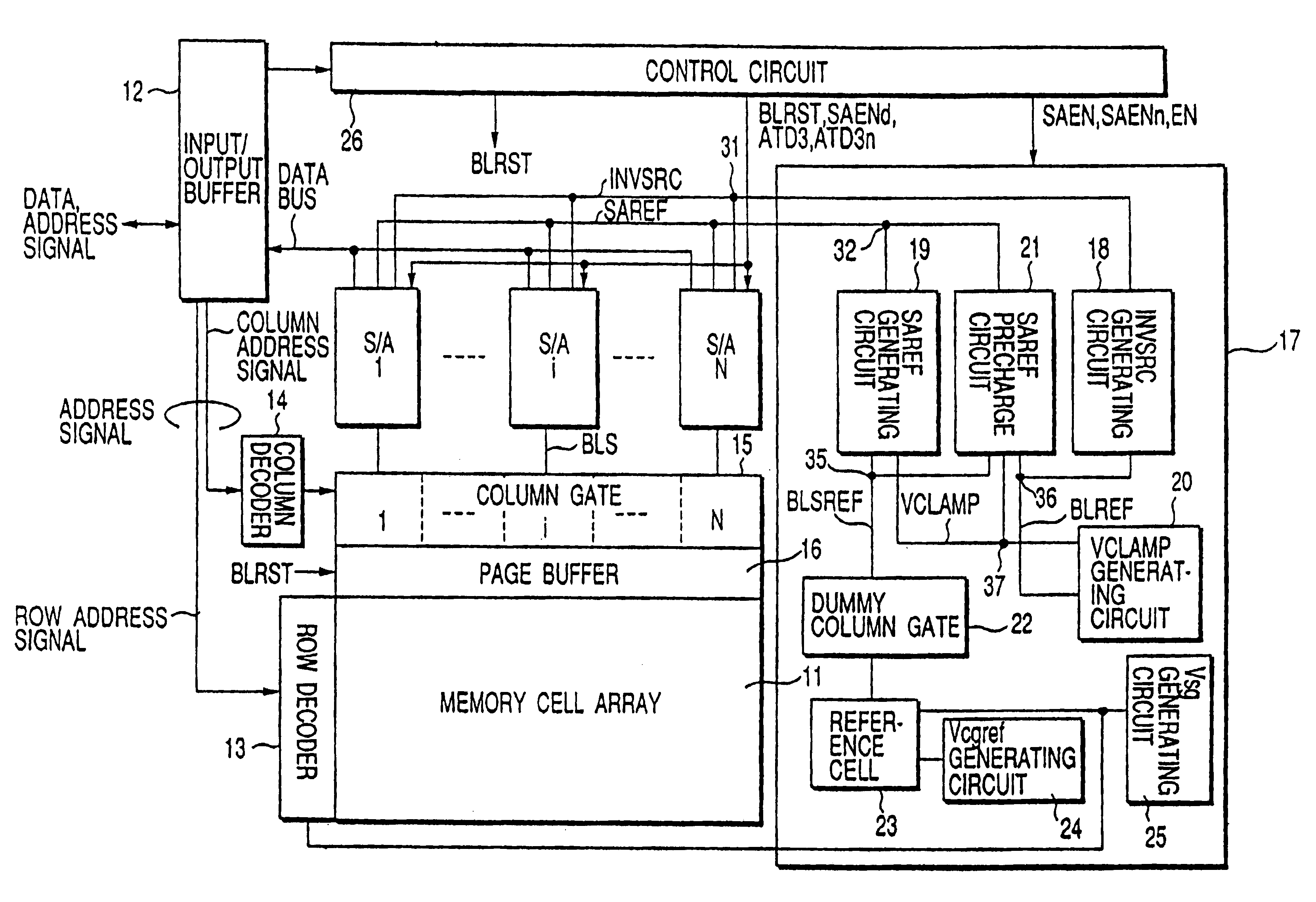

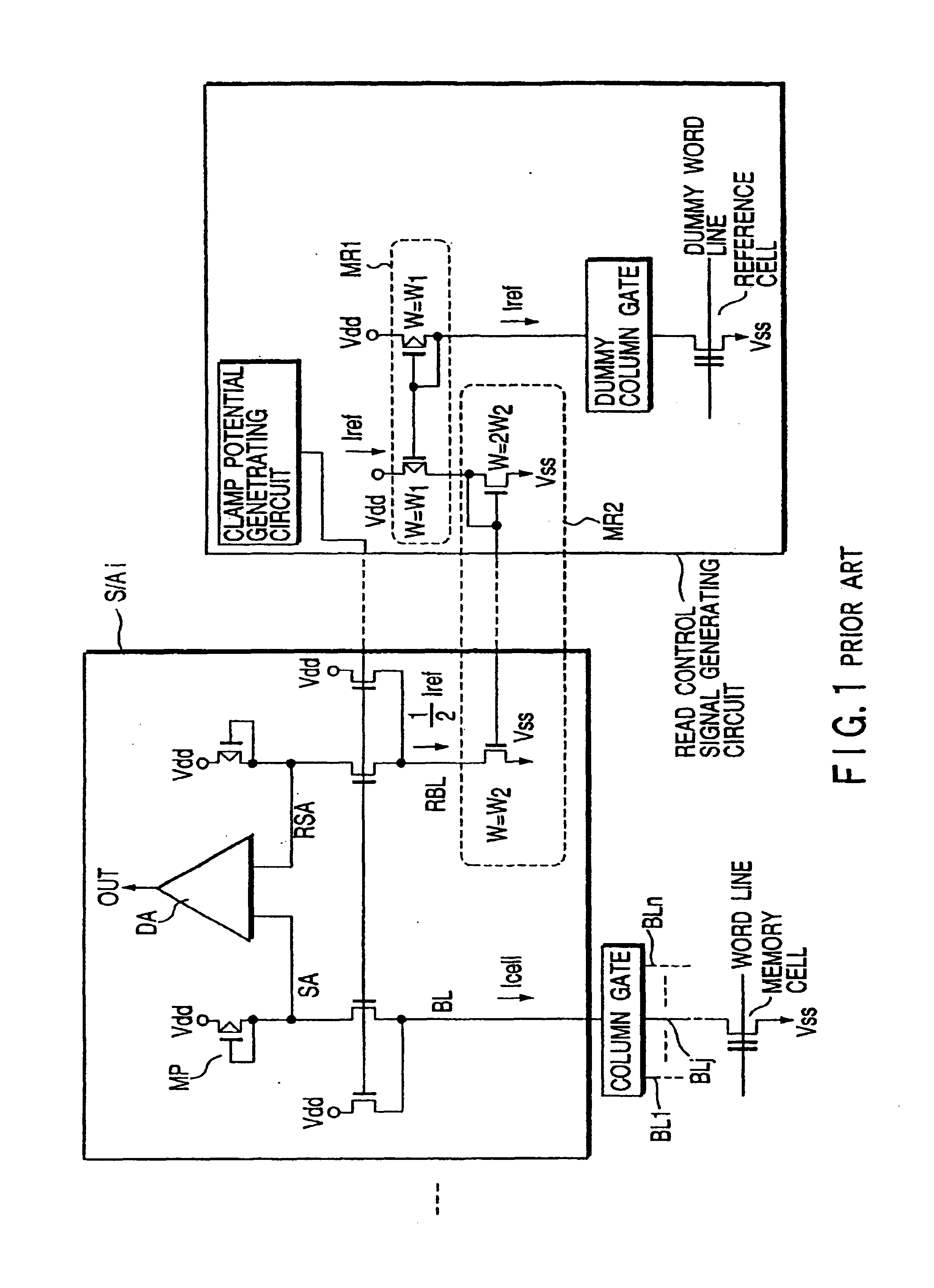

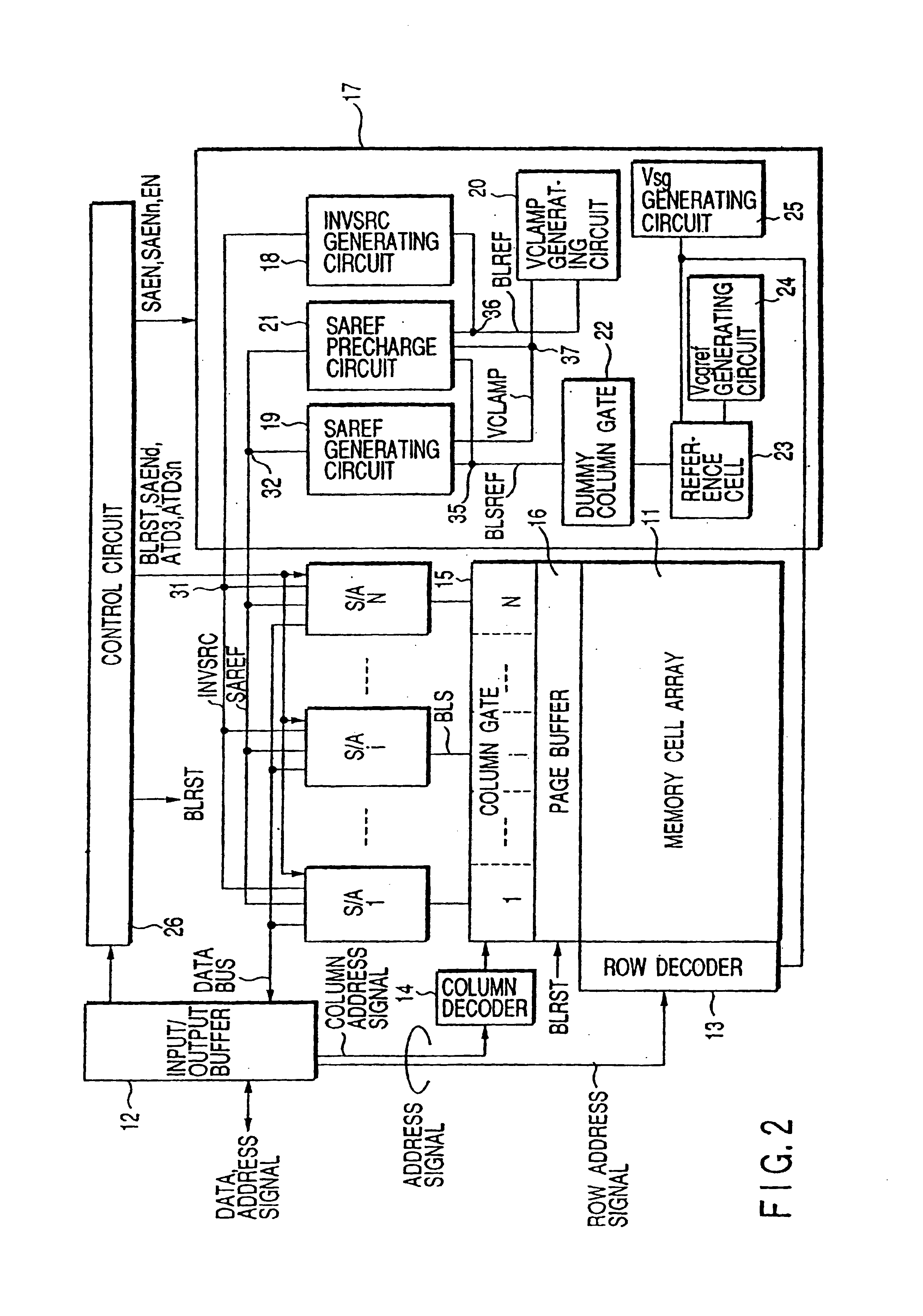

Read circuit of nonvolatile semiconductor memory

InactiveUS6845047B2Total current dropPerforming readRead-only memoriesDigital storageBit lineComputer architecture

Owner:KK TOSHIBA

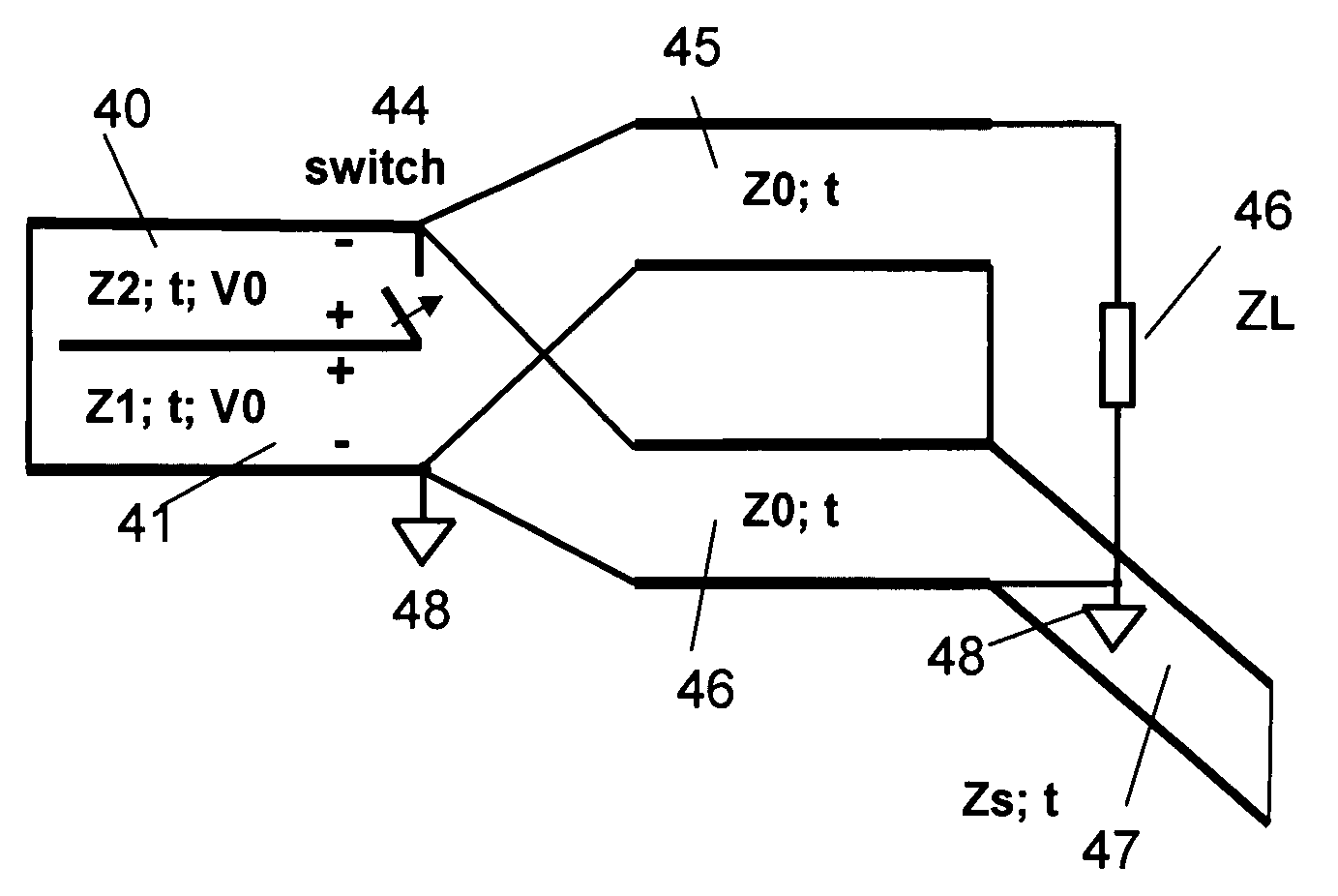

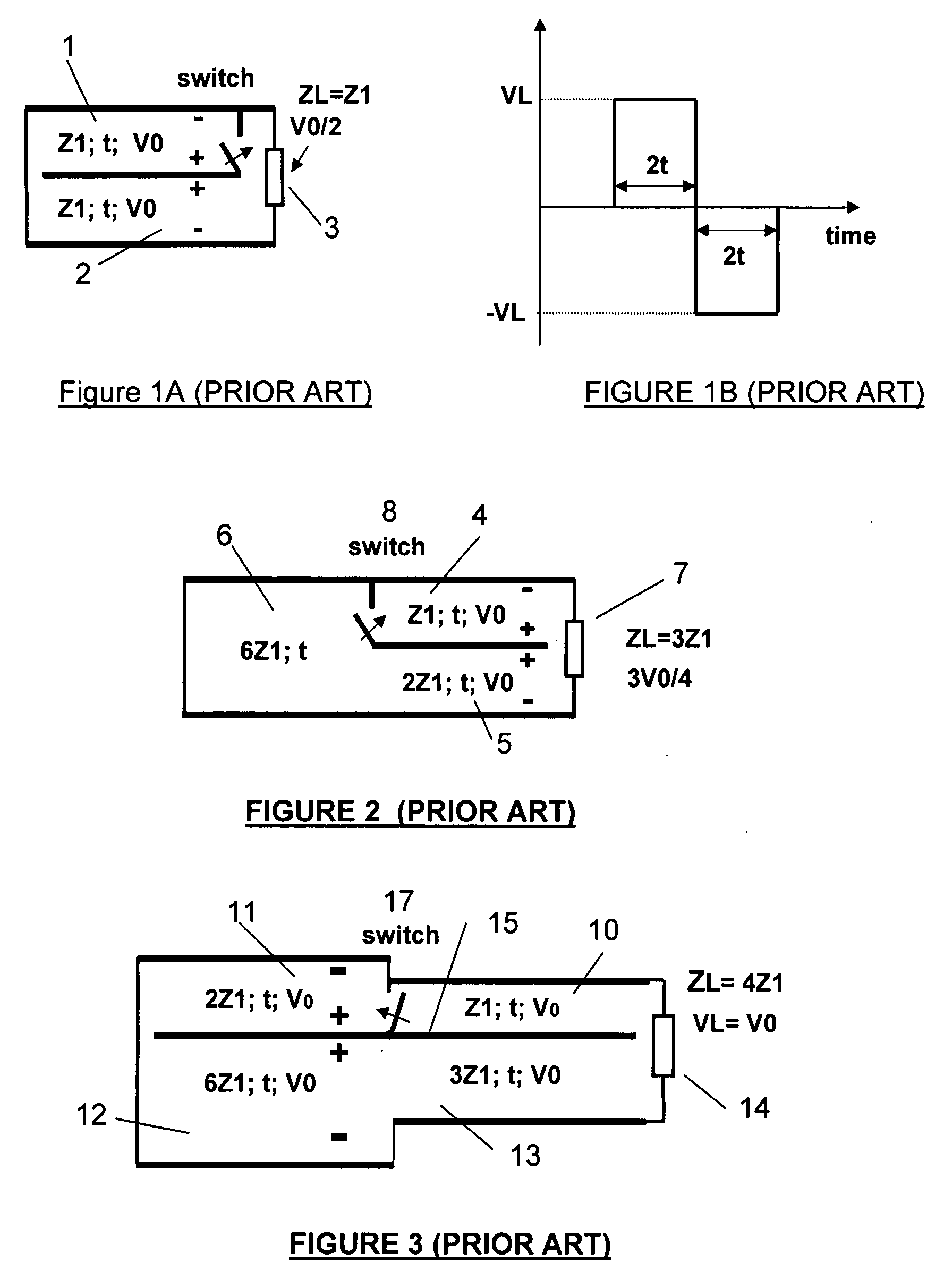

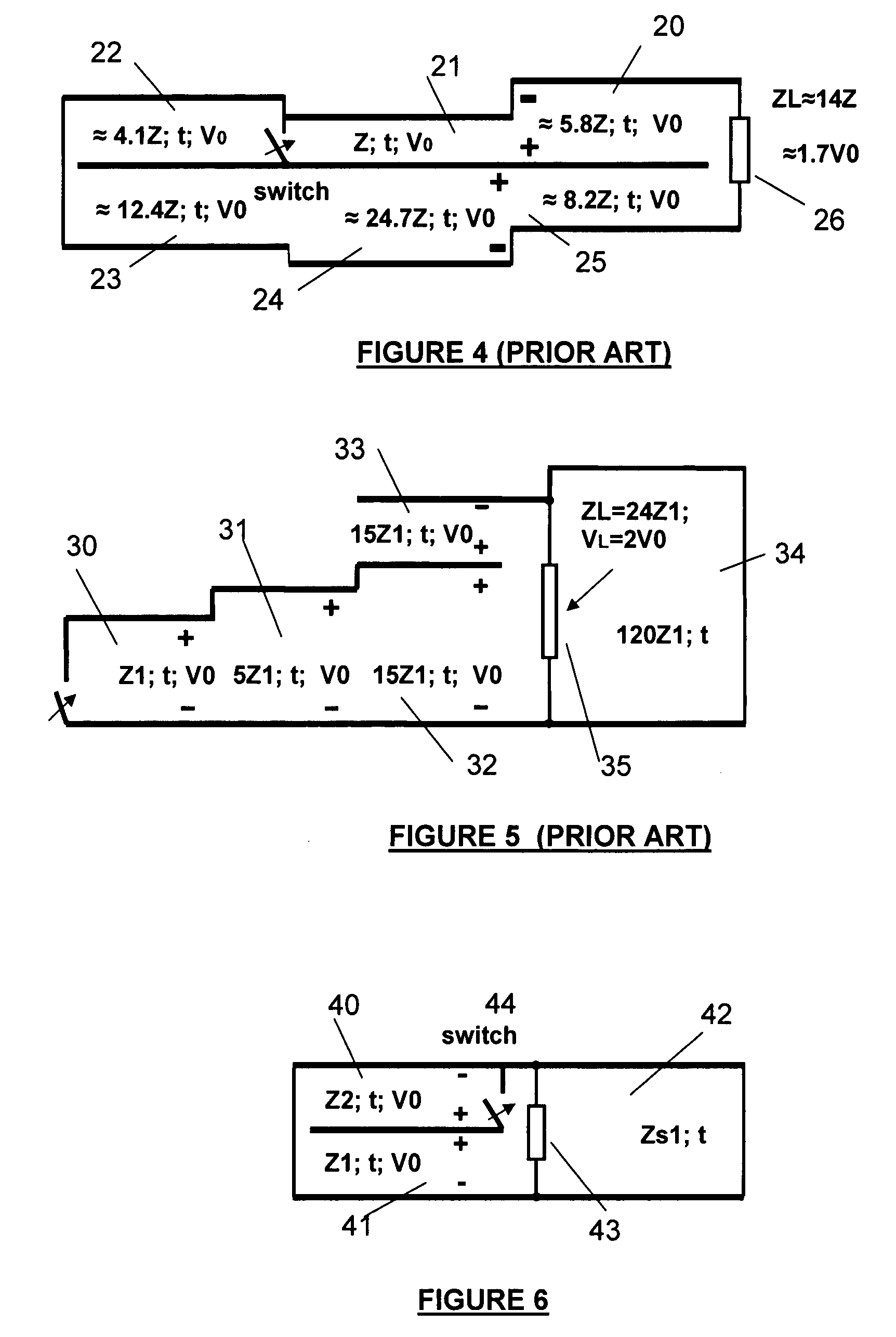

High power bipolar pulse generators with impedance transformation

InactiveUS20080224794A1Efficient impedance transformationMaximize energy transferMultiple-port networksTransmission control/equlisationHigher PowerTransmission line transformer

A bipolar pulse generator circuit generates bipolar pulses and provides an impedance transformation. The circuit is amenable for implementation in a variety of configurations depending on the size and pulse width requirements for the design. It also maximizes energy transfer and may be implemented in a straight forward, easy manner.The generator may be implemented with one or two switches in a three, five or more transmission line implementation and may include inductive stub, which is inherent element of transmission line transformers. The generator may also be implemented in a multi-layer folded configuration, with or without the addition of a ground potential conductor. The generator may also be implemented in stacked or / and balanced configurations.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

Radiation tolerant combinational logic cell

InactiveUS20070109865A1Increase energy levelReduce sensitivityRead-only memoriesDigital storageCMOSData set

Owner:IDAHO UNIV OF +1

Static electricity neutralizer

InactiveUS20080192403A1Eliminate static electricityRelaysElectrostatic chargesElectrical connectionHemt circuits

A method of dissipating static electricity for a charged object includes the steps of electrically connecting an electrostatic probe with an electric terminal of an electrostatic dissipater; contacting the electrostatic probe with the charged object for electrically conducting the charged object with the electrostatic dissipater through the electric terminal and the electrostatic probe to form a electrostatic dissipation circuit, wherein when the charged object possess static electricity, the static electricity is in electric connection with the electrostatic probe; and diverting the static electricity of the charged object to the electrostatic dissipater through the electrostatic probe and the electric terminal, wherein the electrostatic dissipater converts the electrostatic energy into another predetermined form of energy as consumption of the static electricity so as to eliminate the static electricity of the charged object through the electrostatic dissipation circuit.

Owner:CHEN PIN KUANG

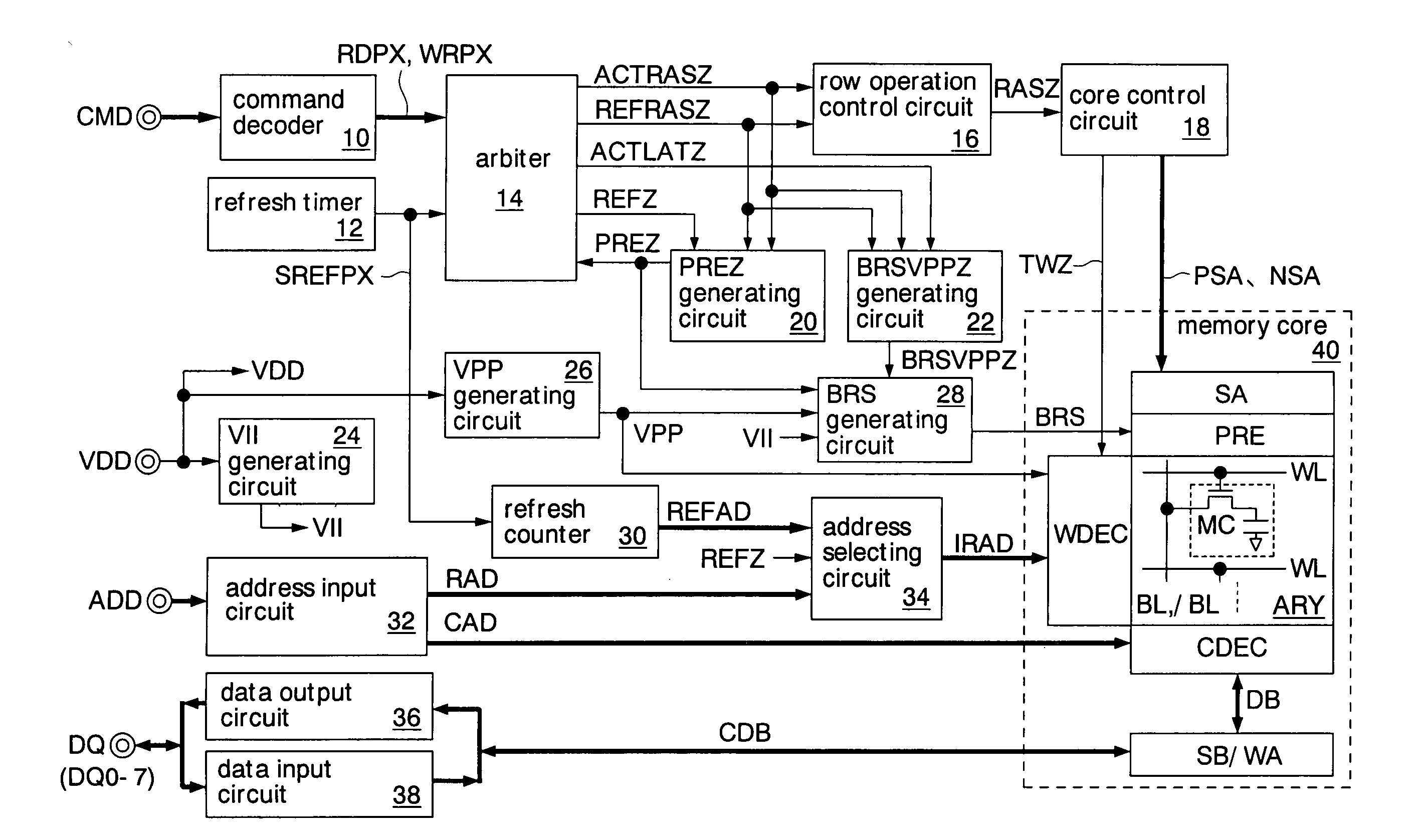

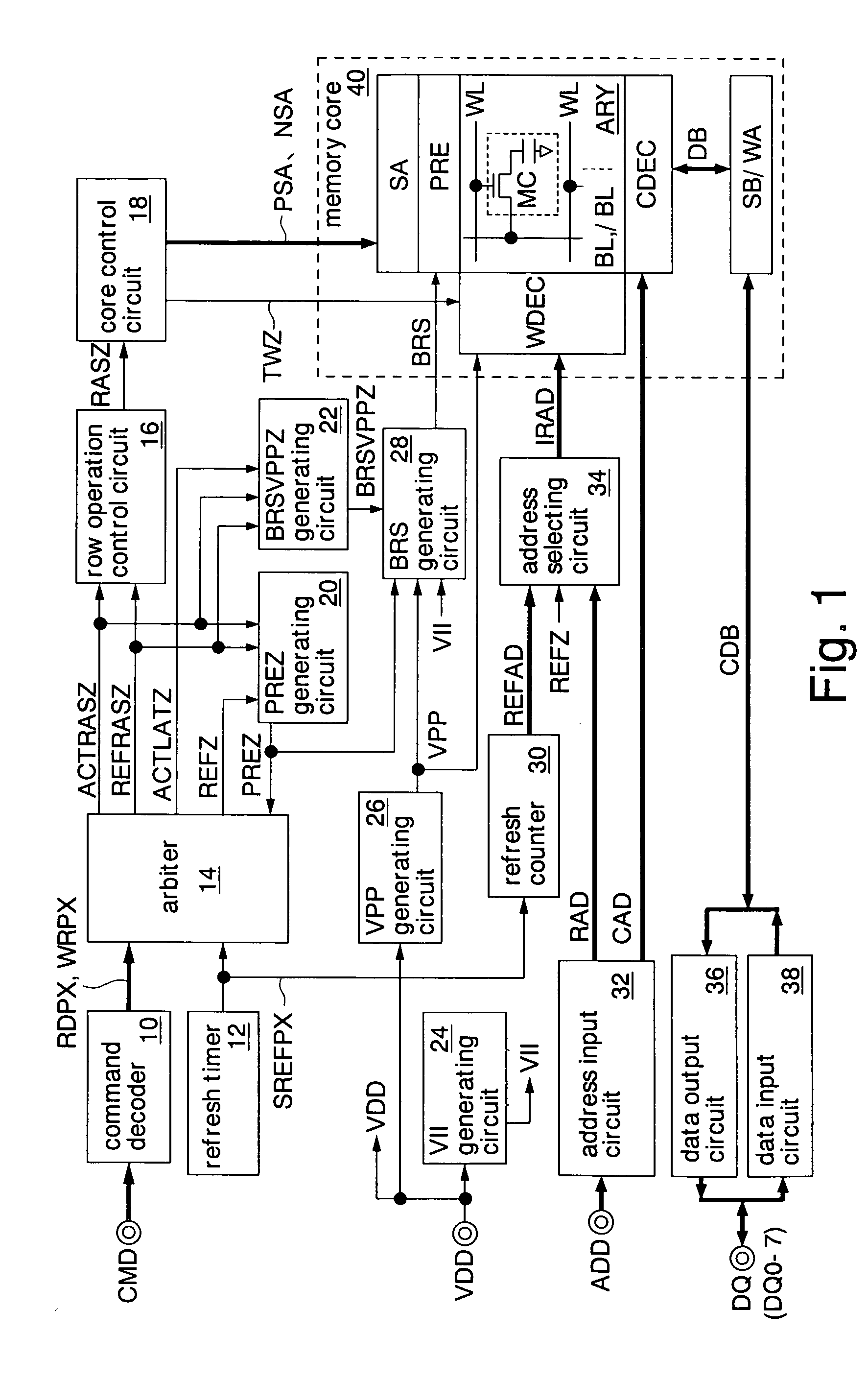

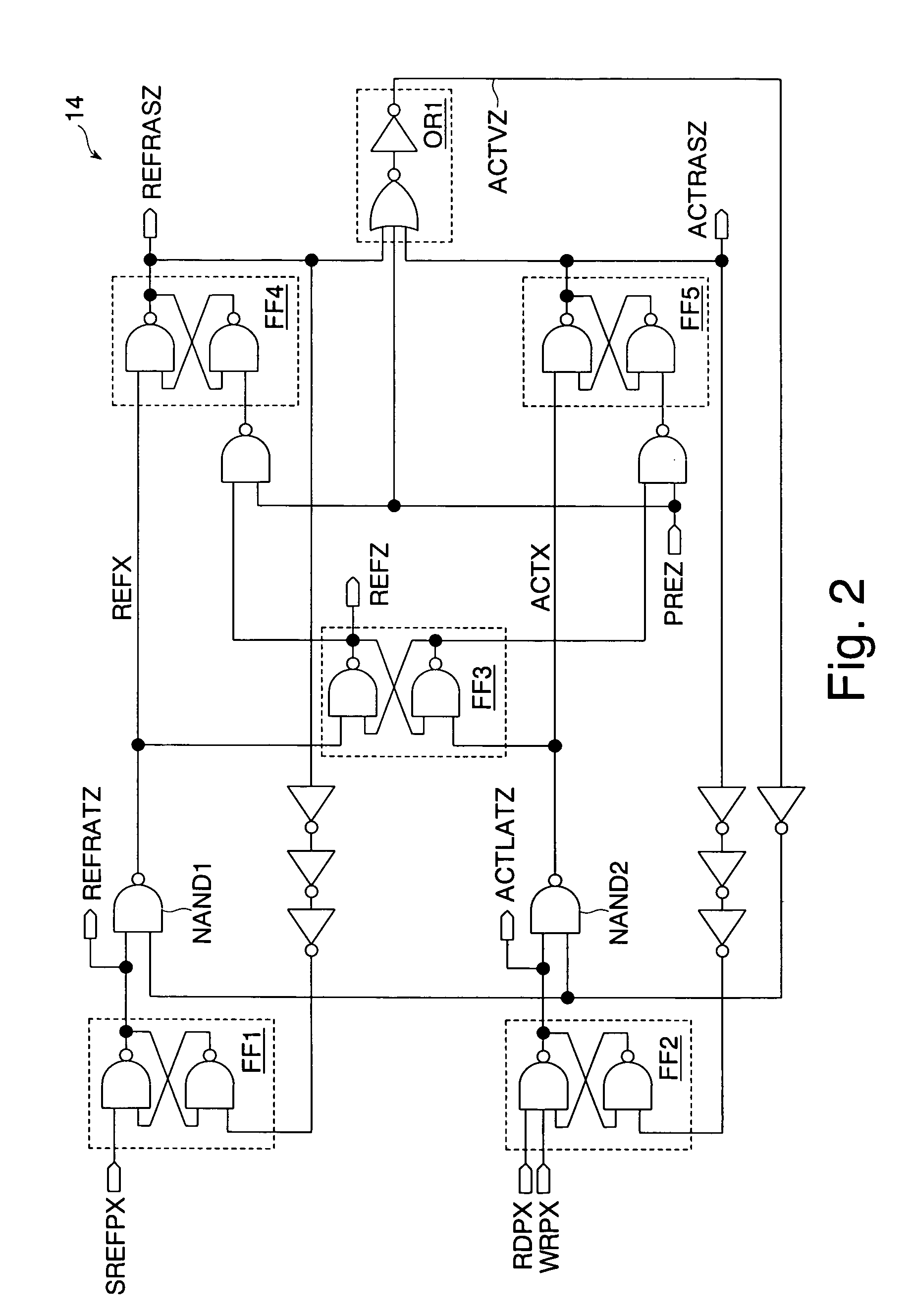

Semiconductor device having reset function

A semiconductor device comprises a memory cell array, a row control circuit for controlling an access to the memory cell array, and a refresh control circuit for instructing the row control circuit to refresh the memory cell array. After temporarily transiting to a reset state due to an activation of a reset signal, the refresh control circuit instructs to refresh the memory cell array in response to a transition to an initial state due to a de-activation of the reset signal.

Owner:LONGITUDE SEMICON S A R L

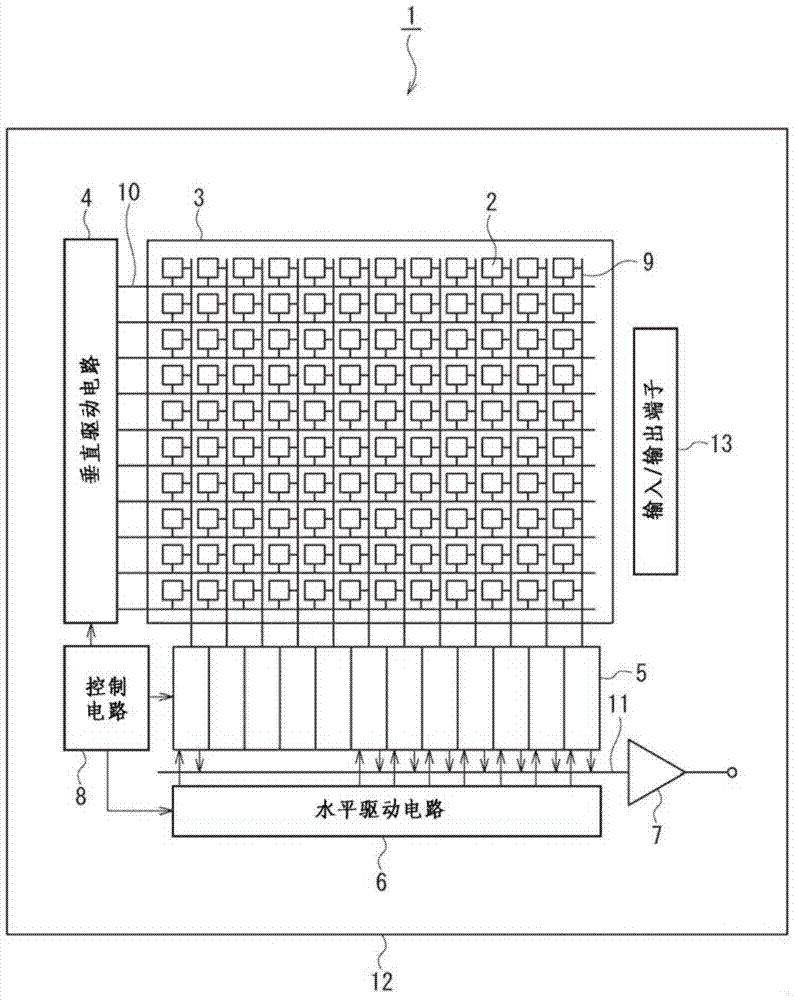

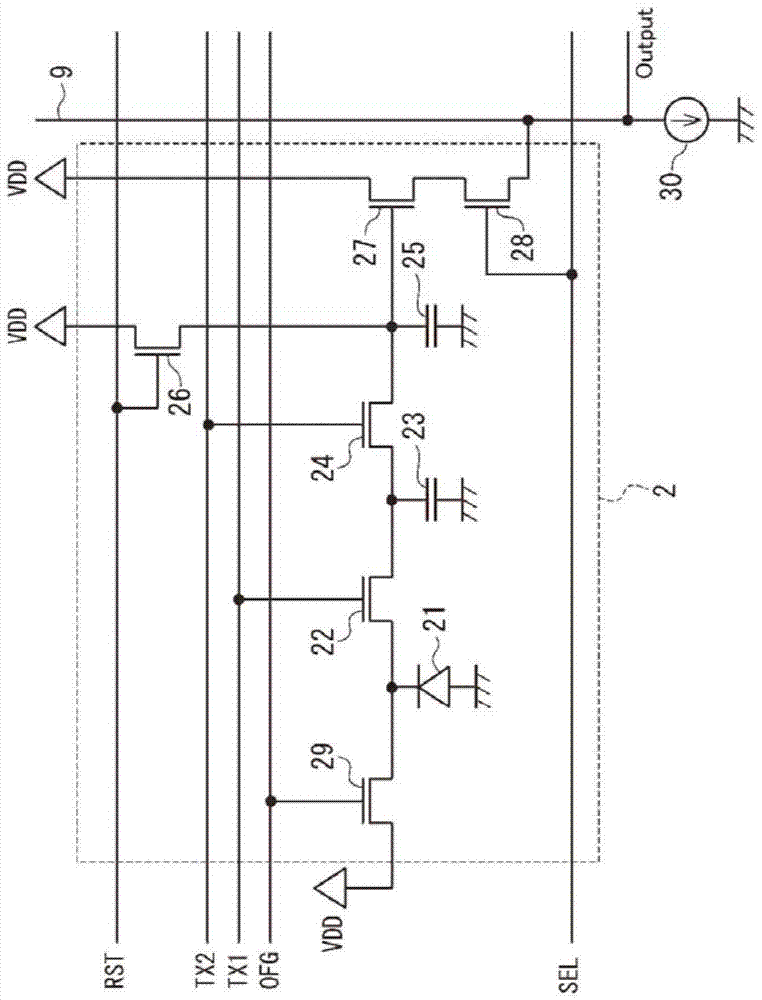

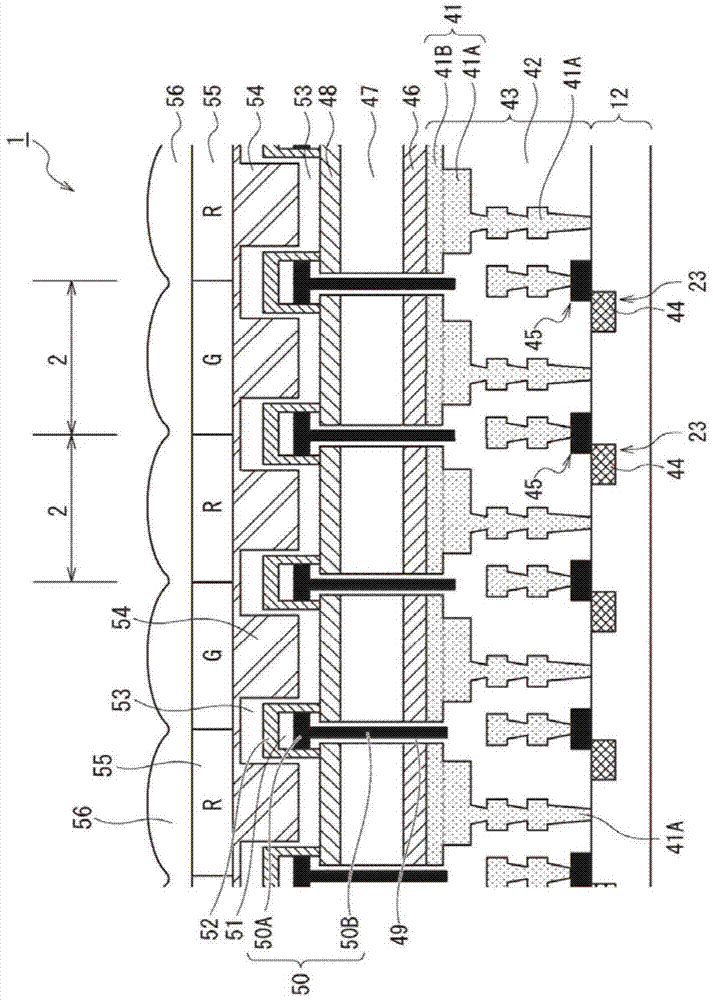

Solid-state image sensor, method of producing the same, and electronic apparatus

Owner:SONY SEMICON SOLUTIONS CORP

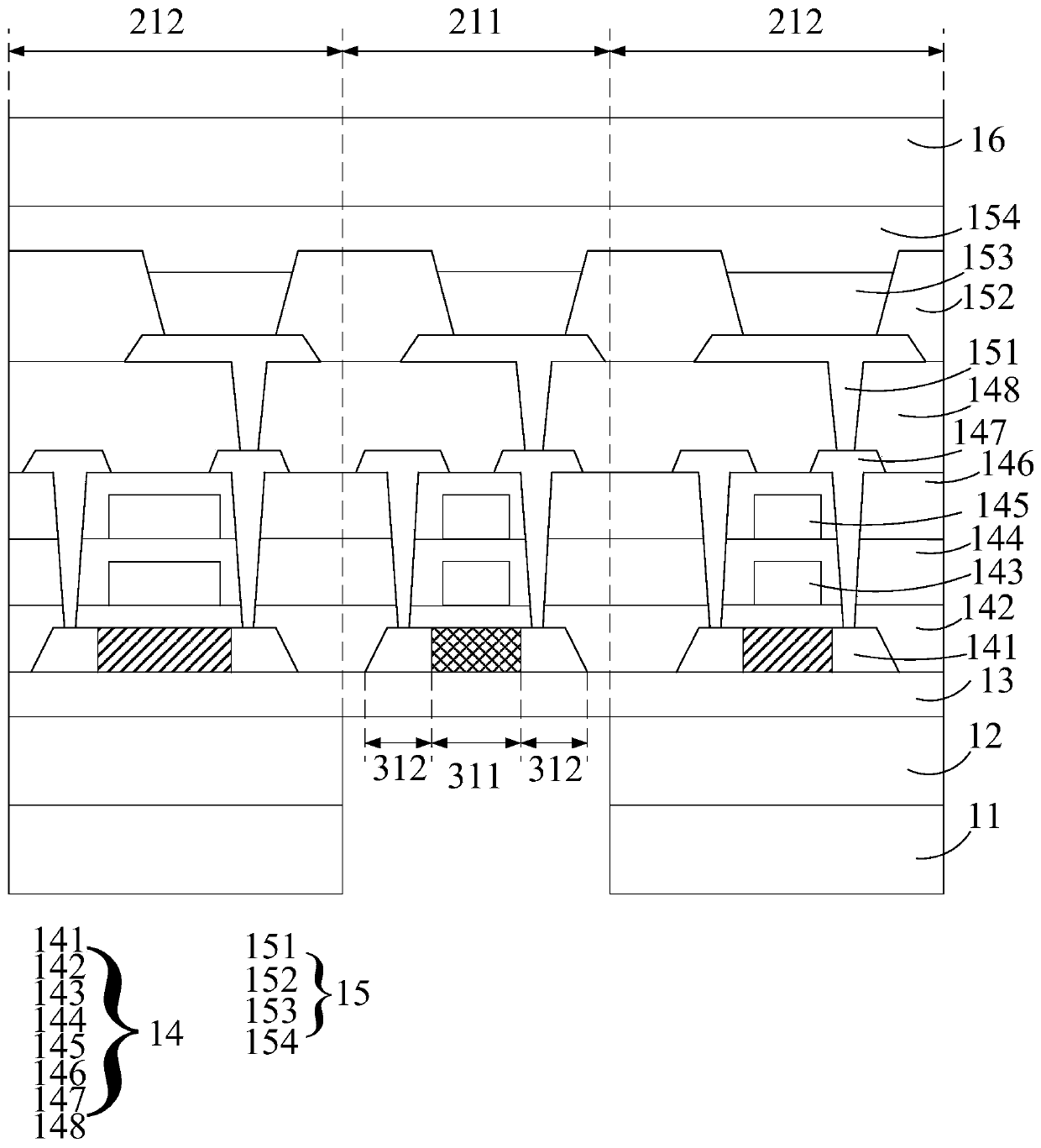

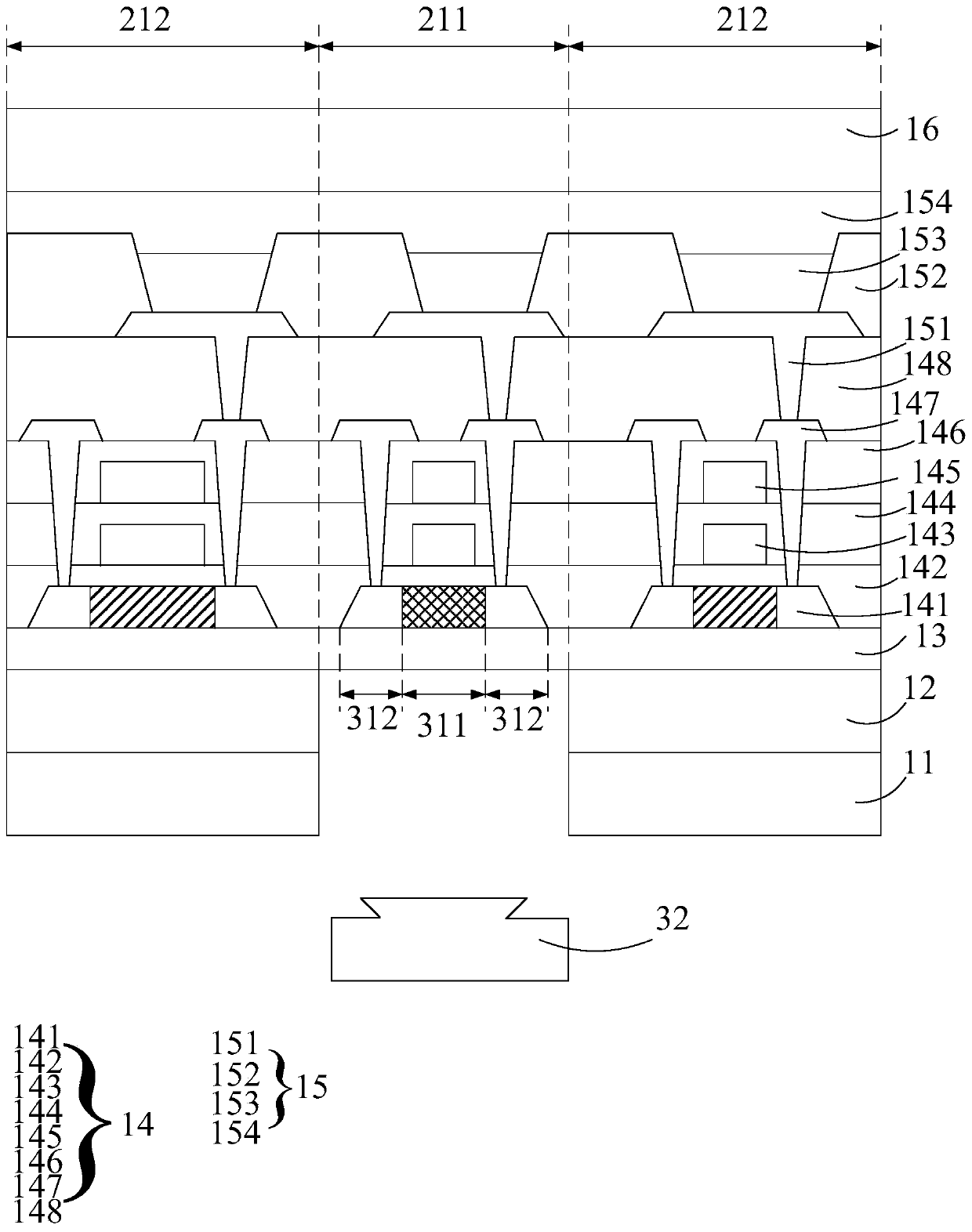

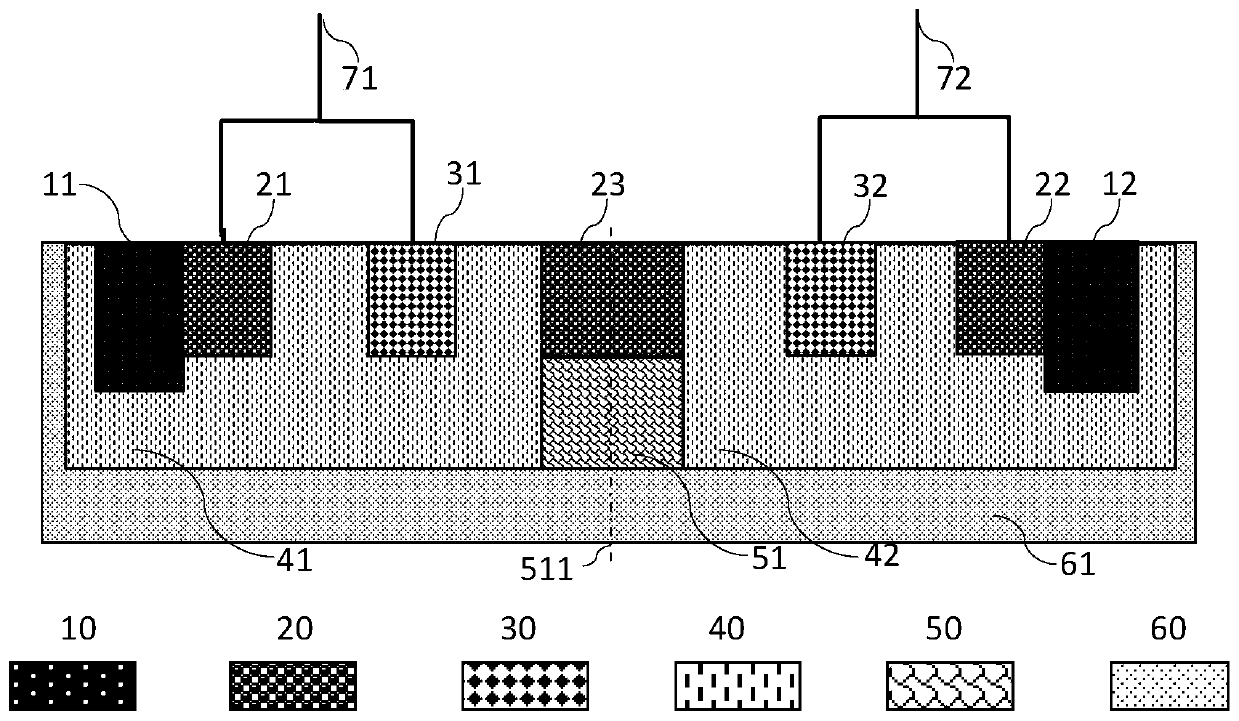

OLED display panel and manufacturing method thereof, and OLED display device

ActiveCN111211156AHigh light transmittanceIncrease the screen ratioSolid-state devicesPhotovoltaic energy generationDisplay deviceHemt circuits

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Organic light emitting diode pixel compensation circuit, and display panel and display device containing the same

An Organic Light Emitting Diode pixel compensation circuit is disclosed. The circuit includes first through fifth transistors, and a storage capacitor. The first transistor is coupled to a first scan signal, a power supply voltage, and a first electrode of the storage capacitor. In addition, the second transistor is coupled to the first scan signal, a data signal, and the third transistor. The third transistor is coupled to the power supply voltage, and the fifth transistor. Furthermore, the fourth transistor is coupled to a second scan signal, the third transistor, and the storage capacitor, and fifth transistor is coupled to a light emitting signal, and the OLED. In addition, the storage capacitor is coupled to the fifth transistor, and a low-level signal and emits light based on a drive current generated by the third transistor.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD +1

LDO circuit

InactiveCN108021169AReduce power consumptionSmall fluctuationElectric variable regulationReference currentHemt circuits

The invention provides an LDO circuit. The LDO circuit comprises a reference source, a differential amplifier and an LDO output stage. The reference source provides one reference voltage and one reference current bias voltage; a first input end of the differential amplifier is connected to the reference voltage output by the reference source, a second input end of the differential amplifier is connected to the output voltage of the LDO, and the output end of the differential amplifier is connected to a grid of a power output tube of the LDO. The differential amplifier and the LDO output stageform a closed loop to make the output voltage stabilized at the reference voltage. The LDO output stage comprises a tail current source NM6 which can reduce fluctuation of the output voltage. The LDOcircuit is simple in structure, has low technological requirements and reduces the complexity of chip design.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

Circuit and technique for accurately sensing low voltage flash memory devices

Owner:MONTEREY RES LLC

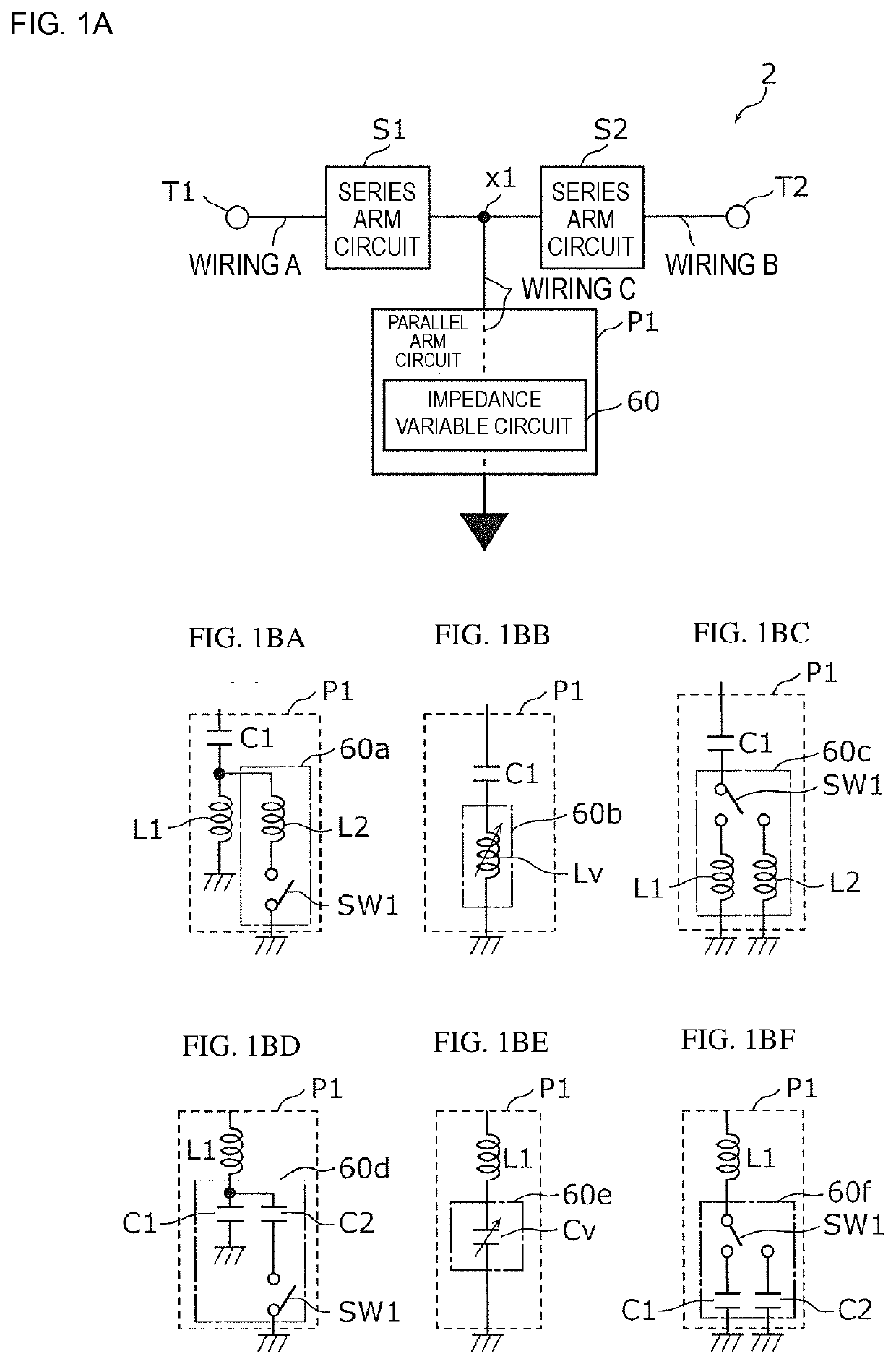

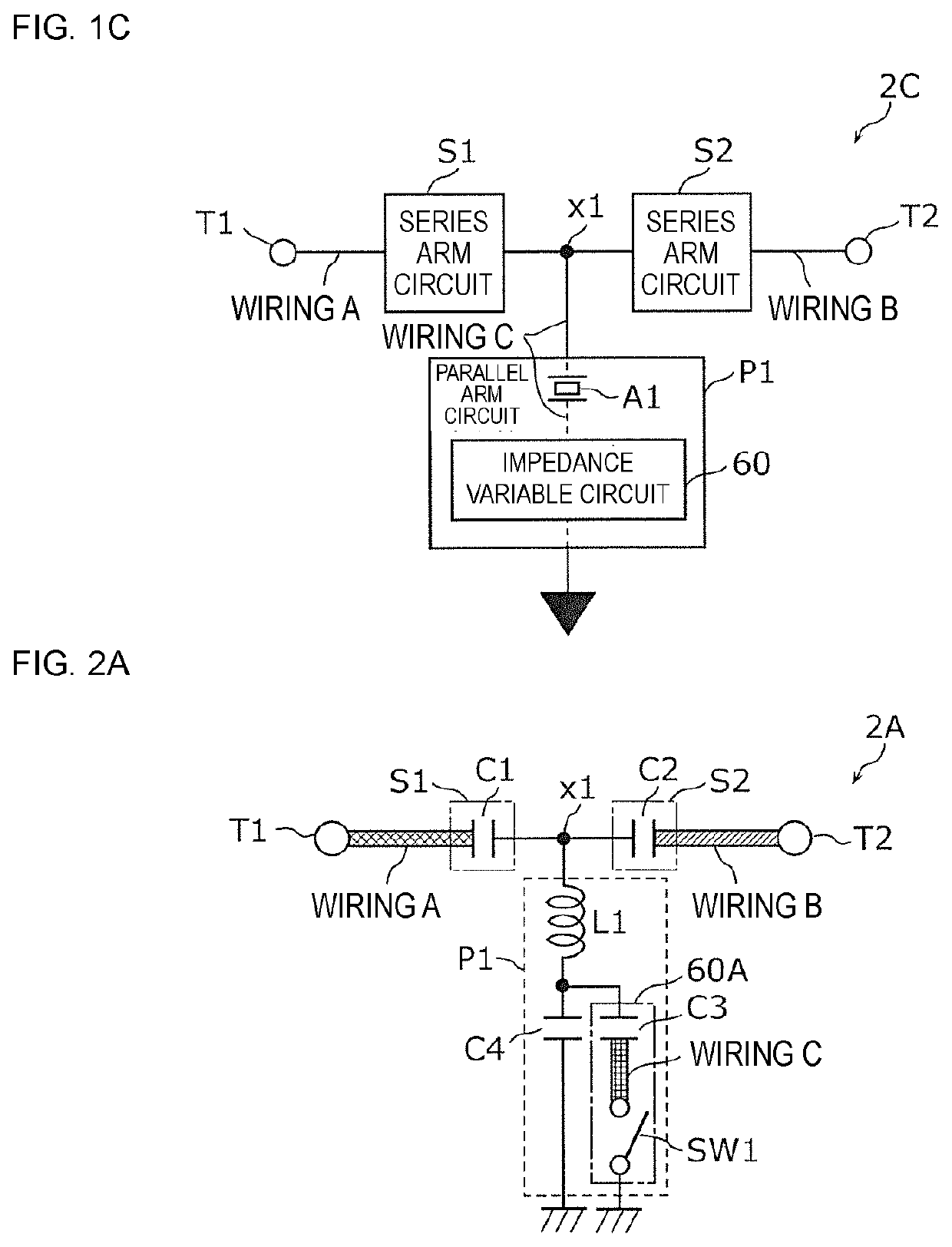

Radio frequency circuit, multiplexer, radio frequency front end circuit and communication apparatus

ActiveUS20200252042A1Reduce lossSpeed up the descentMultiple-port networksFrequency-division multiplex detailsMultiplexingMultiplexer

Owner:MURATA MFG CO LTD

Triangular phase modulation wave driving apparatus for closed loop feedback control of fiber-optic gyroscope

ActiveCN107747952AAvoid errorsAvoid electromagnetic interferenceMeasurement devicesClosed loop feedbackHemt circuits

The invention discloses a triangular phase modulation wave driving apparatus for closed loop feedback control of a fiber-optic gyroscope. The apparatus is used for achieving the closed loop feedback control of the fiber-optic gyroscope. In the technical scheme, on the basis of a conventional sawtooth wave phase modulation method, the apparatus is modified so as to solve a problem caused by flashback of voltage during restoration time of the sawtooth wave. The improved design is described as follows: by means of difference characteristics and symmetry of DAC and a driving circuit, two paths ofdifferential triangular wave, which are symmetrical about 0V, are generated by the DAC and the driving circuit; by controlling two paths of analogue switches, the signal channels of the two paths of triangular waves are switched with each other at the vertexes, so that the two paths of differential triangular waves are spliced to form two paths of differential sawtooth waves. The sawtooth wave, when being applied to two electrodes of Y waveguide, has equivalent effect as directly-outputted sawtooth wave in a conventional scheme. After bias modulation is overlapped, the closed loop feedback control of the fiber-optic gyroscope is achieved.

Owner:WEIWEI TECH (BEIJING) CO LTD

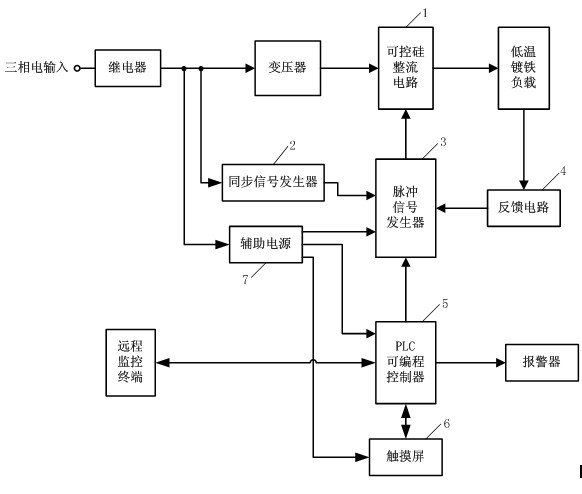

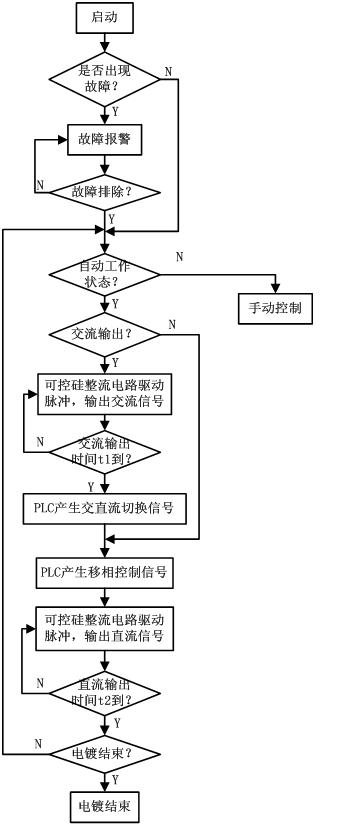

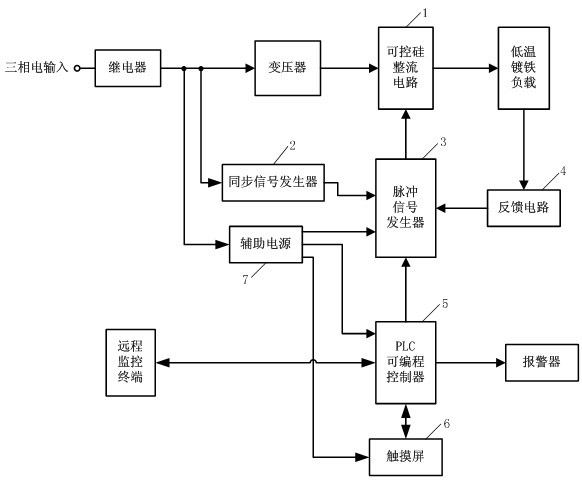

Intelligent power supply device for low-temperature etching-free iron plating process and power supply method thereof

InactiveCN102185498AAC and DC amplitude adjustmentStrong reliabilityAc-dc conversionSilicon-controlled rectifierEtching

Owner:HUANGSHAN JINYI POWER SUPPLY

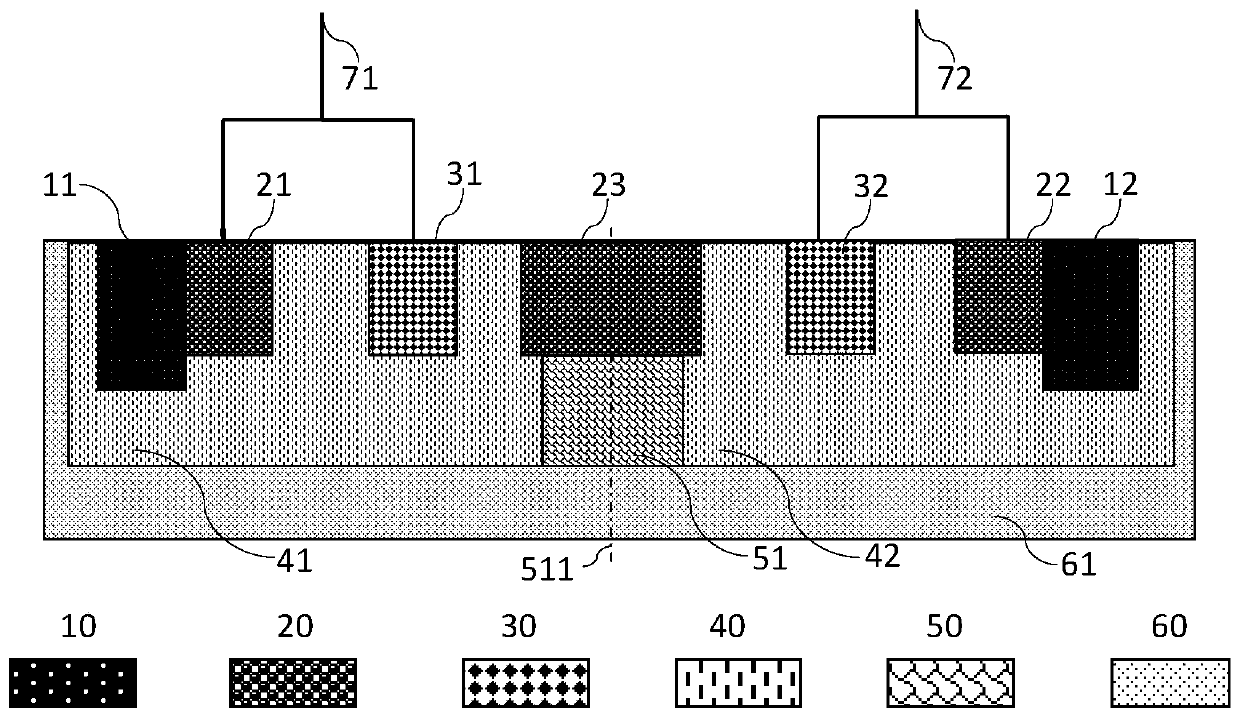

Silicon-controlled rectifier and manufacturing method

PendingCN110867487AWill not cause a conduction conditionApplicable anti-static protection functionSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationHemt circuits

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Voltage clamping circuits using mos transistors and semiconductor chips and methods of clamping voltages

A clamping circuit is provided, which may clamp a voltage at a node of a circuit to a stable level by using a transistor already included in the circuit. The clamping circuit may clamp a voltage at a first node of a circuit inside a semiconductor chip to a more stable level when electro-static discharge (ESD) occurs. The clamping circuit may include a transistor and a capacitive element to store a control voltage to turn on the transistor in response to ESD.

Owner:SAMSUNG ELECTRONICS CO LTD

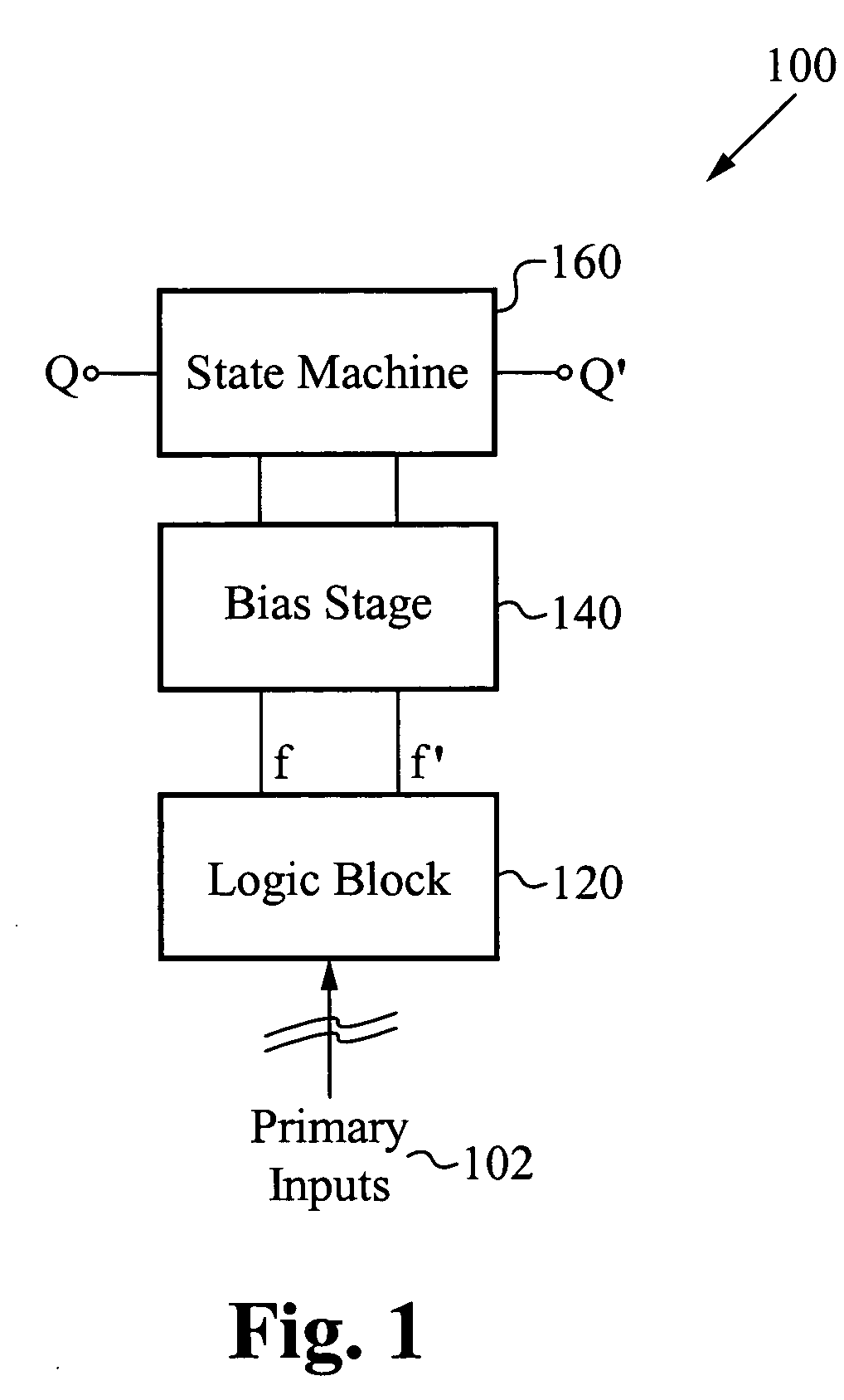

System and method for optimizing integrated circuit design

ActiveCN113361219AConfiguration CADElectric pulse generatorComputer architectureSoftware engineering

Embodiments of the present invention provide a system and method for optimizing an integrated circuit design, including a standard cell having a plurality of input and output memory elements (such as flip-flops, latches, etc.) with some combinatorial logic interconnected between these elements. In an embodiment, slave latches on an input flip-flop are replaced by a smaller number of latches at a downstream node of combinatorial logic, thereby improving performance, area, and power while maintaining functionality at interface pins of the standard cell. Also described is a process of inferring such a standard cell, or a process of remapping an equivalent sub-circuit from a netlist to the standard cell, from a behavioral description of the design, such as an RTL. The embodiment of the invention also provides a computer readable medium for encoding with a cell library.

Owner:TAIWAN SEMICON MFG CO LTD

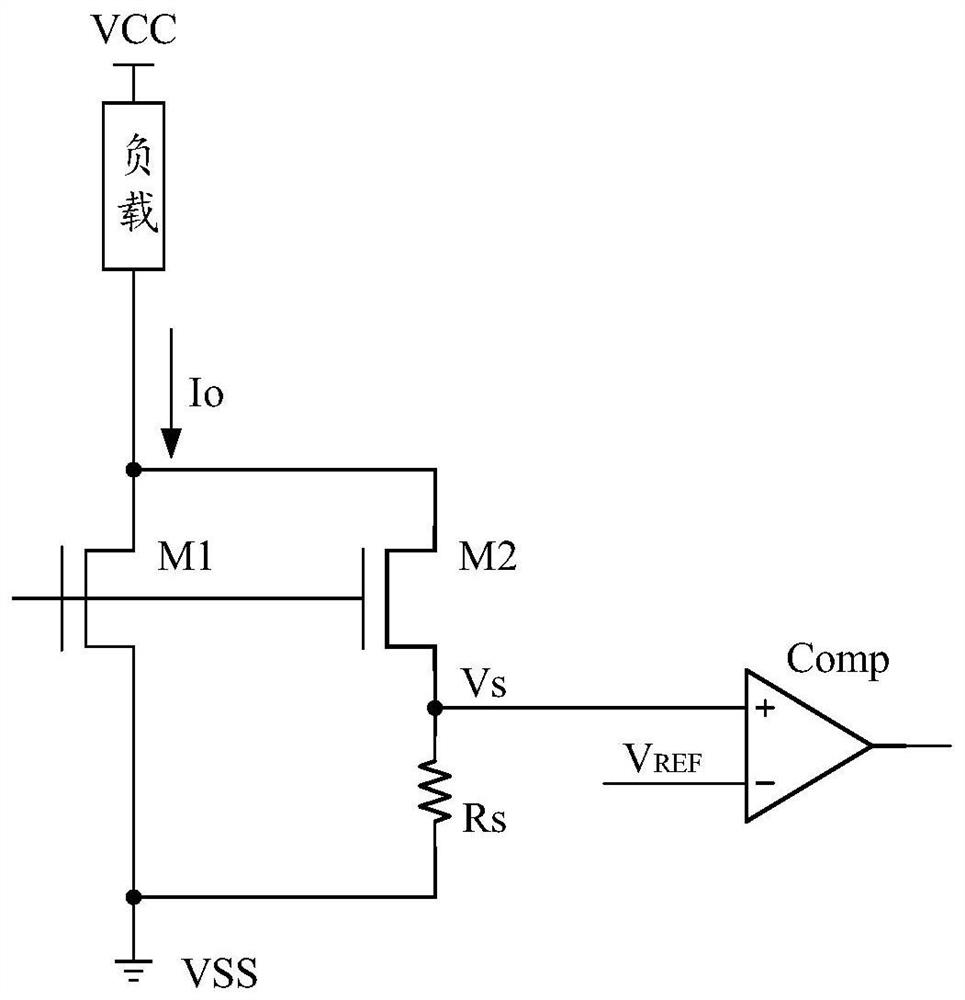

Over-current detection and protection circuit for power MOS tube, and power MOS tube assembly

PendingCN112701663AEmergency protection detectionArrangements responsive to excess currentCurrent thresholdHemt circuits

Owner:SHANGHAI EASTSOFT MICROELECTRONICS

Semiconductor memory and operation method for same

InactiveUS20060285405A1Reduce pre-charge timeShorten access cycle timeDigital storageBit lineHemt circuits

Owner:SOCIONEXT INC

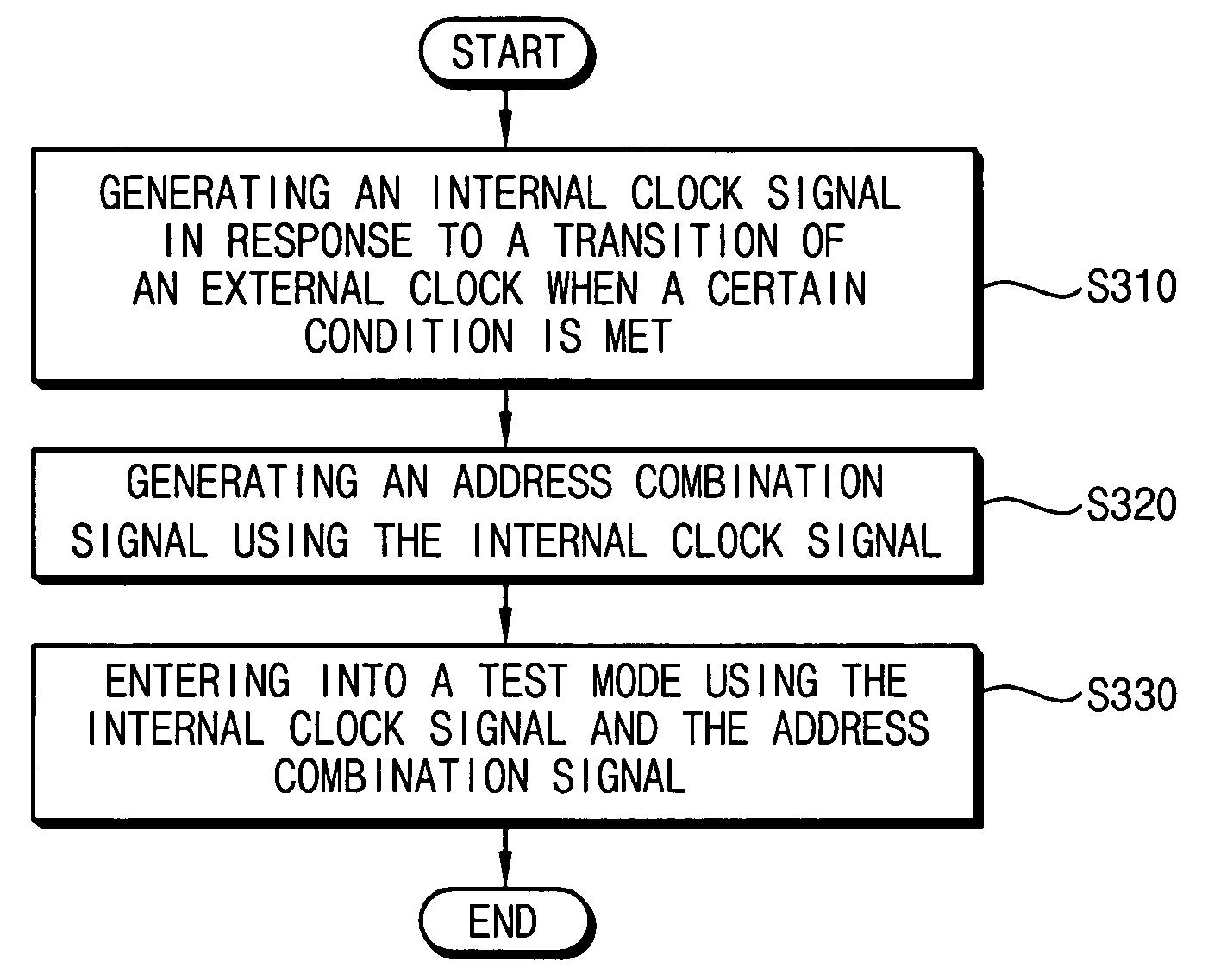

Circuit and method for test mode entry of a semiconductor memory device

Owner:SAMSUNG ELECTRONICS CO LTD

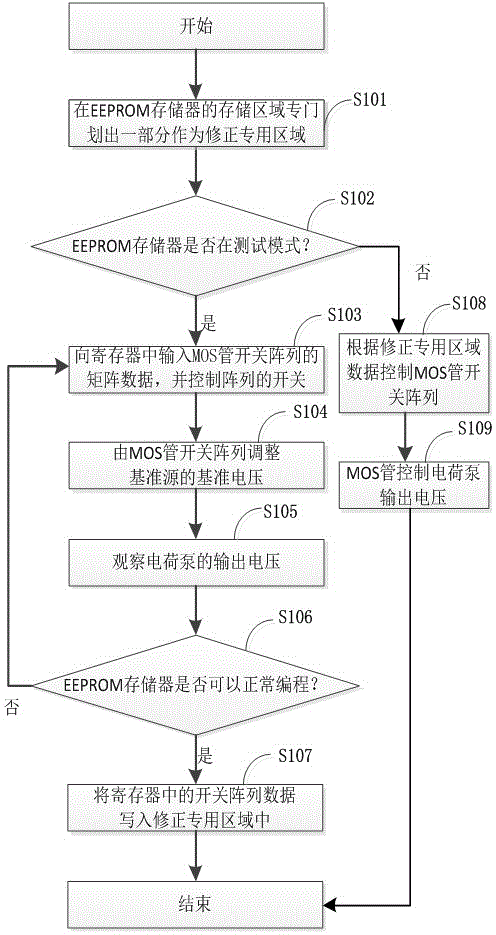

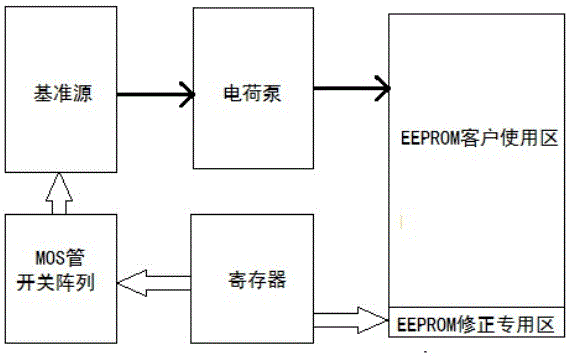

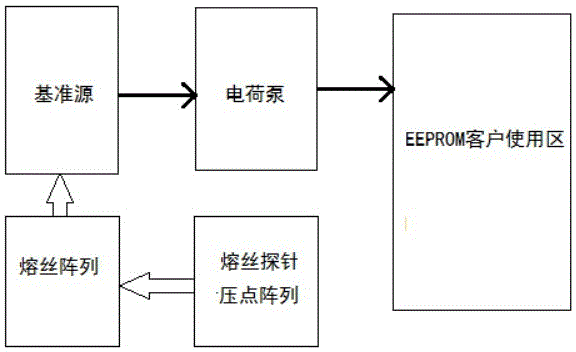

Booster circuit and method for improving programming accuracy of EEPROM

Owner:深圳市航顺芯片技术研发有限公司

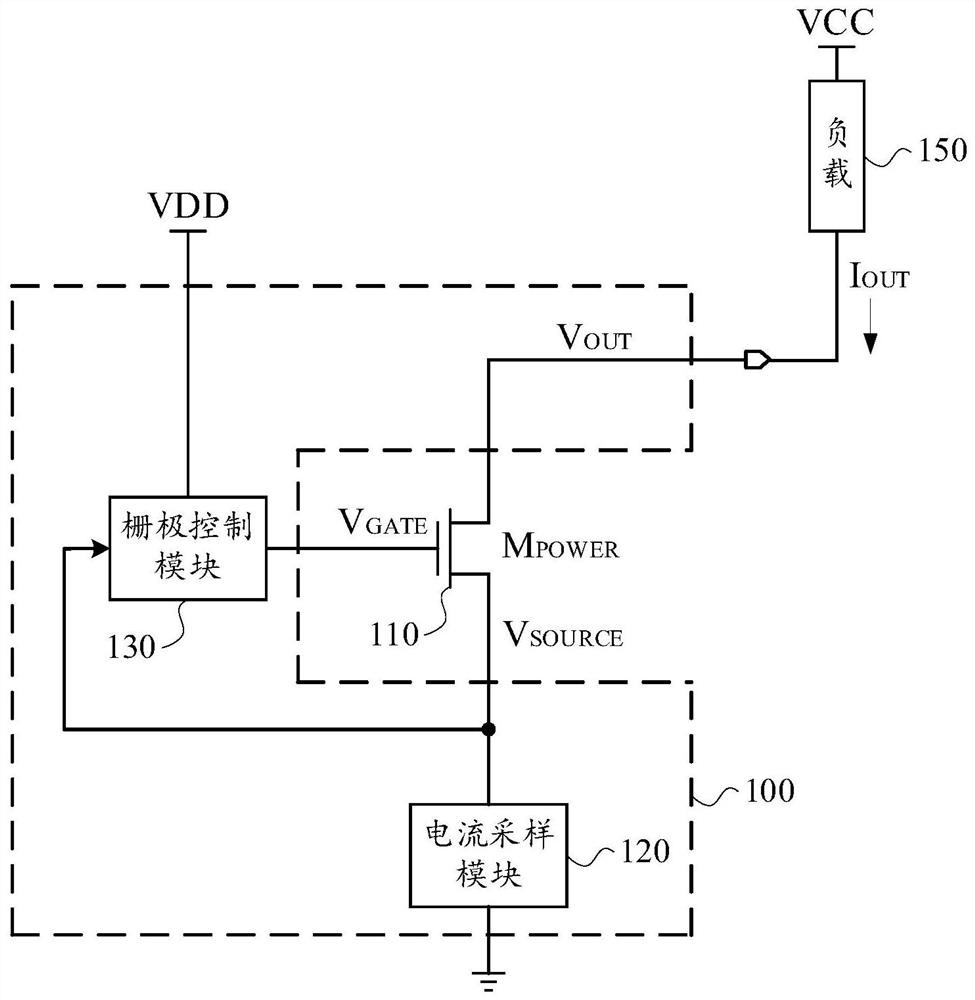

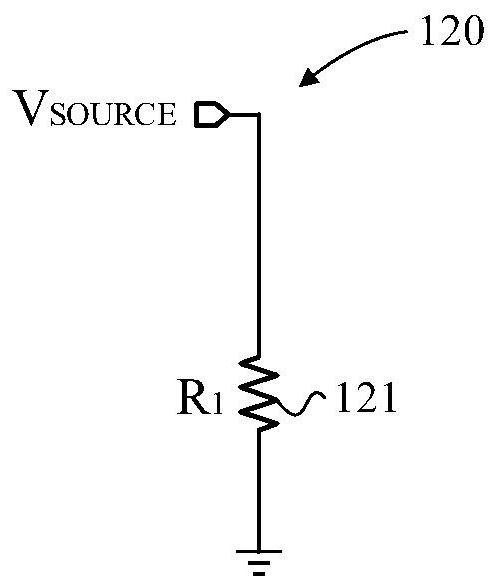

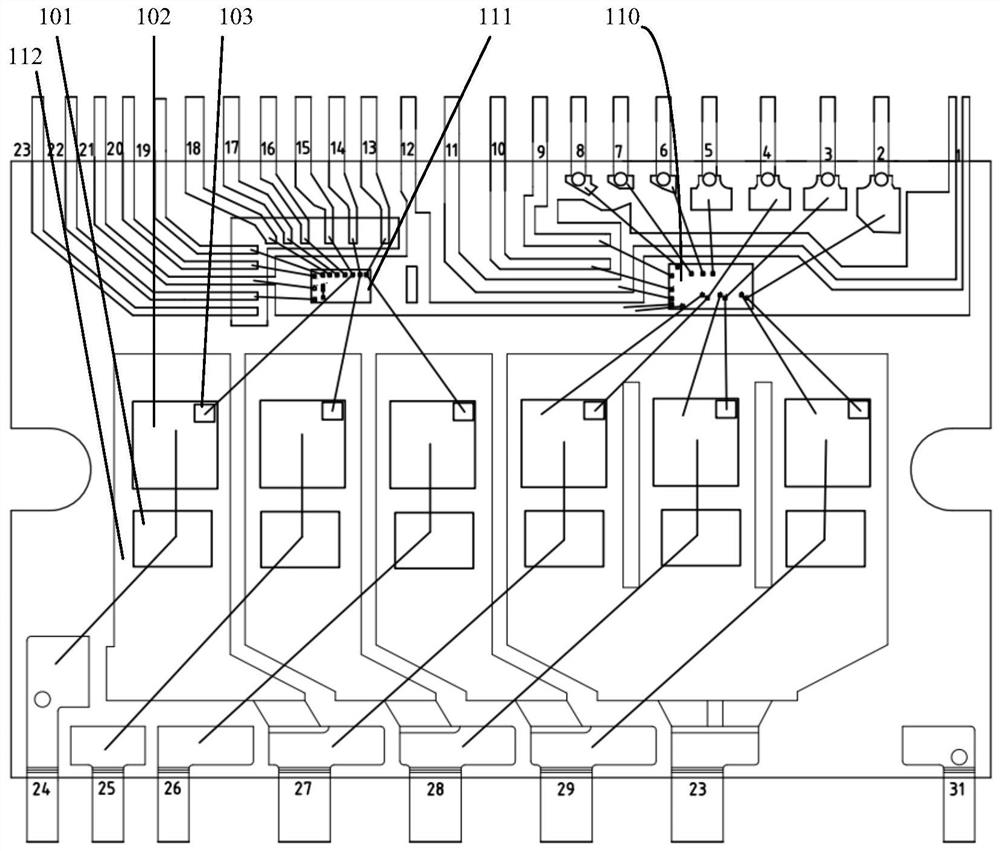

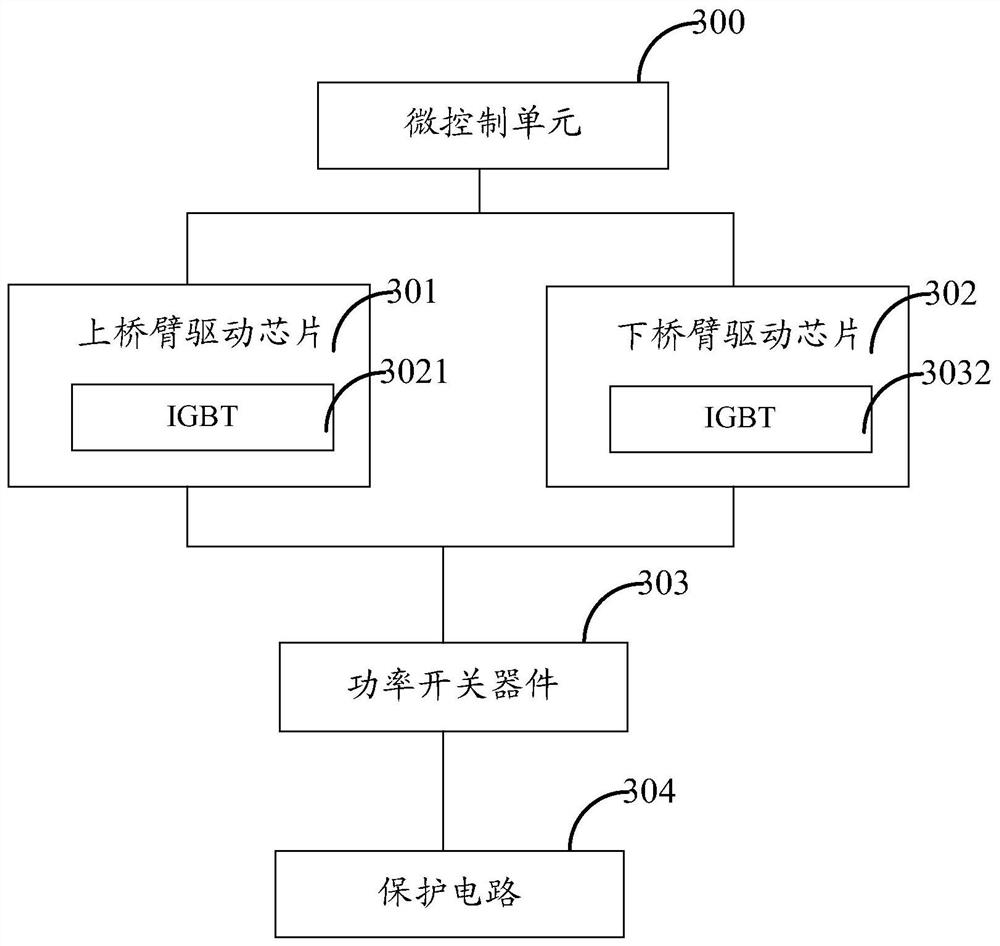

Power switch circuit system

InactiveCN112564461AMinimize problems such as failureIncrease usagePower conversion systemsControl engineeringHemt circuits

Owner:GREE ELECTRIC APPLIANCES INC

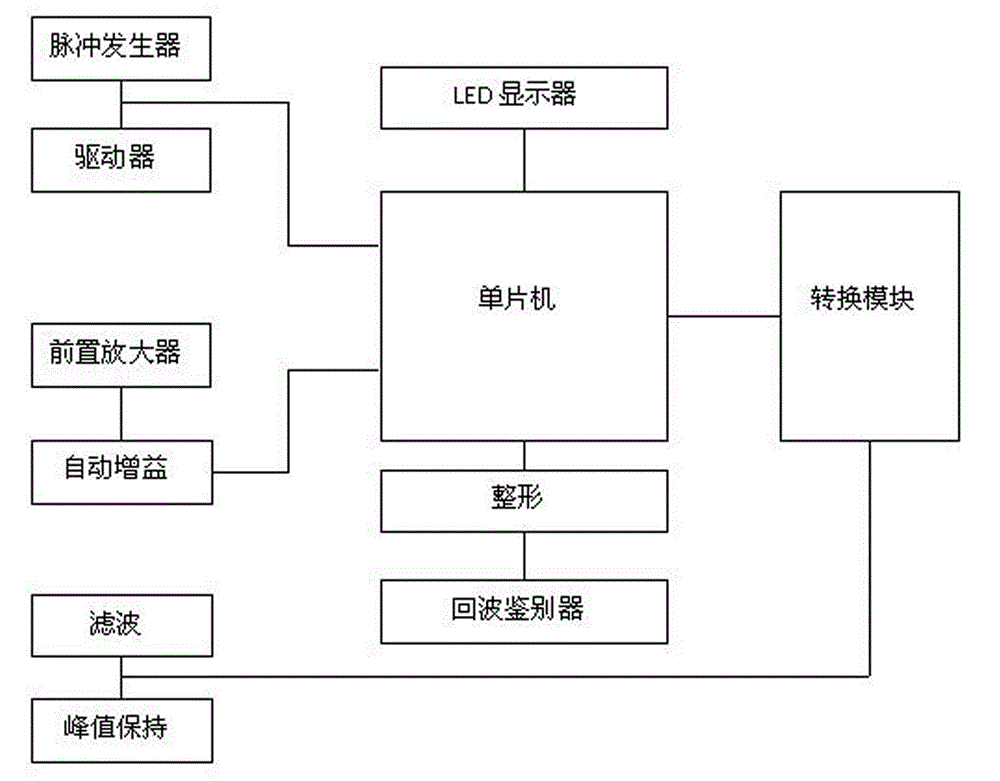

Ultrasonic ranging system based on single-chip microcomputer

InactiveCN104459700ADirectionalReduce consumptionAcoustic wave reradiationDisplay deviceHemt circuits

Owner:刘铮

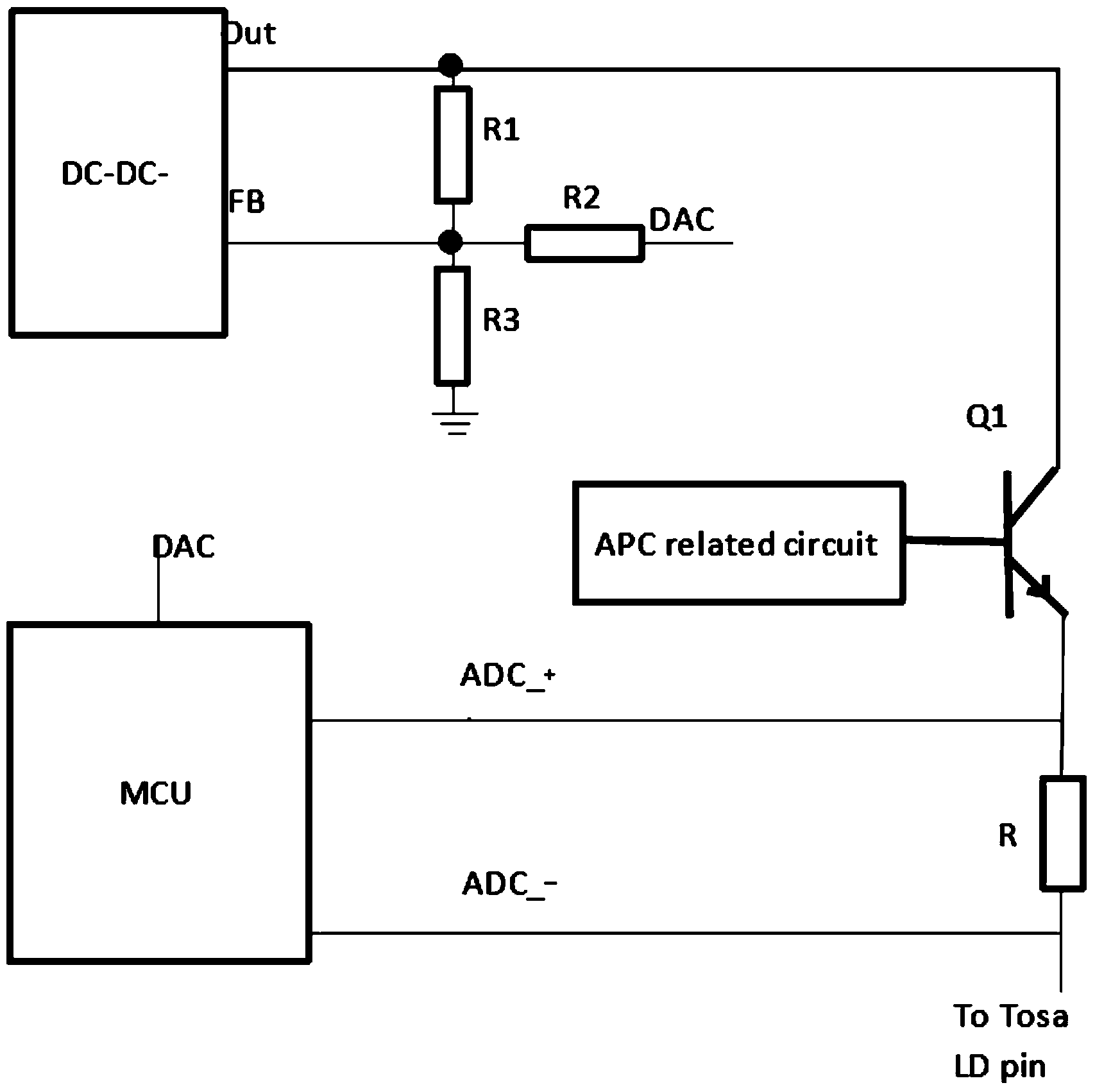

Circuit and method for reducing power consumption of TOSA

ActiveCN103762498AReduce power consumptionStable jobLaser detailsSemiconductor lasersMicrocontrollerHemt circuits

Owner:SOURCE PHOTONICS CHENGDU

Self-induction-type liquid crystal display stripping structure

InactiveCN103513461AImprove yieldEasy to operateLamination ancillary operationsLaminationLiquid-crystal displayHemt circuits

Owner:苏州工业园区赫光科技有限公司

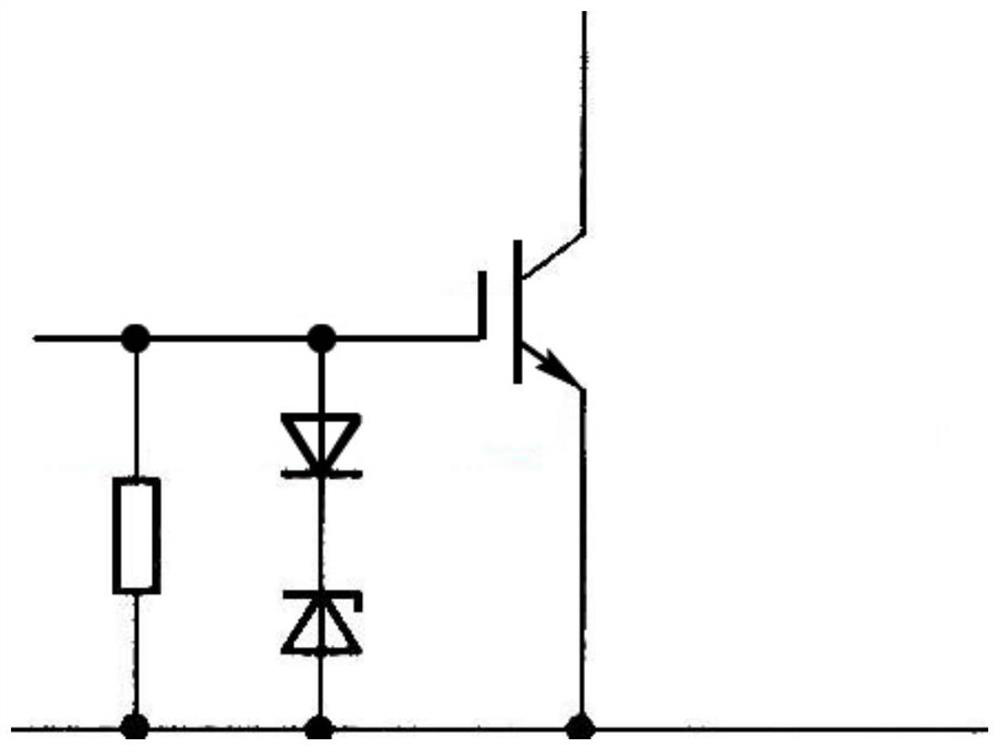

Power device drive circuit with detection function

The invention discloses a power device drive circuit with detection function. An overcurrent detection circuit comprises a diode D1, a voltage-regulator tube Z1, a triode T1 and a photoelectric coupler IC2, wherein the cathode and the anode of the voltage-regulator tube Z1 are respectively connected with the anode of the diode D1 and the base of the triode T1; and the collector of a secondary phototriode of the photoelectric coupler IC2 forms output signals SC of the overcurrent detection circuit. A drive signal feedback circuit comprises a diode D2, a voltage-regulator tube Z2, a triode T3 and a photoelectric coupler IC3, wherein the collector of a secondary phototriode of the photoelectric coupler IC3 forms output signals FS of the drive signal feedback circuit. According to the invention, the circuit can judge whether power devices have overcurrent or are abnormally conducted or cut off and timely protects the power devices so that the power devices are prevented from being damaged because of wrong conduction and wrong cutoff. The circuit has the characteristics of low cost, simplicity, reliability and strong anti-jamming capability, has strong adaptability and generalization, and can be used as an optimal circuit for driving high-power power electronic devices at present.

Owner:XINFENGGUANG ELECTRONICS TECH CO LTD

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap