Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

46 results about "Computer architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer engineering, computer architecture is a set of rules and methods that describe the functionality, organization, and implementation of computer systems. Some definitions of architecture define it as describing the capabilities and programming model of a computer but not a particular implementation. In other definitions computer architecture involves instruction set architecture design, microarchitecture design, logic design, and implementation.

Systems and methods for interconnection of multiple FPGA devices

InactiveUS20050256969A1Simple designEnhance intercommunicationDigital computer detailsLogic circuits using elementary logic circuit componentsComputer architectureTransceiver

Application Specific Integrated Circuit (“ASIC”) devices, such as Field Programmable Gate Arrays (“FPGAs”), may be interconnected using serial I / O connections, such as high speed multi-gigabit serial transceiver (“MGT”) connections. For example, serial I / O connections may be employed to interconnect a pair of ASICs to create a high bandwidth, low signal count connection, and in a manner so that any given pair of multiple ASIC devices on a single circuit card may communicate with each other through no more than one serial data communication link connection step. A reconfigurable hardware architecture (“RHA”) may be configured to include a communications infrastructure that uses a high-bandwidth packet router to establish standard communications protocols between multiple interfaces and / or multiple devices that may be present on a single circuit card. Additionally, a communications infrastructure may be established across multiple circuit cards.

Owner:LIONRA TECH LTD +1

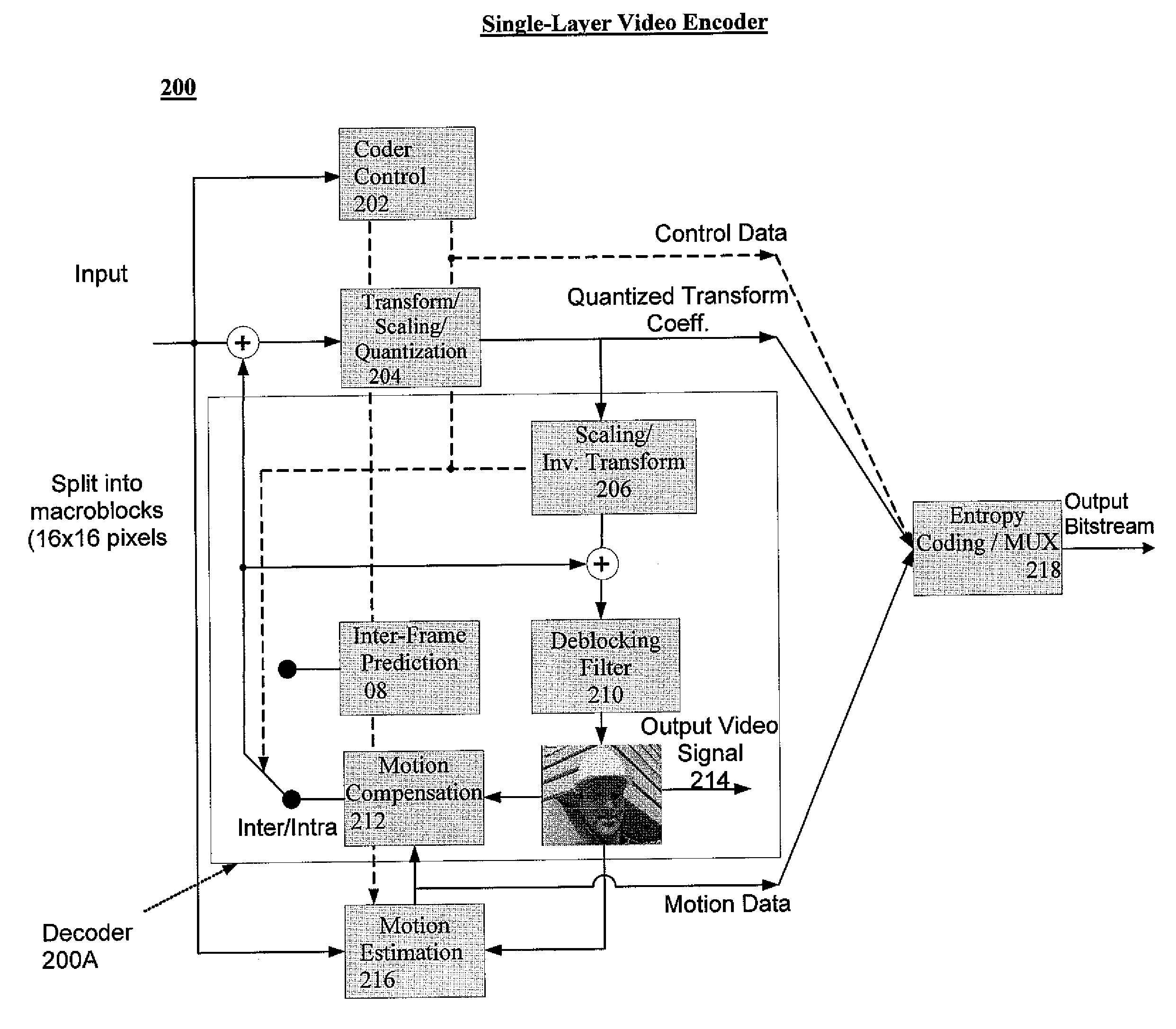

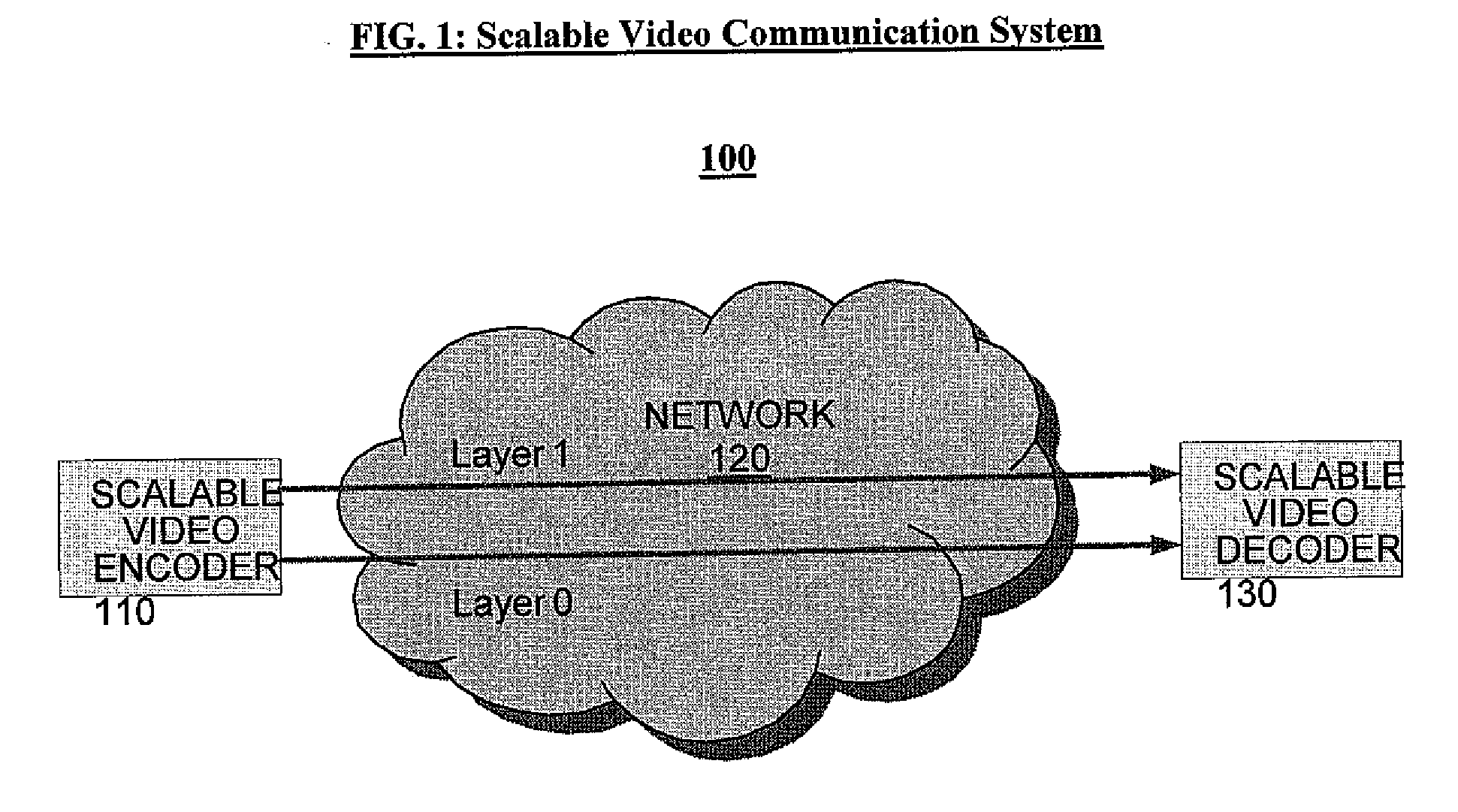

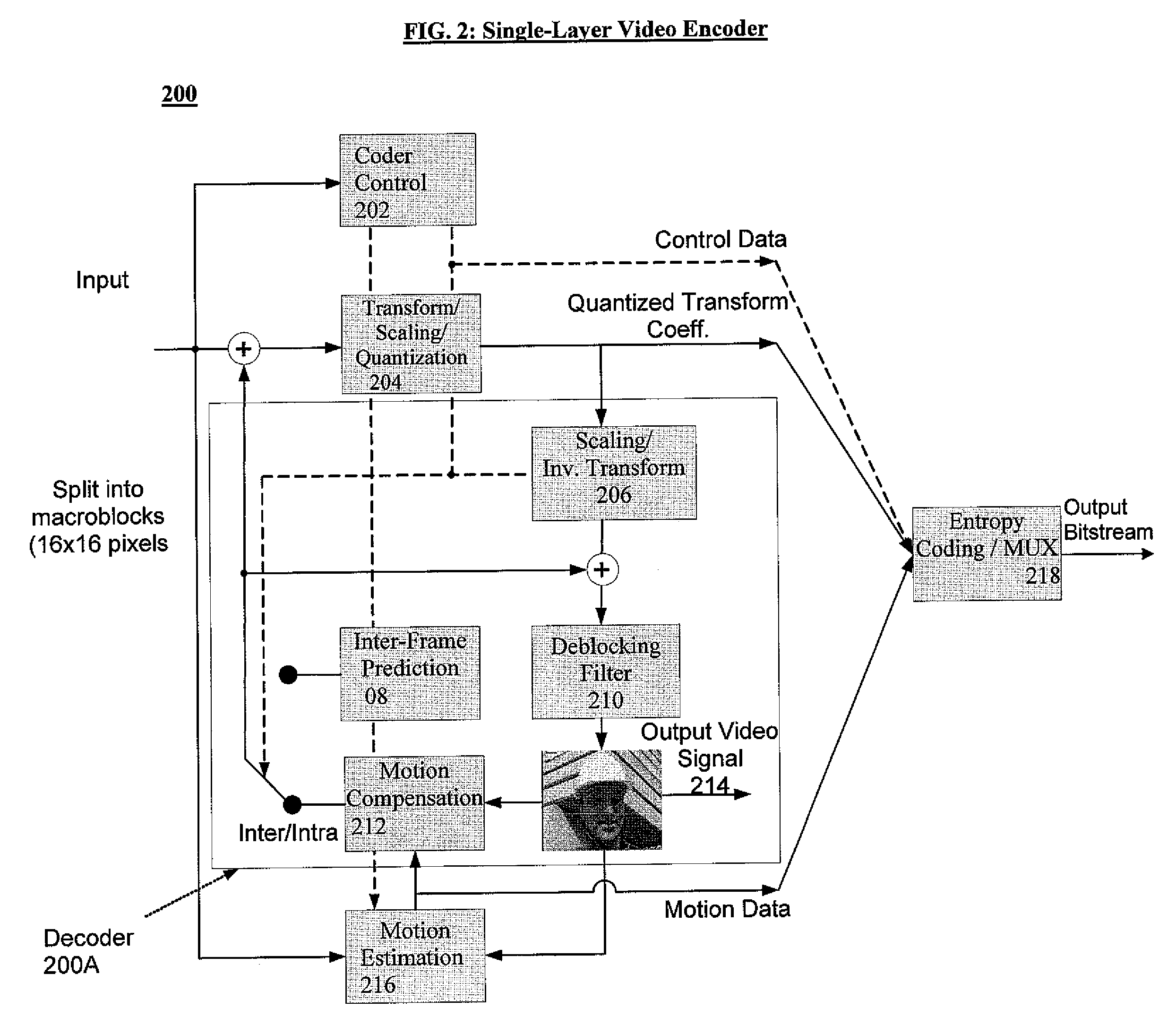

System and method for scalable video coding using telescopic mode flags

ActiveUS20100067581A1Easy to operateImprove coding efficiencyColor television with pulse code modulationColor television with bandwidth reductionComputer architectureInter layer

Owner:VIDYO

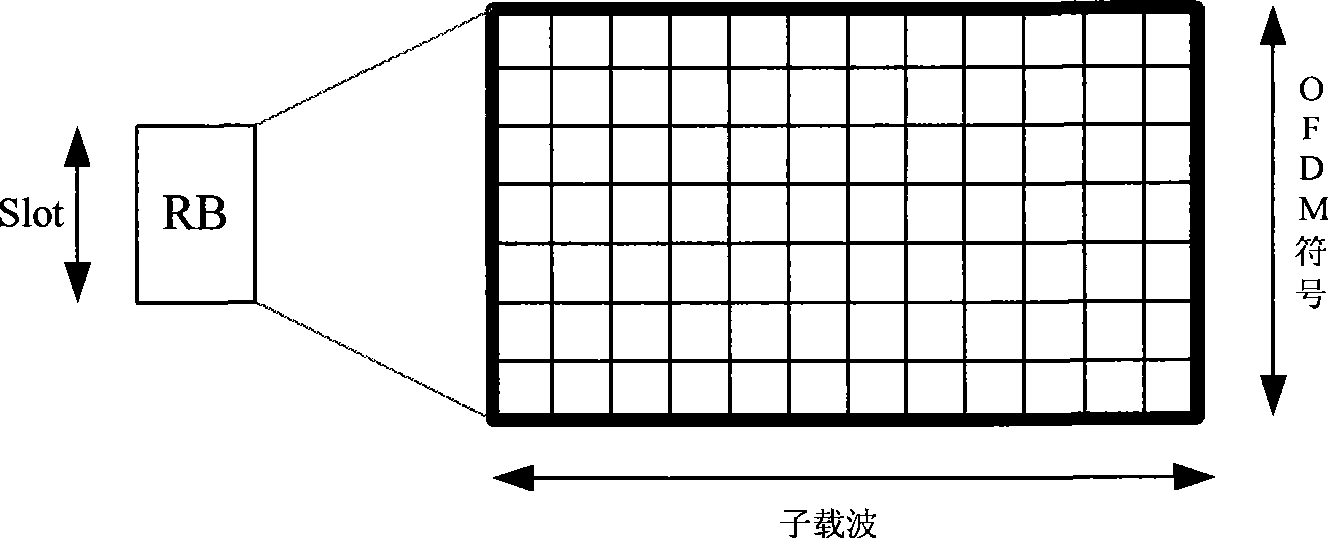

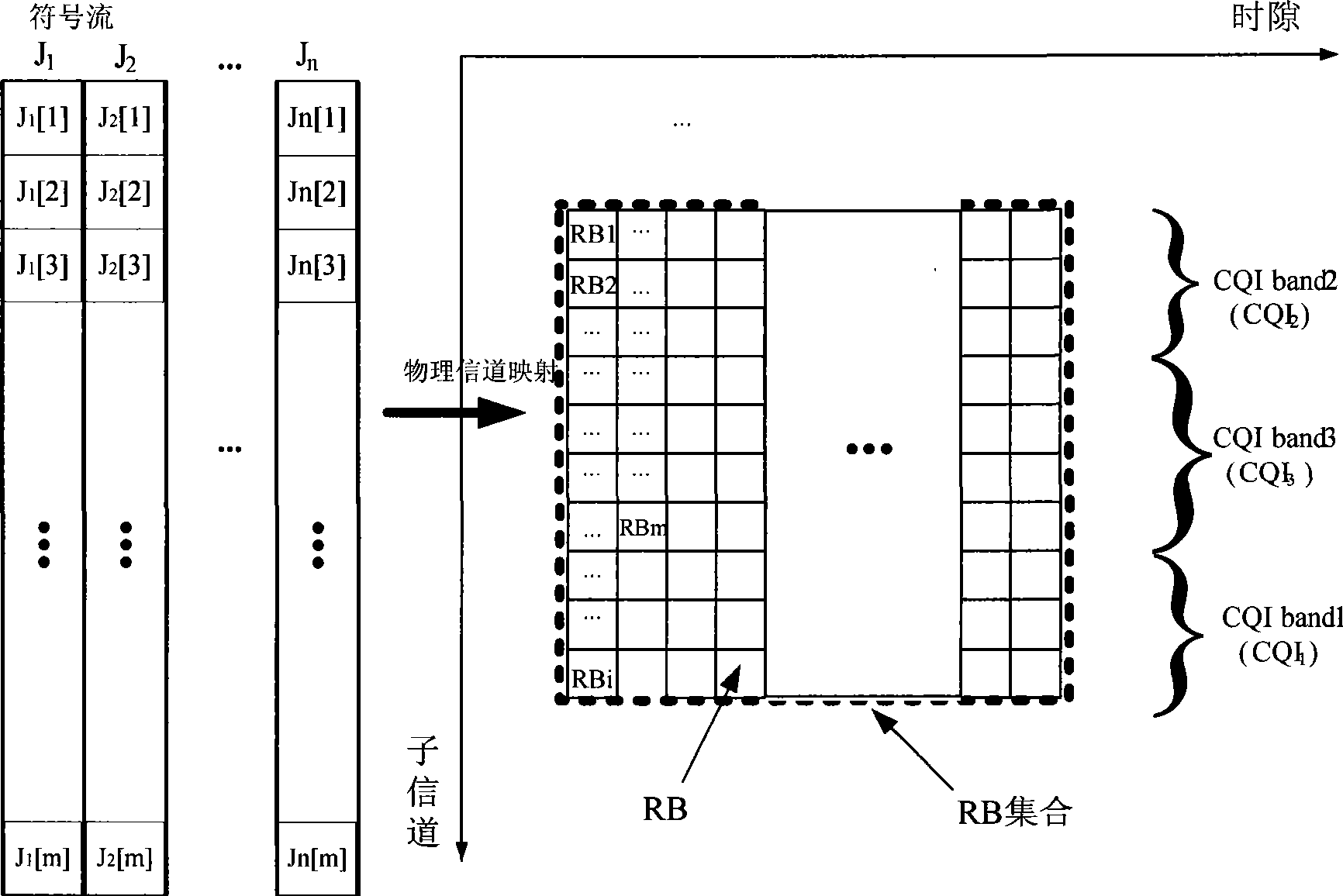

Physical channel mapping device and mapping method for OFDM system

InactiveCN101388743AImprove decoding accuracyReduce the number of retransmissionsError prevention/detection by using return channelMulti-frequency code systemsComputer architectureResource block

Owner:ZTE CORP

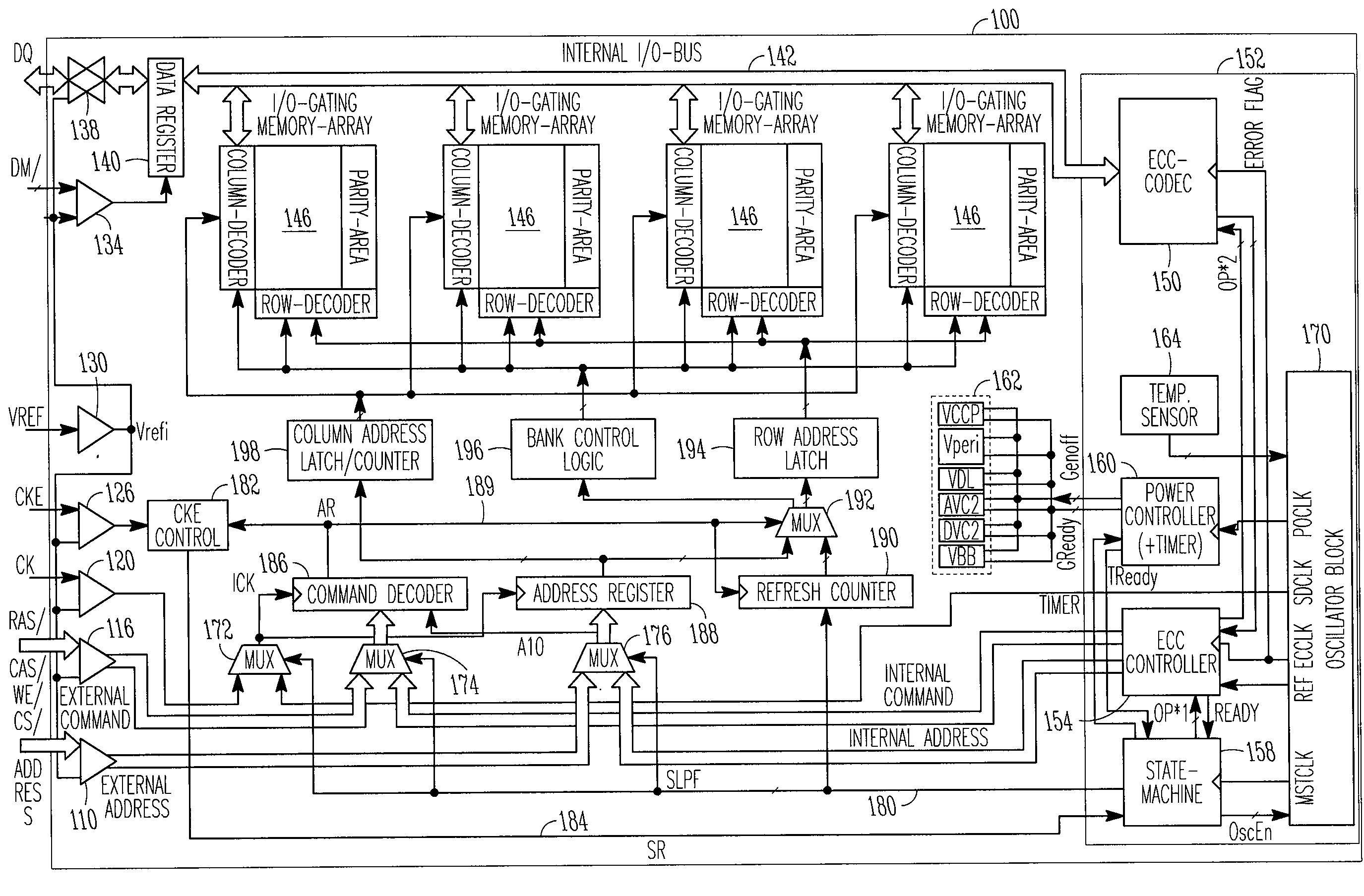

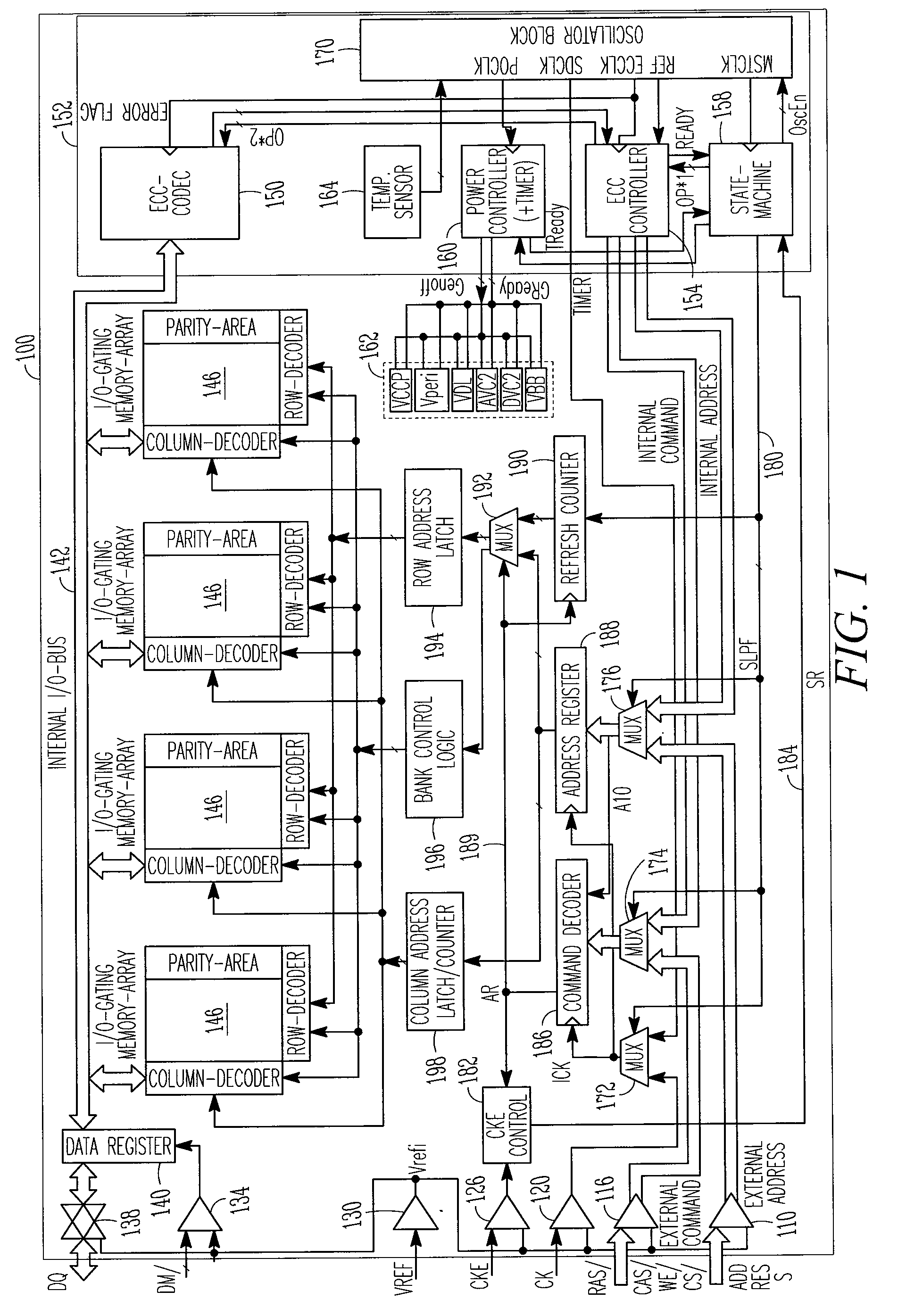

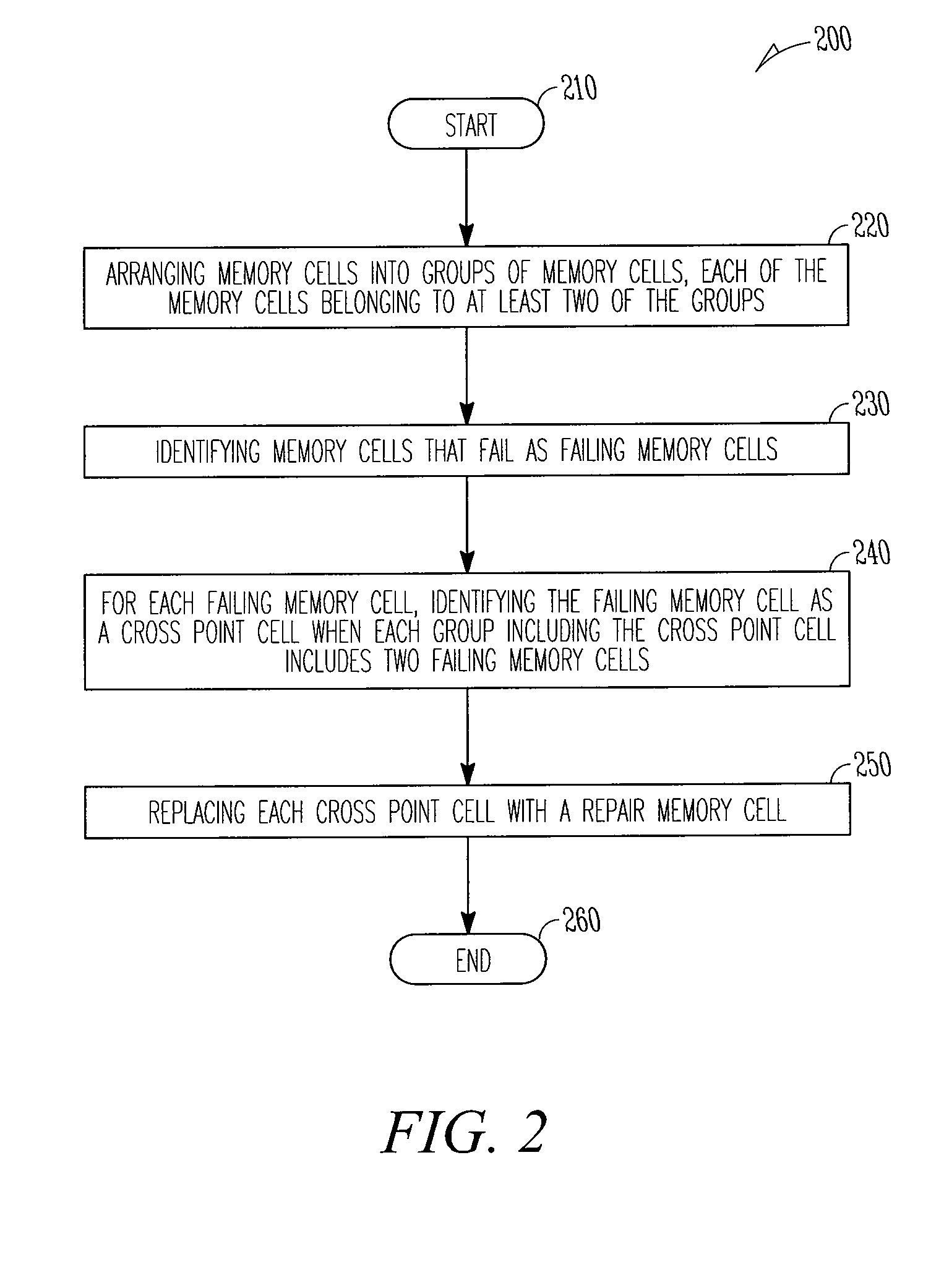

Memory device repair apparatus, systems, and methods

Owner:MICRON TECH INC

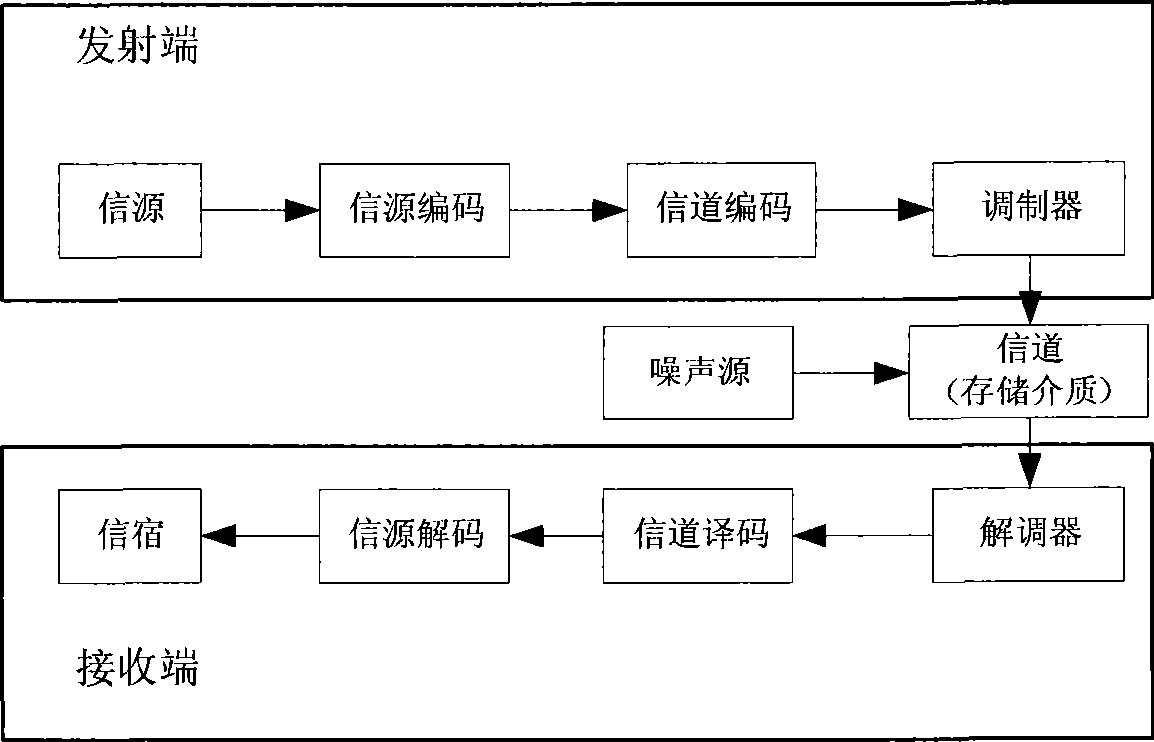

Method and device for coding uplink control information

ActiveCN103220083AImprove transmission performanceImprove transmission efficiencyForward error control useWireless communicationComputer architectureColumn vector

The embodiments of the invention provide a method and device for coding uplink control information. The method and the device are used for optimizing the transmission performance of the uplink control information. The method comprises the steps of: shifting column vectors of a predefined coding matrix M so as to create a new encoding matrix M'; and coding the uplink control information by using the new encoding matrix M'. The coding matrix which is adopted to code the uplink control information is not the fixed predefined coding matrix but the new encoding matrix which is created through shifting the column vectors of the predefined coding matrix. Compared with the method in the prior art that the same coding matrix is adopted to code the uplink control information regardless of the number of bits of the control information, the method provided by the embodiments of the invention has the advantages that corresponding coding matrixes can be determined according to the uplink control information, so that the transmission performance of the uplink control information can be optimized, and then, the efficiency of downlink transmission is increased.

Owner:HUAWEI TECH CO LTD

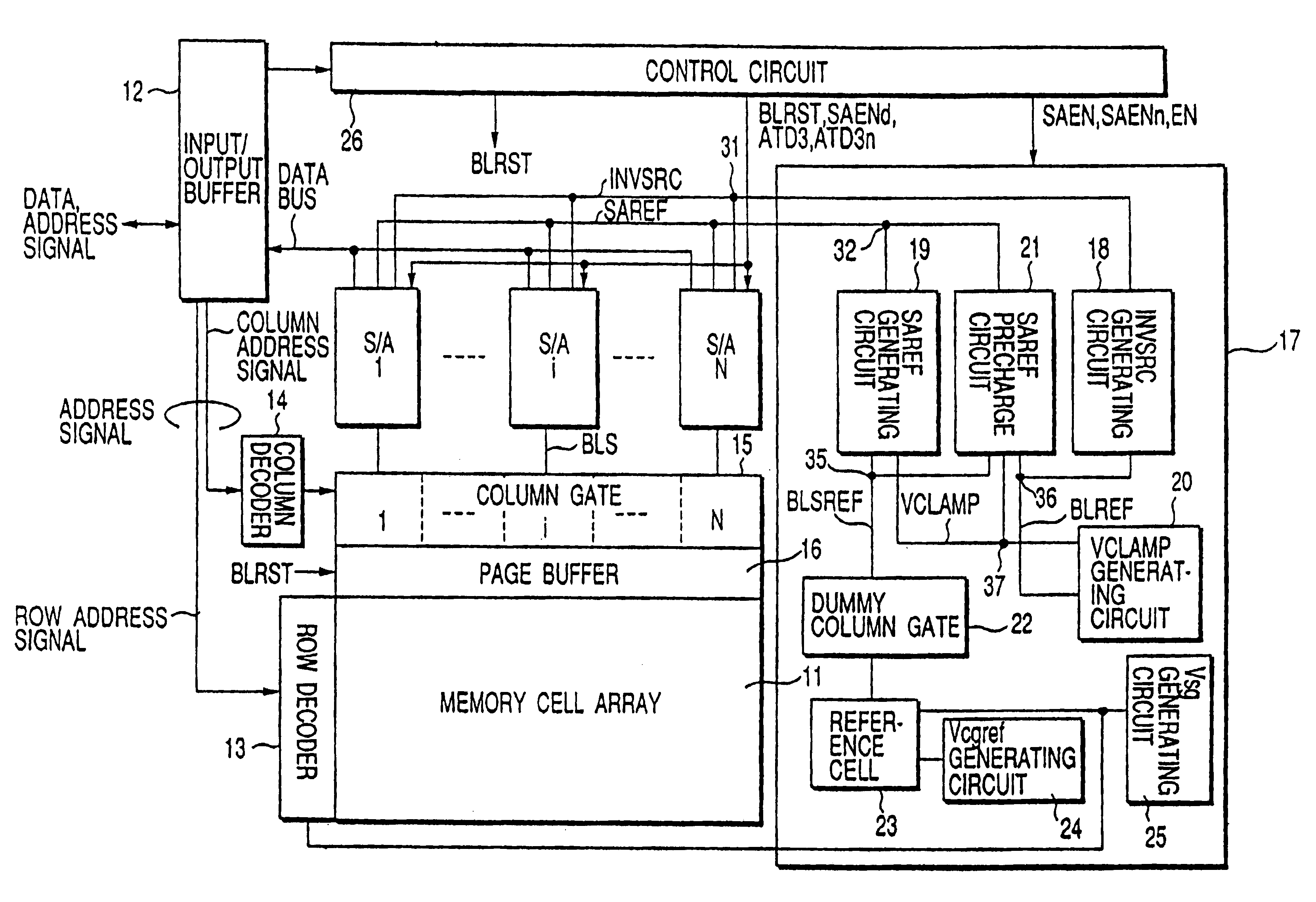

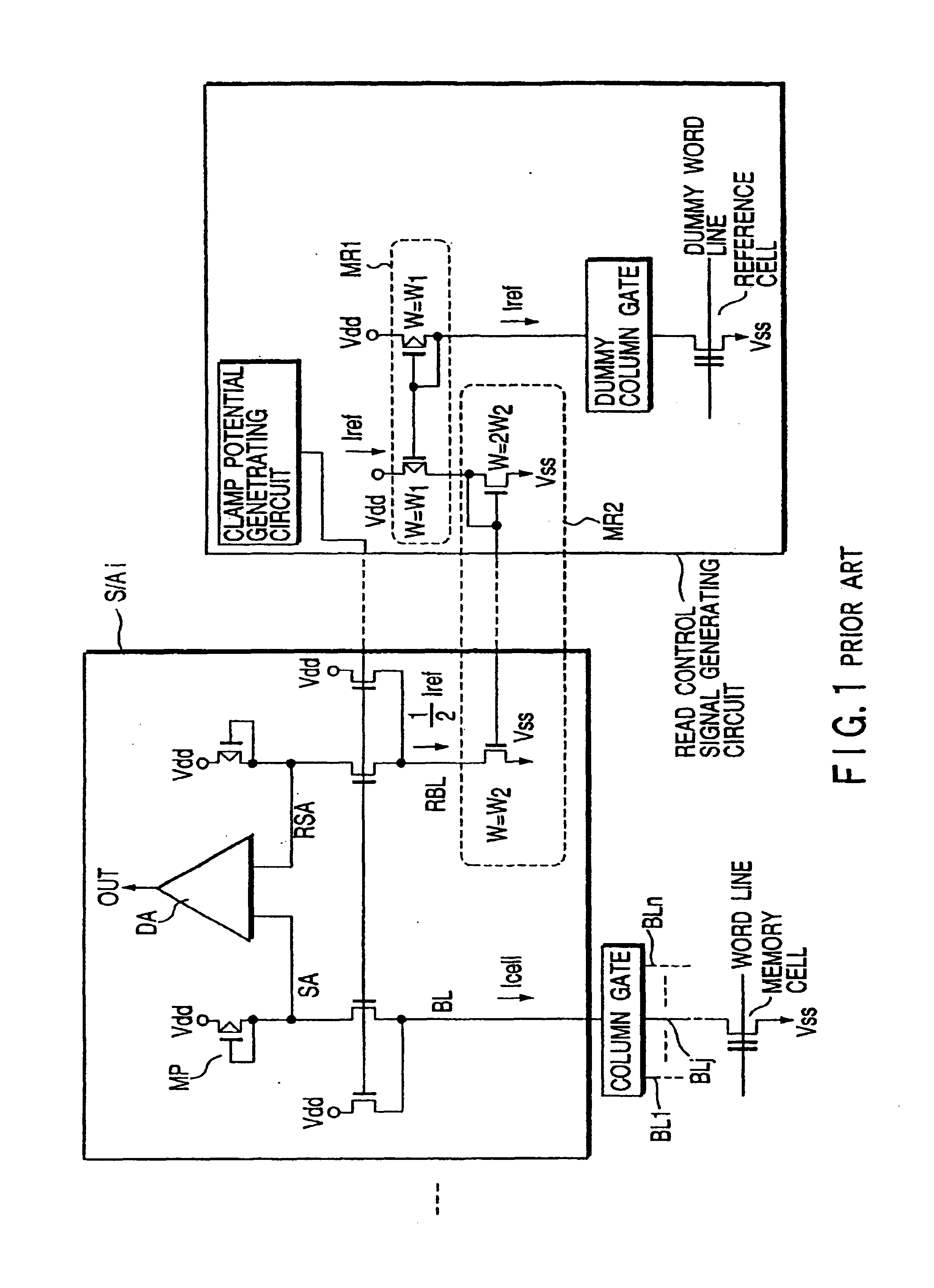

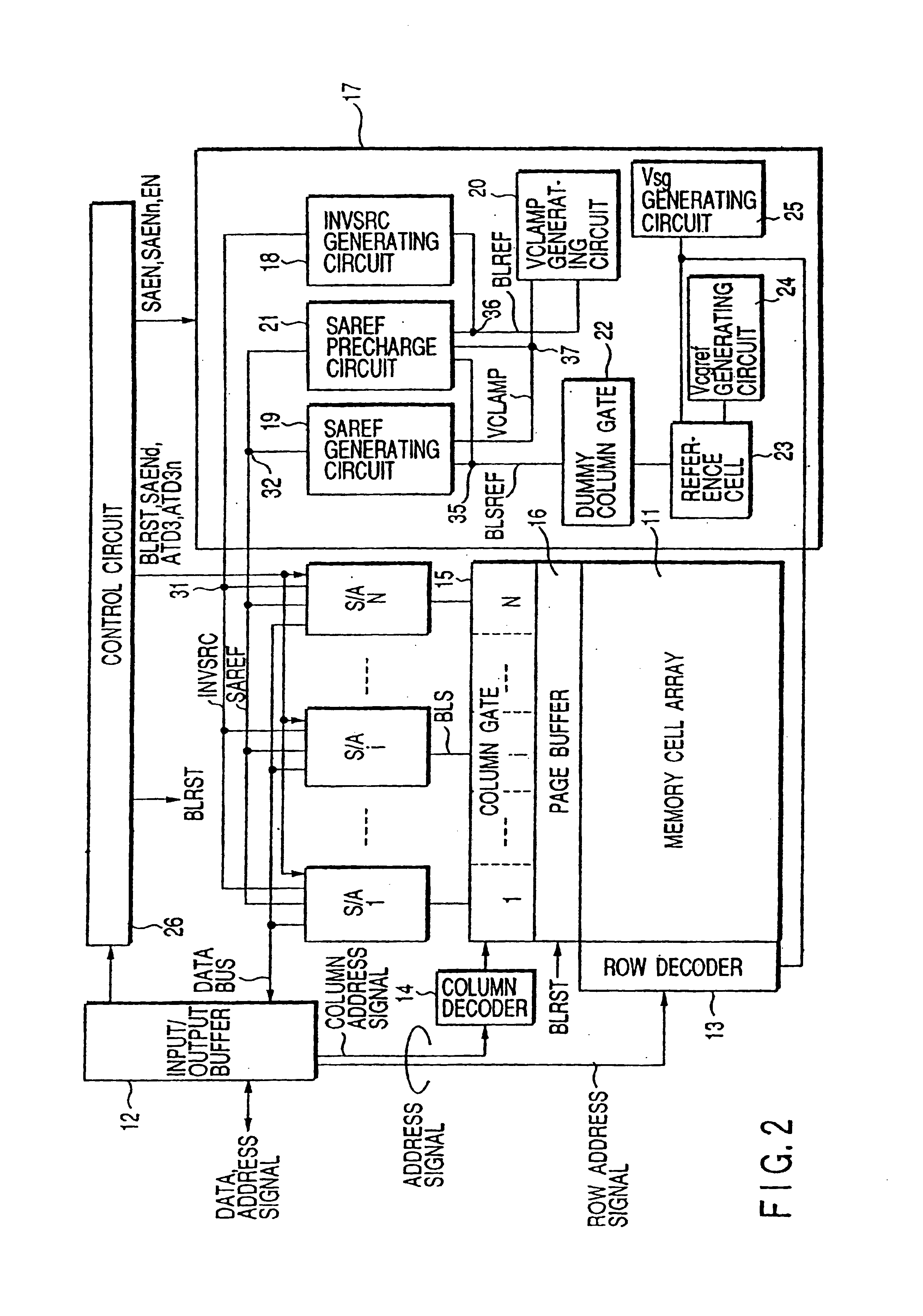

Read circuit of nonvolatile semiconductor memory

InactiveUS6845047B2Total current dropPerforming readRead-only memoriesDigital storageBit lineComputer architecture

Owner:KK TOSHIBA

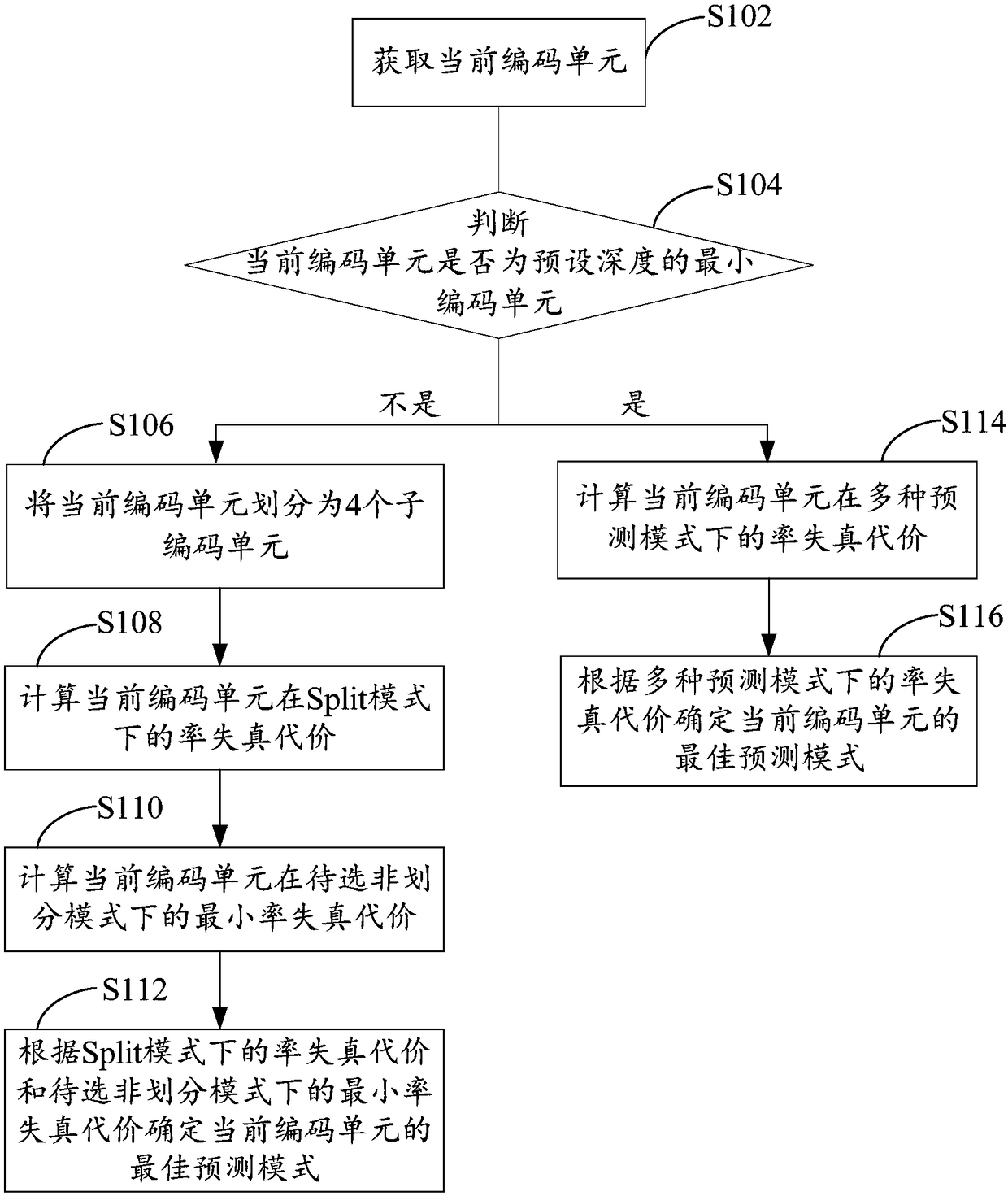

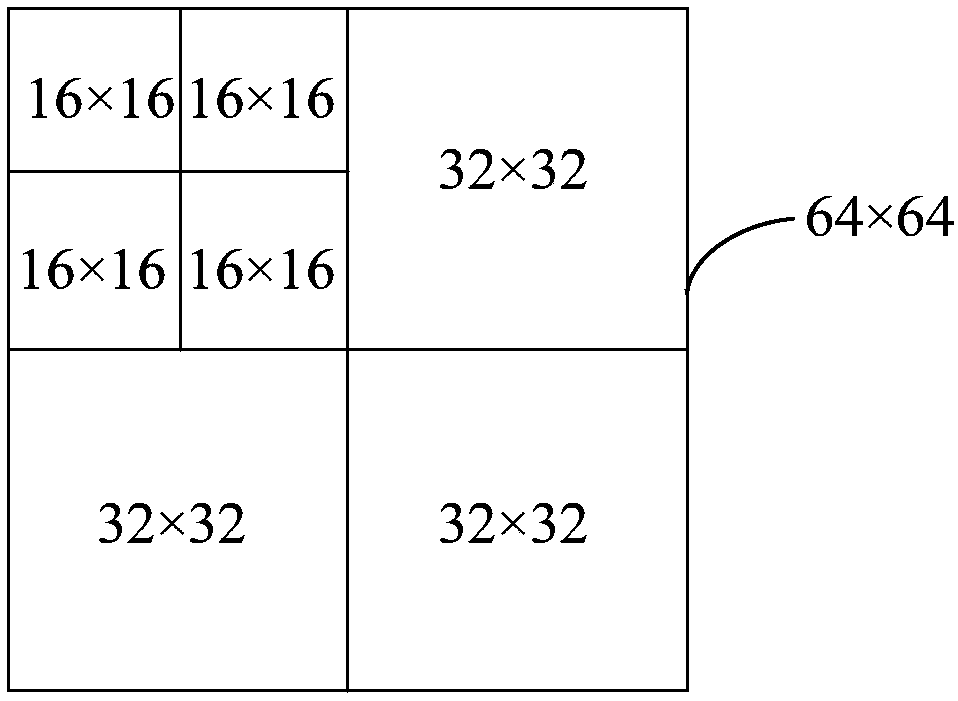

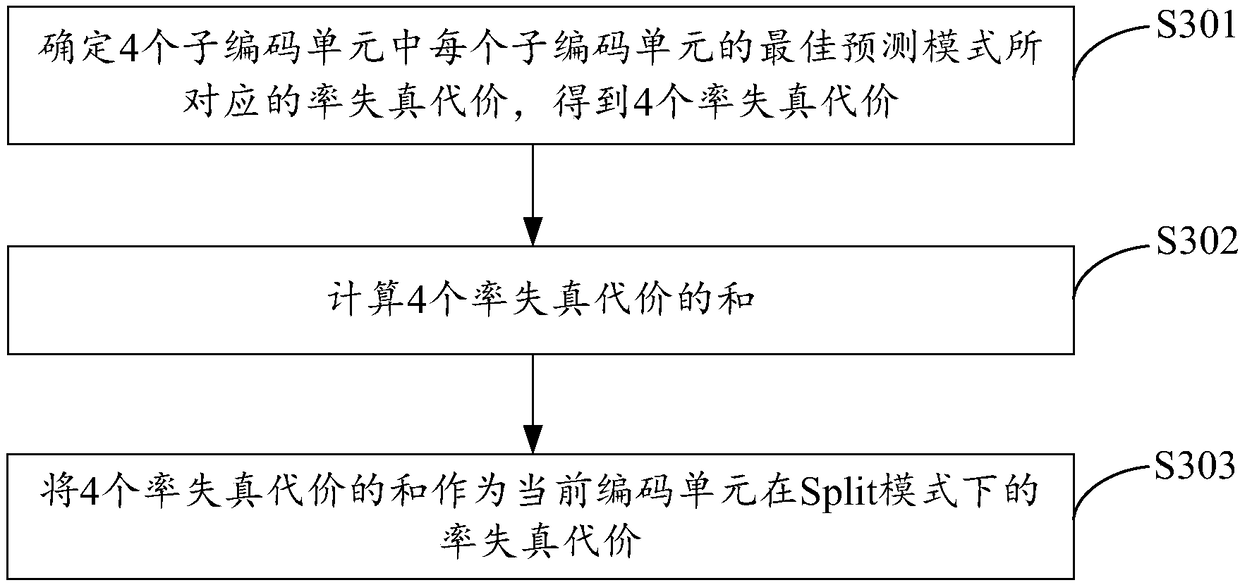

Fast selection method and device of inter-frame prediction mode, and electronic equipment

Owner:SUMAVISION TECH CO LTD

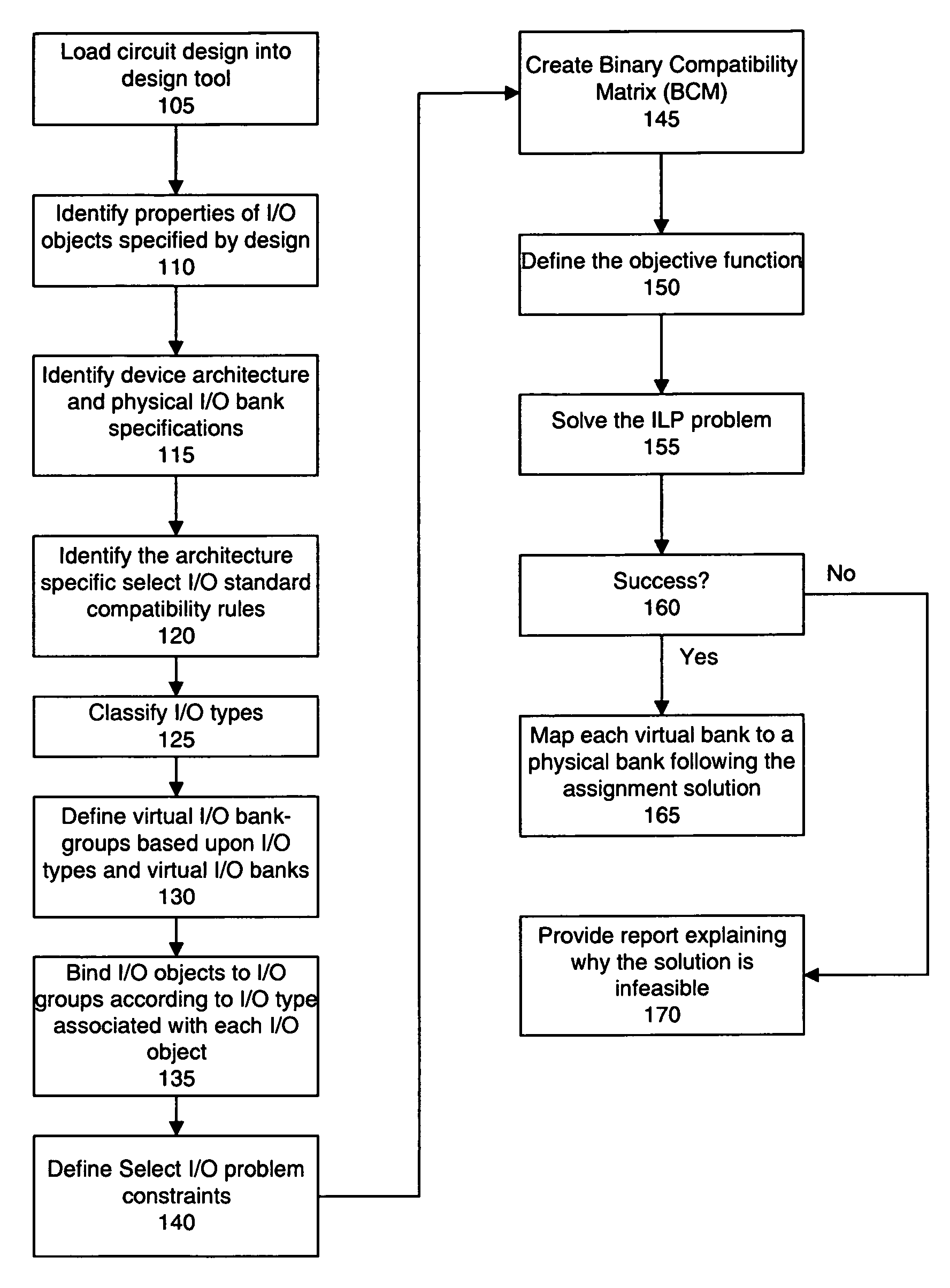

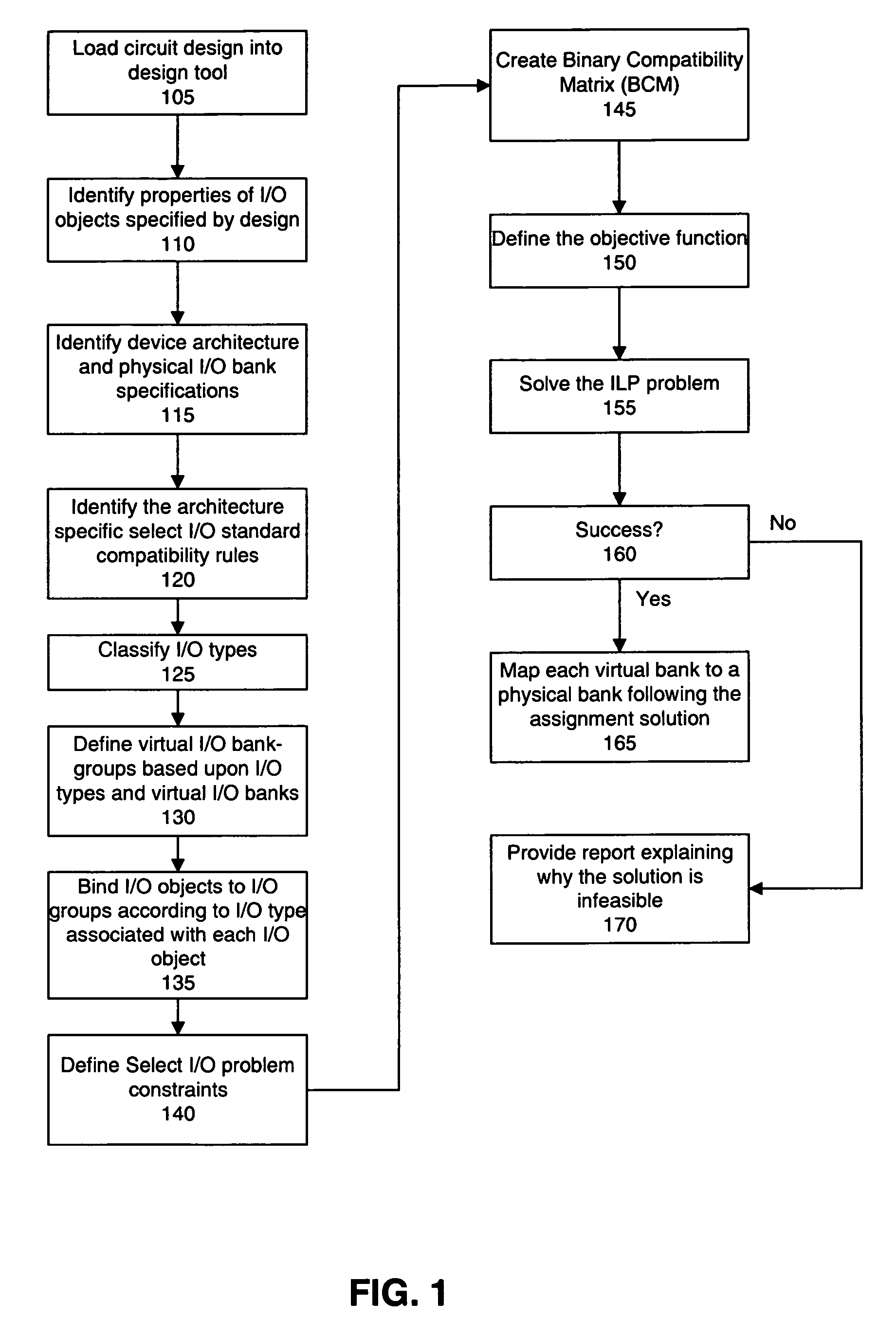

Assignment of I/O objects with multiple I/O standards to virtual I/O banks using integer linear programming

ActiveUS7299439B1Computer aided designSpecial data processing applicationsComputer architectureProgrammable logic device

Owner:XILINX INC

Video coding mode selection method and system based on SSIM evaluation

InactiveCN103634600AImprove performanceQuick fixDigital video signal modificationComputer architectureFrame based

The invention relates to a video coding mode selection method and system based on SSIM evaluation. The method includes the following steps: a step 101) establishing a rate distortion optimization model for each macro block to be coded to acquire lagrange cost values of various coding modes; a step 102) determining a lagrange factor of the frame level of a frame to which the current macro block to be coded belongs according to distortion values of the front two frames of the frame based on SSE evaluation and an average value of ratios between the distortion values based on SSIM evaluation, and then performing further zoom on the obtained lagrange factor of the frame level by utilizing the importance measurement of the macro block to be coded to acquire the lagrange factor of the macro block level of the macro block to be coded; and a step 103) calculating the lagrange cost values of the current coded macro block of various coding modes according to the acquired the lagrange factor of the current macro block to be coded, and finally selecting the coding mode having the minimum lagrange cost value as the coding mode of the current coded macro block for coding.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

AADL model construction method based on SysML module diagram

ActiveCN110502211AQuality improvementLow costSoftware designRequirement analysisComputer architectureConstruct state

The invention discloses an AADL model construction method based on a SysML module diagram. The AADL model construction method comprises the following steps of 1, performing module classification basedon the SysML module diagram; step 2, constructing an ADDL component type declaration based on the SysML module diagram; step 3, constructing an AADL component type based on the SysML module diagram to realize implementation; 4, constructing the state of the AADL assembly based on the SysML state machine diagram; and step 5, constructing state conversion of the AADL assembly based on the SysML state machine diagram. By means of the invention, a user can realize automatic construction of the AADL model based on the SysML module diagram; on the basis of maintaining the association relationship between an embedded system architecture model and a subsystem model, the non-functional attributes of the whole system model and the subsystem model are considered; modeling and verification of the embedded system architecture from the software level to the hardware level are completed, feasibility and correctness of a system architecture model can be verified in the early stage of software development, problems in the aspect of the system architecture are found as soon as possible, the cost of system development is reduced, and the high-reliability target of the whole system is achieved.

Owner:CHINESE AERONAUTICAL RADIO ELECTRONICS RES INST

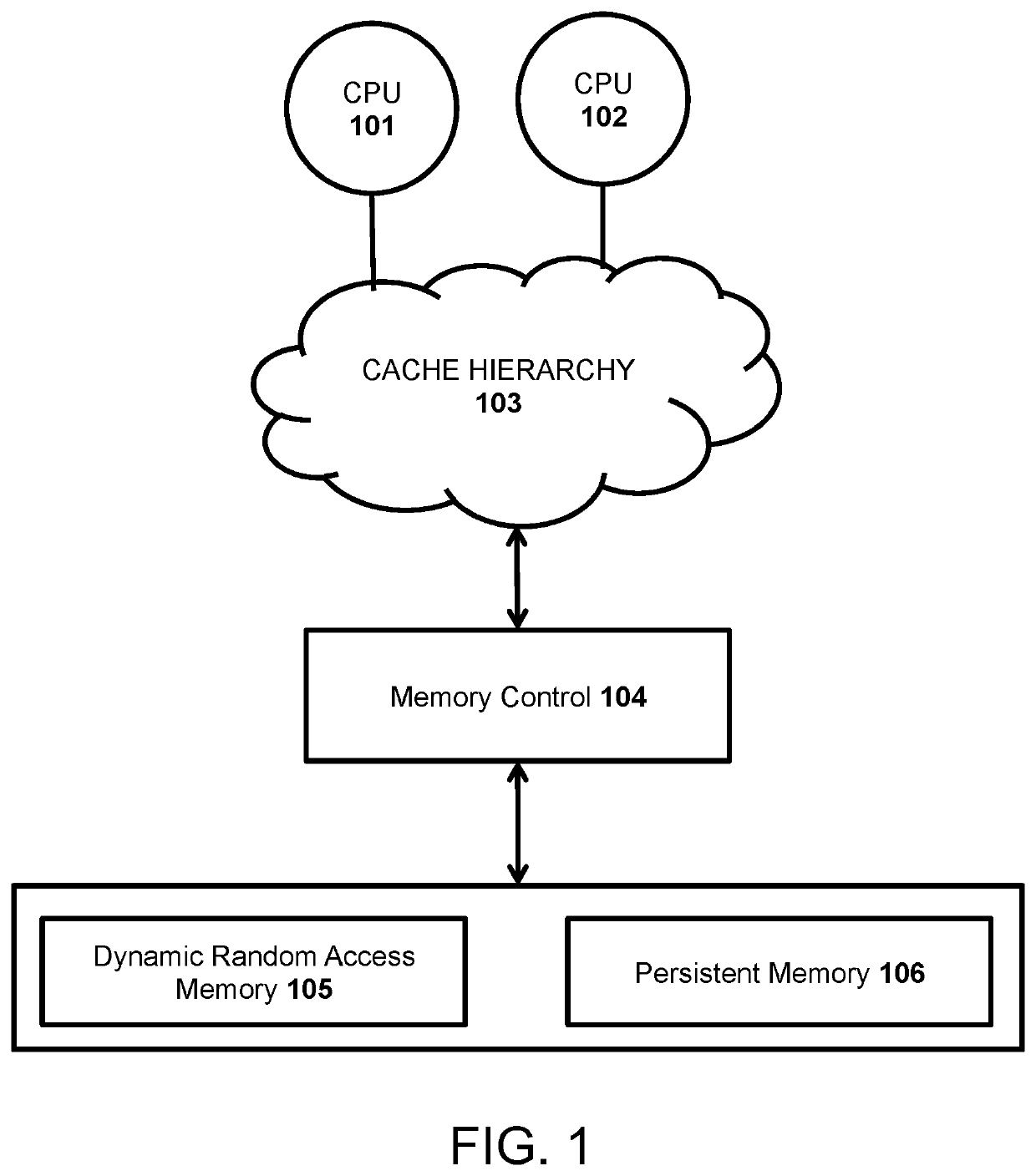

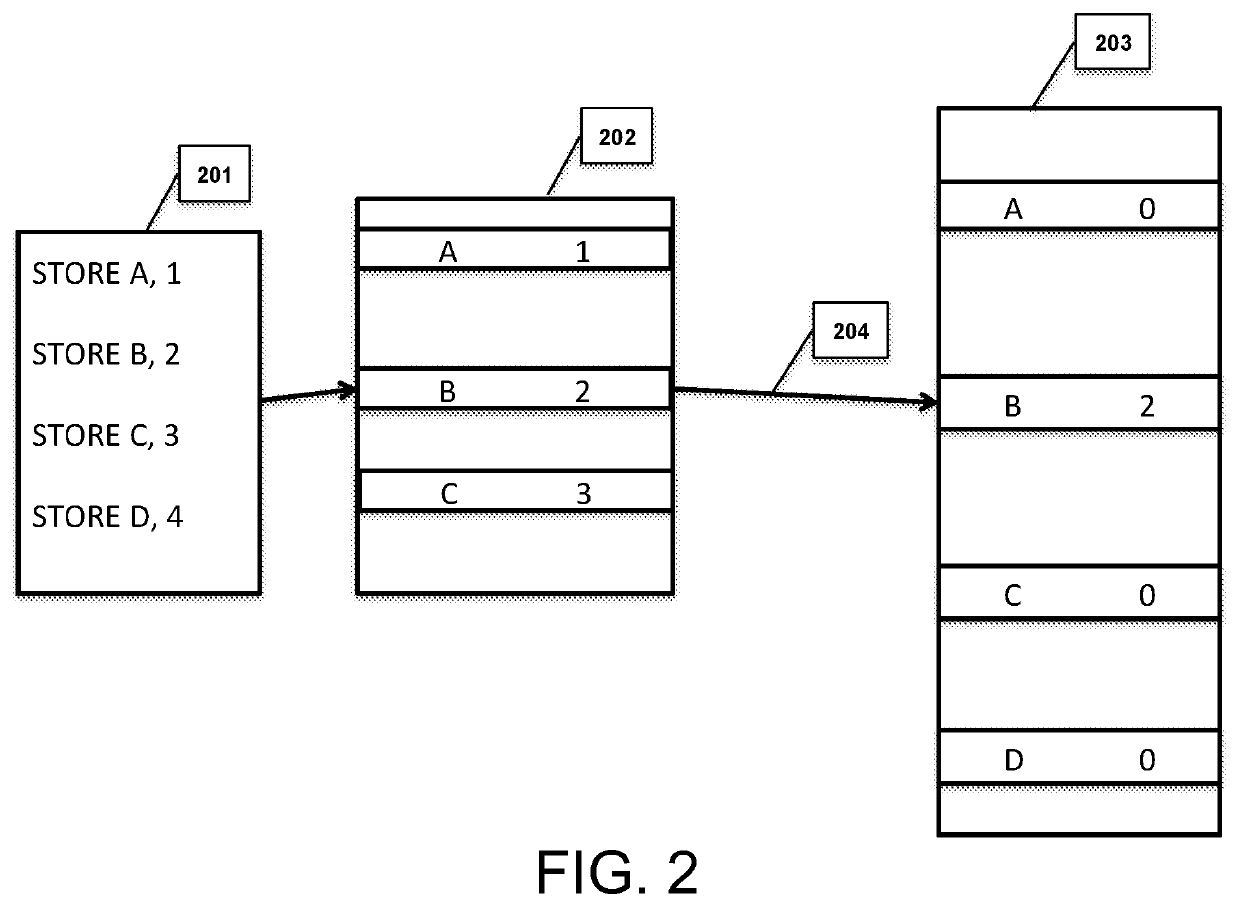

System and method for persisting hardware transactional memory transactions to persistent memory

ActiveUS10956324B1Atomicity of operationDurability of write operationMemory architecture accessing/allocationConcurrent instruction executionComputer architectureConcurrency control

Owner:GILES ELLIS ROBINSON +1

System and method for providing integrated processing platform for optical cable network design

ActiveCN103309965ARealize automatic calculationRealize visualizationSpecial data processing applicationsGraphicsComputer architecture

The invention discloses a system and a method for providing an integrated processing platform for optical cable network design. The system comprises a database server and at least one client side in communication connection with the database server, wherein the database server comprises a base map database for storing and providing geographic element information on a topographic map, a design database for storing and providing optical cable network design data and a resource database for storing and providing optical cable network resource data; the client side comprises an available-resource analysis module for analyzing the optical cable network resource data, a drawing module for drawing or changing an optical cable network plan, an optimized design module for calculating and optimizing optical cable network element parameters, a display module for displaying optical cable network lines and optical cable network elements in real time and a graphic filing module for transmitting optical cable network design and changed data to the database server to generate a design drawing. According to the system and the method disclosed by the invention, the automation of the optical cable network design can be realized.

Owner:SHENZHEN TOPWAY NETWORK ENG CO LTD

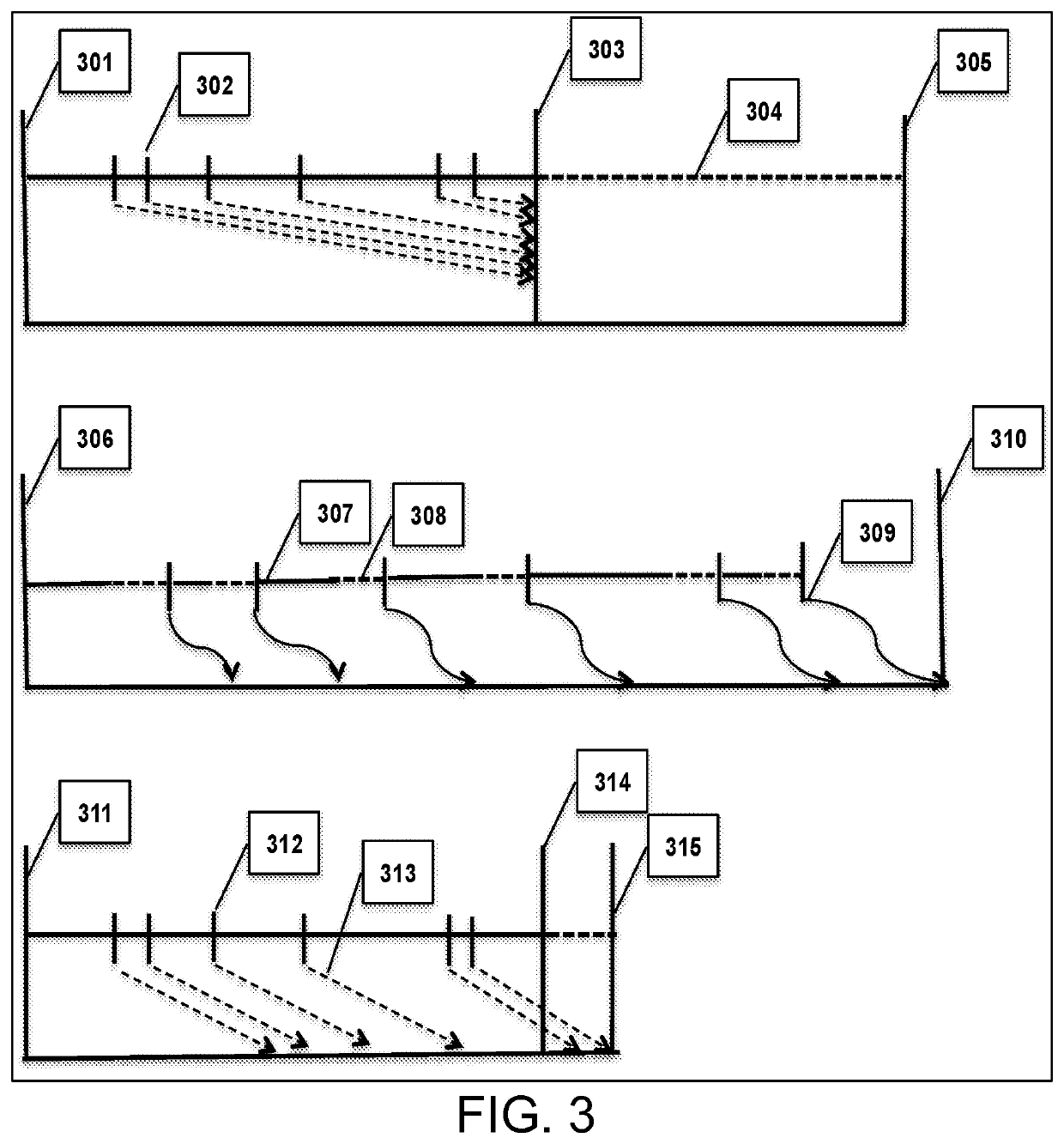

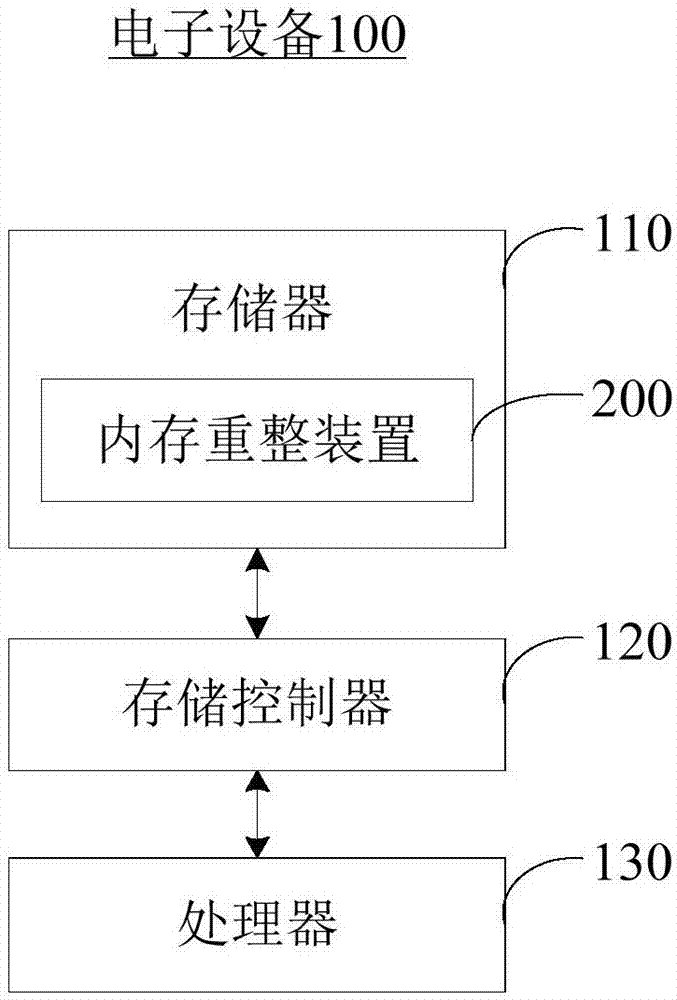

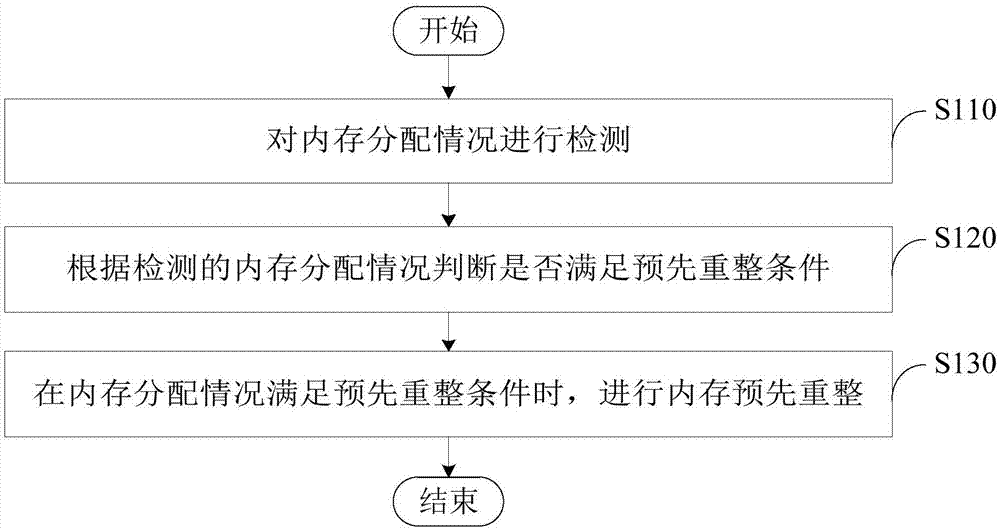

Internal memory reforming method and device, electronic equipment and readable storage medium

ActiveCN107193753AMemory architecture accessing/allocationMemory adressing/allocation/relocationElectronic equipmentComputer architecture

Owner:ONEPLUS TECH SHENZHEN

System and method for optimizing integrated circuit design

ActiveCN113361219AConfiguration CADElectric pulse generatorComputer architectureSoftware engineering

Embodiments of the present invention provide a system and method for optimizing an integrated circuit design, including a standard cell having a plurality of input and output memory elements (such as flip-flops, latches, etc.) with some combinatorial logic interconnected between these elements. In an embodiment, slave latches on an input flip-flop are replaced by a smaller number of latches at a downstream node of combinatorial logic, thereby improving performance, area, and power while maintaining functionality at interface pins of the standard cell. Also described is a process of inferring such a standard cell, or a process of remapping an equivalent sub-circuit from a netlist to the standard cell, from a behavioral description of the design, such as an RTL. The embodiment of the invention also provides a computer readable medium for encoding with a cell library.

Owner:TAIWAN SEMICON MFG CO LTD

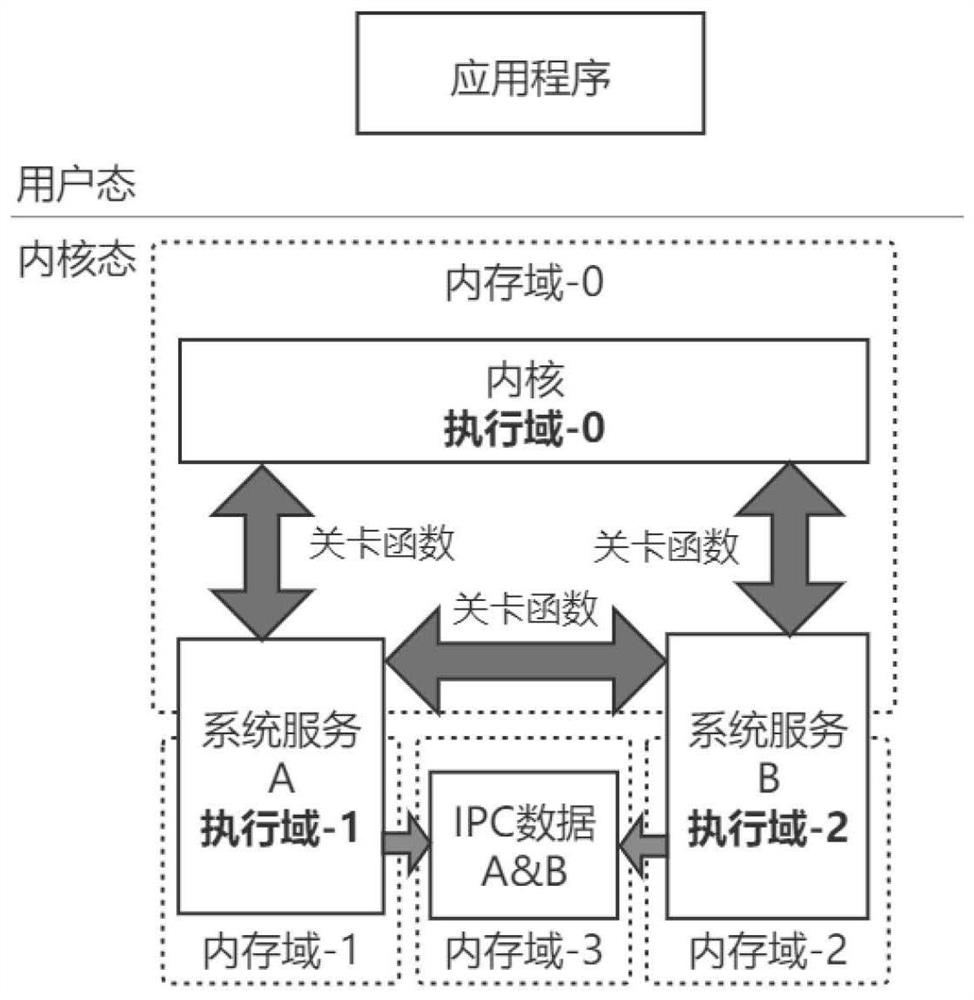

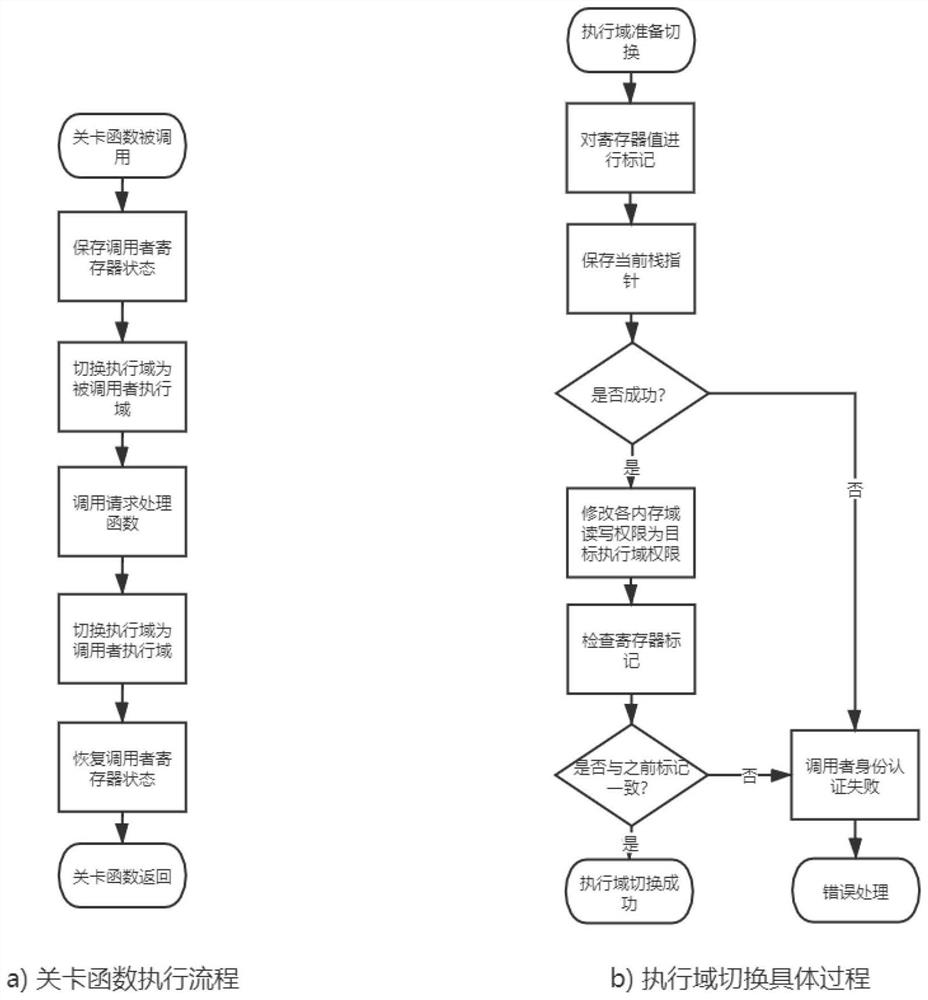

MPK technology-based inter-microkernel-module communication method and system, and medium

PendingCN111949596AReduce IPC performance overheadEnsure safetyDigital computer detailsPlatform integrity maintainanceComputer architectureEngineering

Owner:SHANGHAI JIAO TONG UNIV

Server mainboard and server

ActiveCN112051904AMeet cooling needsDigital processing power distributionComputer architectureEngineering

The invention discloses a server mainboard and a server. The server mainboard comprises: a power supply module for supplying power to a CPU according to the type of the CPU, wherein the type of the CPU comprises an Altra CPU and an Altra max CPU; a PCIe module for connecting the CPU with the part, excluding the CPU, of the server mainboard; a CPU pin connection module for connecting pins on the CPU; and a heat dissipation module for providing a heat dissipation function according to the CPU type so as to dissipate heat of the CPU. In this way, the power supply module, the PCIe module, the CPUpin connection module and the heat dissipation module can be specifically adjusted according to the type of the CPU, and different requirements of the Altra CPU and the Altra max CPU are met, so thatthe server mainboard can be compatible with the Altra CPU and the Altra max CPU.

Owner:SHANDONG YUNHAI GUOCHUANG CLOUD COMPUTING EQUIP IND INNOVATION CENT CO LTD

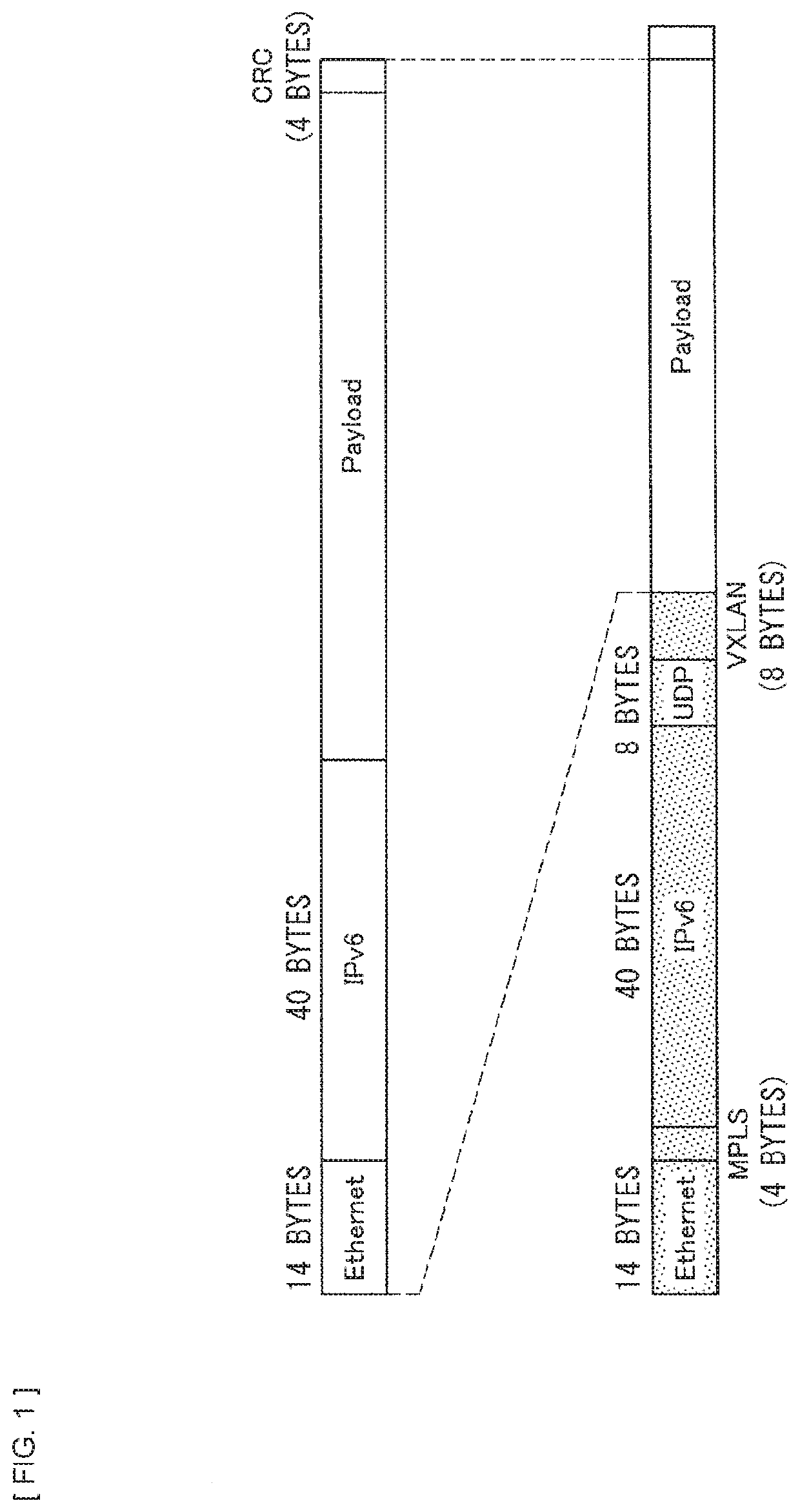

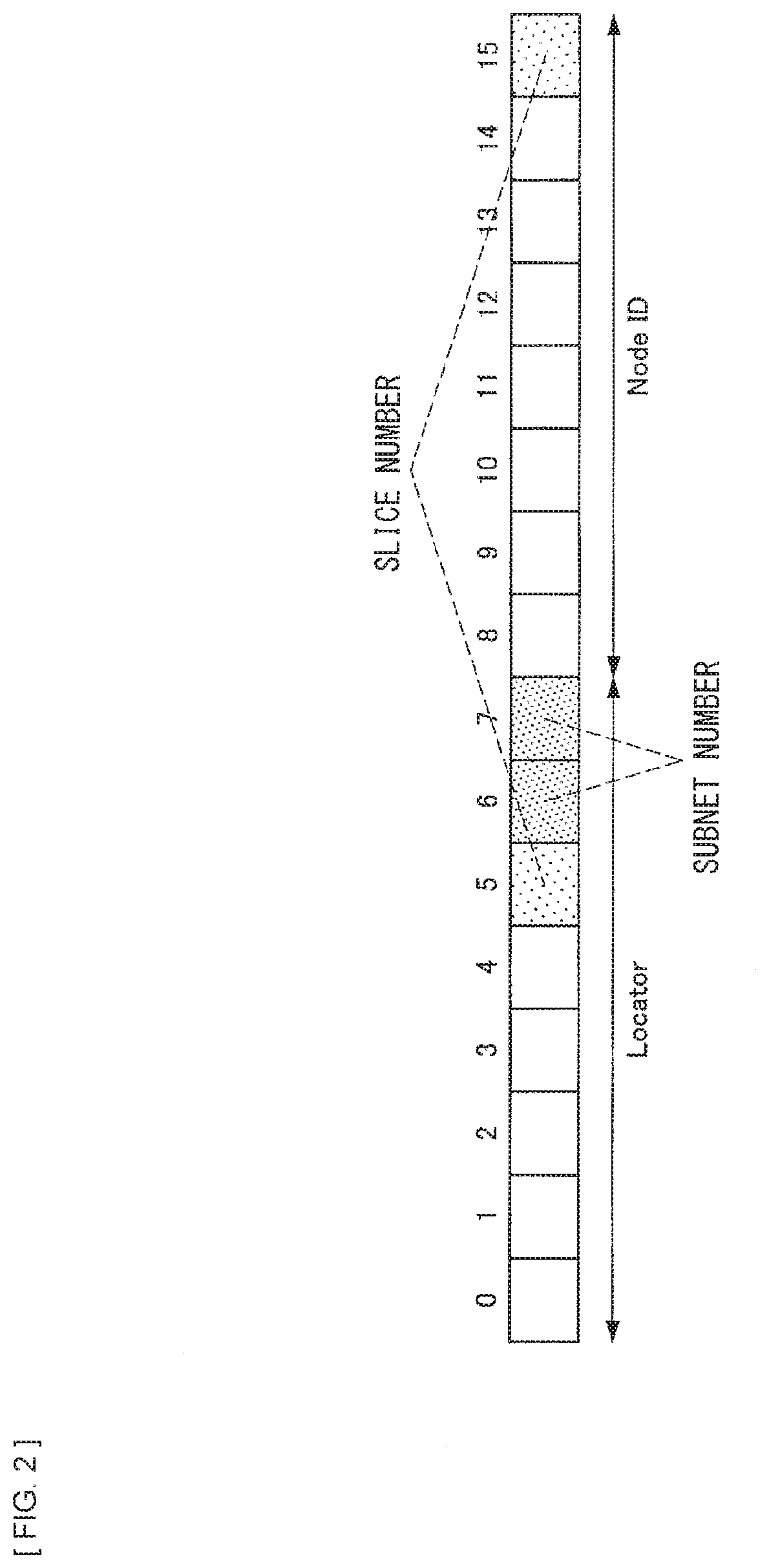

Communication apparatus, communication method, and computer program

ActiveUS20200245296A1Improve communication efficiencyAssess restrictionWireless network protocolsComputer architectureNetwork addressing

Owner:SONY CORP

An electronic code management system and platform of an electronic coupon

The invention discloses a management system for an electronic code of an electronic coupon, including an electronic code generation module, an electronic code storage module an an electronic code issuing module, wherein an electronic code generated by the electronic code generation module comprises a main code; an auxiliary code and a check code, the uniqueness of the electronic code is ensured bythe random code; Generation efficiency is improved, the electronic code storage module respectively obtains a ciphertext full text and a ciphertext index through two encryption algorithms; the security of the electronic code is ensured; and finally, the electronic code issuing module adopts a serial issuing mode for the electronic codes of the same inventory unit, so that repeated issuing is avoided, the issuing efficiency is improved, and therefore, the system realizes the closed loop of the electronic code service, guarantees the safety and high efficiency of the electronic codes to a certain extent, and is more suitable for actual application requirements. In addition, the invention further provides an electronic code management platform of the electronic coupon, and the function of the electronic code management platform corresponds to the function of the system.

Owner:GUANGZHOU PINWEI SOFTWARE

Power wireless relay communication system based on low-power-consumption wide-area communication technology

ActiveCN110856154ARealize functionRealize relay transmissionNetwork topologiesShort range communication servicePower applicationComputer architecture

The invention discloses an electric power wireless relay communication system based on a low-power-consumption wide area communication technology. The system comprises an MCU processor, a power supplymanagement module, a serial communication interface, a ZigBee communication module, a BLE communication module and a LoRaMESH relay communication module. And the MCU processor is connected with the power supply management module, the serial communication interface, the ZigBee communication module, the BLE communication module and the LoRaMESH relay communication module. The electric power wireless communication relay system provided by the invention can realize the functions of panoramic monitoring, transmission control and the like of information access, local processing, relay transmissionand the like of sensing equipment in various communication modes in an electric power application scene.

Owner:JIANGSU FRONTIER ELECTRIC TECH

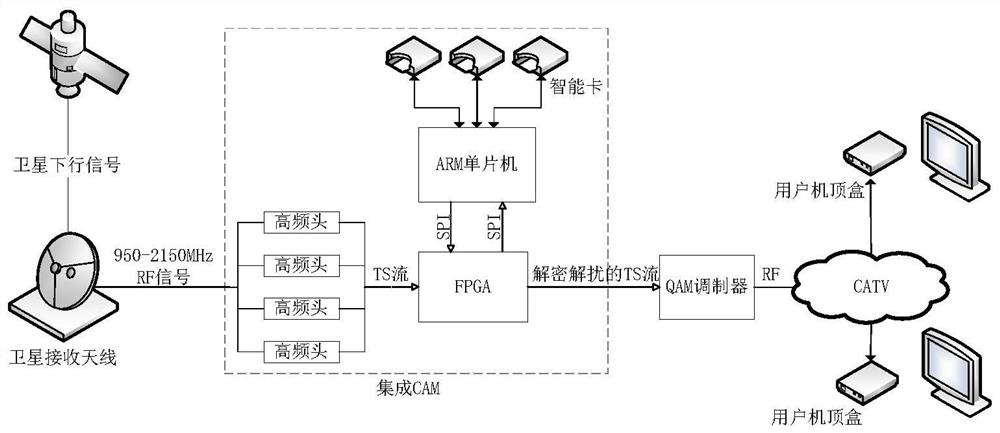

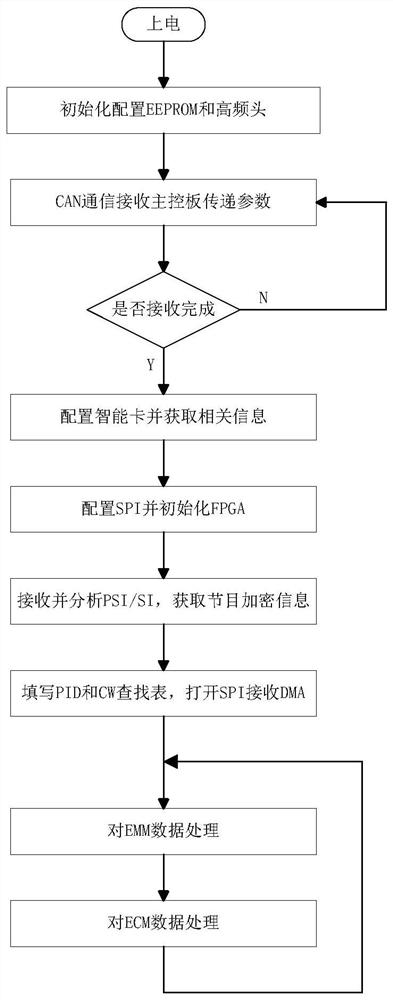

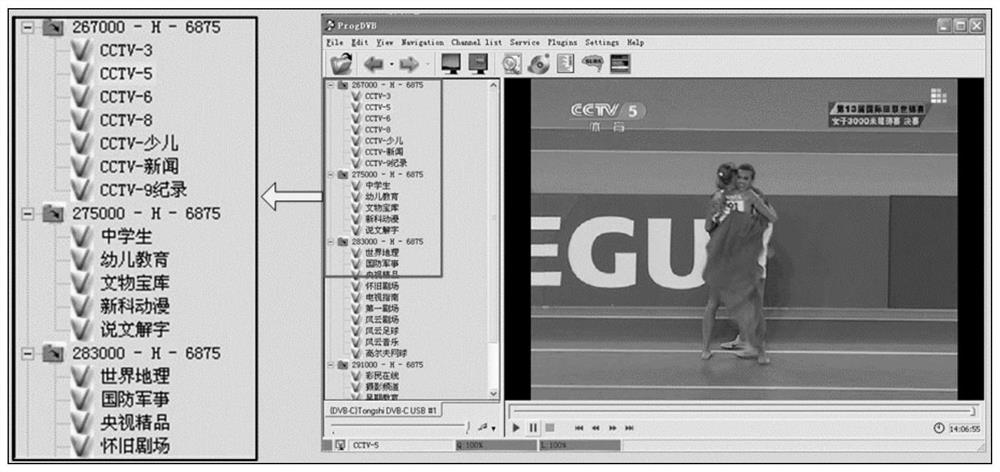

System and method for processing multi-transponder program by integrating conditional access module

ActiveCN113727159AIncrease in sizeIncrease costSelective content distributionComputer architectureConditional access

Owner:XI AN JIAOTONG UNIV

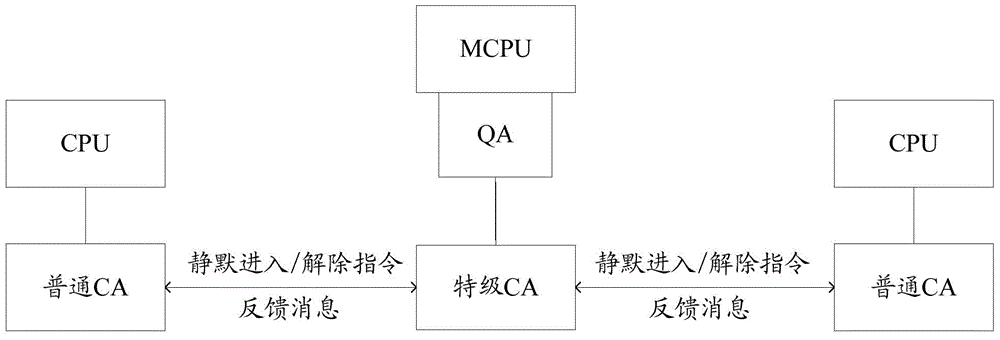

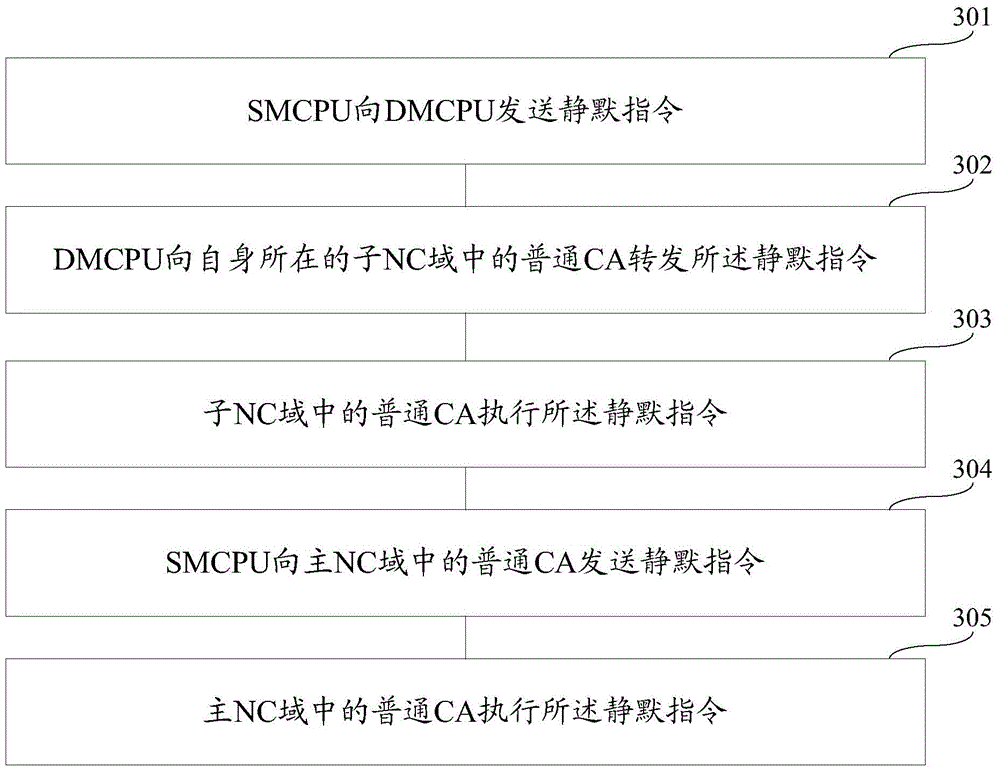

Server quiescing method and system

ActiveCN105335217AShorten the timeAvoid delayMultiprogramming arrangementsSpecific program execution arrangementsComputer architectureA domain

Owner:XFUSION DIGITAL TECH CO LTD

Camera system with low delay, less cache and controllable data output mode and method

ActiveCN109688314ALower latencyCompact handlingTelevision system detailsColor television detailsComputer hardwareComputer architecture

The invention relates to a camera system with low delay, less cache and a controllable data output mode. The camera system comprises a PLL module, a configuration register, a system and logic controlmodule, a photosensitive pixel acquisition control module, a photosensitive pixel matrix module, an analog signal processing module, an A / D conversion module, a digital image processing module, a buffer and an output interface module, wherein the configuration register, the system and logic control module, the photosensitive pixel acquisition control module, the photosensitive pixel matrix module,the analog signal processing module, the A / D conversion module, the digital image processing module, the buffer and the output interface module are sequentially connected; and the system and logic control module is also respectively connected with the PLL module, the A / D conversion module, the digital image processing module, the buffer and the output interface module. According to the scheme ofthe invention, by shrinking the units of image acquisition and output and simplifying the corresponding system logic control, the whole processing procedure is more compact, and the delay and cache space of the camera system and the whole system are reduced.

Owner:FUZHOU SHICHI TECH CO LTD

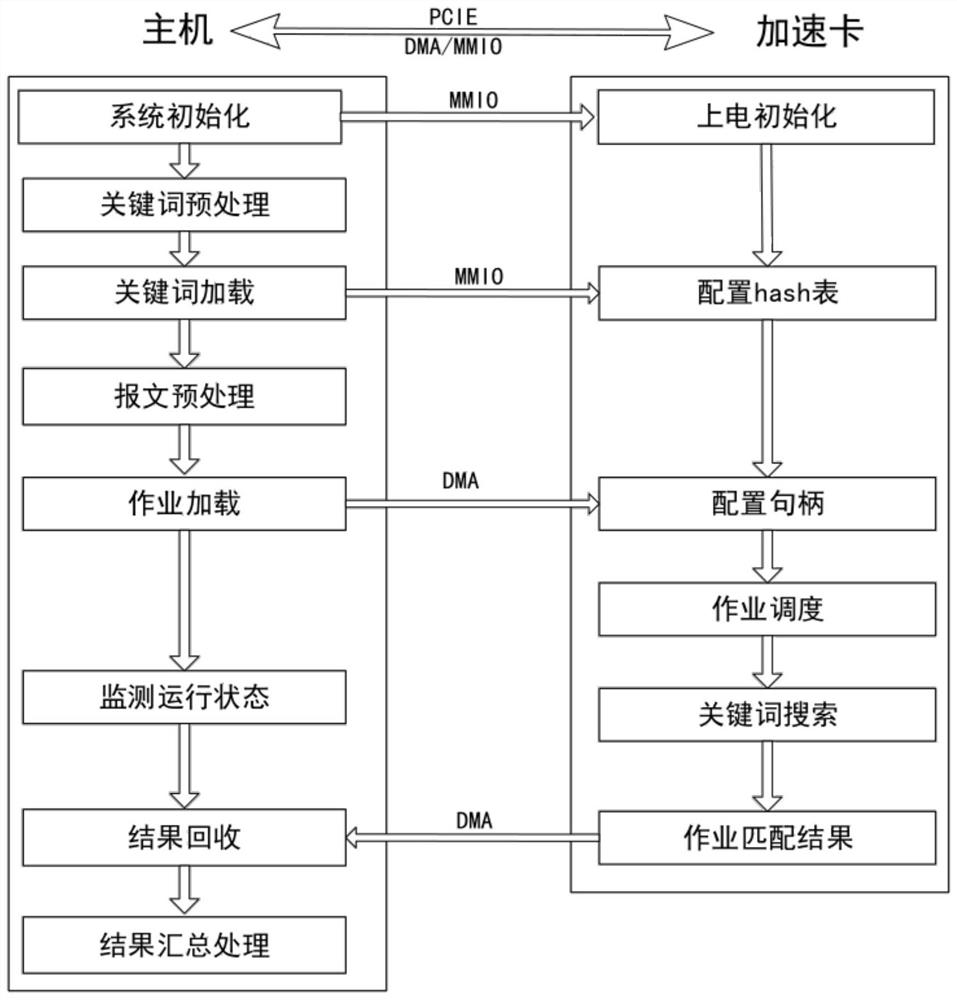

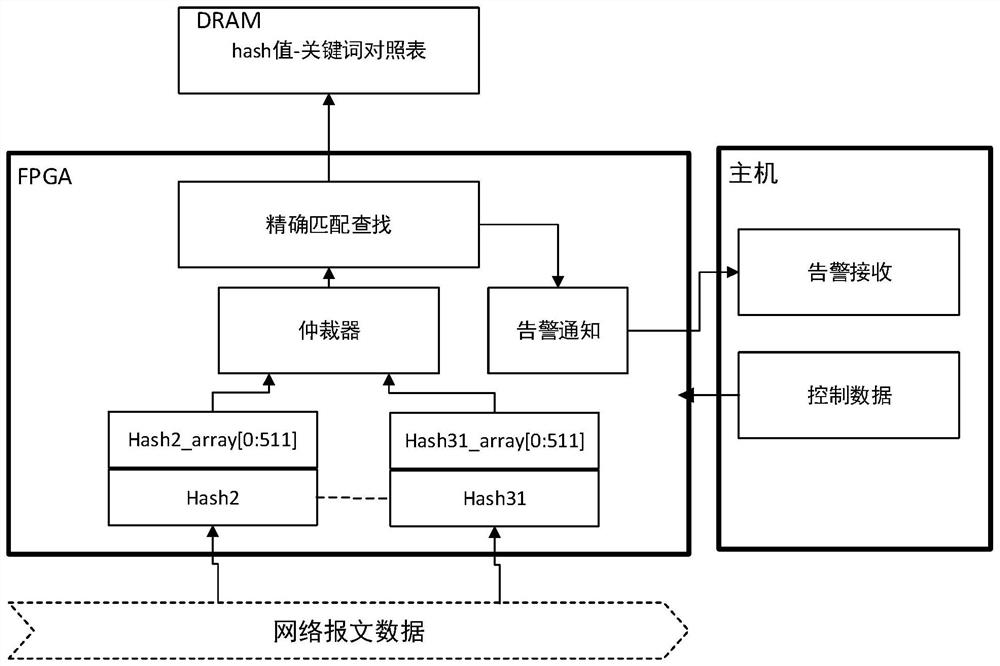

Efficient keyword filtering method for FPGA (Field Programmable Gate Array)

PendingCN114297368AFast searchReduce false alarm rateDigital data information retrievalSpecial data processing applicationsComputer architectureEngineering

Owner:无锡宏创盛安科技有限公司

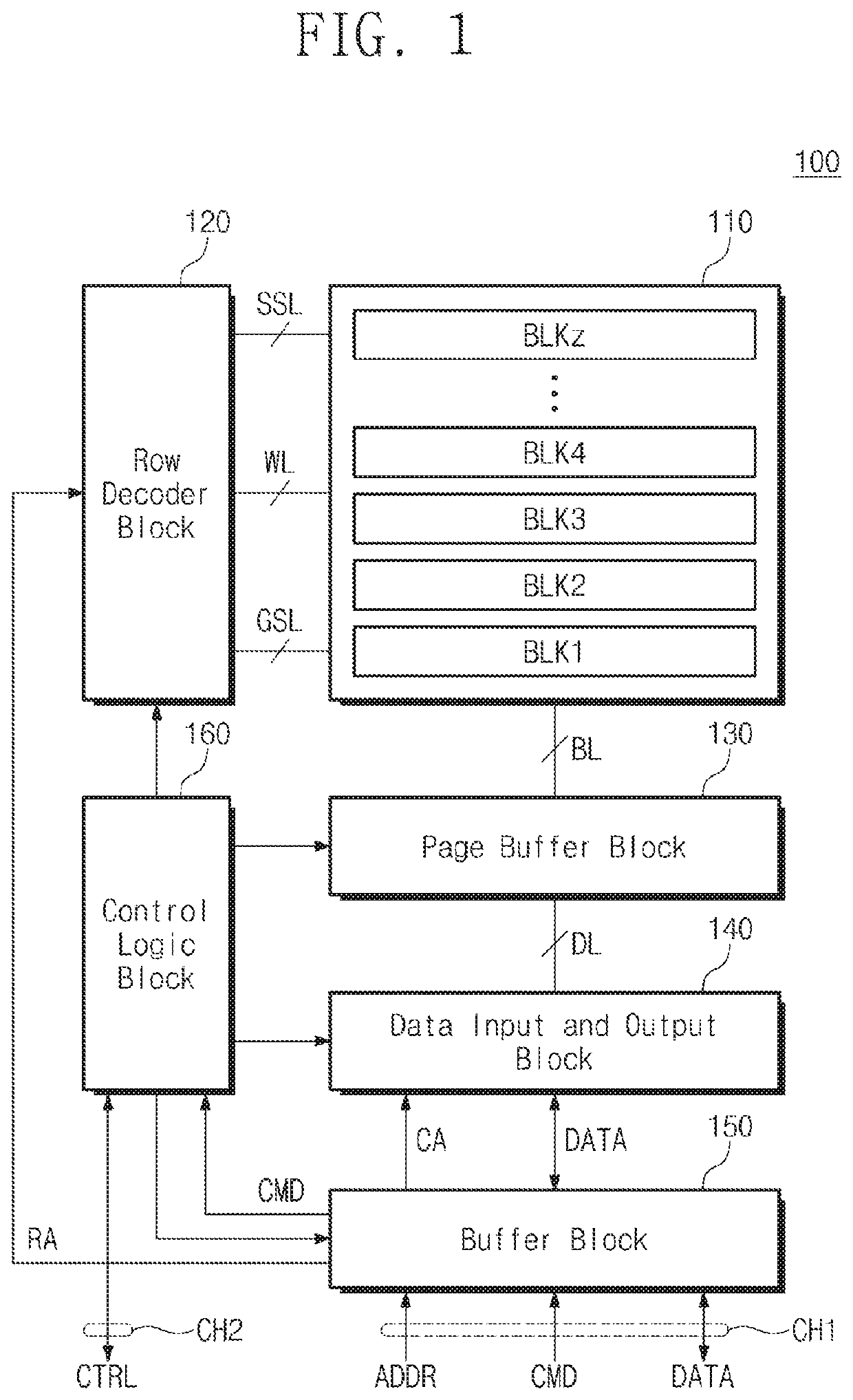

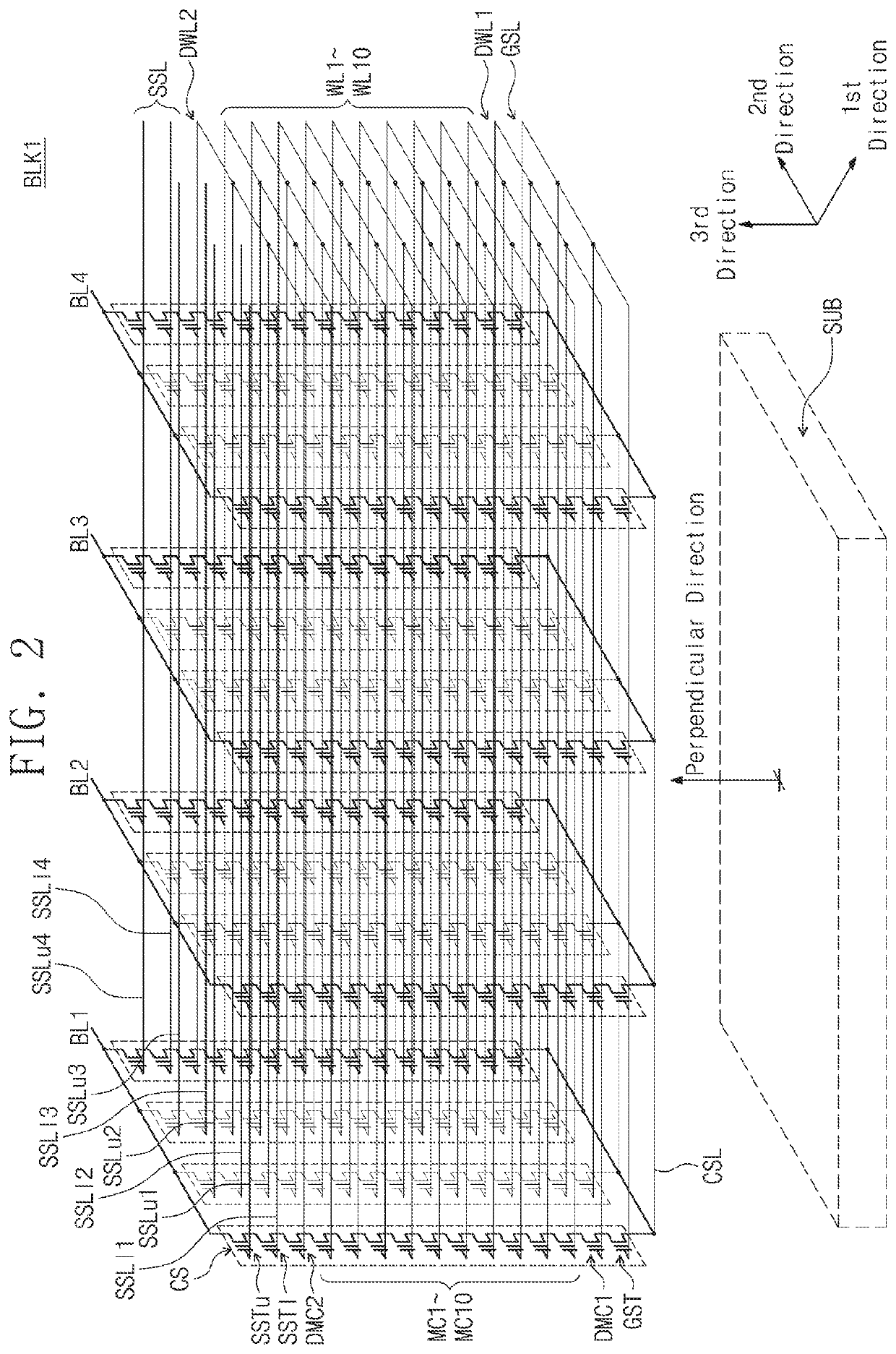

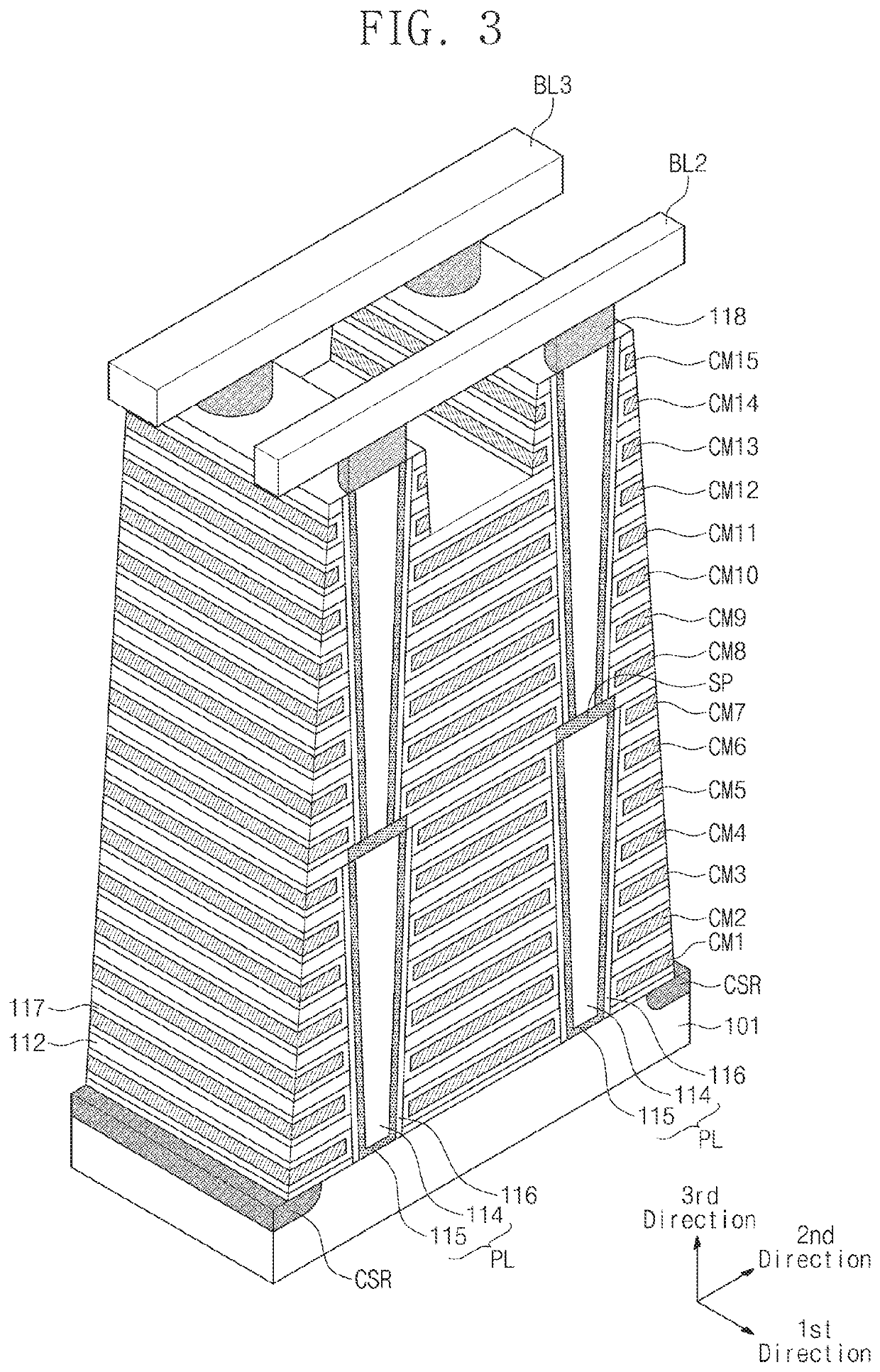

Nonvolatile memory device, storage device, and operating method of nonvolatile memory device

ActiveUS20210065806A1Improve reliabilityLow reliabilitySemiconductor/solid-state device detailsSolid-state devicesComputer architectureMemory cell

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor package

ActiveUS20180059759A1Programme controlMemory architecture accessing/allocationComputer architectureSemiconductor package

Owner:ROHM CO LTD

Method to reduce register access latency in split-die soc designs

Methods and apparatus to reduce register access latency in split-die SoC designs. The method is implemented on a platform including a legacy socket and one or more non-legacy (NL) sockets comprising split-die System-on-Chips (SoC)s including multiple dielets interconnected with a plurality of Embedded Multi-Die Interconnect Bridges (EMIBs). The dielets include core dielets having cores, cache controllers and memory controllers. The method provides an affinity between a control and status registers (CSRs) memory range for the NL sockets such that CSRs in the memory controllers for multiple core dielets are programmed using transactions forwarded along core-to-cache controller datapaths that avoid crossing EMIBs. In one aspect, a transient map of address ranges is created that includes a respective Sub-NUMA Cluster (SNC) range allocated for the NL sockets, with a range of CSR addresses for accessing CSRs in the memory controllers for the NL sockets being stored in the respective SNC ranges.

Owner:INTEL CORP

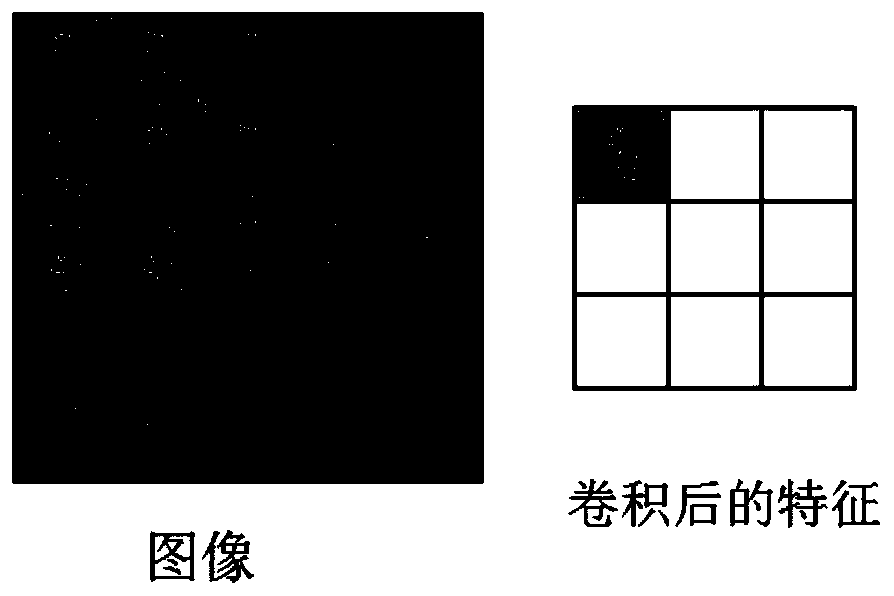

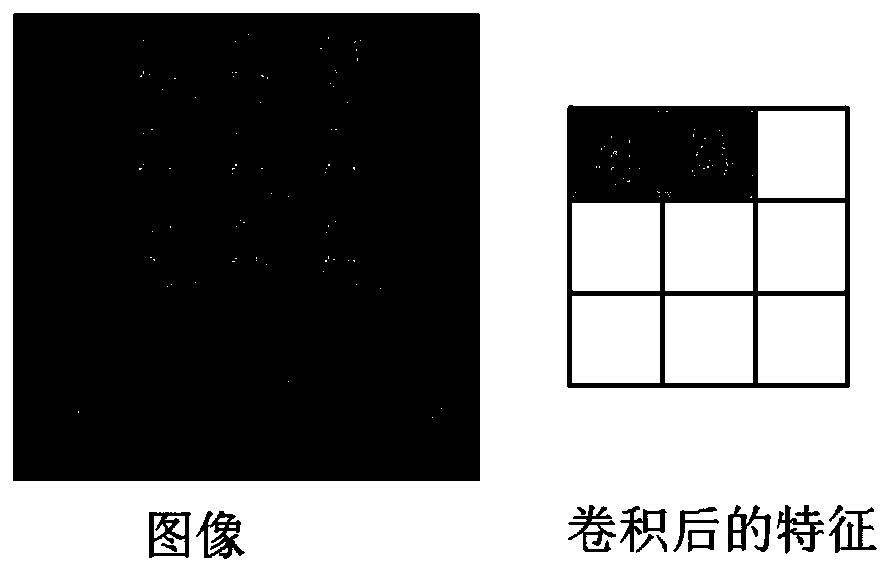

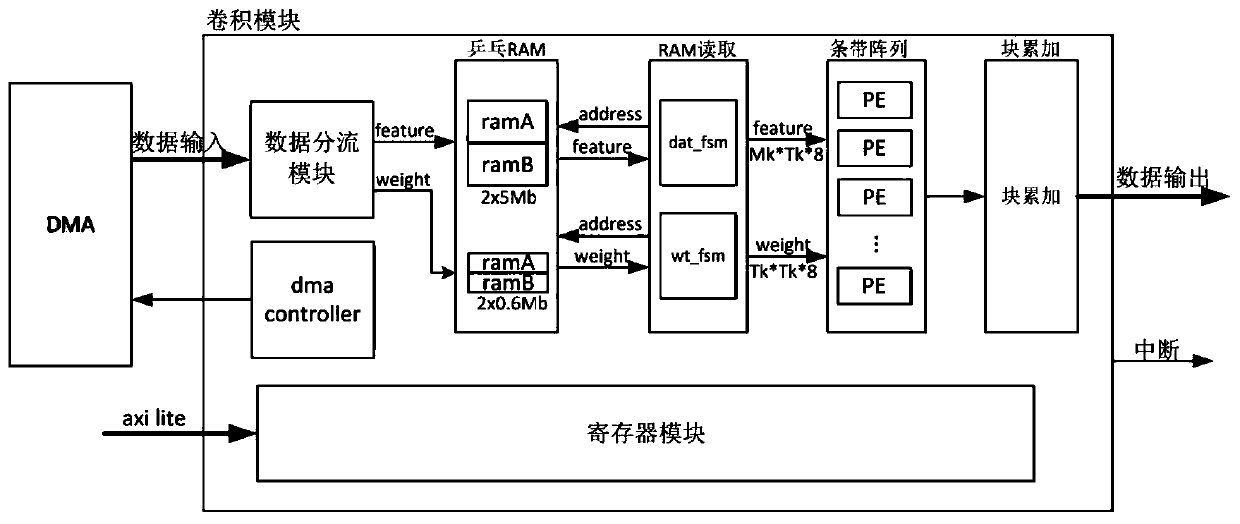

Ping-pong RAM-based strip array convolution module and operation method of convolution module

PendingCN110688616AImprove utilization efficiencyImprove computing efficiencyDigital data processing detailsComplex mathematical operationsData packComputer architecture

Owner:陈小柏

Shift register, electronic device, control method and software program product

ActiveUS20120099696A1Effective controlParallel/series conversionDigital storageMultiplexingShift register

Disclosed is a shift register (200, 400) comprising an input (205), an output (230) and a plurality of register cells (210) serially connected between the input and the output, each register cell being connected to a neighboring cell via a node, wherein at least some of said nodes comprise a multiplexer (220) having an output coupled to the downstream register cell and a plurality of inputs, each of said plurality of inputs being coupled to a different upstream register cell such that different length sections of the shift register can be selectively bypassed, the shift register further comprising a set of parallel IO channels (230, 410) facilitating conversion between interleaved and de-interleaved data, each of said channels being coupled to a different one of said nodes, the number of parallel IO channels being smaller than the total number of register cells in the shift register.

Owner:NXP BV

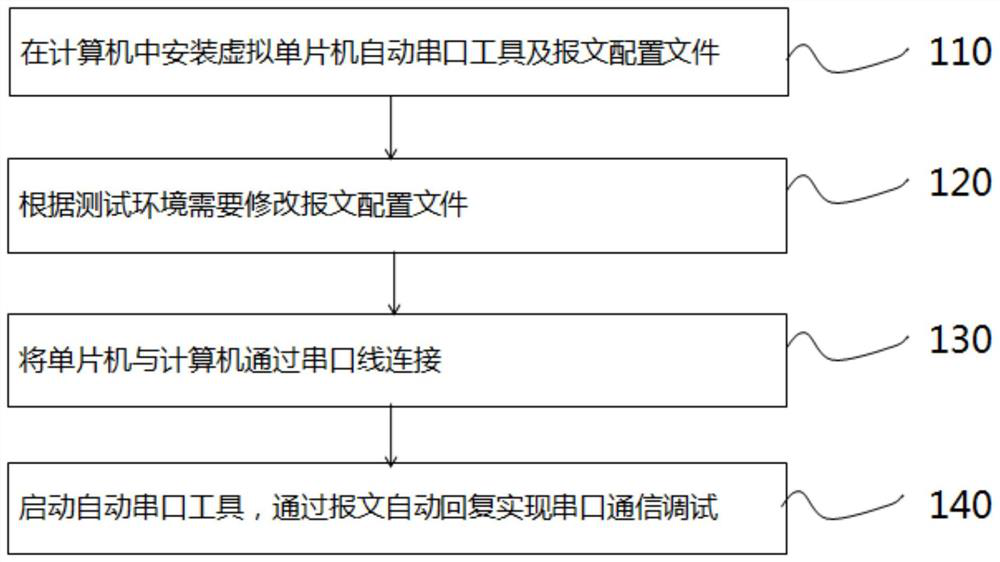

Serial communication debugging method based on test environment

PendingCN112988481AImplement customized auto-replyEasy to debugDetecting faulty computer hardwareComputer architectureEngineering

Owner:SHANDONG YINGXIN COMP TECH CO LTD

A read-write test method for memory chip flash by bypassing a customized system-on-chip chip

The invention provides a read-write test method for memory chip flash by bypassing a customized system-on-chip chip. Comprising the following steps: sending multiple groups of specific binary sequence codes to a data line TDI of a JTAG port through a parallel port of a computer; with the help of an oscilloscope, calculating the instruction length, the data length and the highest transmission speed of the JTAG interface through code streams observed on a data line TDO of the JTAG interface; then, converting an operation instruction corresponding to the specification and model of the flash chip needing to be subjected to read-write test into a corresponding binary sequence code according to characteristic parameters of a JTAG interface, and finally loading the binary sequence code to a parallel port card of a computer, so that the parallel port card can automatically match the level of the JTAG interface and shift the sequence code into the pin of the system-on-chip according to the sequence; meanwhile, isolating the internal control logic circuit of the system-on-chip automatically; finally, sending the binary sequence code accurately to the control bus of the flash chip, and realizing the full-automatic read-write test of the flash storage chip.

Owner:GUANGZHOU HANGXIN ELECTRONIC CO LTD

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap