Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

158results about How to "Reduce power consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

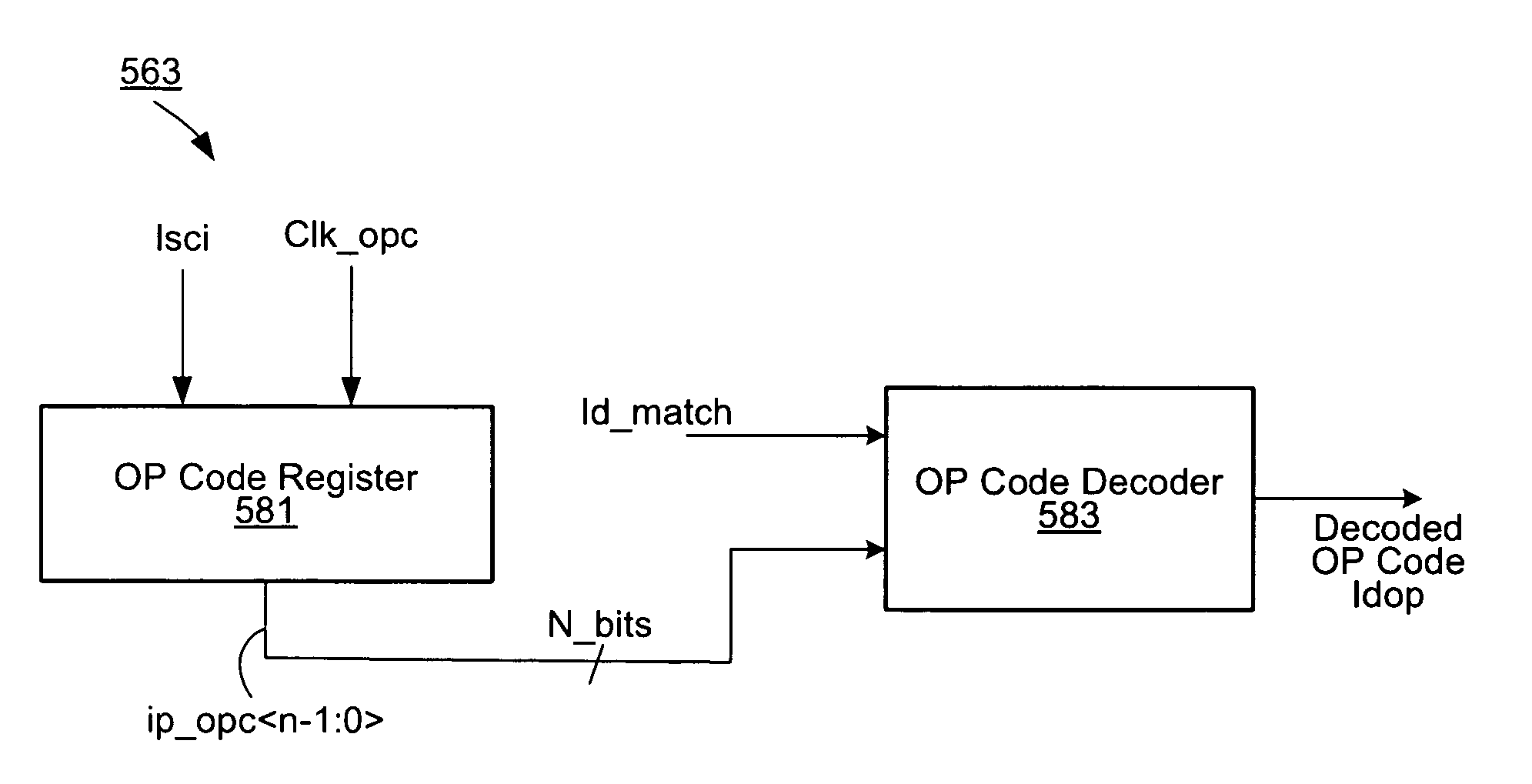

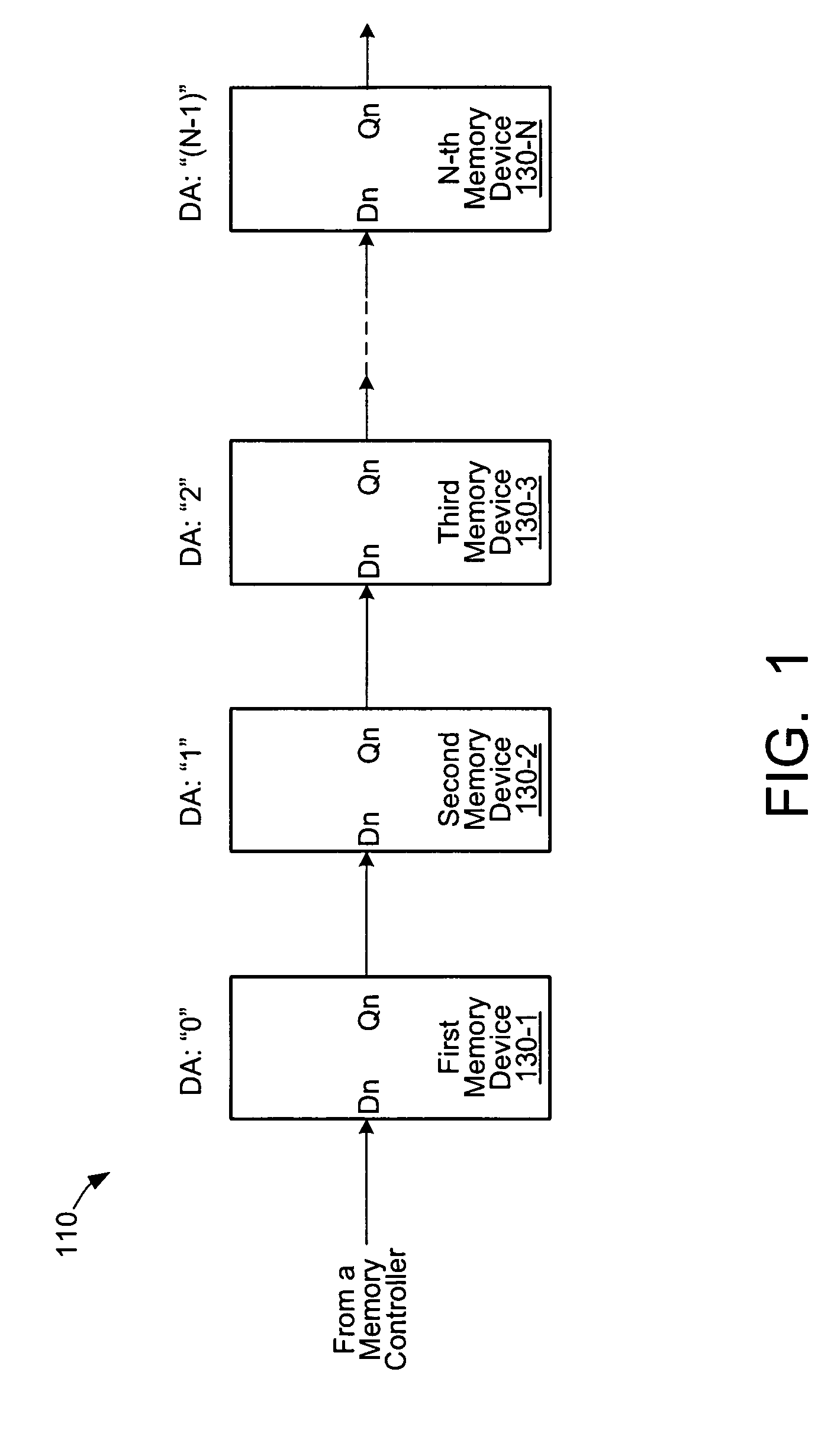

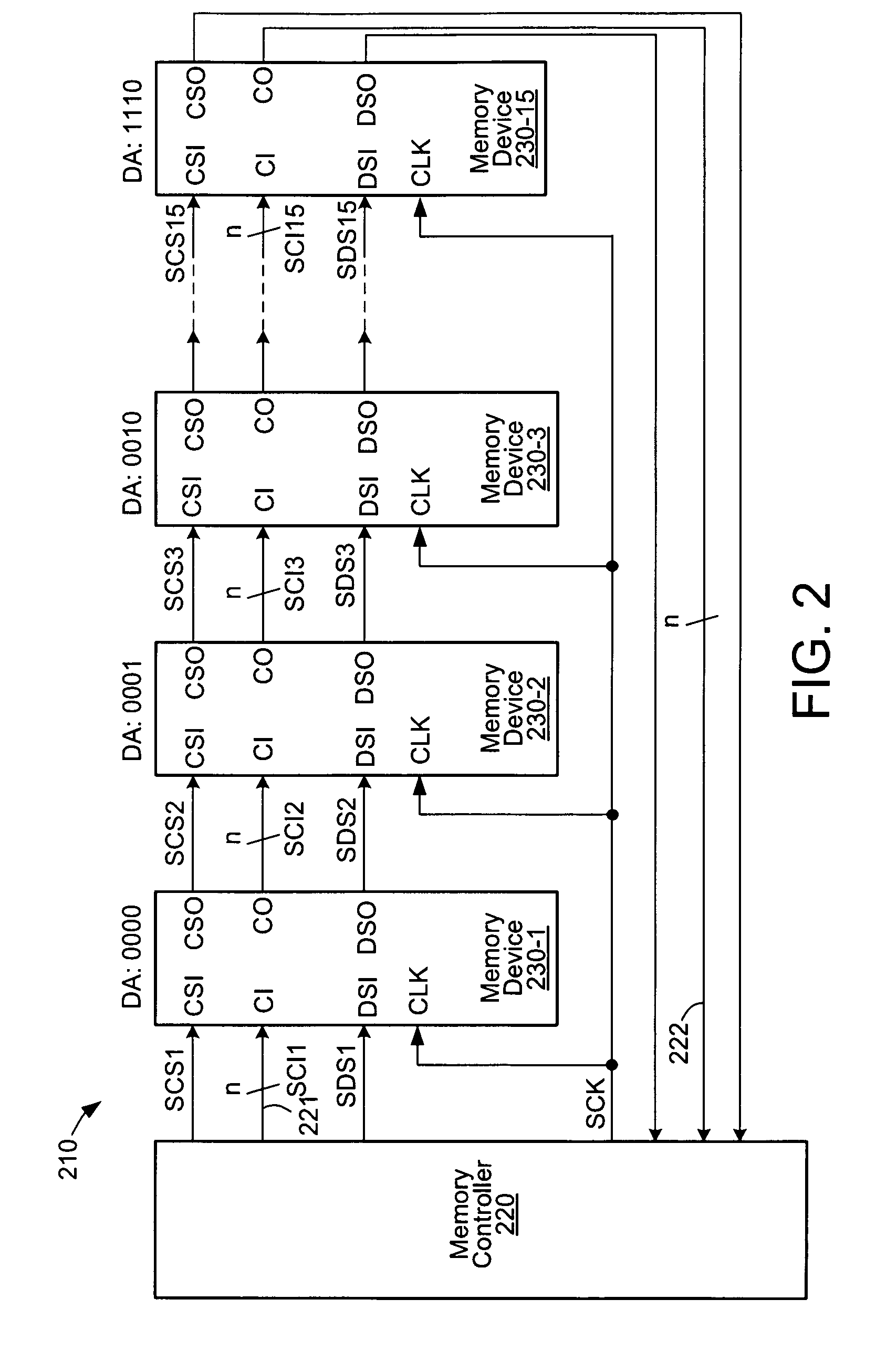

Semiconductor device and method for reducing power consumption in a system having interconnected devices

InactiveUS20080201588A1Reduce power consumptionReduce power consumption levelDigital storagePower supply for data processingClock generatorEngineering

Owner:CONVERSANT INTPROP MANAGEMENT INC

Memory Element and Semiconductor Device, and Method for Manufacturing the Same

InactiveUS20080205132A1InexpensiveReduce power consumptionDigital storageNanoinformaticsComputer scienceMiniaturization

Owner:ORACLE INT CORP +1

Light guide module having embedded LED

InactiveUS20050100288A1Improve light guide efficiencyExtended service lifeInput/output for user-computer interactionCoupling light guidesLight guideOptoelectronics

A light guide module of optical mouse is disclosed. The light guide module comprises a LED die within a light guide input of light guide means. The light guide input comprises an internal paraboloid. Light emitted by the LED die and parallel reflected from the paraboloid is impinged on a light guide output.

Owner:SUNPLUS TECH CO LTD

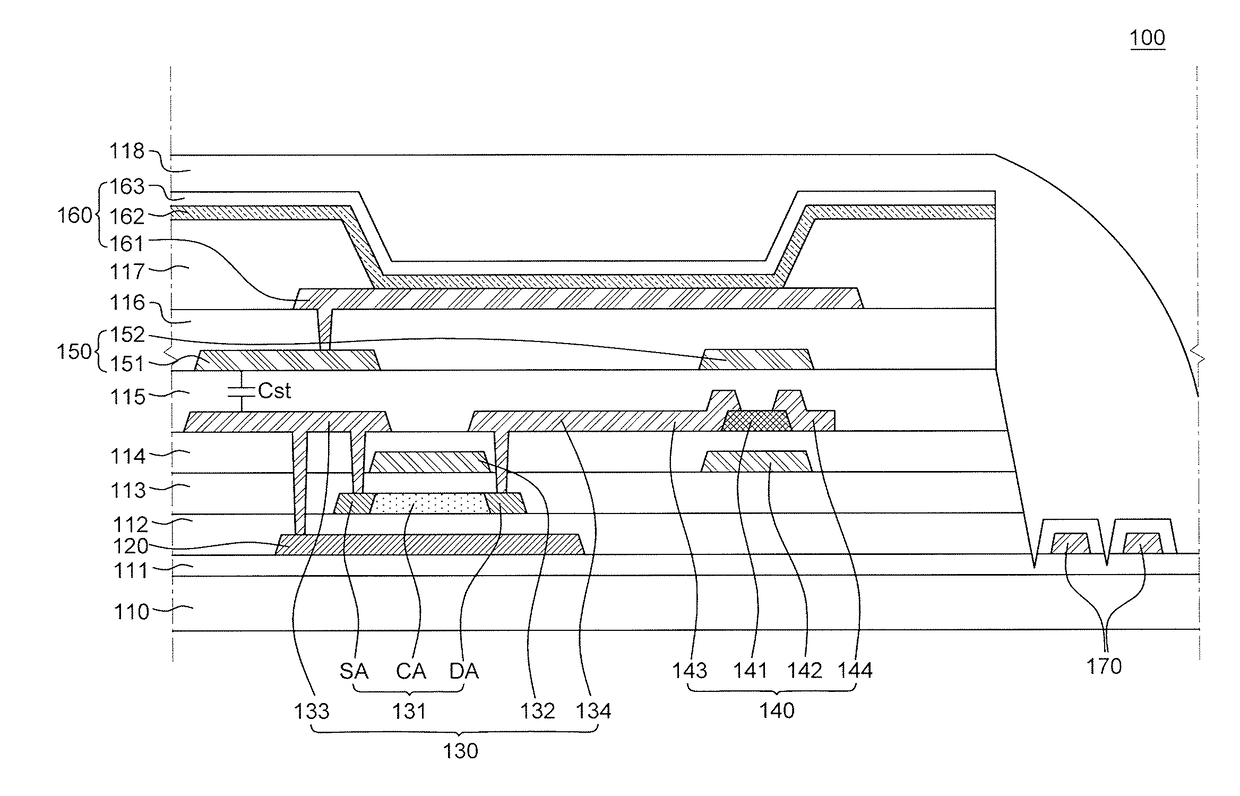

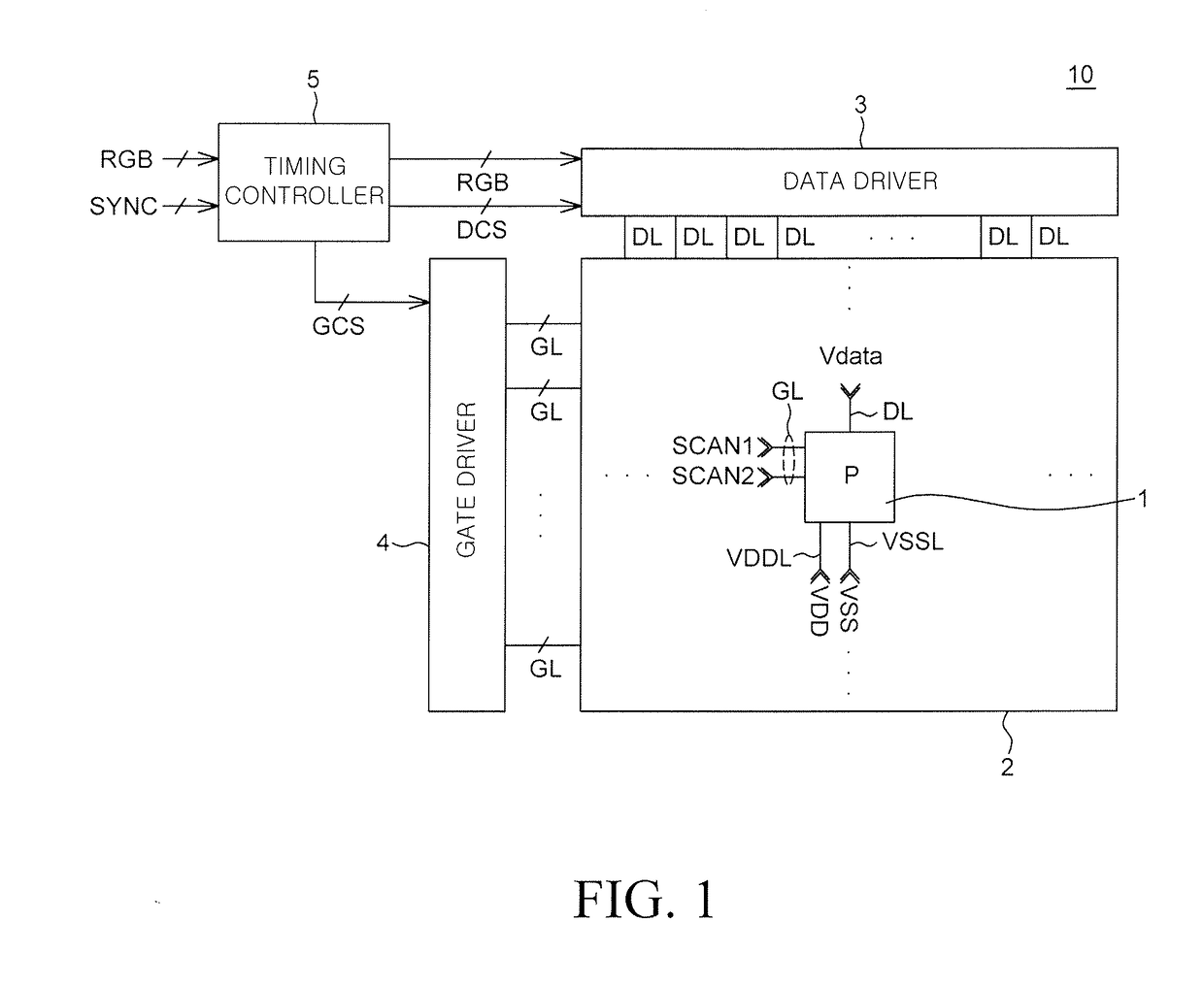

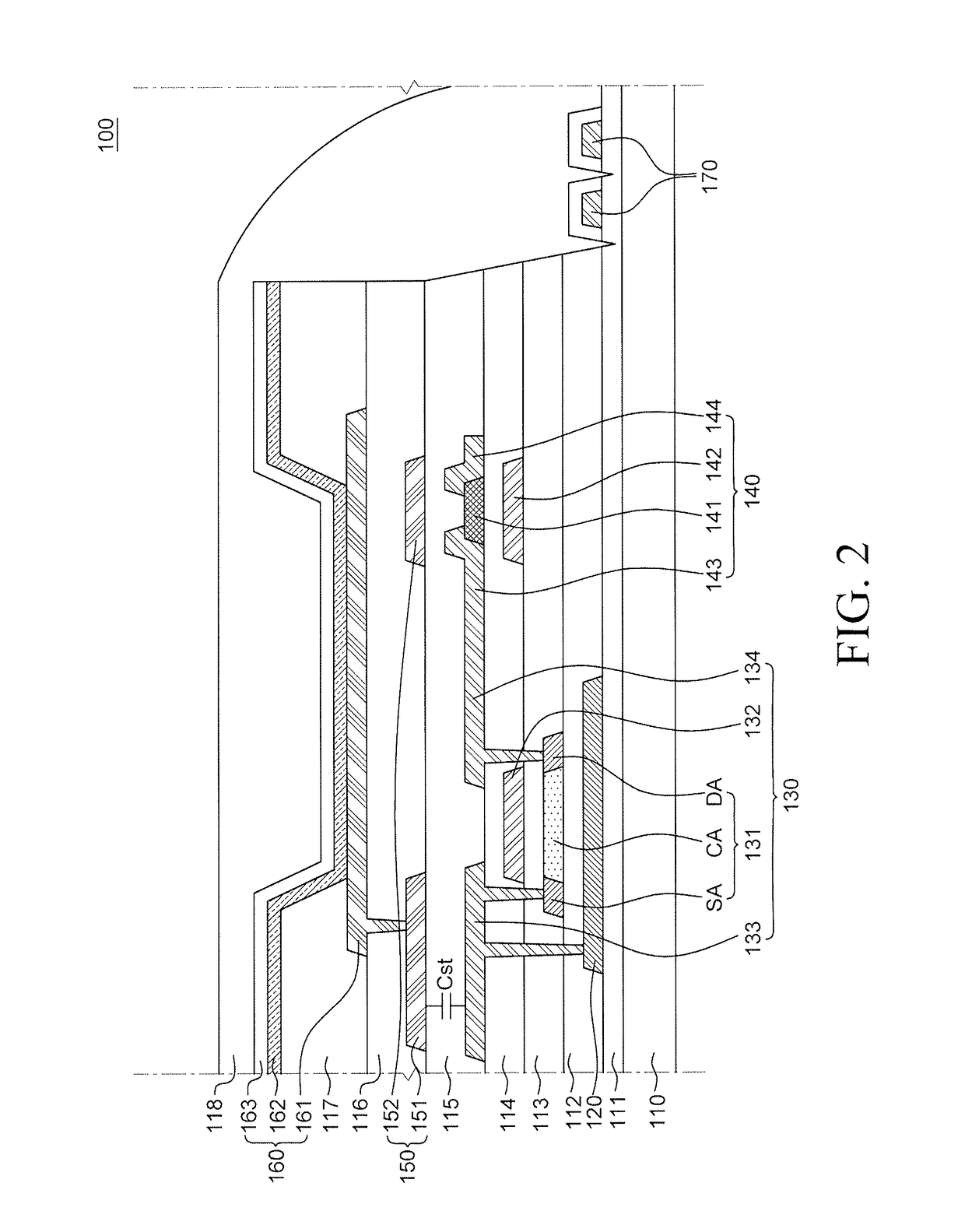

Hybrid thin film transistor and organic light emitting display device using the same

ActiveUS20180033849A1Reduce power consumptionImprove bias temperature stressSolid-state devicesSemiconductor/solid-state device manufacturingPolycrystalline siliconOptoelectronics

Owner:LG DISPLAY CO LTD

Method And Apparatus For Controlling Powder Saving Mode In Wireless Portable Internet System

InactiveUS20070274244A1Reduce power consumptionPower managementEnergy efficient ICTTelecommunicationsStation

Disclosed is a method and device for controlling a power saving mode for applying the sleep mode for saving power consumption to the mobility of subscriber stations in a mobile communication network and a wireless Internet system. Subscriber stations entering the sleep mode are constantly grouped, listening intervals of the subscriber stations for each group are not superimposed, the existence state of traffic in the subscriber stations is independently notified for each group, and the overhead of signaling messages is minimized when the traffic is notified to the subscriber station in the sleep mode.

Owner:KT CORP +4

Differential pipelined analog to digital converter with successive approximation register subconverter stages

InactiveUS6879277B1Improve conversion speedReduce power consumptionElectric signal transmission systemsAnalogue-digital convertersAnalog-to-digital converterCapacitor

Pipelined analog to digital conversion systems are provided having cascaded multi-bit successive approximation register subconverter stages. Capacitor arrays are provided in the subconverter stages, where switching logic selectively couples the capacitors to operate in sample, conversion, and residue amplification modes for generating multi-bit subconverter digital outputs and analog subconverter residue outputs. In one implementation, the capacitors are switched according to a thermometer code to reduce differential converter non-linearity, and the first subconverter stage gain is reduced to improve the conversion system bandwidth.

Owner:TEXAS INSTR INC

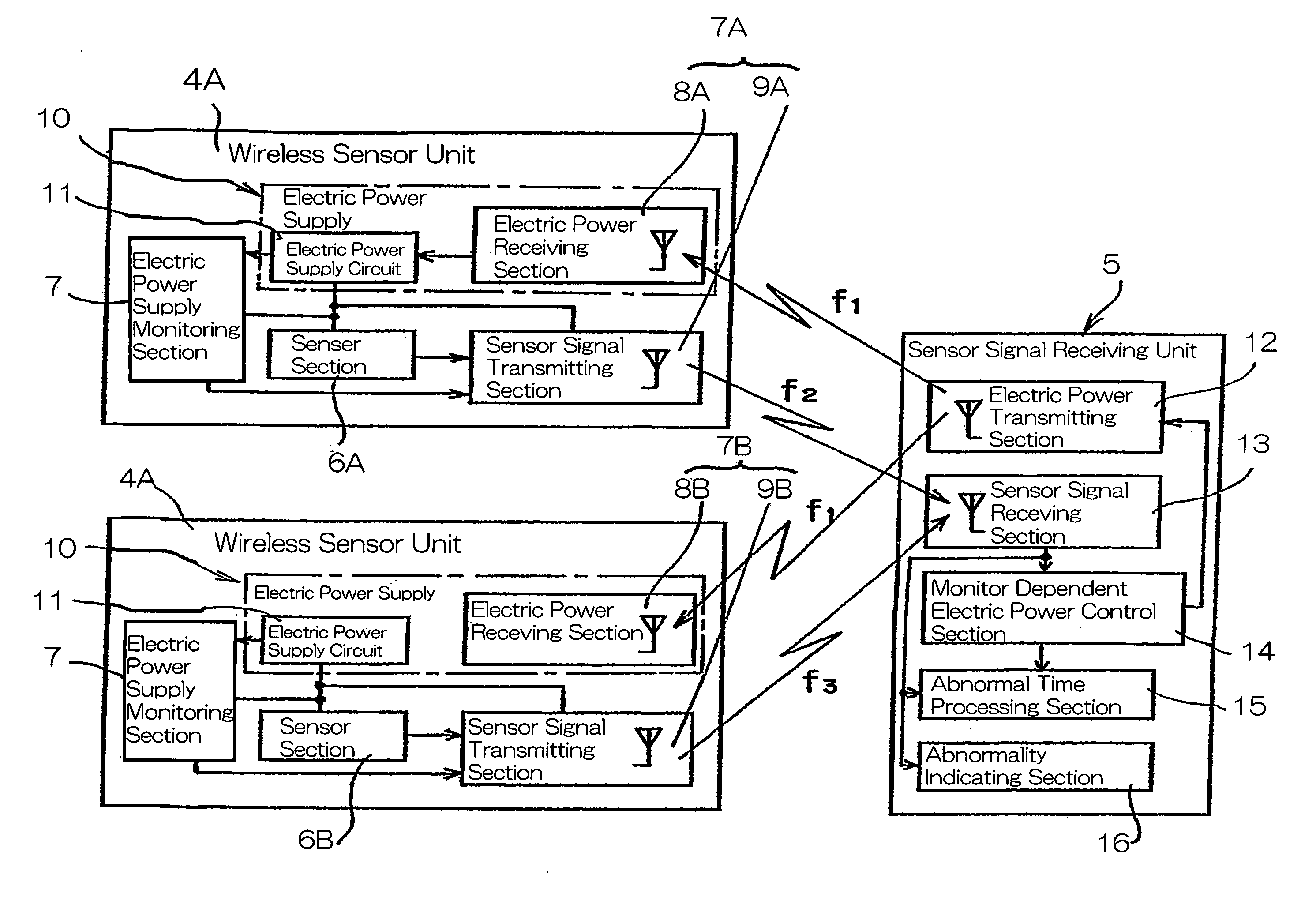

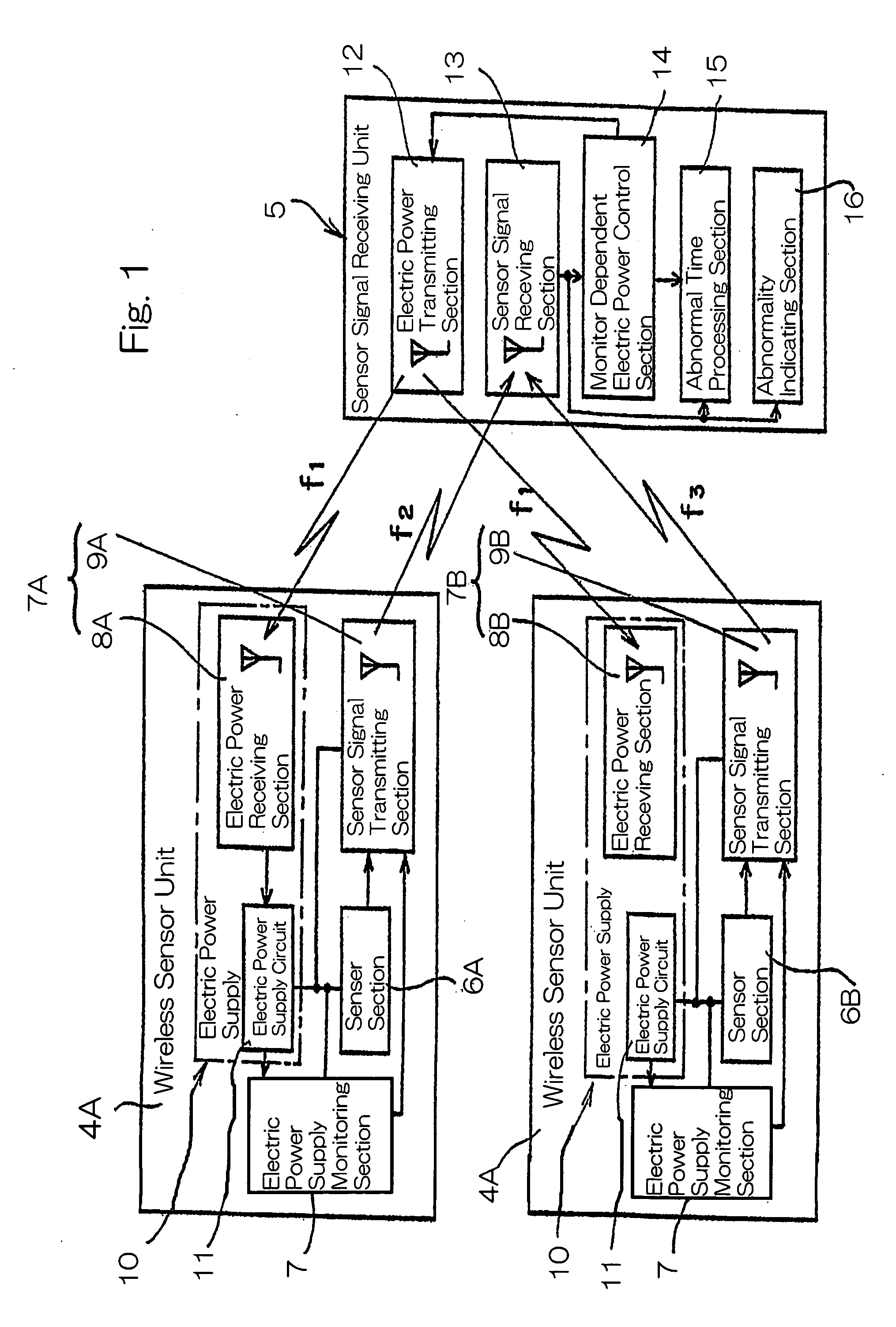

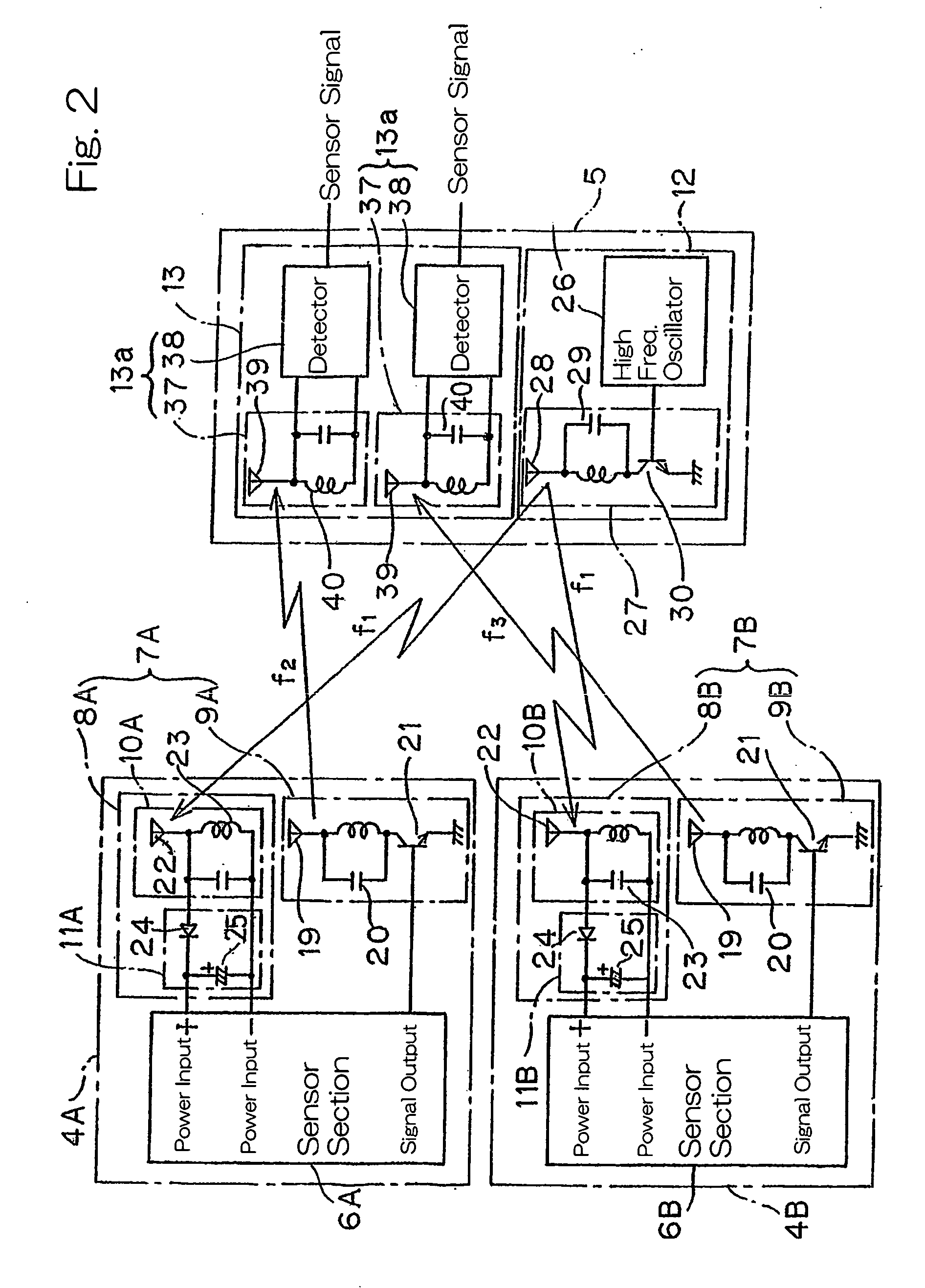

Wireless sensor system, and bearing apparatus with wireless sensor

InactiveUS20070018837A1Reduce electric powerReduce power consumptionBearing assemblyTransmission systemsPower controlLine sensor

Owner:NTN CORP

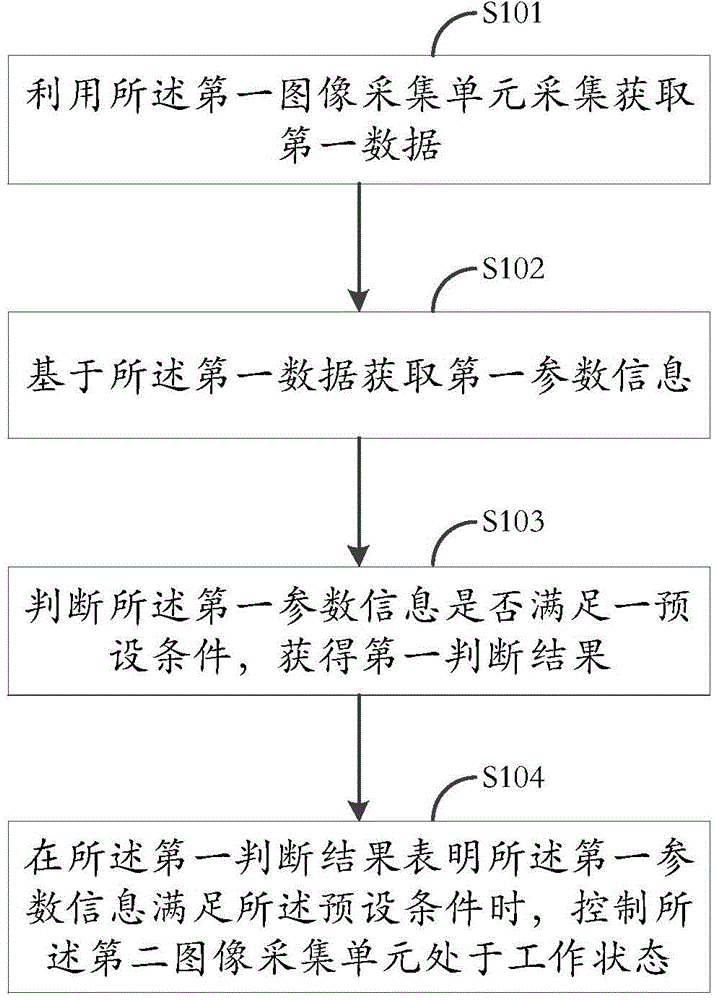

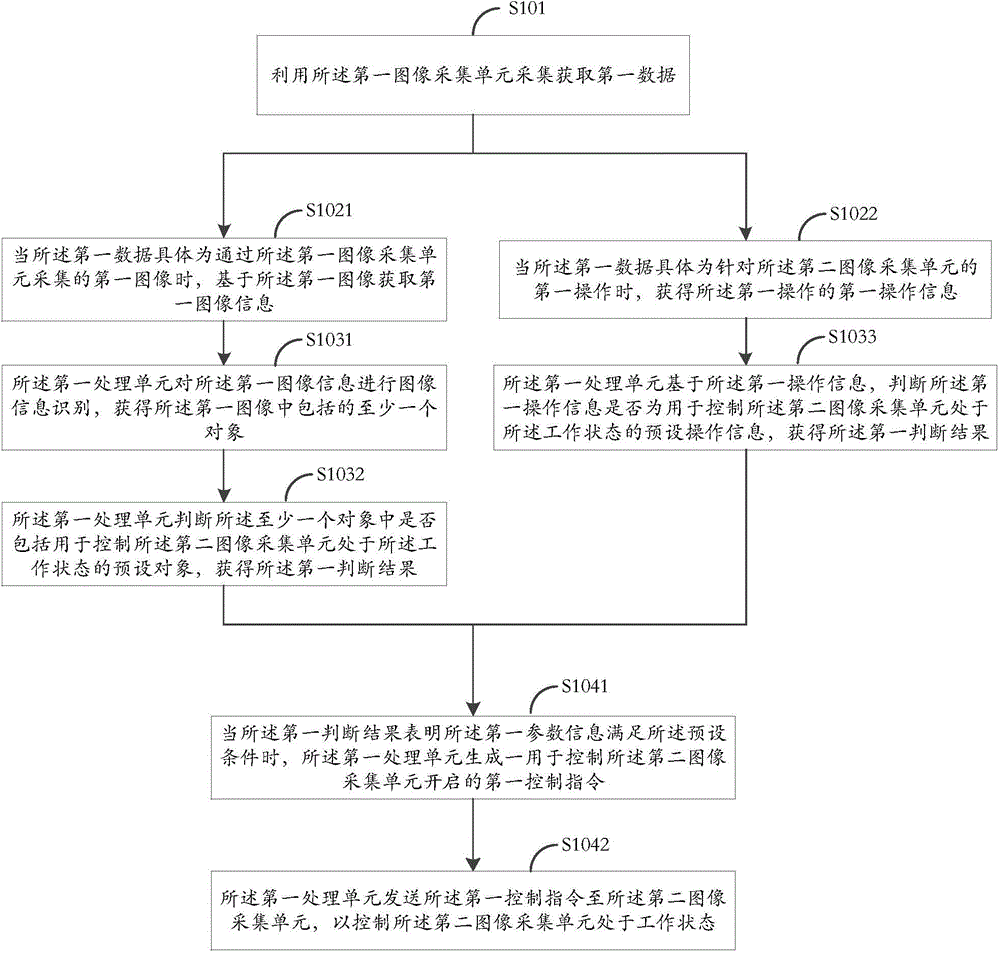

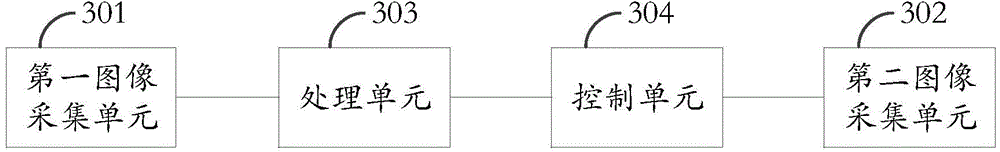

An information processing method and electronic device

ActiveCN104410785AReduce power consumptionIncrease power consumptionTelevision system detailsColor television detailsReal-time computingPower consumption

The invention discloses an information processing method, which is applied to an electronic device, said electronic device comprising at least a first image collecting unit and a second image collecting unit, wherein the first image collecting unit has a first power consumption lower than a second power consumption of the second image collecting unit; said method comprising: collecting a first data by the first image collection unit; obtaining first parameter information based on the first data; determining whether the first parameter information satisfies a predetermined condition to obtain a first judgment result; and controlling the second image collection unit to be in a working state when the first judgment result shows that the first parameter information satisfies the predetermined condition. The method provided in the invention solves a technical problem that in the prior art, the electronic device occupies much more system resource when using a camera and thus the power consumption of the electronic device is increased, and the method achieves a technical effect of saving system resources.

Owner:LENOVO (BEIJING) CO LTD

Pipelined analog-digital converter

InactiveCN101552609AReduce power consumptionAnalogue-digital convertersDigital down converterAudio power amplifier

The present invention relates to a pipelined analog-digital converter, including a plurality of sub pipelined stages for implementing analog-to-digital conversion and allowance amplification to input analog signals; a time-delay synchronization register for implementing time-delay alignment to output digital codes from each pipelined stage; a digital correction module for receiving output digital codes from the synchronization register, and implementing bit shift addition to the output digital codes to obtain digital output codes of the analog-digital converter; a dynamic bias circuit for adjusting the bias level of the operational amplifier of each sub pipelined stage according to the frequency of sampling clocks to each sub pipelines stage; and a built-in band-gap reference source circuit for generating a reference voltage source of the dynamic bias circuit, thus the ''excess'' of the operational amplifier quantity for meeting the built-up time of a highest sampling frequency may be avoided, and an amplifying power will be reduced accordingly relative to a lower sampling frequency, thereby the power consumption of the analog-digital converter will be saved integrally.

Owner:SUZHOU TONGCHUANG WEIXIN CO LTD

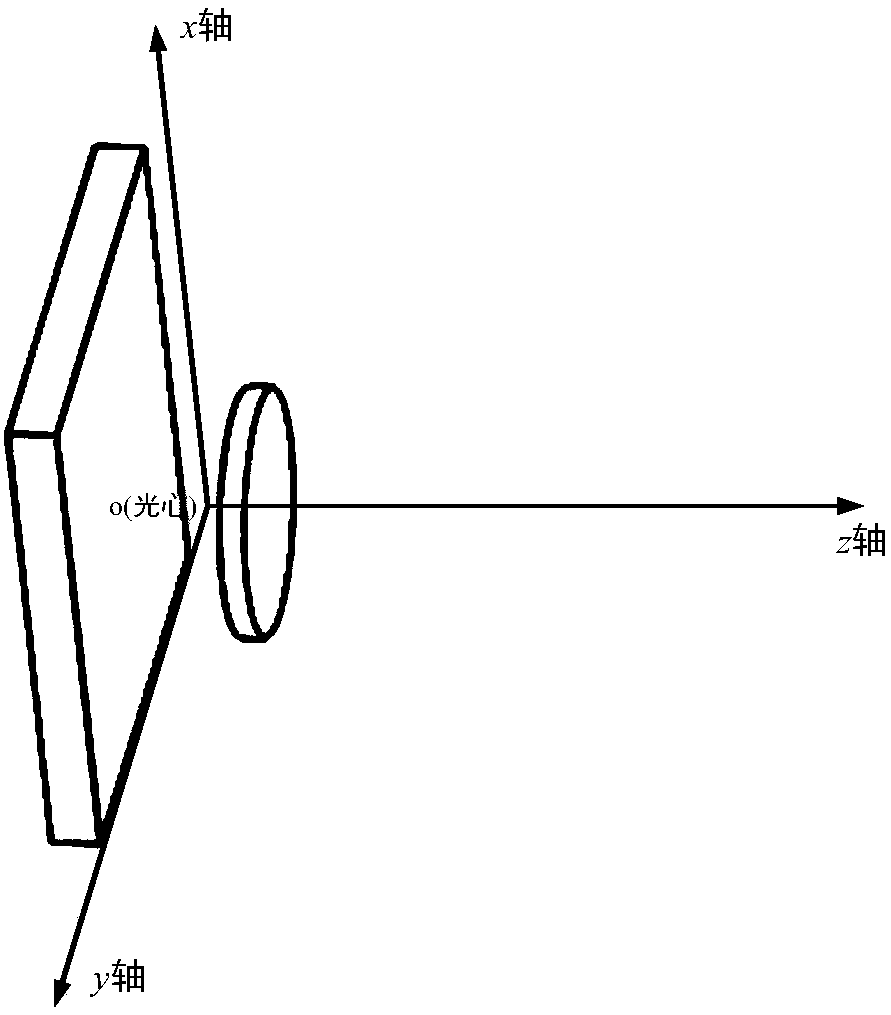

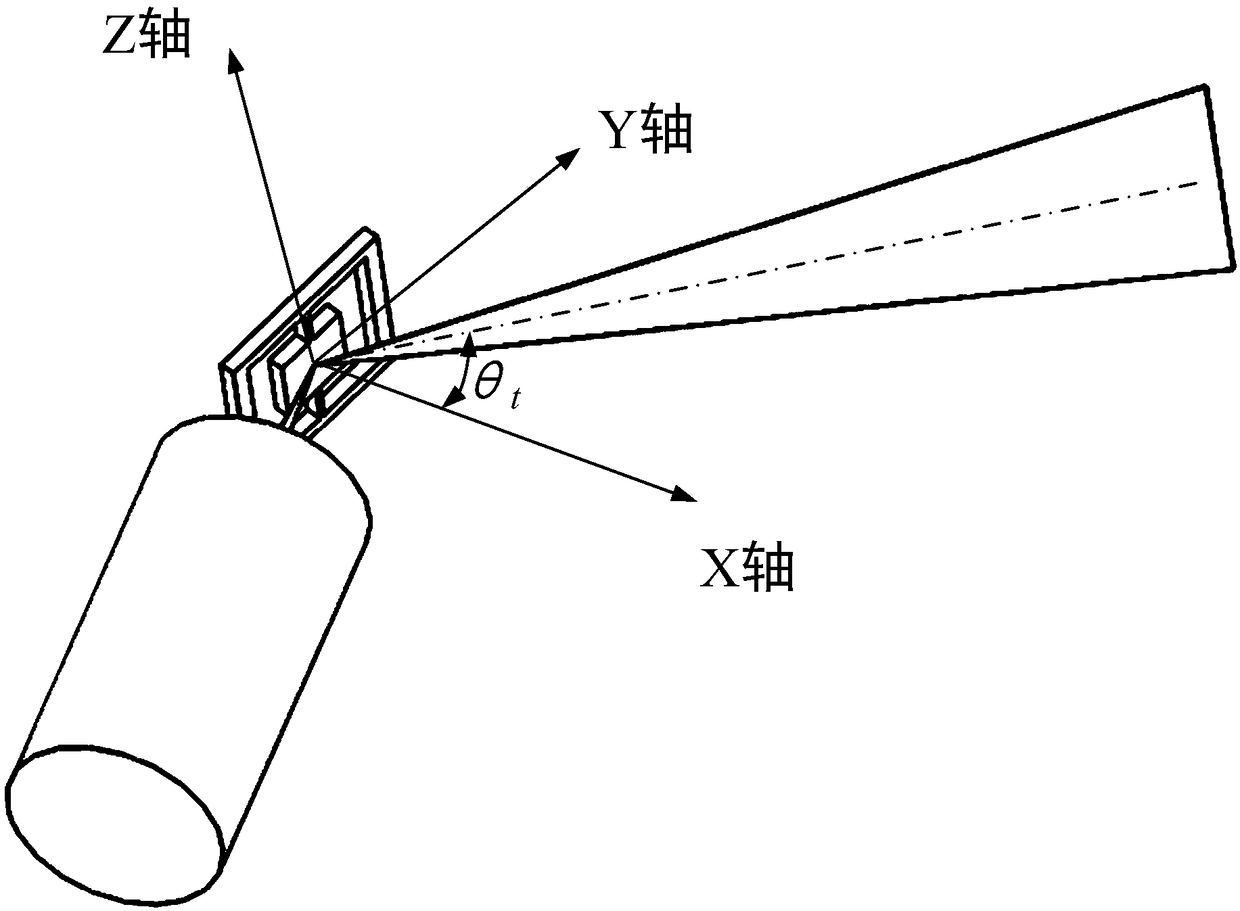

Laser line scanning 3D detection method and system based on scanning galvanometer and event camera

ActiveCN109458928ASimple algorithmSmall amount of calculationUsing optical meansGalvanometerLaser scanning

The invention belongs to the field of 3D detection and measurement, and particularly relates to a laser line scanning 3D detection method and system based on a scanning galvanometer and an event camera. The method comprises the following steps: the laser line is reflected to an object to be detected by the scanning galvanometer, so that laser line scanning is achieved; the event camera is adoptedto collect laser line signal information reflected from the object to be measured, and pixel points with changed brightness on the object to be measured and corresponding time points are stored and output; the position coordinate of the space point of the object to be detected scanned by the laser line at the moment is calculated through the relative position between the scanning galvanometer andthe event camera, the pixel point output in the step 2 and the scanning galvanometer rotation angle corresponding to the moment point corresponding to the pixel point; the steps are repeated to complete all space point coordinates of the object to be measured so as to obtain 3D point cloud data of the object to be measured, thereby solving the limitations of frame rate, resolution and illuminationresistance in the current 3D scheme.

Owner:XI AN ZHISENSOR TECH CO LTD

Signal processing unit

ActiveUS20120274356A1Reduce power consumptionNon-destructive readPower reduction in field effect transistorsSolid-state devicesNon destructiveData storing

A signal processing unit with reduced power consumption is provided. A transistor in which a channel is formed in an oxide semiconductor is used for a storage circuit included in the signal processing unit, so that data can be held (stored) even while supply of power is stopped. Non-destructive reading can be performed on the data stored in the storage circuit even when supply of power to the signal processing unit is stopped.

Owner:SEMICON ENERGY LAB CO LTD

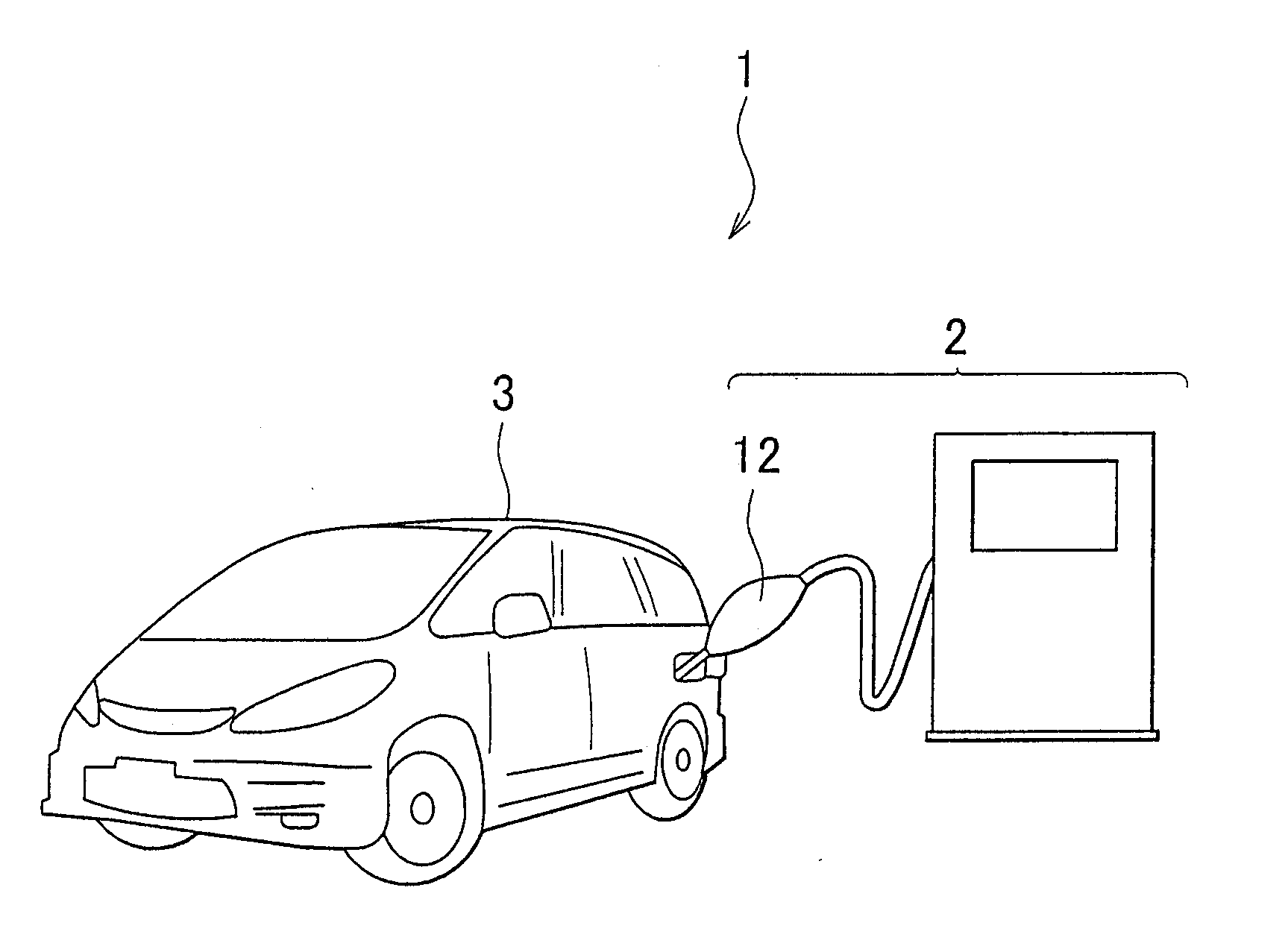

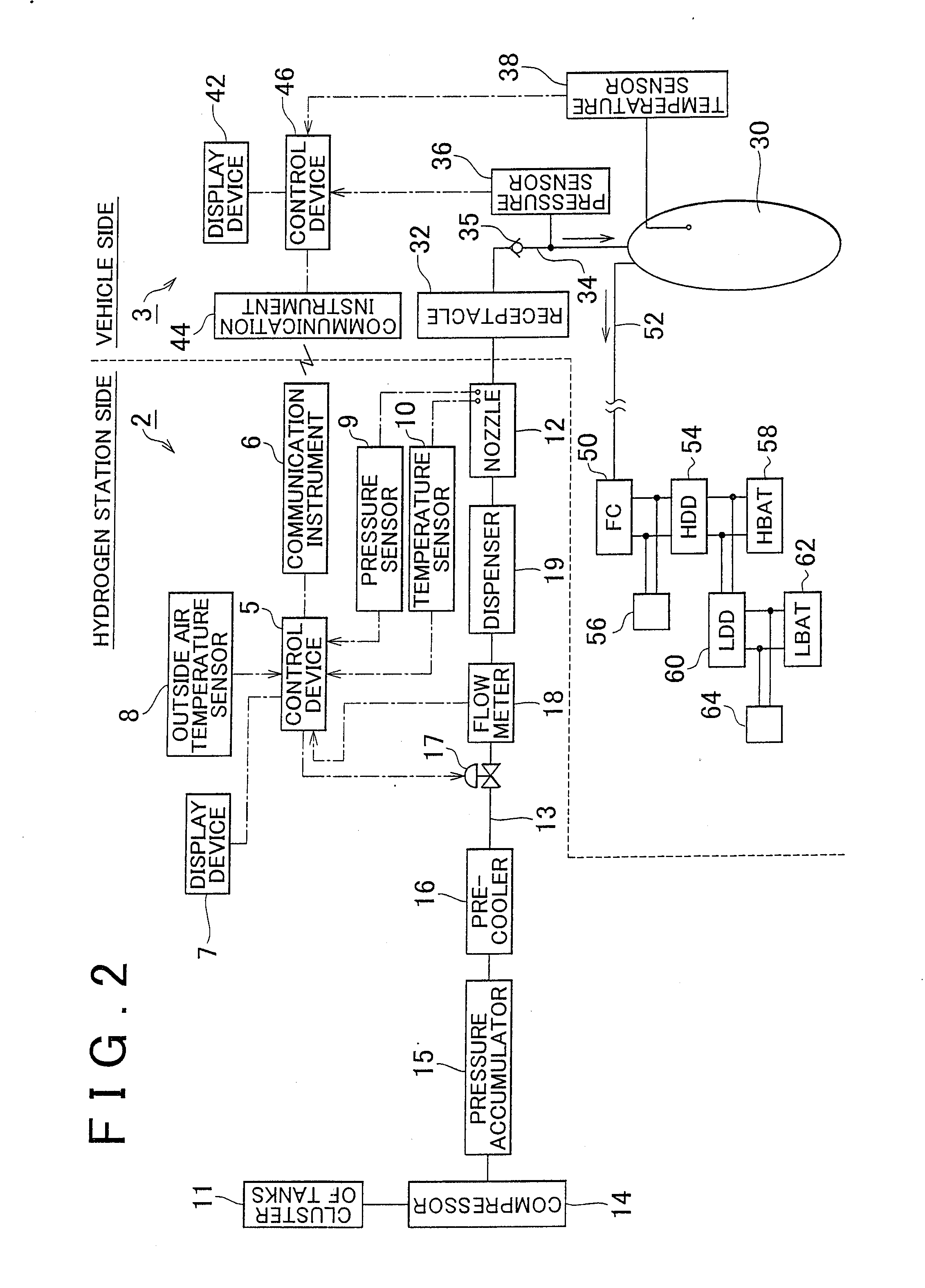

Gas filling system, and vehicle

ActiveUS20120298256A1Reduce power consumptionLiquid fillingGas handling applicationsAutomotive engineeringControl equipment

A vehicle includes: a fuel tank into which gas is filled from a gas station that has a receiver; a transmitter; and a control device connected to the transmitter. The control device changes a transmission cycle of a signal transmitted from the transmitter to the receiver during the gas filling from the gas station into the fuel tank, according to a state quantity regarding an interior of the fuel tank.

Owner:TOYOTA JIDOSHA KK

Receiver with discrete-time filtering and down-conversion

InactiveUS20090161801A1Moderate influenceReduce power consumptionAmplitude-modulated carrier systemsClock signalDiscrete time filtering

Owner:IND TECH RES INST

Embedded Internet of things gateway-based agricultural greenhouse indoor environment monitoring system

ActiveCN105610900AEasy to monitorEffective monitoringTransmissionSimultaneous control of multiple variablesIot gatewayWeb service

The invention relates to an embedded Internet of things gateway-based agricultural greenhouse indoor environment monitoring system. The system is characterized in that the system includes a user end, a web server, an embedded type Internet of things gateway, a plurality of environmental parameter sensors, a plurality of execution devices, a database and a power supply device; the environmental parameter sensors are arranged in an agricultural greenhouse and are used for transmitting acquired environmental parameters in the agricultural greenhouse to the embedded type Internet of things gateway through a bus control local area network or a wireless local area network; the embedded type Internet of things gateway sends received environmental parameter data to the web server through the Internet or other satellite networks; the web server processes received data and sends control instructions to the embedded type Internet of things gateway; the embedded type Internet of things gateway sends the control instructions to the execution devices in the agricultural greenhouse through the wireless local area network or the bus control local area network, so that the execution devices can act; and the power supply device is used for supplying power for all electric devices.

Owner:FRUIT TREE INST OF CHINESE ACAD OF AGRI SCI +1

Global navigation satellite system receiver and method of operation

InactiveUS20090109091A1Prolong battery lifeReduce power consumptionBeacon systems using radio wavesNavigational calculation instrumentsEnvironmental geologyMarine navigation

Owner:SAMSUNG ELECTRONICS CO LTD

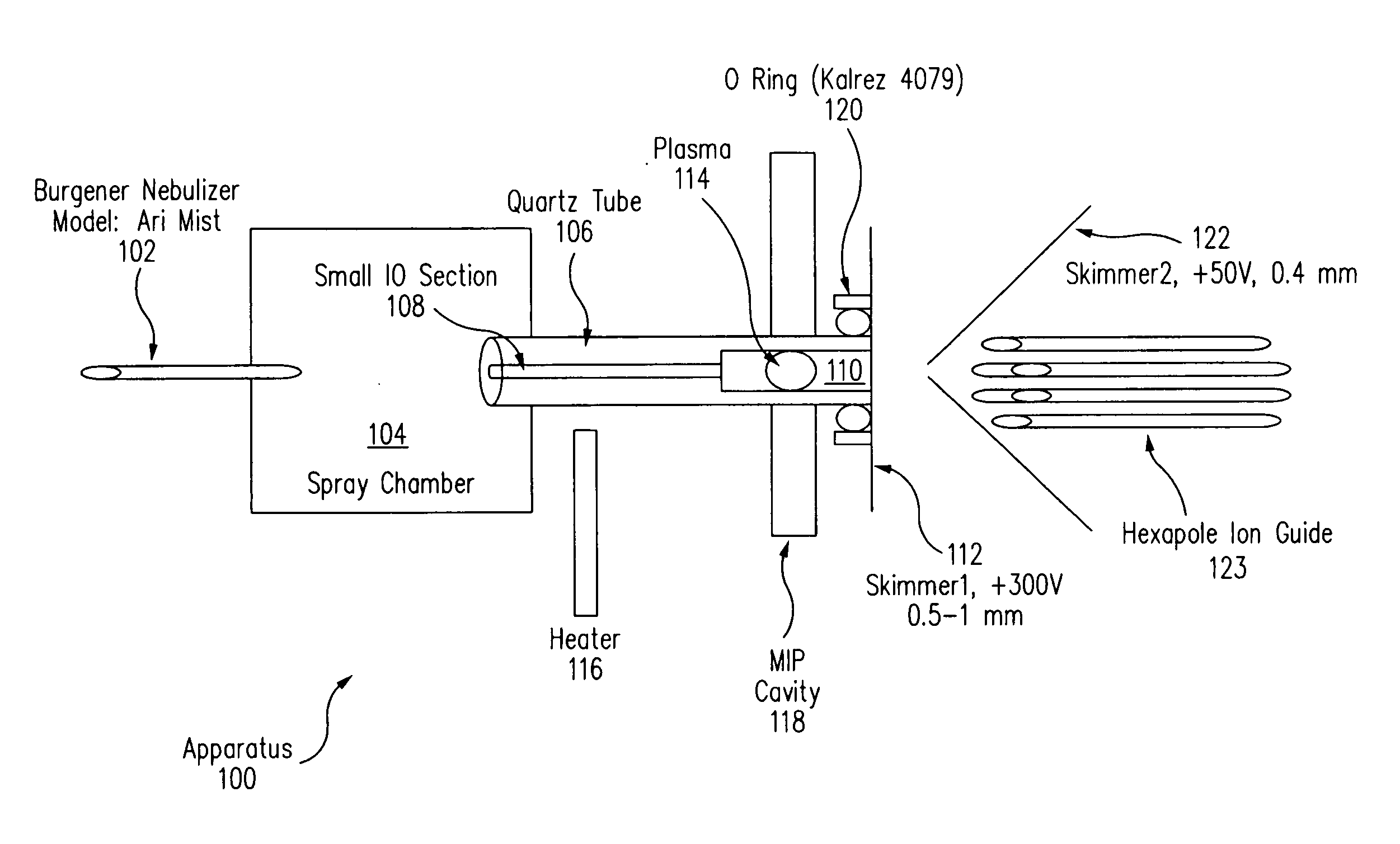

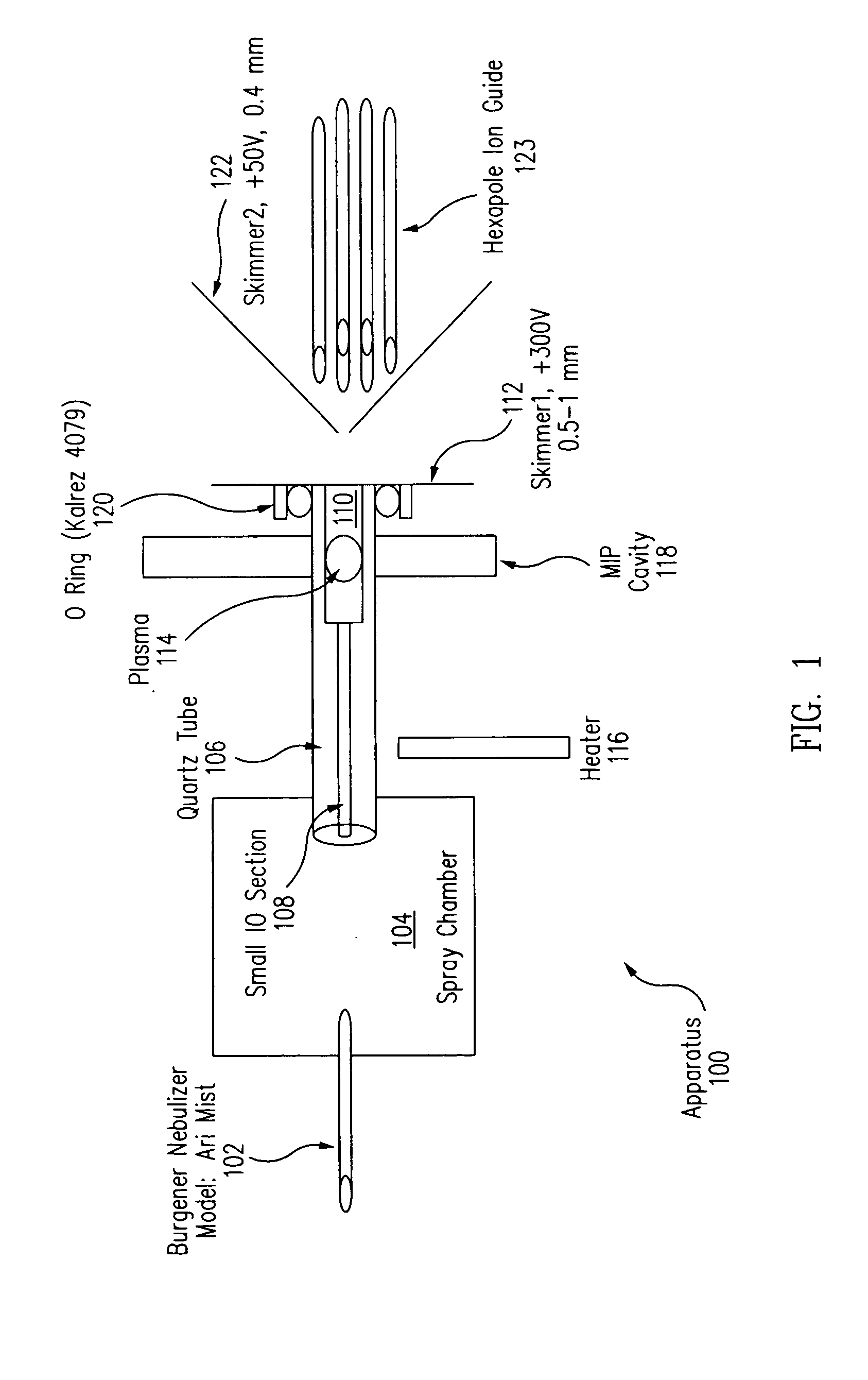

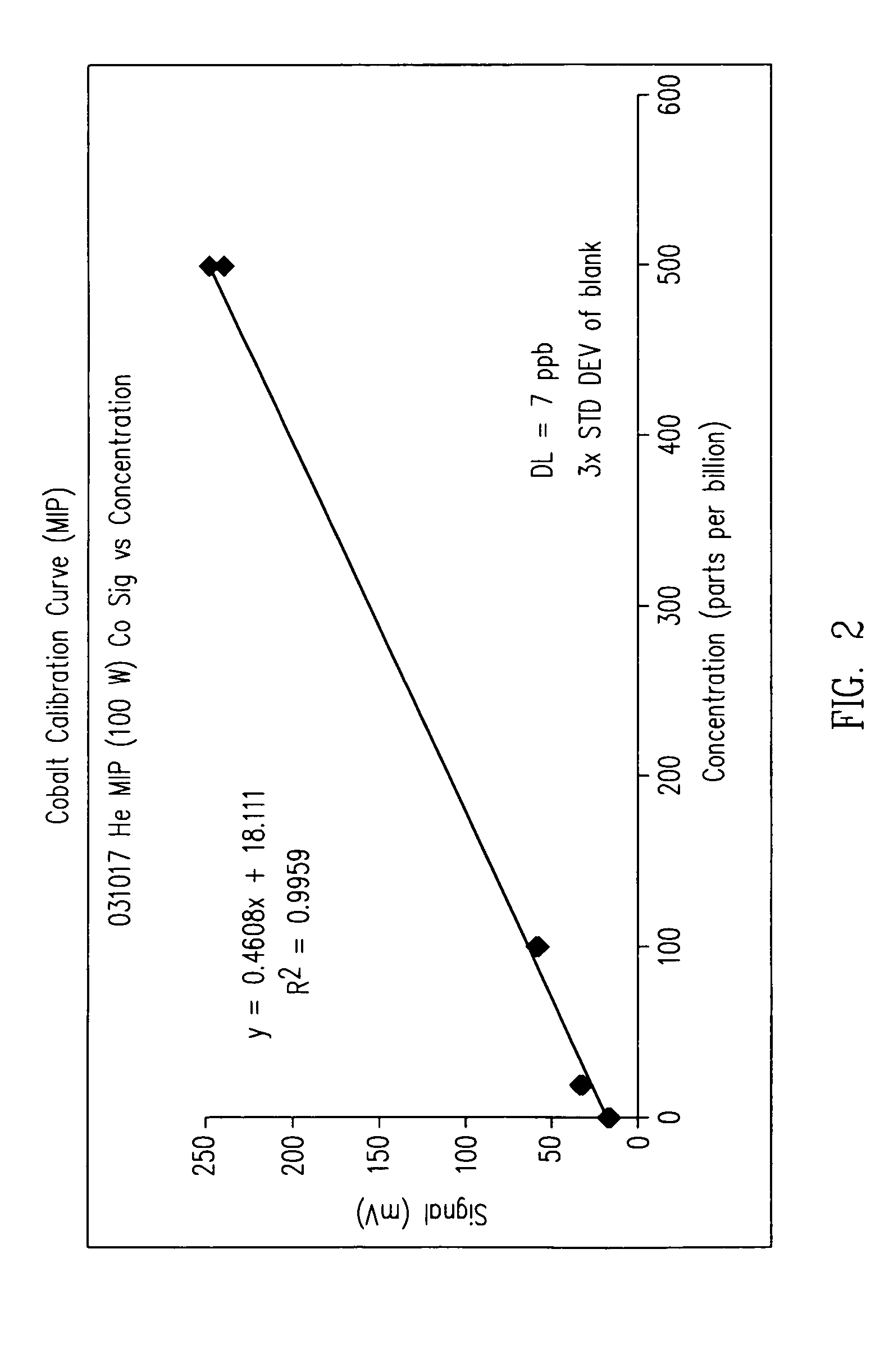

Nebulizer with plasma source

InactiveUS20050173628A1Small sizeReduce power consumptionStability-of-path spectrometersTime-of-flight spectrometersIonizationPhysics

Owner:METARA

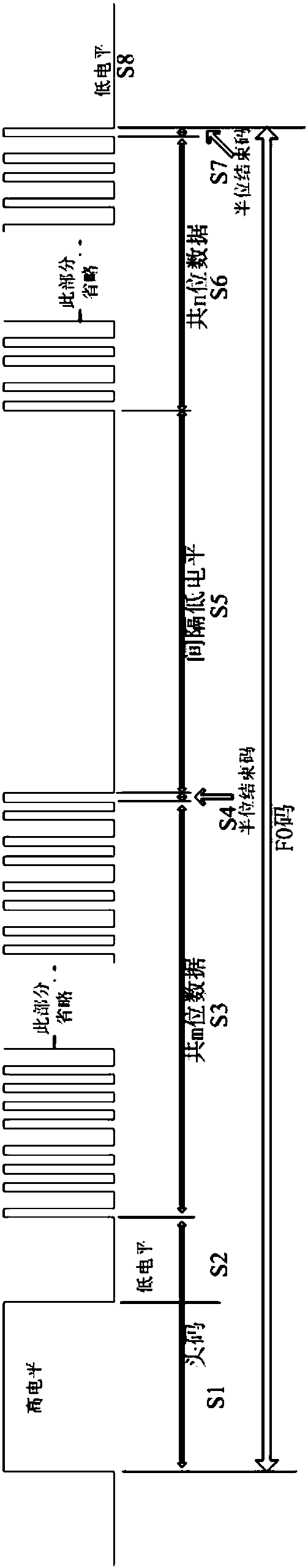

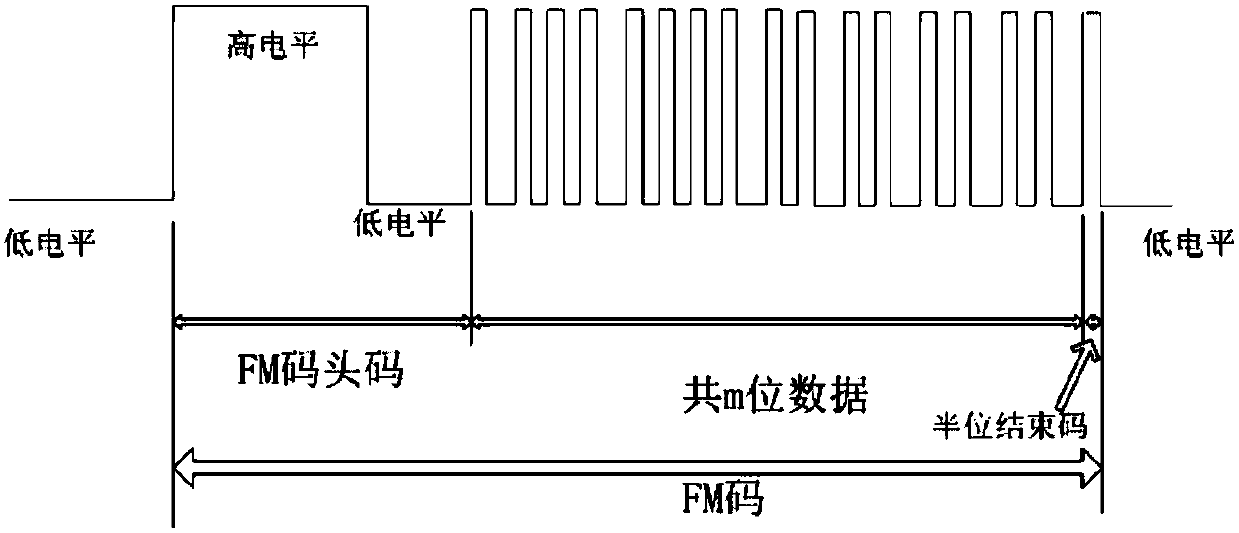

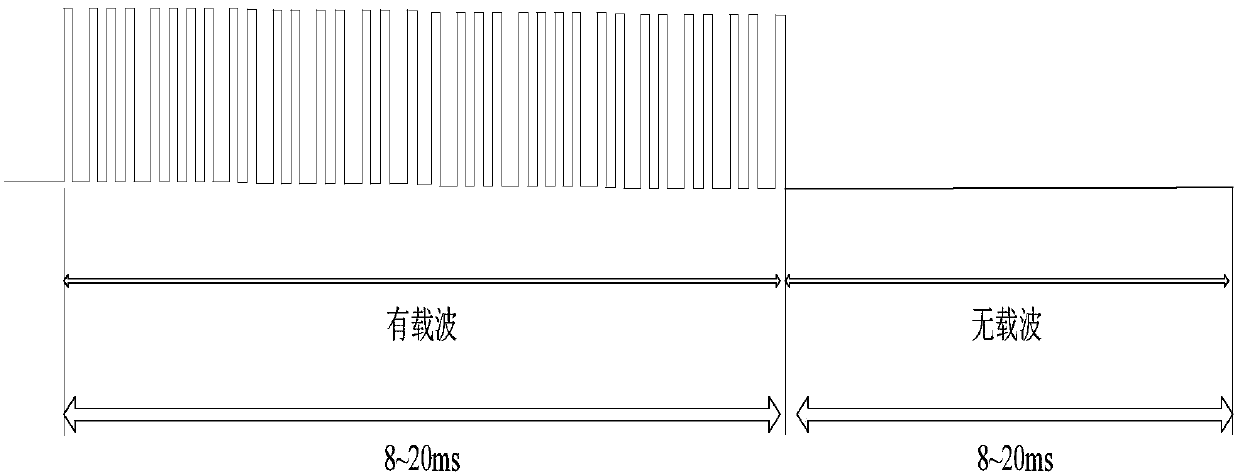

Infrared protocol based infrared code transmitting circuit, chip, remote controller and air conditioner

ActiveCN109859454AReduce power consumptionReduce programming difficultyClose-range type systemsNon-electrical signal transmission systemsCarrier signalComputer module

Owner:GREE ELECTRIC APPLIANCES INC OF ZHUHAI

DLL circuit

InactiveUS7020228B2Reduce power consumptionPulse automatic controlDigital storageDelay-locked loopPhase relationship

A DLL (delay locked loop) circuit for outputting a phase lock signal having a predetermined phase relationship with an input signal. The DLL circuit has: a functional block having a constant-current source; and bias generator for generating a constant current source bias signal for controlling the constant current source of the functional block, the bias generator comprising a bias control which changes the bias signal according to the frequency of the input signal.

Owner:LONGITUDE SEMICON S A R L

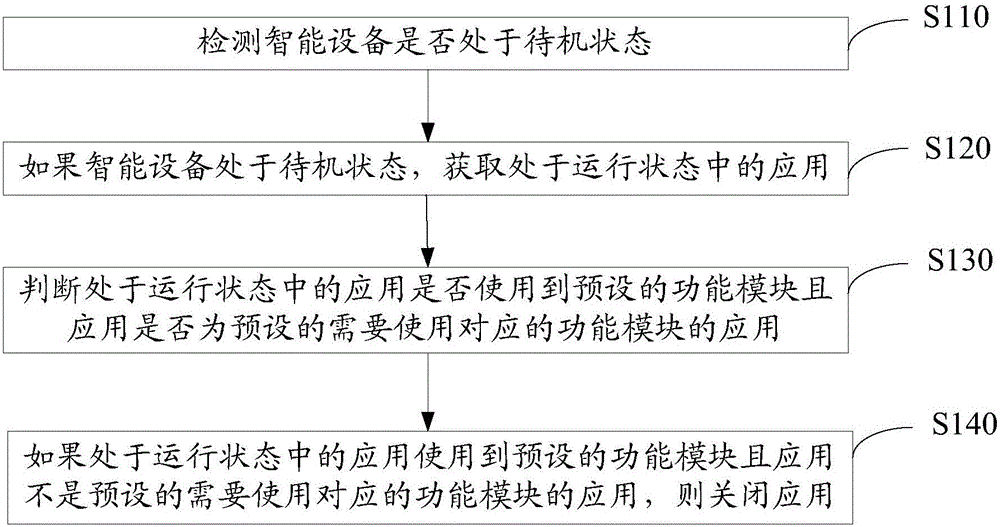

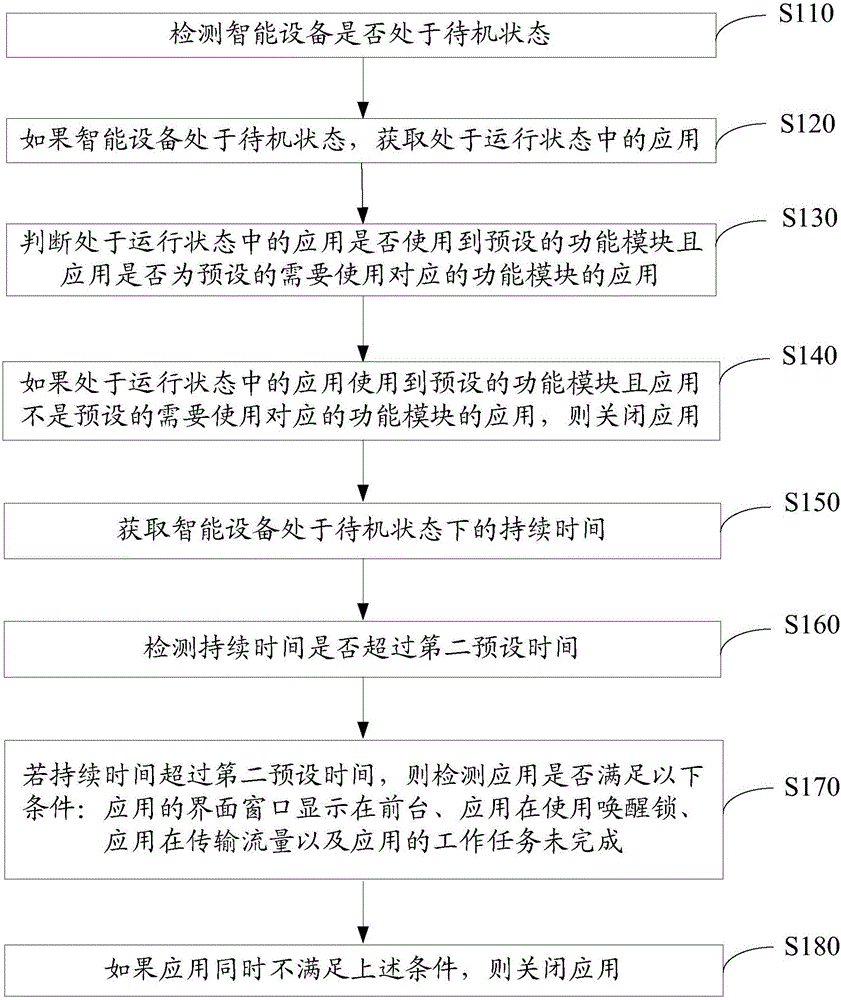

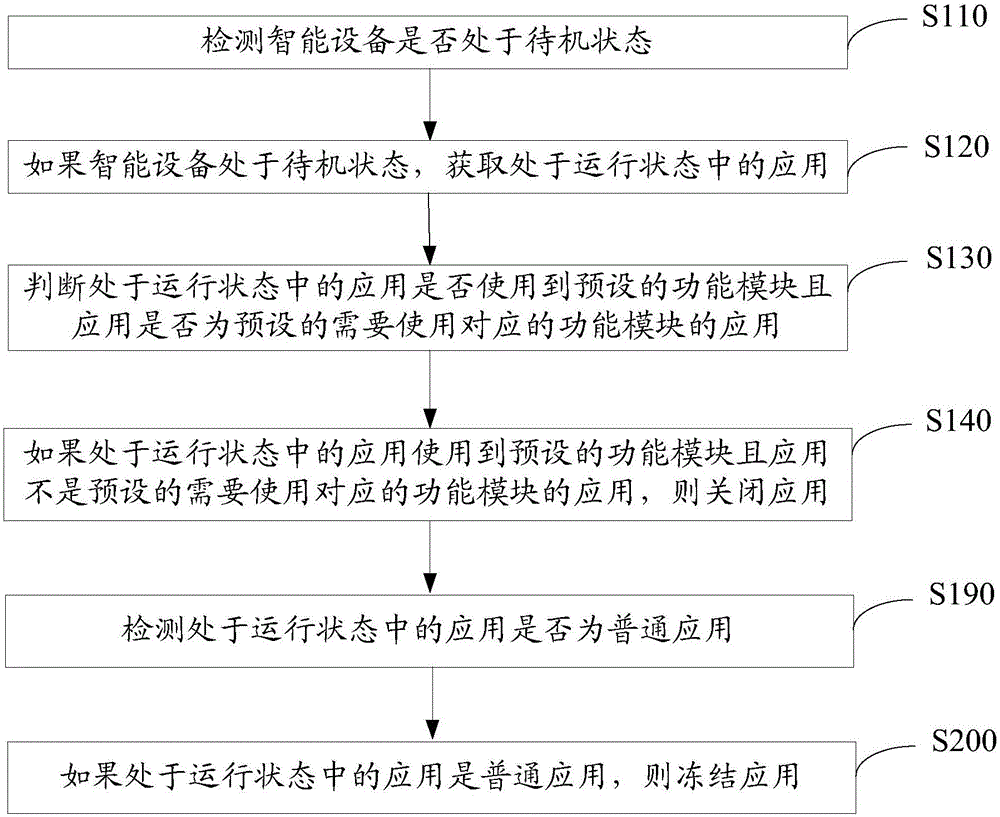

Application control method and apparatus for intelligent device in standby state

Owner:ONEPLUS TECH SHENZHEN

Cooking apparatus and method of manufacturing the same

Owner:LG ELECTRONICS INC

Neuromorphic calculation circuit based on multi-bit parallel binary synaptic array

ActiveCN110378475AReduce power consumptionReduce areaAnalogue/digital conversionElectric signal transmission systemsIntegratorHigh energy

The invention discloses a neuromorphic calculation circuit based on a multi-bit parallel binary synapse array. The neuromorphic calculation circuit comprises a neural axon module, the multi-bit parallel binary RRAM synapse array, a time division multiplexer, a plurality of integrators and a shared successive approximation analog-to-digital converter, wherein the neural axon module comprises two basic units, namely a time sequence scheduler and an adder, and the time sequence scheduler is used for arranging the time sequence of signals, so that input signals are sequentially input into a multi-bit parallel binary RRAM synapse array by adopting a dendritic priority strategy; the adder is used for expanding the array scale, and when the configured neural network input layer is greater than the input of one RRAM array, the adder is used for adding the calculation results of the plurality of arrays to obtain the output of the network layer. Compared with the current system, the method has the advantages of high precision and low power consumption, can be configured into most deep neural network applications, and is particularly suitable for being deployed in edge computing equipment with high energy consumption requirements.

Owner:ZHEJIANG UNIV

Bus controller

ActiveUS20160308452A1Reduce power consumptionAc-dc conversion without reversalBatteries circuit arrangementsBus voltageDc converter

Owner:ROHM CO LTD

Liquid crystal device, driving circuit for liquid crystal device, method of driving liquid crystal device, and electronic apparatus

ActiveUS20080238842A1Simple configurationDecrease in withstand-voltagesStatic indicating devicesDriving circuitElectronic equipment

A liquid crystal device includes a plurality of pixels disposed in the shape of a matrix of n rows×m columns (where n and m are natural numbers equal to or larger than two), n scanning lines, 2m data lines including pairs of a first data line and a second data line for each column of the plurality of pixels, and a data line driving circuit that generates a first gray scale voltage corresponding to higher bits acquired by dividing gray scale data of plural bits into the higher bits and lower bits and generates a second gray scale voltage corresponding to the lower bits. Each one of the plurality of pixels includes a first switching element and a second switching element which are controlled to be turned on or off by the common scanning lines, a first pixel electrode to which the first or second gray scale voltage is supplied from the first data line through the first switching element, and a second pixel

Owner:BOE TECH GRP CO LTD

Enhancing time keeping accuracy for low power GPS receivers

InactiveUS7535417B2Low power consumptionReduce power consumptionBeacon systemsSatellite radio beaconingClock signalEngineering

Owner:WSOU INVESTMENTS LLC

Method and apparatus for managing broadcast for portable terminal

ActiveUS20130111524A1Reduce power consumptionAnalogue secracy/subscription systemsBroadcast characteristics identification/recognitionBroadcast channelsField strength

Owner:SAMSUNG ELECTRONICS CO LTD

Interactive image system, interactive apparatus and operating method thereof

ActiveUS20090052730A1Reduce power consumptionCathode-ray tube indicatorsCharacter and pattern recognitionComputer moduleImage system

Owner:PIXART IMAGING INC

Base station in wide-band wireless access-in system and method for realizing multi-cast business

InactiveCN1852231ARealize transmissionReduce power consumptionConnection managementData switching by path configurationMulticast addressBroadband

In broadband wireless access system, base station with router and multiple user stations being connected to includes following parts: listening module in use for listening message between user station and router, or module of message proxy in use for intercepting message between user station and router; module for maintaining forwarding table of multicast address, module for executing multicast forwarding are in use for allotting an identical connection id for all user station in multicast group in order to manage adding or removed group of user station, or maintaining user data, and sending multicast data to user station. The invention also discloses relevant method. User stations in multicast group are not possible to receive multicast message by using the invention so as to reduce power consumption of user station, and raise safety. Moreover, equipment in base station does not need to carry out replication of multicast packet so as to save bandwidth resource of aerial port.

Owner:HUAWEI TECH CO LTD

Digital interface radio frequency chip and implementation method thereof

ActiveCN103209070ALow costReduce power consumptionTransmitter/receiver shaping networksSynchronising arrangementMultiplexingDigital down converter

The invention discloses a digital interface radio frequency chip and an implementation method thereof. The digital interface radio frequency chip comprises a receiving antenna, a radio frequency analog front-end subsystem and an analog baseband subsystem, wherein the analog baseband subsystem comprises an oversampling analog-to-digital converter, an internal clock generating module, a digital signal processor and a multiplexing parallel module, an output end of the receiving antenna is connected with an input end of the multiplexing parallel module through the radio frequency analog front-end subsystem, the oversampling analog-to-digital converter and the digital signal processor sequentially, and an output end of the internal clock generating module is connected with a clock input end of the oversampling analog-to-digital converter and a clock input end of the multiplexing parallel module respectively. According to the digital interface radio frequency chip, clocks generated inside the radio frequency chip serve as reference clocks, so that the correctness of the baseband chip data collection can be guaranteed; and no complex first-in first-out (FIFO) structure is required, the structure is simple, the integration is easy, and the cost and the power consumption are reduced. The digital interface radio frequency chip and the implementation method thereof are widely applied in the technical field of communications.

Owner:TOLL MICROELECTRONIC CO LTD

Mobile communication hand-off control system and unit

InactiveUS7409215B2Valid choiceReduce power consumptionCode division multiplexRadio/inductive link selection arrangementsCommunication qualityControl system

When a first base station serving a mobile communication terminal in a standby mode, a first neighbor list is acquired from the first base station and stored in a memory. If the serving base station is changed in a standby mode from the first base station to a second base station, a second neighbor list is acquired from the second base station. When the second base station is serving the mobile communication terminal in a standby mode, the communication quality between the mobile communication terminal and each second peripheral base station listed in the acquired second neighbor list, and between the terminal and each first peripheral base station listed in the stored first neighbor list. Based on the measurement results, a peripheral base station that satisfies a preset condition is selected as a hand-off destination candidate.

Owner:KK TOSHIBA

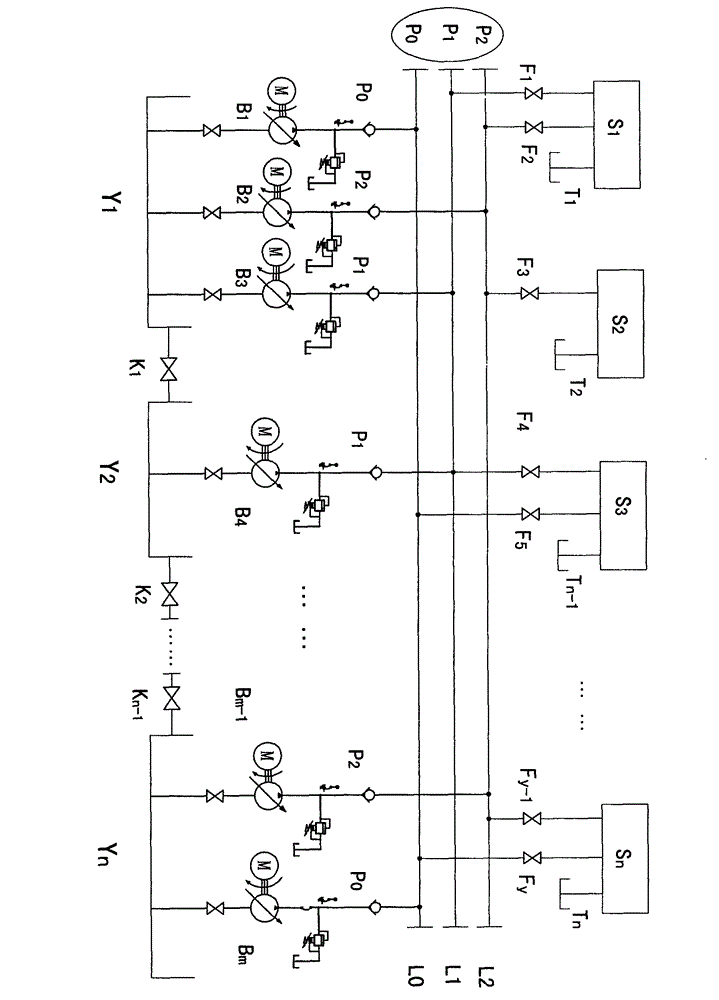

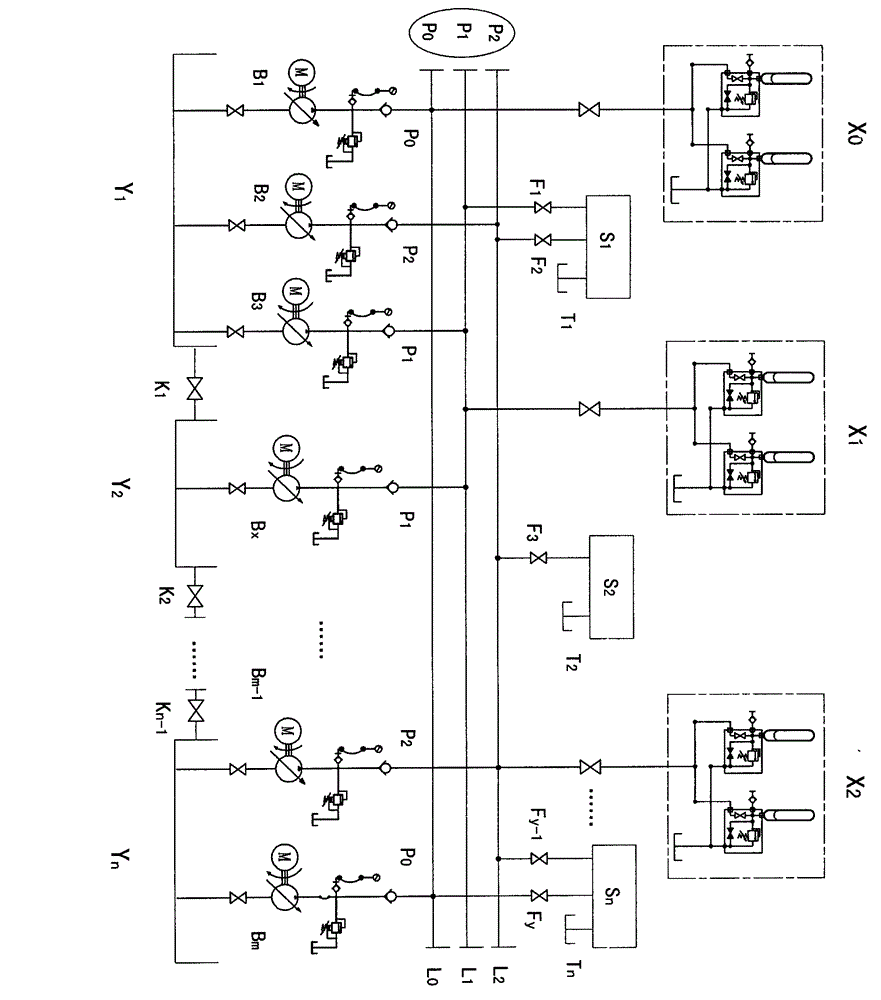

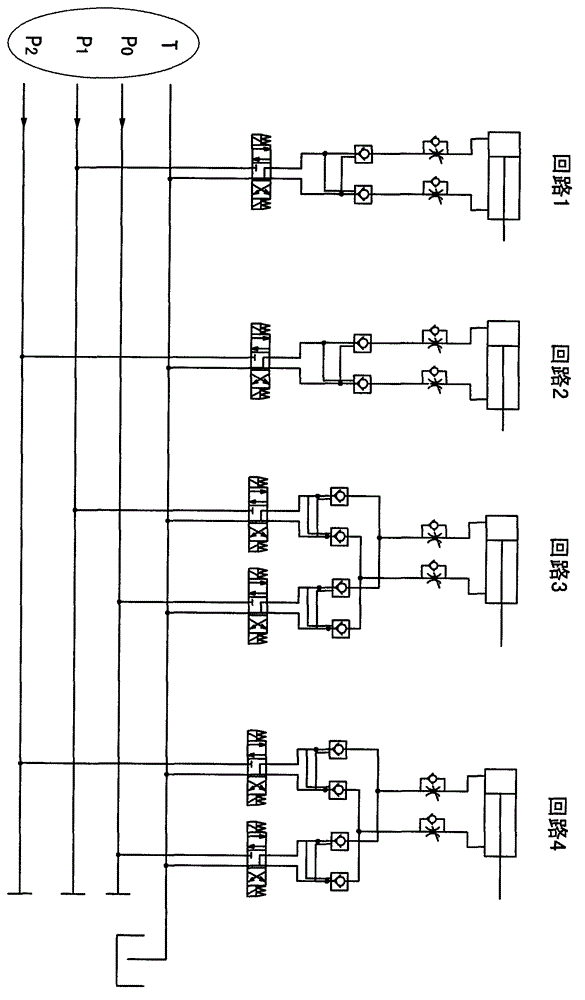

Multistation hydraulic group control energy-saving technology

InactiveCN103939399AReduce no-load power consumptionReduce power consumptionFluid-pressure actuator componentsElectric motorEnergy storage

Owner:何荣志

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap