Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30 results about "Polycrystalline silicon" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Polycrystalline silicon, also called polysilicon or poly-Si, is a high purity, polycrystalline form of silicon, used as a raw material by the solar photovoltaic and electronics industry. Polysilicon is produced from metallurgical grade silicon by a chemical purification process, called the Siemens process. This process involves distillation of volatile silicon compounds, and their decomposition into silicon at high temperatures. An emerging, alternative process of refinement uses a fluidized bed reactor. The photovoltaic industry also produces upgraded metallurgical-grade silicon (UMG-Si), using metallurgical instead of chemical purification processes. When produced for the electronics industry, polysilicon contains impurity levels of less than one part per billion (ppb), while polycrystalline solar grade silicon (SoG-Si) is generally less pure. A few companies from China, Germany, Japan, Korea and the United States, such as GCL-Poly, Wacker Chemie, OCI, and Hemlock Semiconductor, as well as the Norwegian headquartered REC, accounted for most of the worldwide production of about 230,000 tonnes in 2013.

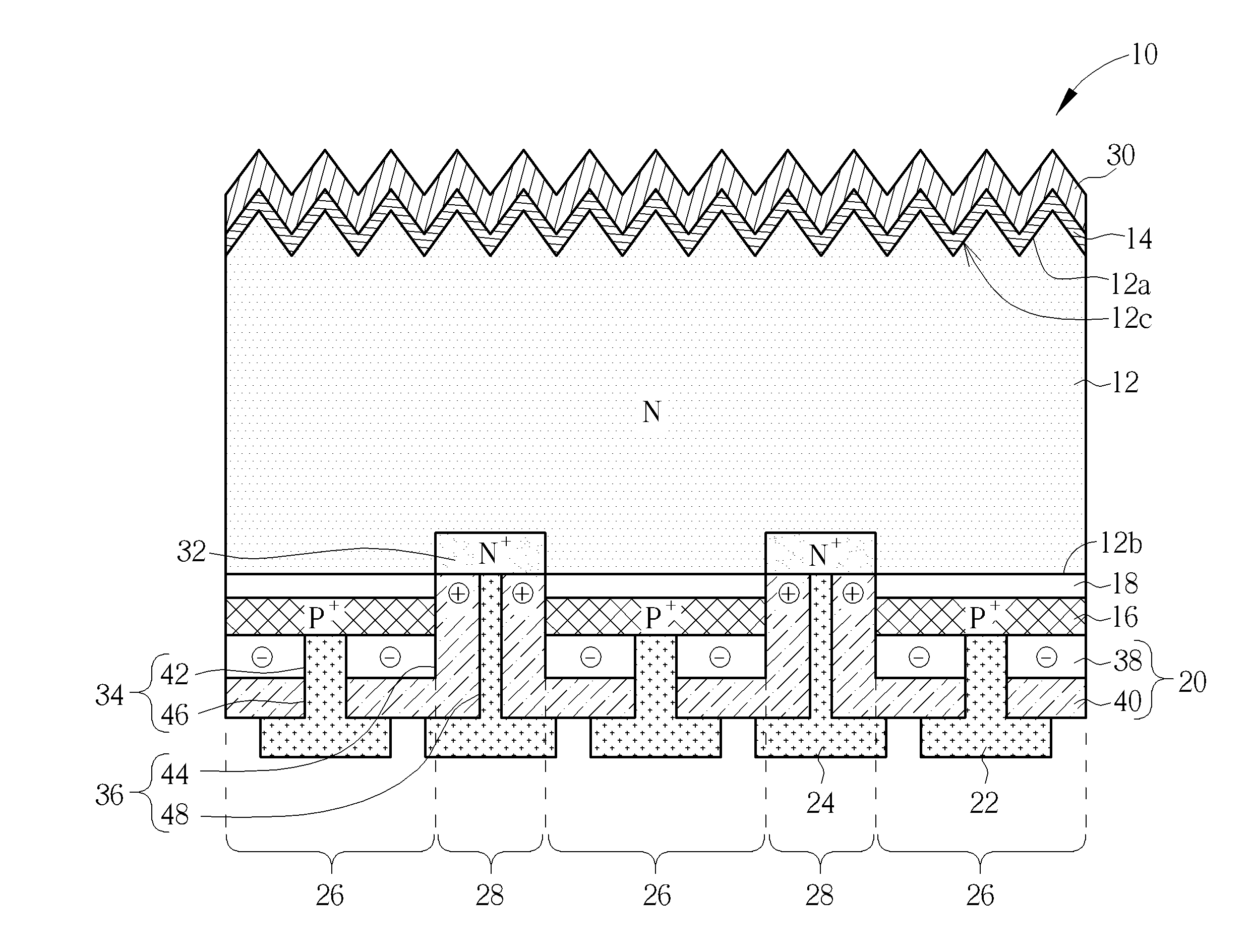

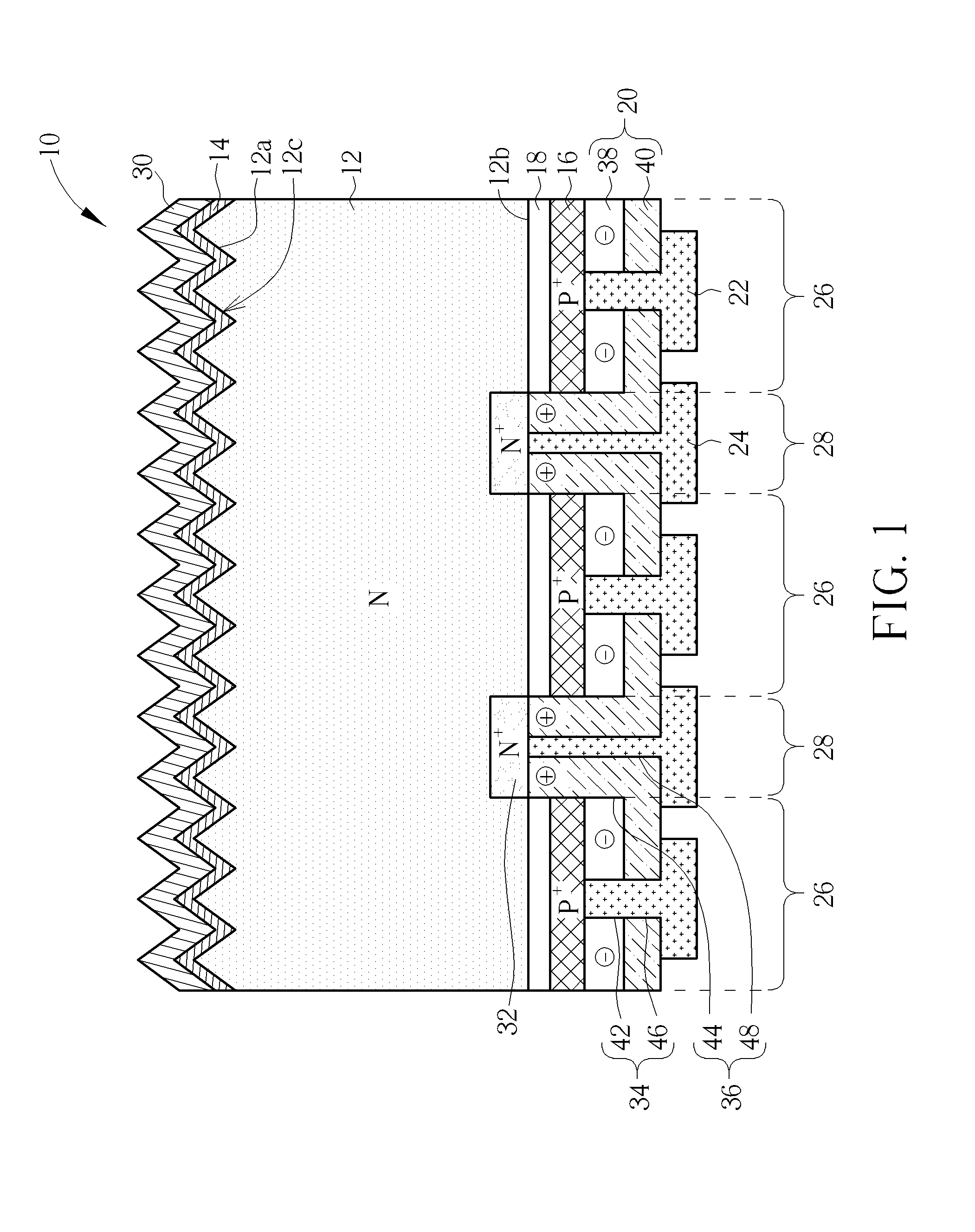

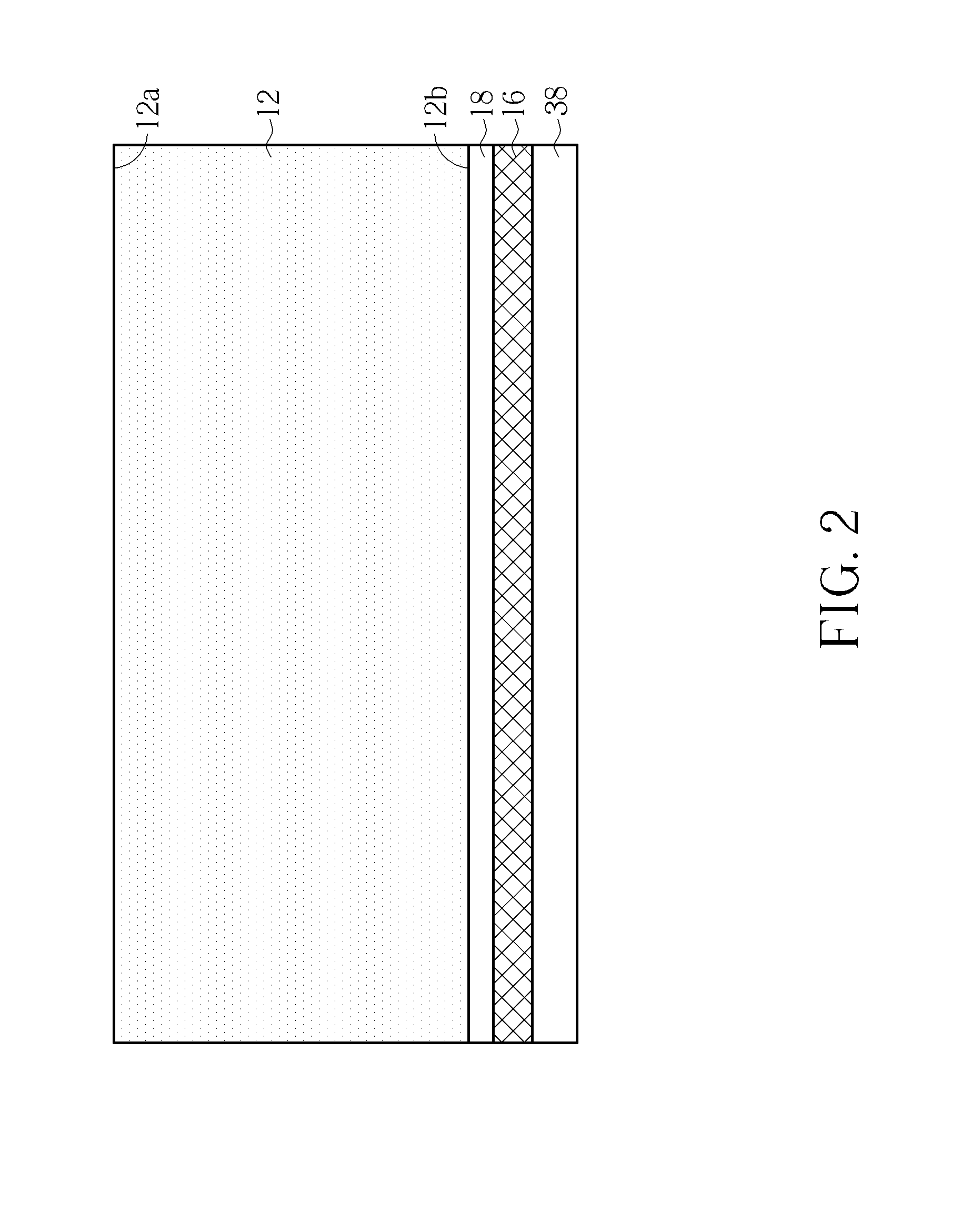

Solar cell and method for making thereof

ActiveUS20140096821A1Reduce generationImprove photoelectric conversion efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingSolar cellSemiconductor

Owner:AU OPTRONICS CORP

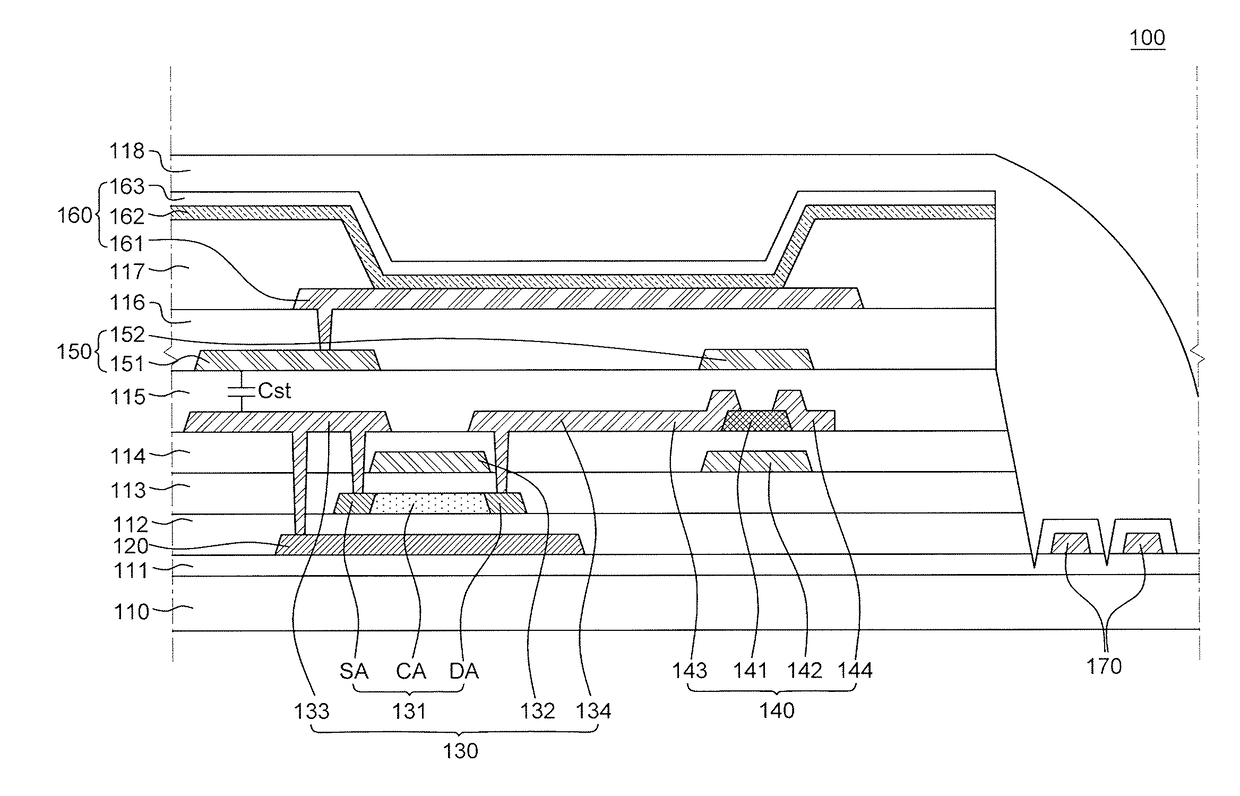

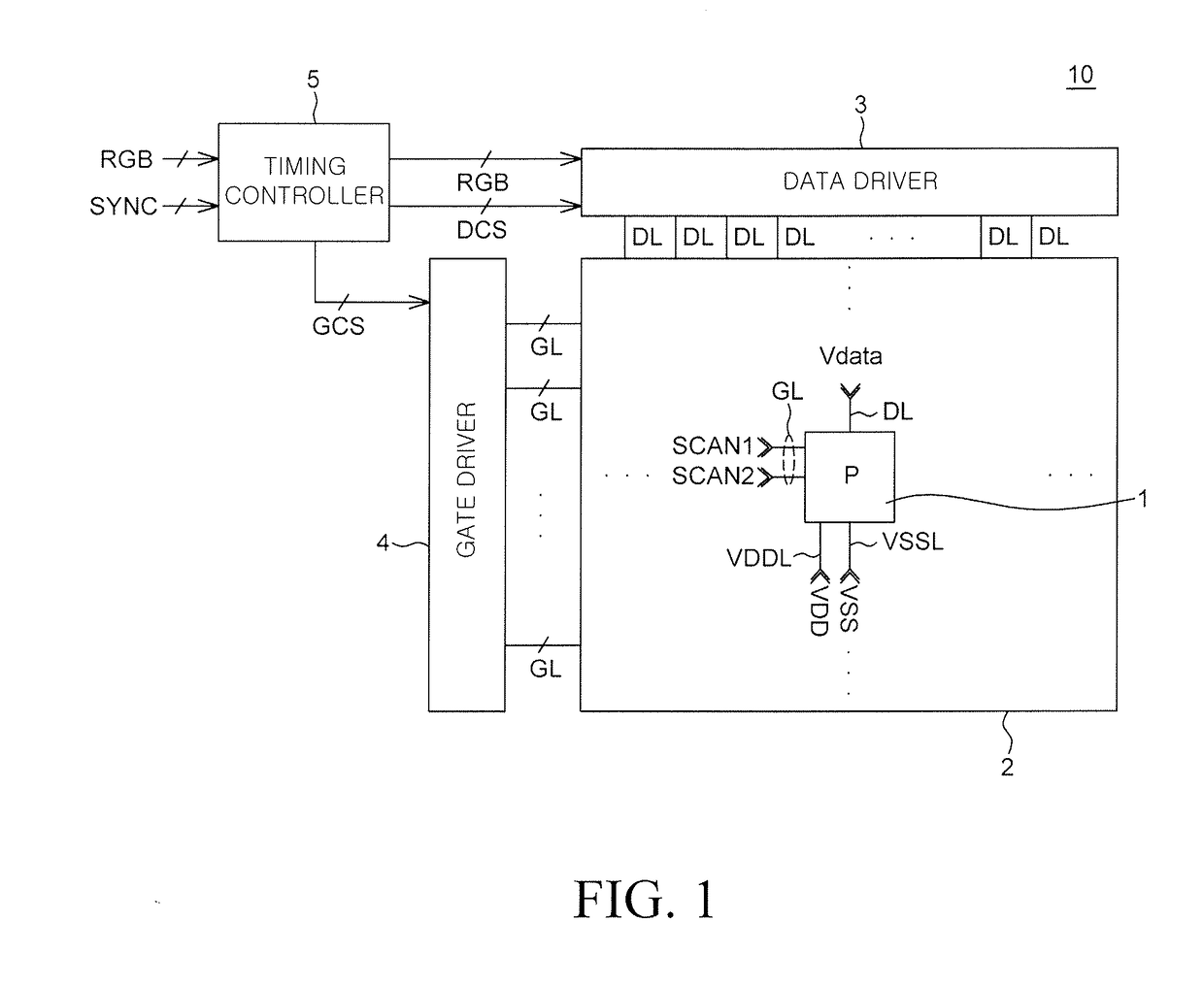

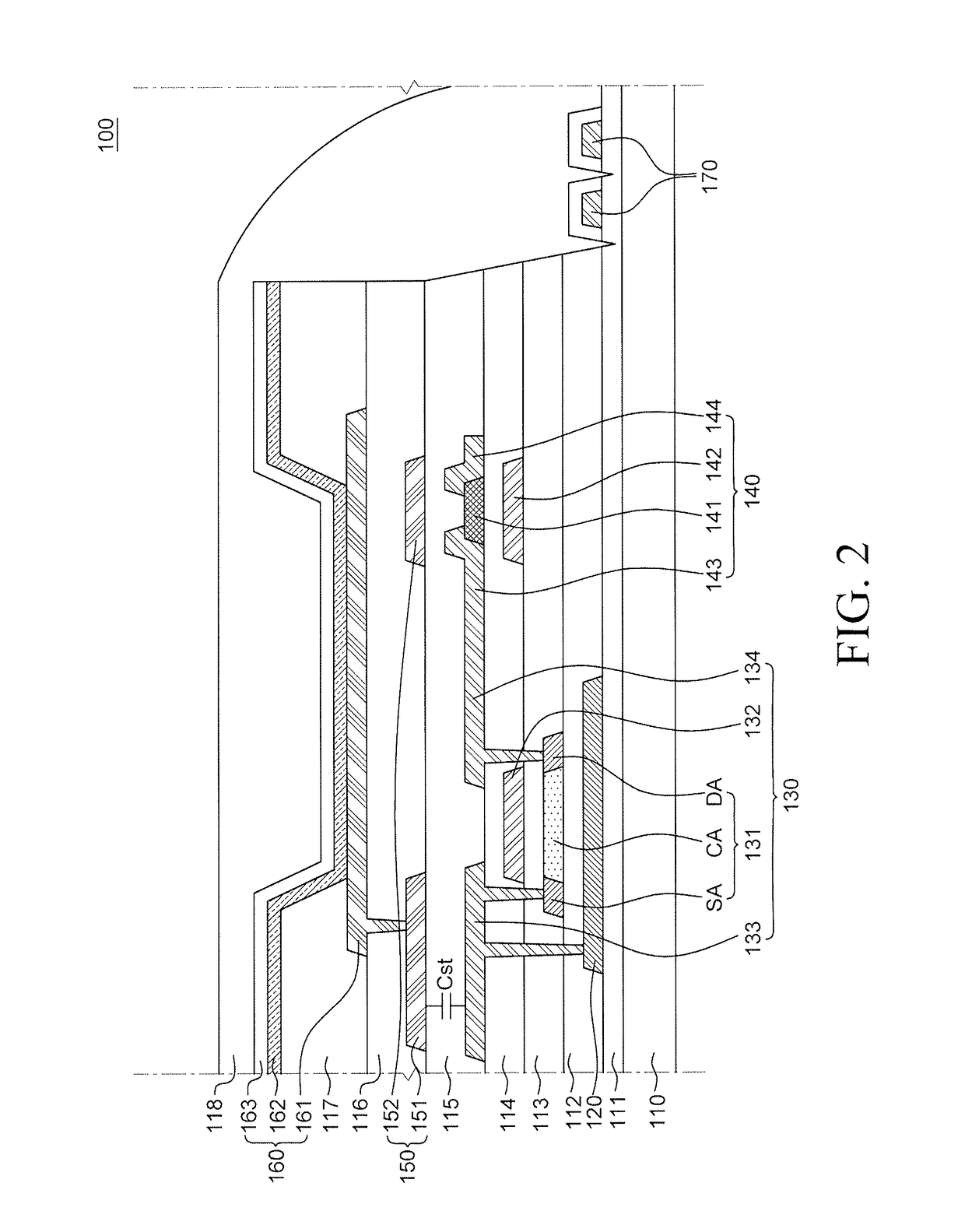

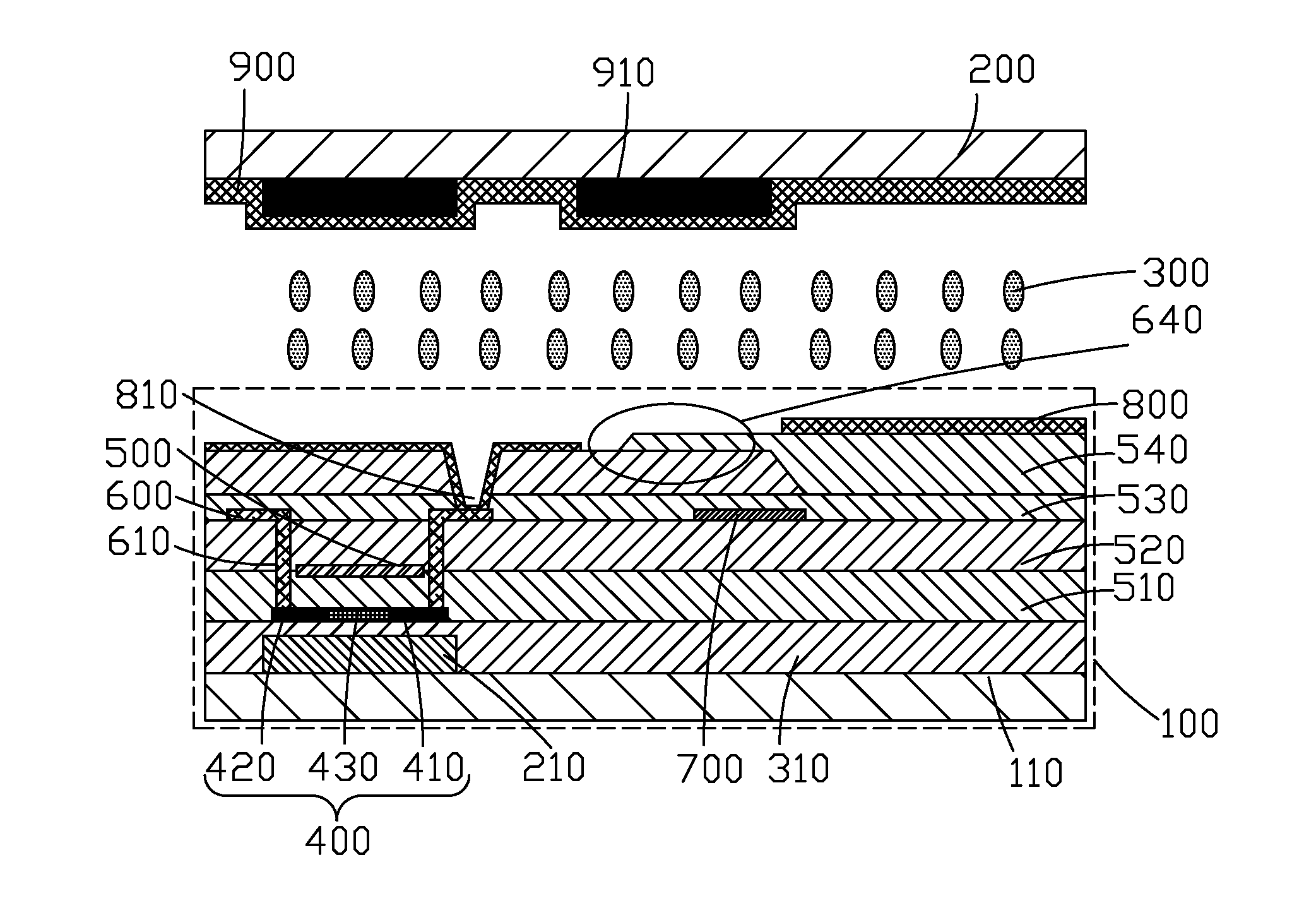

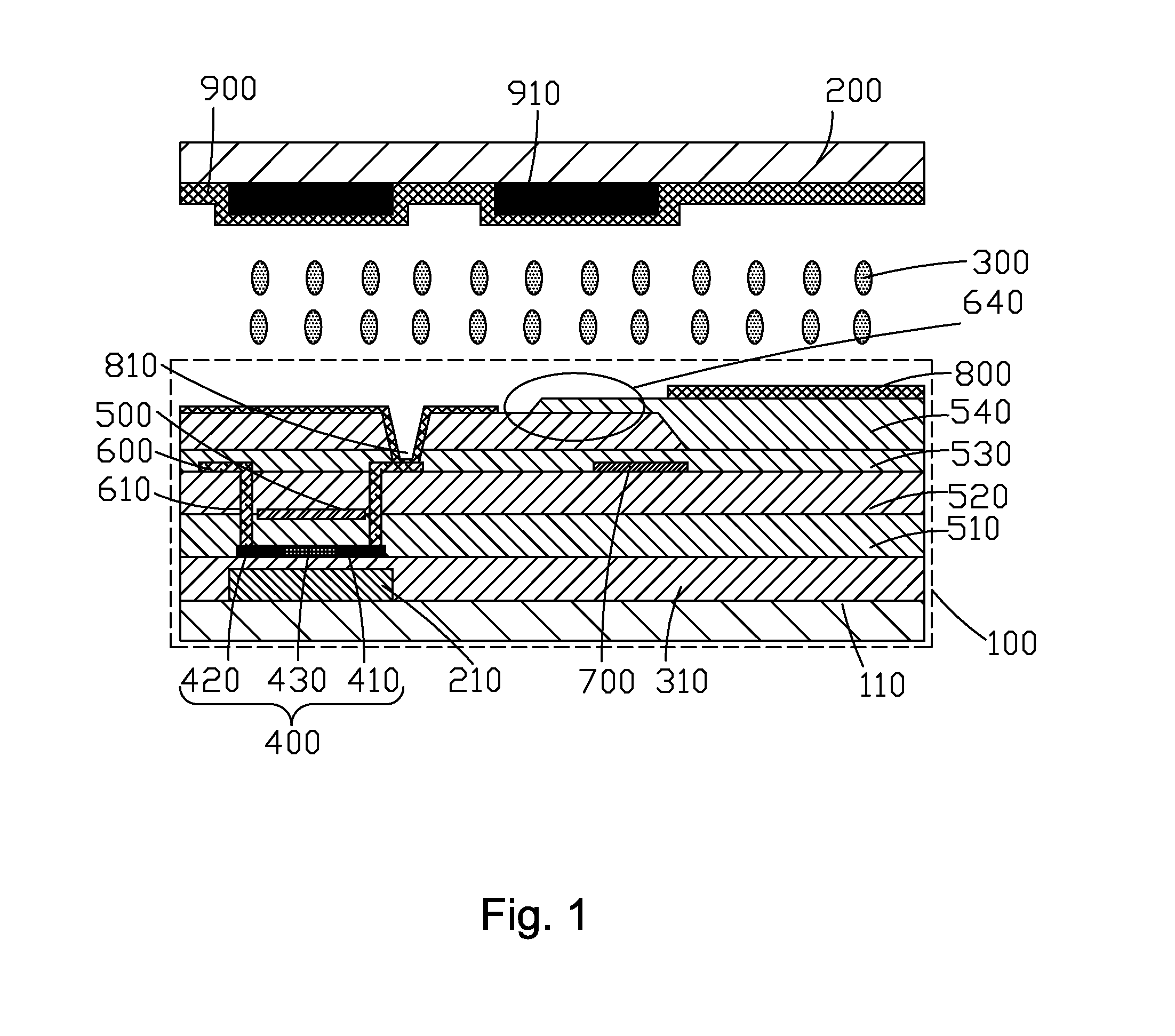

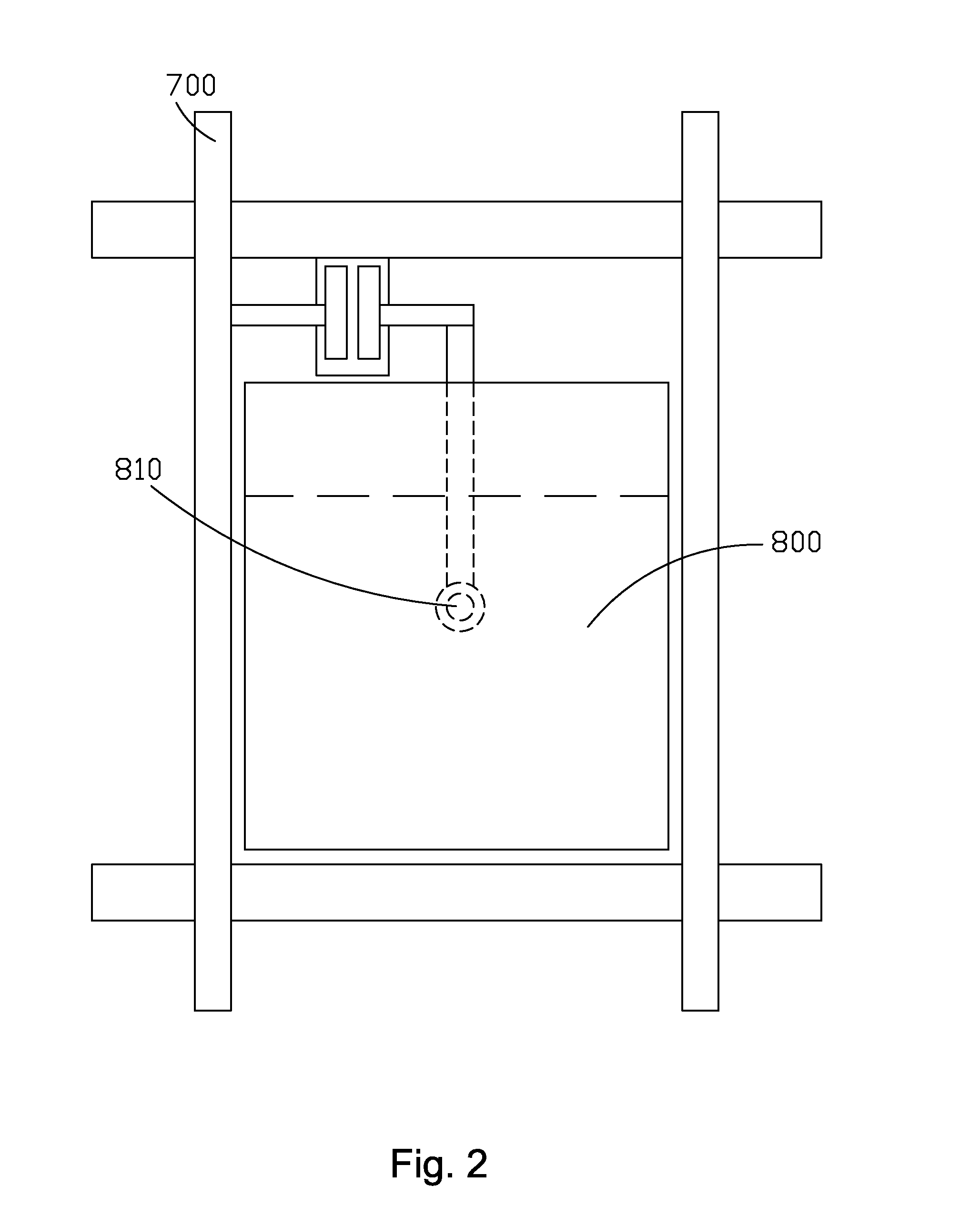

Hybrid thin film transistor and organic light emitting display device using the same

ActiveUS20180033849A1Reduce power consumptionImprove bias temperature stressSolid-state devicesSemiconductor/solid-state device manufacturingPolycrystalline siliconOptoelectronics

Owner:LG DISPLAY CO LTD

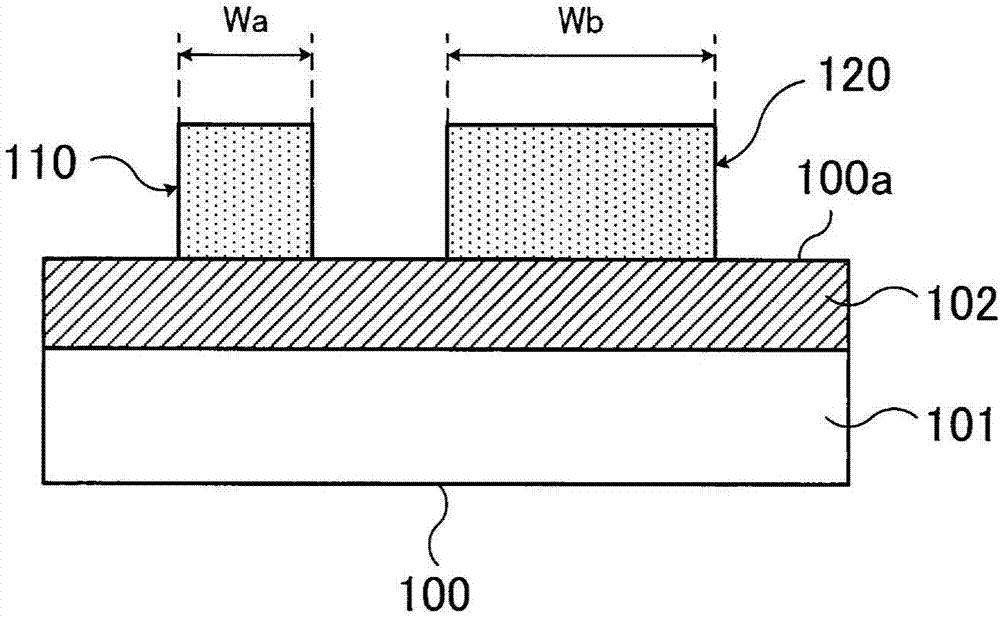

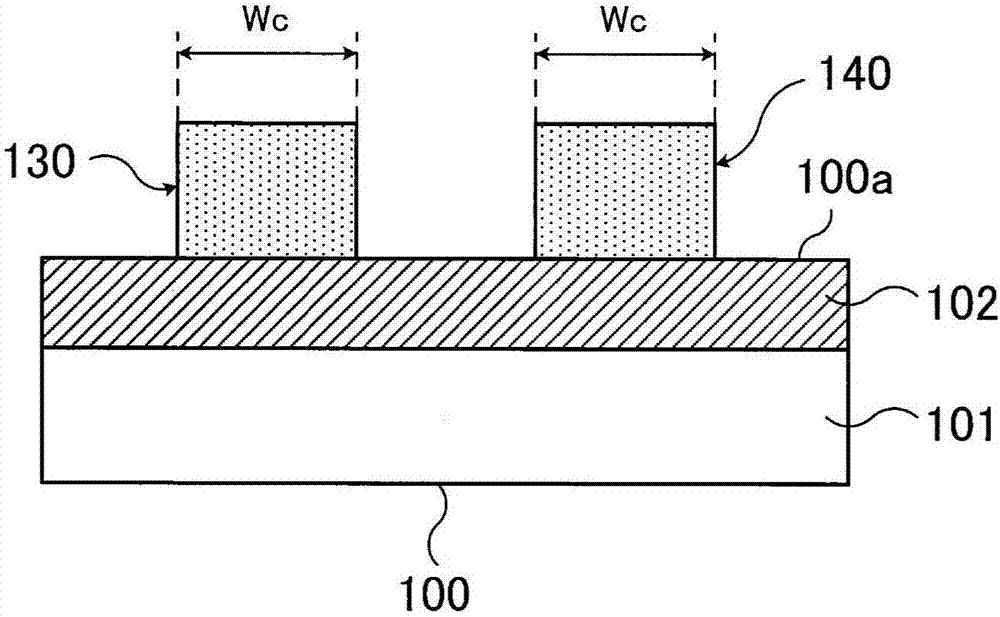

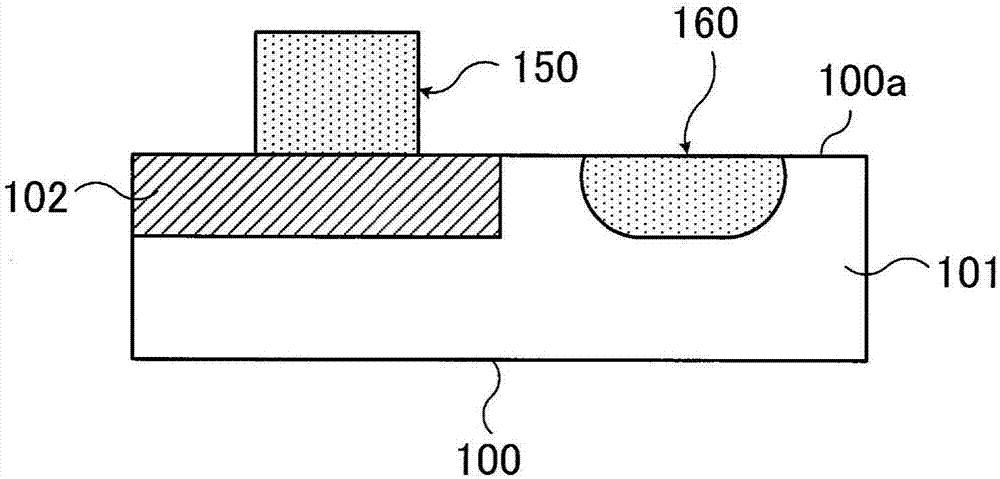

Polysilicon thin film transistor and method of fabricating the same

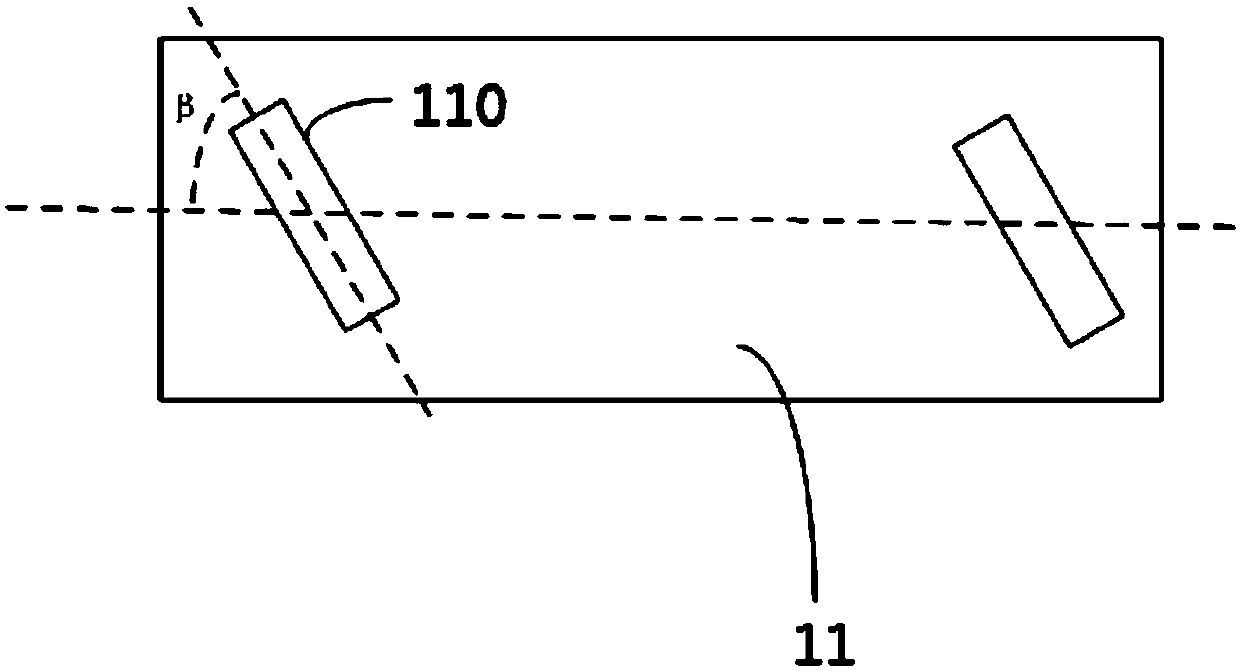

A method of fabricating a polycrystalline silicon thin film transistor is disclosed. One embodiment of the method includes: forming an amorphous silicon layer on a panel; scanning a continuous wave laser beam having a wavelength range of about 600 to about 900 nm between a visible light range of a red color and a near infrared range onto the amorphous silicon layer to preheat the amorphous silicon layer; overlappingly scanning a pulse laser beam having a wavelength range of about 100 to about 550 nm between a visible light range and an ultraviolet range in addition to the continuous wave laser beam on the panel to melt the preheated amorphous silicon layer; and stopping scanning the pulse laser beam to crystallize the molten silicon layer.

Owner:SAMSUNG MOBILE DISPLAY CO LTD

Preparation method of power diode

ActiveCN104576361AReduce reverse leakage currentLower forward voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesPhotoresistImpurity

The invention provides a preparation method of a power diode. The preparation method comprises the following steps: providing a substrate and growing an N type layer; forming a terminal protection ring; forming an oxide layer, and performing knot guiding on the terminal protection ring; forming a gate oxide layer, and depositing a polycrystalline silicon layer on the gate oxide layer; forming an N type heavily doped region; forming a P+ region; performing ion bombardment on a wafer, etching photoresist, and enlarging the photo-etched window; forming a P type body region; performing thermal annealing to activate the injected impurities; performing front metallization and back metallization. According to the preparation method of the power diode, the photo-etched window is enlarged by the ion bombardment to the photoresist which is used as a masking layer when being injected to form the P type body region; the ion bombardment time can be adjusted to control the feature size of the polycrystalline silicon photoresist, so as to adjust the length of the P type body region, namely the length of an MOS channel, and optimize the relation between the reverse leakage current and the forward voltage drop of the device.

Owner:CSMC TECH FAB2 CO LTD

Novel design method for ESD protection

InactiveCN101692425ALow costIncrease lithographySemiconductor/solid-state device detailsSolid-state devicesPorous mediumGate oxide

Owner:GUANGDONG YUEJING HIGH TECH CO LTD

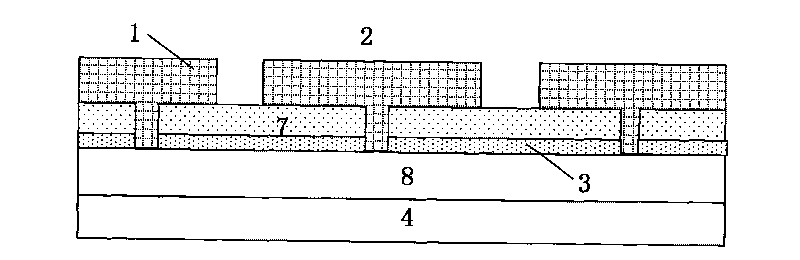

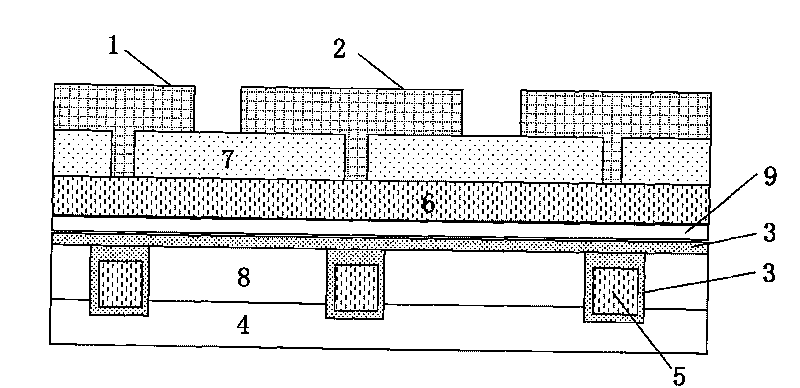

Method for manufacturing coa liquid crystal panel and coa liquid crystal panel

InactiveUS20170038653A1Avoid light leakageSimple manufacturing processTransistorSolid-state devicesSelf shieldingPolycrystalline silicon

The present invention provides a method for manufacturing a COA liquid crystal panel and a COA liquid crystal panel. The method includes forming a planarization layer on a color resist layer to eliminate height difference resulting from stacking or overlapping of adjacent color resist blocks and also includes forming a pixel electrode layer on the planarization layer to set a pixel electrode block thereof located above sub pixel zones in such a way that a lateral border thereof is located above a scan line and a longitudinal border thereof is located above a signal line, whereby the array substrate achieves self-shielding of leaking light in the lateral direction by means of the scan line and also achieve self-shielding of leaking light in the longitudinal direction by means of the signal line and thus no black matrix is necessary is shielding leaking light. As such, the manufacturing process is simplified, the aperture ratio is heightened, and a gate terminal and an amorphous silicon layer are respectively formed on upper and lower sides of the poly-silicon layer to shield light, preventing light leakage from occurring in the site of a channel to affect the liquid crystal layer and also to prevent light leakage caused by misalignment between an array substrate and a glass substrate or panel flexing of a curved display device.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

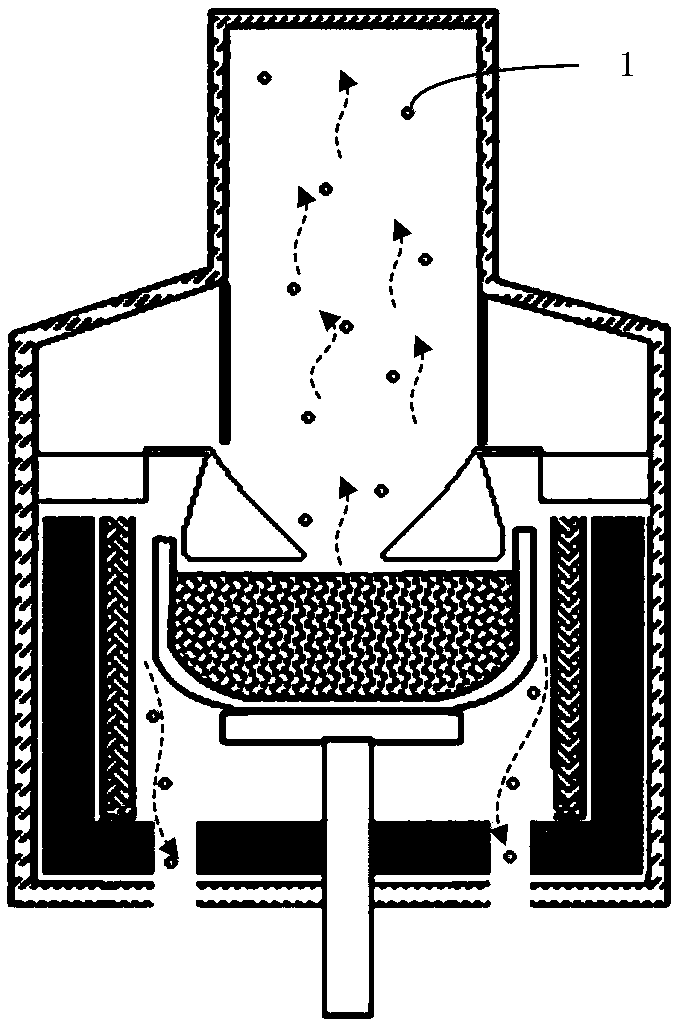

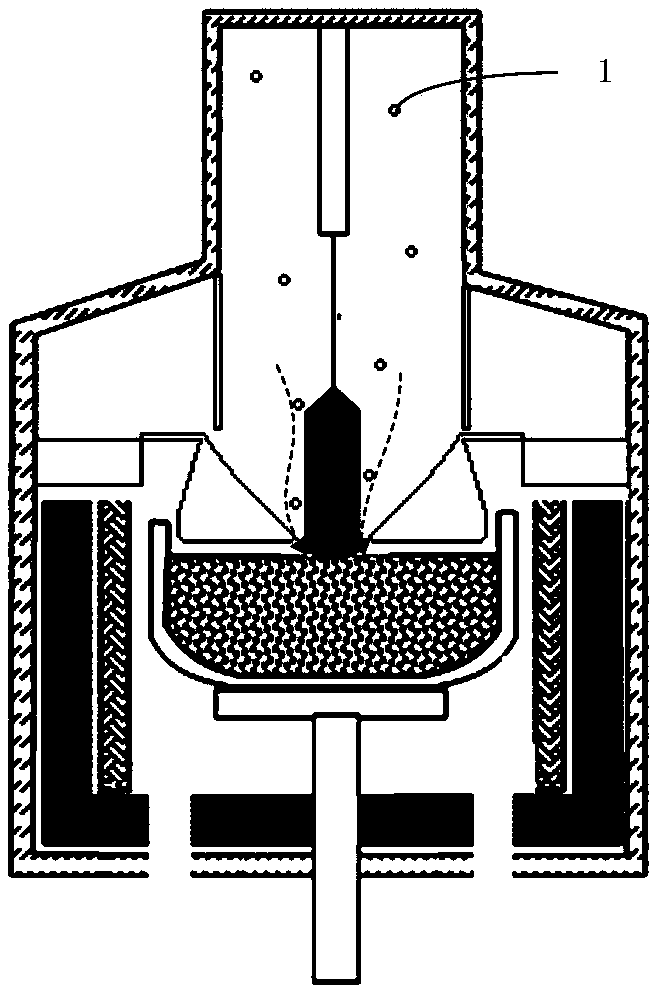

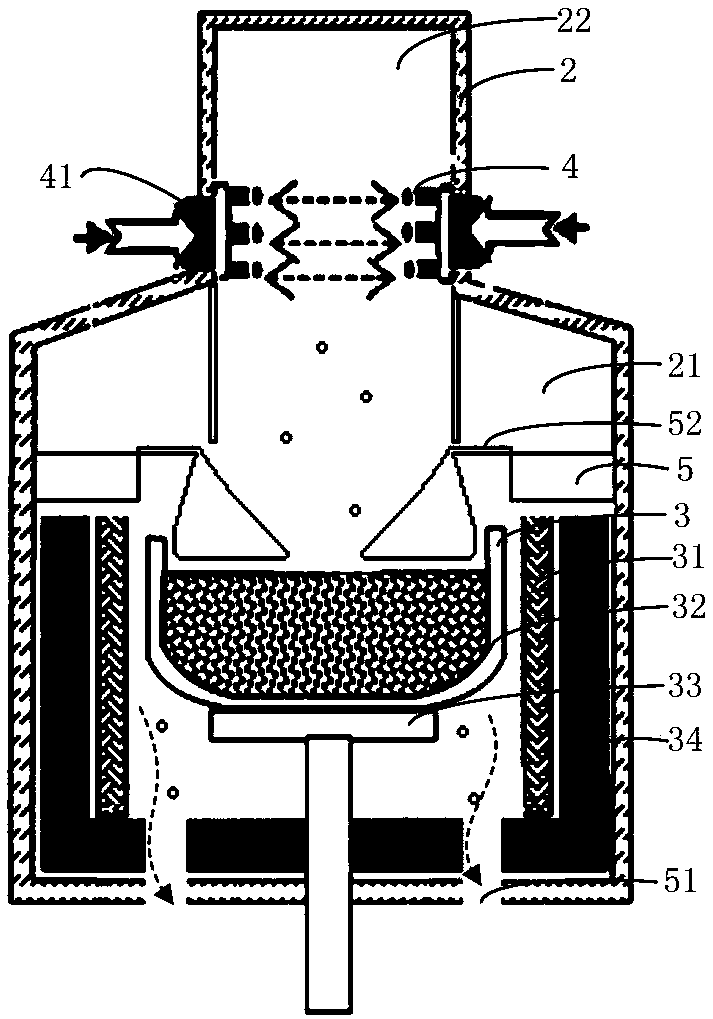

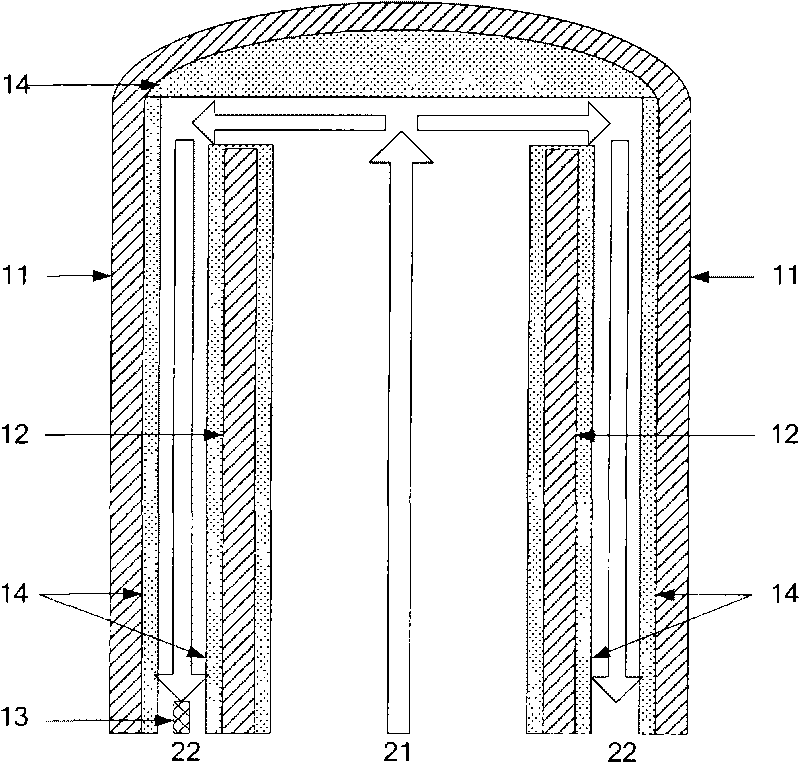

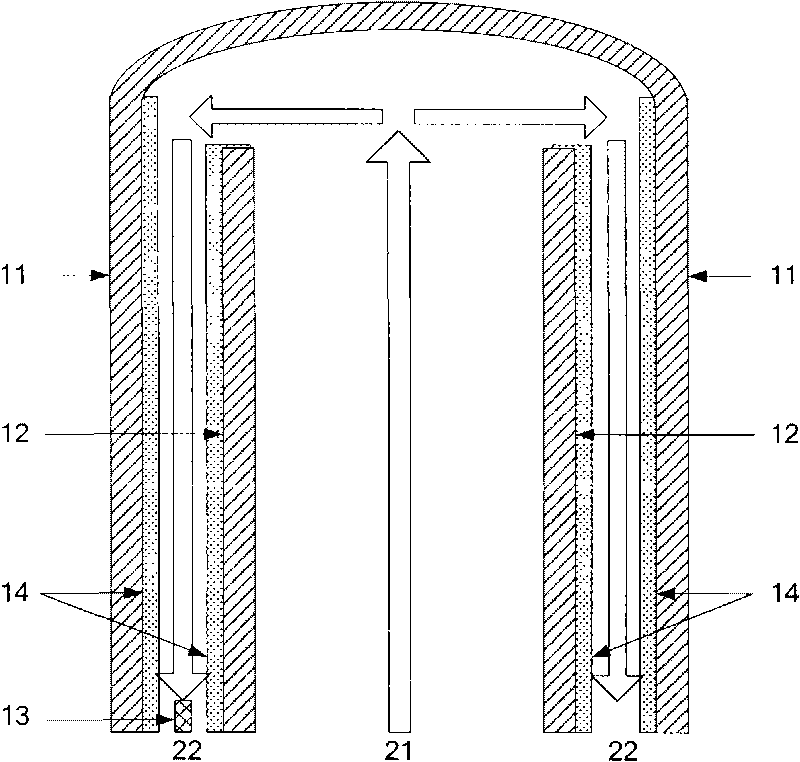

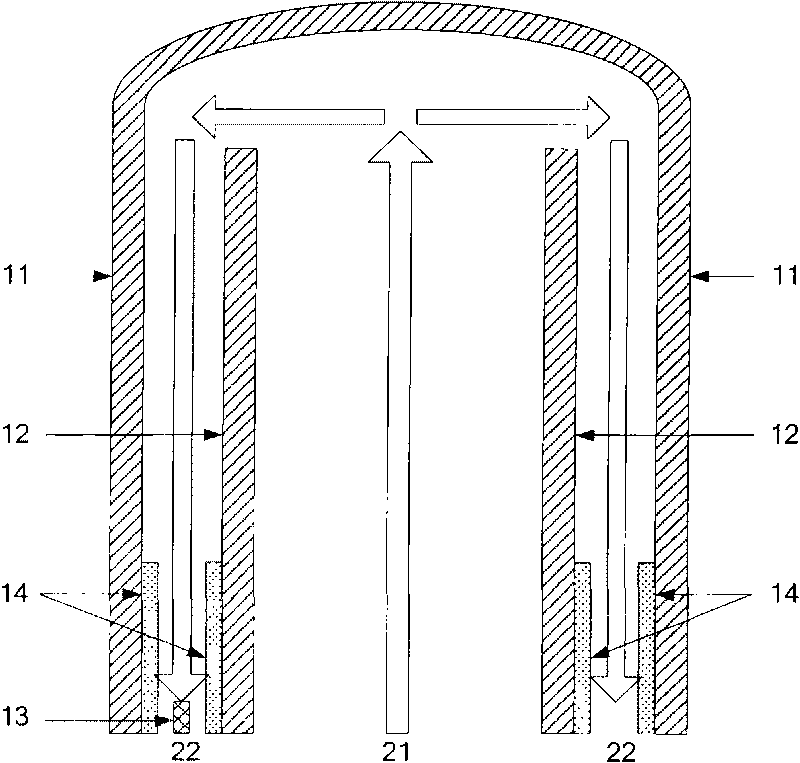

Ingotting furnace for polycrystalline silicon and quasi single crystal silicon and application method for ingotting furnace

ActiveCN103966657AReduce heat lossImprove securityPolycrystalline material growthFrom frozen solutionsDirectional solidificationPolycrystalline silicon

The invention discloses an ingotting furnace for polycrystalline silicon and quasi single crystal silicon and an application method for the ingotting furnace. The ingotting furnace comprises a quartz crucible, wherein first induction heating devices are arranged on the outer side of the quartz crucible, second induction heating devices are arranged at the bottom of the quartz crucible, third induction heating devices are arranged at the top of the quartz crucible, a graphite crucible is arranged outside the quartz crucible, a thermal insulating layer is arranged between the quartz crucible and the graphite crucible, and the first induction heating devices are arranged on the outer side of the graphite crucible in a surrounding manner. According to the ingotting furnace for the polycrystalline silicon and the quasi single crystal silicon and the application method for the ingotting furnace, provided by the invention, through the adoption of the double-layered crucible, a plurality of induction heating devices are arranged at different positions, so that the vortex current can be generated in polycrystalline silicon raw materials and solution by adopting the alternating magnetic field generated by spiral coils; because the induction coils are positioned out of the high-temperature thermal regions, the hot loss is less when heating is conducted; through the optimal design of the coil distribution of the induction heating devices, the accurate directional temperature gradient in the furnace can be realized, the direction of the crystal growth can be controlled better, and the directional solidification can be conducted quickly.

Owner:江苏盎华光伏工程技术研究中心有限公司

Method for preparing polysilicon

InactiveCN1727525AReduce the temperatureLower threshold voltagePolycrystalline material growthSemiconductor/solid-state device manufacturingFine lineSemiconductor materials

A process for preparing polycrystal silicon includes preparing non-crystal silicon film on glass substrate, preparing a thin Ni layer, photoetching the Ni layer to become fine lines, laser annealing, removing excessive Ni, and laser annealing again for crystallizing the silicon film. Its advantages are short time and low substrate temp.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

Tunnelling resonance microsound sensor

InactiveCN1746638AHigh sensitivityImprove temperature stabilitySubsonic/sonic/ultrasonic wave measurementUsing electrical meansResonant cavityQuantum well

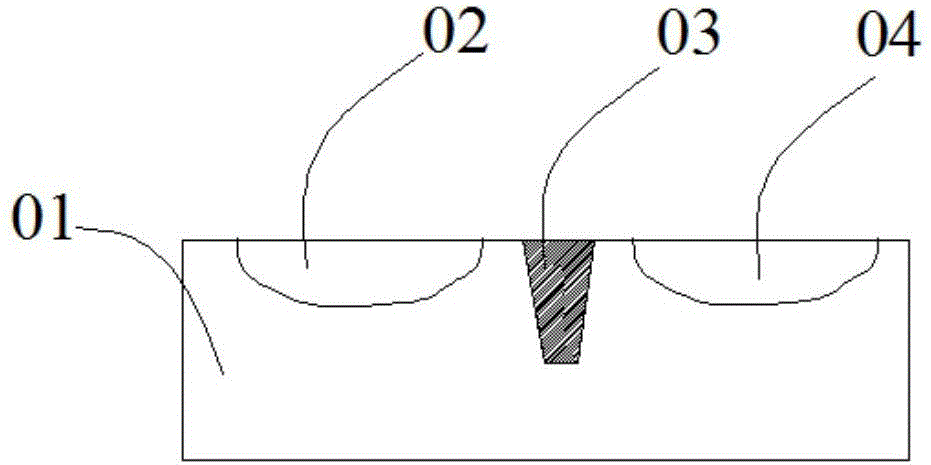

A resonant tunneling micro sound transducer is prepared as fabricating out resonant tunneling piezo ¿C resistance on super lattice film, fabricating super lattice film substrate to be force transmission structure of indent resonant cavity and setting four resonant tunneling piezo ¿C resistances on edge of indent resonant cavity. The said transducer is actually a quantum component prepared by MEMS process.

Owner:ZHONGBEI UNIV

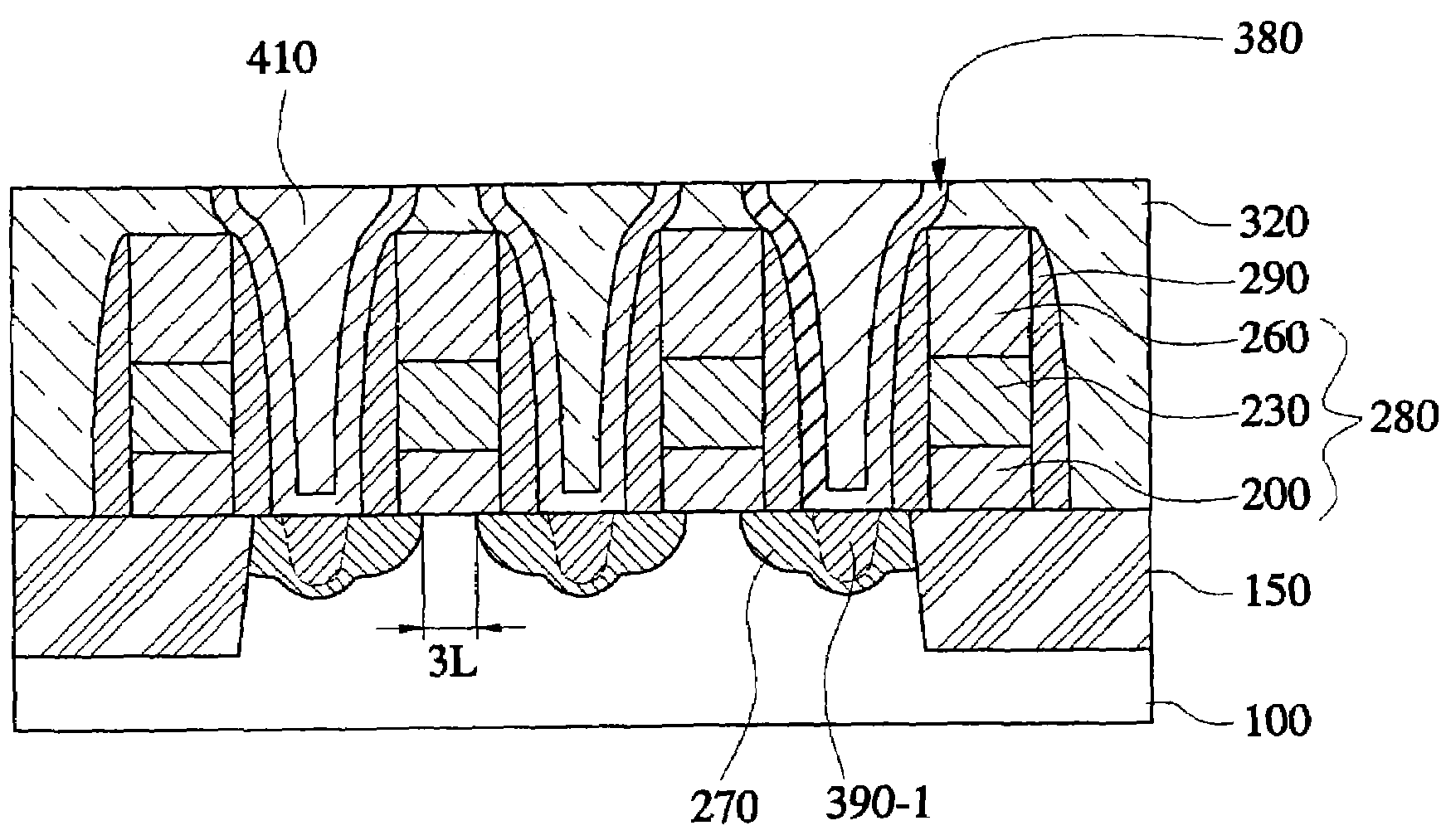

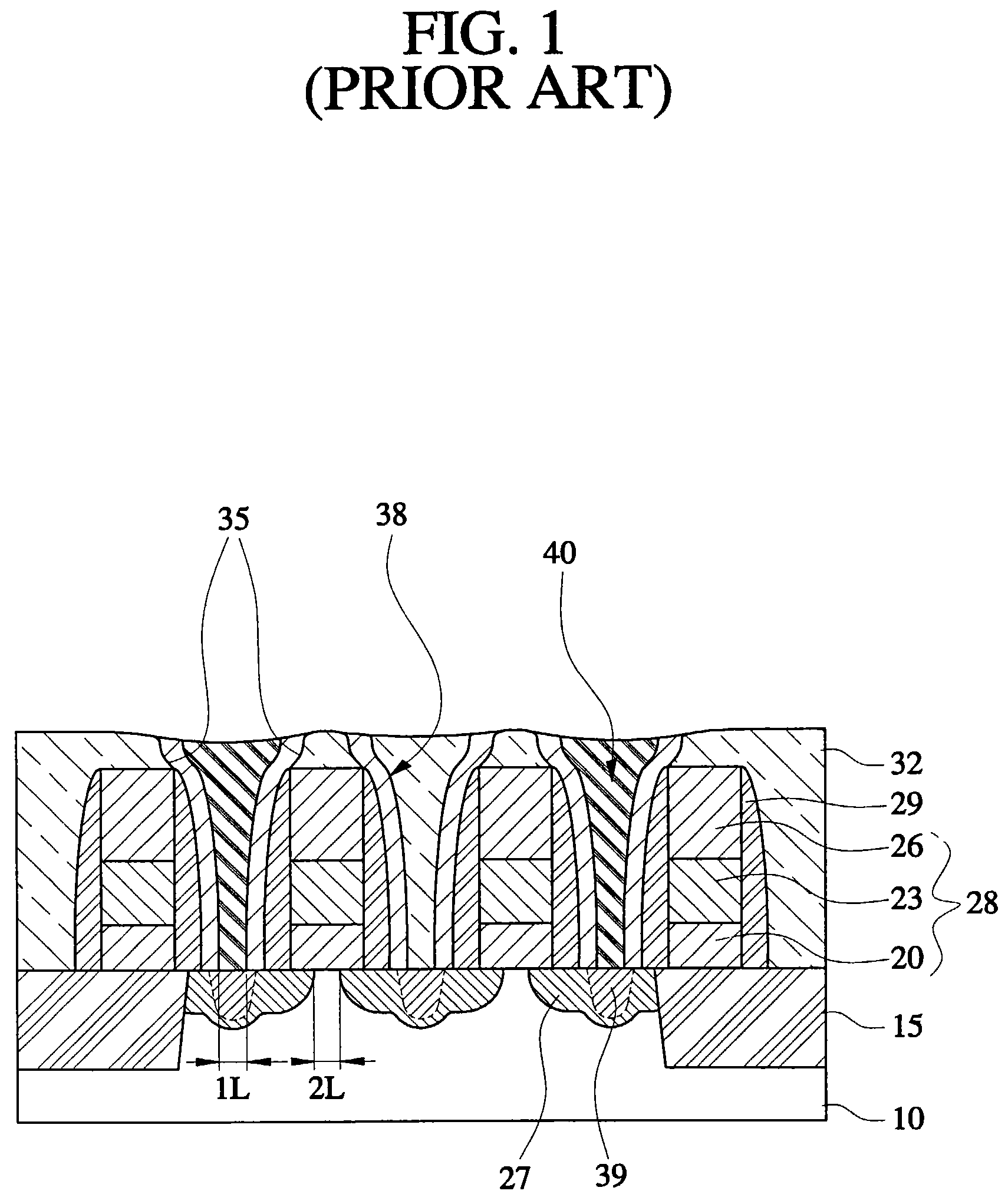

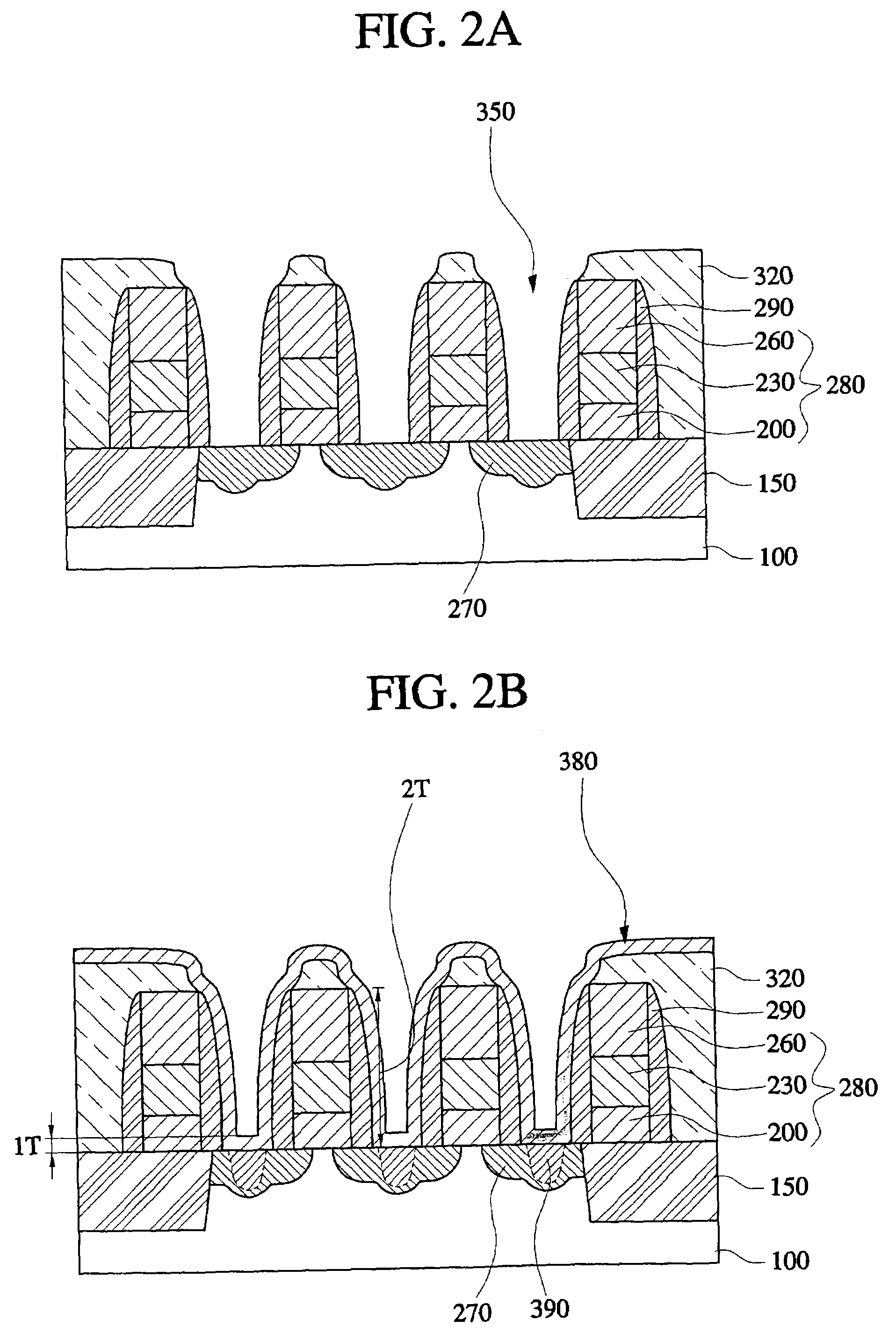

Methods of forming integrated circuit devices including a multi-layer poly film cell pad contact hole

InactiveUS7307008B2TransistorSemiconductor/solid-state device manufacturingIntegrated circuitPolycrystalline silicon

Owner:SAMSUNG ELECTRONICS CO LTD

Single crystal pulling device, preparation method of single crystal silicon and single crystal silicon

InactiveCN109554756APrevent inflowReduce dislocationPolycrystalline material growthUnder a protective fluidSingle crystalEngineering

Owner:XIAN ESWIN SILICON WAFER TECH CO LTD

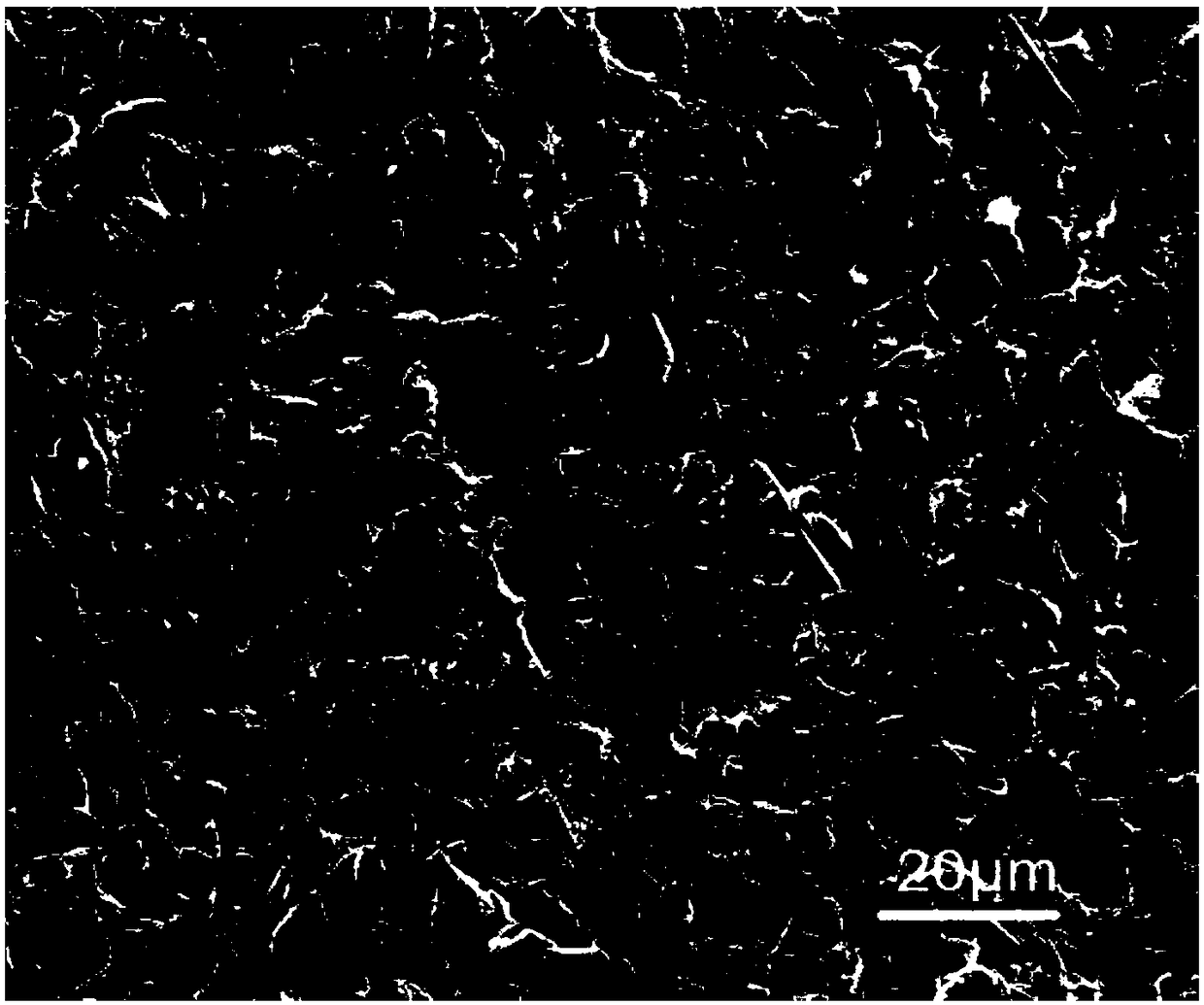

Dissociation-solidification abrasive particle composite wire saw cutting method for photovoltaic polycrystalline silicon cells

InactiveCN108437244AImprove processing efficiencyImprove surface accuracyFine working devicesWear particleMicroscopic scale

Owner:SHANDONG UNIV

Semiconductor device and semiconductor device fabrication method

ActiveCN107104134AInhibition of poor performanceTransistorSemiconductor/solid-state device detailsPower semiconductor deviceBoron

Owner:UNITED SEMICON JAPAN CO LTD

Solar-grade polycrystalline silicon product and production method thereof

PendingCN110386605AImprove ductilityHigh densitySilicon compoundsPolycrystalline siliconPhysical property

The invention discloses a solar-grade polycrystalline silicon product and a production method thereof. The polycrystalline silicon product includes a silicon core and a polycrystalline silicon body which grows around the silicon core. On the cross section of the polycrystalline silicon rod product, the polycrystalline silicon body forms in a substantially elliptical shape, and the silicon core forms in a substantially rectangular shape which is centered in the elliptical shape. The elliptical-rod polycrystalline silicon product has good physical properties, is favorable for subsequent efficient transportation, and can be produced in a more economical mode.

Owner:巴彦淖尔聚光硅业有限公司

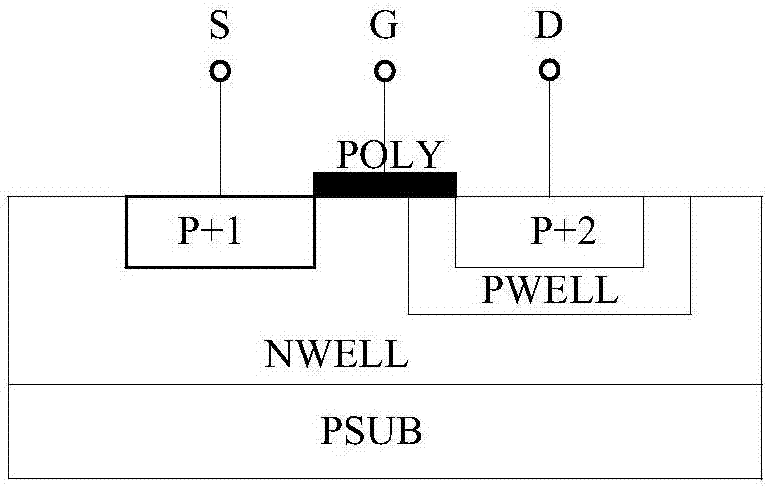

High-voltage PMOS transistor in low-voltage process

Owner:长沙方星腾电子科技有限公司

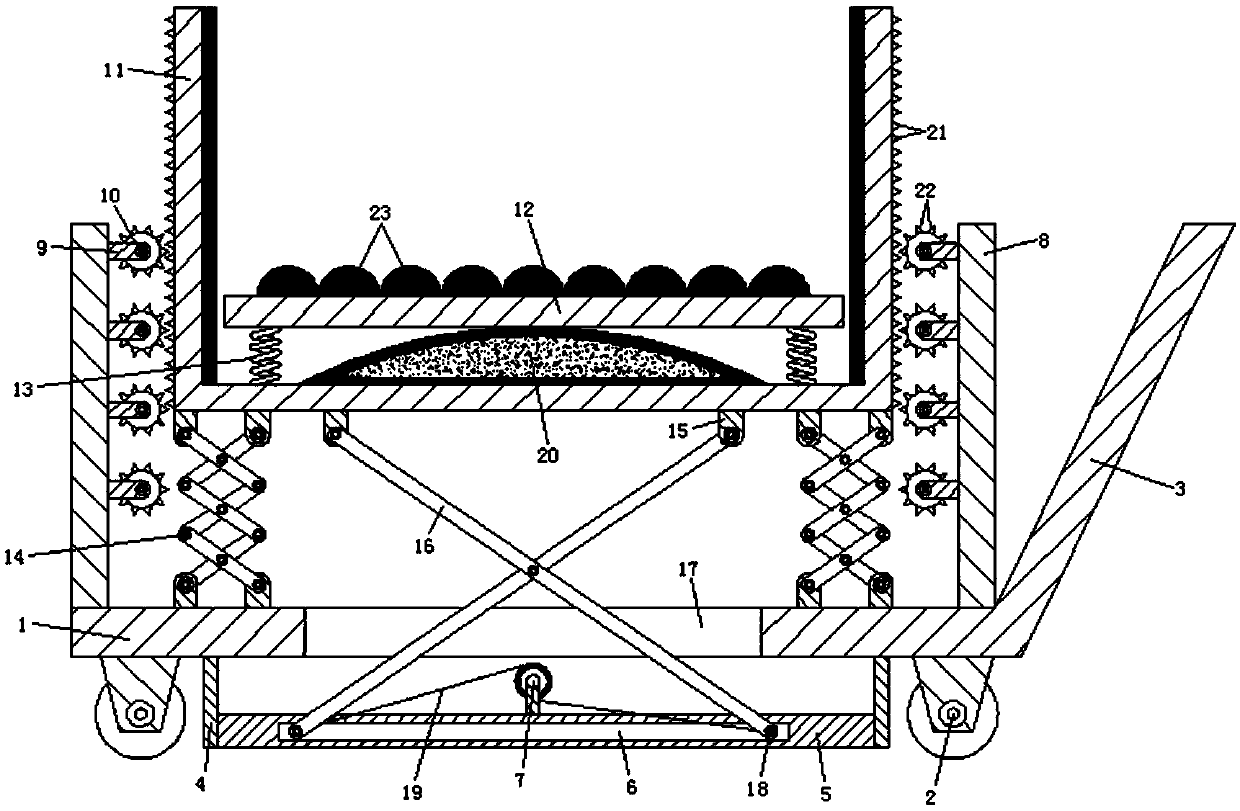

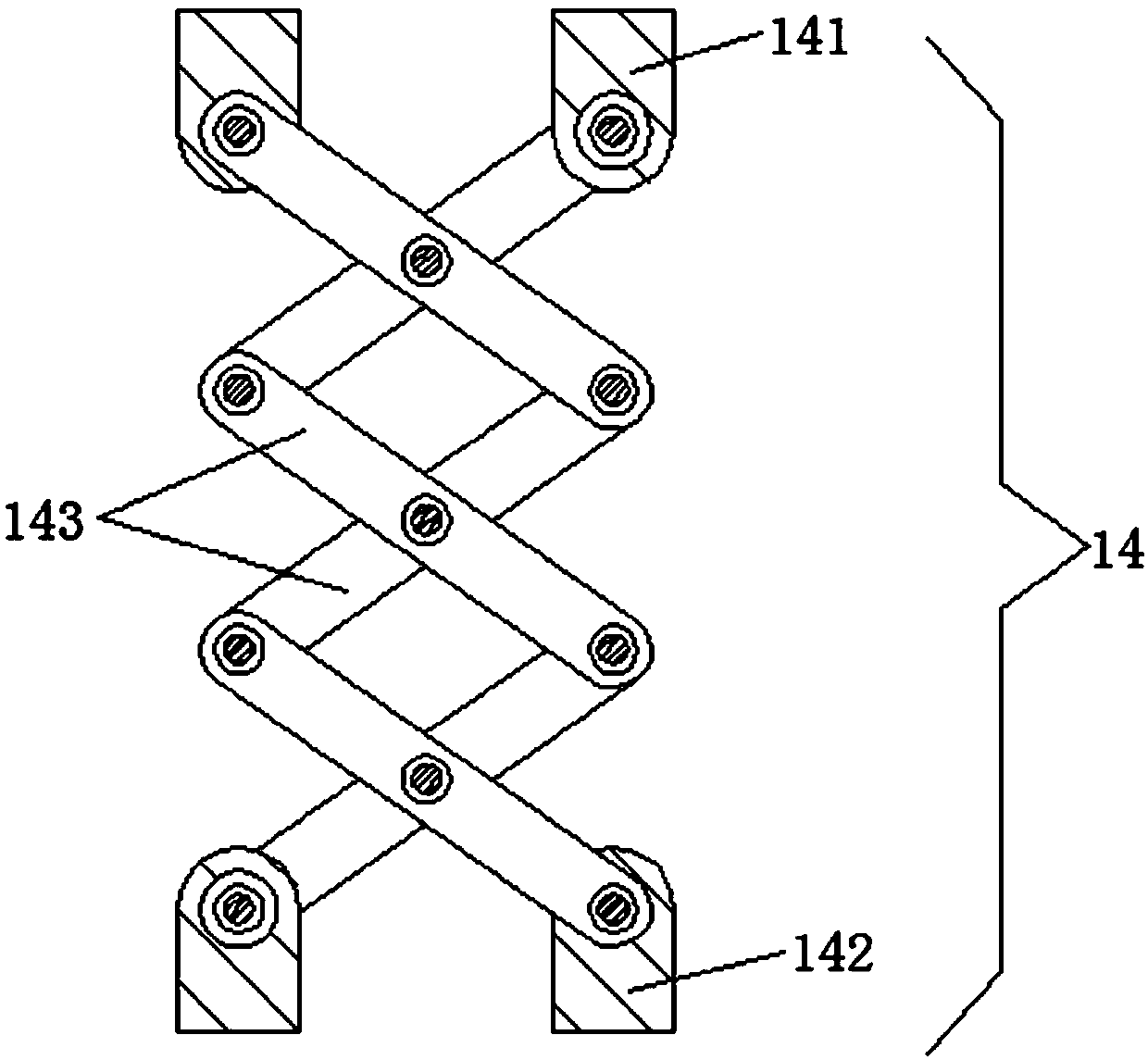

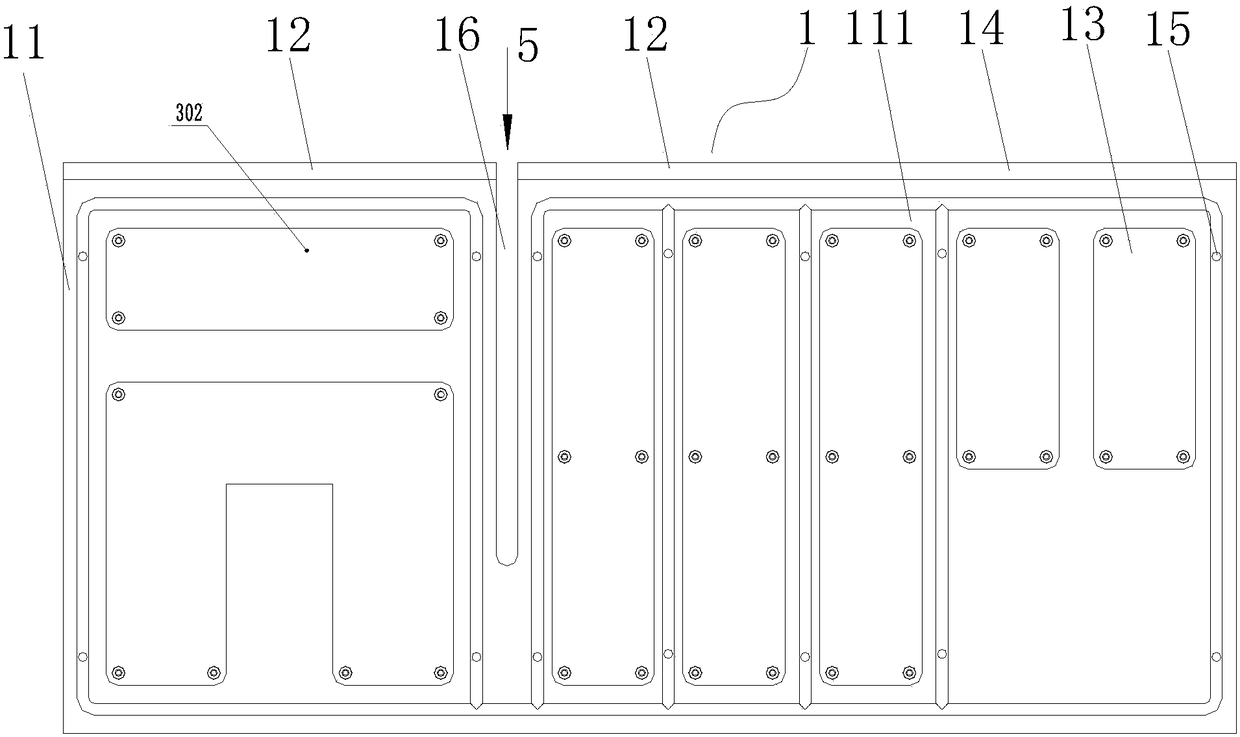

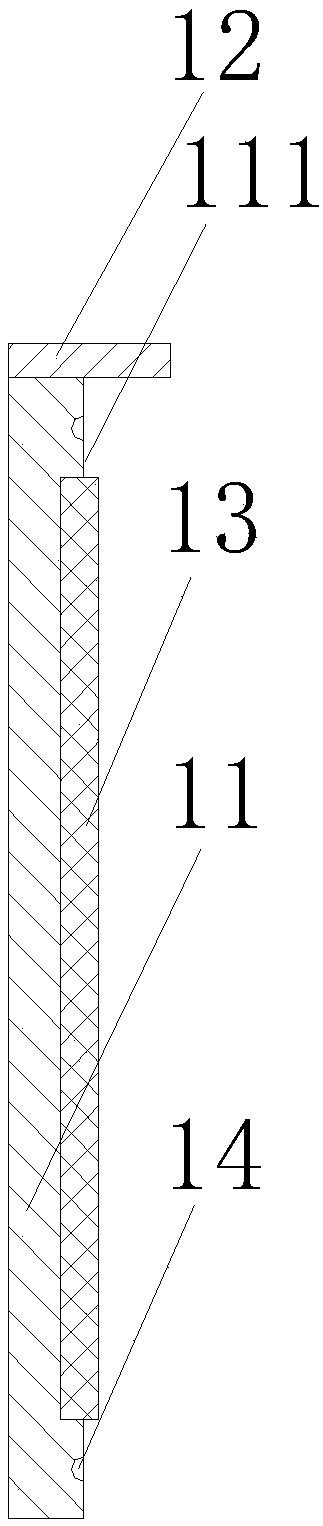

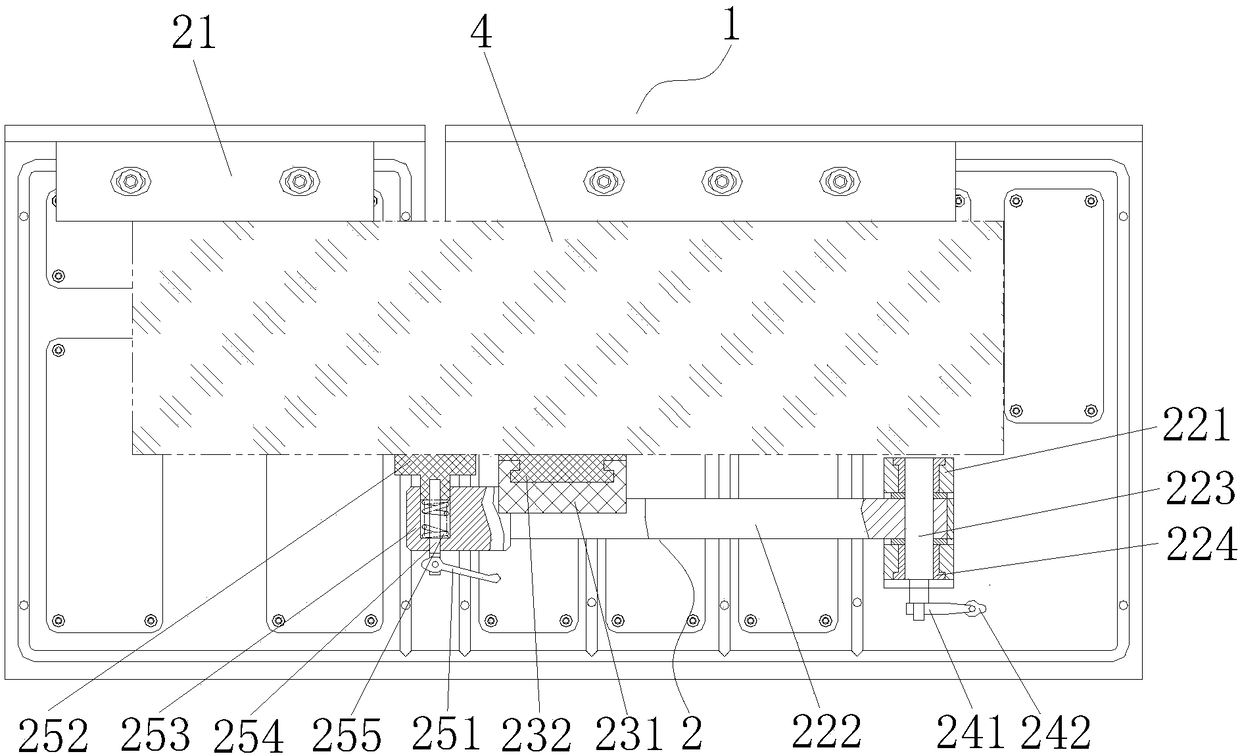

Efficient and safe transfer device for polycrystalline silicon ingots

InactiveCN110936999AHand carts with multiple axesHand cart accessoriesEngineeringPolycrystalline silicon

Owner:江苏德润光电科技有限公司

Semiconductor device with Schottky metal junction and manufacturing method thereof

PendingCN110931569AReduce leakage currentReduce conduction voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierDevice material

Owner:广微集成技术(深圳)有限公司

System for recycling silicon powder in polycrystalline silicon reduction tail gas and method thereof

InactiveCN111661827AHigh activityReduced activityNitrogen compoundsHalogenated silanesSlagSolid content

The invention discloses a system for recycling silicon powder in polycrystalline silicon reduction tail gas and a method thereof, the recycling system comprises a main filter and a residual liquid filter which are connected in sequence, a silicon powder outlet of the residual liquid filter is connected with a nitriding furnace, and an outlet of the nitriding furnace is connected with a grinder. Through cooperative filtering of the main filter and the residual liquid filter, the solid content of drying liquid in the residual liquid filter is increased, drying energy consumption can be reduced,and the drying effect can be enhanced. Compared with an existing silicon slag recovery method, the method has the advantages that the separated silicon powder basically has no silane residue on the surface, is high in activity, can be directly fed into a nitriding furnace to be used for manufacturing silicon nitride powder, and is high in recycling value. The method is low in energy consumption and good in drying effect, the silicon powder discharged out of the filter is high in activity and can be directly recycled, meanwhile, the silicon powder with low value is changed into a silicon nitride product with higher additional value, and the economic value of polycrystalline silicon reduction reaction byproducts is increased.

Owner:SICHUAN YONGXIANG POLY SILICON

Method for controlling terminal by using chlorine trifluoride to etch polysilicon growth furnace

InactiveCN101724912ATimely detection of reaction endpointsAvoid wastingAfter-treatment apparatusReaction temperaturePolycrystalline silicon

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

Dry cleaning apparatus using plasma and steam

ActiveCN113811400AReduce processing timeExtended cleaning cycleElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringSilicon oxide

A dry cleaning apparatus using plasma and steam, according to the present invention, comprises: a chamber having an upper supply port formed on an upper surface part thereof, having a discharge port formed on a lower surface part thereof, having a side supply port formed on a side surface part thereof, and providing a cleaning space; a chuck which is coupled to the lower surface part of the chamber, and on which a monocrystalline silicon substrate including amorphous silicon, polycrystalline silicon, silicon oxide, or silicon nitride is arranged; an RF electrode which is coupled to the upper surface part of the chamber, and to which RF power is applied; an upper shower head which is coupled to the RF electrode so as to communicate with the upper supply port formed on the upper surface part of the chamber, and which has a plurality of upper spray holes formed thereon; a lower shower head, which is coupled to the side surface part of the chamber, has a plurality of first lower spray holes, has a plurality of second lower spray holes that allow communicating with the side supply port, formed thereon and are electrically grounded; a reaction gas supply unit for supplying reaction gas through the upper supply port formed on the upper surface part of the chamber; and a stem supply unit for supplying hot steam through the side supply port formed on the side surface part of the chamber.

Owner:ASEI CO LTD

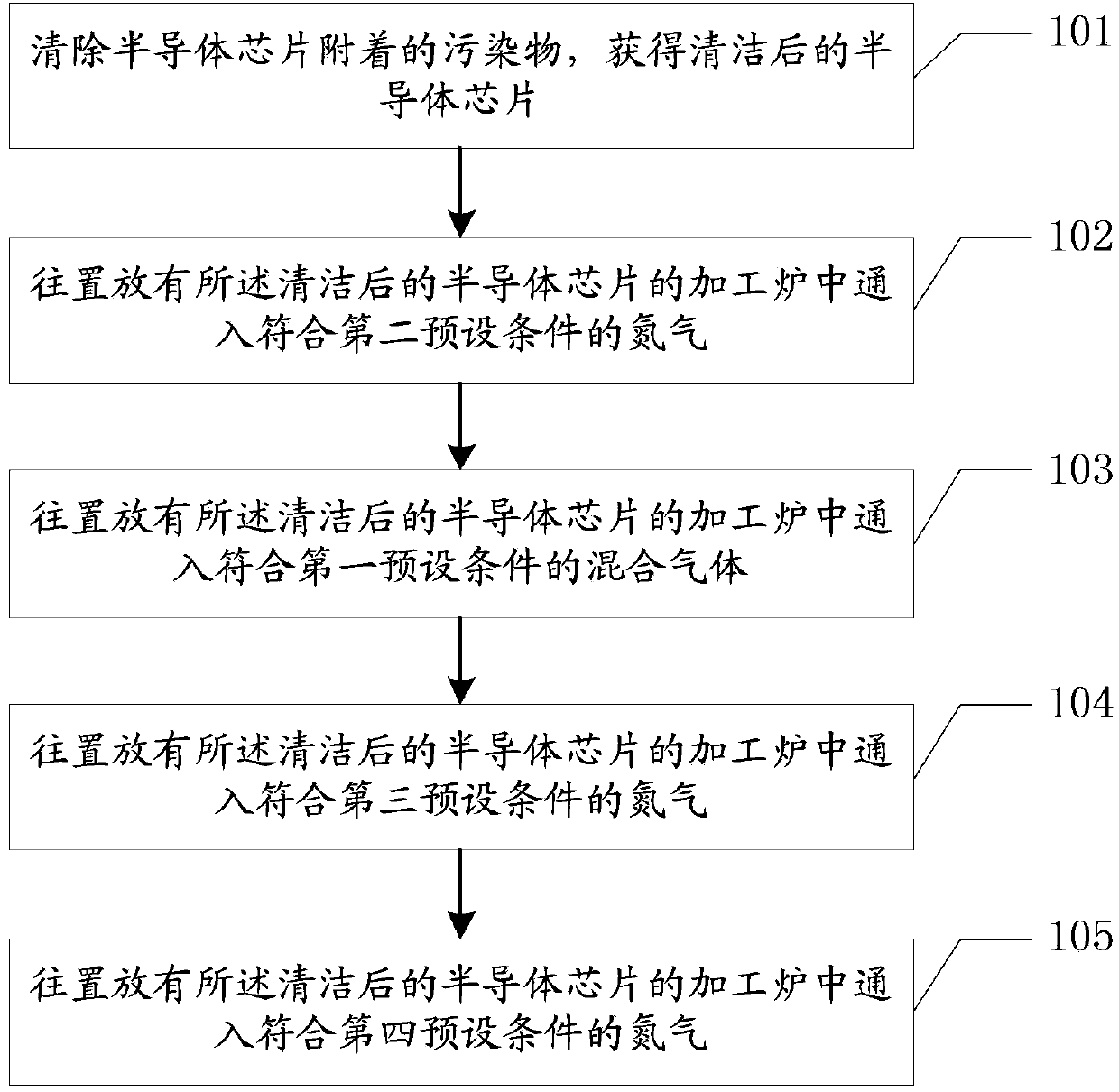

Method for processing semiconductor chip

InactiveCN103871836ASolve the technical problem of unstable physical and electrical characteristicsStable physical and electrical propertiesTransistorSemiconductor/solid-state device manufacturingSemiconductor chipNitrogen

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

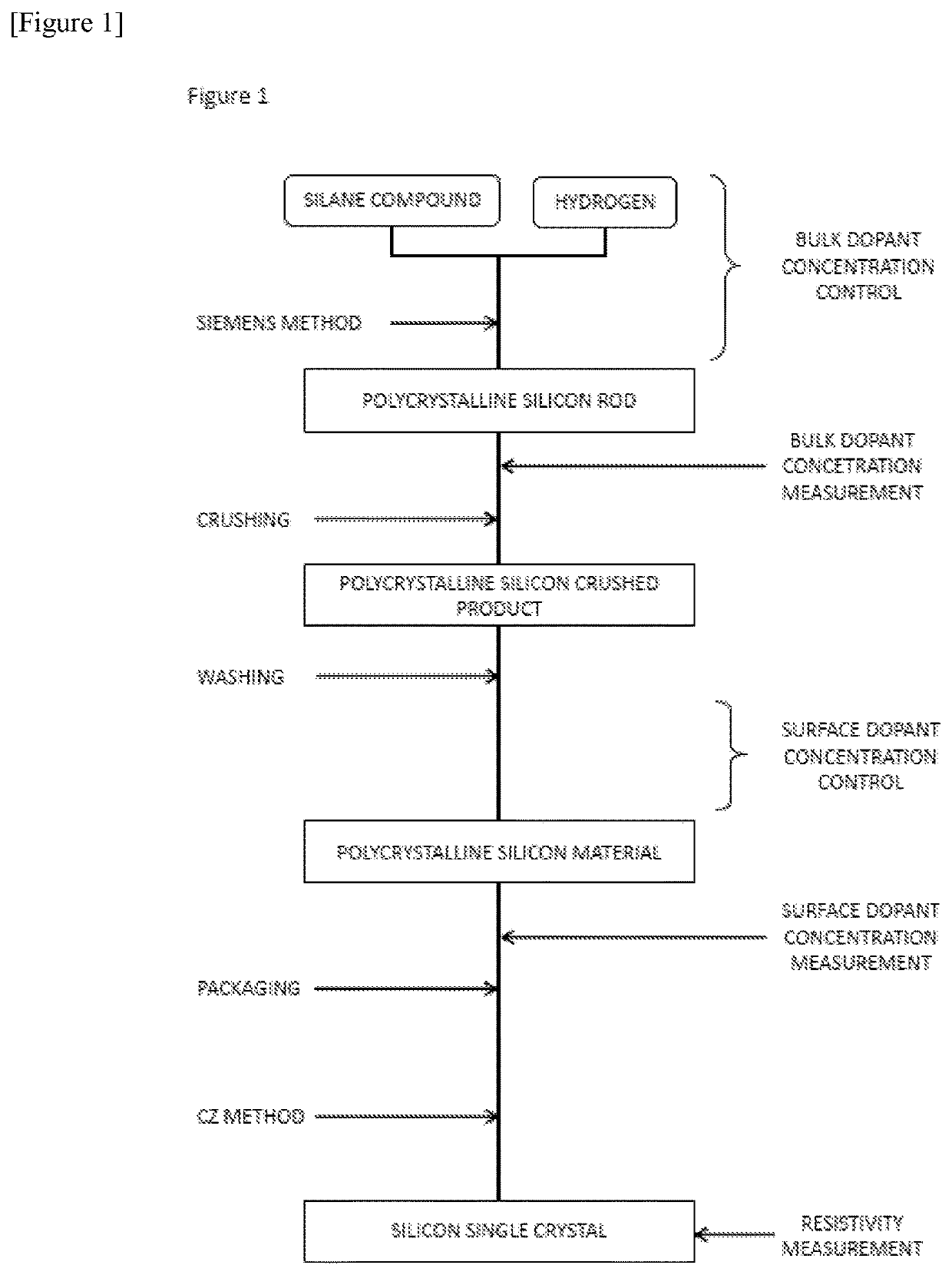

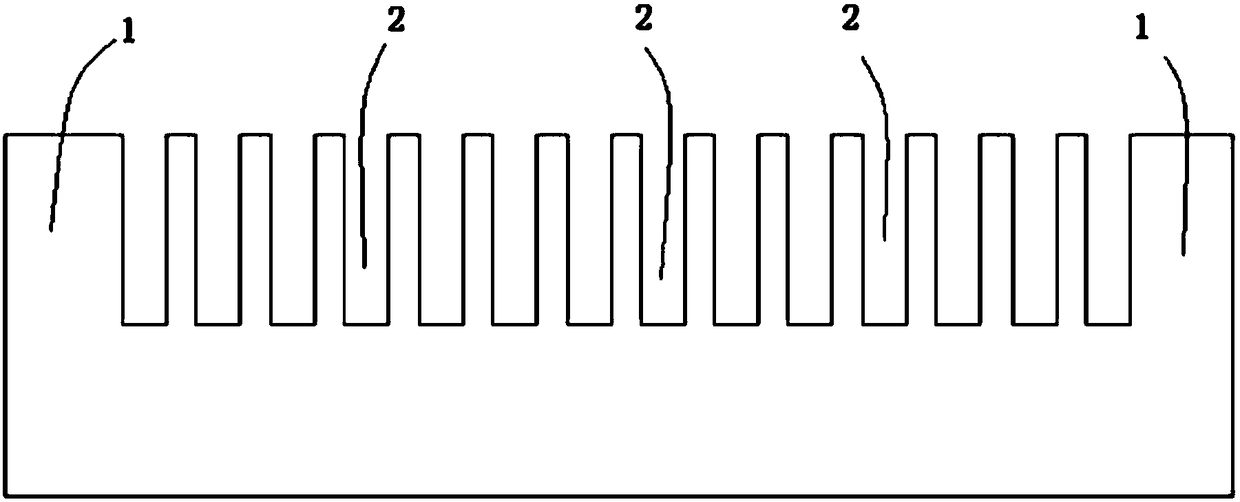

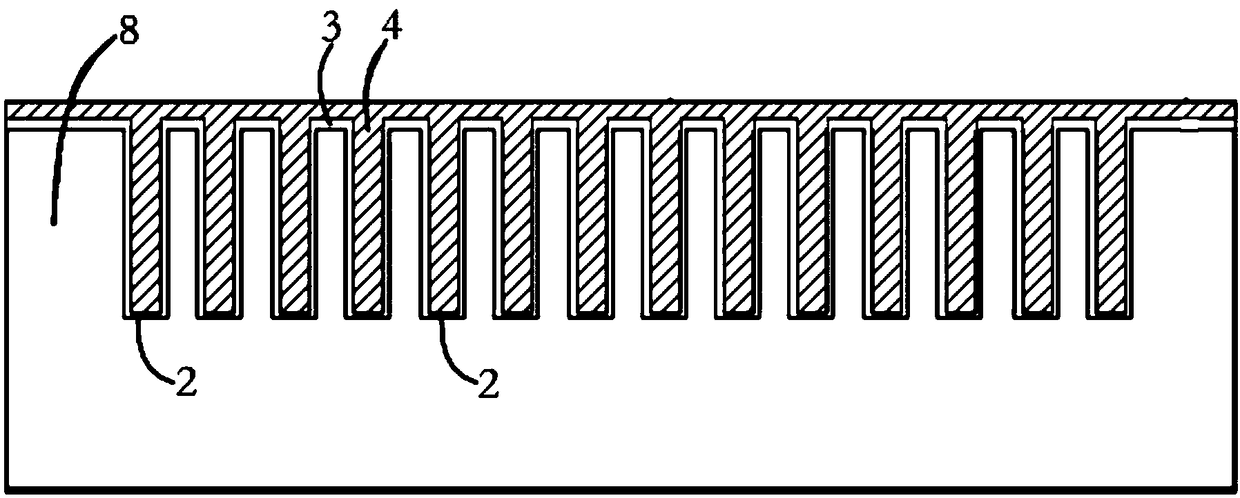

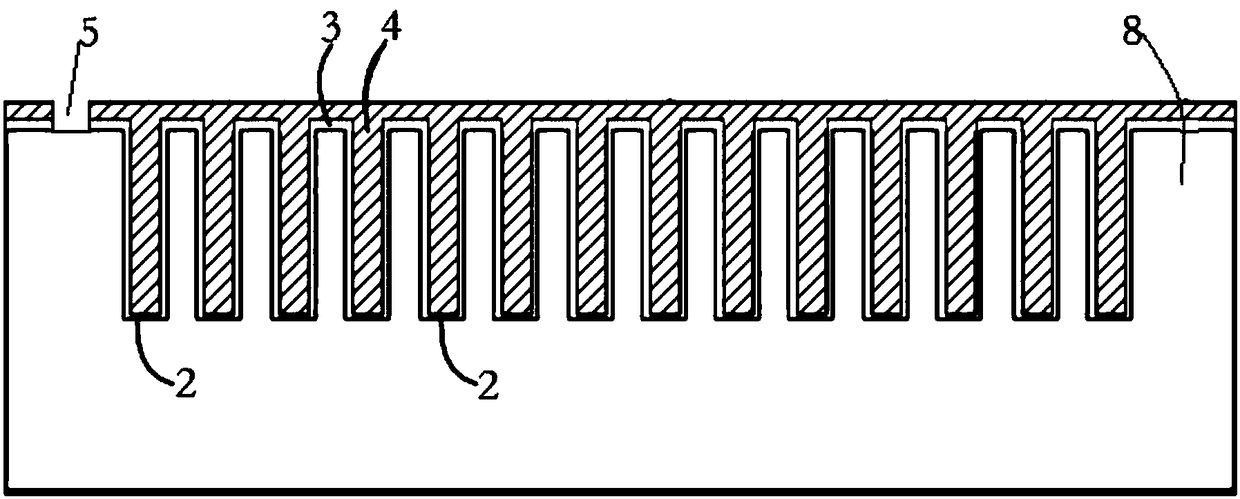

Polycrystalline Silicon Material

PendingUS20220204349A1Polycrystalline material growthSiliconMonocrystalline siliconPolycrystalline silicon

Owner:TOKUYAMA CORP

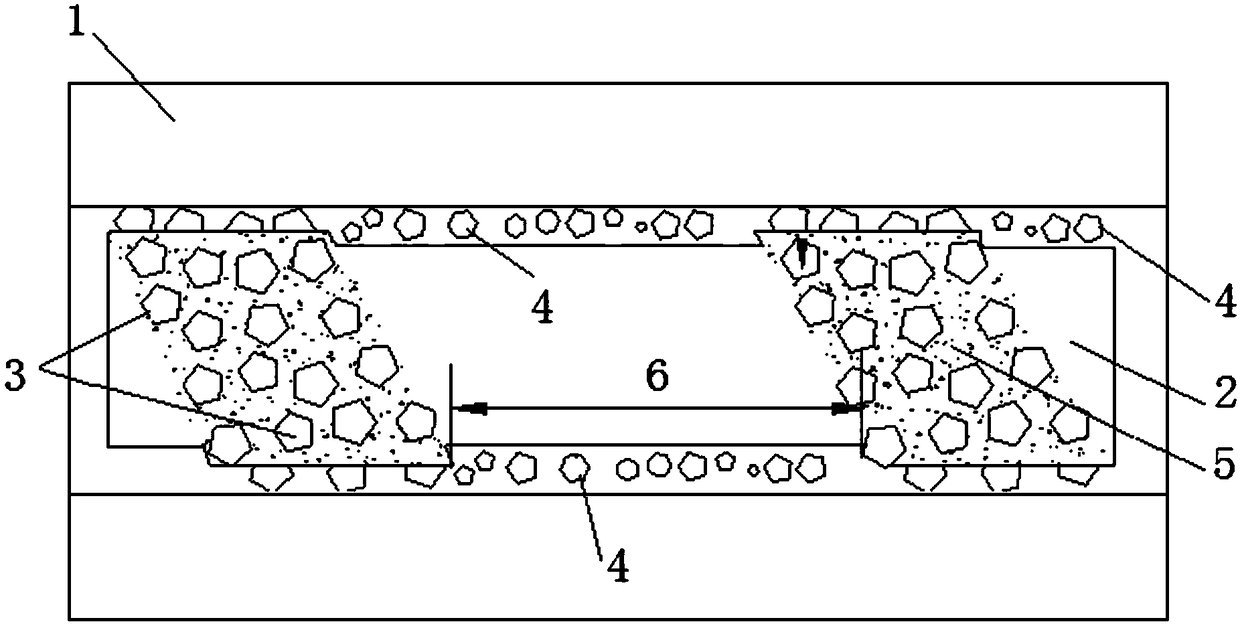

Method for manufacturing high-evenness grid lines

ActiveCN103489767ASimple manufacturing processMeet uniformity requirementsPhotomechanical apparatusSemiconductor/solid-state device manufacturingPhotoresistLine structure

The invention discloses a method for manufacturing high-evenness grid lines. The method comprises the steps of sequentially and directly depositing a polycrystalline silicon thin film on a substrate silicon wafer, then sequentially directly coating the polycrystalline silicon thin film with a spinning coating carbon thin film and a first photoresist, carrying out exposure and development so as to form a first grid line structure in a first photoresist film, coating the first photoresist with a curing material containing alkyl groups and amidogens to cure the first grid line structure in the first photoresist, heating the curing material to enable the cure material to be reacted with the surface of the first photoresist to form an isolating film which does not dissolve into a second photoresist, coating the cured first photoresist with the second photoresist, completing the exposure and the development to form a first line-end cutting graph in a second photoresist film, using the second photoresist film as a covering film, etching the isolating film and a first grid line to form a second line-end cutting graph, using the remaining isolating film and the first grid line as a covering film, and continuously and sequentially etching the spinning coating carbon thin film and the polycrystalline silicon thin film to form a second grid line structure.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

A method for manufacturing a high-frequency silicon capacitor

InactiveCN109003962ASemiconductor/solid-state device detailsSolid-state devicesCapacitancePolycrystalline silicon

Owner:无锡中微晶园电子有限公司

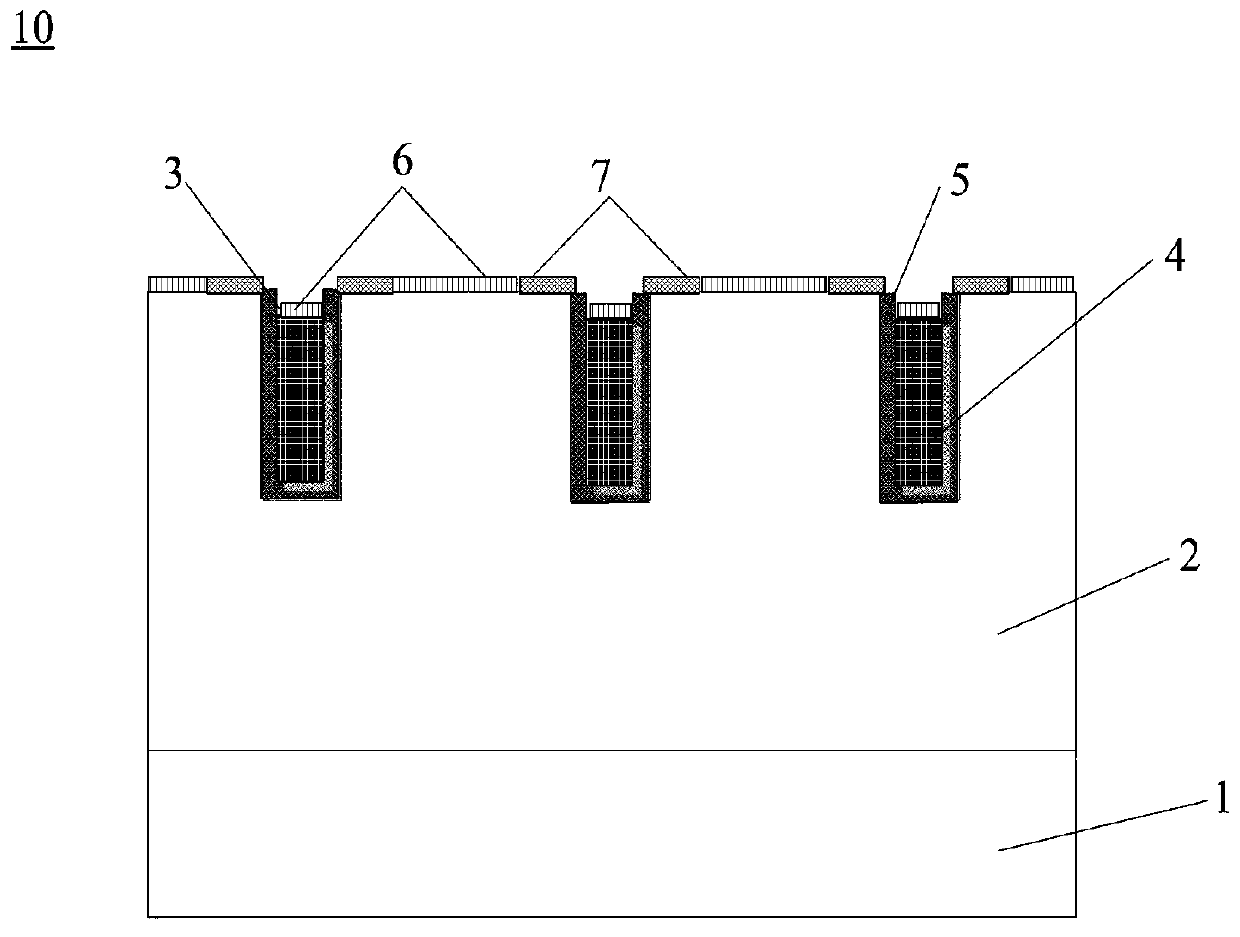

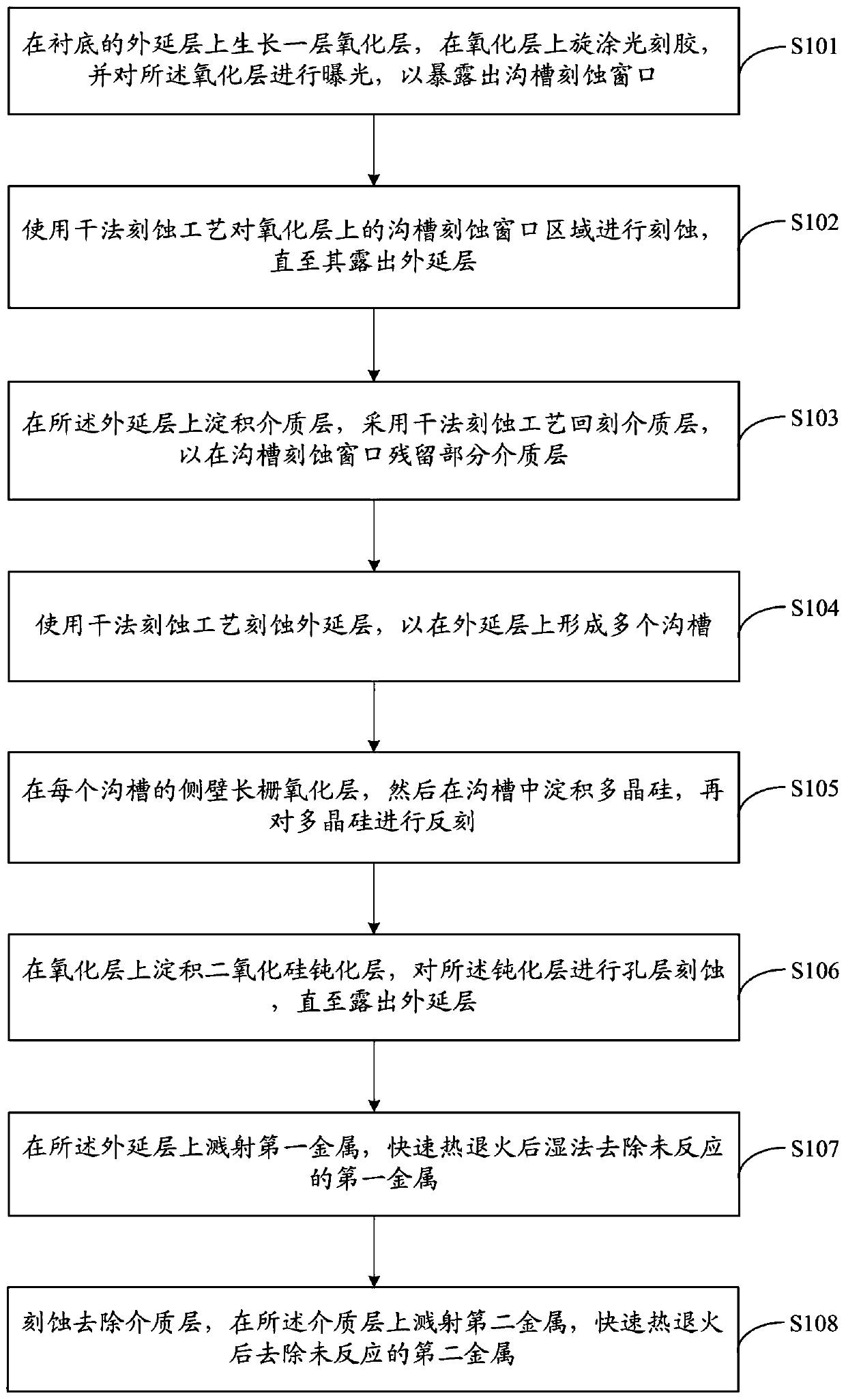

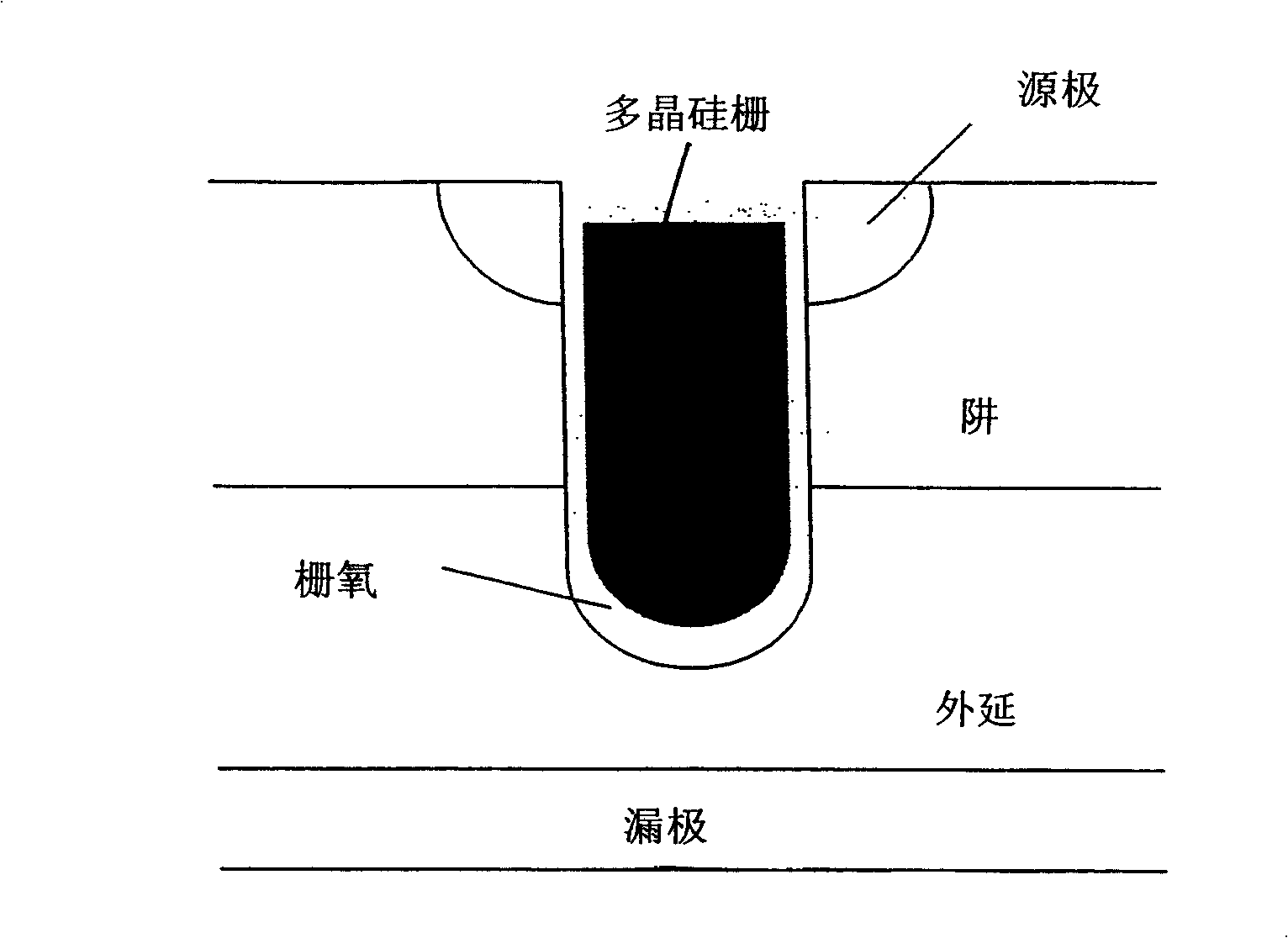

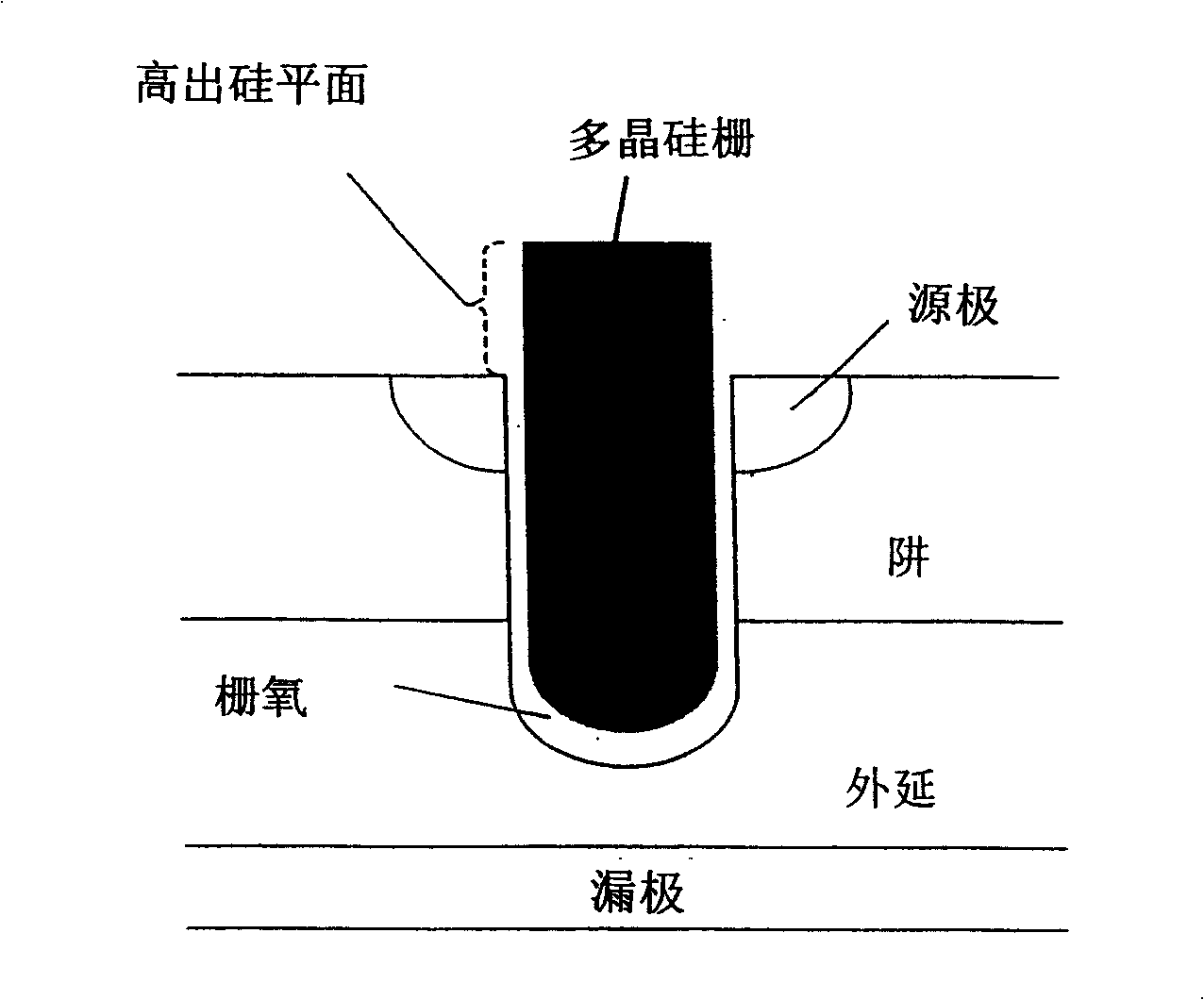

High power MOS transistor manufacturing method

ActiveCN100416856CIncrease the cross-sectional areaImprove frequency characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceGrating

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

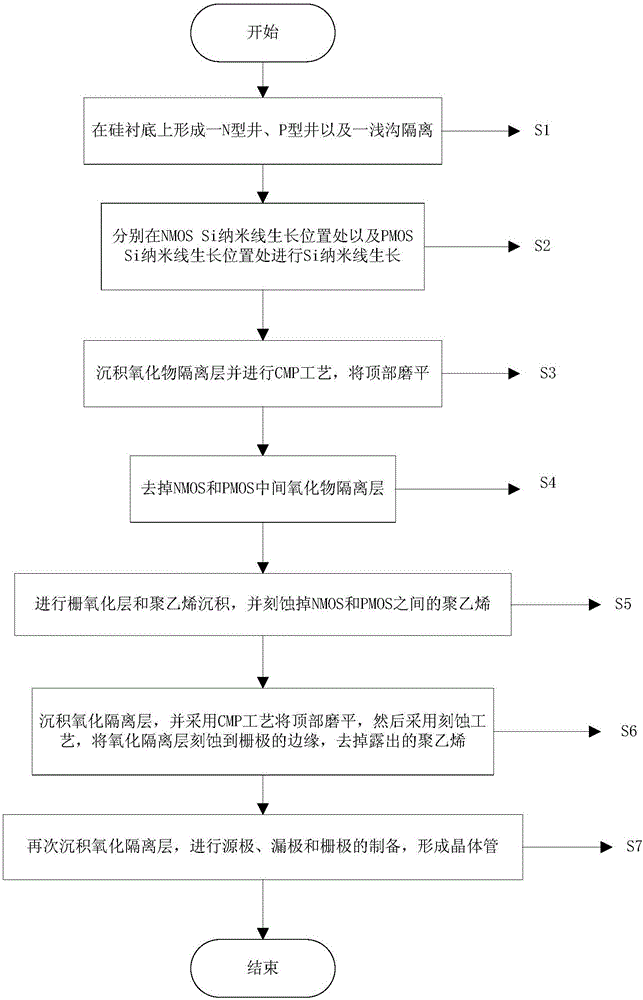

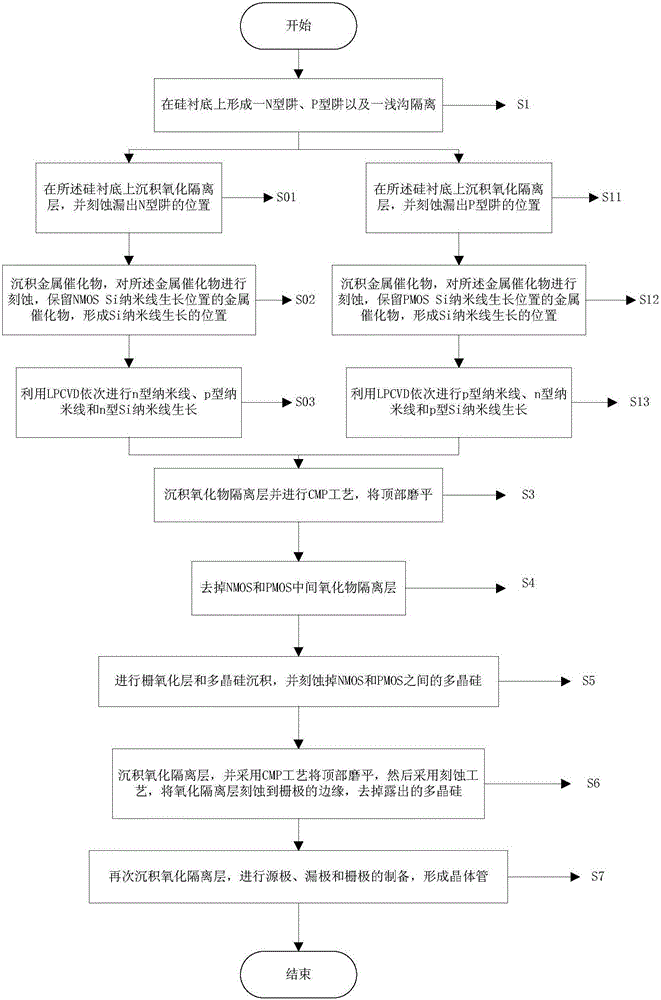

Preparation method of 3D peripheral grid MOS tube

InactiveCN105870192AImprove controlImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon nanowiresIsolation layer

Owner:WUHAN XINXIN SEMICON MFG CO LTD

Silicon crystal clamping tool and silicon crystal cutoff machine

Owner:福州天瑞线锯科技有限公司

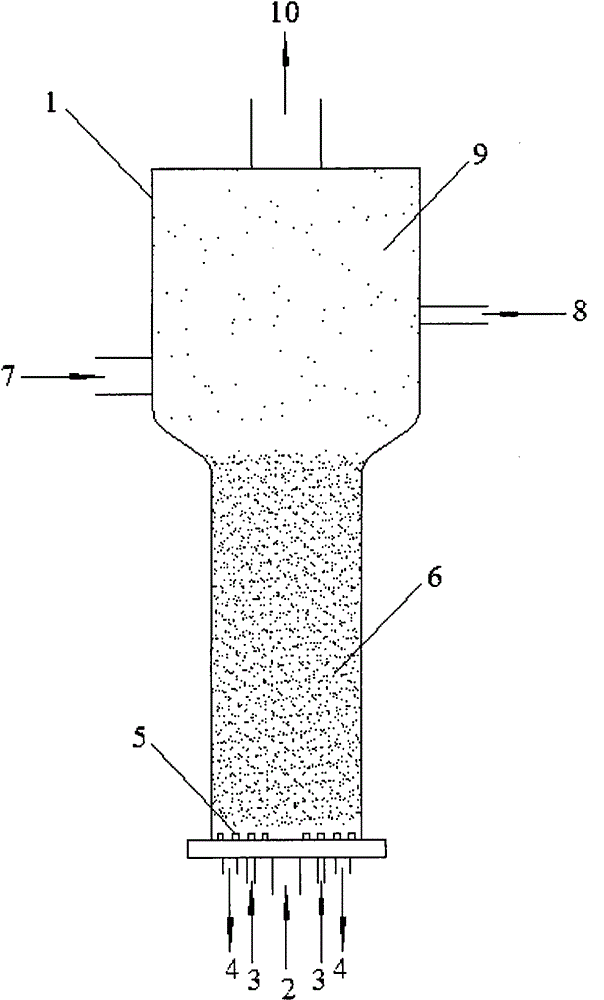

Method and device for producing granular polysilicon

Owner:JIANGSU ZHONGNENG POLYSILICON TECH DEV

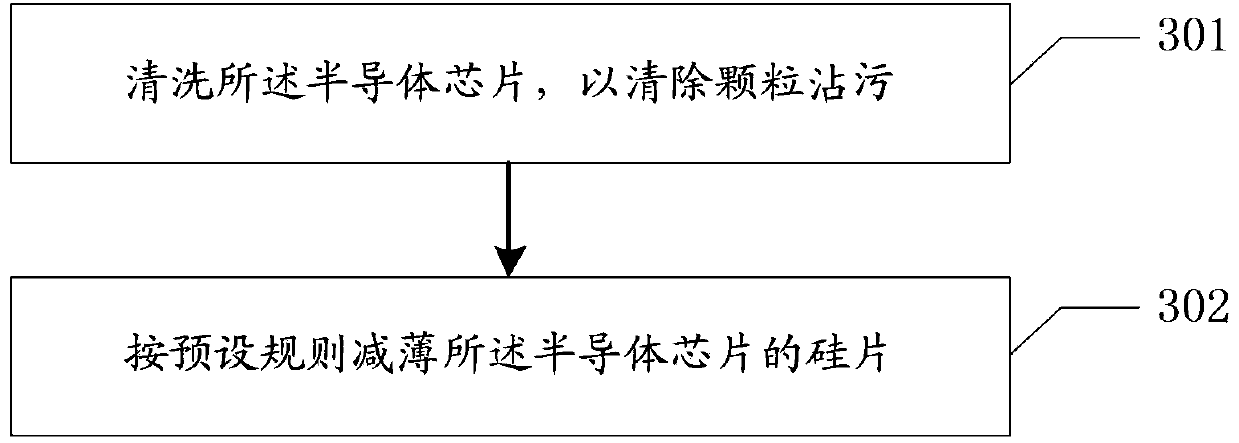

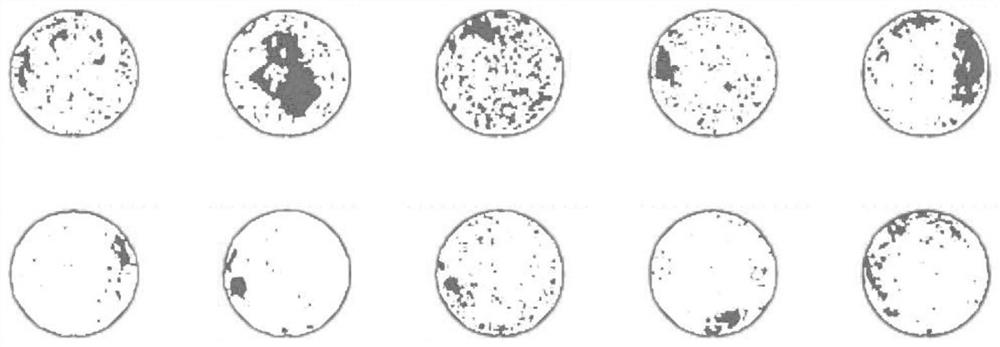

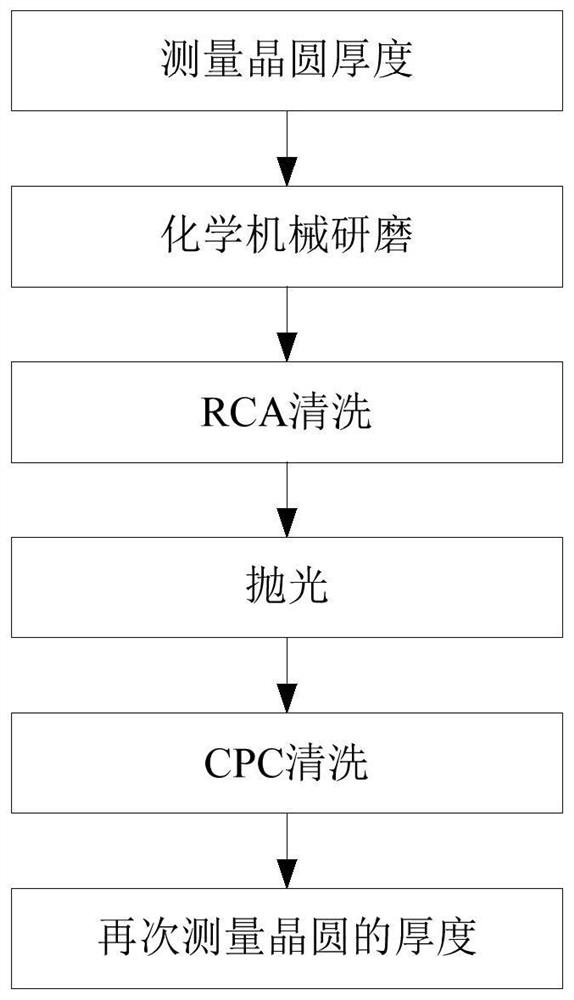

Grinding process for polycrystalline silicon layer and wafer

PendingCN114121637ASemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingPolycrystalline siliconRCA clean

Owner:HEJIAN TECH SUZHOU

Grid-control Darlington electrostatic protection device and manufacturing method thereof

InactiveCN114823660AIncrease current gainSmall emitter junction charging timeTransistorSolid-state devicesElectric current flowPolysilicon gate

The invention discloses a grid-control Darlington electrostatic protection device which comprises a P-type substrate, a first DN-Well region and a second DN-Well region are arranged in the P-type substrate, a first N + injection region and a second N + injection region are arranged on the first DN-Well region, a P-Well region is arranged in the first DN-Well region, a P-BODY region is arranged on the second DN-Well region, and a P + injection region, a third N + injection region and a fourth N + injection region are arranged on the P-BODY region. A first polysilicon gate is arranged between the P + injection region and the third N + injection region, and a second polysilicon gate is arranged between the third N + injection region and the fourth N + injection region. The first NPN triode and the second NPN triode form an NPN type Darlington tube structure, and after the device is conducted, the current gain is far larger than that of a single NPN tube.

Owner:HUNAN NORMAL UNIVERSITY

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap