Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37 results about "Time sequence" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Most commonly, a time series is a sequence taken at successive equally spaced points in time. Thus it is a sequence of discrete-time data. Examples of time series are heights of ocean tides, counts of sunspots, and the daily closing value of the Dow Jones Industrial Average.

Graph convolutional neural network model and vehicle trajectory prediction method using same

PendingCN111931905AImprove forecast accuracyImprove robustnessImage enhancementImage analysisVehicle behaviorTraffic scene

The invention discloses a graph convolutional neural network model and a vehicle trajectory prediction method using the same. The model is composed of an encoder module, a spatial information extraction layer module and a decoder module. The method comprises the following steps: firstly, sampling a predicted vehicle and surrounding vehicles in a traffic scene at a frequency of 5Hz, and collectingposition coordinates and kinetic parameters of each vehicle sampling point, including horizontal and longitudinal coordinates, horizontal and longitudinal vehicle speeds and accelerations; calculatingcollision time TTC between the predicted vehicle and surrounding vehicles according to the coordinates and speeds of the predicted vehicle and the surrounding vehicles, and judging vehicle behaviors;inputting each historical track of the vehicle containing the information into the model, encoding time sequence interaction features in the track, extracting spatial features, summarizing the features into context vectors, and inputting the context vectors into an LSTM decoder to generate future track coordinates of the vehicle. According to the method, the problem that feature information generated by vehicle interaction cannot be obtained by using a traditional recurrent neural network is solved, and the prediction precision of the vehicle trajectory is greatly improved.

Owner:JIANGSU UNIV

Method for identifying human faces based on HMM-SVM hybrid model

ActiveCN101604376AReduce recognition errorsImprove stabilityCharacter and pattern recognitionHuman bodySingular value decomposition

The invention discloses a method for identifying human faces based on an HMM-SVM hybrid model, which comprises the following steps: firstly, sampling human face images from top to bottom by sampling windows; extracting characteristic parameters of each sampling window image by respectively adopting discrete cosine transform (DCT) and singular value decomposition (SVD), and serially connecting the characteristic parameters into one-dimensional observation vectors; then, using the observation vectors of the training images of each human body to train the HMM model of each human body; adopting the Viterbi algorithm to calculate the output probability of the observation vectors of all images corresponding to each HMM model; and using the output probability to support the classified training and the identification test of a vector machine. Because each HMM model has good time sequence modeling ability, the numerical characteristics of each organ of a human face can be effectively combined by a state transfer model to more integrally describe the human face to support the excellent performance of the vector machine in the aspect of classification of limited samples.

Owner:DALIAN UNIV

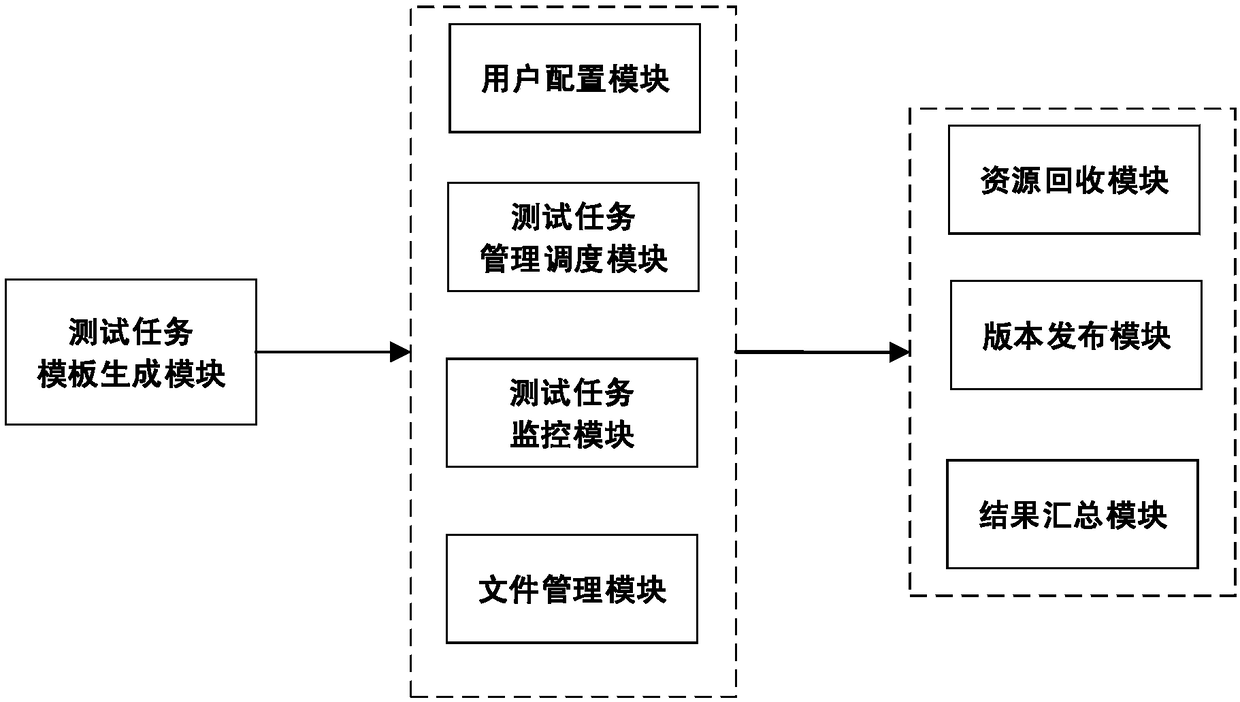

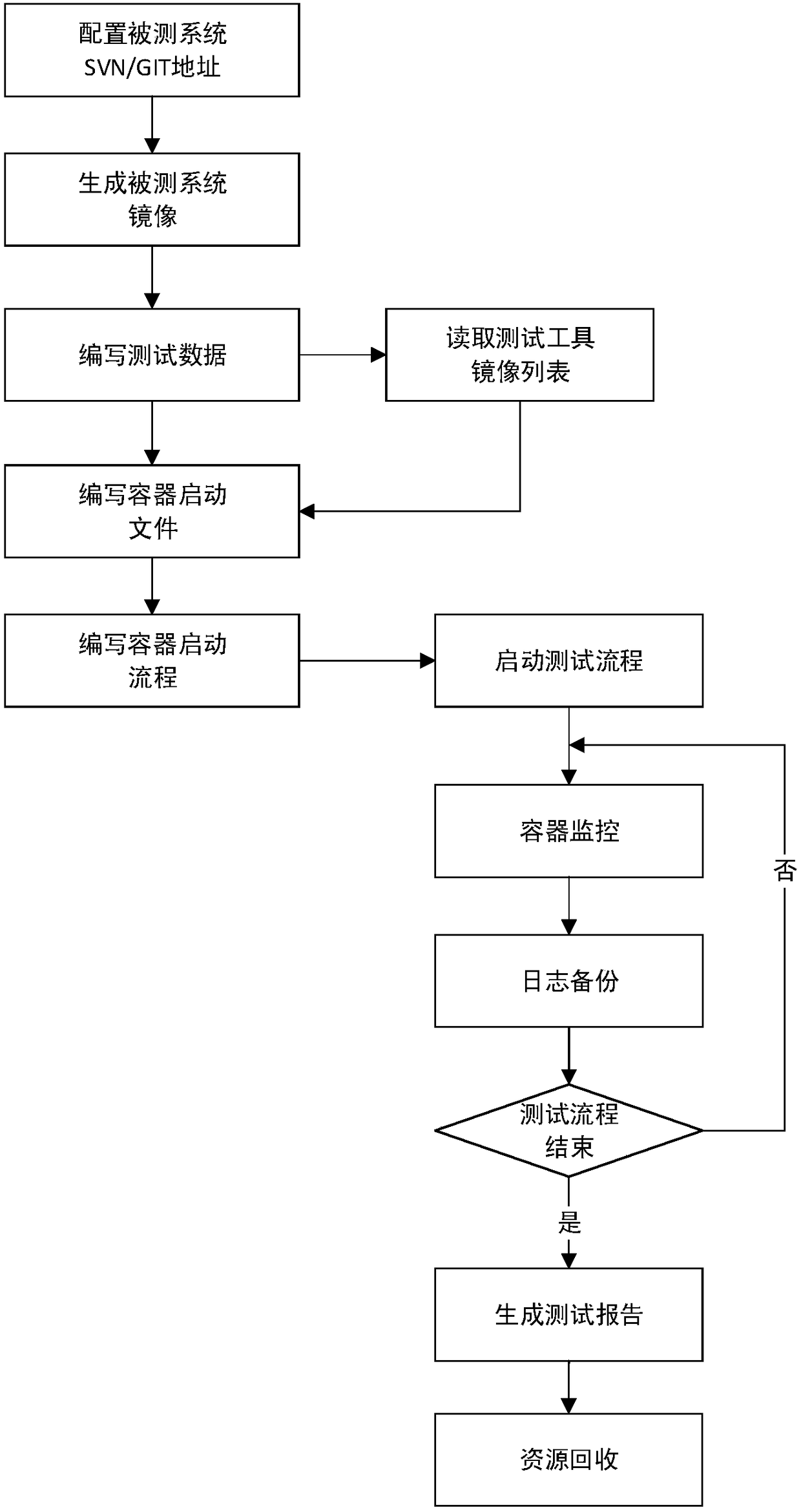

Multi-task scheduling automated testing method and system based on Docker container

Owner:CHINA INTERNET NETWORK INFORMATION CENTER

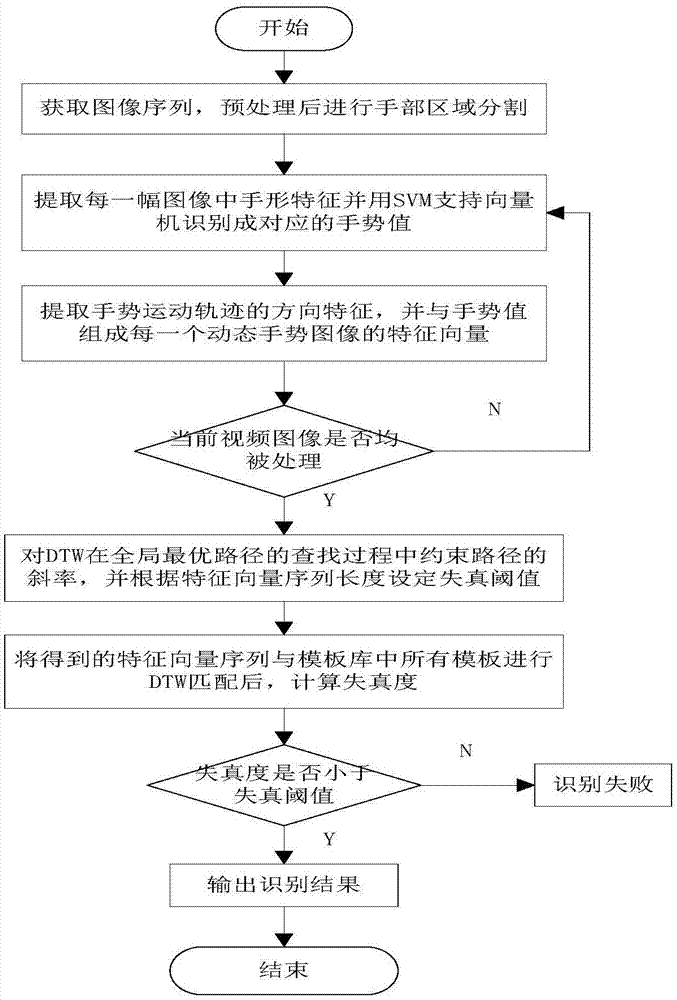

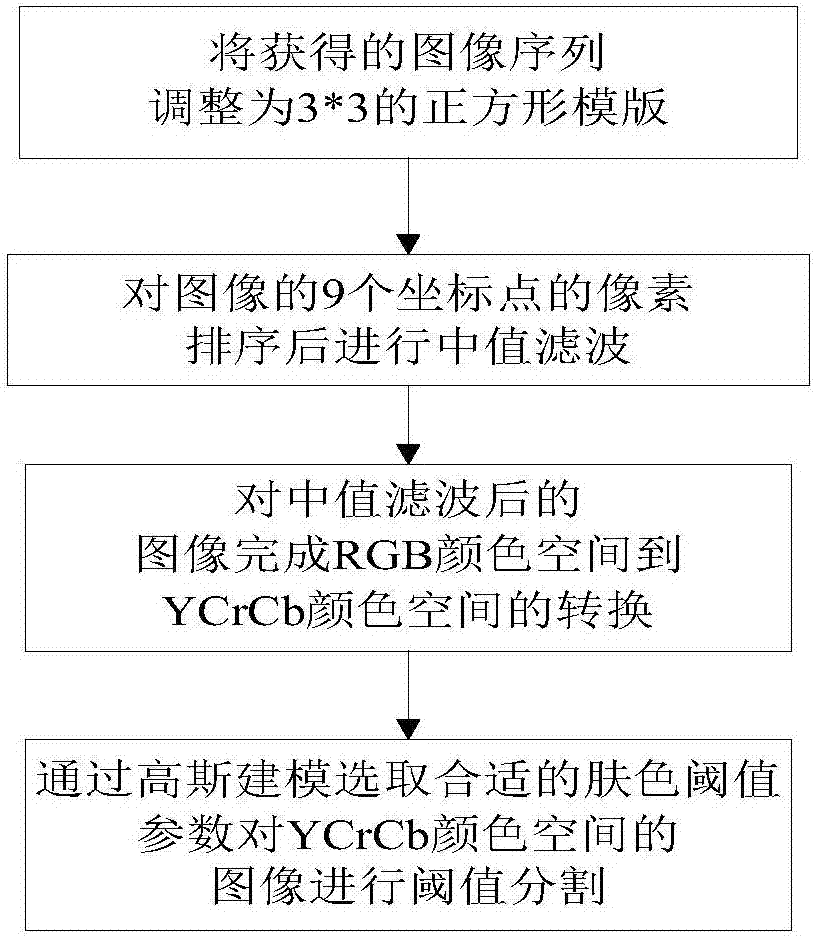

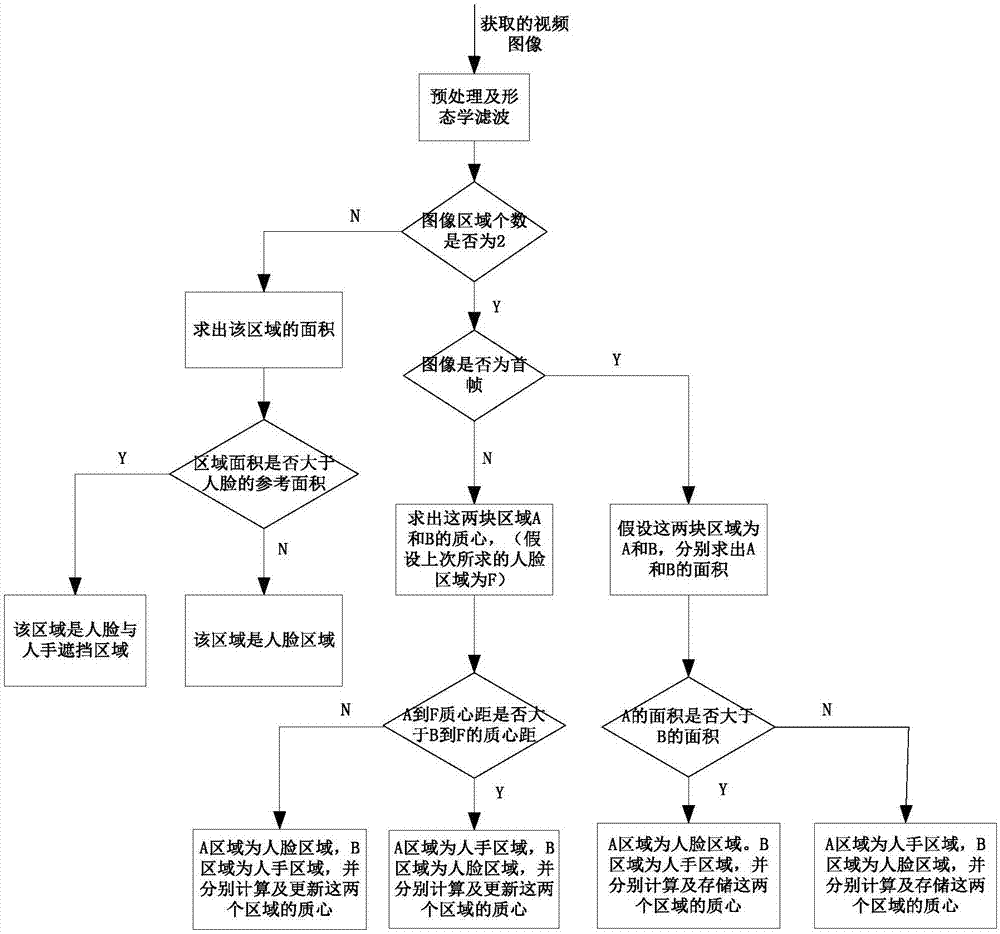

Real-time gesture recognition method

InactiveCN107958218AImprove dynamic gesture recognition rateImprove recognition rateInput/output for user-computer interactionCharacter and pattern recognitionSupport vector machineFeature vector

Owner:NANJING UNIV OF POSTS & TELECOMM

Neuromorphic calculation circuit based on multi-bit parallel binary synaptic array

ActiveCN110378475AReduce power consumptionReduce areaAnalogue/digital conversionElectric signal transmission systemsIntegratorHigh energy

The invention discloses a neuromorphic calculation circuit based on a multi-bit parallel binary synapse array. The neuromorphic calculation circuit comprises a neural axon module, the multi-bit parallel binary RRAM synapse array, a time division multiplexer, a plurality of integrators and a shared successive approximation analog-to-digital converter, wherein the neural axon module comprises two basic units, namely a time sequence scheduler and an adder, and the time sequence scheduler is used for arranging the time sequence of signals, so that input signals are sequentially input into a multi-bit parallel binary RRAM synapse array by adopting a dendritic priority strategy; the adder is used for expanding the array scale, and when the configured neural network input layer is greater than the input of one RRAM array, the adder is used for adding the calculation results of the plurality of arrays to obtain the output of the network layer. Compared with the current system, the method has the advantages of high precision and low power consumption, can be configured into most deep neural network applications, and is particularly suitable for being deployed in edge computing equipment with high energy consumption requirements.

Owner:ZHEJIANG UNIV

Rotatory inertia piezoelectric actuator comprising dual-rhombic series driving mechanism and actuation method

ActiveCN106208806AChange the status quo of power-off unlockingReduce assembly requirementsPiezoelectric/electrostriction/magnetostriction machinesInterference fitPiezoelectric actuators

The invention discloses a rotatory inertia piezoelectric actuator comprising a dual-rhombic series driving mechanism and an actuation method. The actuator consists of an upper baffle, a lower baffle, a bearing, a rotary output shaft, the dual-rhombic series driving mechanism and piezoelectric stacks, wherein the dual-rhombic series driving mechanism comprises series dual-rhombic rings; the piezoelectric stacks are in interference fit inside the series dual-rhombic rings; a friction block is arranged at a series joint of the piezoelectric stacks; the rotary output shaft of the actuator is connected with the upper baffle and the lower baffle through the bearing respectively; and the dual-rhombic series driving mechanism is fixedly assembled between the upper baffle and the lower baffle. After finish of assembly, a side face of the friction block is in close contact with the rotary output shaft, and the actuator can drive a load to output bidirectional rotary motion by control of voltage time sequences and amplitudes of the piezoelectric stacks. The rotatory inertia piezoelectric actuator has the characteristics of easiness in assembly, quick response and accurate action.

Owner:XIAN LONGWEI TECH CO LTD

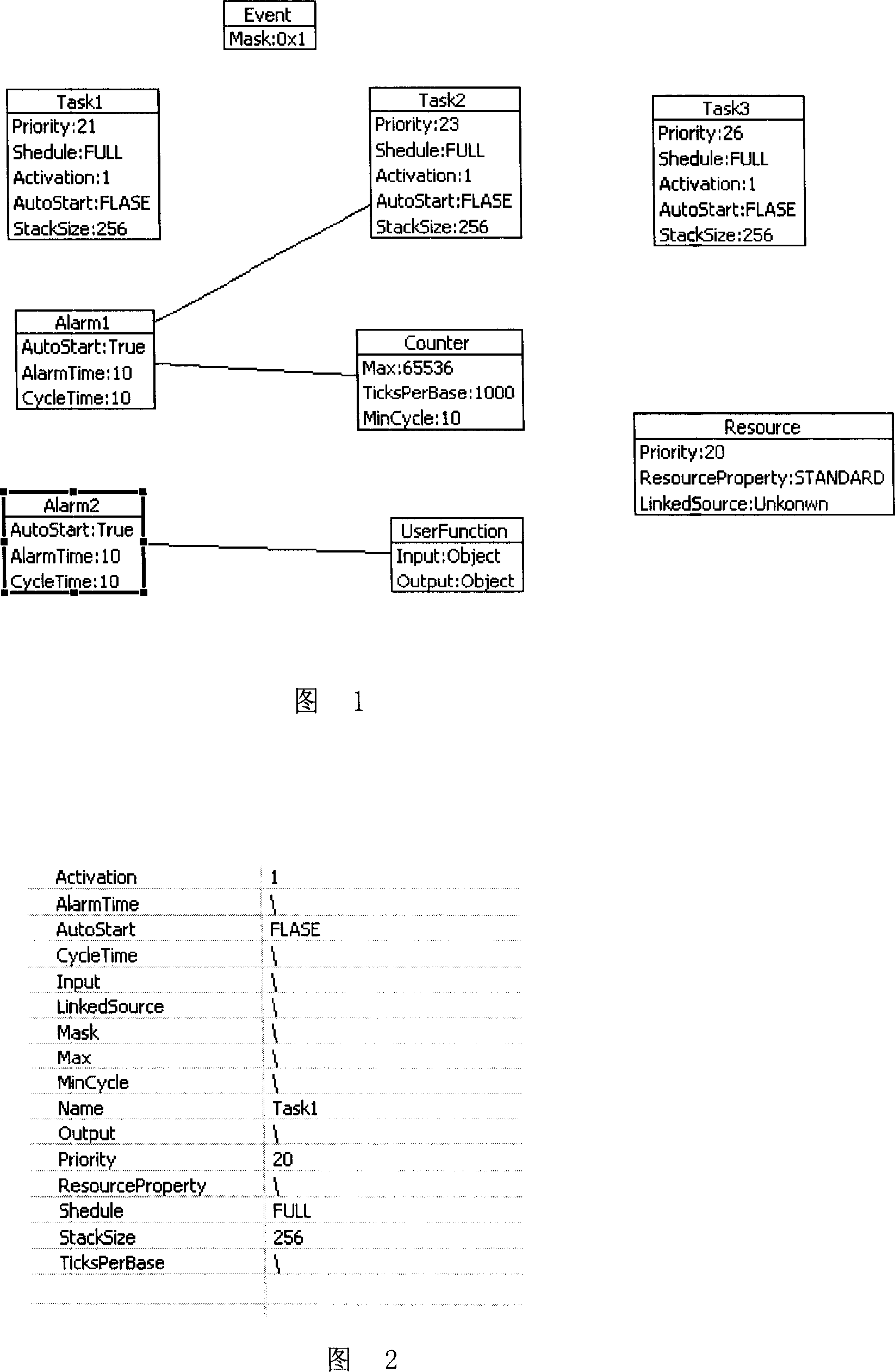

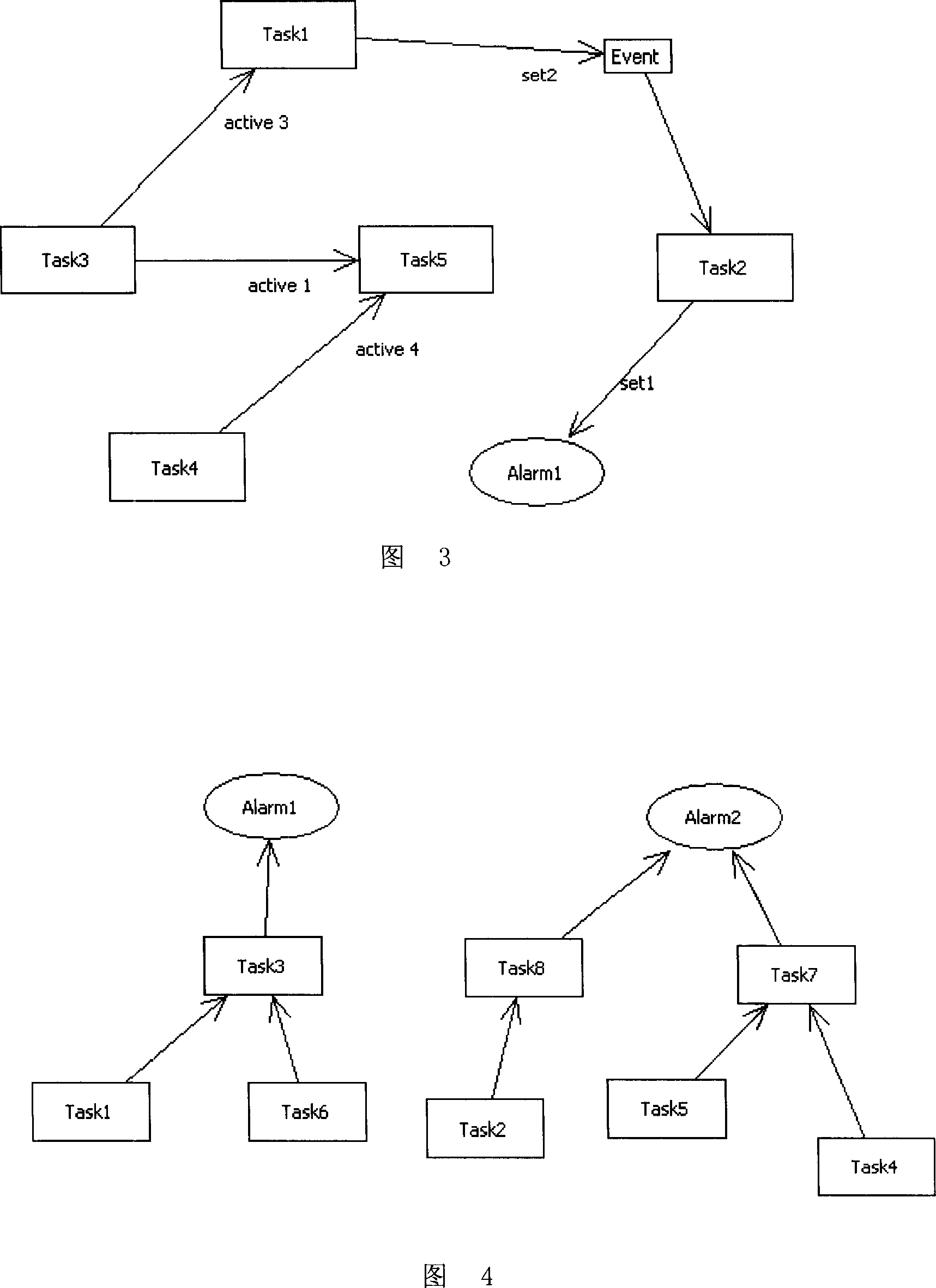

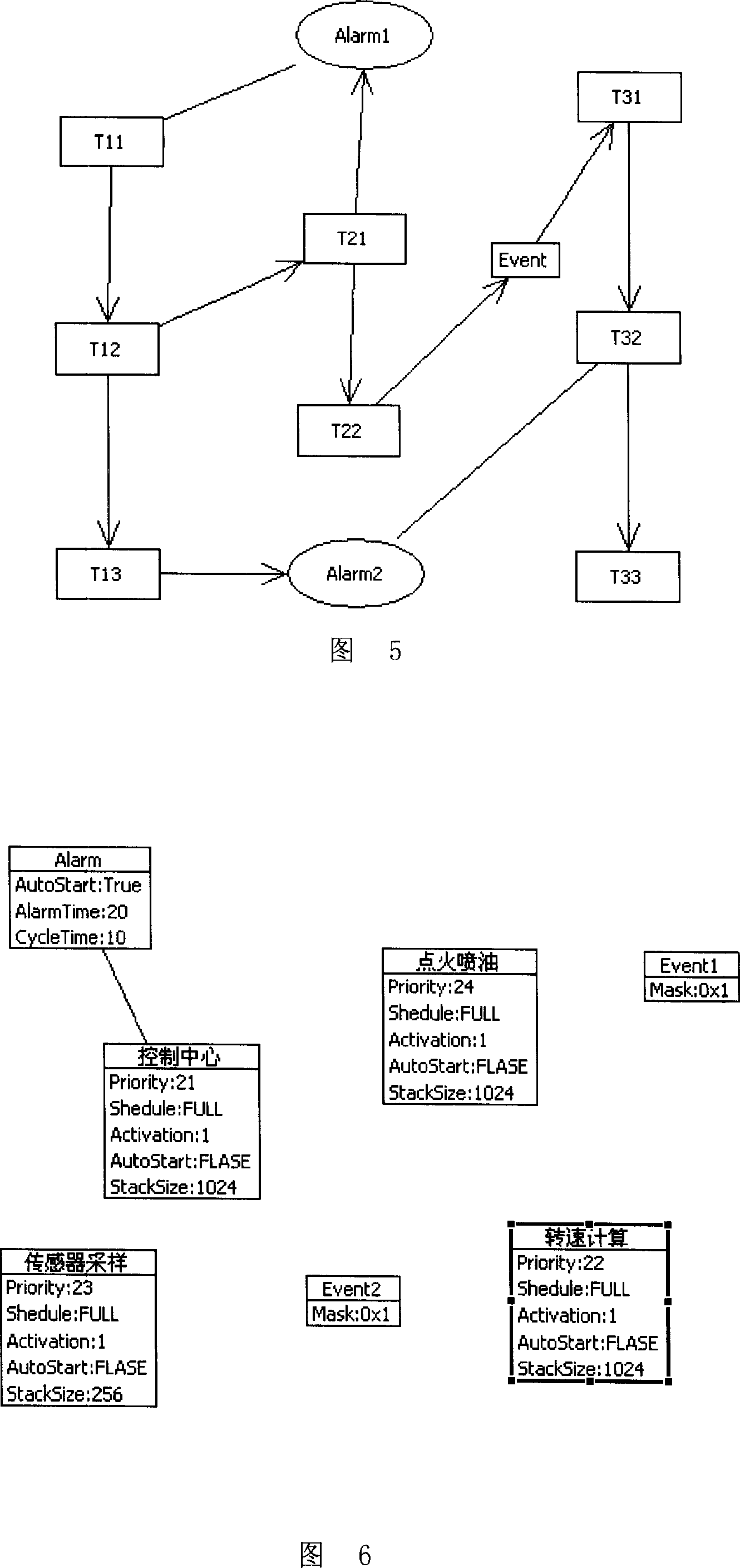

Modeling method for embedded type real-time operating system based on model

InactiveCN1996237AMake up for incompatibilitiesImprove accuracySpecific program execution arrangementsModel methodOperational system

Owner:ZHEJIANG UNIV

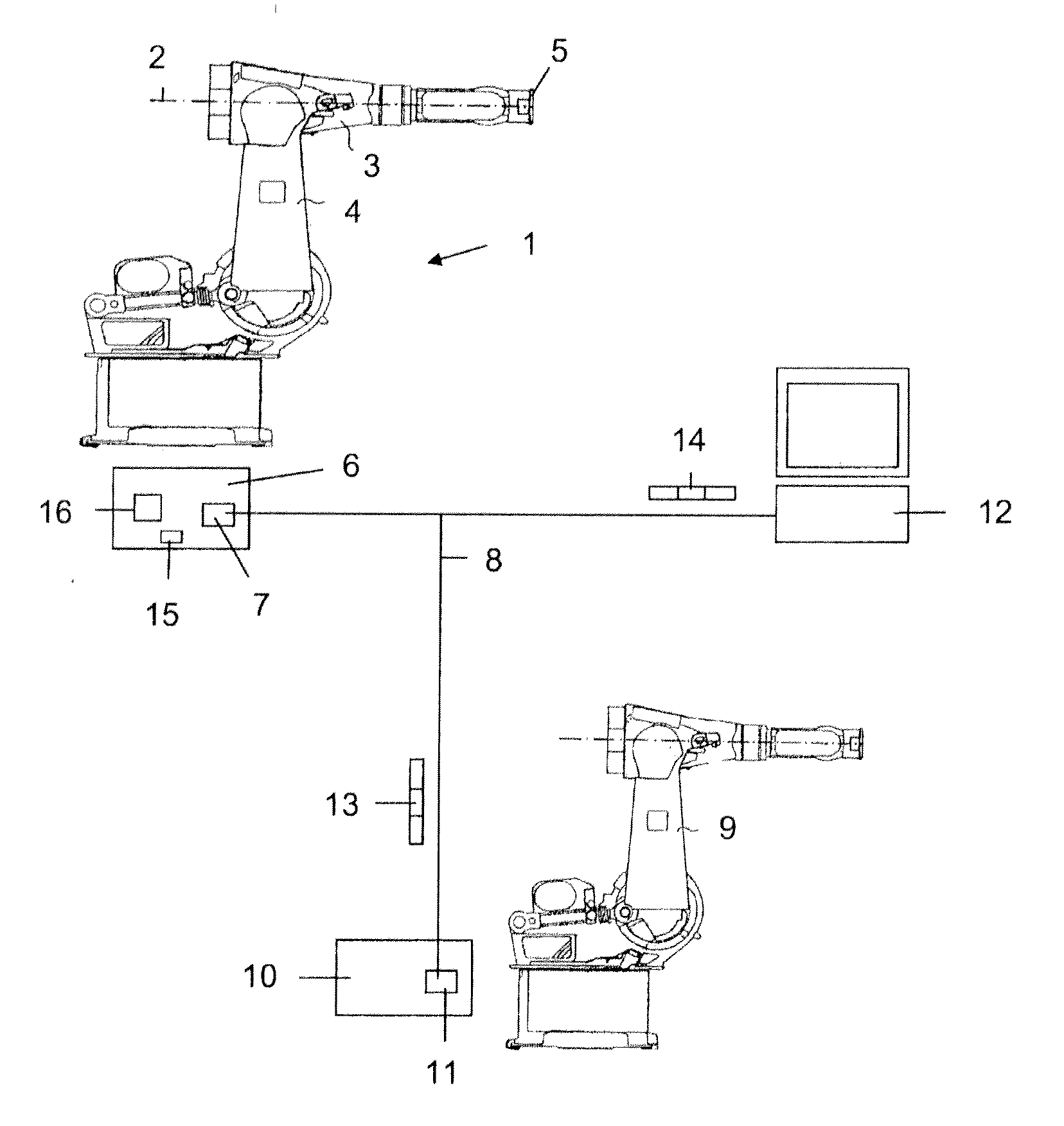

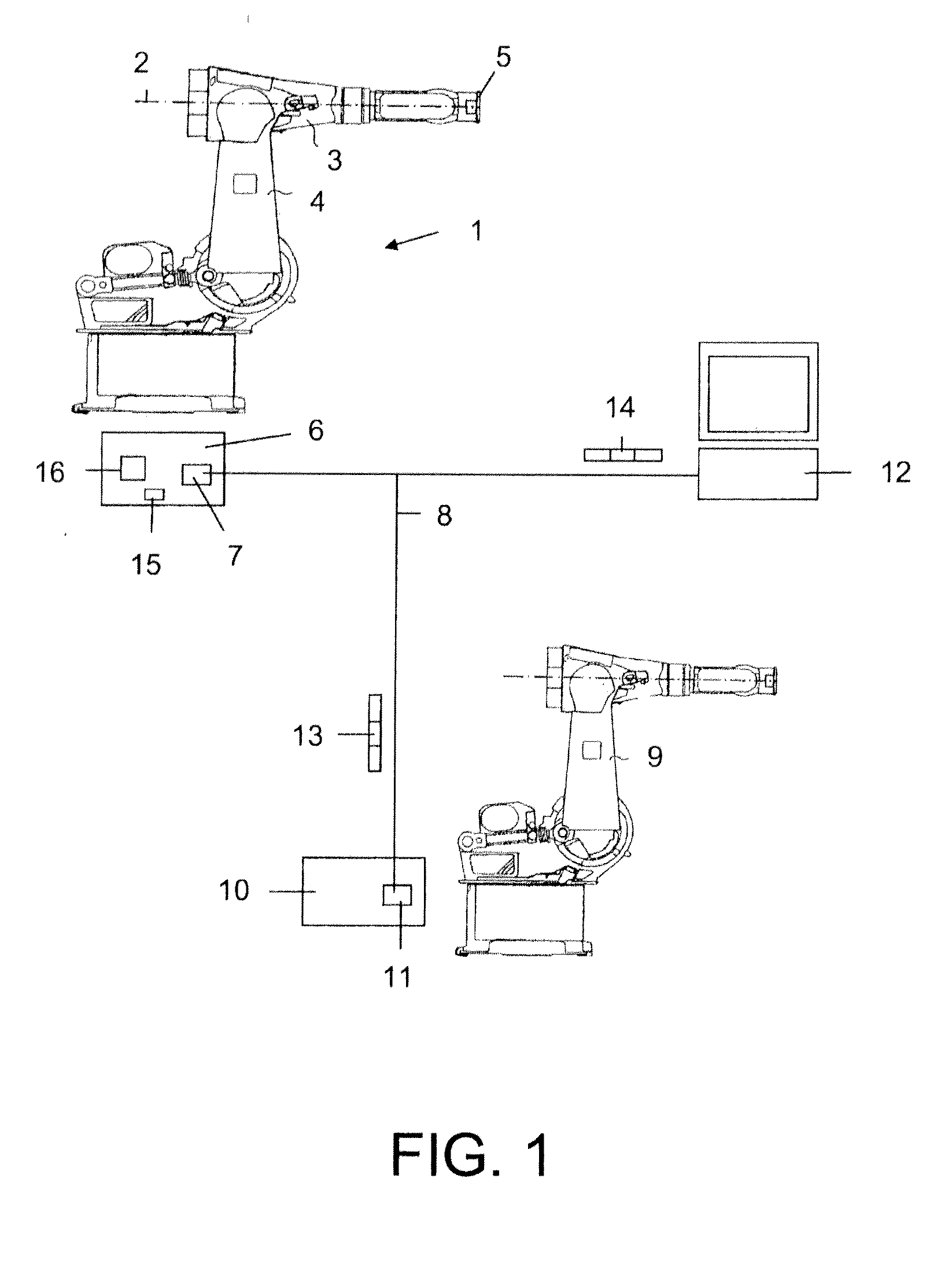

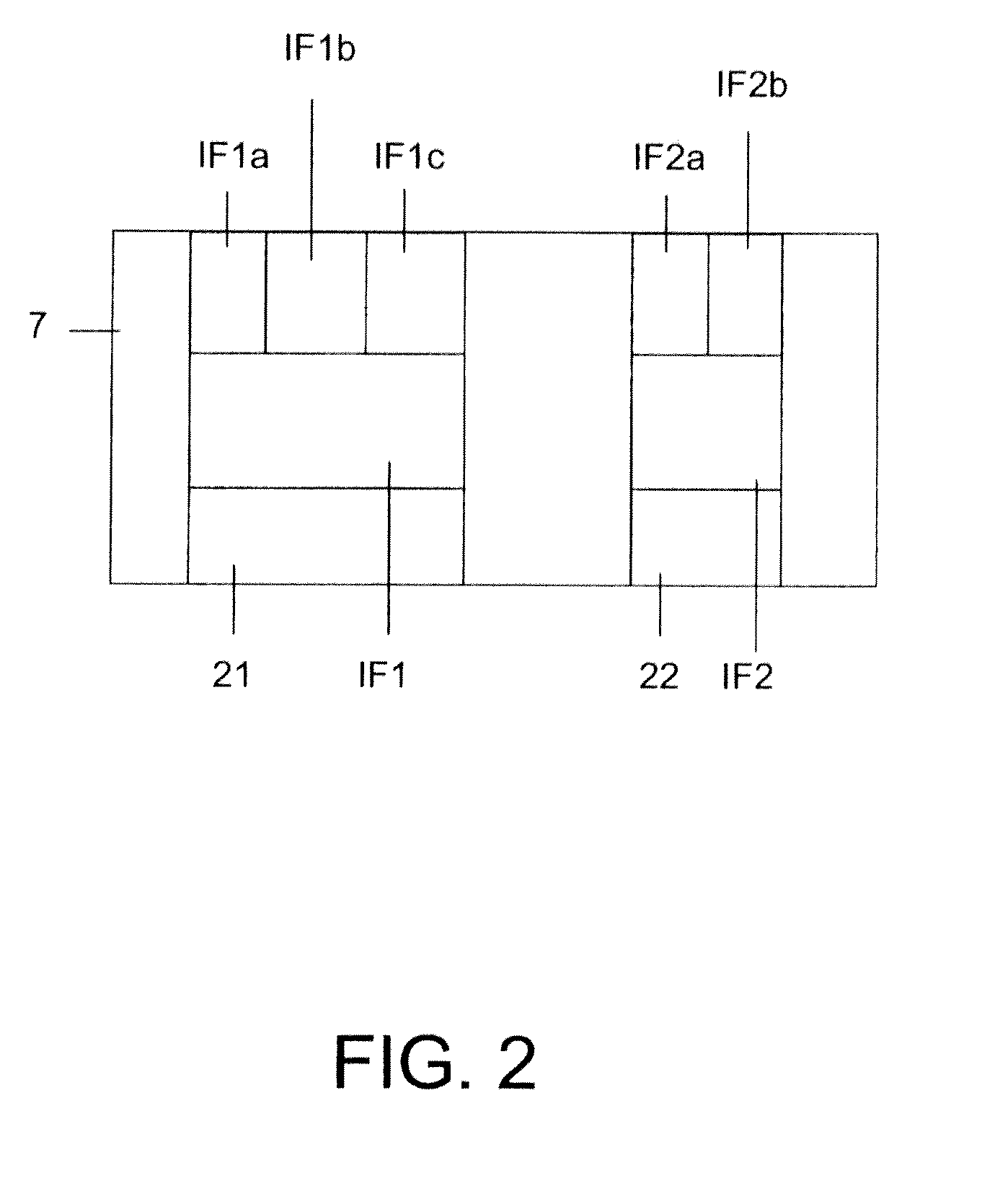

Data processing system for an industrial robot and method for managing available resources thereof

ActiveUS20100324730A1Improve service qualityData switching networksSpecial data processing applicationsData processingTime sequence

Owner:KUKA LAB GMBH

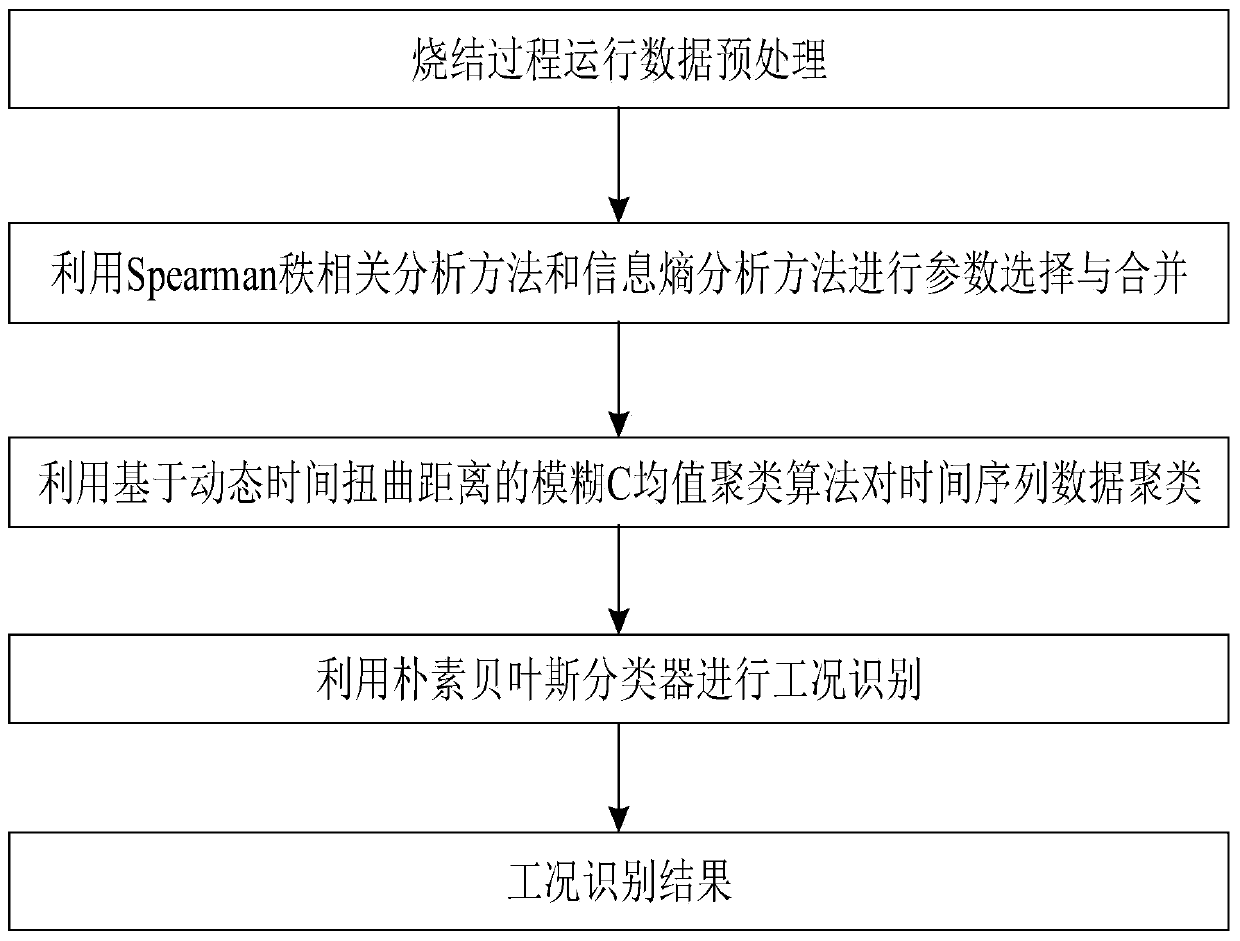

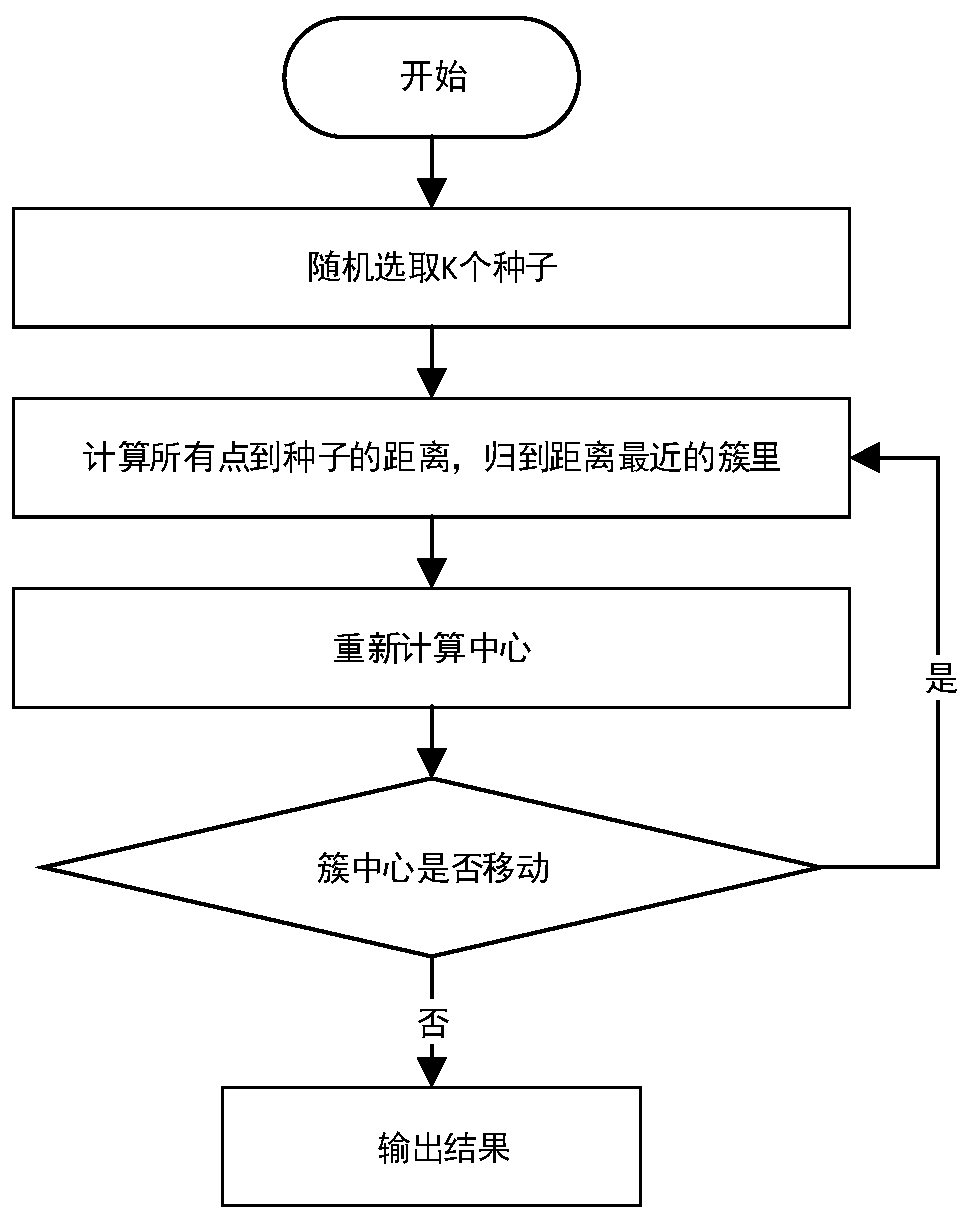

Sintering process working condition identification method and system considering time sequence

ActiveCN110245850AEfficient identificationCharacter and pattern recognitionResourcesCluster algorithmNaive Bayes classifier

Owner:CHINA UNIV OF GEOSCIENCES (WUHAN)

Non-volatile memory system and method with variable error correcting capability

InactiveCN101499325ARealize the ability to adjust and correct errorsOptimal error correction configurationCode conversionStatic storageComputer moduleBus interface

The invention discloses a nonvalatile memory system with variable error correcting capability, which comprises a system bus interface module, an RS encoder, an RS decoder, an NAND read-write time sequence generator and an error correcting capability configuration module. The error correcting capability configuration module carries out order input and error correcting information feedback with outside world through the bus interface module. The error correcting capability configuration module carries out error correcting capability configuration to the RS encoder and the RS decoder respectively in accordance with instructions and outputs feedback information obtained from the RS encoder and the RS decoder respectively through the bus interface module. The system takes both speed and error correcting capacity into consideration, thus realizing the error correcting capacity adjustment in various environments so as to obtain the best error correcting configuration.

Owner:ARKMICRO TECH

MRI apparatus

InactiveUS20080211496A1Measurements using NMR imaging systemsElectric/magnetic detectionImaging conditionOrder set

An MRI apparatus for performing an MRI examination to an object by sequentially applying an imaging method group, which is constituted by time-sequentially arranging a plurality of different imaging methods, to each of the imaging methods, has an imaging method group setting unit, a performing order setting unit and an imaging condition setting unit. The imaging method group setting unit sets the imaging method group. The performing order setting unit sets a performing order as a performing order of the imaging methods constituting the imaging method group. The imaging condition setting unit sets an imaging condition to each of the imaging methods. The workflow setting unit obtains an examination history data corresponding to the imaging method group, the performing order and the imaging condition from the examination history data previously stored to a storage unit, and sets a first workflow relating to the MRI examination by estimating an imaging time of each of the imaging methods in the performing order based on the obtained examination history data.

Owner:TOSHIBA MEDICAL SYST CORP

Method for building fractal dimension-based multi-phase mixed effect prediction model

ActiveCN101930501ATimely adjustmentTimely analysisSpecial data processing applicationsHigh rateTime delays

Owner:KUNMING UNIV OF SCI & TECH

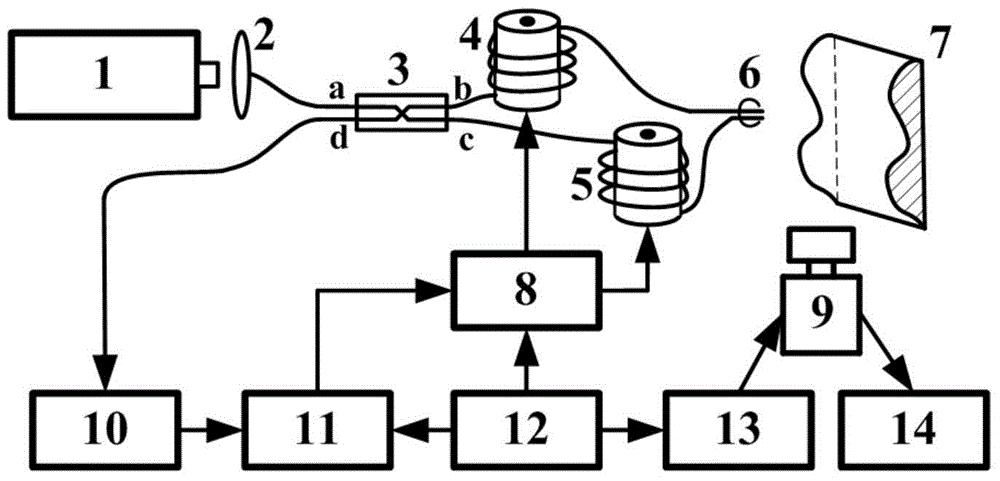

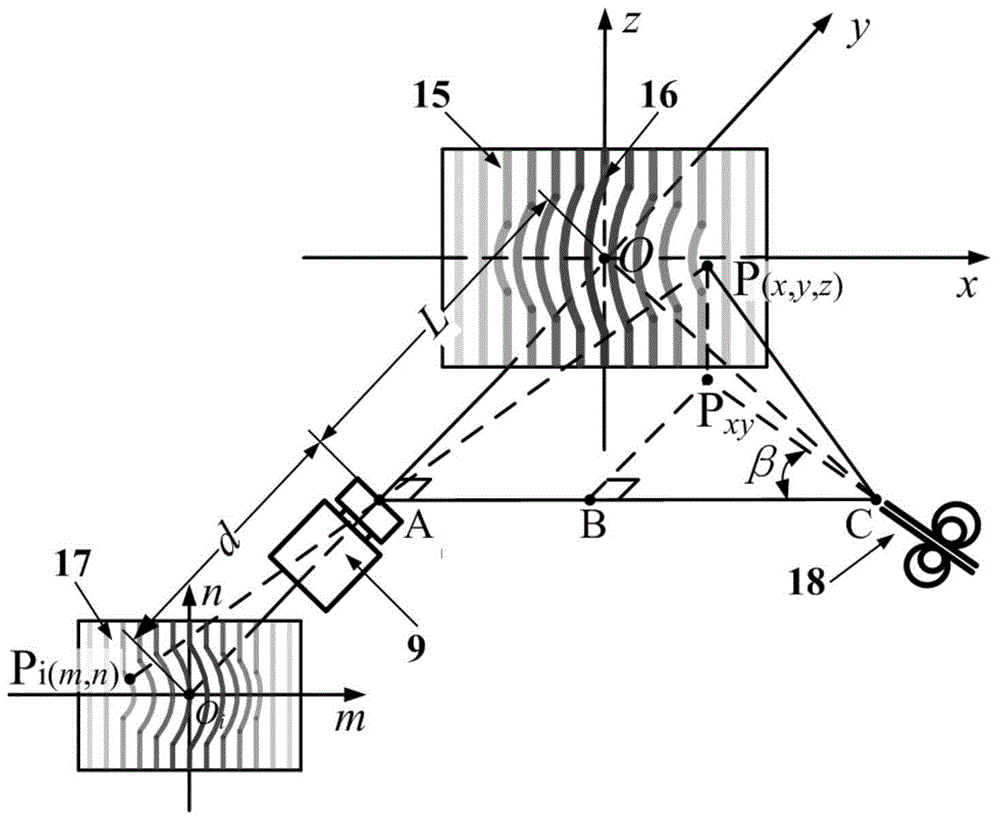

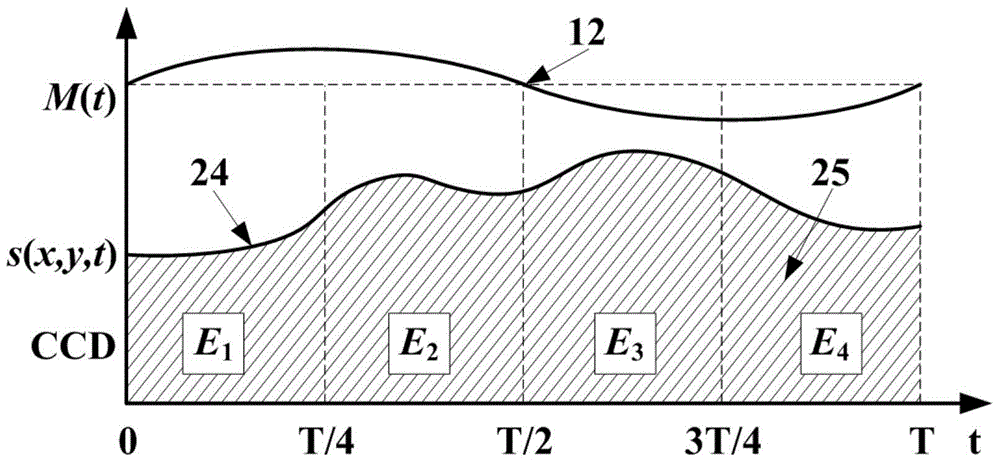

Three-dimensional shape measuring system of fringe projection based on sine phase modulation four-step integral

InactiveCN103983211AEliminate Phase DriftMeet contactlessUsing optical meansMathematical modelCarrier signal

Owner:TIANJIN UNIV

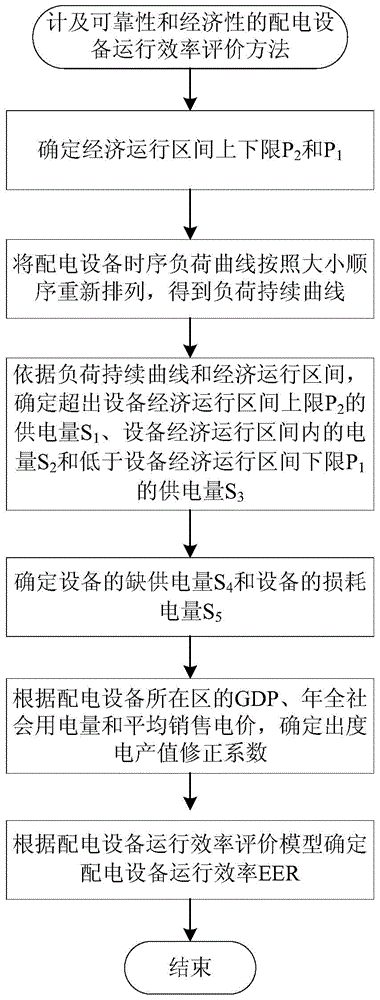

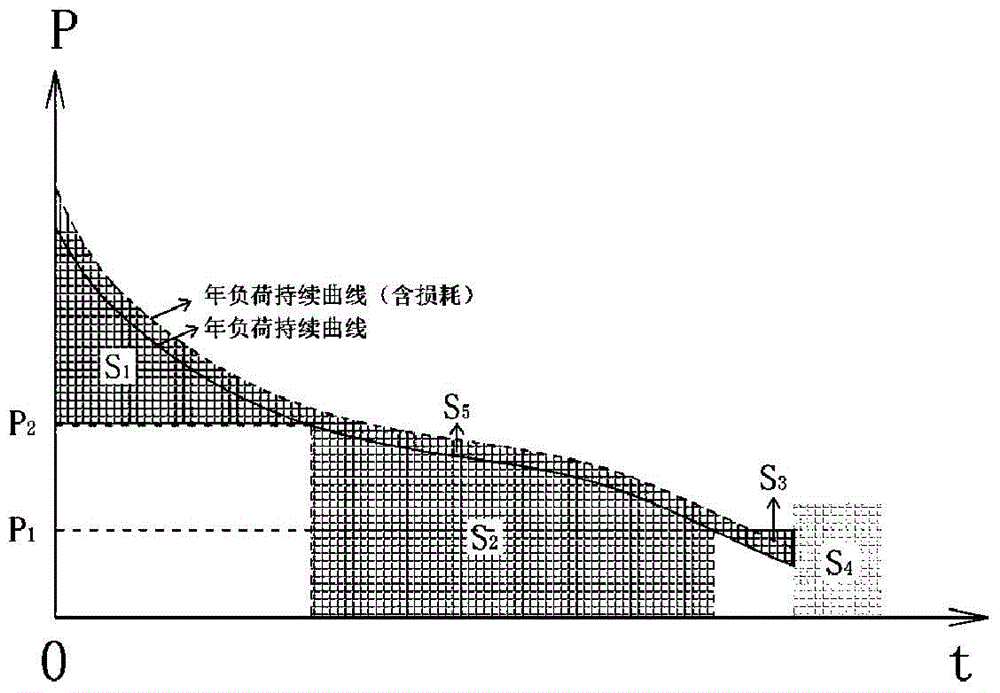

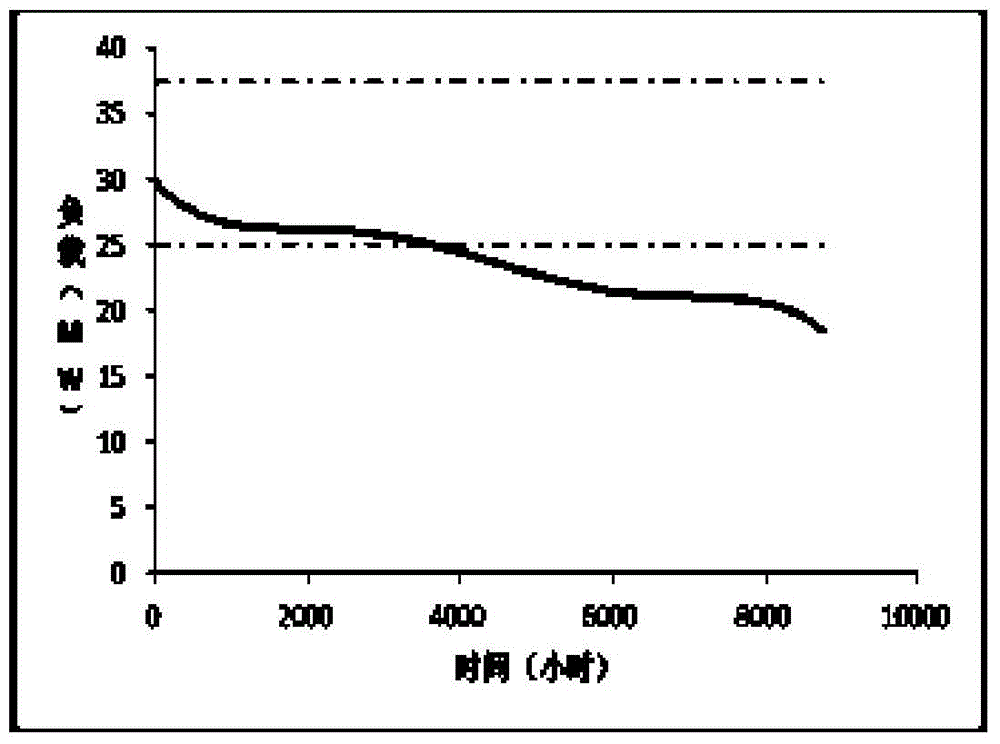

Distribution equipment operation efficiency evaluation method involving reliability and economy

ActiveCN105023194AAccurately and objectively reflectData processing applicationsSystems intergating technologiesTime domainLower limit

Owner:STATE GRID CORP OF CHINA +3

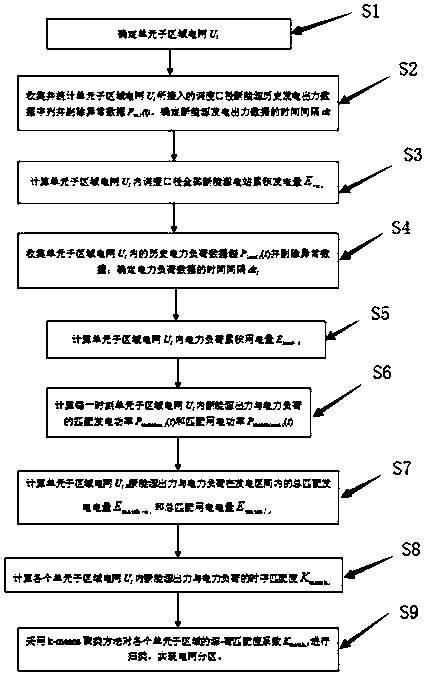

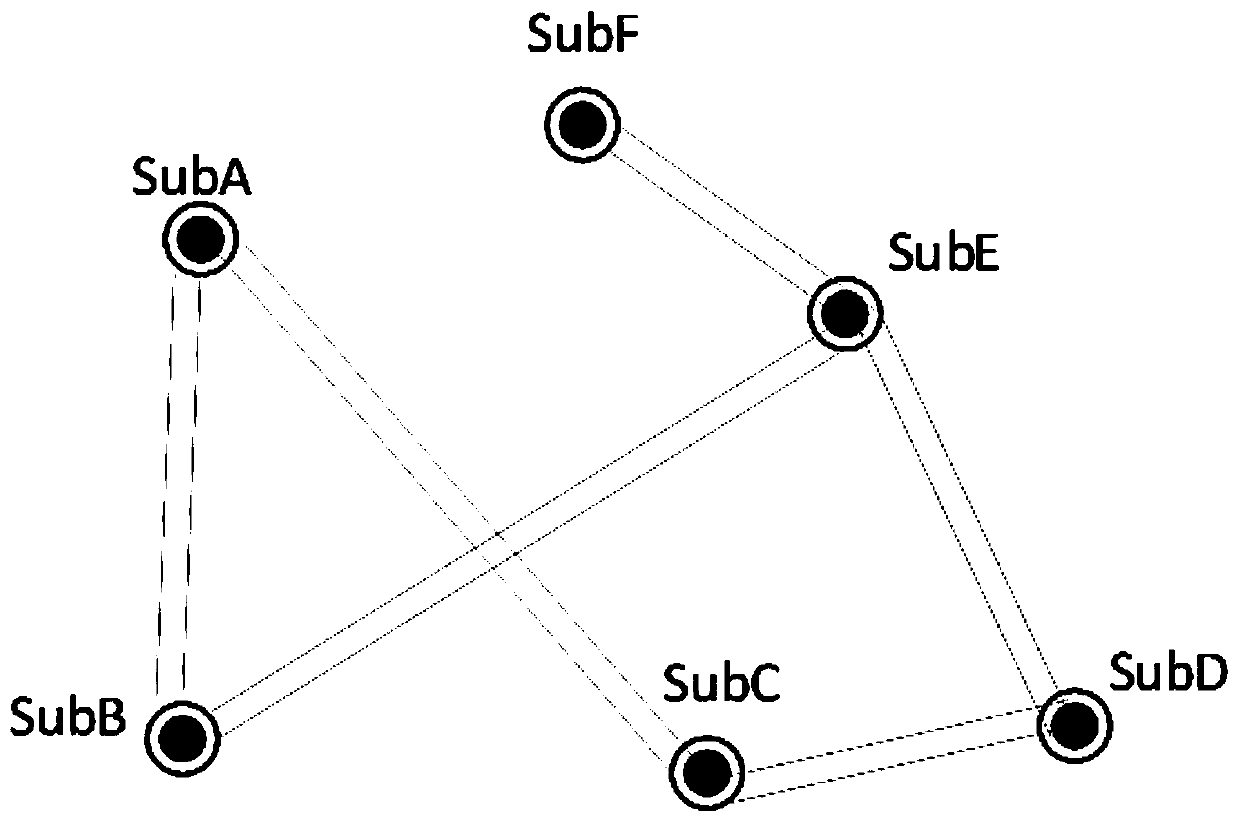

Power grid optimization partitioning method for new energy consumption analysis

ActiveCN110635506AClear processData sources are readily availableSingle network parallel feeding arrangementsTechnology managementNew energyEngineering

Owner:STATE GRID ZHEJIANG ELECTRIC POWER CO LTD JIAXING POWER SUPPLY CO +1

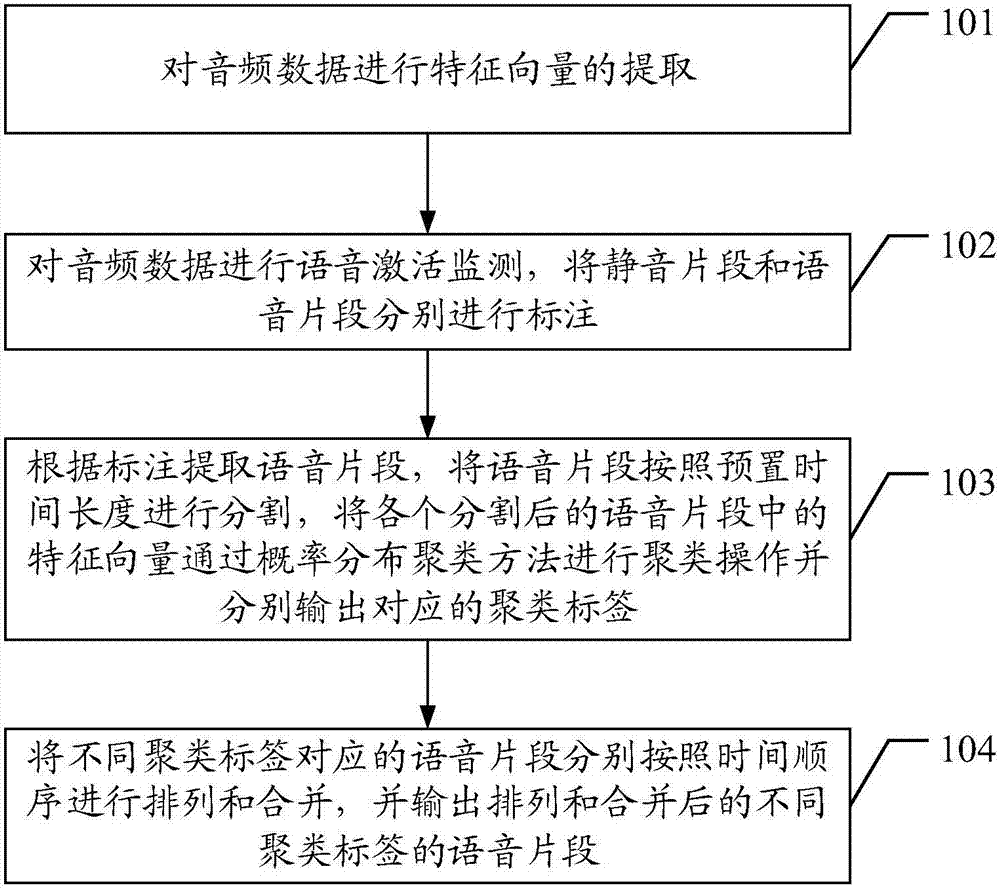

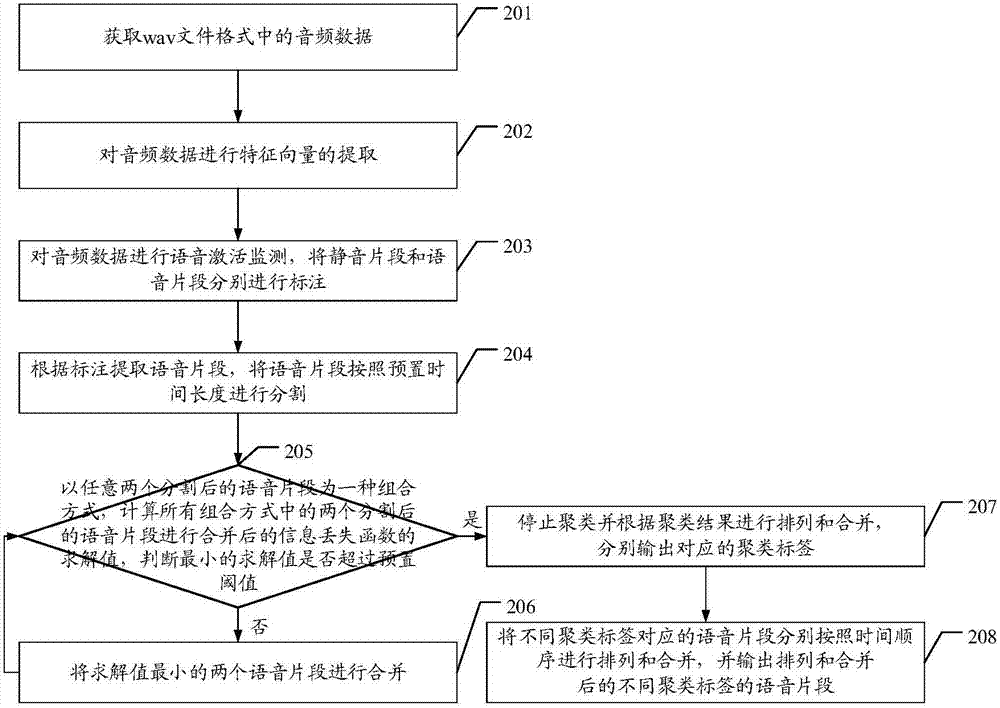

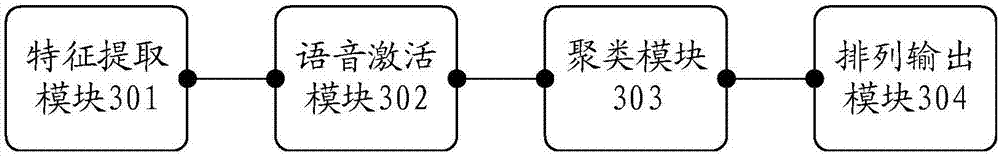

Human voice segmentation method and device

ActiveCN107967912AReduce workloadSolve technical problems that are inefficient and time-consumingSpeech recognitionFeature vectorChronological time

Owner:SPEAKIN TECH CO LTD

Light-controlled light exchange structure adopting multiband mark

InactiveCN1404236AImprove efficiencyIncrease exchange speedFibre transmissionSelection arrangementsLength waveLight switch

The present invention relates to a light exchanging structure which is operated by the light and applies multiwavelength mark. The light exchanging matrix is composed of the array of light-operated light switch, the light grouping head is to be marked by the light impulse of several different wavelengthes and each combination of light impulses in different wavelenghes represents a different route information. The light impulse of different bit in light grouping head will control the light switch with different row and column in the light switch array separately according to the differences of timing sequence and optional wavelength so as to realize light route selection. The light grouping head to directly control the light operated light switch can avoid the light-electric conversion in conventional light exchanging to let the control course of the whole exchanging be realized in light

Owner:SHANGHAI JIAOTONG UNIV +1

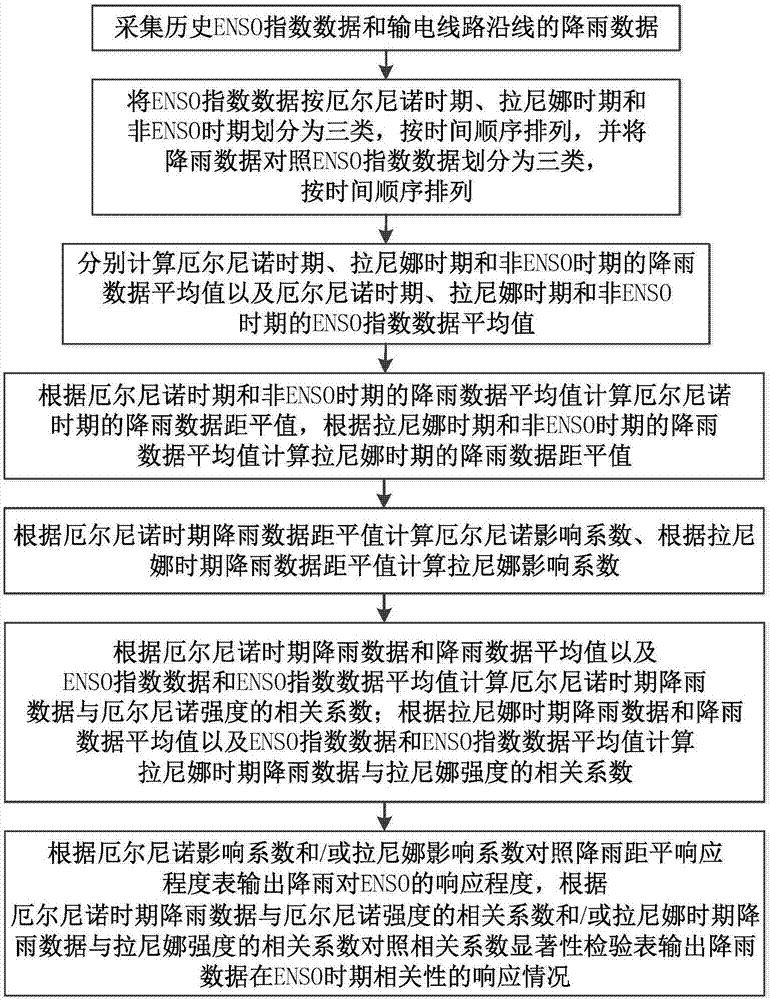

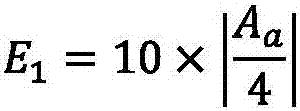

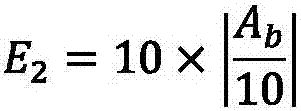

Method for calculating response degrees of rainfall along electric transmission lines and system thereof

ActiveCN107092793AImprove targetingReduce lossesSpecial data processing applicationsInformaticsLa NiñaChronological time

Owner:STATE GRID HUNAN ELECTRIC POWER +2

Classification device

ActiveCN104382375AAccurate classificationImprove classification efficiencyBook cabinetsEngineeringPaper sheet

A classification device comprises a base, two supporting plates, a fixing shaft, a fixing disc and a rotating part. The two supporting plates are parallelly arranged on the base. Two ends of the fixing shaft are respectively and fixedly arranged on the two supporting plates. The fixing disc is fixedly arranged on the fixing shaft and provided with a paper inlet. The rotating part comprises a rotating wheel, a rotating ring, a plurality of partition plates and a plurality of doorway pages, wherein the rotating wheel is rotatably arranged on the fixing shaft, the partition plates are radially and fixedly arranged on the rotating wheel, the rotating ring is fixedly connected with the sides away from the rotating wheel, of the partition plates, and the doorway pages are rotatably arranged on the partition plates. Each pair of adjacent partition plates, the fixing disc and the rotating ring define an accommodating cavity. The rotating part of the classification device is rotatably matched with the fixing disc through the rotating wheel, the rotating ring and the partition plates, accordingly printing paper can be accurately classified in time sequence, and the classification efficiency is also high.

Owner:XUZHOU BO GEN CONSTR DEV GRP CO LTD

Non-contact synchronous measuring instrument for subgrade and rail vibration

InactiveCN101915603AAvoid the influence of human factorsRealize intelligenceSubsonic/sonic/ultrasonic wave measurementUsing wave/particle radiation meansVibration amplitudeStatic random-access memory

The invention relates to a non-contact synchronous measuring instrument for subgrade and rail vibration. A CCD (Charge Coupled Device) drive circuit is respectively connected with a CCD video signal binaryzation processing unit, an A / D and SRAM (Static Random Access Memory) working time sequence controller and an address counter time sequence generator and used for providing a necessary working pulse for a CCD and generating an interface signal between the CCD drive circuit and a data acquisition card; and the output of the CCD video signal binaryzation processing unit and the outputs of the A / D and SRAM working time sequence controller and the address counter time sequence generator are connected with a data acquisition interface circuit based on a parallel interface. By computer control automatic measurement, the invention greatly prevents the influence of human factors, realizes the intellectualization of detection, solves the synchronous problem of two different vibration frequencies and vibration amplitudes by non-contact synchronous measurement and can carry out software calibration at random, thereby preventing precision reduction caused by long-term use. A photoelectric probe is just dedusted regularly without replacing a detecting probe regularly.

Owner:TIANJIN UNIV

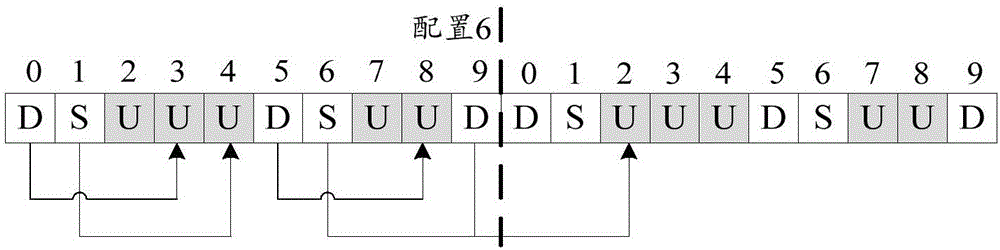

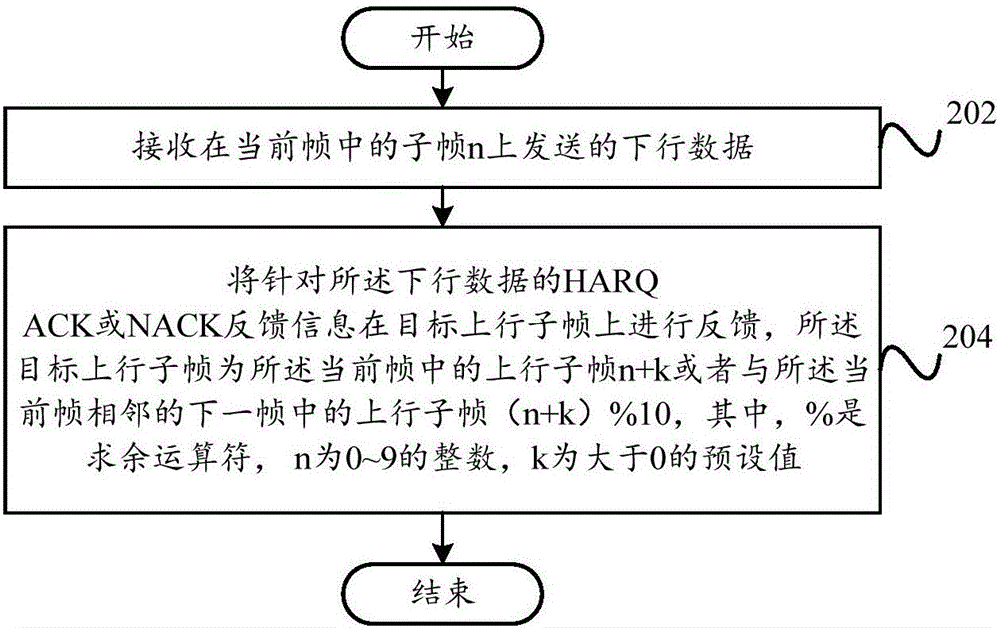

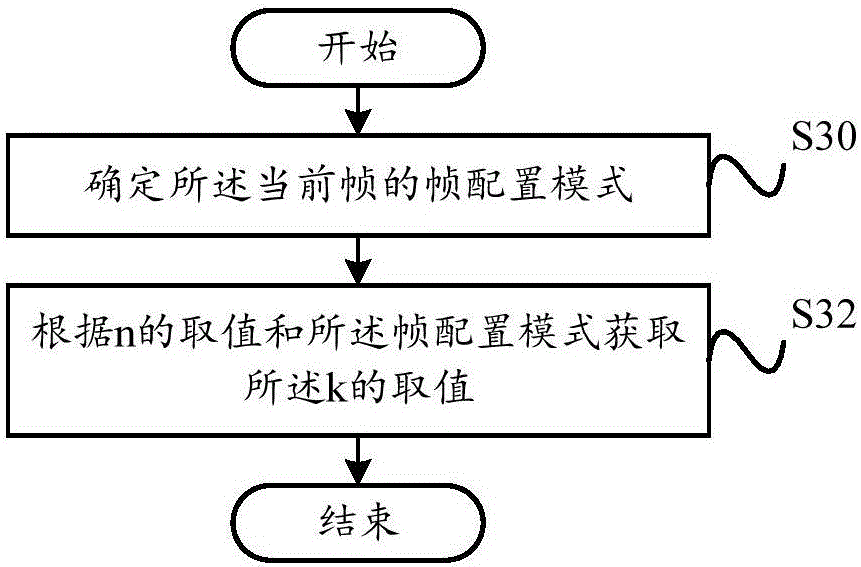

Downlink HARQ feedback method and device under TDD system

InactiveCN106411482AError prevention/detection by using return channelSignal allocationTelecommunicationsTime sequence

Owner:MEIZU TECH CO LTD

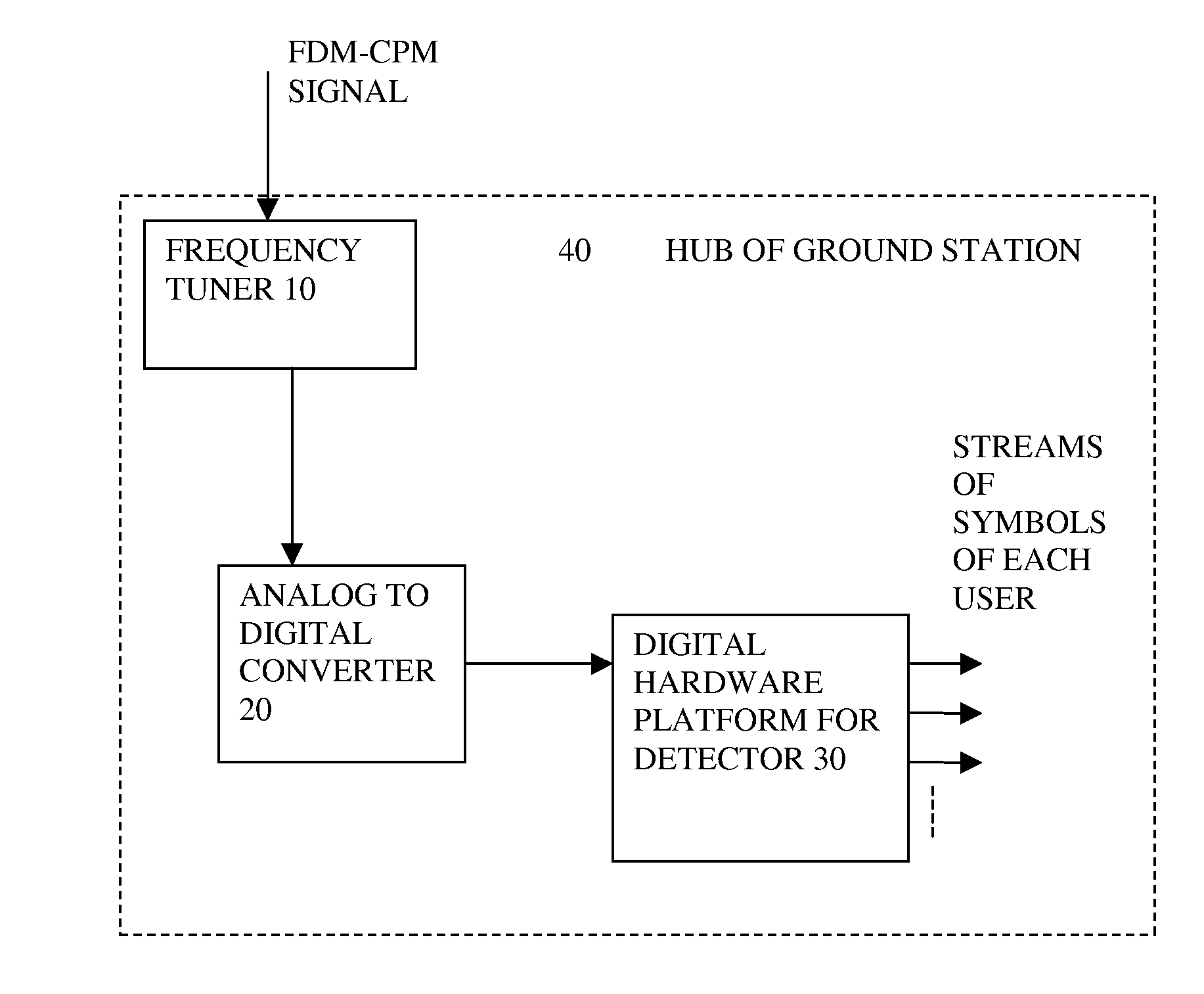

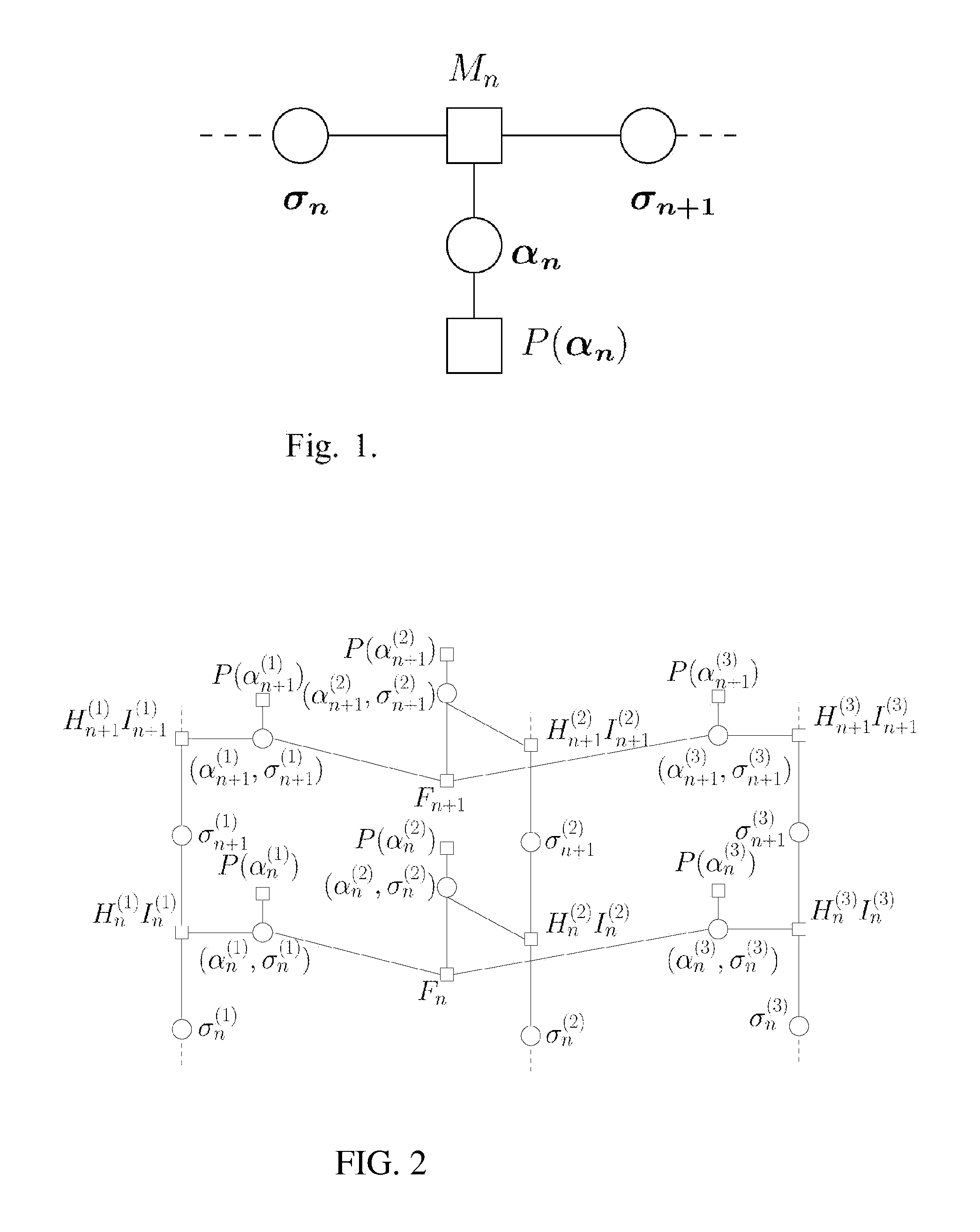

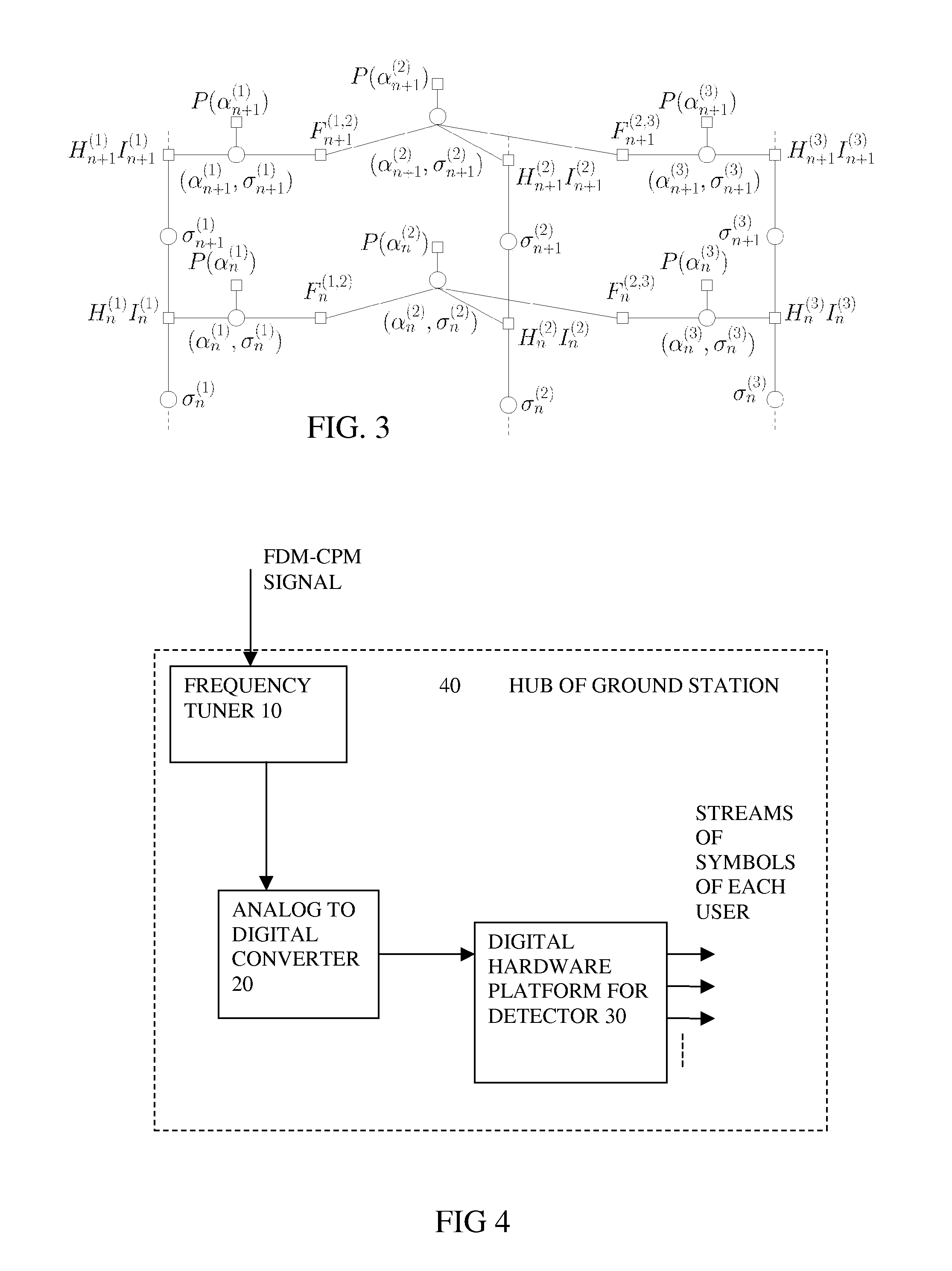

Reduced complexity fdm-cpm dectector with multiple access interference cancellation

InactiveUS20120098612A1Reduce complexityReduce degradationModulated-carrier systemsAngle modulationPhase detectorExponential complexity

Owner:NEWTEC CY

Median filtering implementation method for integrated circuit design

InactiveCN104811161AIncrease the median filter rateDigital technique networkTheoretical computer scienceIntegrated circuit

The invention discloses a median filtering implementation method for integrated circuit design. The median filtering implementation method for the integrated circuit design is implemented based on a memory and an FSM. The median filtering implementation method for the integrated circuit design comprises the step S1 of initialization and the step S2 of filtering output. The step S1 of initialization comprises the step that N data which are sorted by size are stored in the memory according to a data structure so as to establish a data table, wherein when the number of stored data is smaller than N, and new data come, polling is conducted from any one end of a stored sorted data table, the stored data and the new data are compared, the appropriate positions of the new data in the sorted data table are found out, the new data are inserted into the sorted data table, and the new data are inserted one by one until the number of the data is equal to N, and therefore initialization is completed. The step S2 of filtering output comprises the steps that the data table is reestablished in a deletion and insertion mode according to the time sequence on the basis of the established data table, and a median of the N data is outputted according to the reestablished data table. When the median filtering implementation method is applied, the hardware cost can be reduced, the median filtering rate can be increased to 700 KHz, the median filtering depth can be increased to 32, and therefore the comprehensive constraint conditions can be changed.

Owner:SHANGHAI PANCHIP MICROELECTRONICS CO LTD

Multipath all-phase microwave numerical-control phase shifter control system and method

InactiveCN105974369AReduce volumeFirmly connectedWave based measurement systemsNumerical controlTransceiver

The invention discloses a multipath all-phase microwave numerical-control phase shifter control system, and the system comprises a far end and a local end. The far end comprises control software, a computer and an optical fiber transceiver A, wherein the control software, the computer and the optical fiber transceiver A are connected sequentially. The local end comprises an optical fiber transceiver B, a serial port server, a time sequence controller and a numerical control phase shifter, wherein the optical fiber transceiver B, the serial port server, the time sequence controller and the numerical-control phase shifter are connected sequentially. The optical fiber transceiver A and the optical fiber transceiver B are used for receiving and transmitting optical fiber signals in a paired manner. The system enables a numerical-control phase shifter to achieve large-scale phase shift (0-360 degrees) in a high-frequency range, employs a mode of the serial port server + the time sequence controller for design , simplifies the connection of external cables, improves the reliability of systems, effectively solves problems that the phase precision decreases after the phase shifter carries out 180-degree shift (reverse) and there is a nonlinear change, and guarantees that the phase precision is less than 2.5 degrees.

Owner:INST OF APPLIED ELECTRONICS CHINA ACAD OF ENG PHYSICS

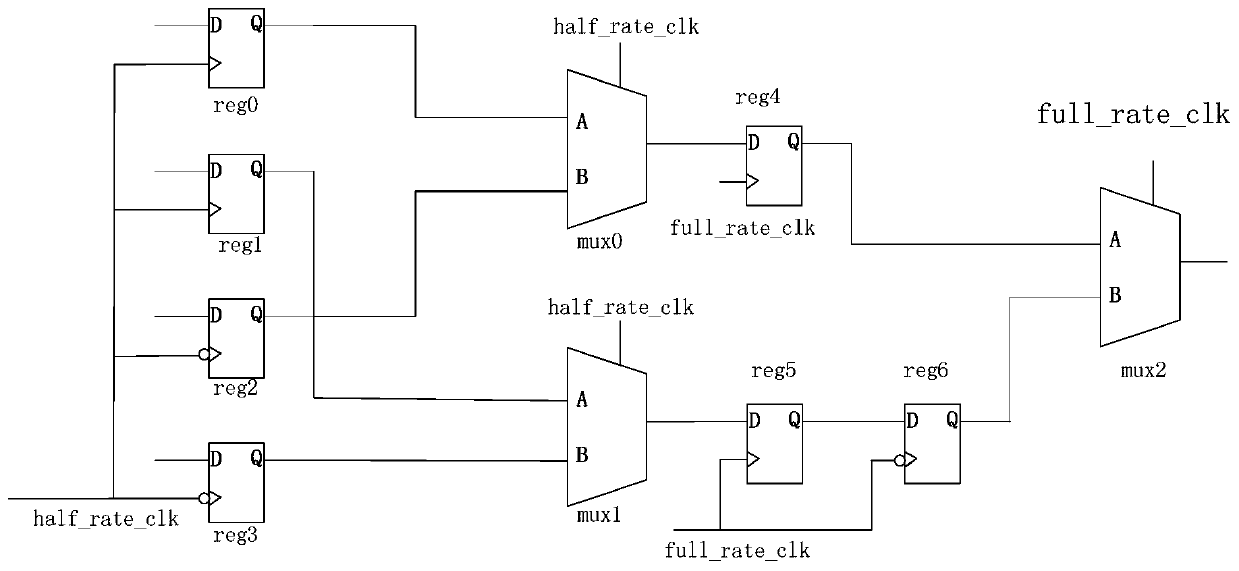

Transmitting circuit based on DDR writing channel

PendingCN110489363ATroubleshoot Timing ClosureElectric digital data processingTime sequenceProcessor register

The invention discloses a transmitting circuit based on a DDR writing channel. The transmitting circuit based on the DDR writing channel comprises first to seventh registers and first to third clock selectors, respective output ends of the first register and the third register are respectively connected with two input ends of the first clock selector, respective output ends of the second registerand the fourth register are respectively connected with two input ends of the second clock selector, the output end of the first clock selector is connected with the input end of the fifth register, the output end of the second clock selector is connected with the input end of the sixth register, the output end of the sixth register is connected with the input end of the seventh register, and respective output ends of the fifth register and the seventh register are respectively connected with two input ends of the third clock selector. Therefore, the time sequence requirement of the circuit can be reduced, and the time sequence convergence is easier.

Owner:BRITE SEMICON SHANGHAI CORP

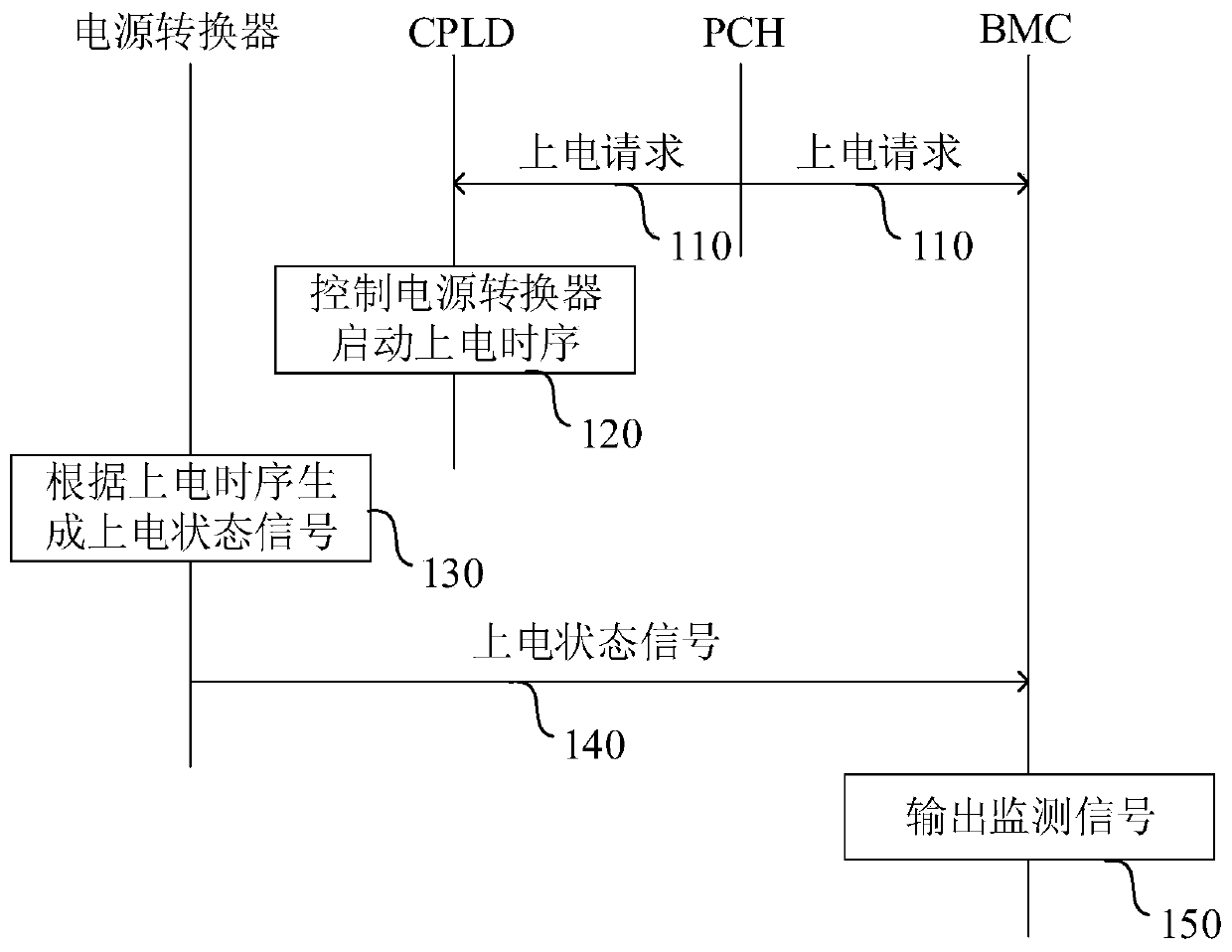

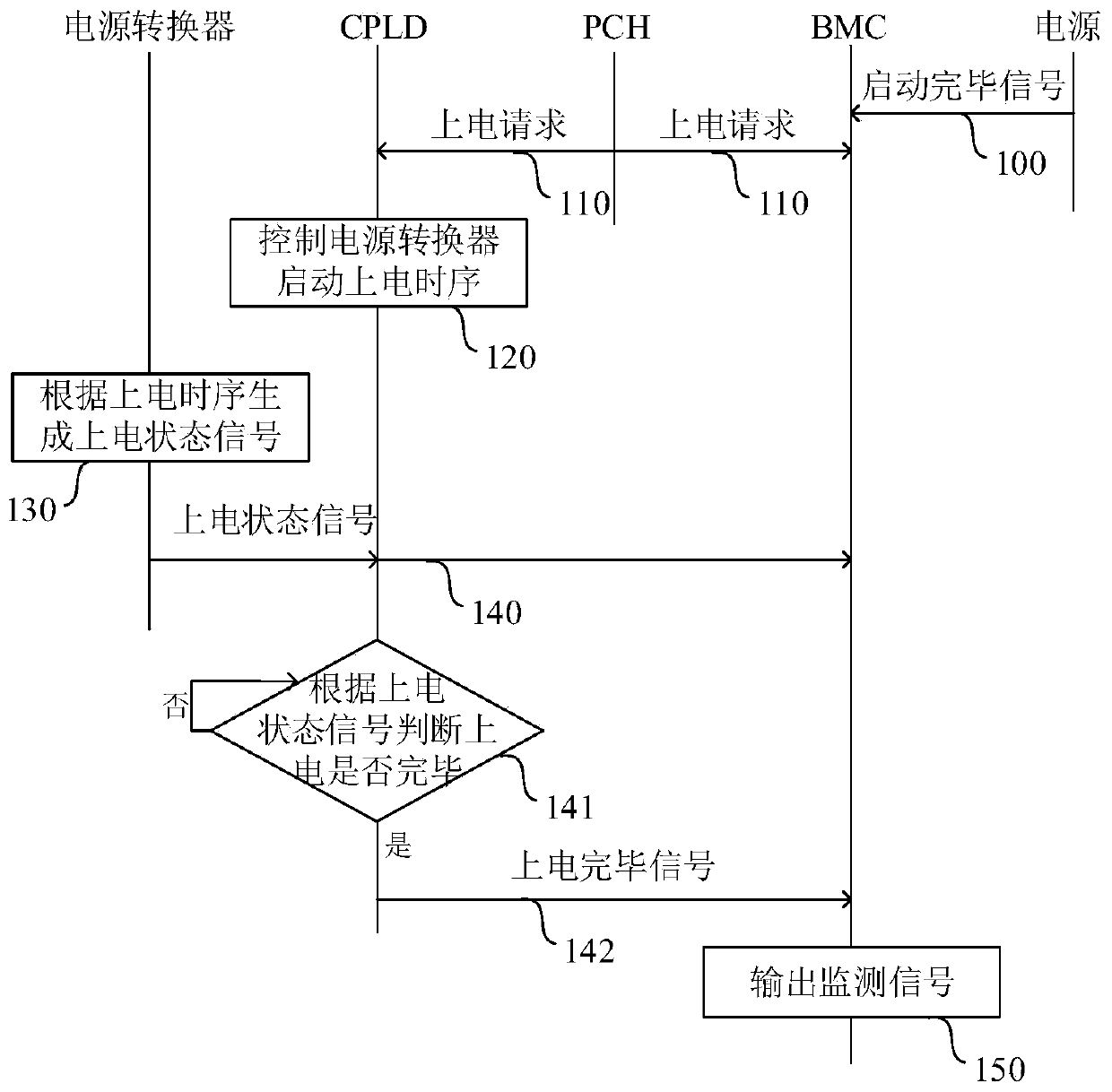

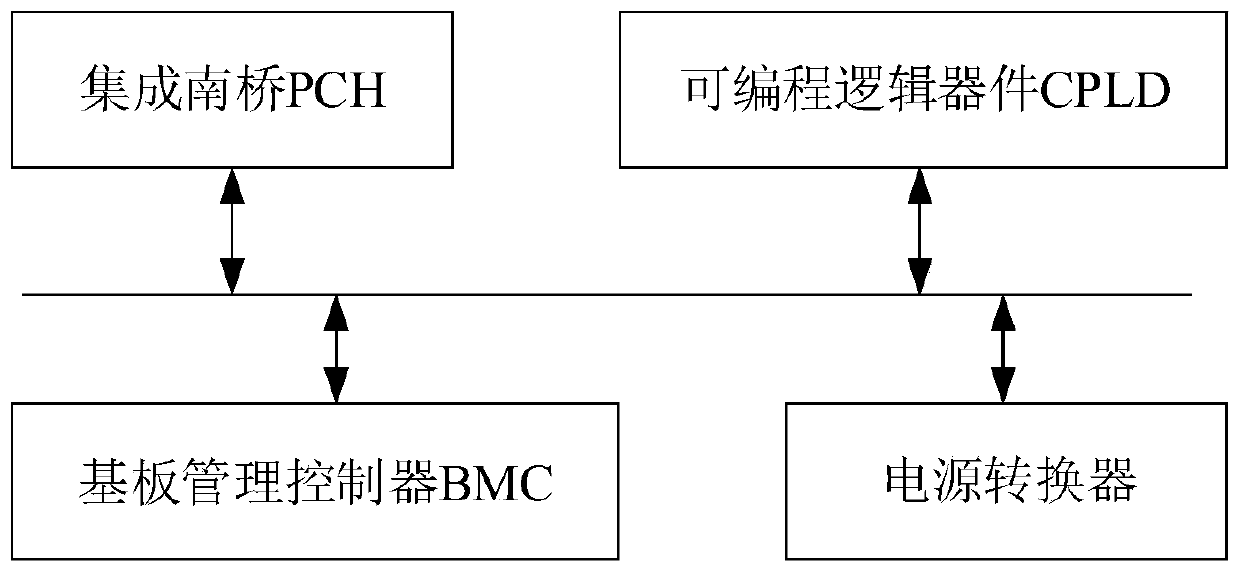

Baseboard management controller BMC, terminal and power-on state diagnosis assembly and method

InactiveCN109885437AQuick collectionAccurate collectionDetecting faulty computer hardwareElectricityBaseboard

Owner:XIAN YIPU COMM TECH

Electronic device and control method and device for electronic device

The application discloses an electronic device and a control method and device for the electronic device. The electronic device comprises a display screen and a time-of-flight component, wherein a front side and a back side which are opposite to each other are formed in the display area of the display screen; the display screen comprises first and second sub-screens which can be independently controlled; the first sub-screen forms a first sub-display area; the second sub-screen forms a second sub-display area; the time-of-flight component comprises an optical receiver; the optical receiver isarranged on the back side of the display screen and corresponds to the first sub-display area; and the optical receiver is used for receiving the reflected laser pulse passing through the first sub-display area. When the optical receiver is turned on, the first sub-display area displays an image in a first display time sequence, and the optical receiver exposes the image in an exposure time sequence. The effective working state corresponding to the first display time sequence is staggered from the effective working state corresponding to the exposure time sequence. The optical receiver is arranged on the back side of the display screen, so that a hole aligned with the optical receiver does not need to be formed on the display screen, and the screen-to-body ratio is relatively high.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

Charge pump high-speed detection circuit and method

ActiveCN110165887AReduce power consumptionHigh speedEfficient power electronics conversionCurrent/voltage measurementCapacitanceFixed capacitor

The invention discloses a charge pump high-speed detection circuit and method, and the circuit comprises a time sequence control circuit, a charge pump circuit, a comparator, a fixed capacitor, an adjustable capacitor, and first, third, fourth, and sixth switches. The time sequence control circuit outputs a time sequence control signal to the charge transfer circuit, and the output end of the charge transfer circuit is connected with one end of the fixed capacitor through the sixth switch; the other end of the fixed capacitor is connected with one end of the adjustable capacitor, the other endof the adjustable capacitor is grounded, and the two ends of the fixed capacitor are grounded through the first and third switches respectively; the common end of the fixed capacitor and the adjustable capacitor is connected with a reference voltage pin of the comparator through a fourth switch; the comparator collects a voltage value output by the fourth switch, compares the voltage value with areference voltage and outputs a comparison result to the time sequence control circuit, and the time sequence control circuit controls on-off of the charge transfer circuit. According to the invention, the power consumption is saved, the capacitance detection mode is adopted, the speed is higher, and ripples are smaller.

Owner:SHENZHEN AIXIESHENG TECH CO LTD

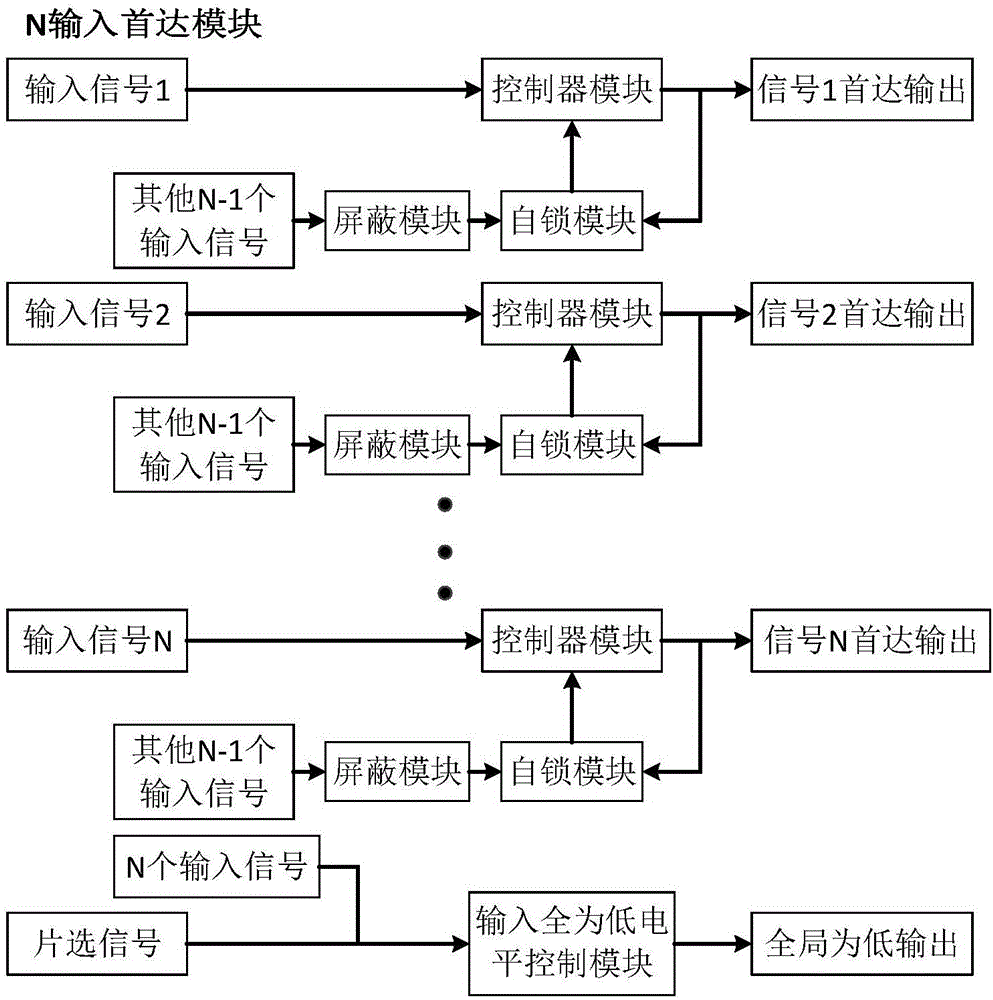

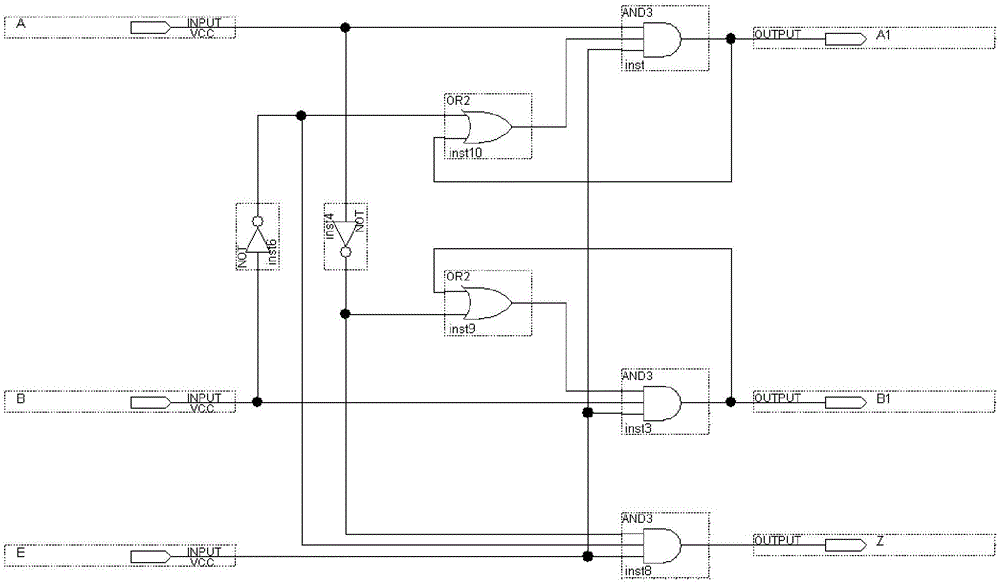

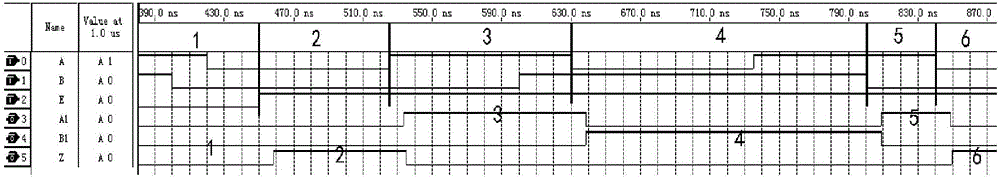

Time sequence decoder

ActiveCN106559069AImprove general performanceImprove scalabilityLogic circuits characterised by logic functionChip selectData transmission

Owner:DONGHUA UNIV

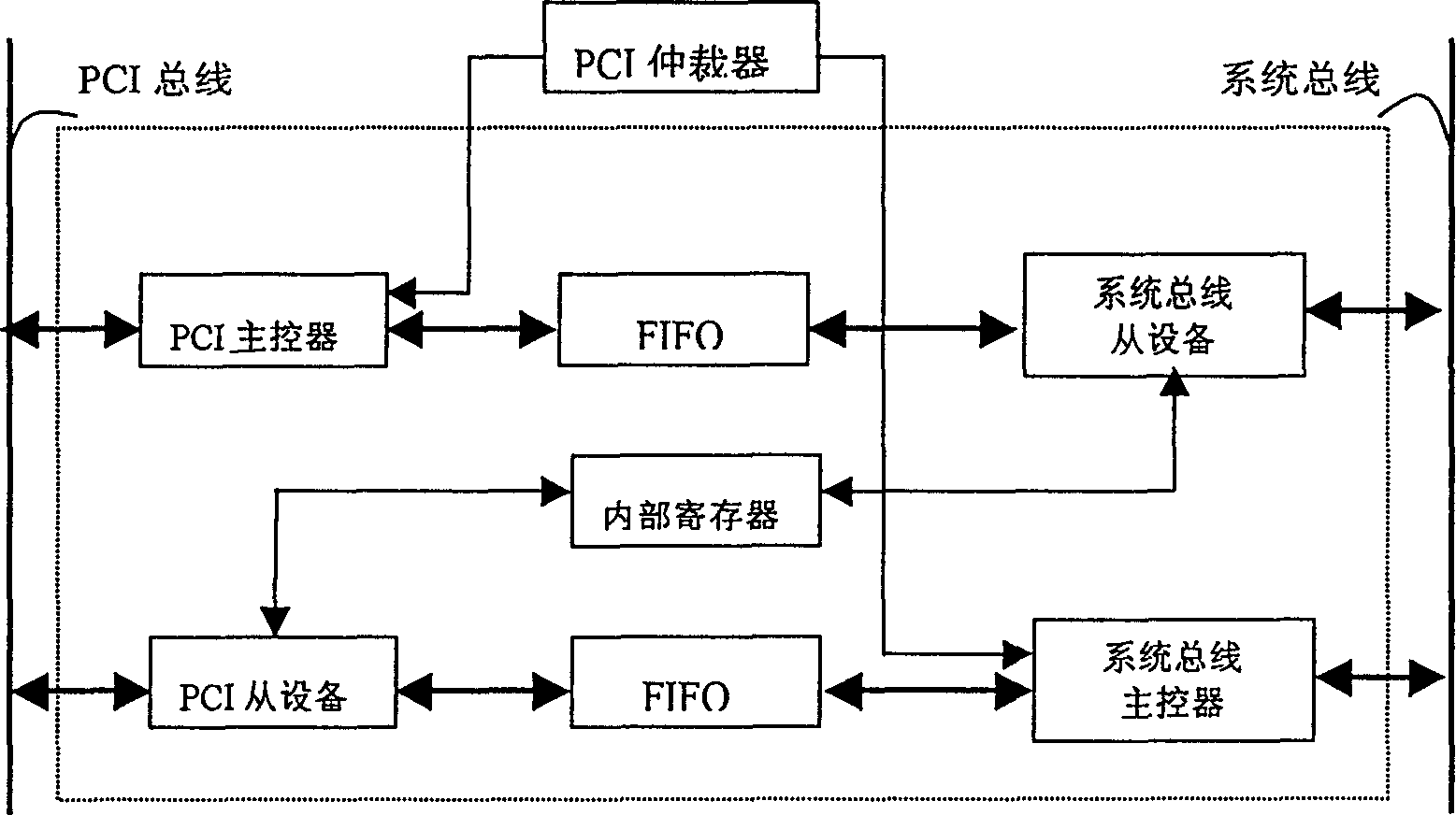

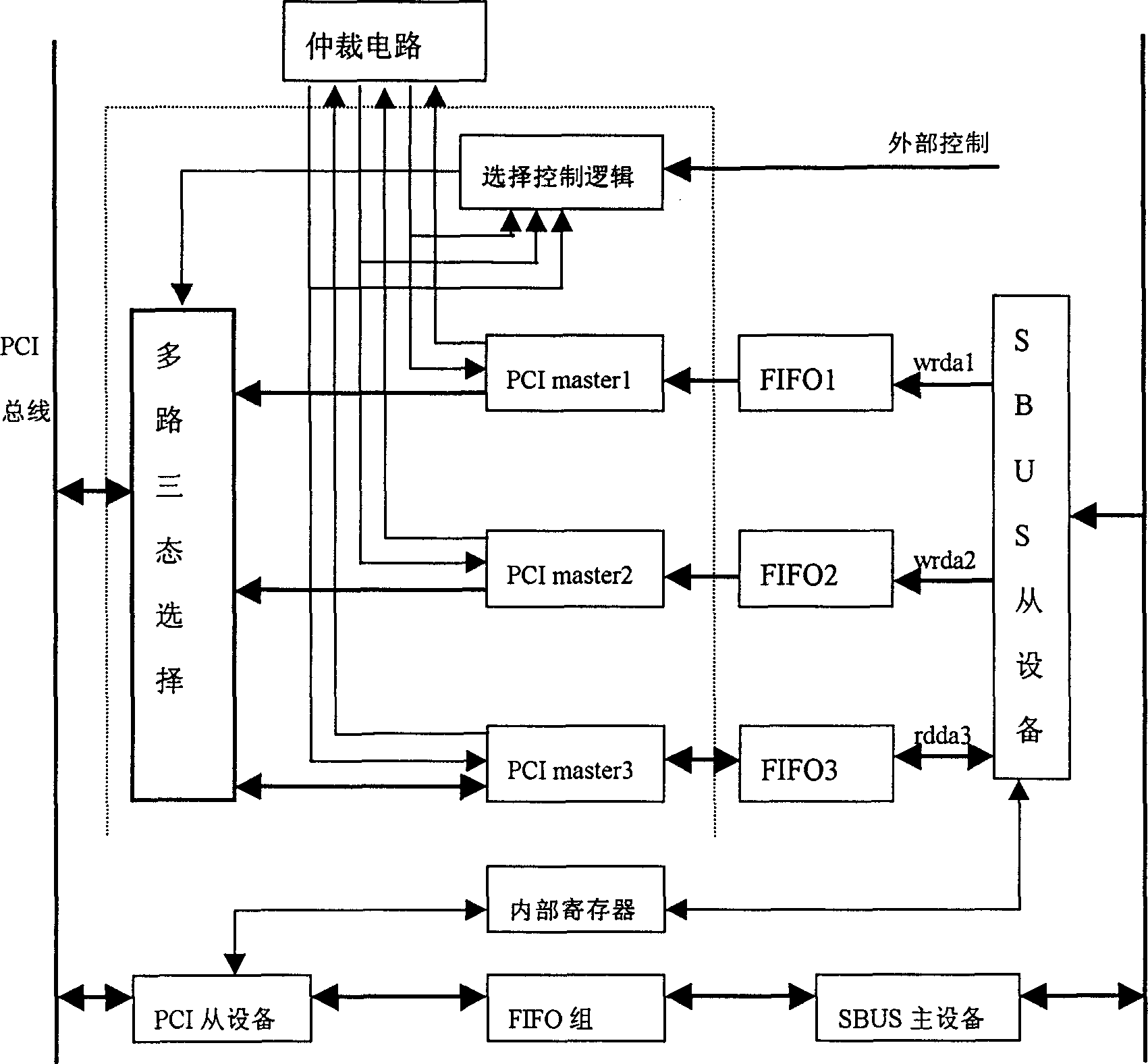

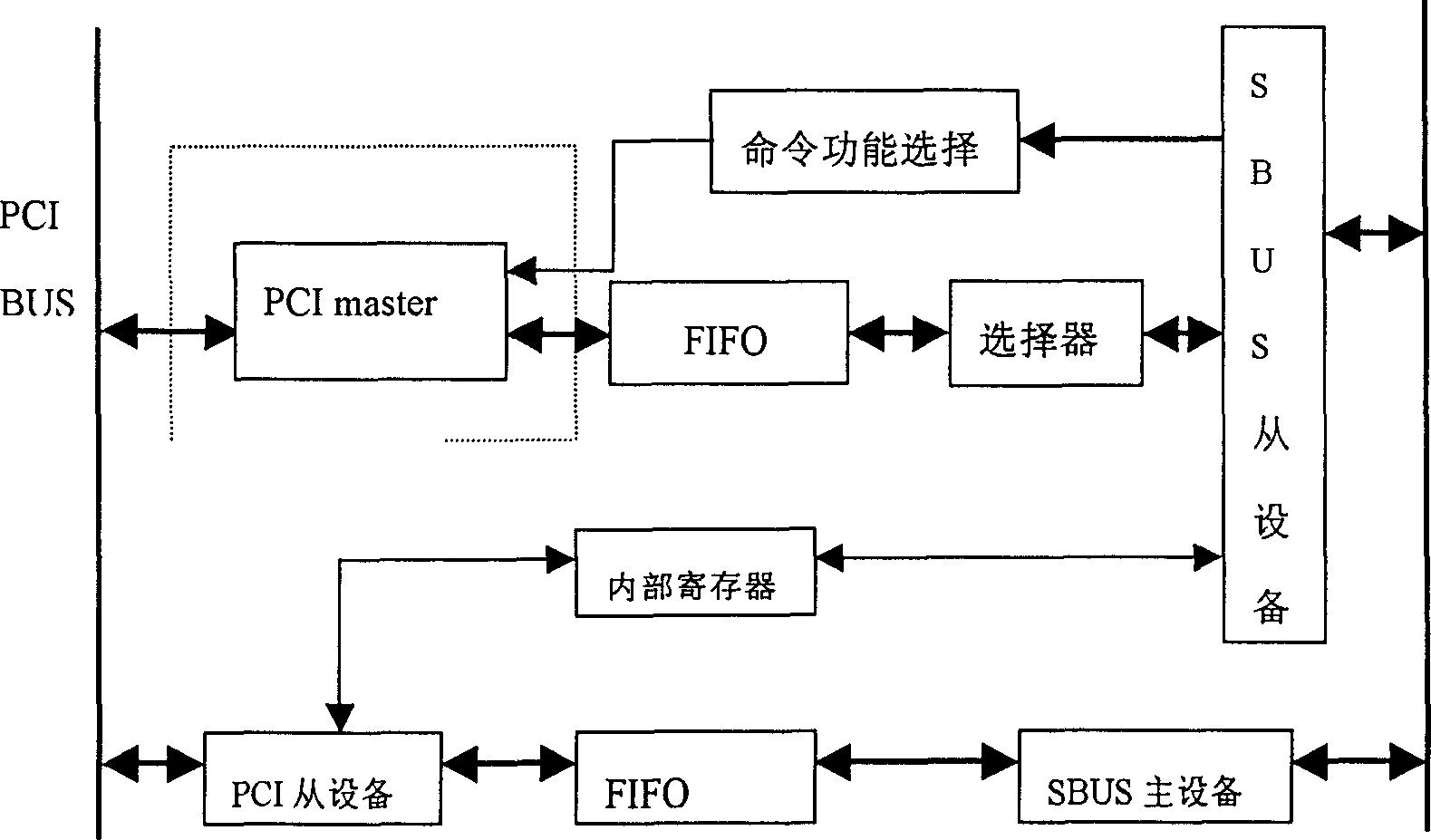

PCI bridge with improved structure

InactiveCN1191530CImprove transmission efficiencyElectric digital data processingTime sequenceHigh transmission

The invention discloses an improved structure of PCI main bridge in computer area. The PCI main controller in the mainbridge includes PCI main controlling unit, multiplex selector, internal arbitration circuit and 'Or' gate. Several instruction parts share the PCI main control unit. For each instruction part, a relevant group of FIFO is provided for exchanging the time sequence. Output data of each group of FIFO enter the input end of PCI main control unit through the multiplex selector, then passing through the output of multiplex selector that is controlled by the internal arbitration circuit. The invention possesses merits of high transmission efficiency, simple circuit and low cost.

Owner:NATIONZ TECH INC

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap