Cascoded semiconductor devices

A cascading, transistor technology, applied in semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve problems such as power supply short-circuit, GaN switches cannot operate reliably in reverse conduction mode, and achieve low switching losses. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

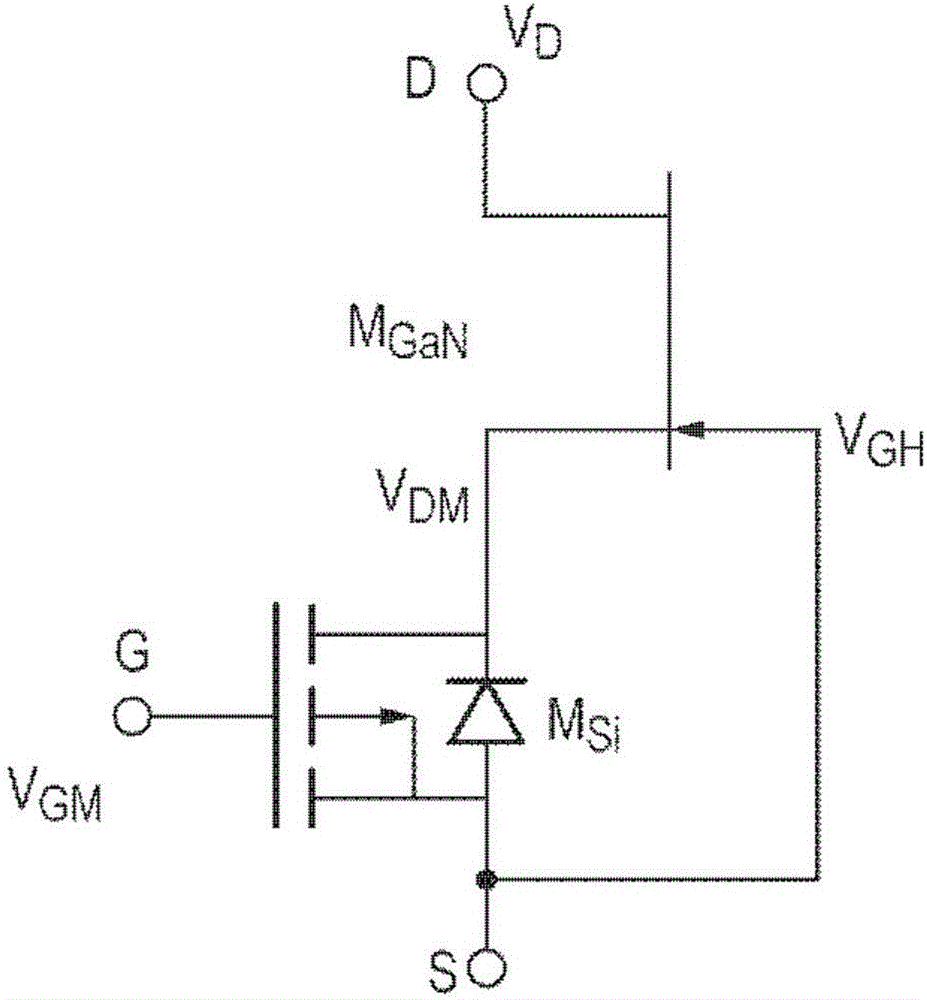

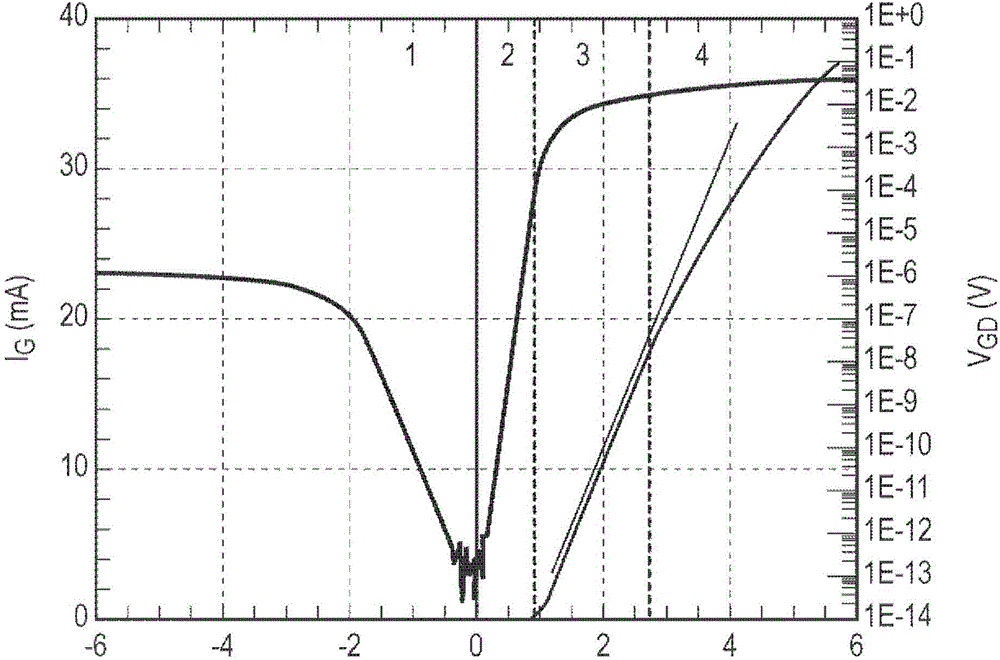

[0033] Embodiments of the present invention propose a cascode transistor circuit having a main depletion mode transistor and a cascode MOSFET formed, the two transistors being packaged to form the cascode transistor circuit. The bias circuit is connected between the gate of the power transistor and the low supply line of the circuit. A biasing circuit is integrated into the transistor circuit for compensating the forward voltage of the body diode of the cascaded MOSFET. In the absence of a bias circuit, the Schottky gate is in parallel with the body diode of the cascode MOSFET. Because the forward voltages can be nearly equal, a larger current can flow through the Schottky gate.

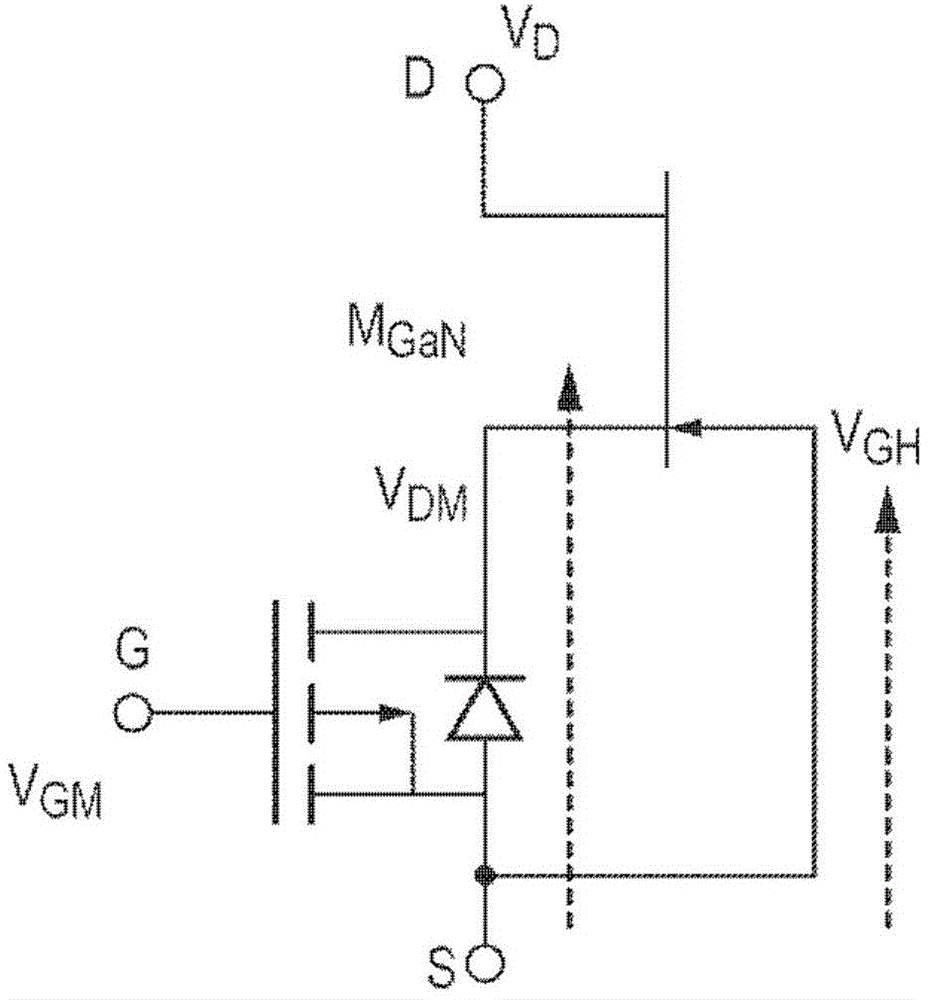

[0034] The bias circuit intentionally increases the forward voltage of the Schottky gate for reverse current, so all the current will flow through the MOSFET body diode.

[0035] Therefore, the proposed cascode transistor circuit structure can enable reliable reverse operation of the cascode switch.

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap