Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

104results about "Error prevention" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

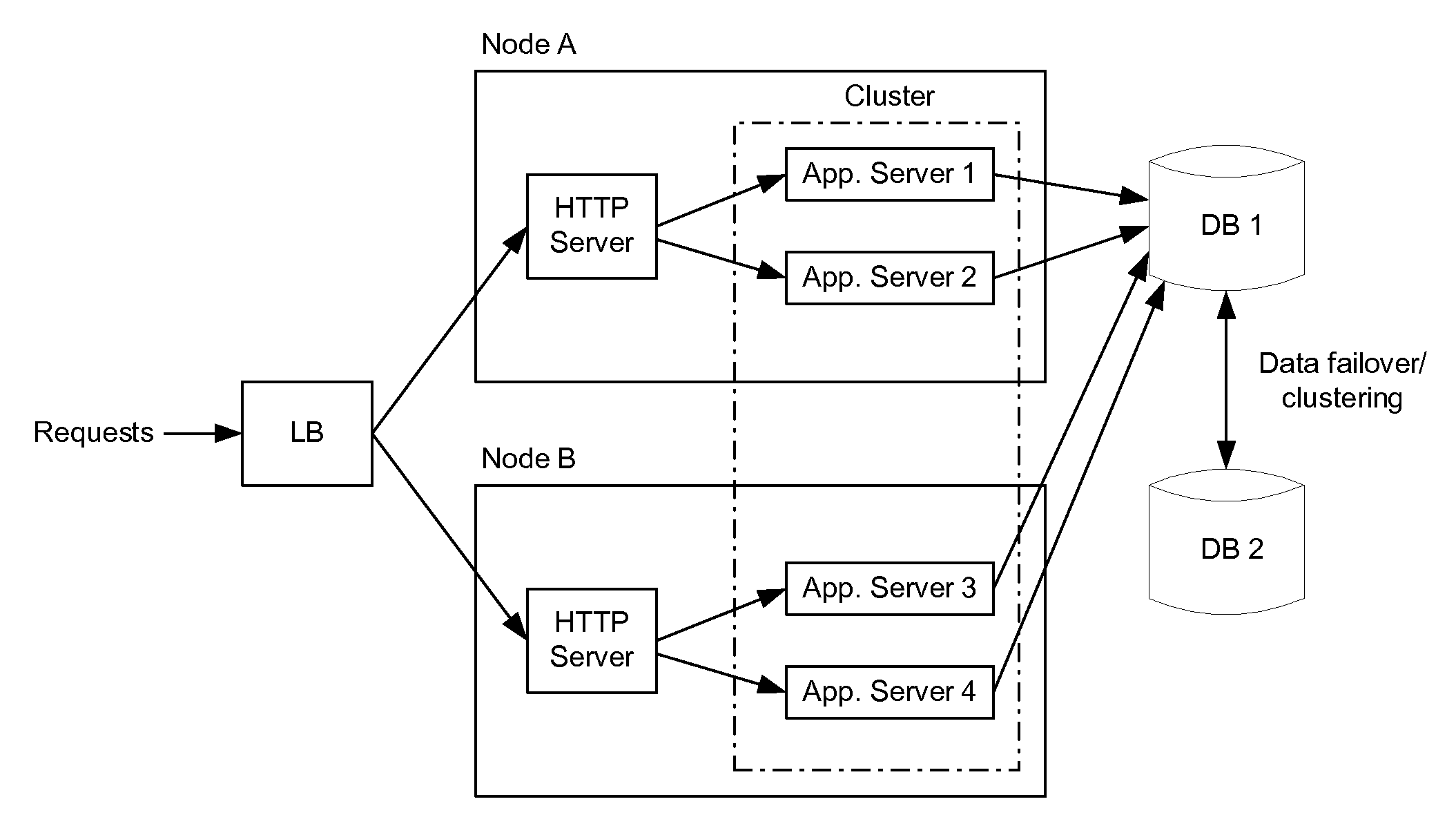

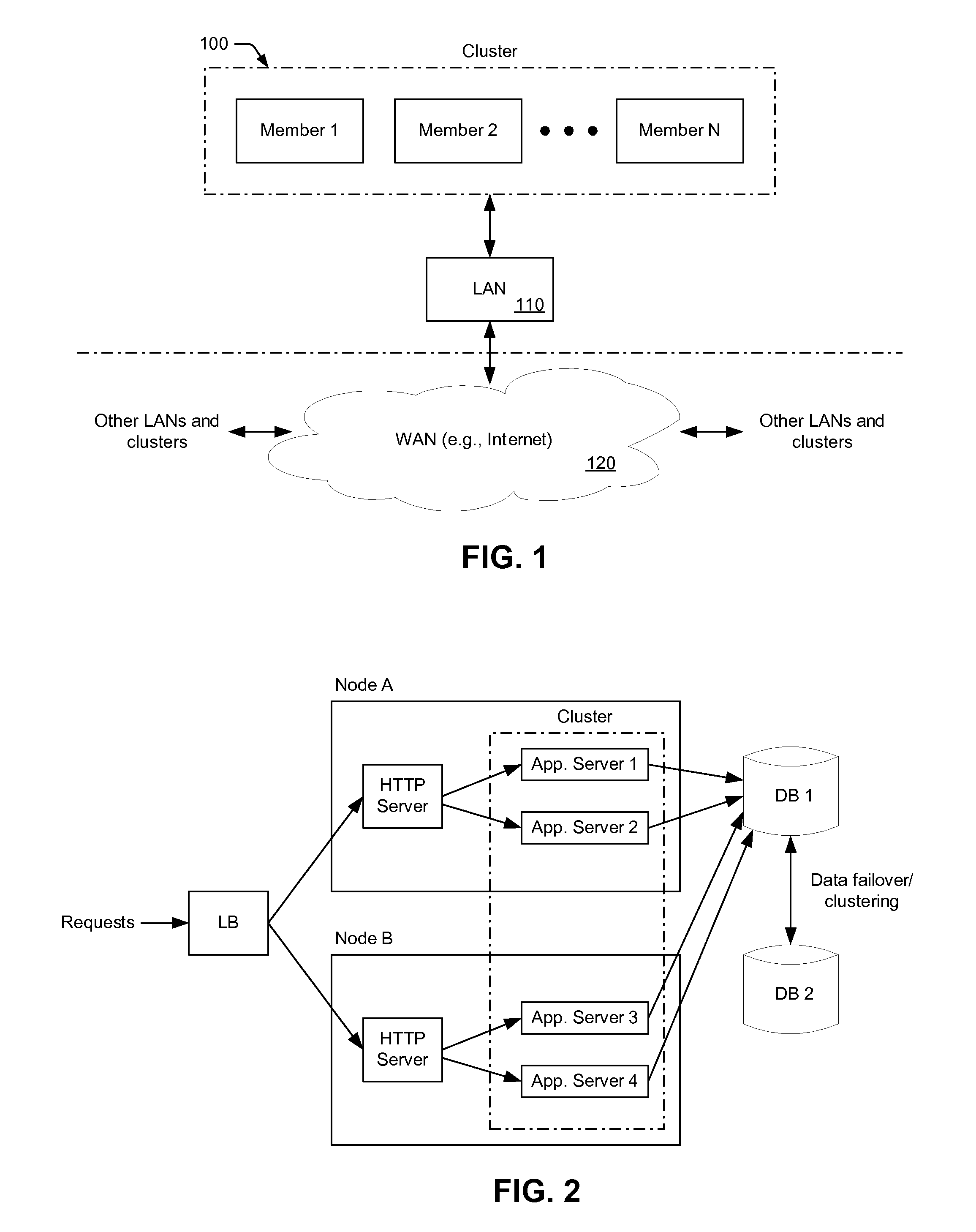

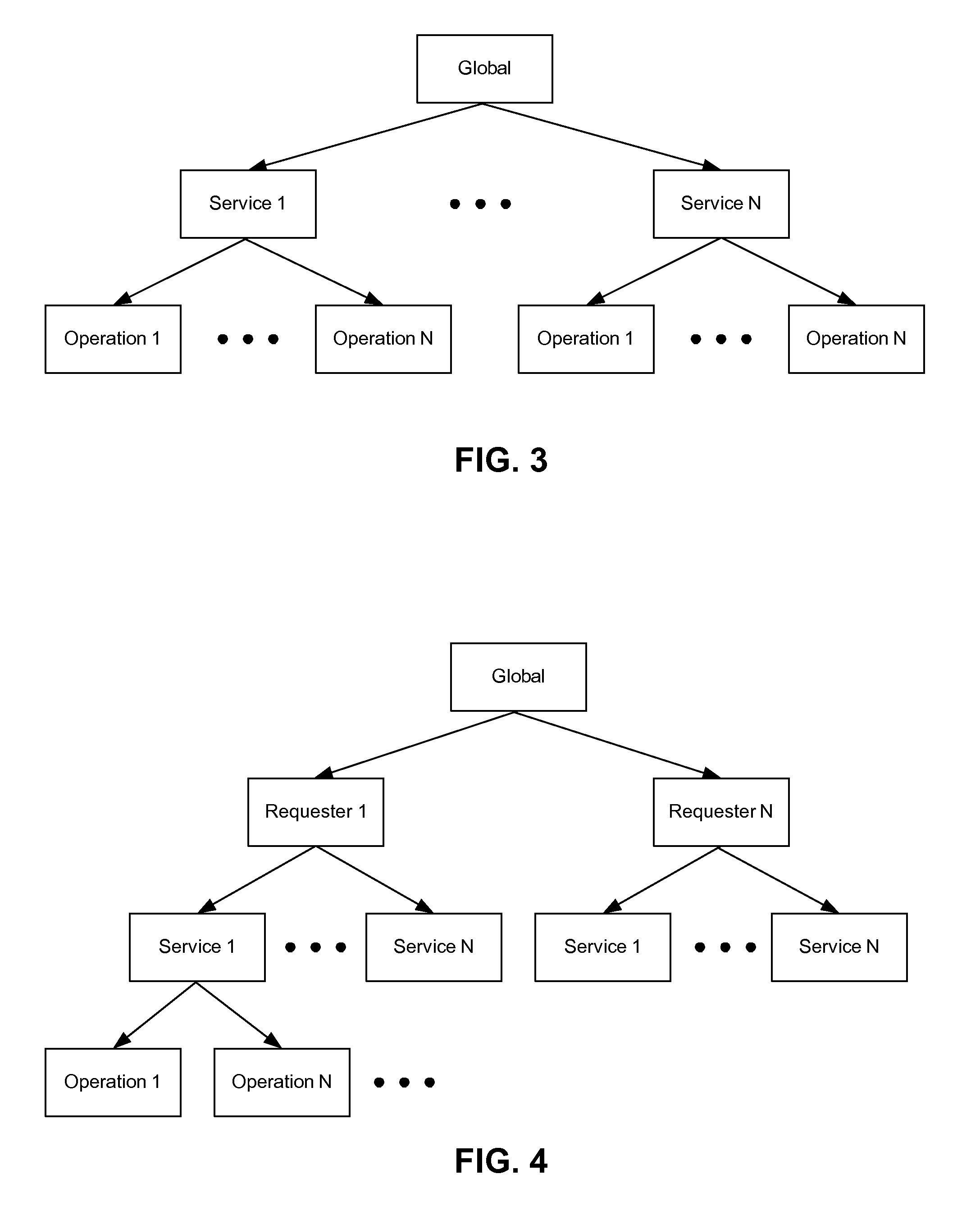

Method for Distributed Traffic Shaping across a Cluster

InactiveUS20080008095A1Error preventionFrequency-division multiplex detailsTraffic volumeTraffic shaping

Owner:IBM CORP

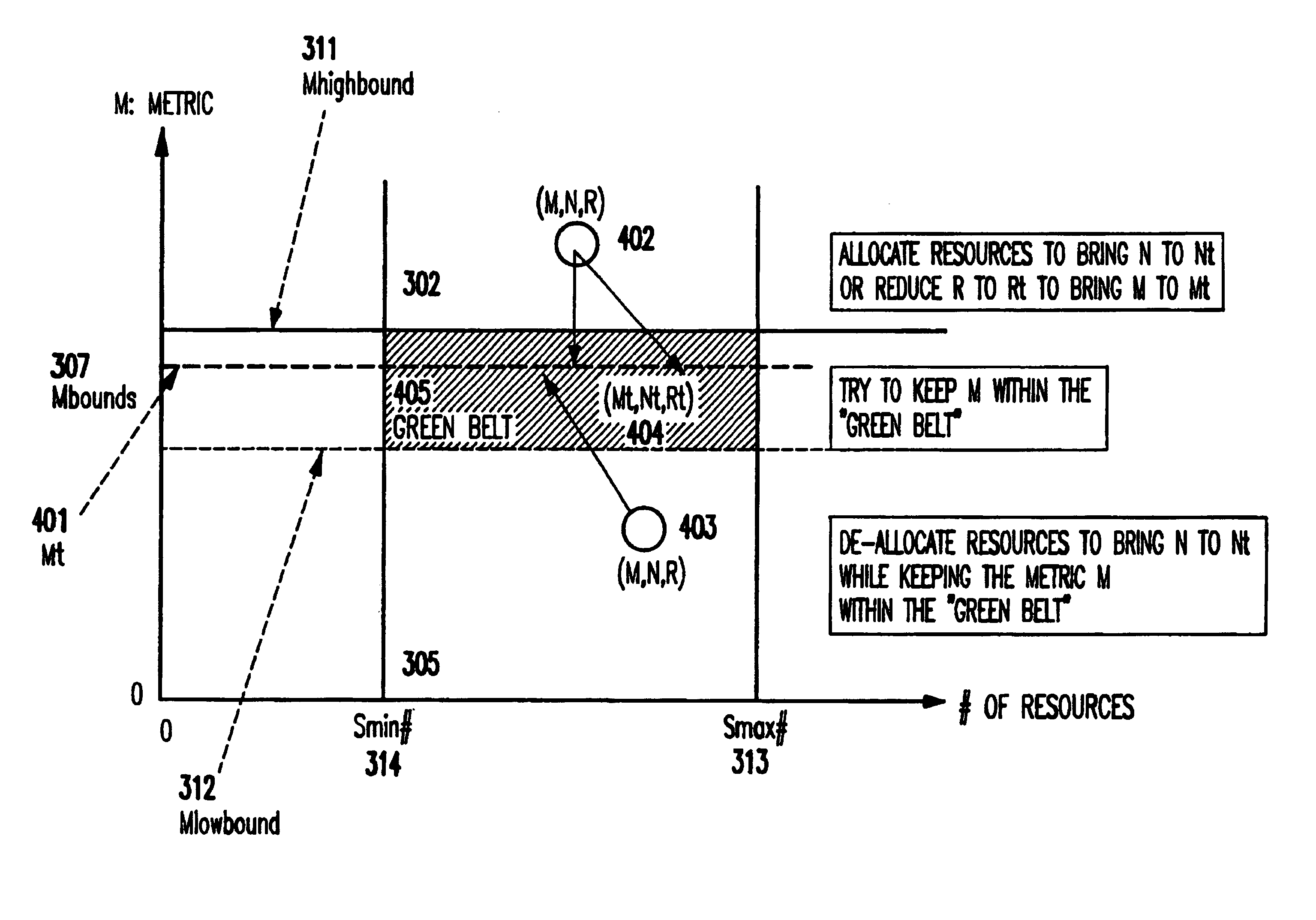

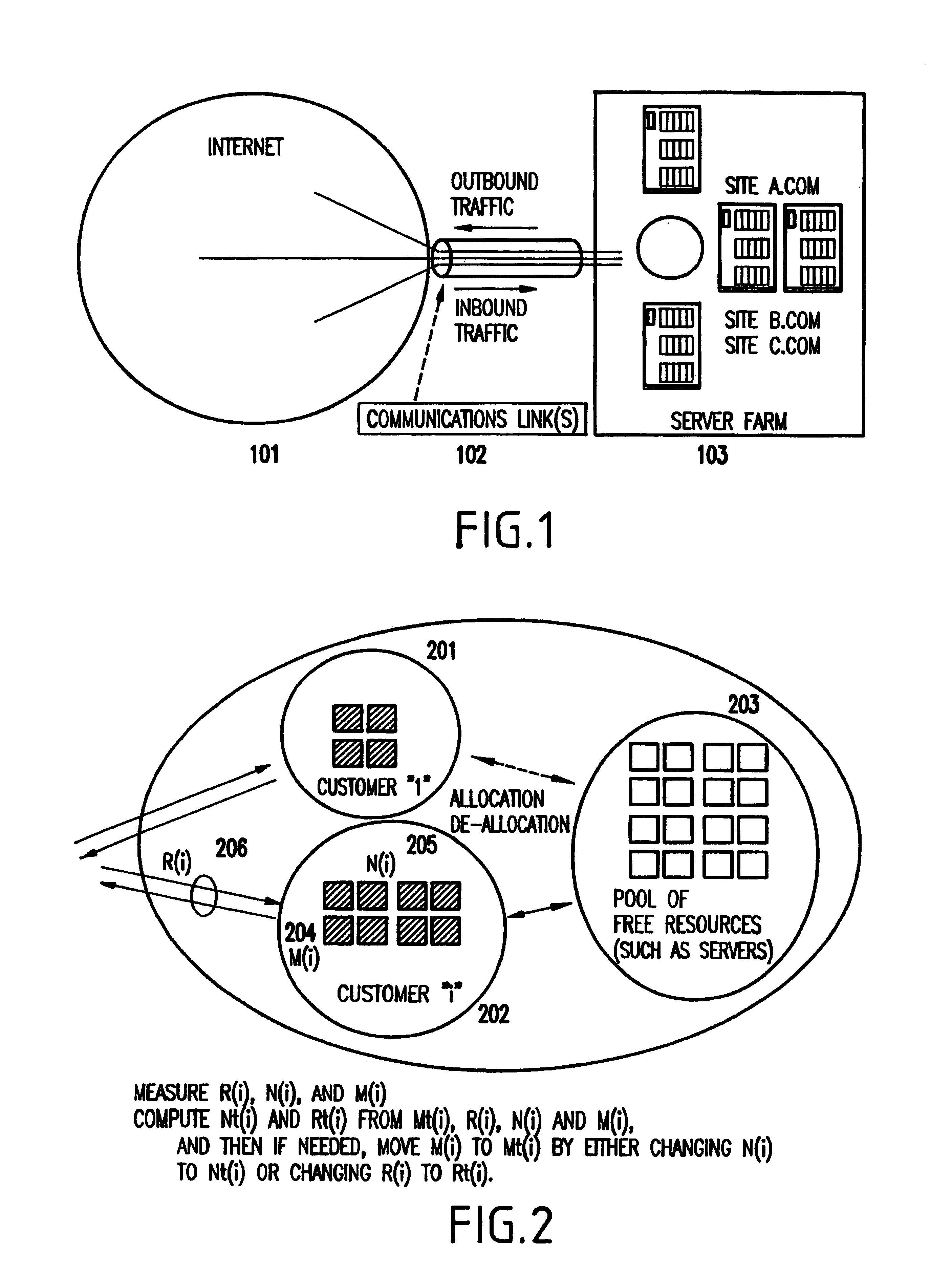

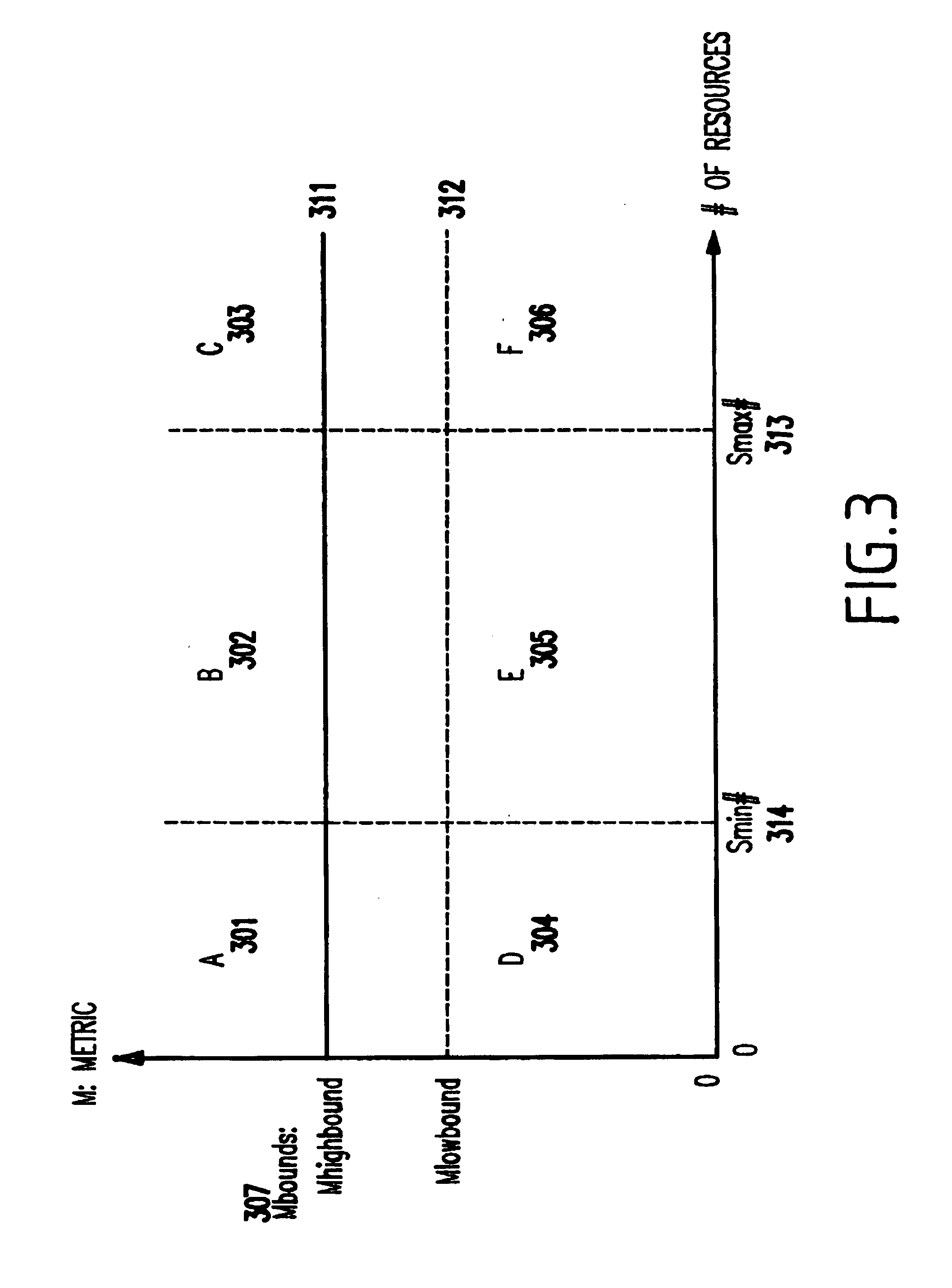

Method and apparatus for dynamically adjusting resources assigned to plurality of customers, for meeting service level agreements (SLAS) with minimal resources, and allowing common pools of resources to be used across plural customers on a demand basis

InactiveUS7054943B1Easy to usePrevent crashError preventionFrequency-division multiplex detailsService-level agreementResource pool

Owner:IBM CORP

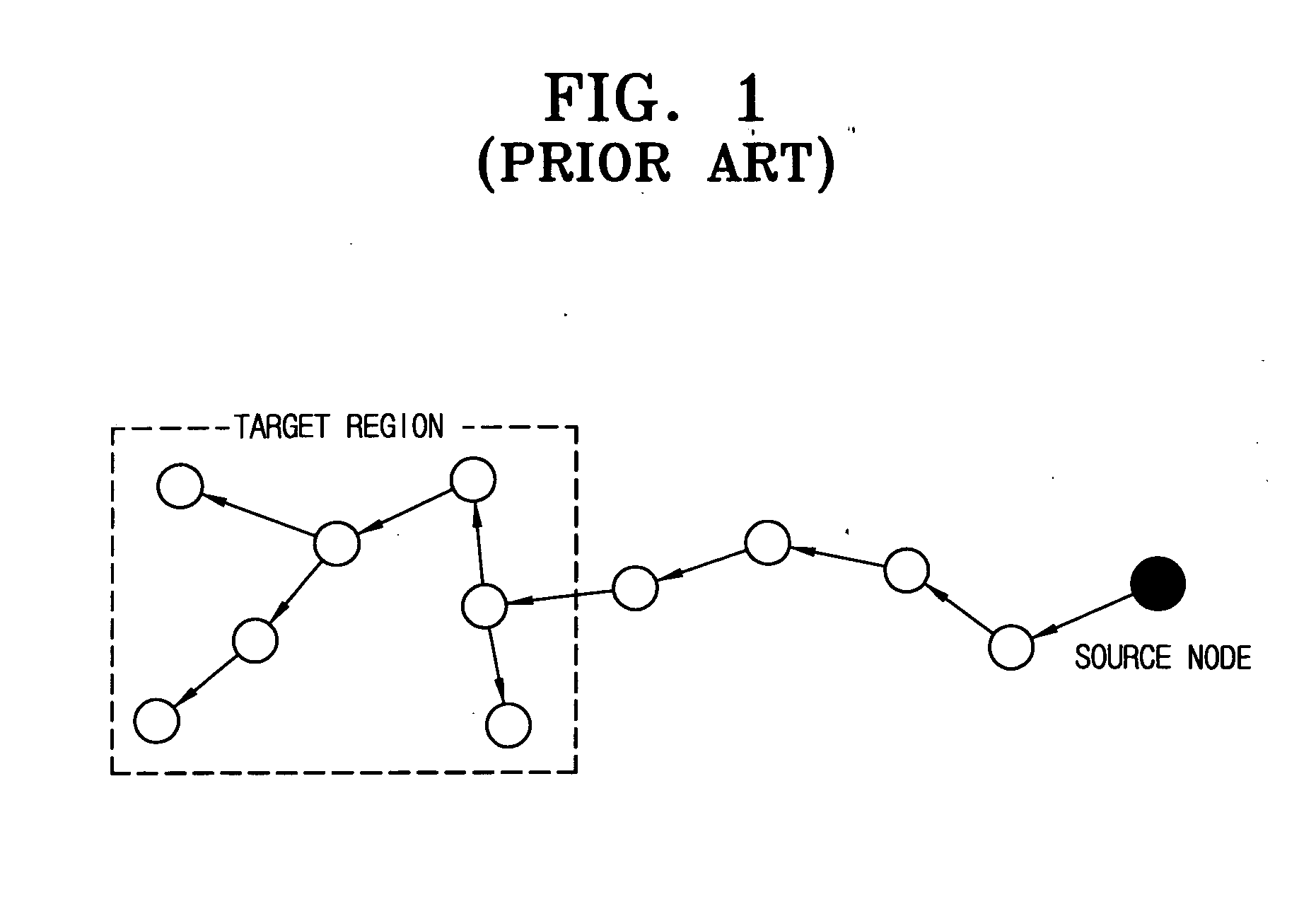

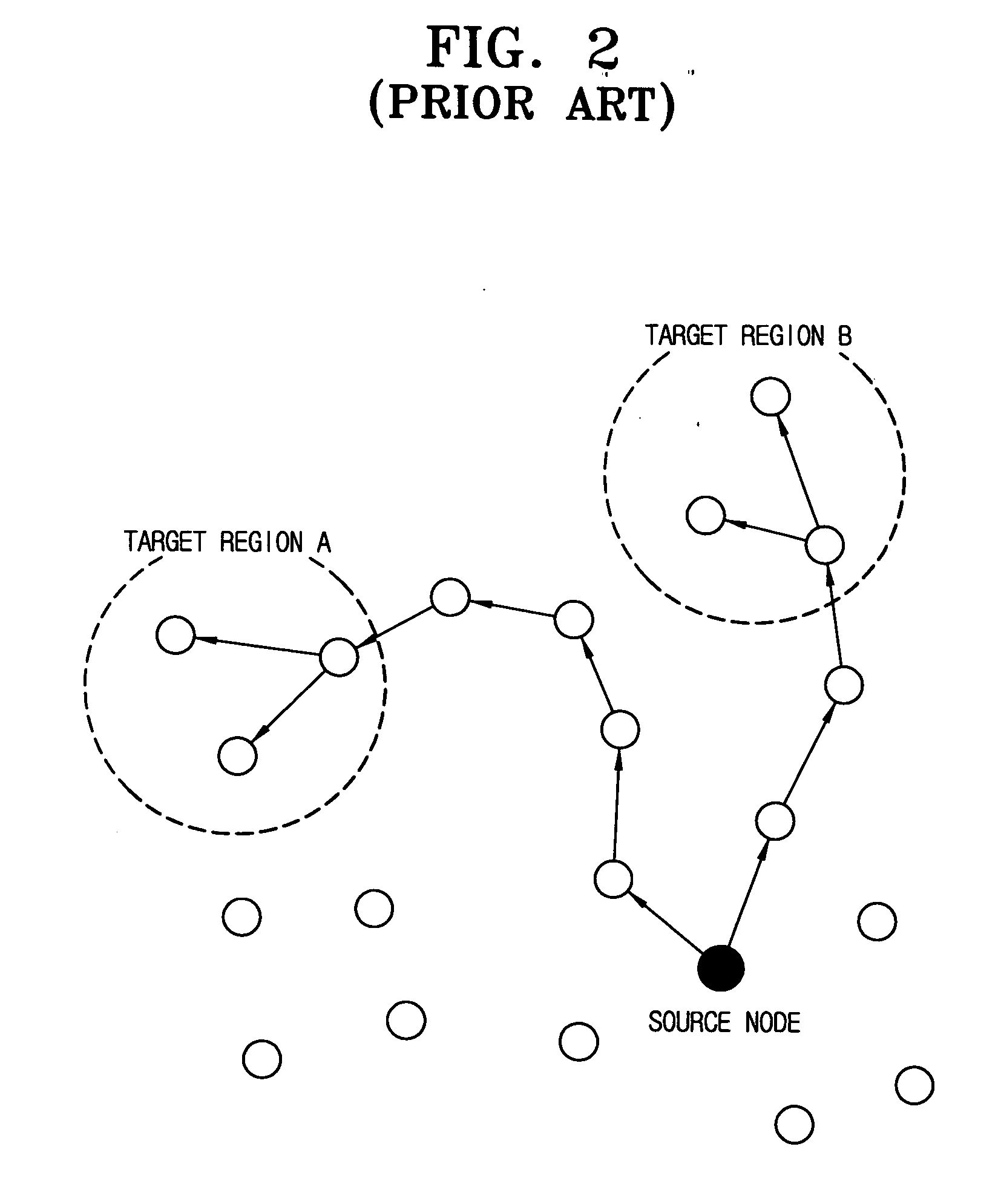

Ad-hoc network for transmitting packets to plural target regions and packet transmission method thereof

ActiveUS20060153157A1Error preventionFrequency-division multiplex detailsSelf-organizing networkNetsniff-ng

Owner:SAMSUNG ELECTRONICS CO LTD

Adaptive device-initiated polling

InactiveUS20070078976A1Error preventionFrequency-division multiplex detailsSelf adaptiveEnterprise system

A method includes periodically sending a polling call to an enterprise system outside the firewall at a first polling rate during normal operating conditions, monitoring for a fault condition, periodically sending polling calls to the device outside the firewall at a second polling rate when a fault condition is detected, the second polling rate being higher than the first polling rate. The second polling rate is used as result of a fault condition. The method also includes sending a problem report with the polling calls when the fault condition is detected.

Owner:PARAMETRIC TECH CORP

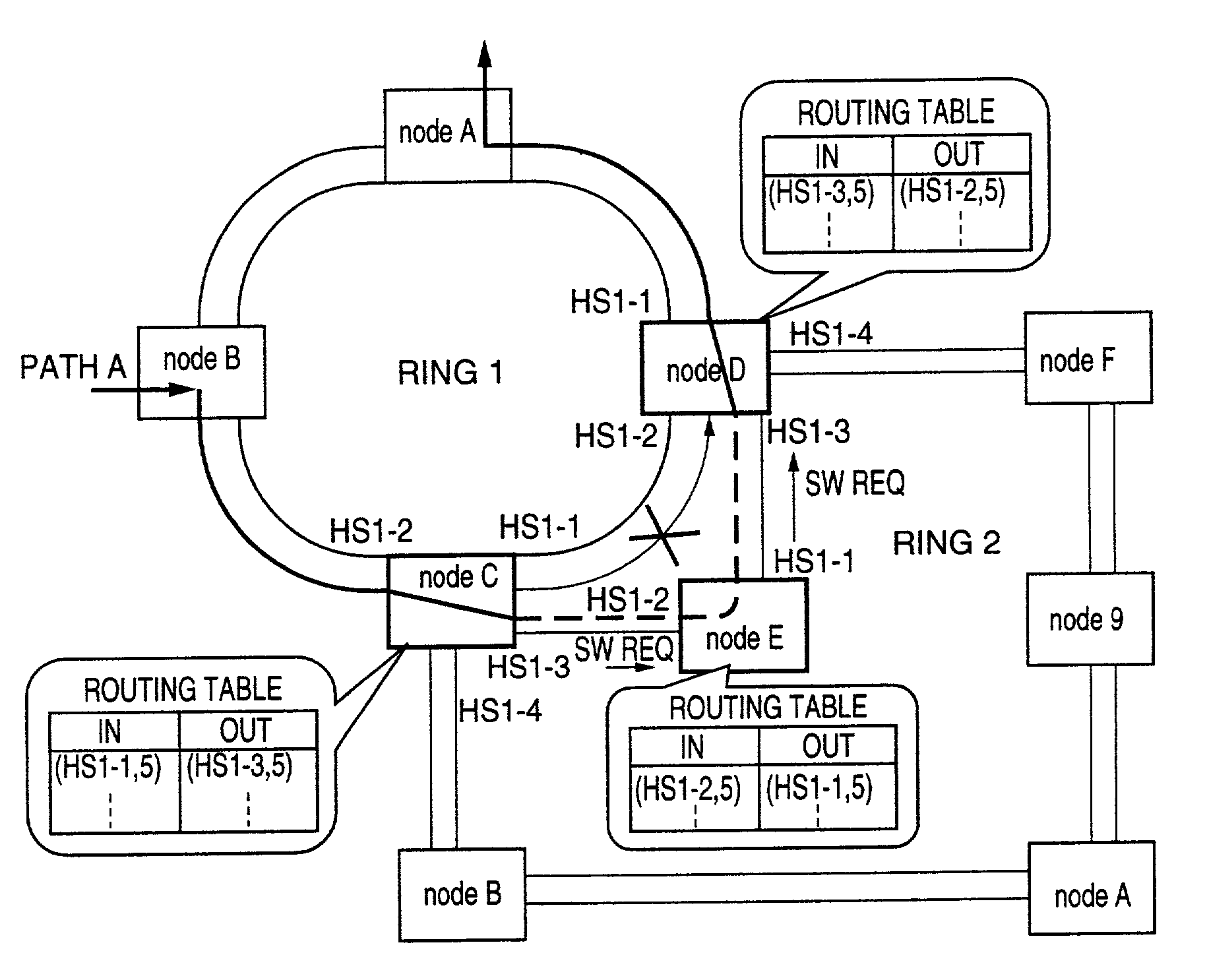

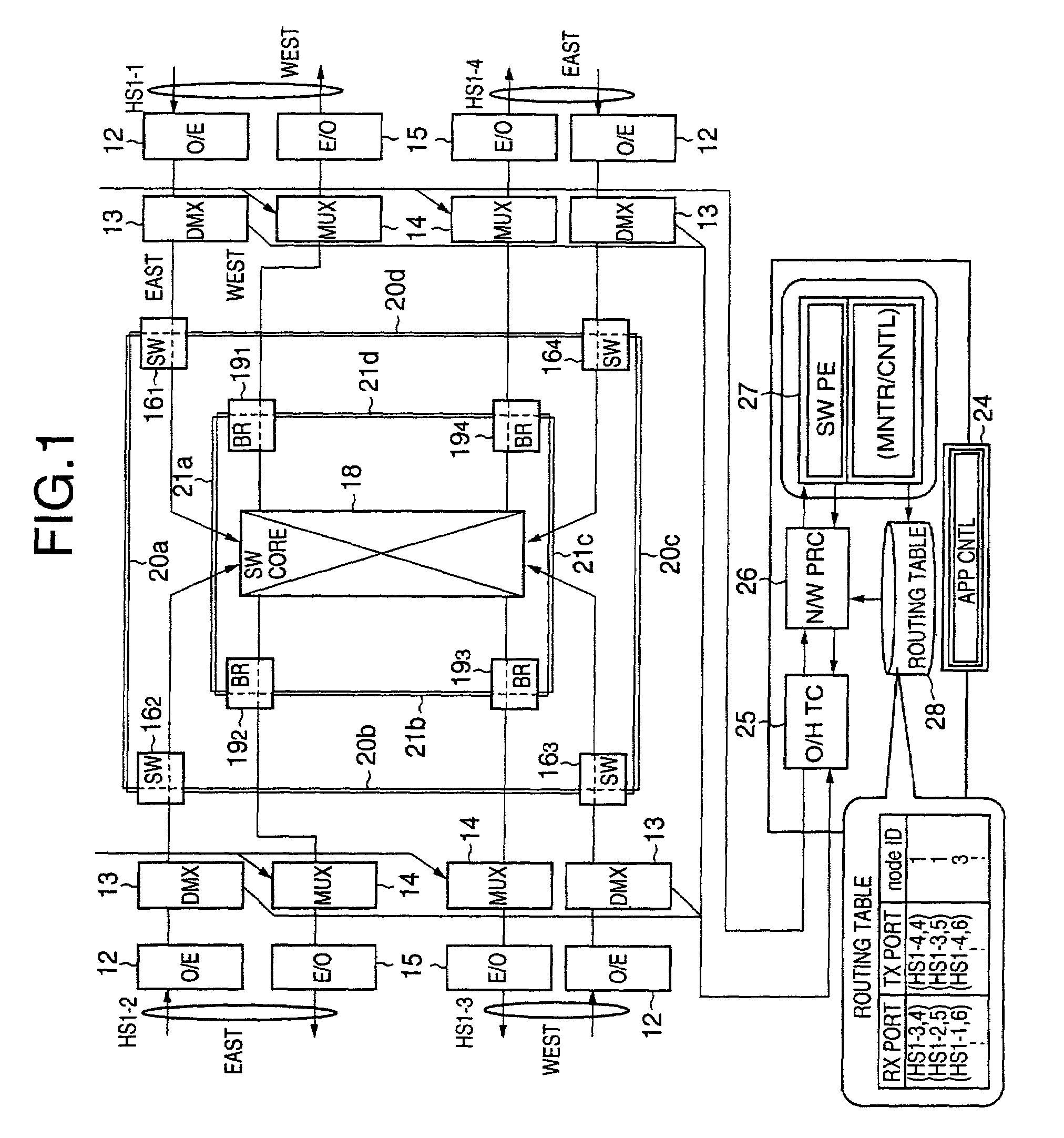

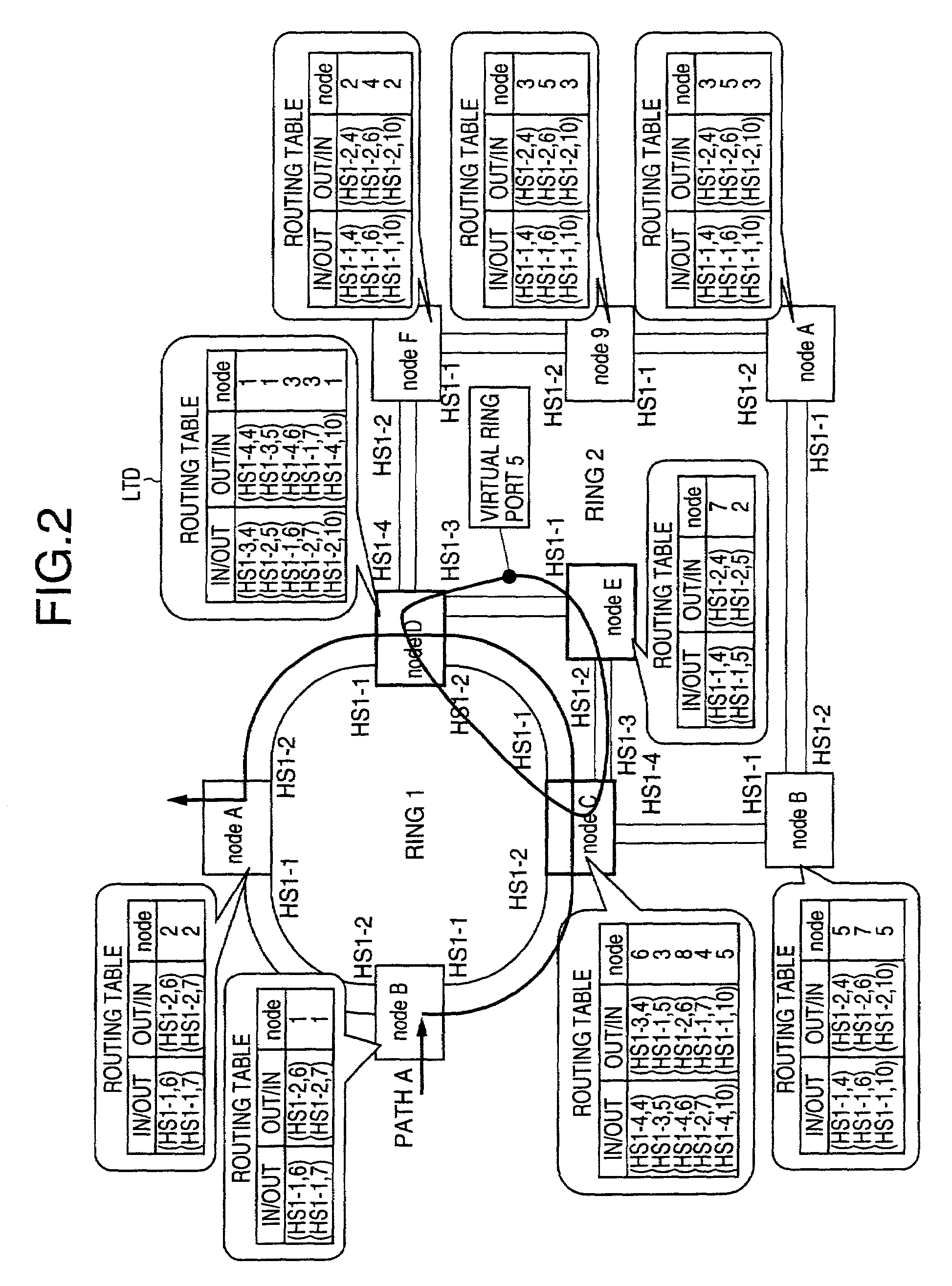

Ring switching method and node apparatus using the same

InactiveUS7065040B2Lower ratioRing-type electromagnetic networksError preventionTransmission lineDefining relationship

Owner:FUJITSU LTD

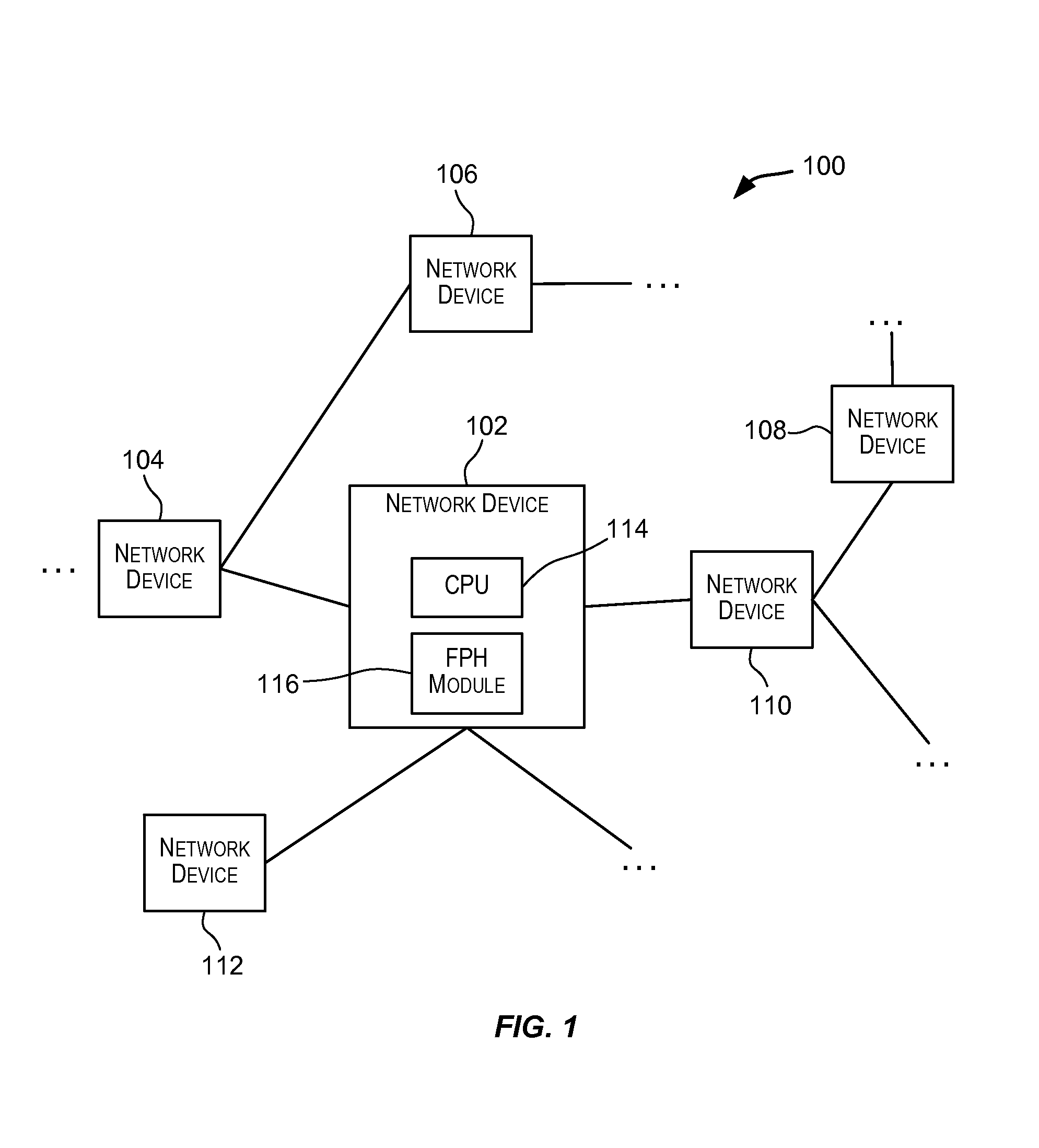

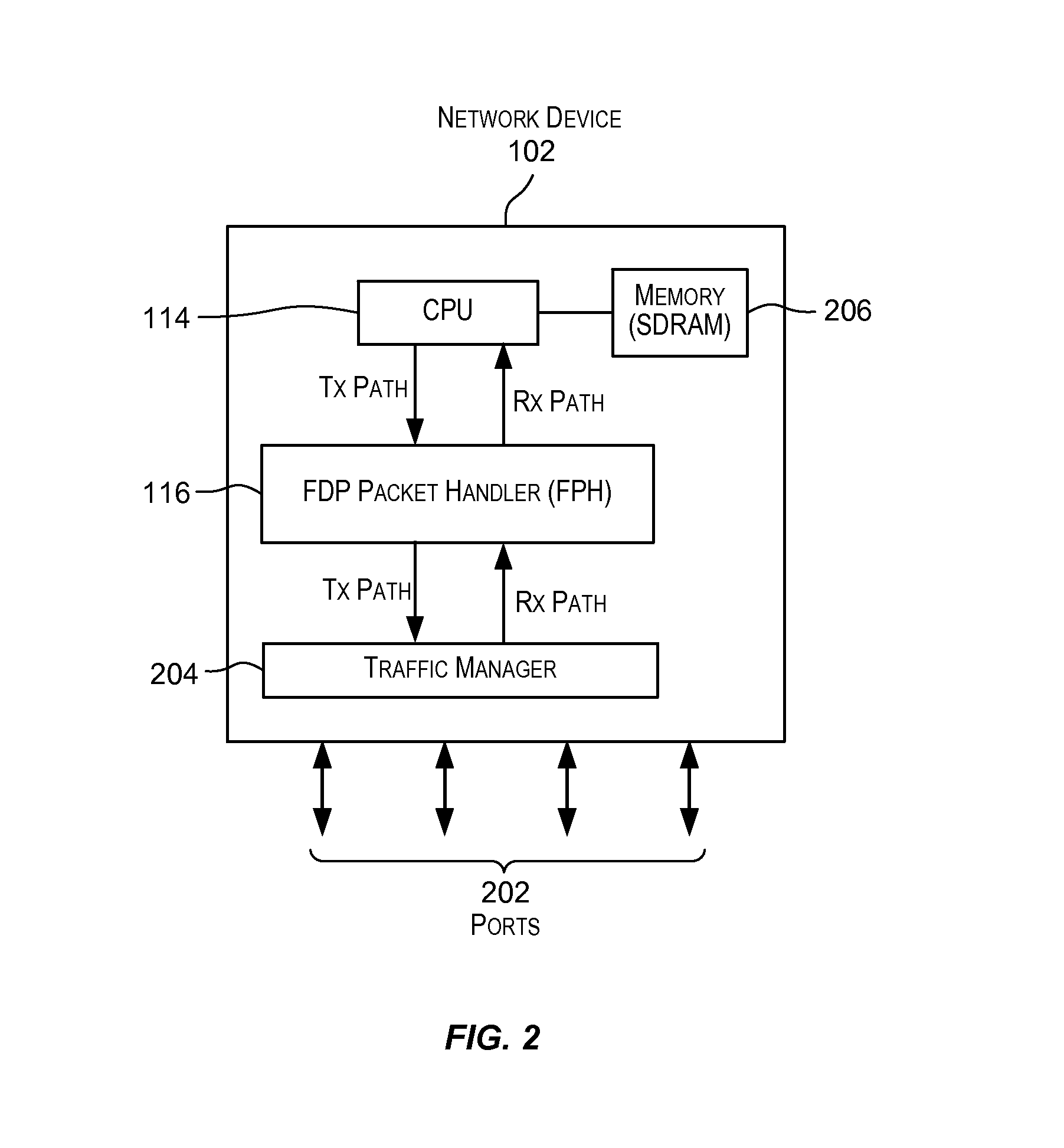

Techniques for detecting non-receipt of fault detection protocol packets

Owner:EXTREME NETWORKS INC

Delay-reduced stall avoidance mechanism for reordering a transport block

InactiveUS20060062223A1Reduce transmission delayAvoid procrastinationNetwork traffic/resource managementError preventionMissing dataUplink transmission

A method for implementing a stall avoidance mechanism during uplink transmission of data blocks from transmitter to a receiver includes first determining a missing data block in response to a successful receipt of a received data block at the receiver. Once the missing data block is determined, the receiver requests retransmission of the missing data block. The receiver starts a timer when the request for retransmission is made such that the timer has a time value based on the number of reception attempts of the received data block made by the receiver.

Owner:NOKIA SOLUTIONS & NETWORKS OY

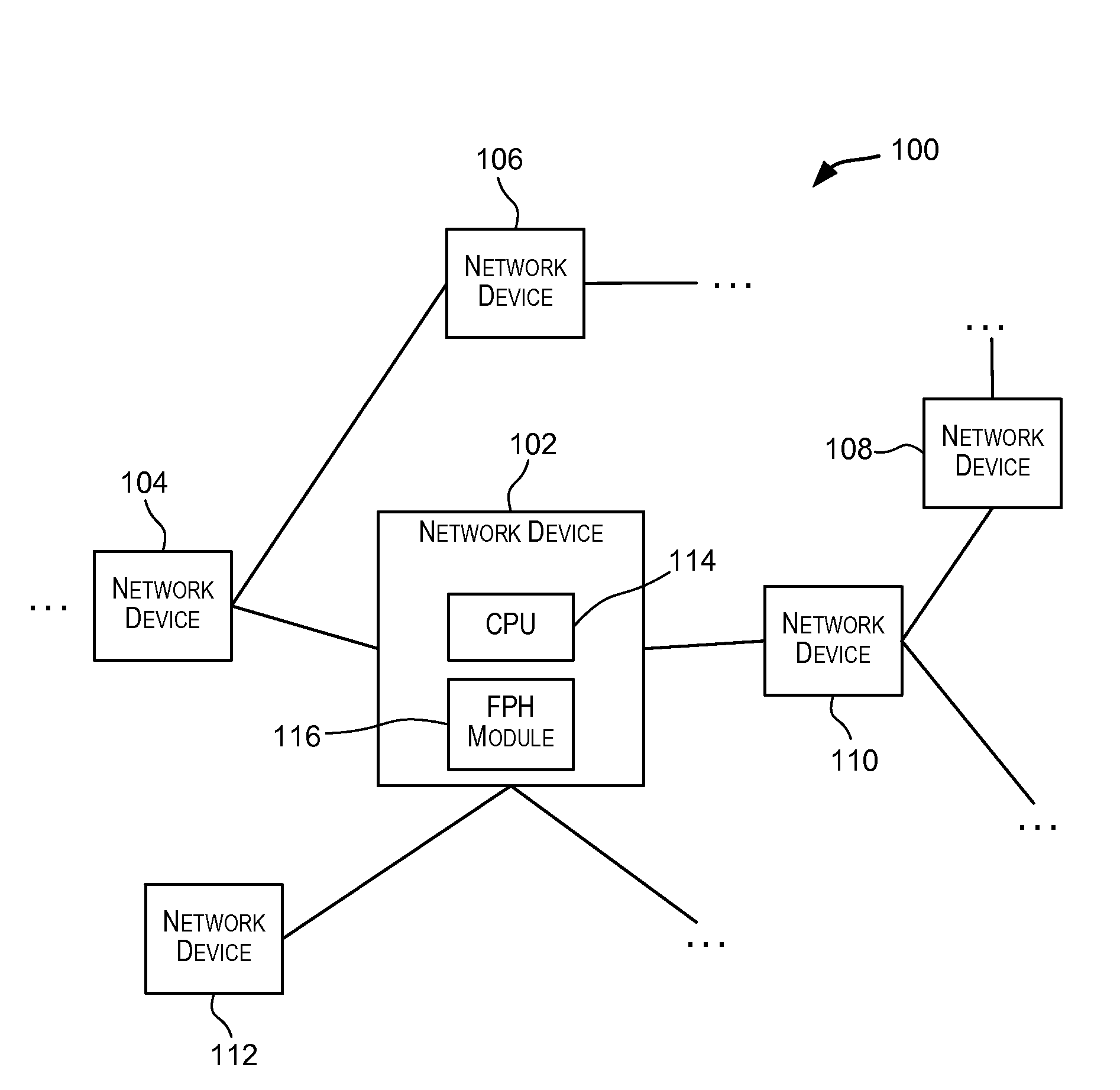

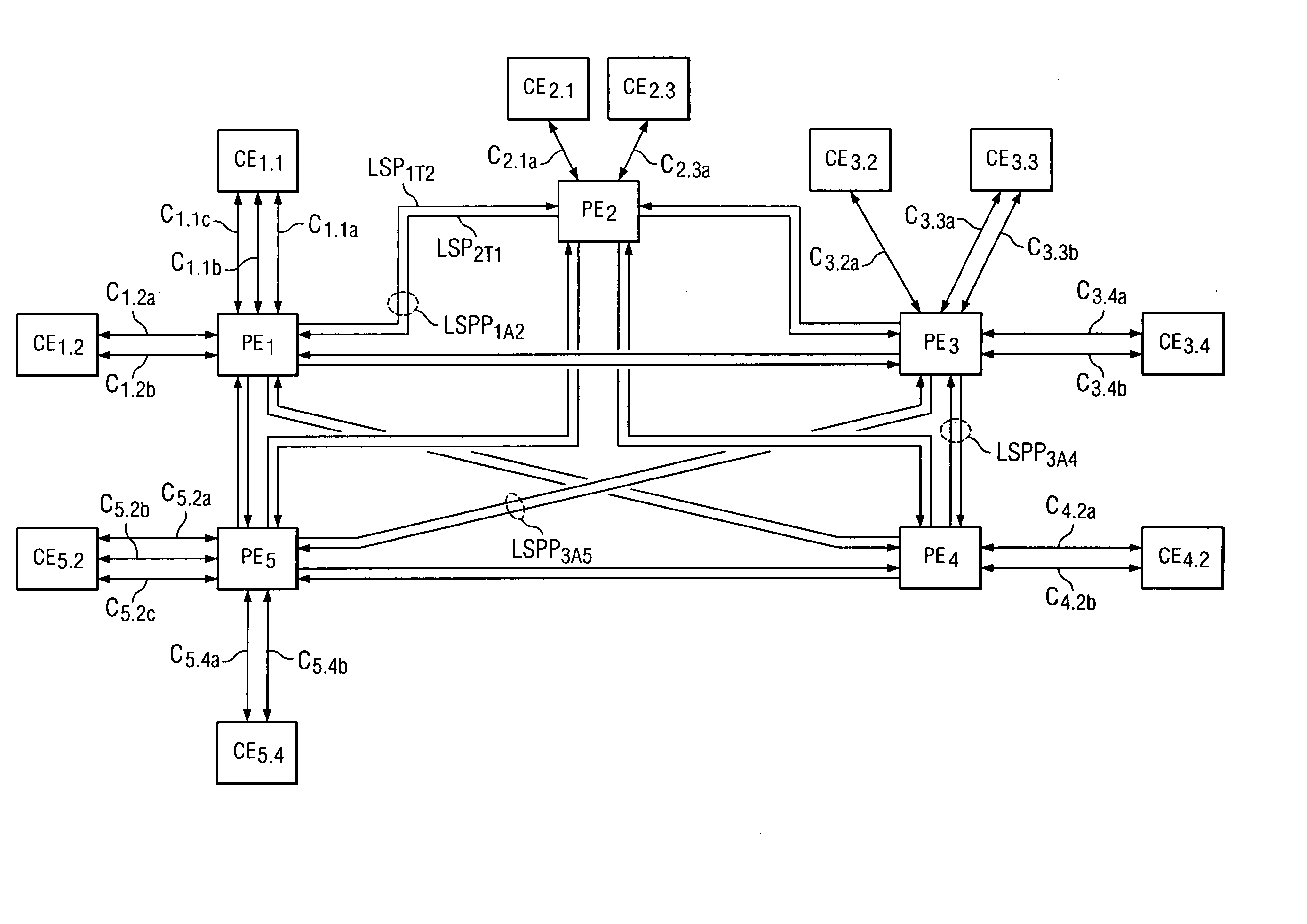

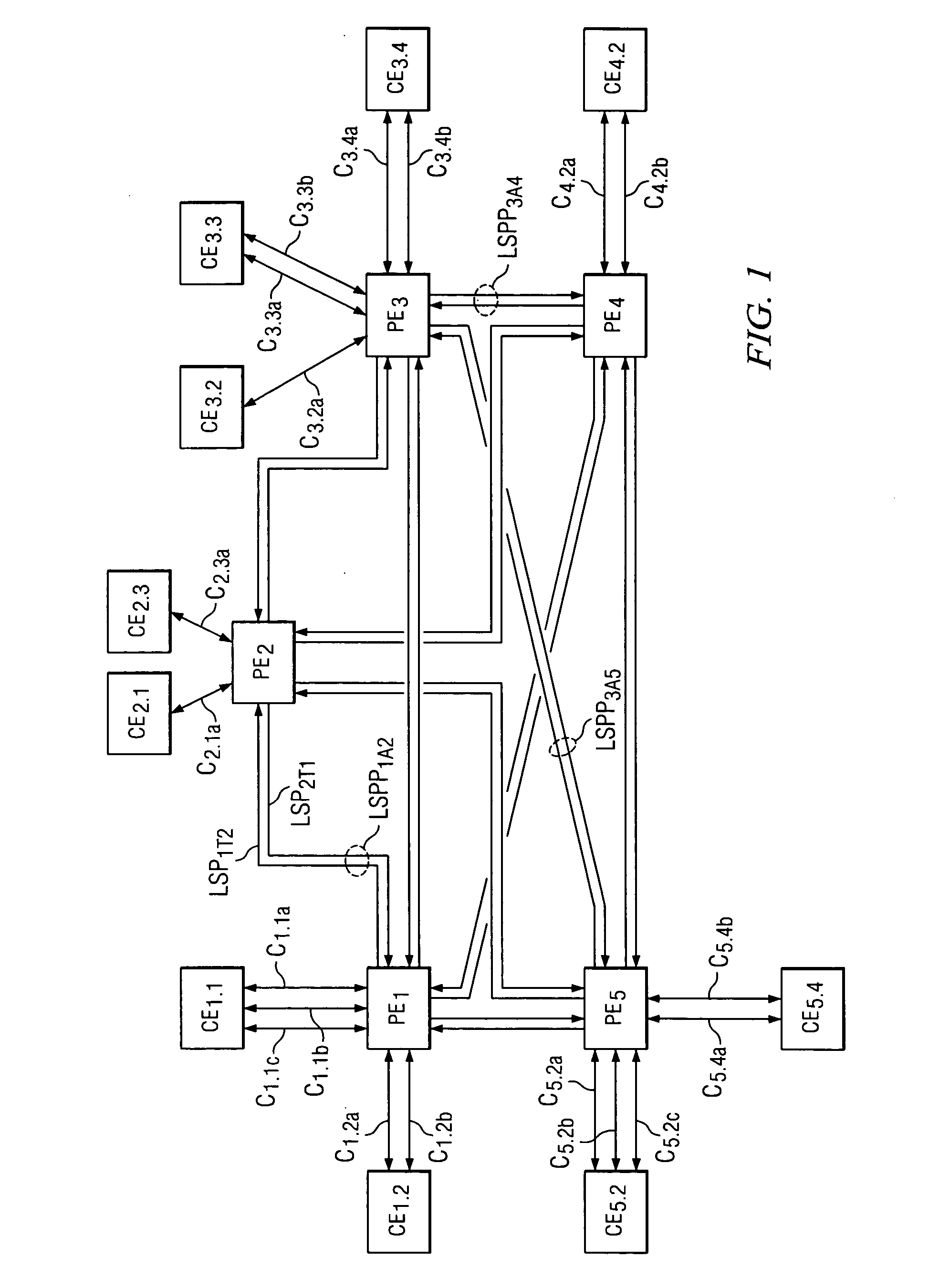

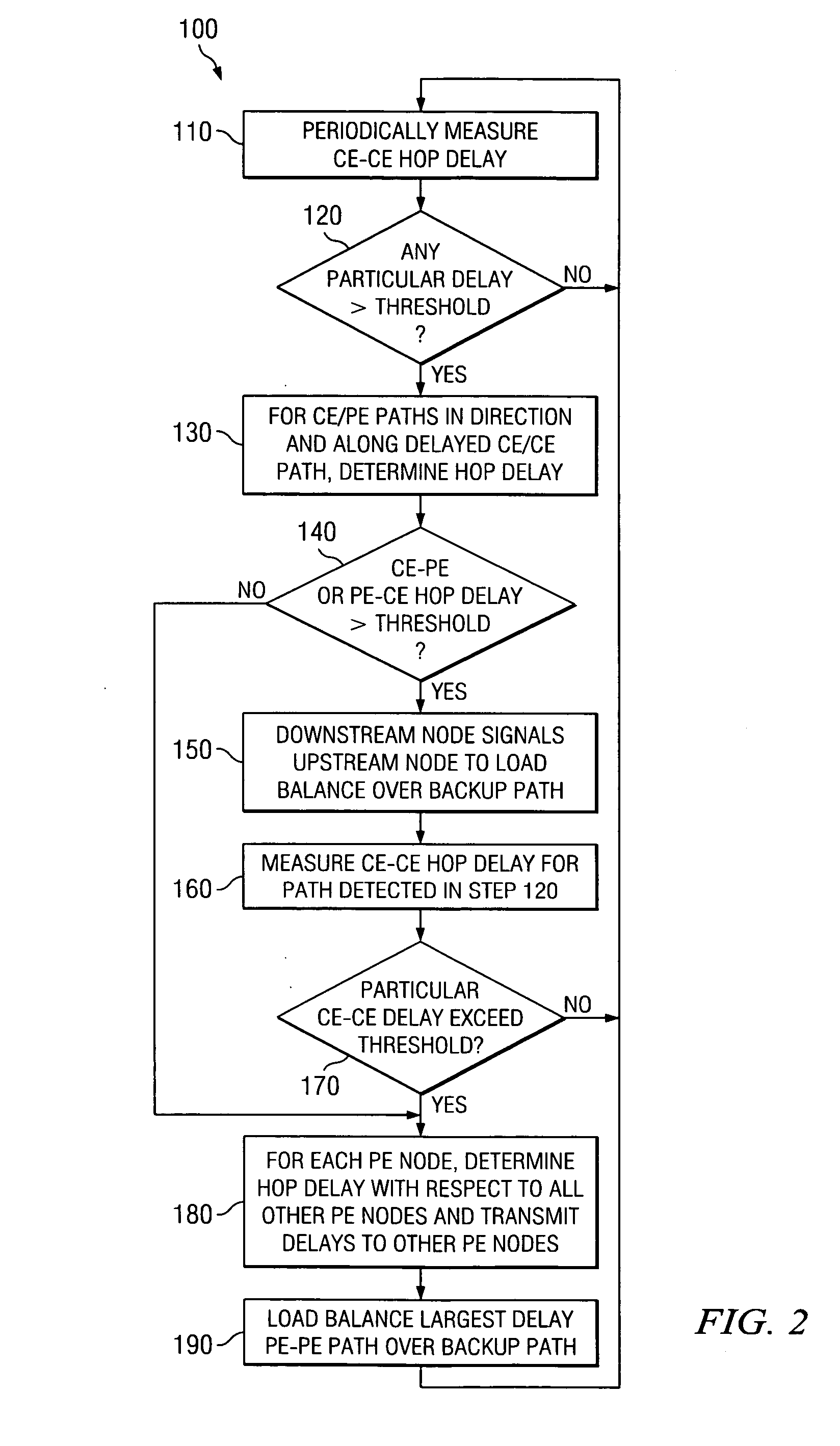

Load balancing in a virtual private network

ActiveUS20060018252A1Error preventionFrequency-division multiplex detailsNetworked systemDistributed computing

A network system (10). The system comprises a plurality of nodes (PE, CE). Each node in the plurality of nodes is coupled to communicate with at least one other node in the plurality of nodes. Further, each node in the plurality of nodes is coupled to communicate to another node via a respective primary path and via a respective backup path. Still further, each node in the plurality of nodes is operable to perform the steps of, when receiving network traffic as a receiving node, detecting delay (110, 120; 130, 140; 160, 170) in traffic received from a transmitting node, and, in response to detecting delay, communicating a signal to the transmitting node. In response to the signal, the transmitting node is operable to dynamically adjust (150; 190) a distribution of traffic through a respective primary path and a respective backup path from the transmitting node to the receiving node.

Owner:RPX CORP

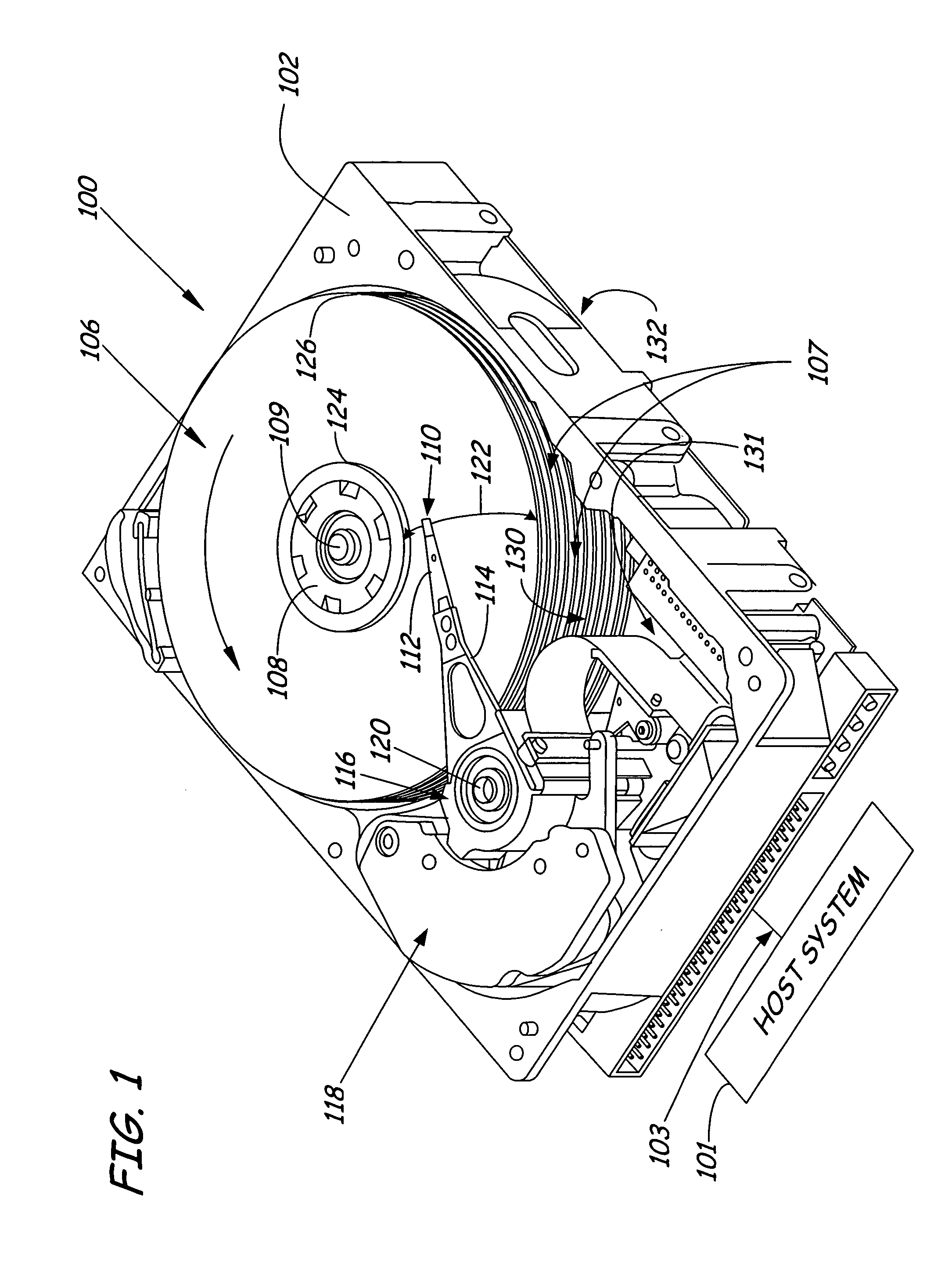

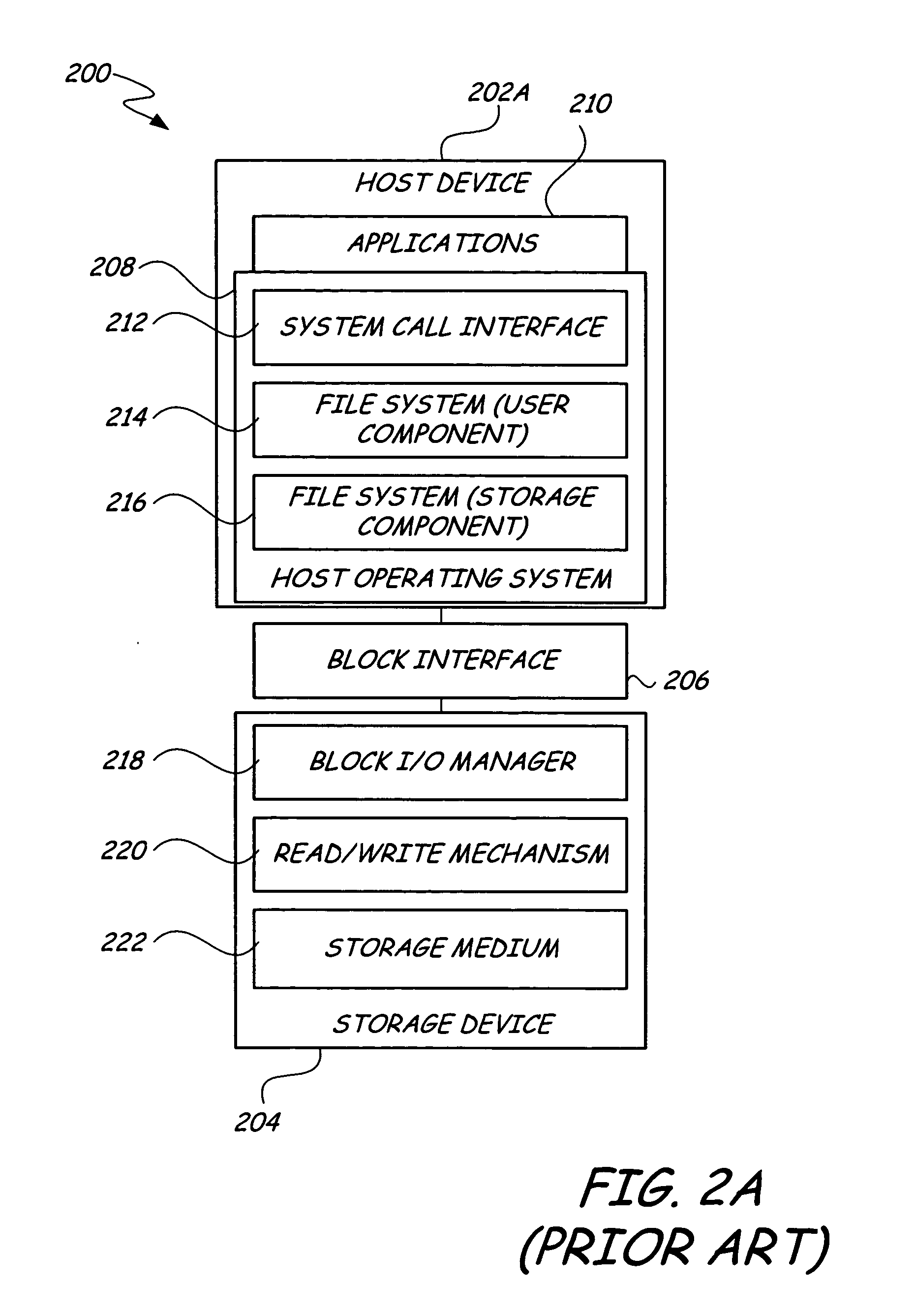

Redundancy for storage data structures

Owner:SEAGATE TECH LLC

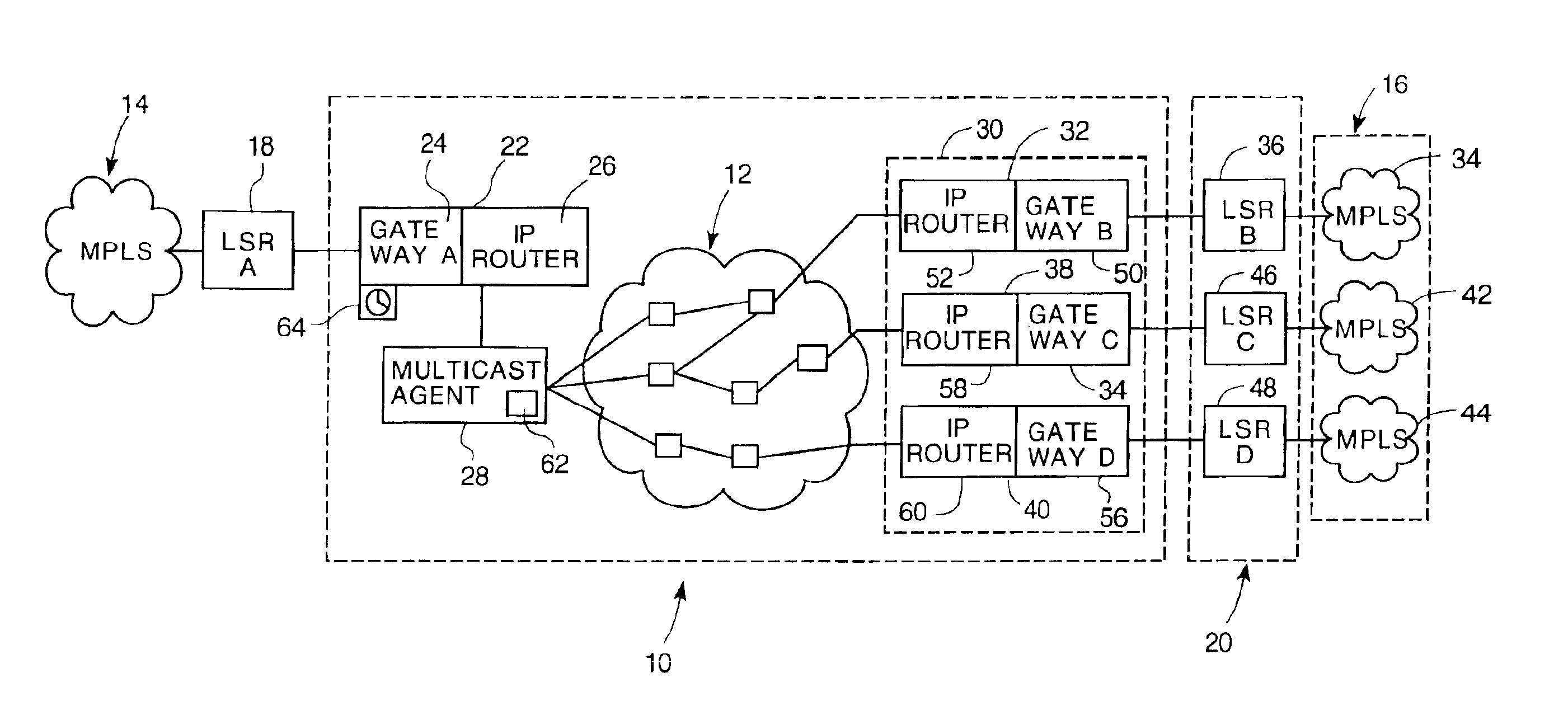

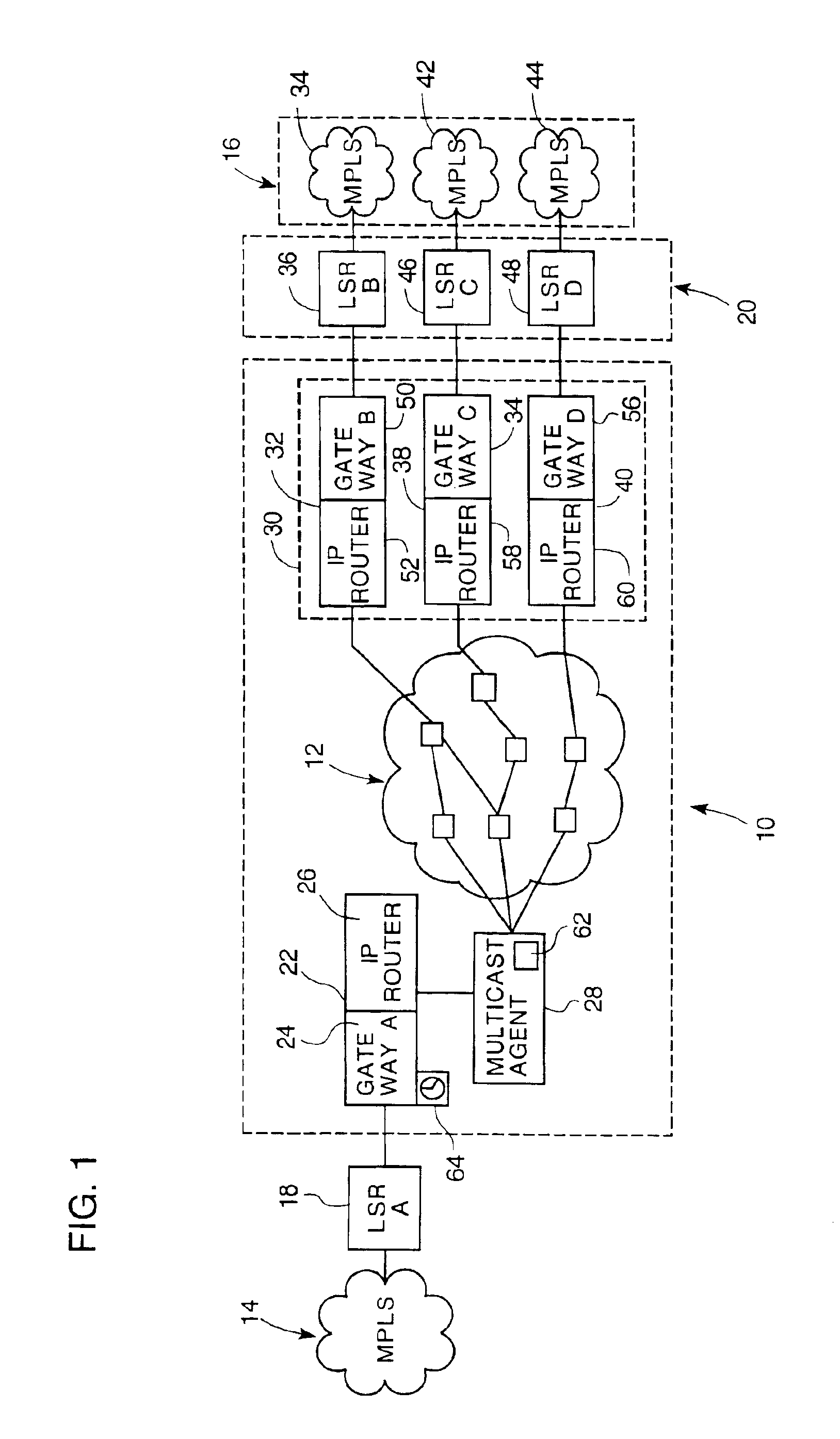

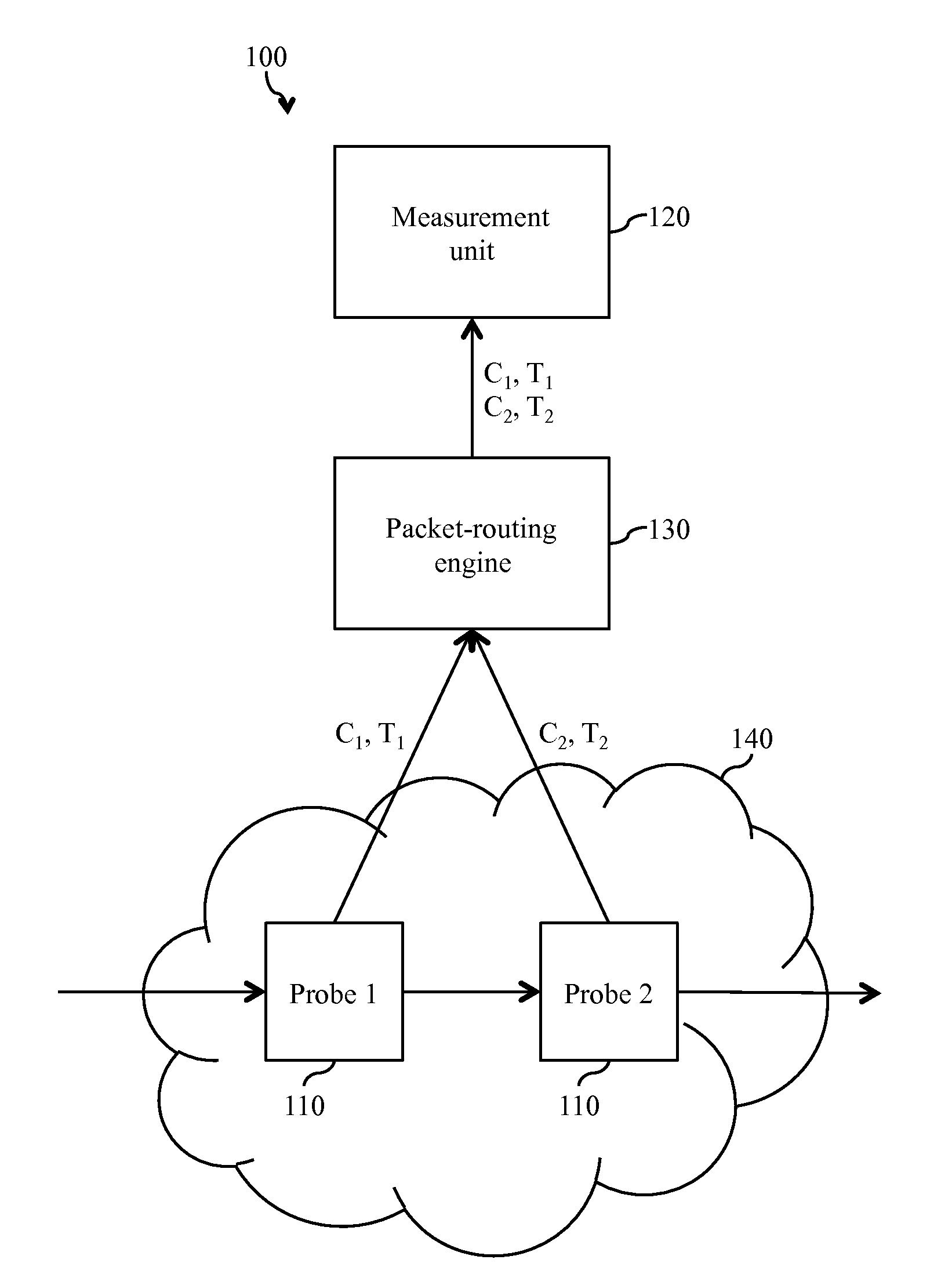

Distributed label switching router

InactiveUS6947428B1Error preventionFrequency-division multiplex detailsPublic networkDistributed computing

Owner:RPX CLEARINGHOUSE

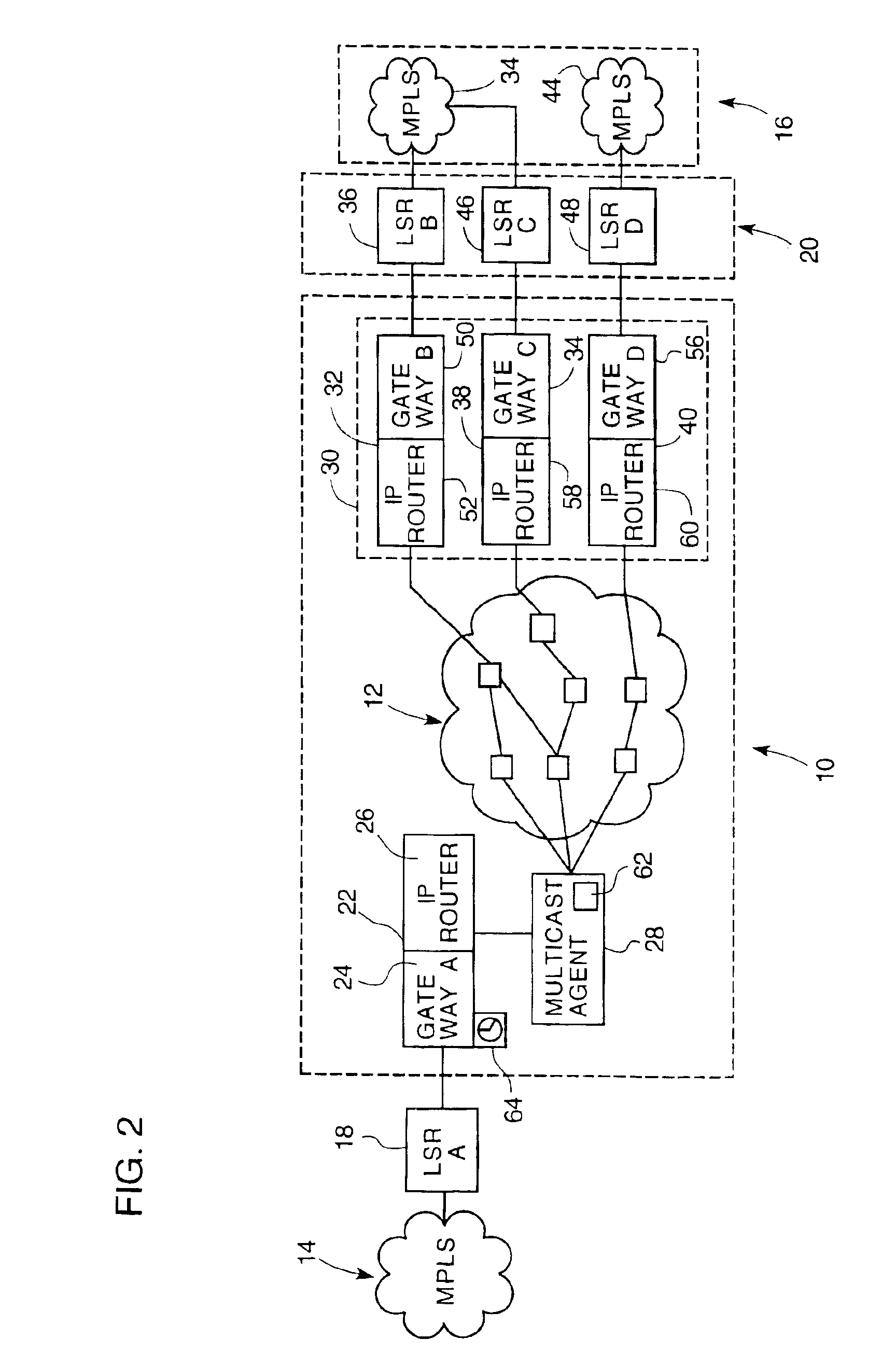

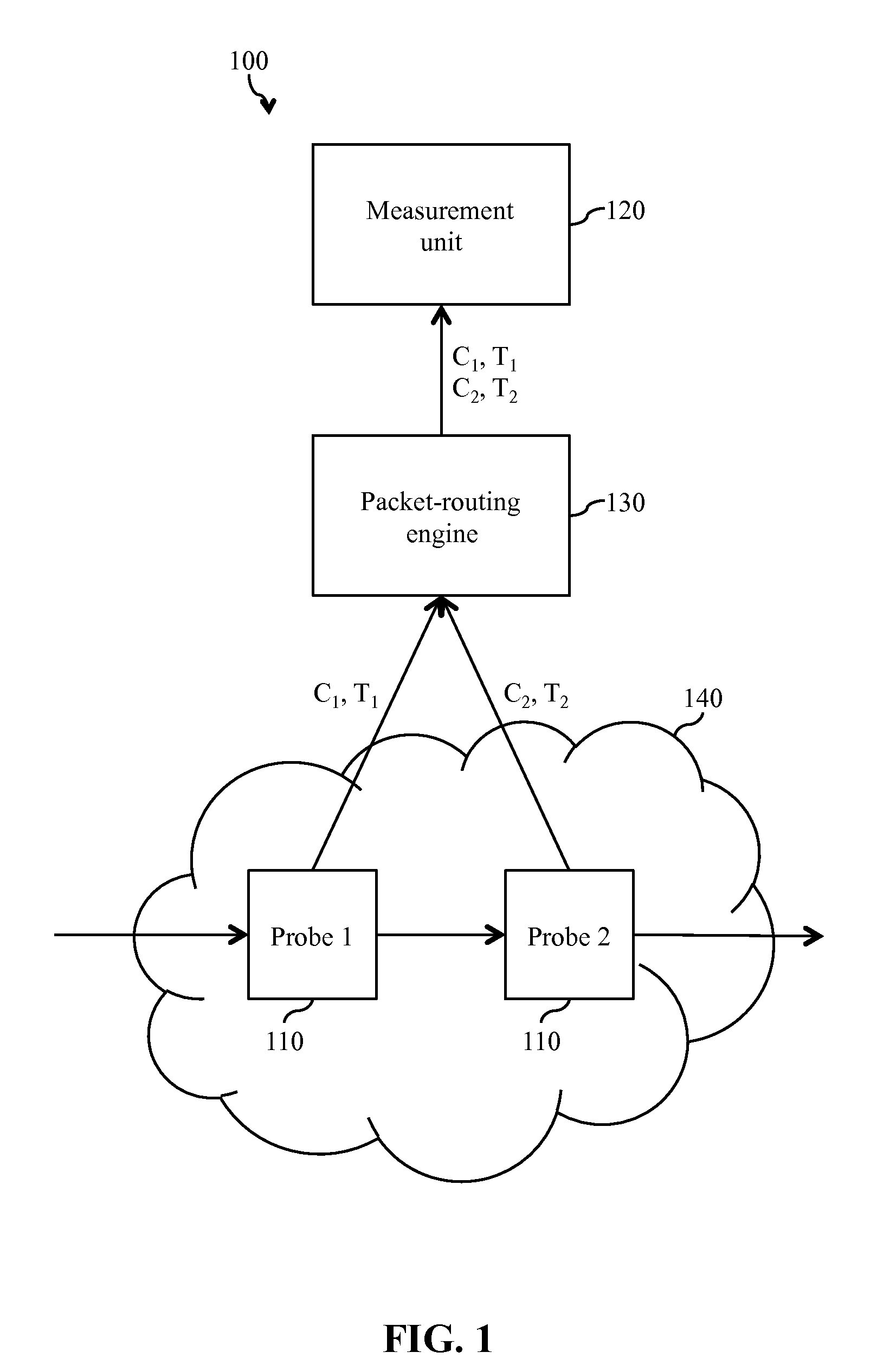

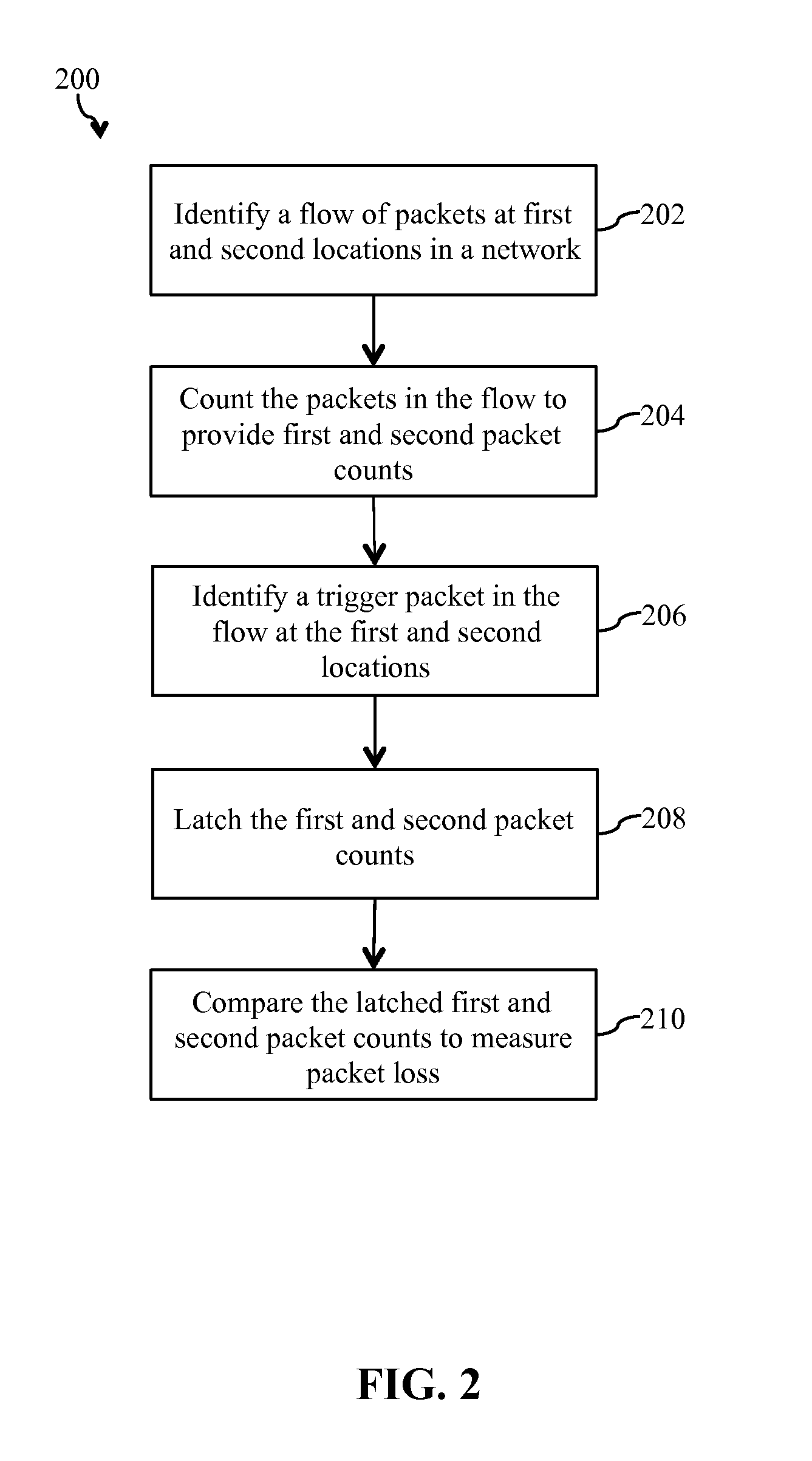

Method and system for measuring packet loss

ActiveUS20140328206A1Error preventionFrequency-division multiplex detailsReal-time computingPacket loss

Owner:VIAVI SOLUTIONS INC

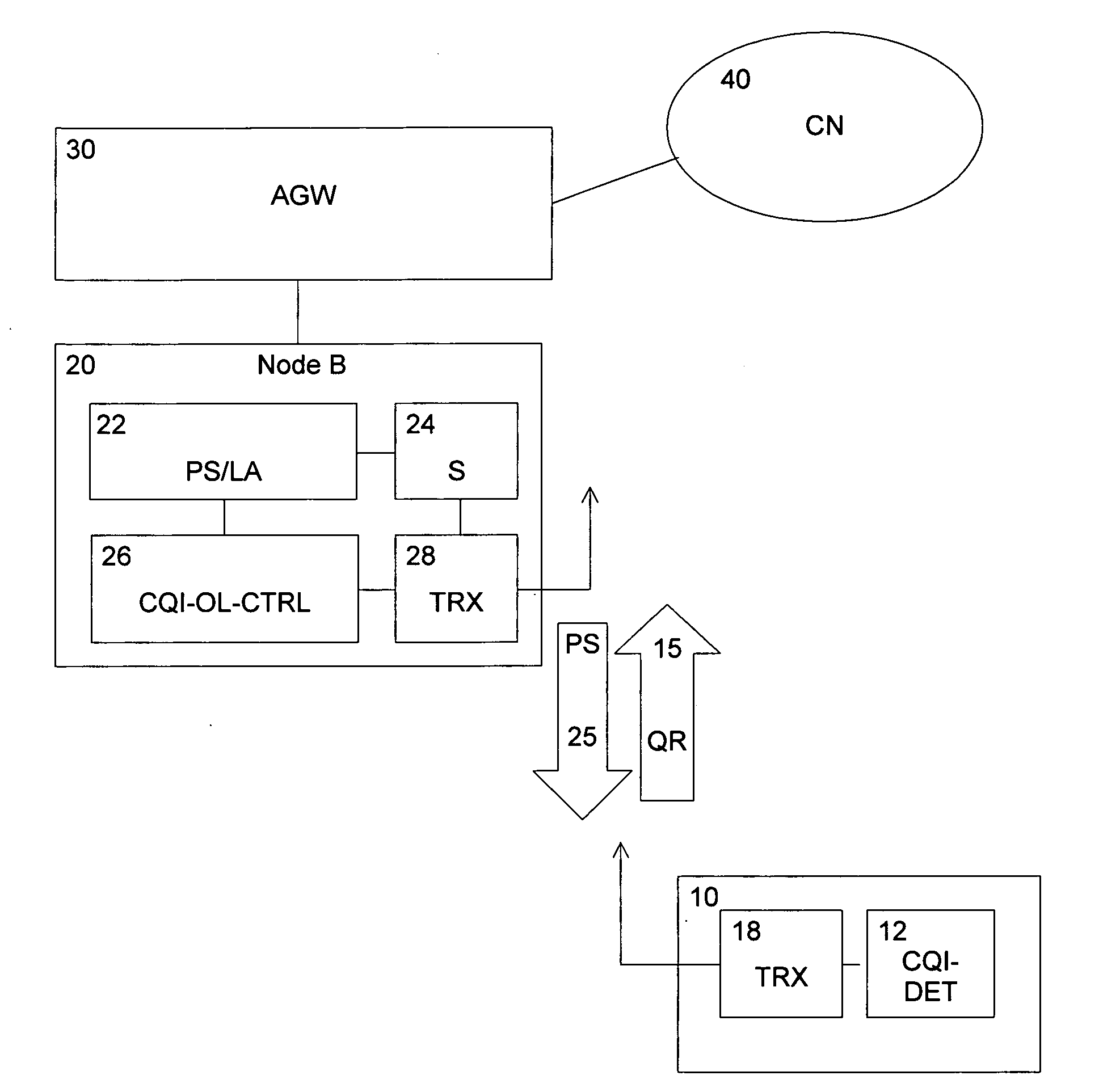

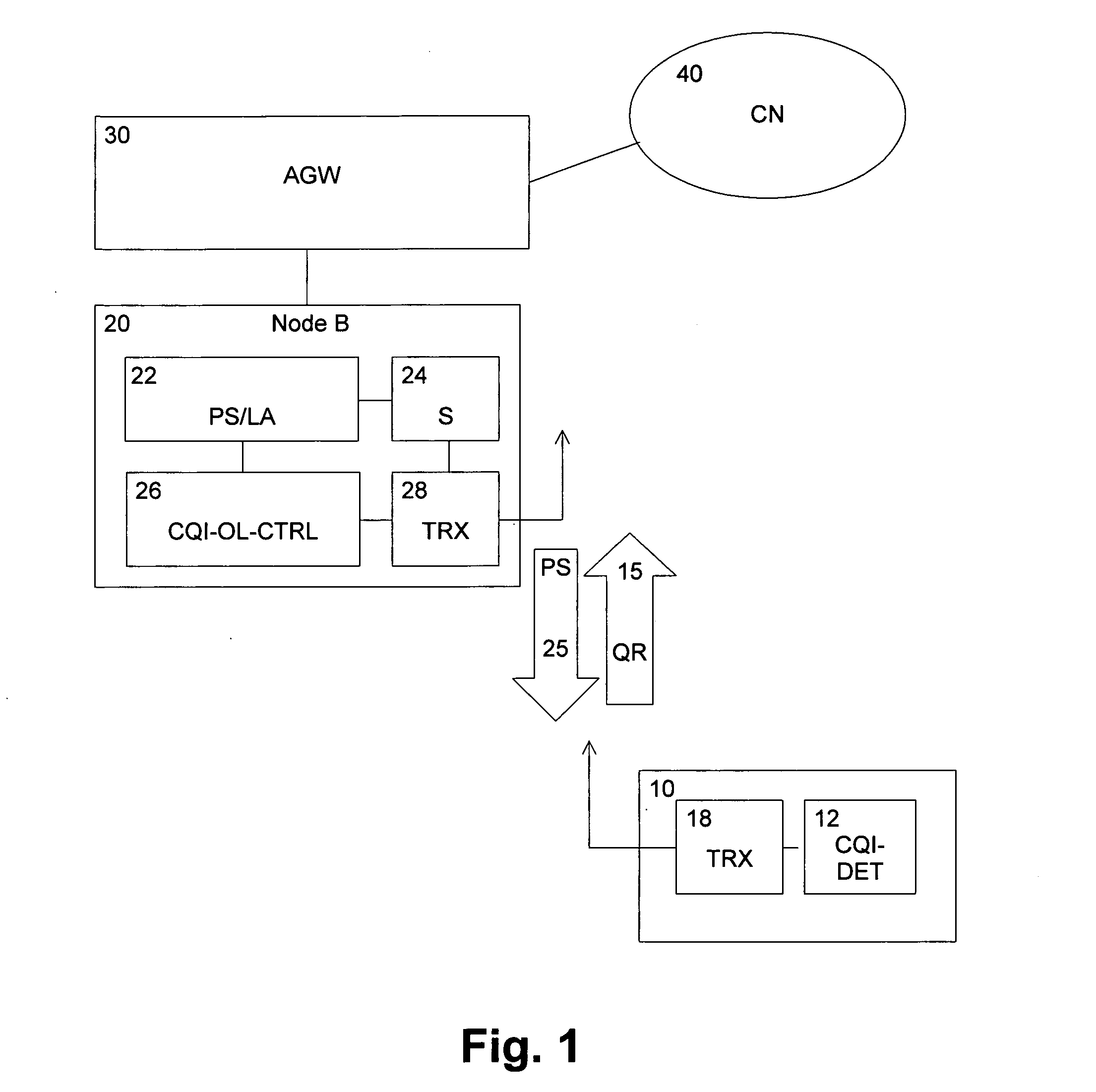

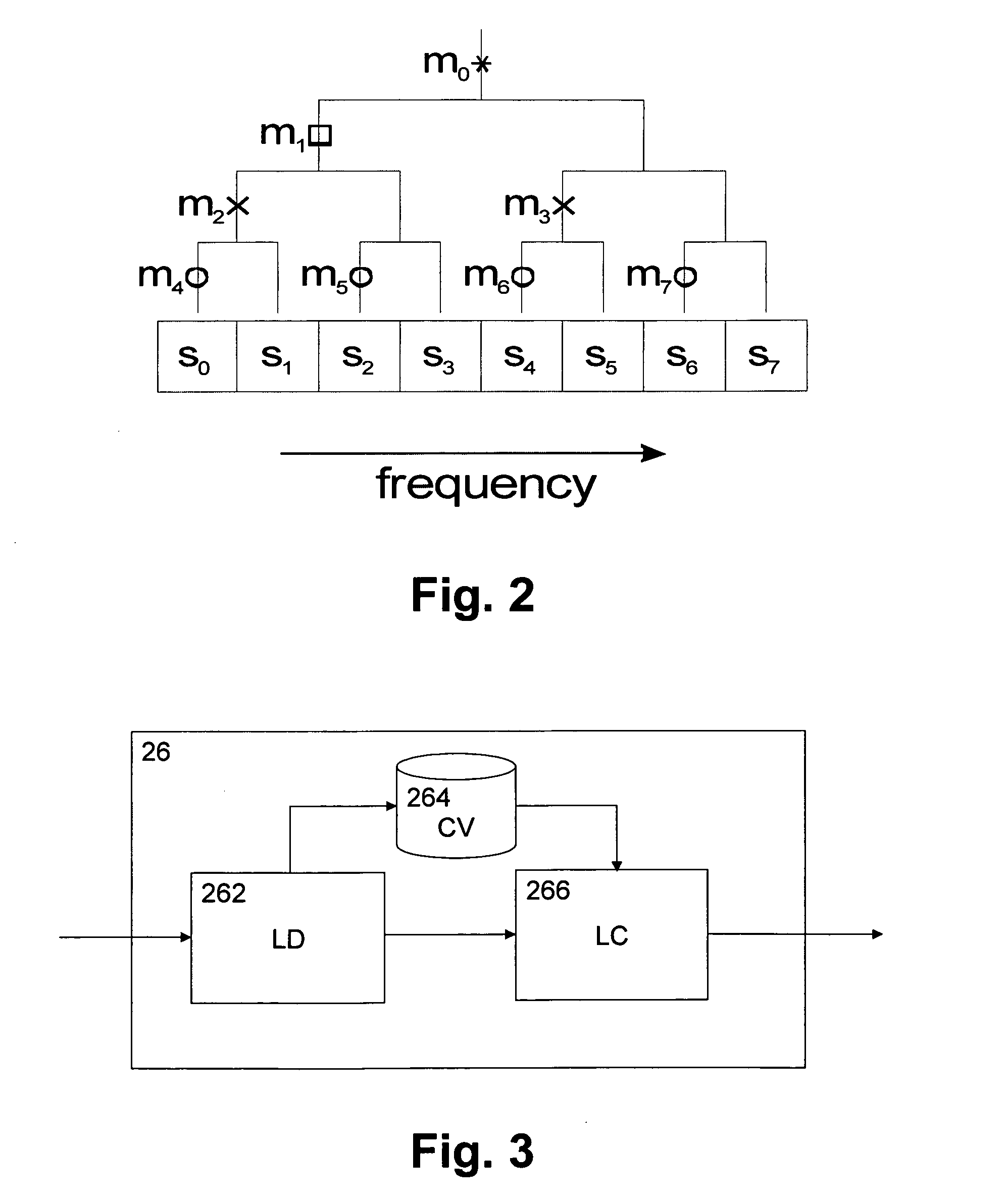

Multi-level control for measurement reports

InactiveUS20080004030A1Error preventionFrequency-division multiplex detailsNetwork elementEngineering

Owner:WSOU INVESTMENTS LLC

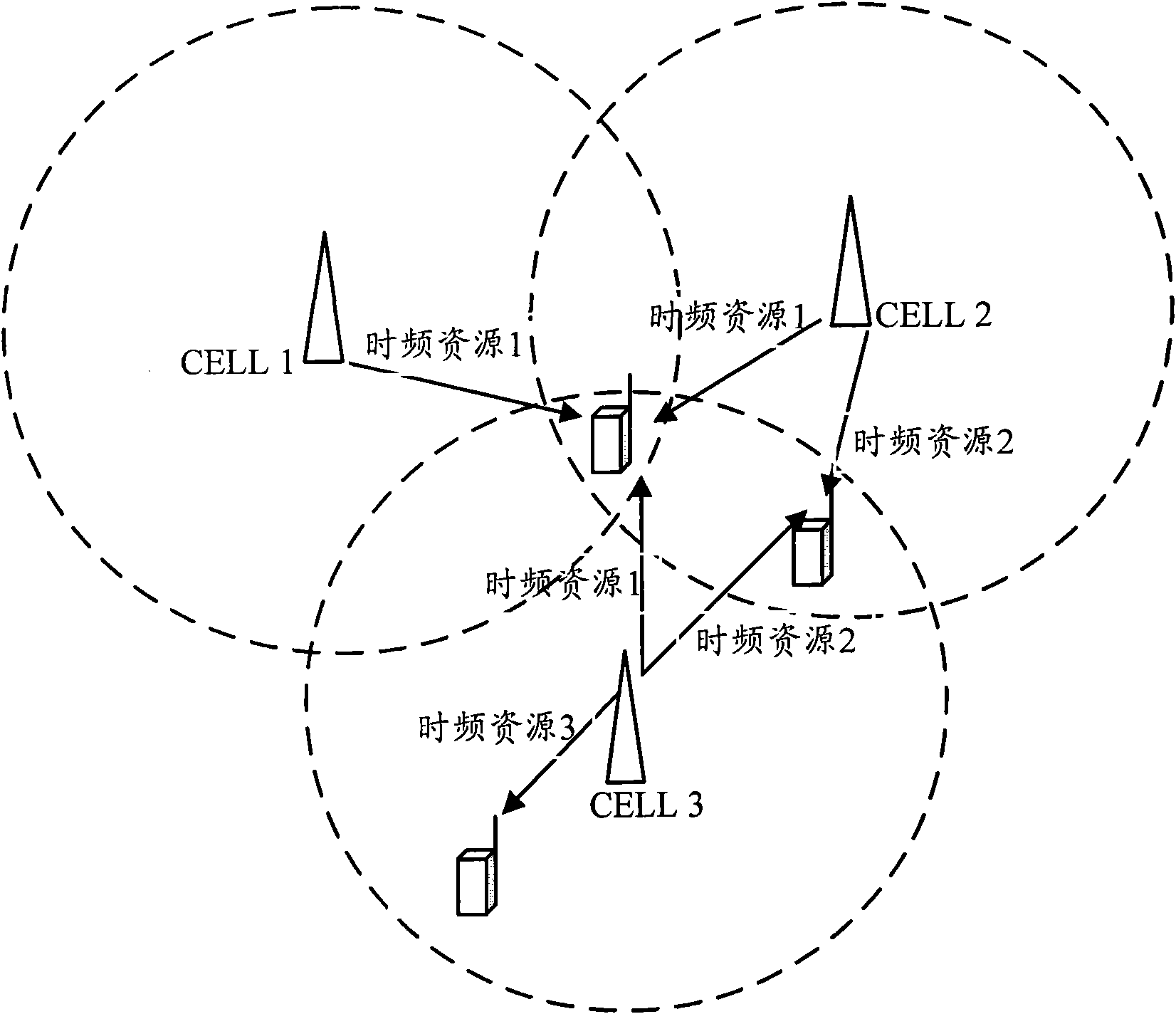

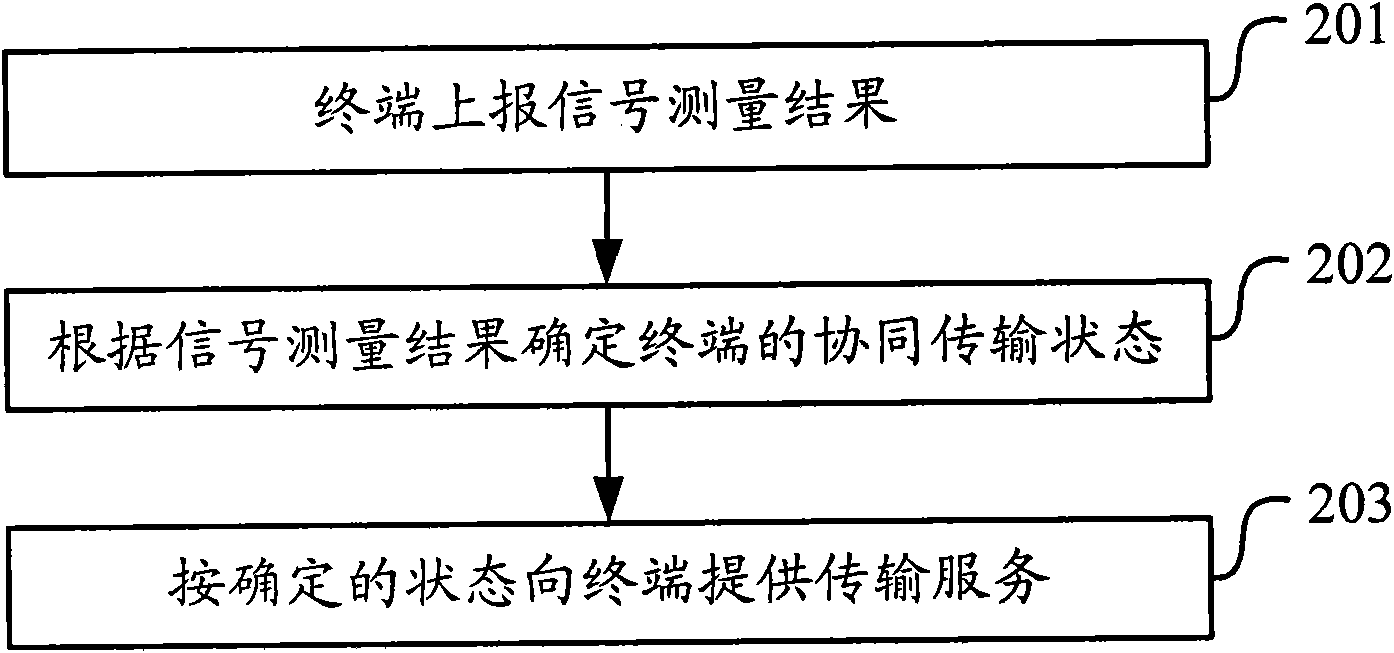

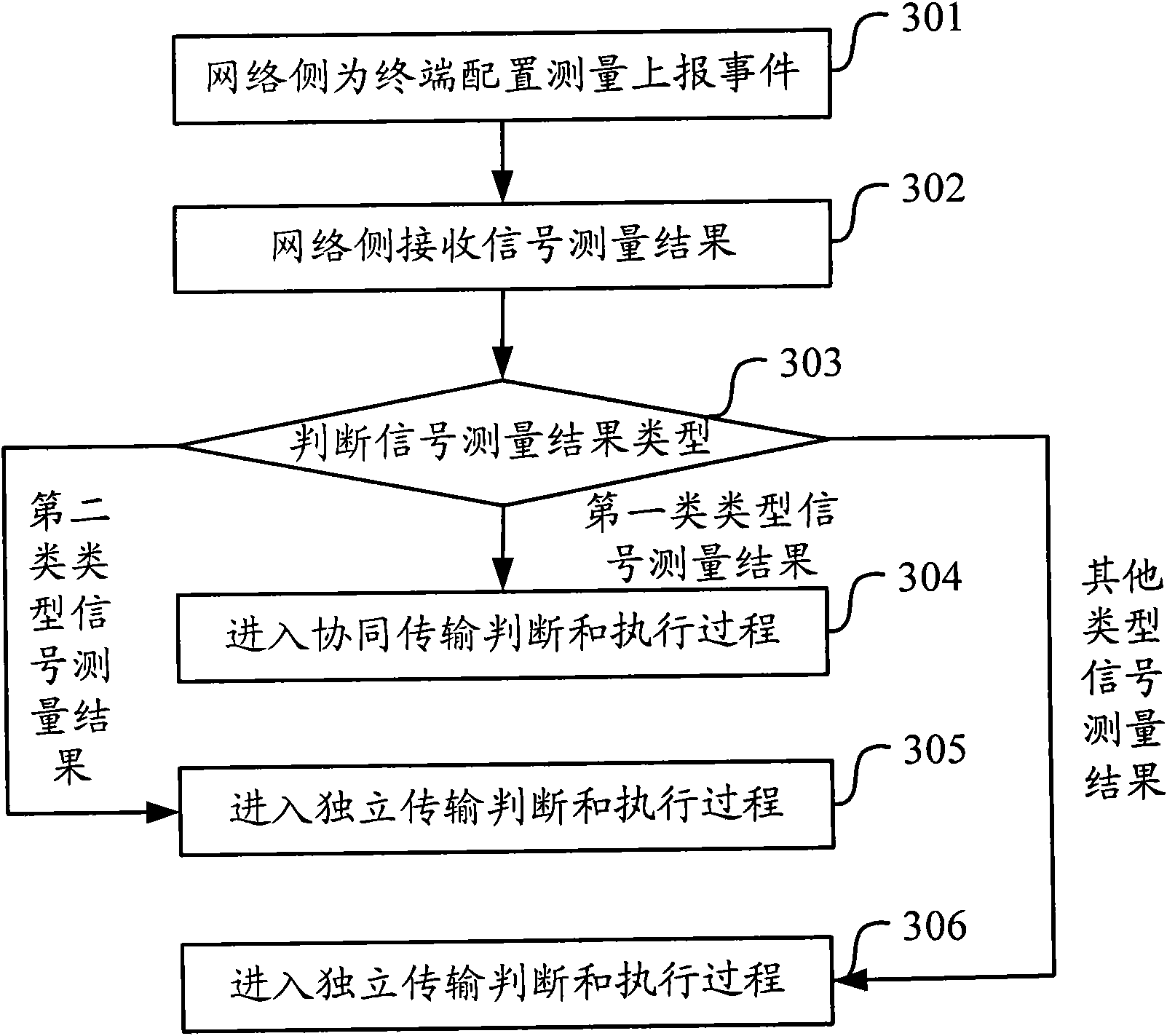

Method and device for cooperative transmission

ActiveCN101789806AOvercoming the inadequacies that cannot meet the needs of CoMPImprove throughputError preventionWireless communicationThroughputReal-time computing

Owner:DATANG MOBILE COMM EQUIP CO LTD

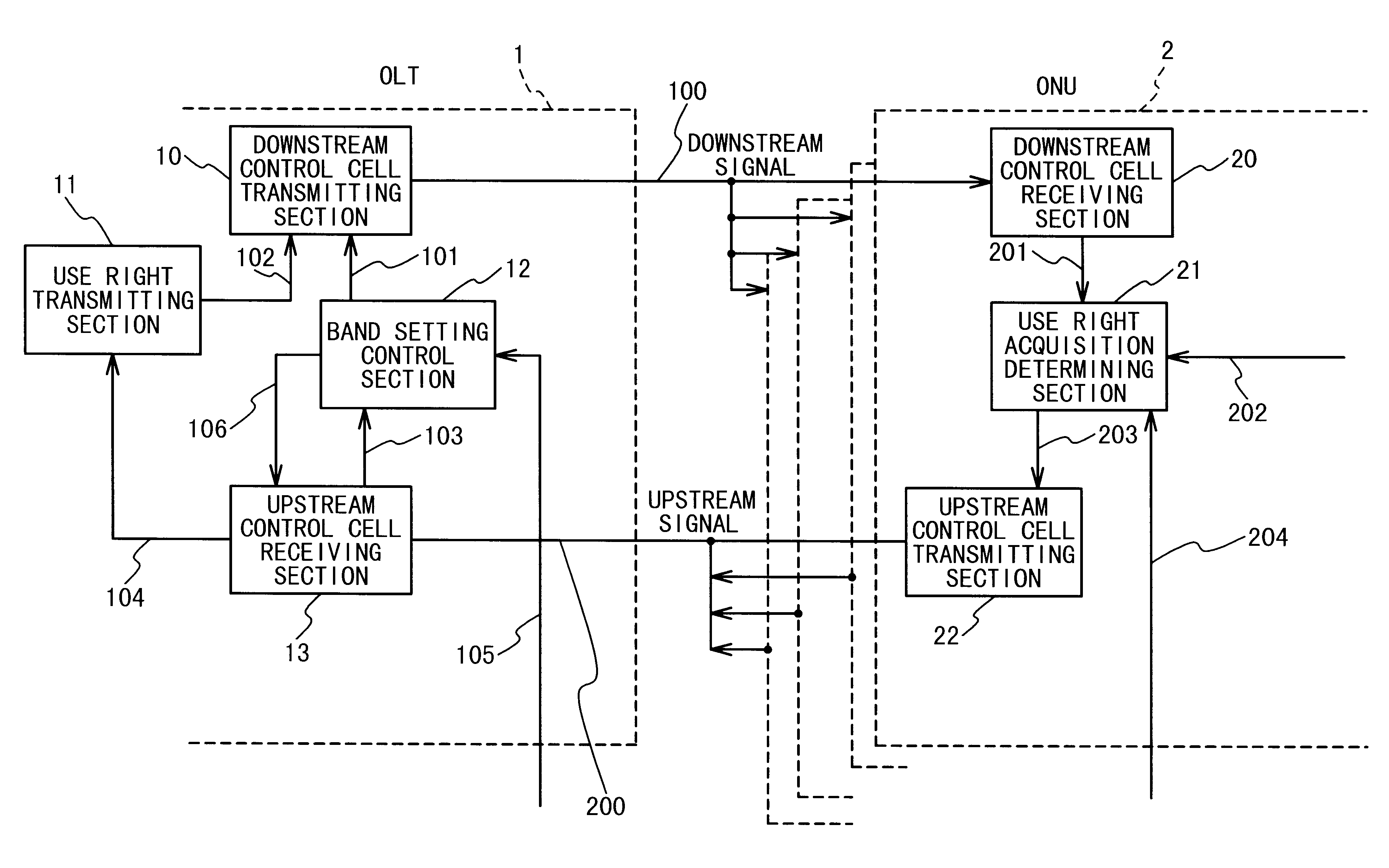

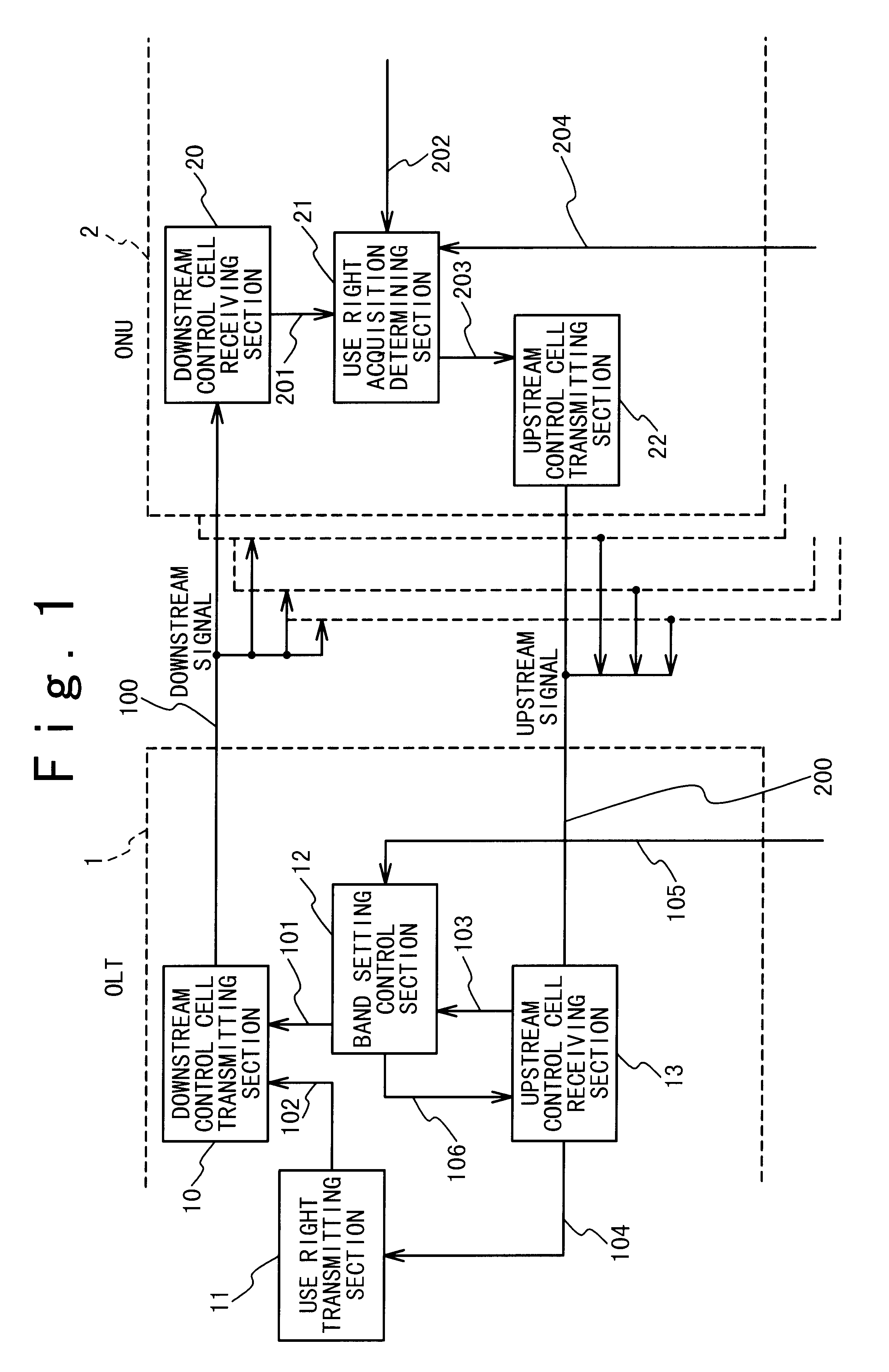

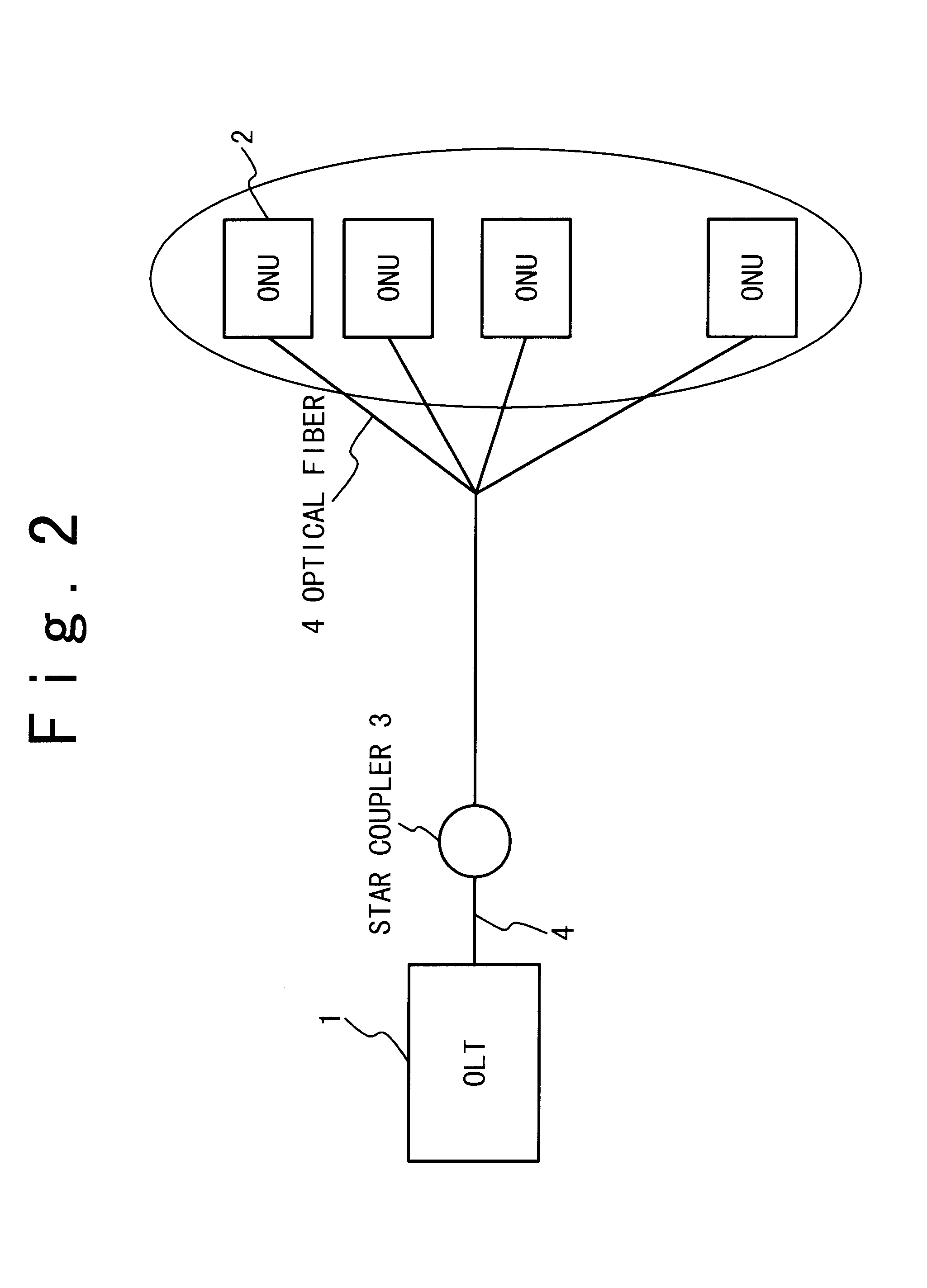

Unused band use right acquisition controlling method and passive optical network for the same

InactiveUS6850711B2Easy to useError preventionFrequency-division multiplex detailsControl cellOptical line termination

Owner:JUMIPER NETWORKS INC

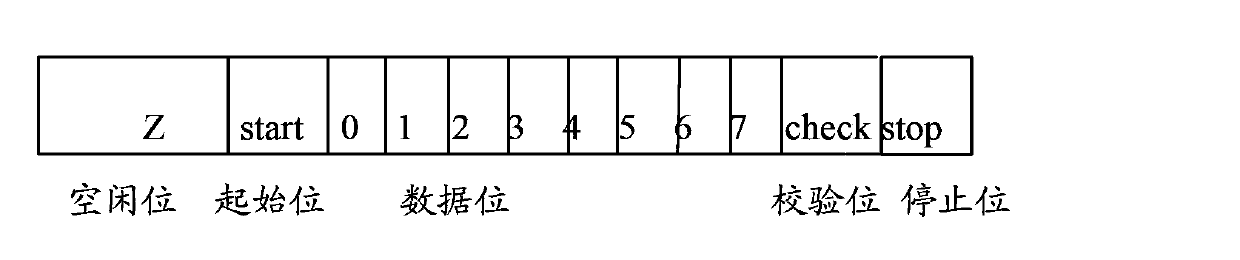

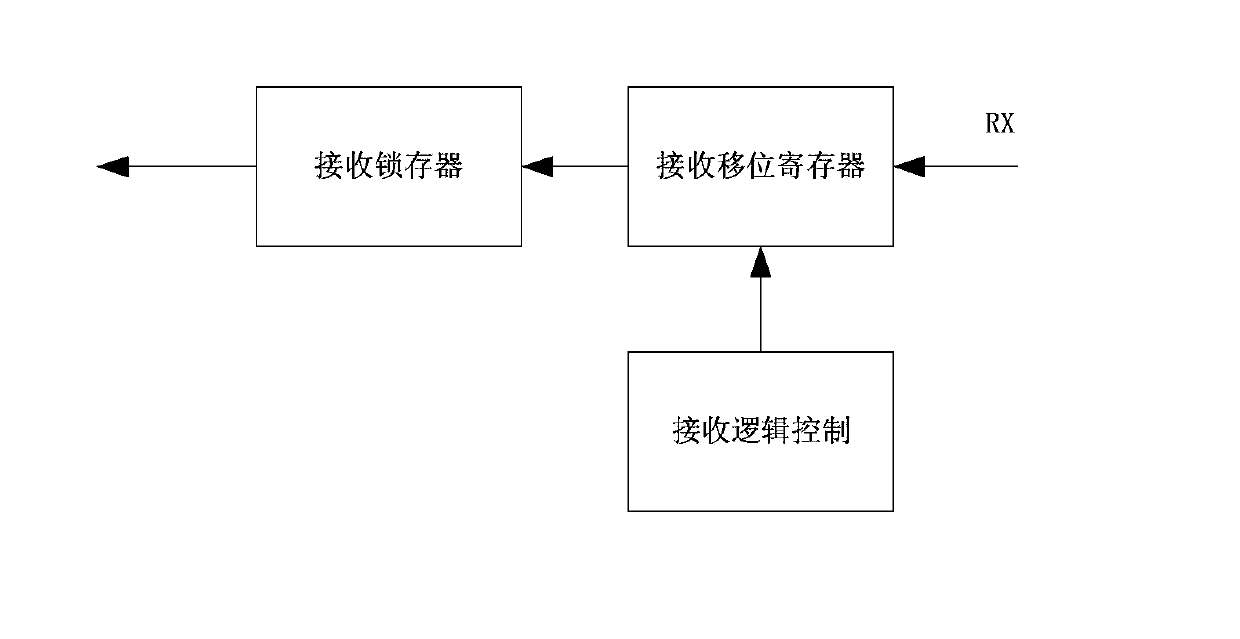

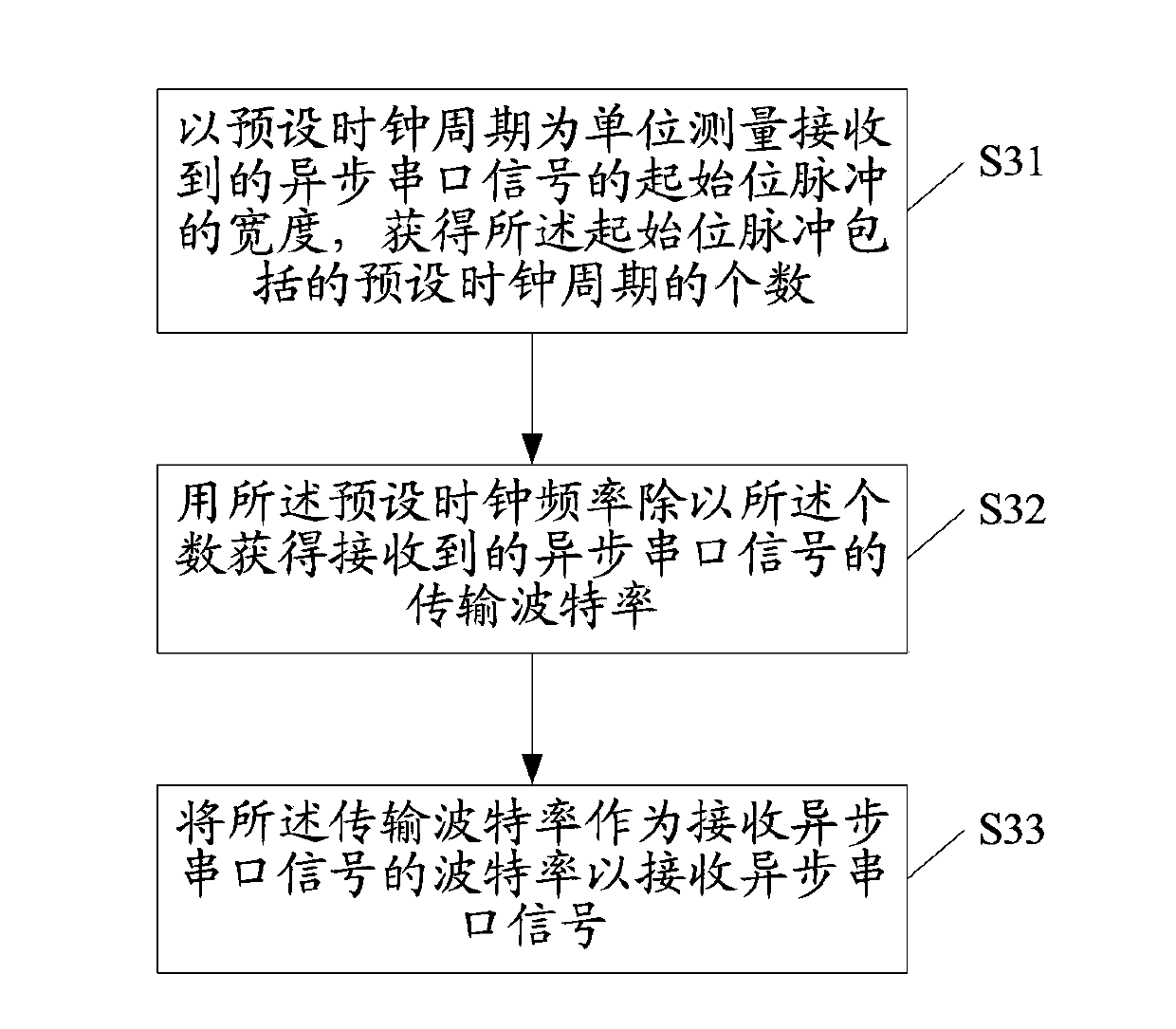

Baud rate adaptive method for UART, device and UART

InactiveCN103684678AGet durationAccurate receptionError preventionUniversal asynchronous receiver/transmitterComputer science

Owner:STATE GRID CORP OF CHINA +2

HIGH SPEED PLC NETWORK-ETHERNET BRIDGE SYSTEM SUPPORTING QoS

Provided is a bridge system of a high-speed PLC network and Ethernet. The bridge system includes a QoS control unit for controlling a QoS process of an entire bridge system; a flow managing unit for storing and managing connection information on a flow, QoS information required by each flow, and information required for executing a bridge function; a bridge QoS processing unit for allocating and managing internal resources of the bridge system and providing the QoS by controlling the QoS control unit and making reference to information stored in the flow managing; a PLC QoS processing unit for managing the QoS of the PLC network by control of the QoS control unit; and an Ethernet QoS processing unit for managing a link state of the Ethernet and providing the link state to the QoS control unit.

Owner:ELECTRONICS & TELECOMM RES INST

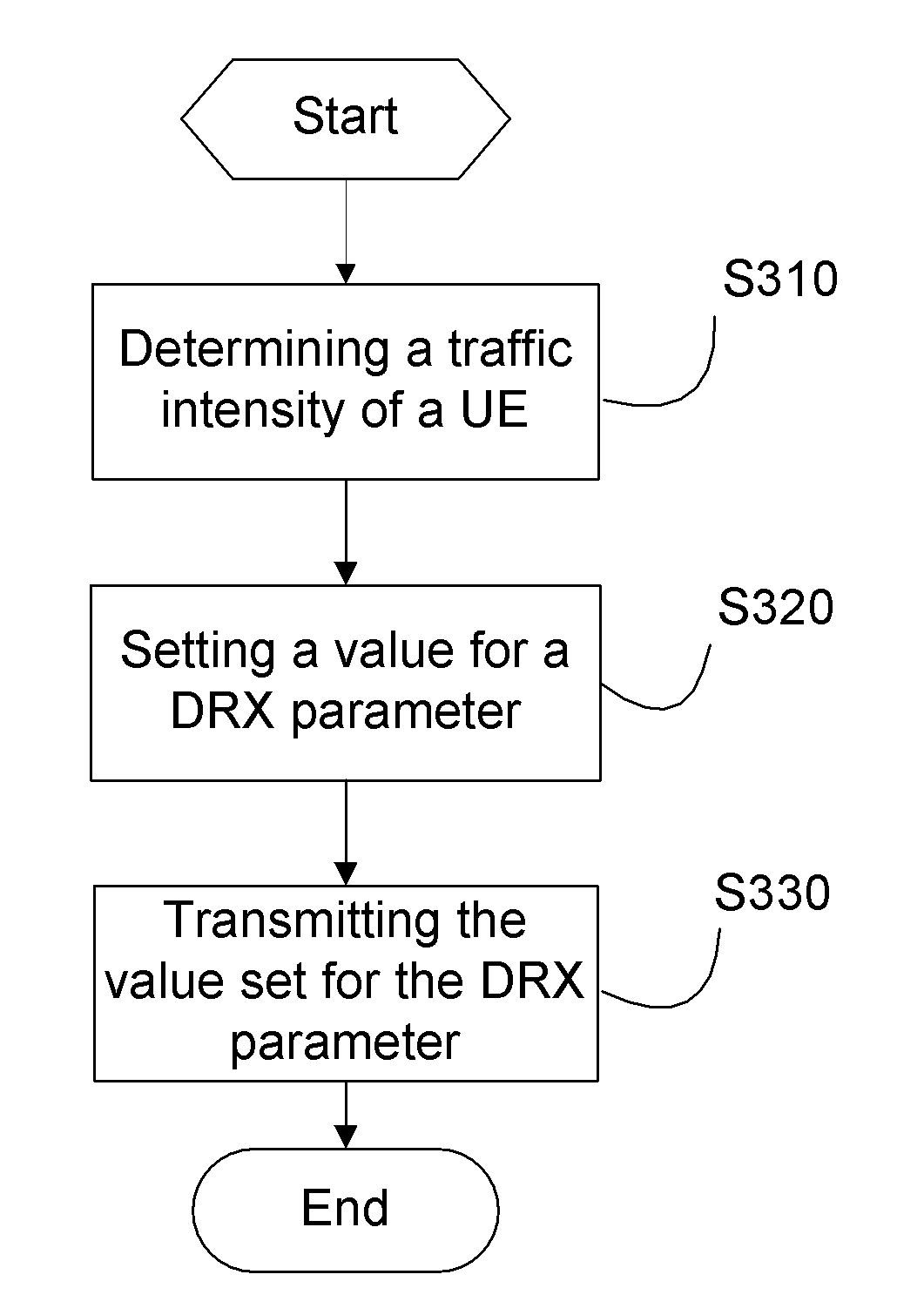

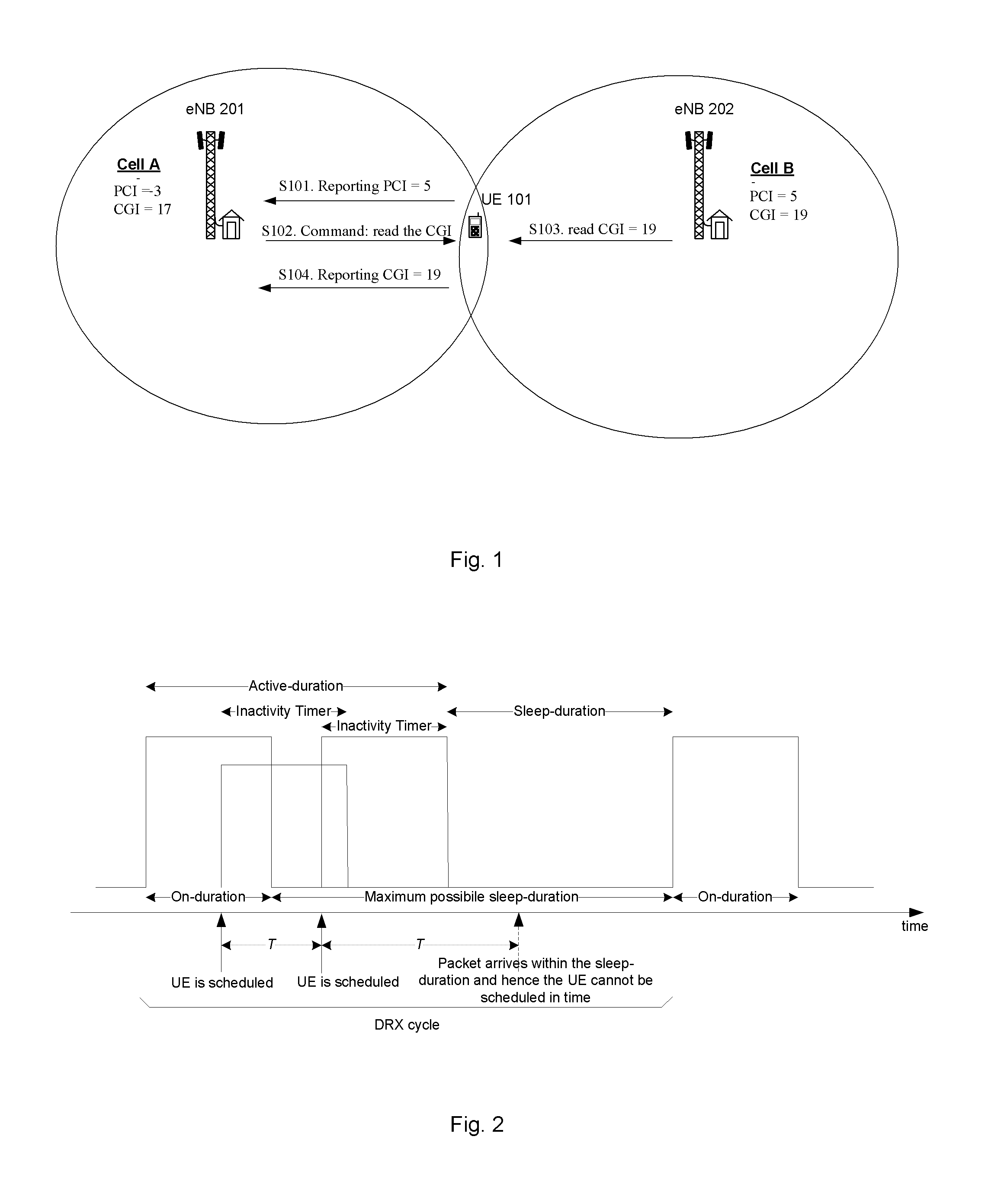

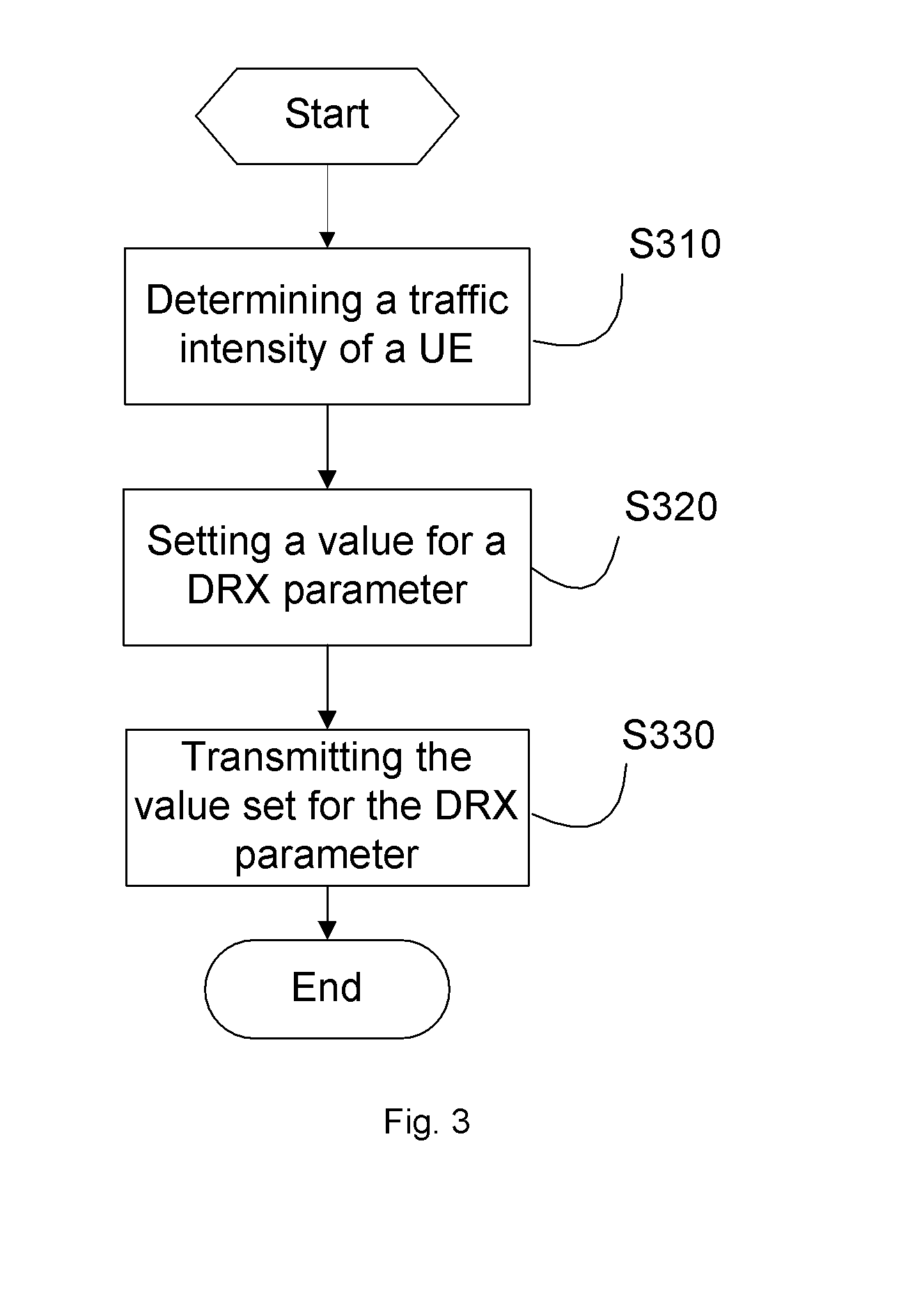

Drx parameter configuration method and associated base station for facilitating anr measurement

ActiveUS20150351151A1Improve performanceError preventionFrequency-division multiplex detailsNeighbor relationValue set

Owner:TELEFON AB LM ERICSSON (PUBL)

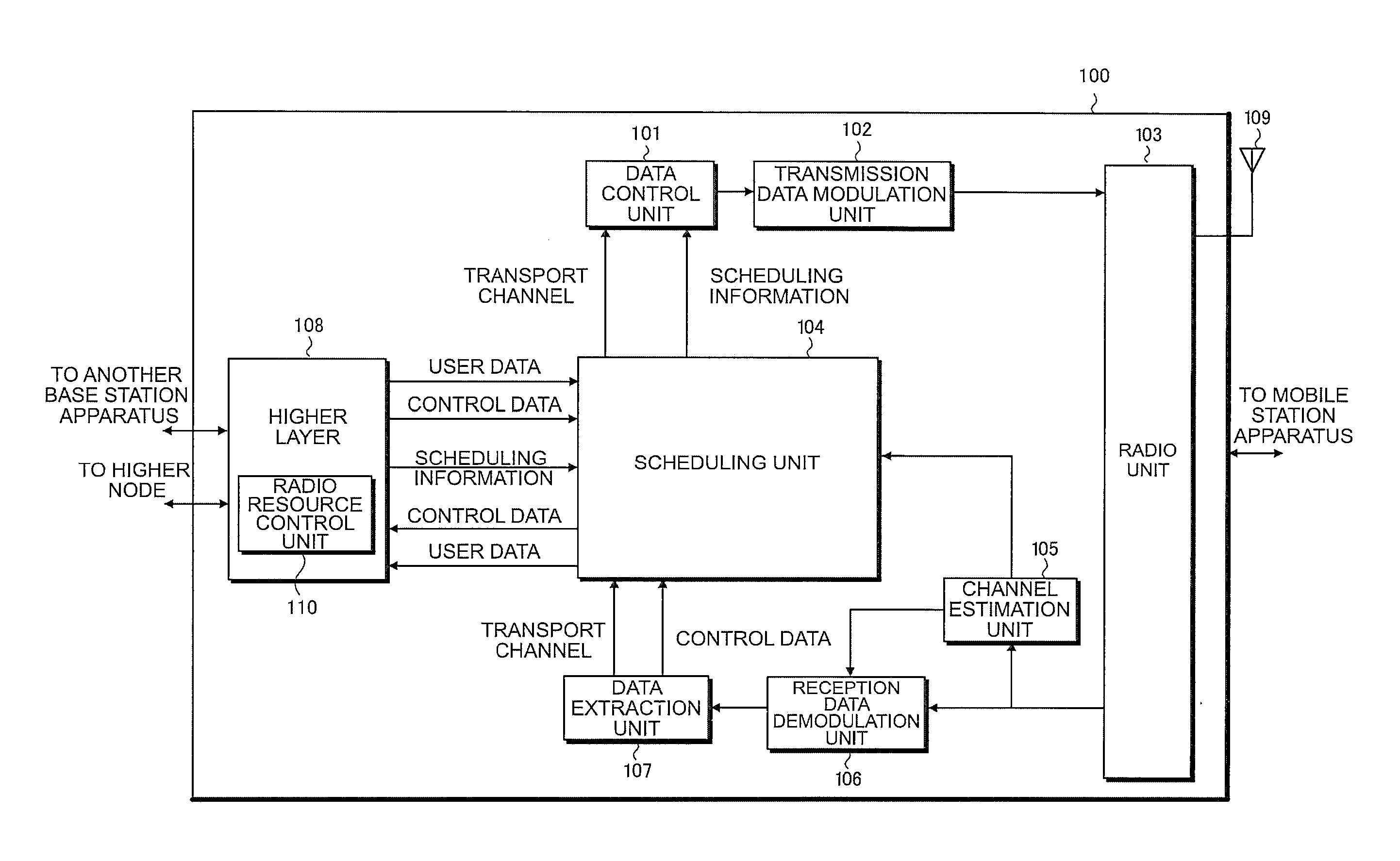

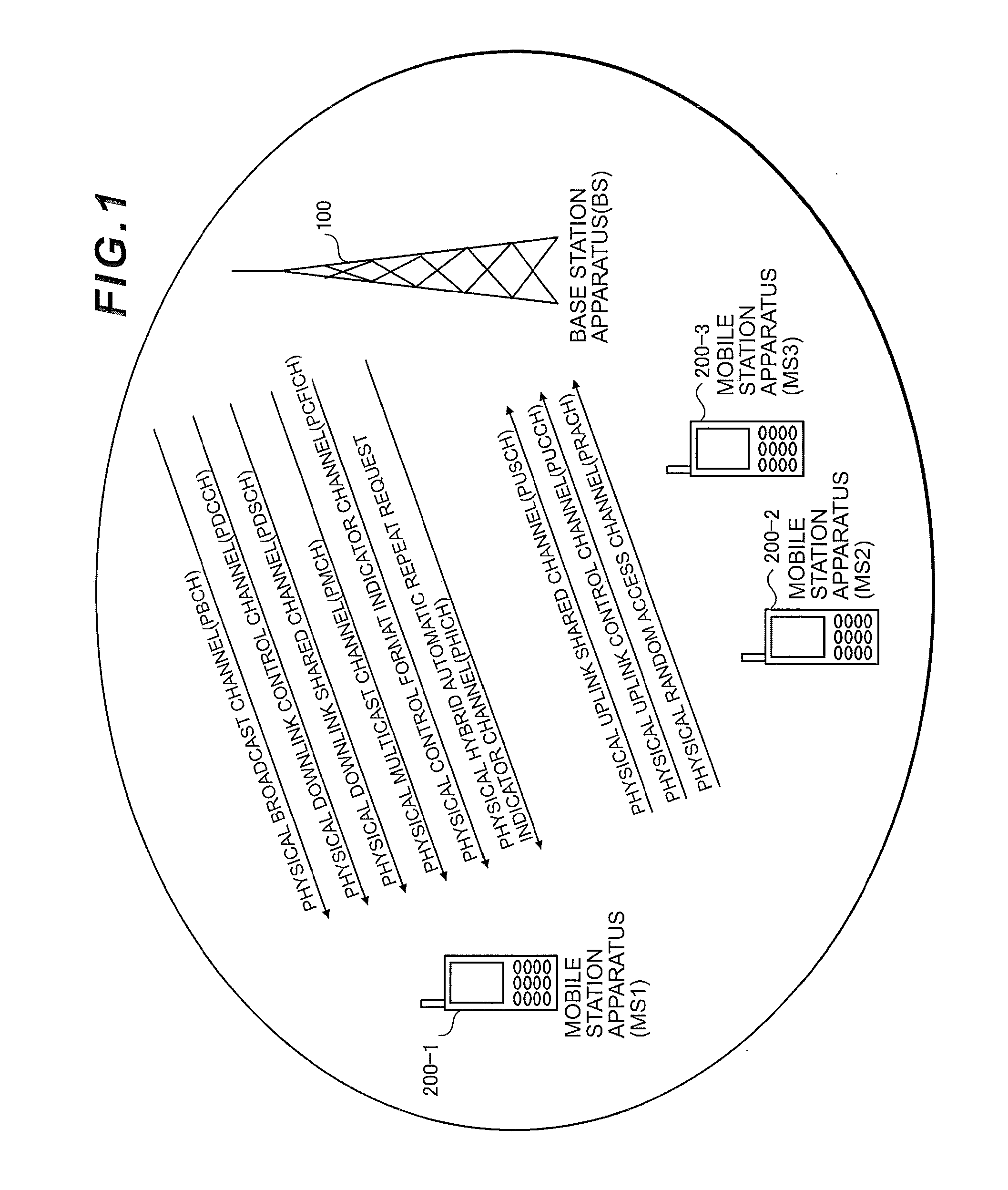

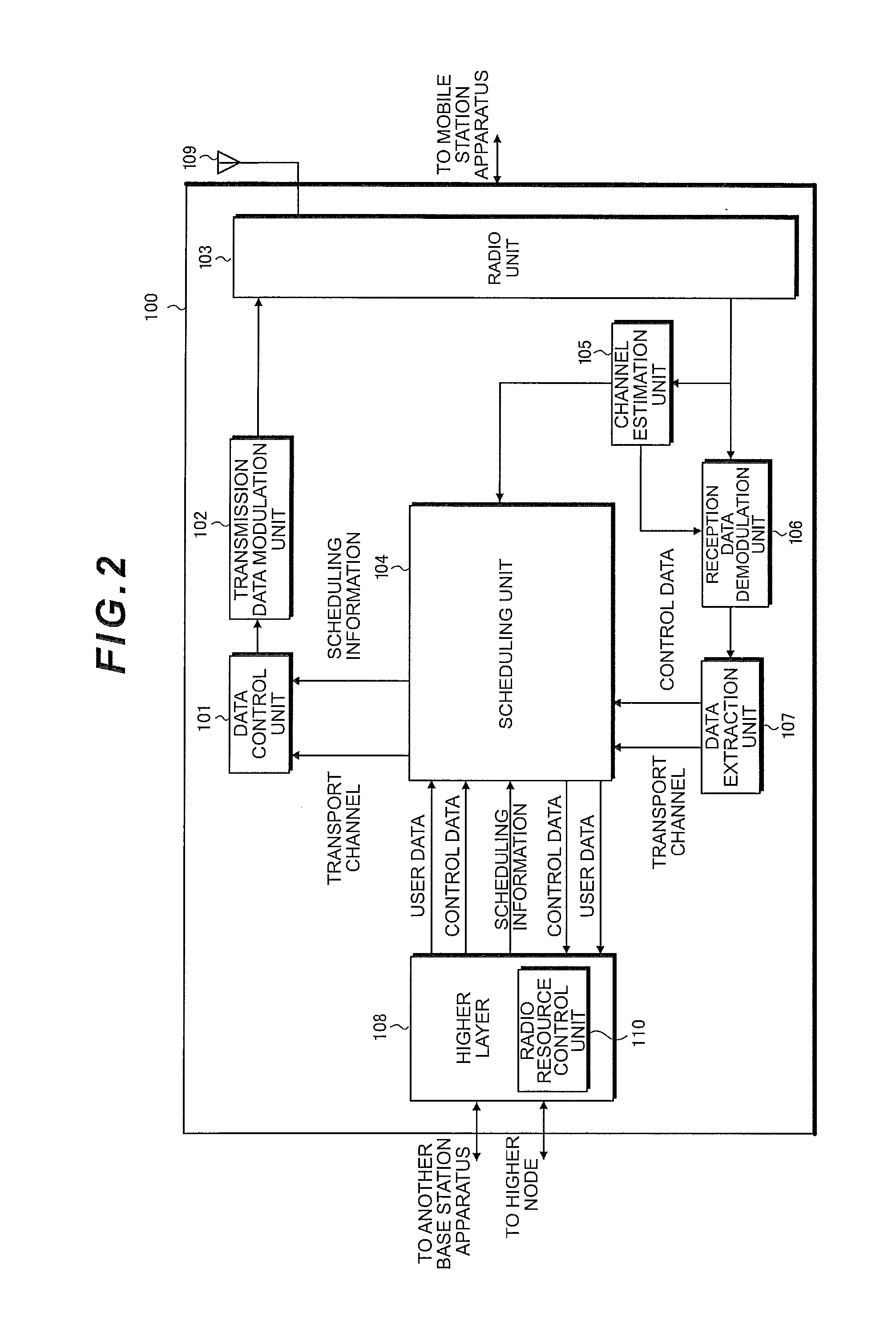

Mobile communication system, base station apparatus, mobile station apparatus and communication method

ActiveUS20120263087A1Guaranteed normal transmissionEfficient receptionPower managementError preventionCarrier signalControl channel

Owner:SHARP KK

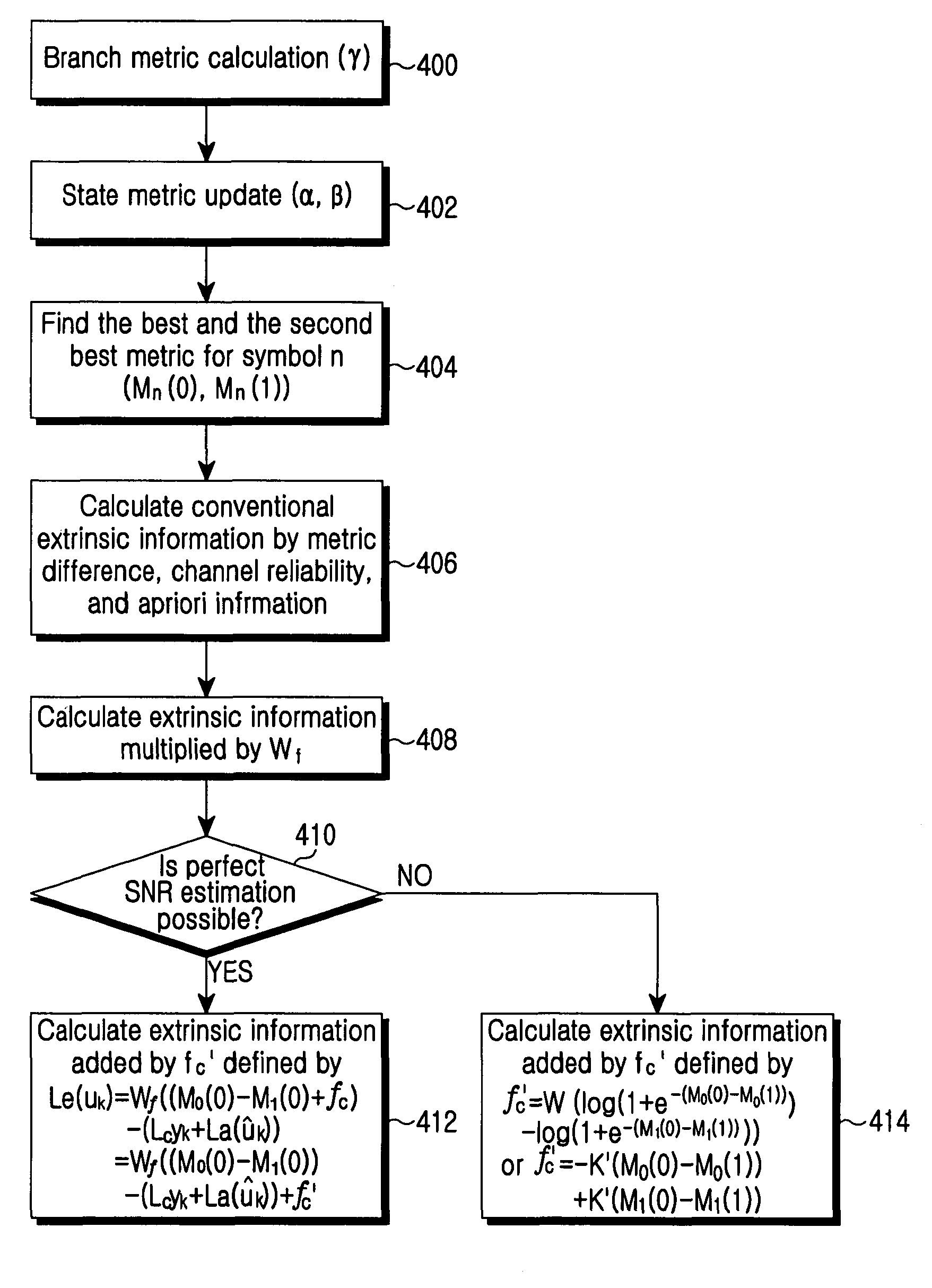

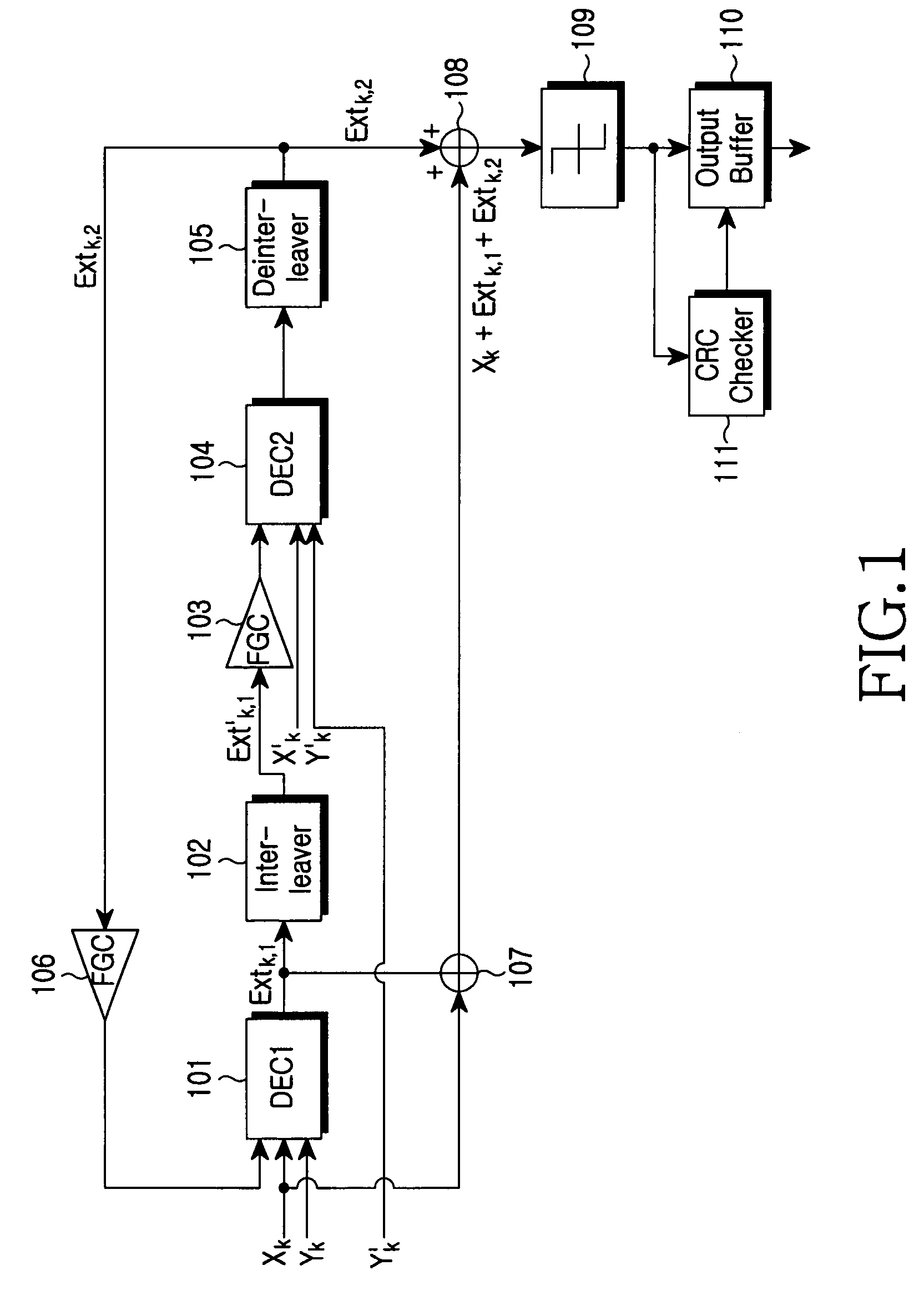

Apparatus and method for reducing Bit Error Rates (BER) and Frame Error Rates (FER) using turbo decoding in a digital communication system

ActiveUS7032156B2Improve performanceLess complexData representation error detection/correctionError preventionCommunications systemBinary multiplier

Owner:SAMSUNG ELECTRONICS CO LTD

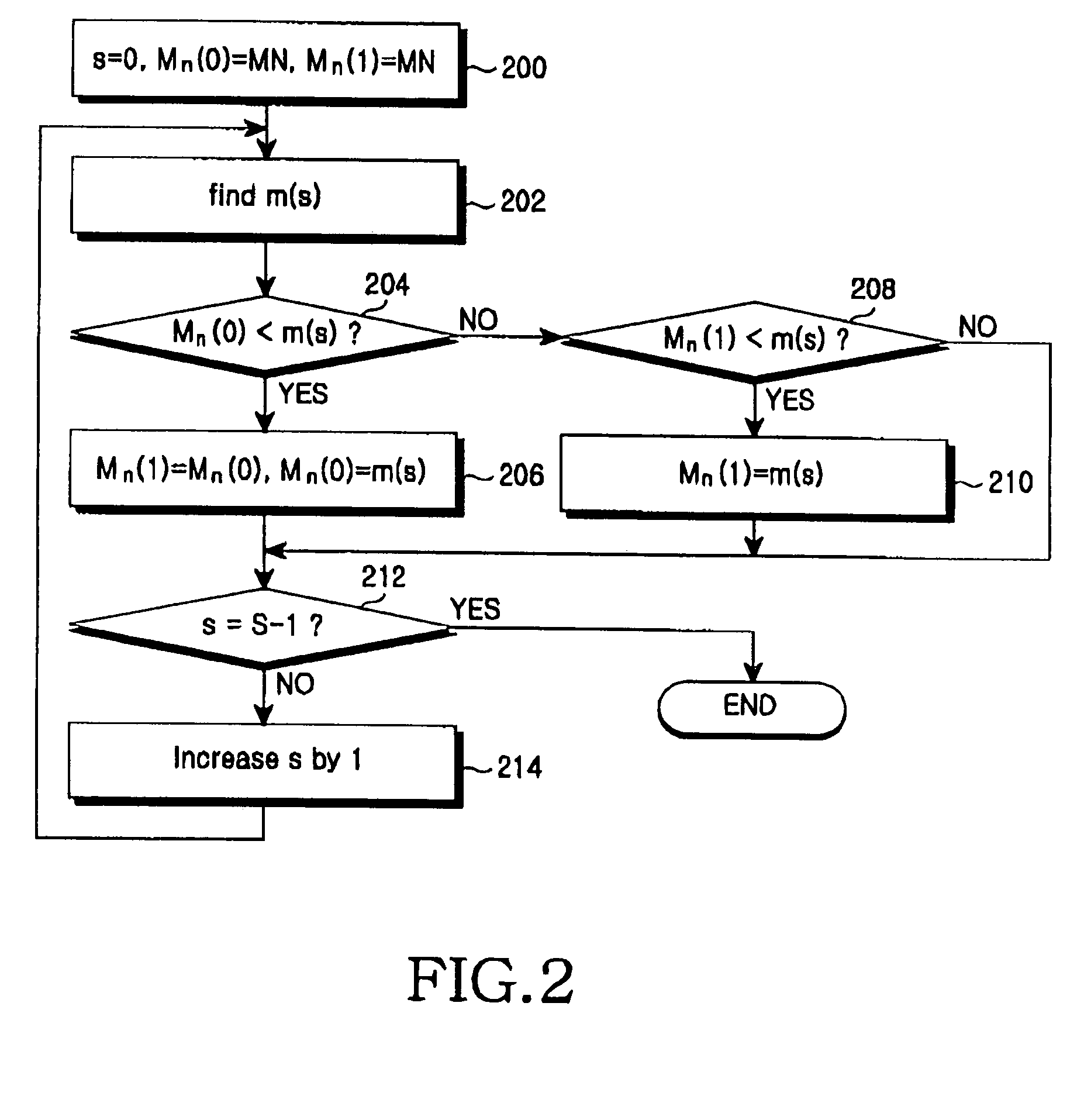

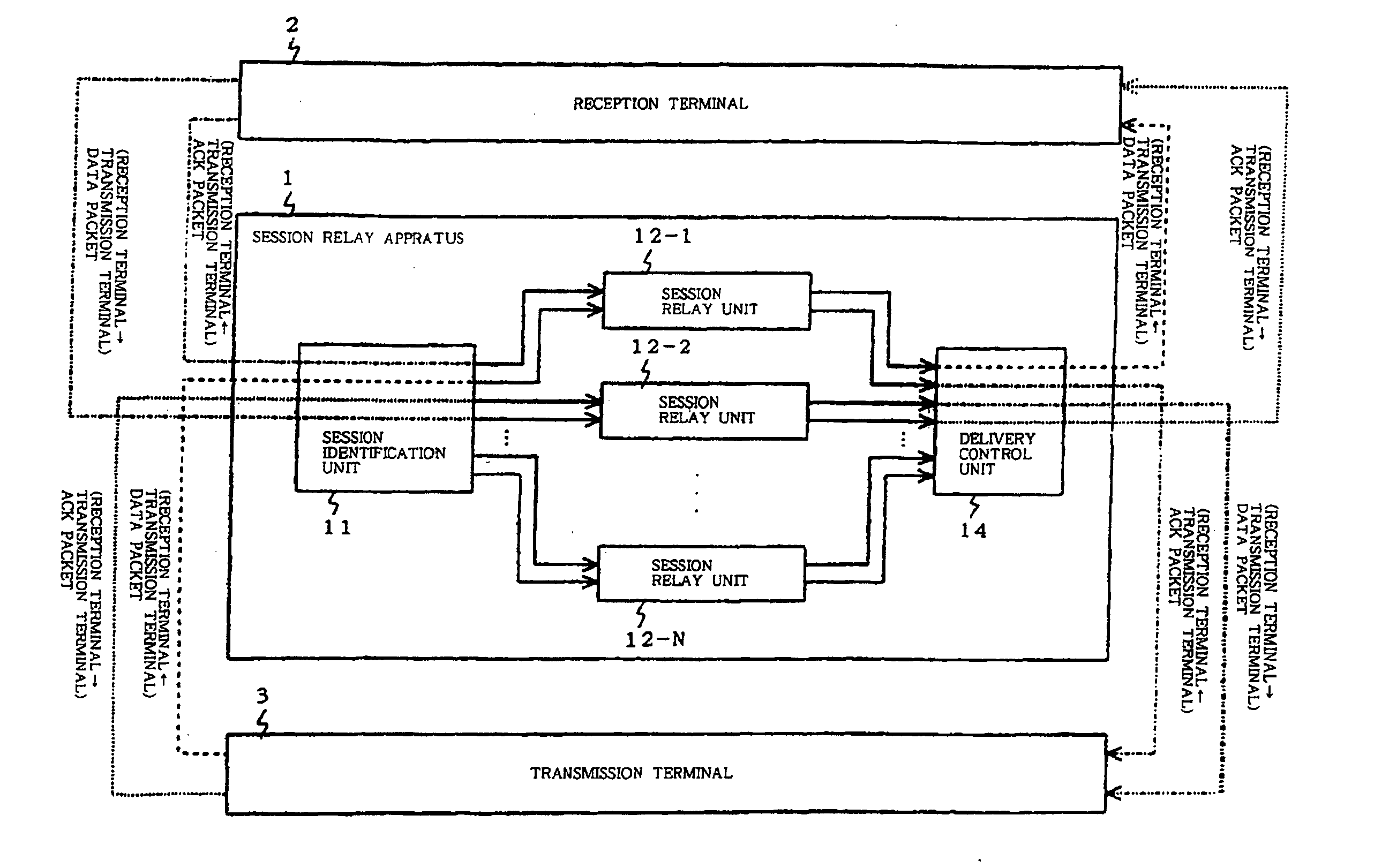

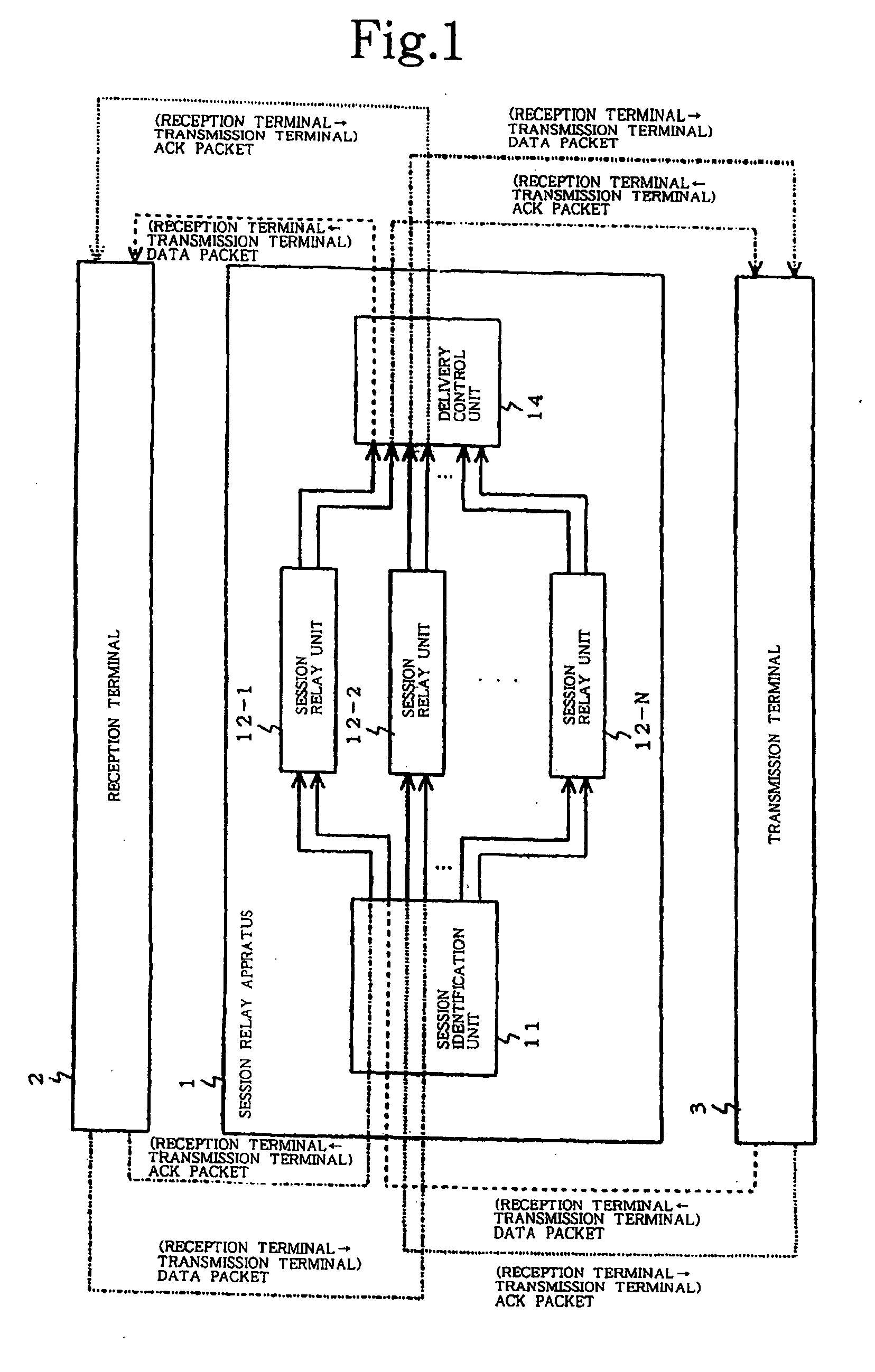

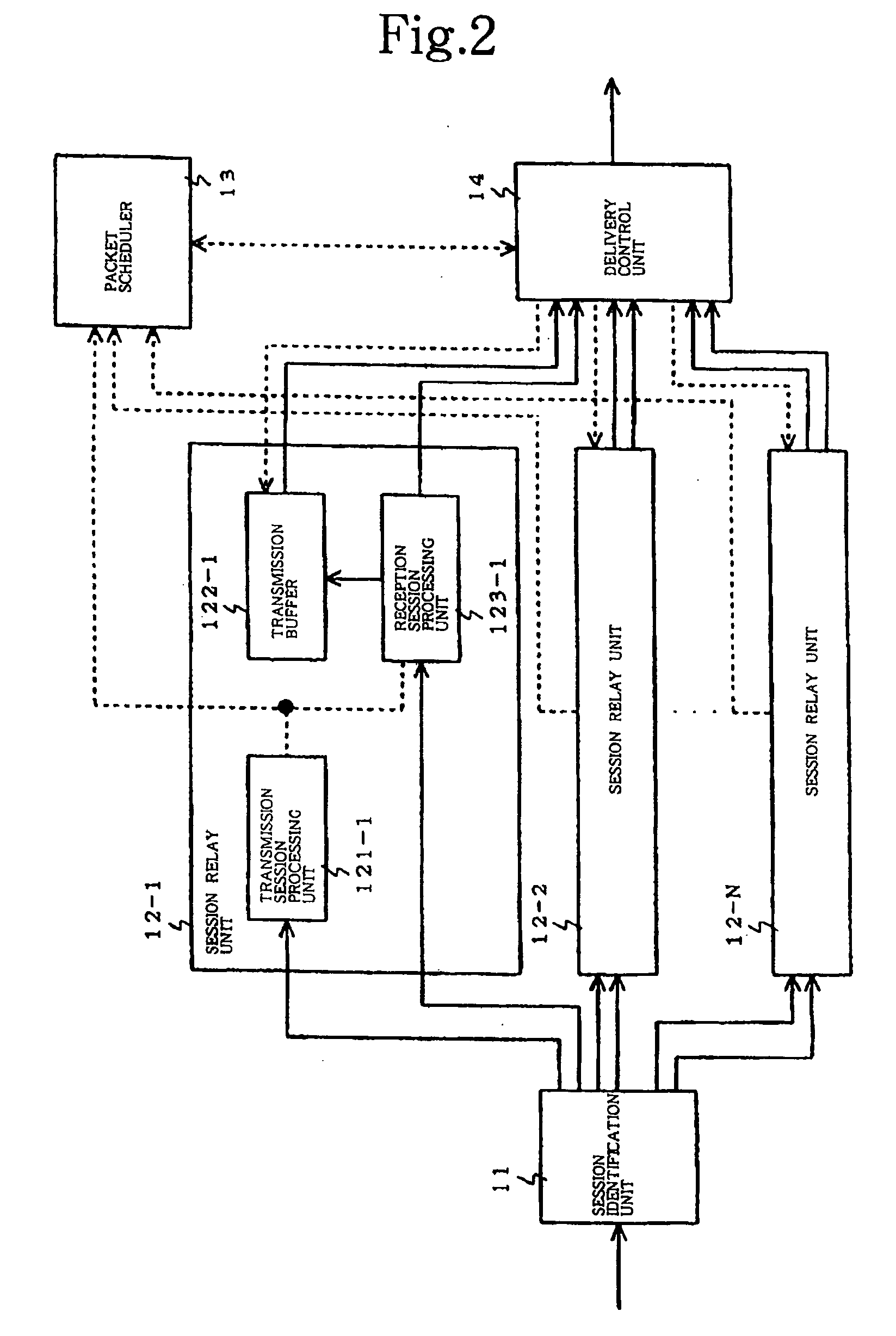

Session relay apparatus and relaying method

InactiveUS20070058534A1Reduce throughputIncrease speedError preventionFrequency-division multiplex detailsComputer networkPacket scheduling

Owner:NEC CORP

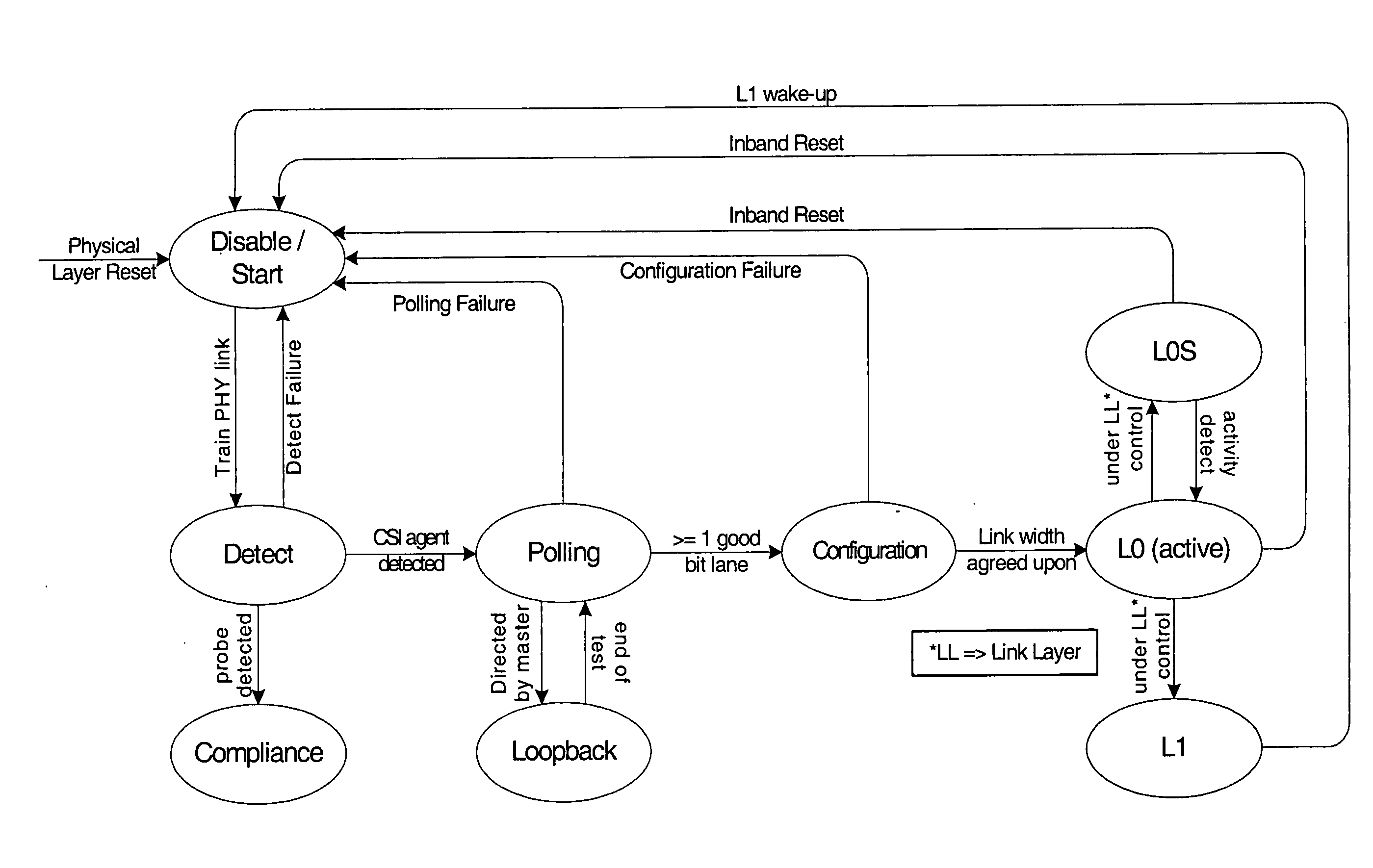

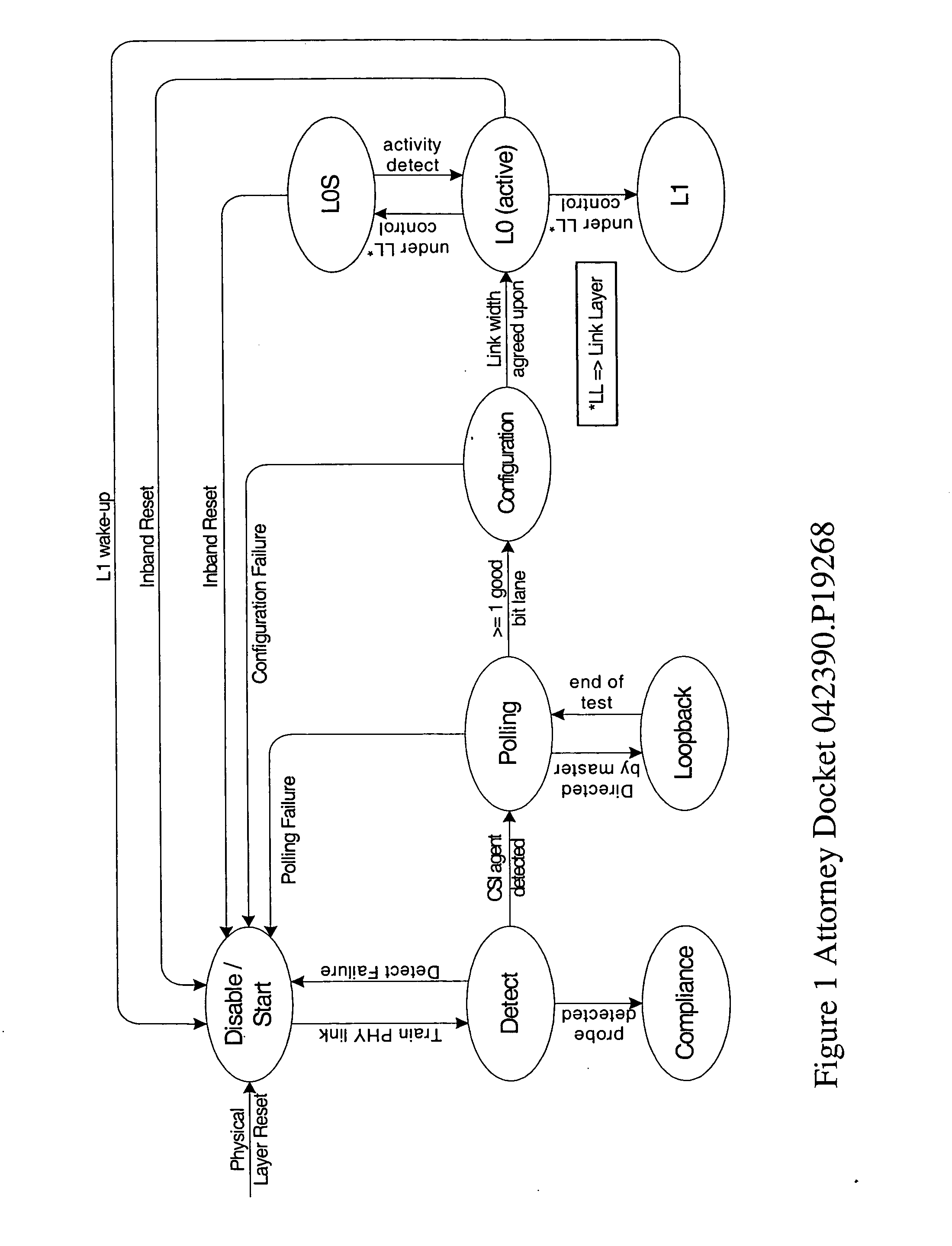

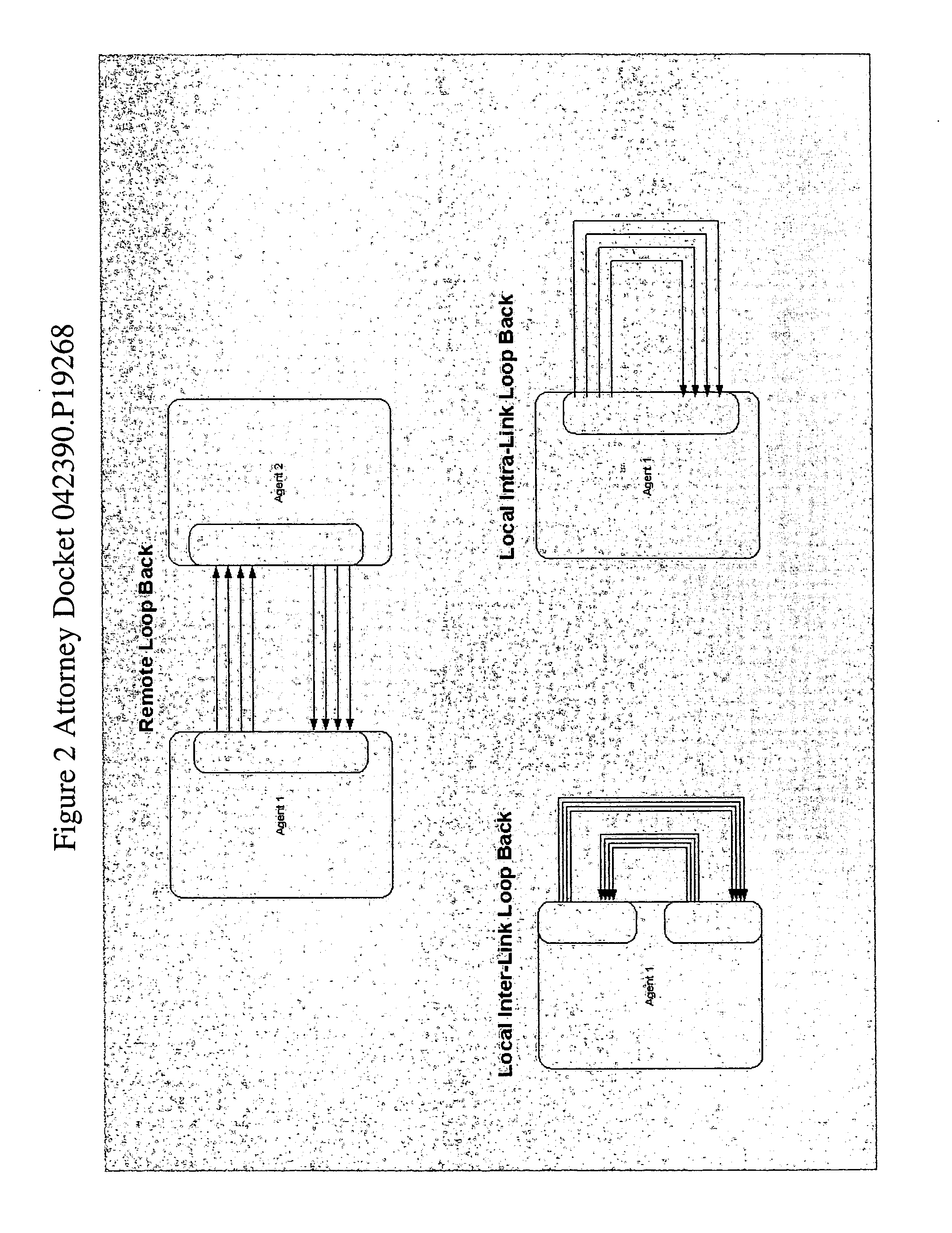

Method, system, and apparatus for loopback parameter exchange

InactiveUS20060018265A1Error preventionFrequency-division multiplex detailsTelecommunications linkLoopback

Owner:INTEL CORP

Transmitting data in a power line network using link quality assessment

InactiveUS6891796B1Transmission/receiving by adding signal to waveError preventionPower line networkQuality assessment

A method for selecting a communication path between two nodes of a powerline network using a link quality assessment algorithm which selects a communication path based on an analysis of historical data regarding the effective throughput of data transmitted between different nodes of the network. The algorithm is also used to select an appropriate gear for such communication based on an analysis of historical data regarding the unit error rates of data transmitted between the two nodes.

Owner:ENIKIA

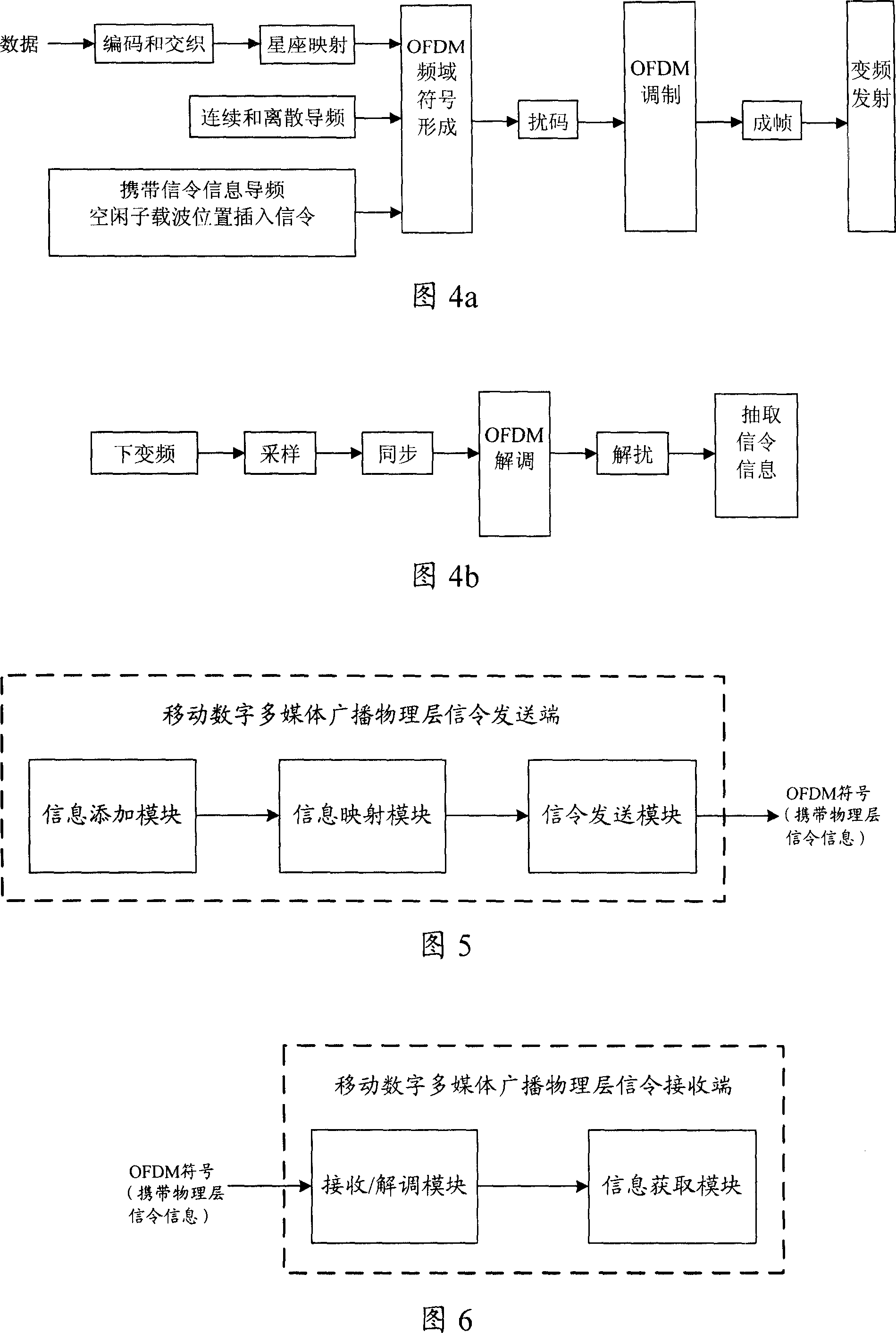

Method and device for transmitting data

InactiveUS20140169161A1Error preventionFrequency-division multiplex detailsResource utilizationNetwork packet

Owner:HUAWEI TECH CO LTD

Method for transmitting and storing downlink data, base station and terminal

ActiveCN105337684AReliable decodingImprove accuracyError preventionNetwork data managementCoding blockReal-time computing

The invention relates to the technical field of communication, and discloses a method for transmitting and storing downlink data, a base station and a terminal. In the scheme, when the base station transmits the downlink data at each time, a bit selection manner adopted by the base station enables that the length and the start point of a sequence expected to receive in initial transmission (or repeat transmission) of the same code block by a terminal in any type are same to the length and the start point of a sequence to be sent by the same code block determined by a sending end, such that the terminal decodes reliably; if decoding is failed, the start point of the sequence in the initial transmission (or repeat transmission) of the same code block stored by the terminal at each time is the same to the start point of the sequence to be sent in the initial transmission (or repeat transmission) of the same code block determined by the sending end; the disadvantage that decoding cannot be carried out accurately due to the fact that storage cannot be carried out accurately when the terminal stores a retransmission code block of the same code block at each time can be avoided; and thus, the decoding accuracy of the terminal is increased.

Owner:HUAWEI TECH CO LTD

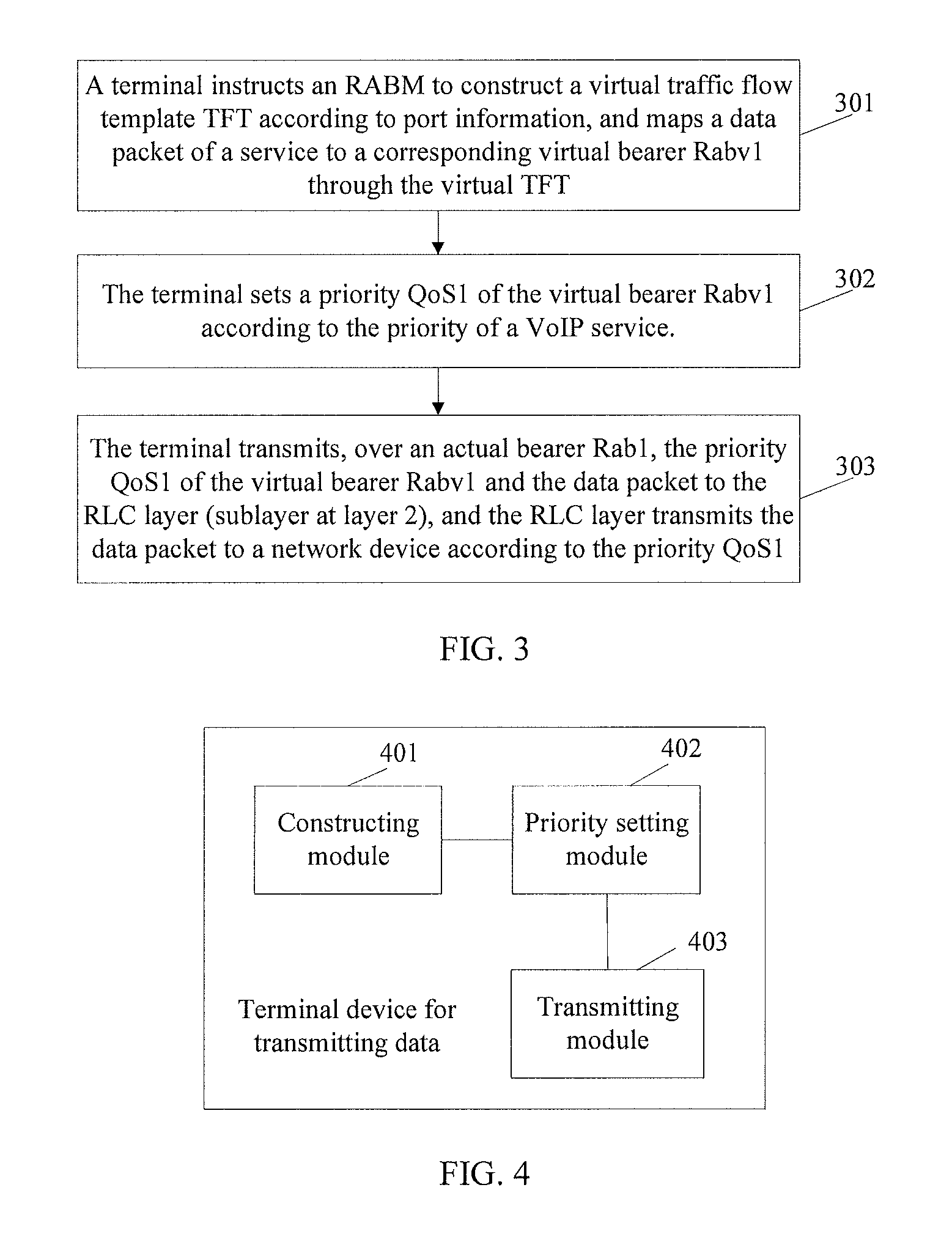

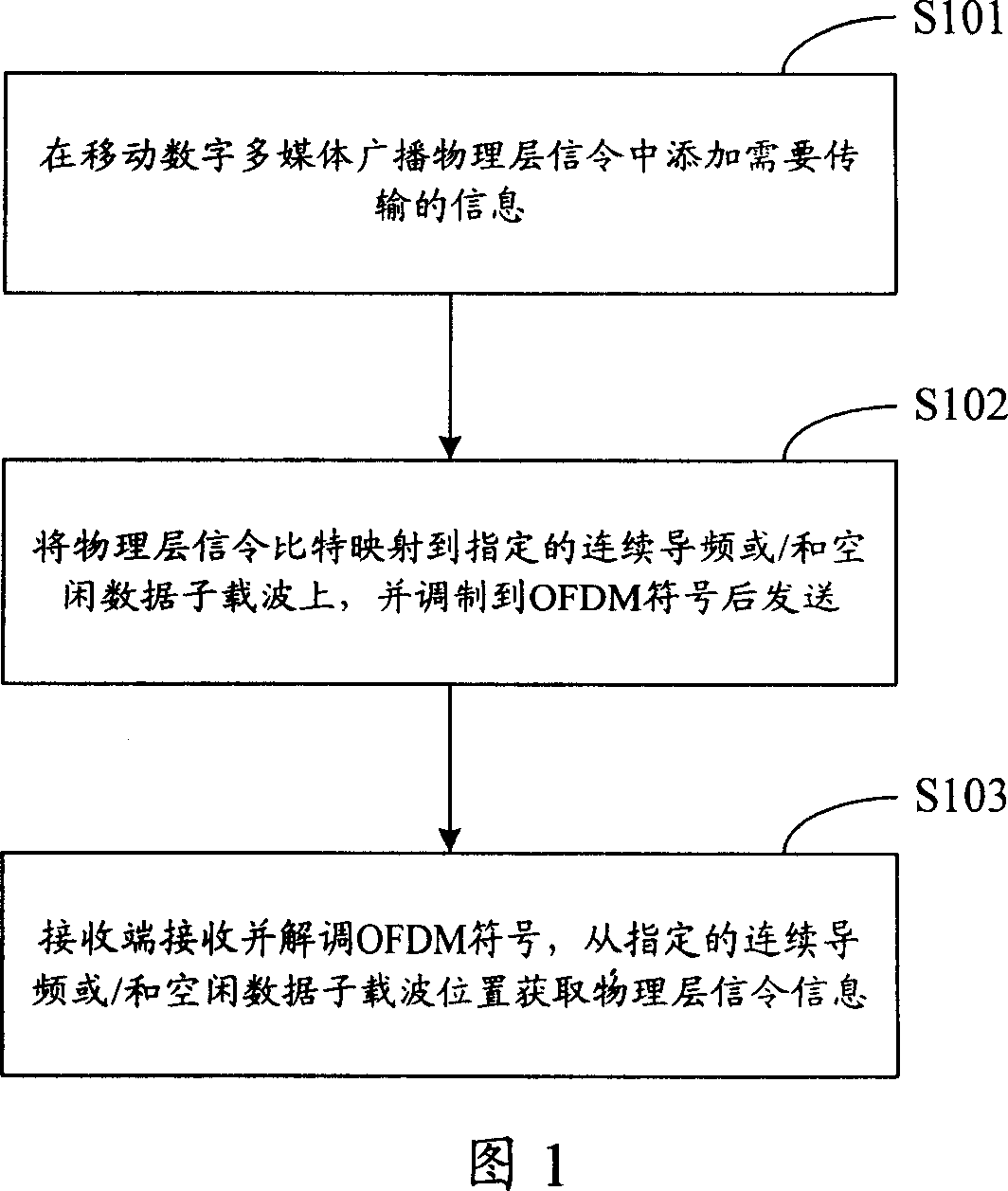

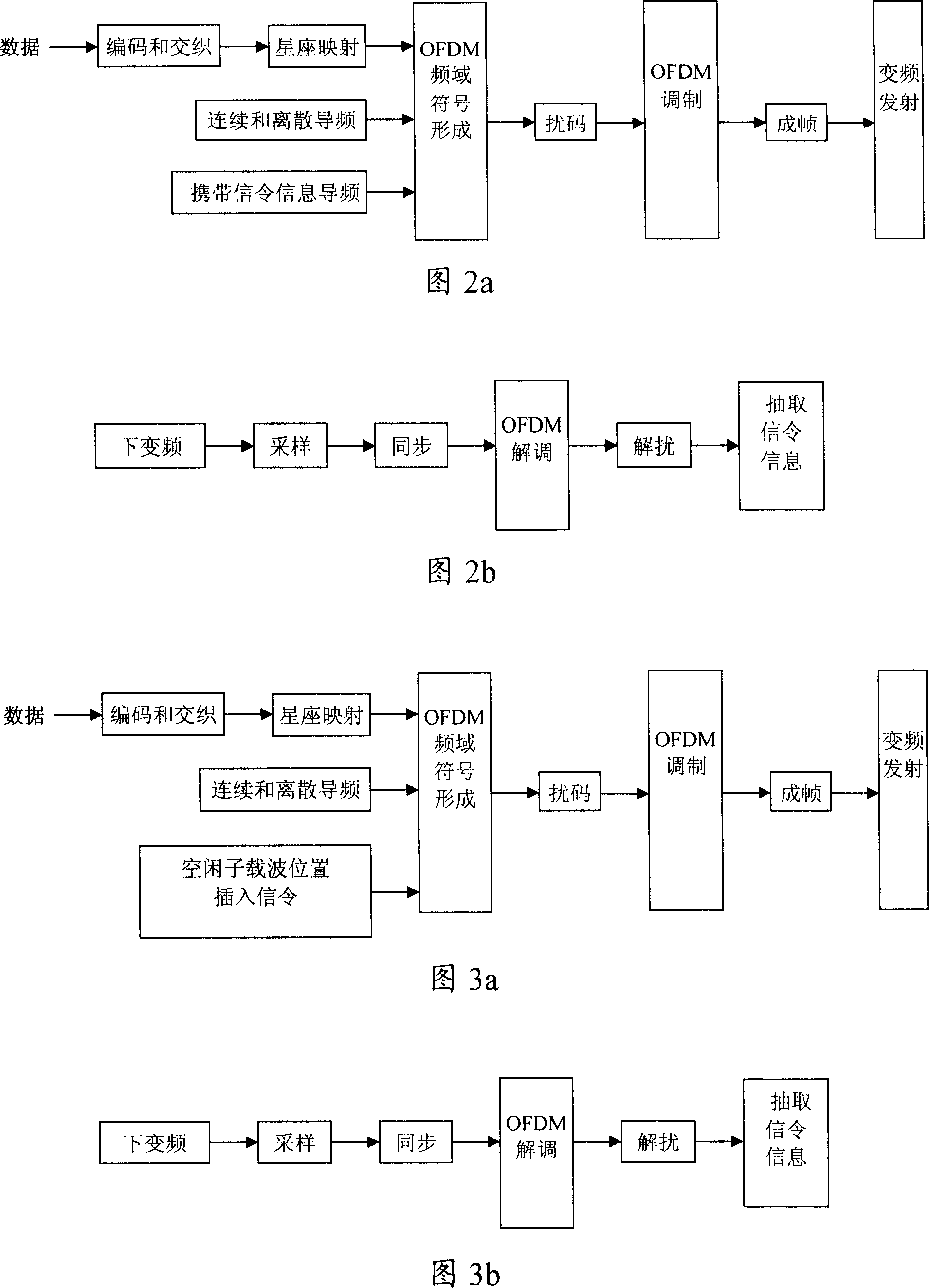

Information transmission and receiving method and end of the mobile digital multimedia broadcast physical layer signaling

InactiveCN101018224AImprove transmission efficiencyFlexible transmissionTelevision system detailsBroadcast with distributionInformation transmissionTelecommunications

Owner:이노피데이인코포레이티드

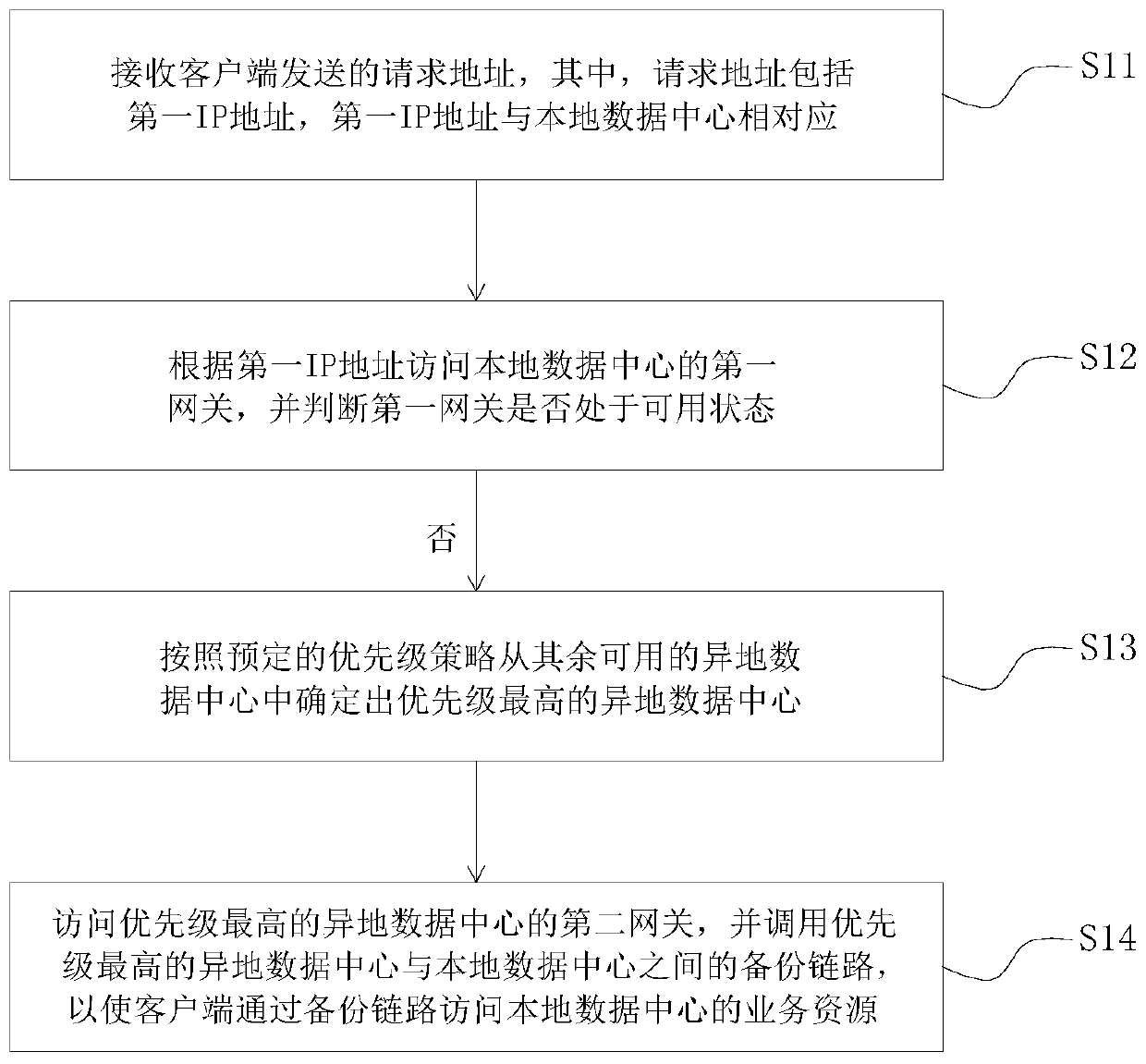

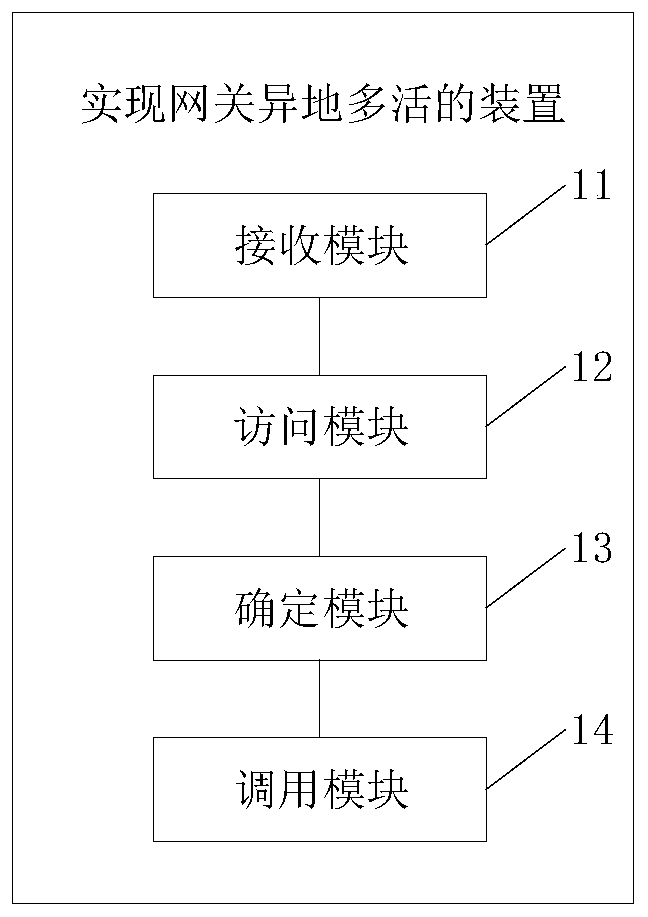

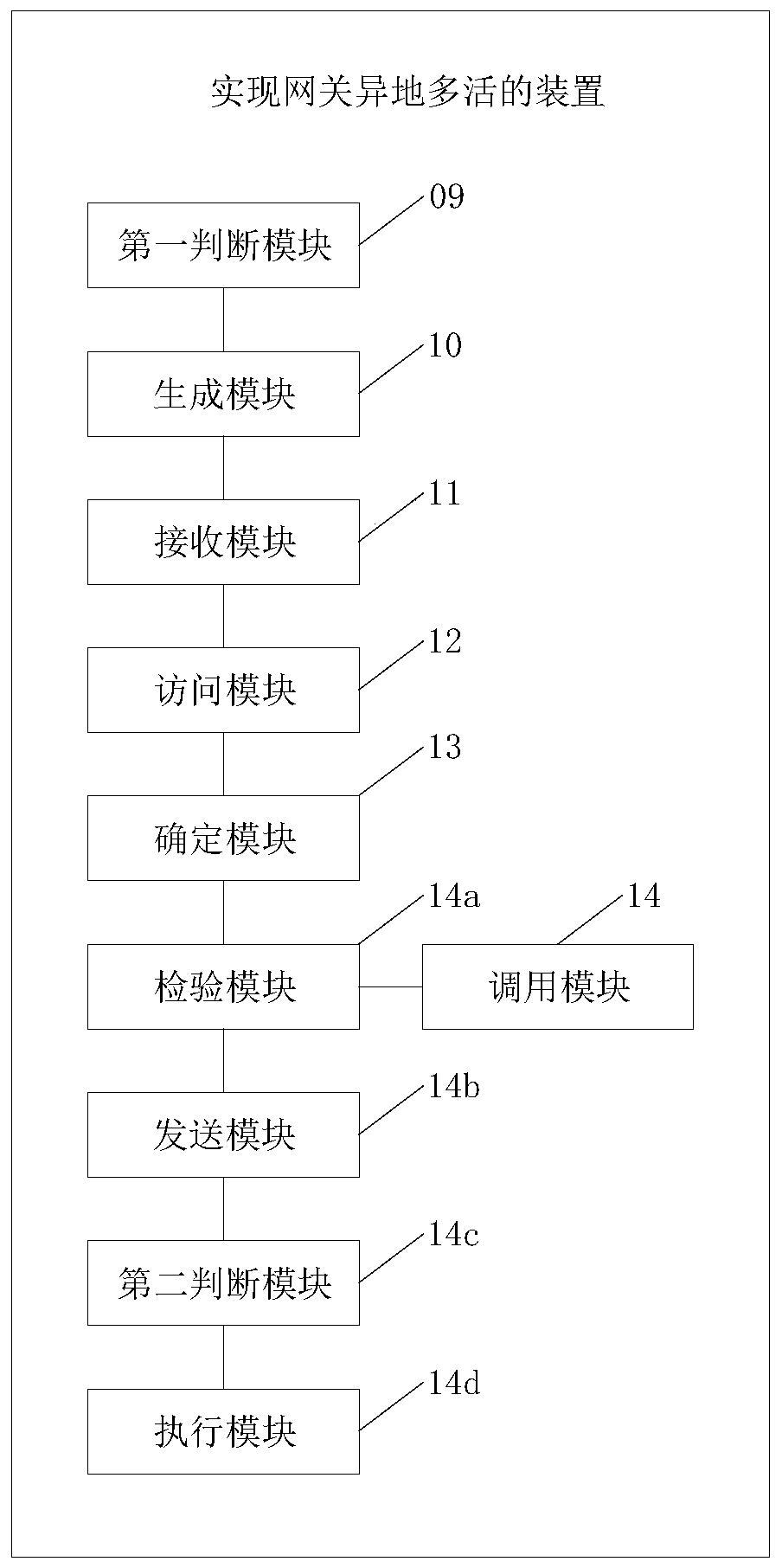

Method and device for realizing gateway remote multi-activity, computer equipment and storage medium

ActiveCN110177007ARealize multiple activities in different placesError preventionUser identity/authority verificationIp addressData center

Owner:PING AN TECH (SHENZHEN) CO LTD

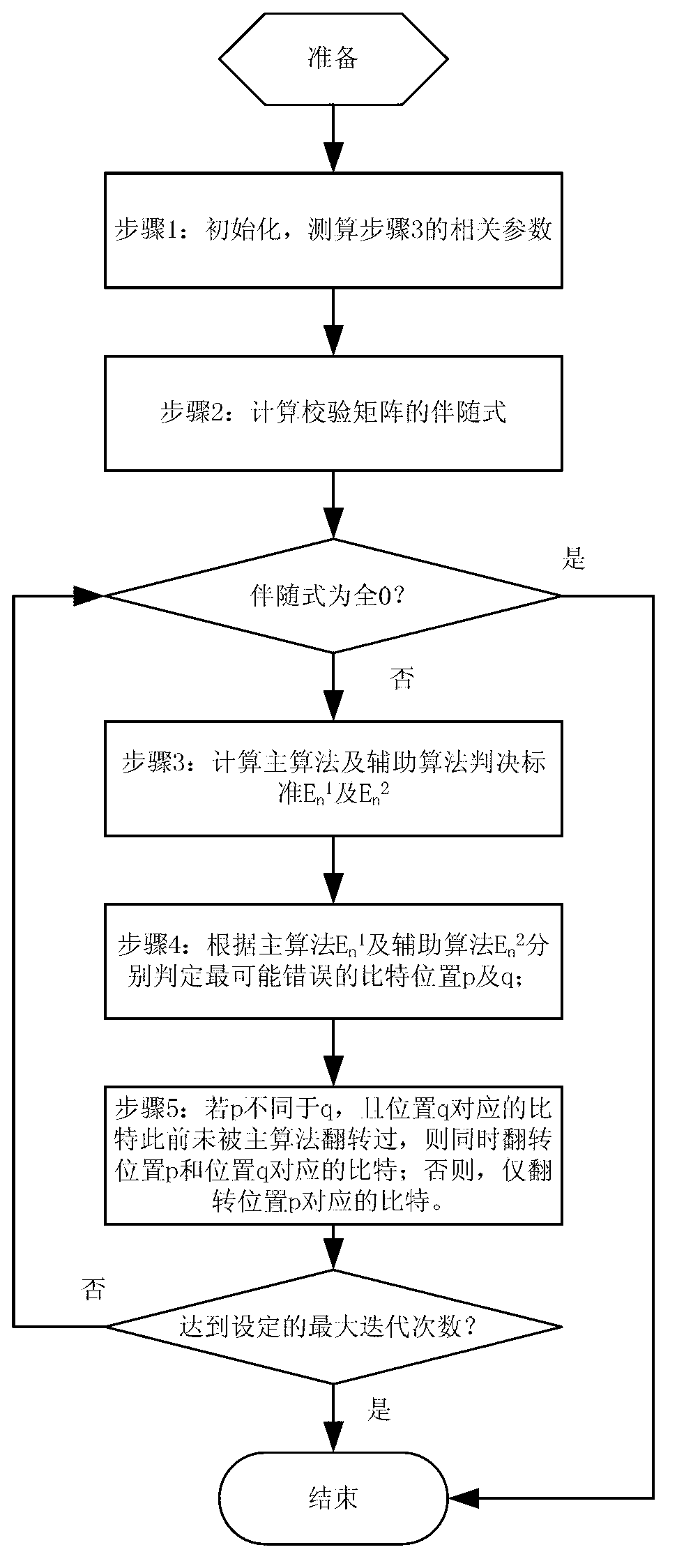

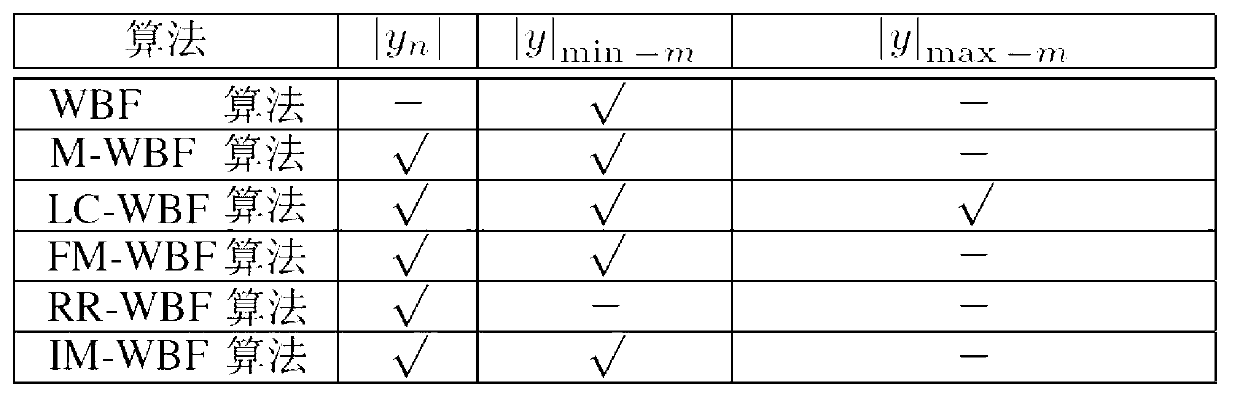

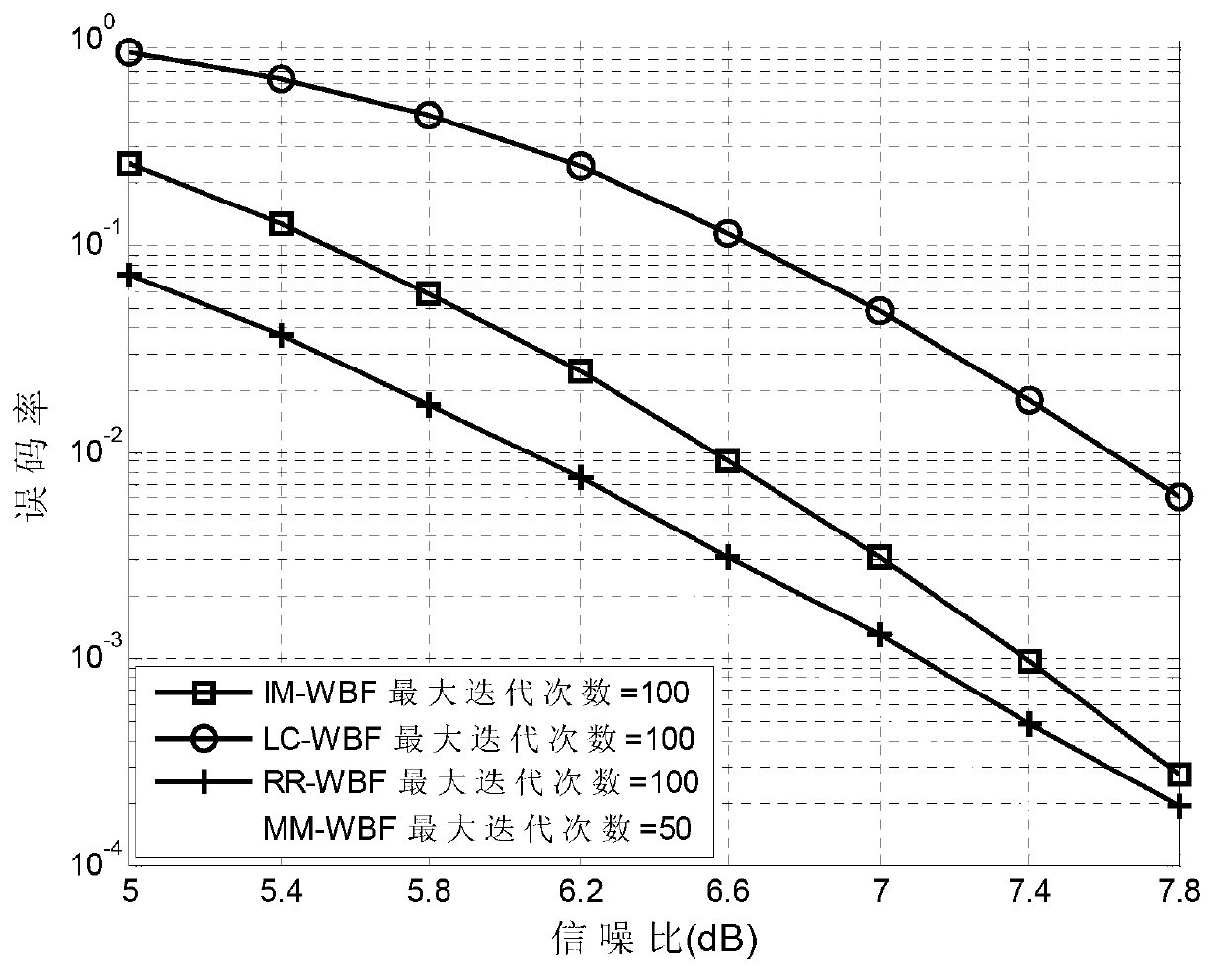

Mixed modified weighted bit-flipping LDPC decoding algorithm

ActiveCN103281090AError preventionError correction/detection using multiple parity bitsRound complexityLdpc decoding

Owner:SOUTH CHINA UNIV OF TECH

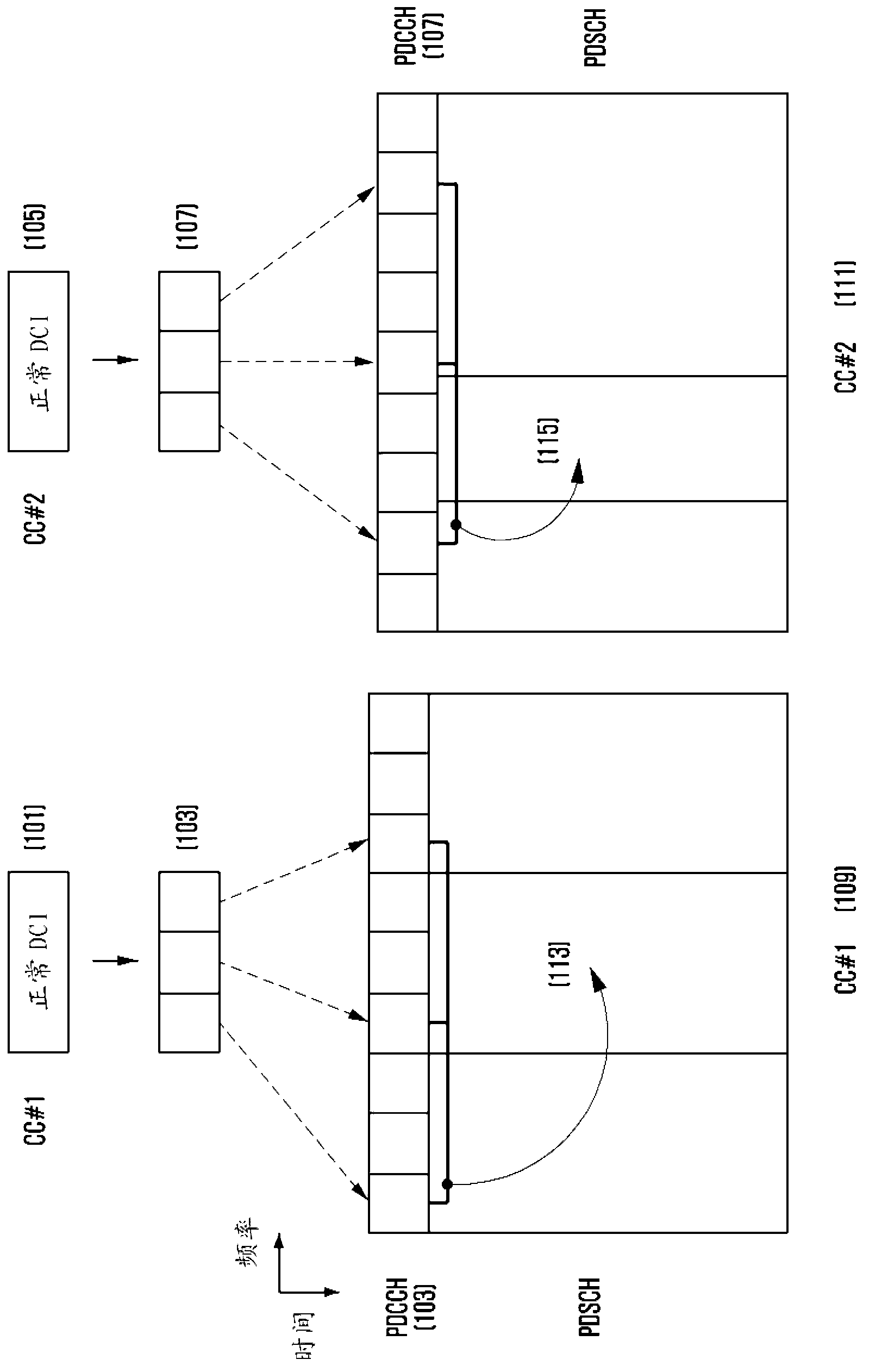

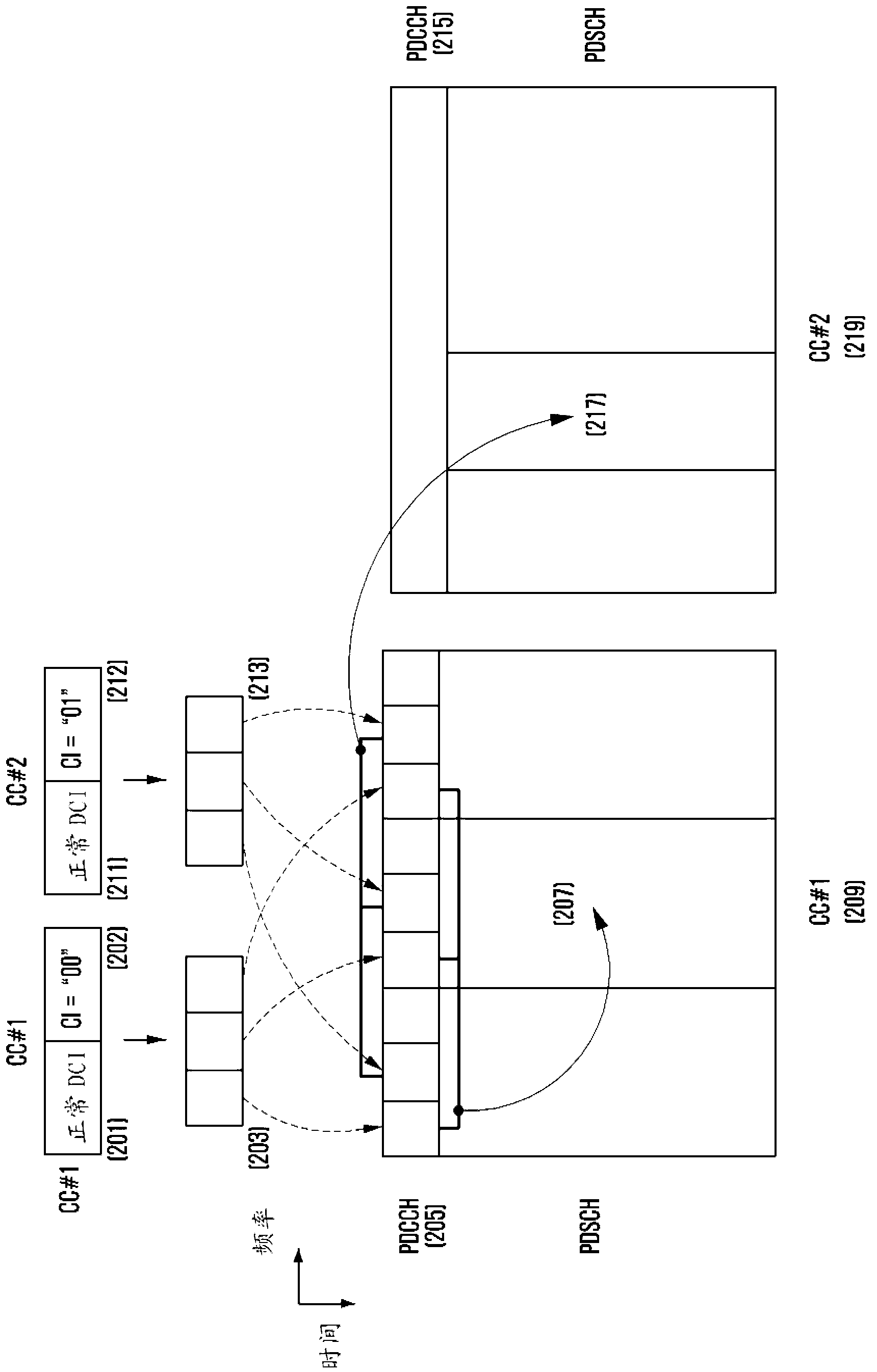

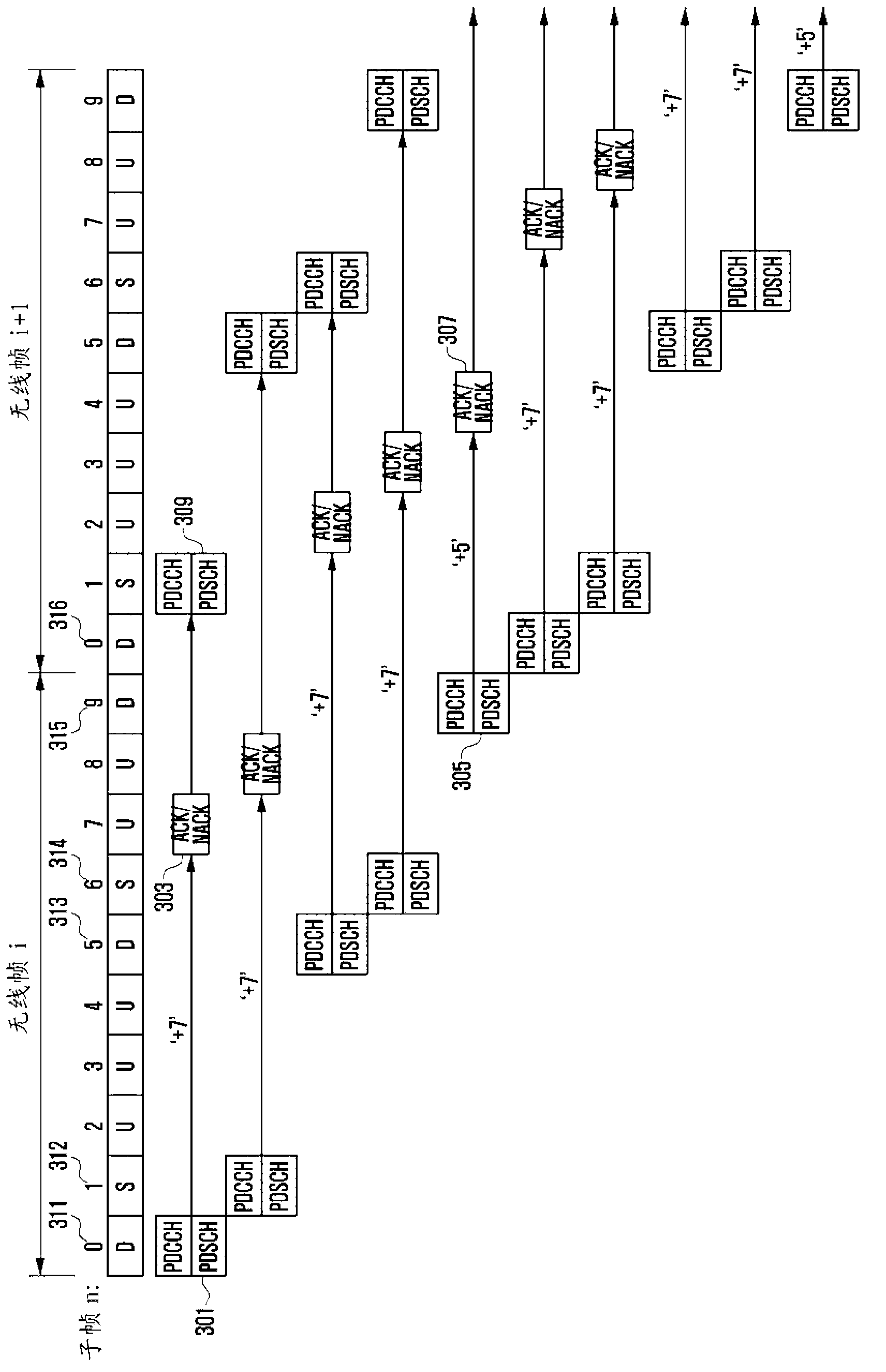

Method and apparatus for defining transceiving timing of a physical channel in a TDD communication system which supports cross-carrier schedulin

ActiveCN102783053AReduce transmission errorsReduce transmission delayError preventionTransmission path divisionCommunications systemCarrier signal

Owner:SAMSUNG ELECTRONICS CO LTD

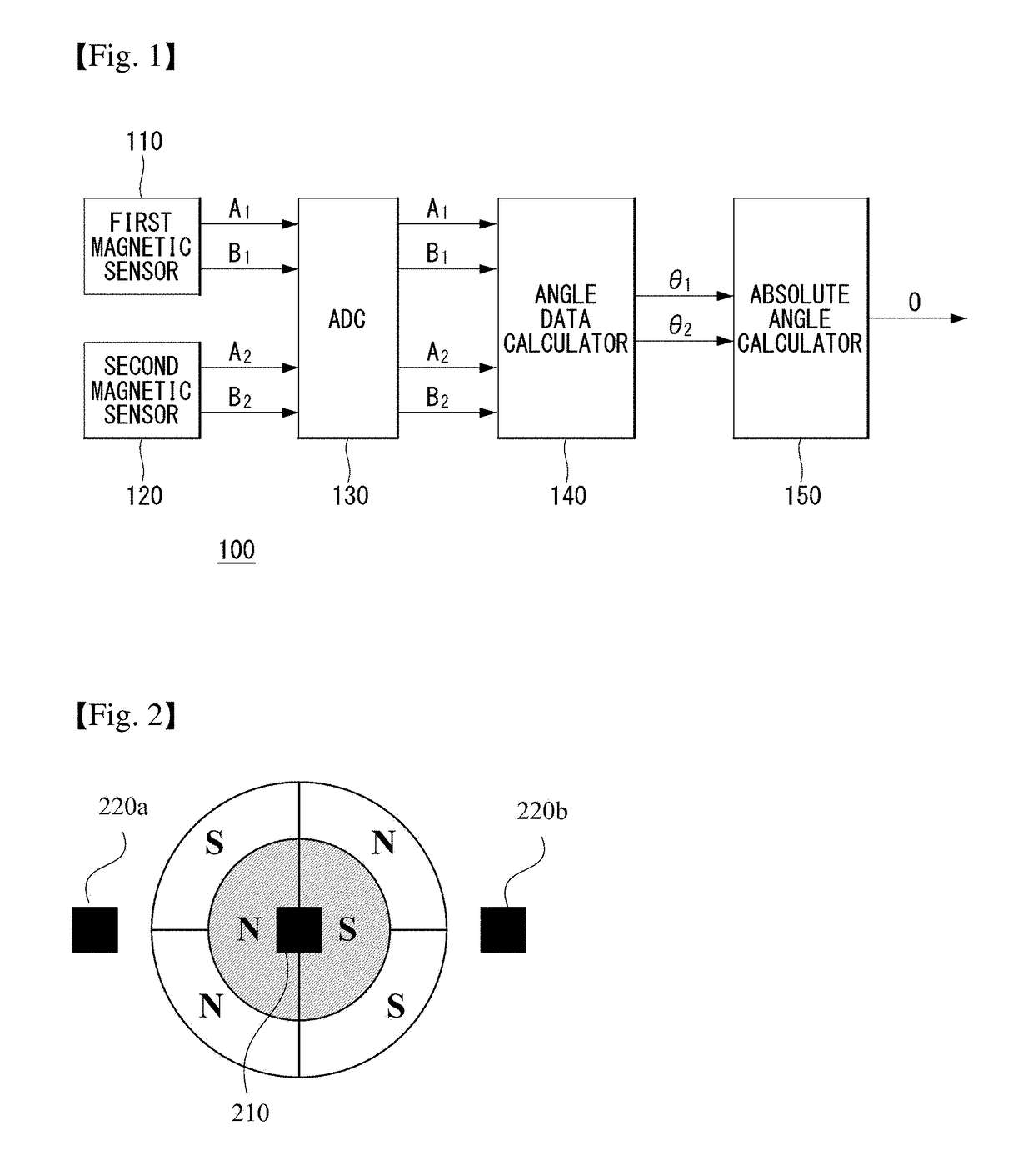

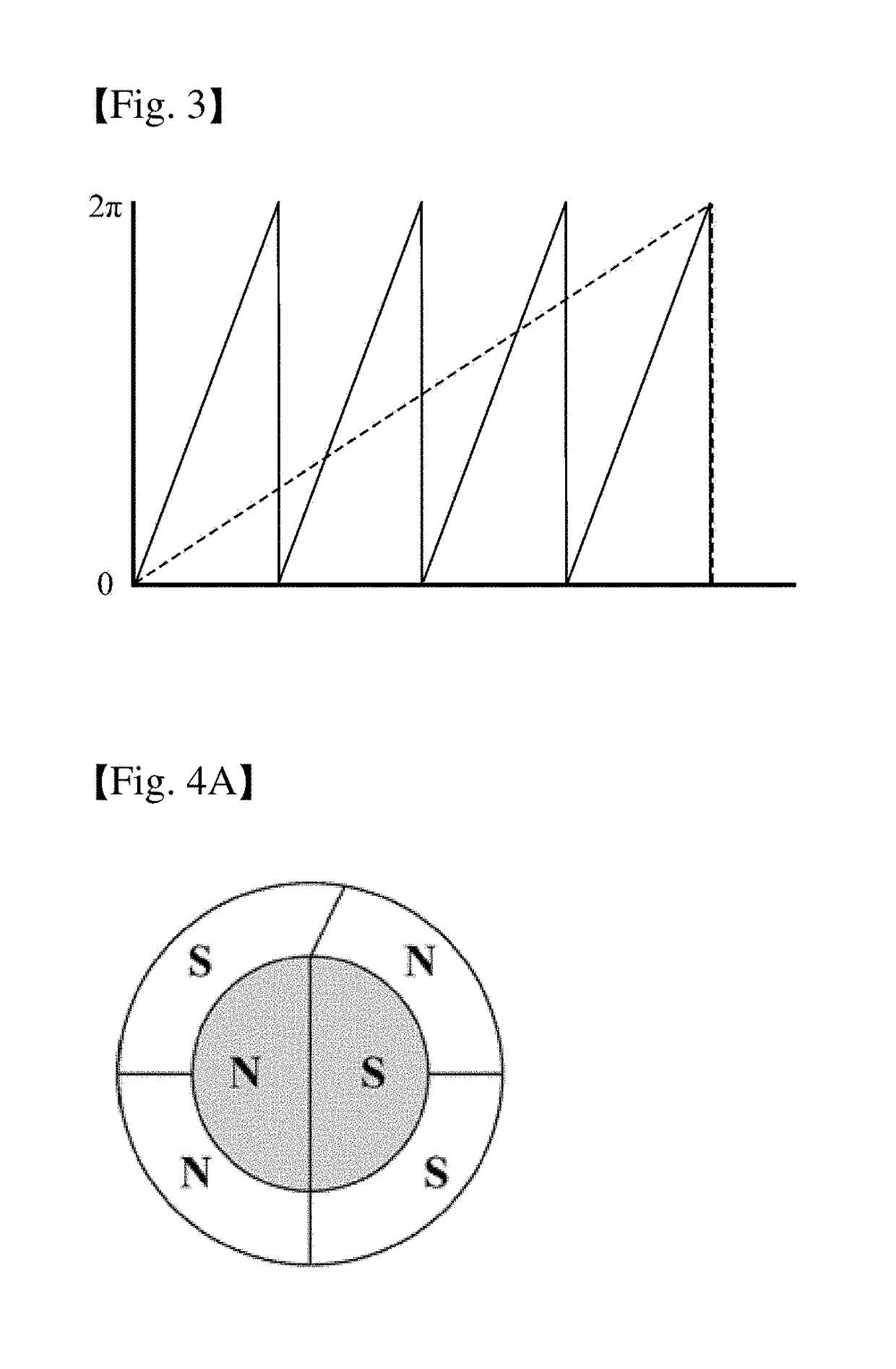

Angle determinating method using encoder signal with noise suppression, adjusting method for output signal of encoder and absolute encoder

ActiveUS20170322014A1Well formedError preventionUsing electrical meansNoise suppressionRotation cycle

Owner:FASTECH

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap