Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4 results about "Breakdown voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The breakdown voltage of an insulator is the minimum voltage that causes a portion of an insulator to become electrically conductive. For diodes, the breakdown voltage is the minimum reverse voltage that makes the diode conduct appreciably in reverse. Some devices (such as TRIACs) also have a forward breakdown voltage.

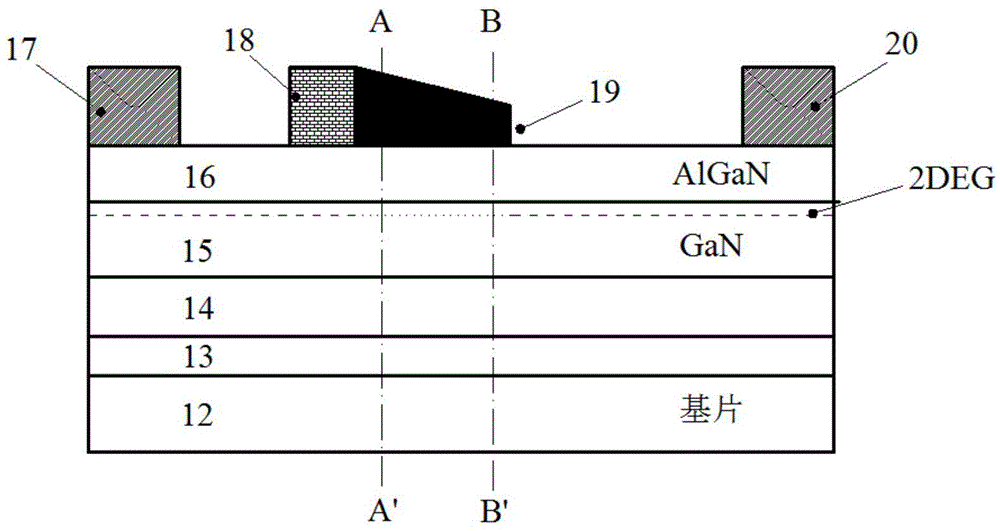

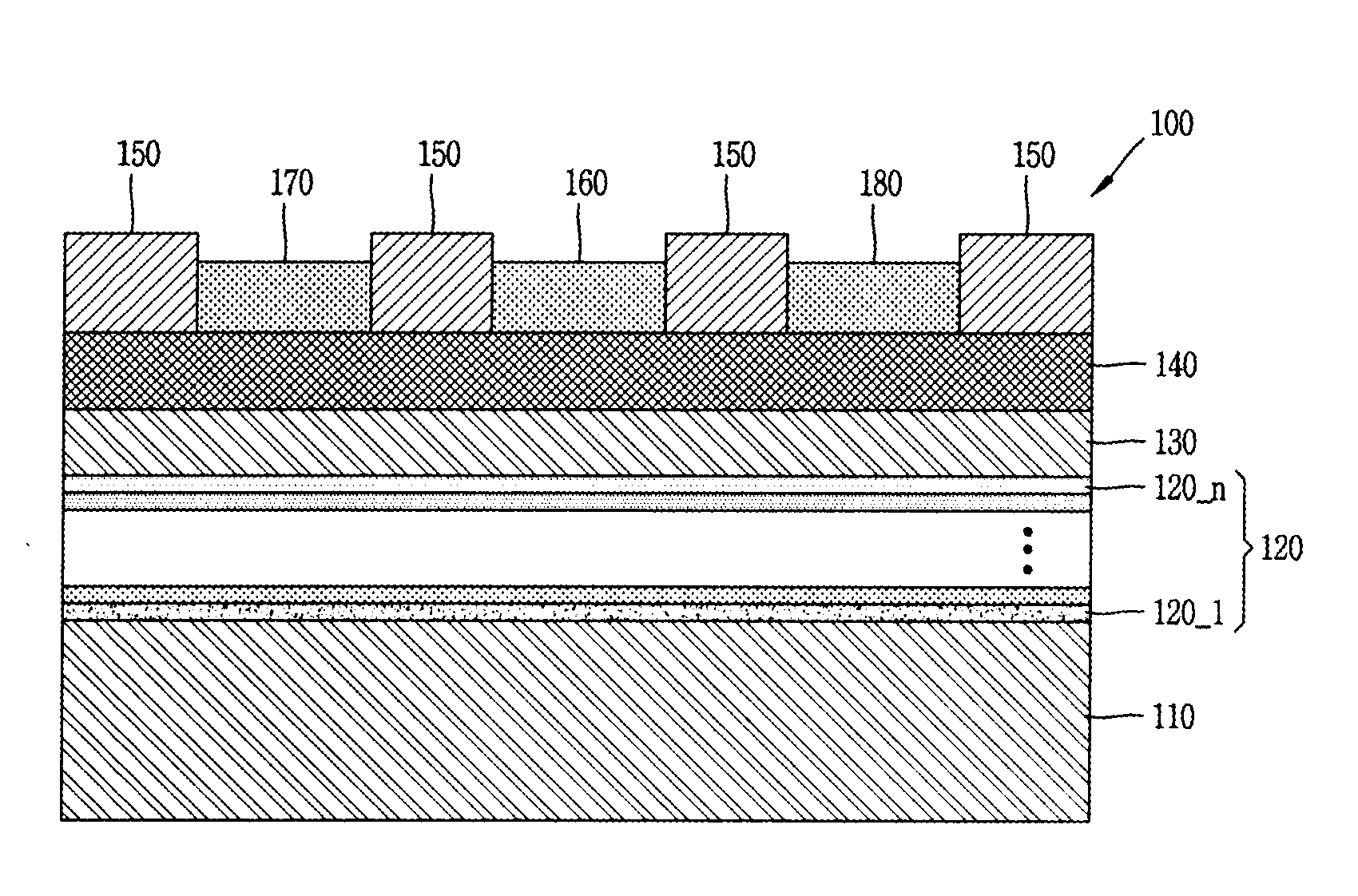

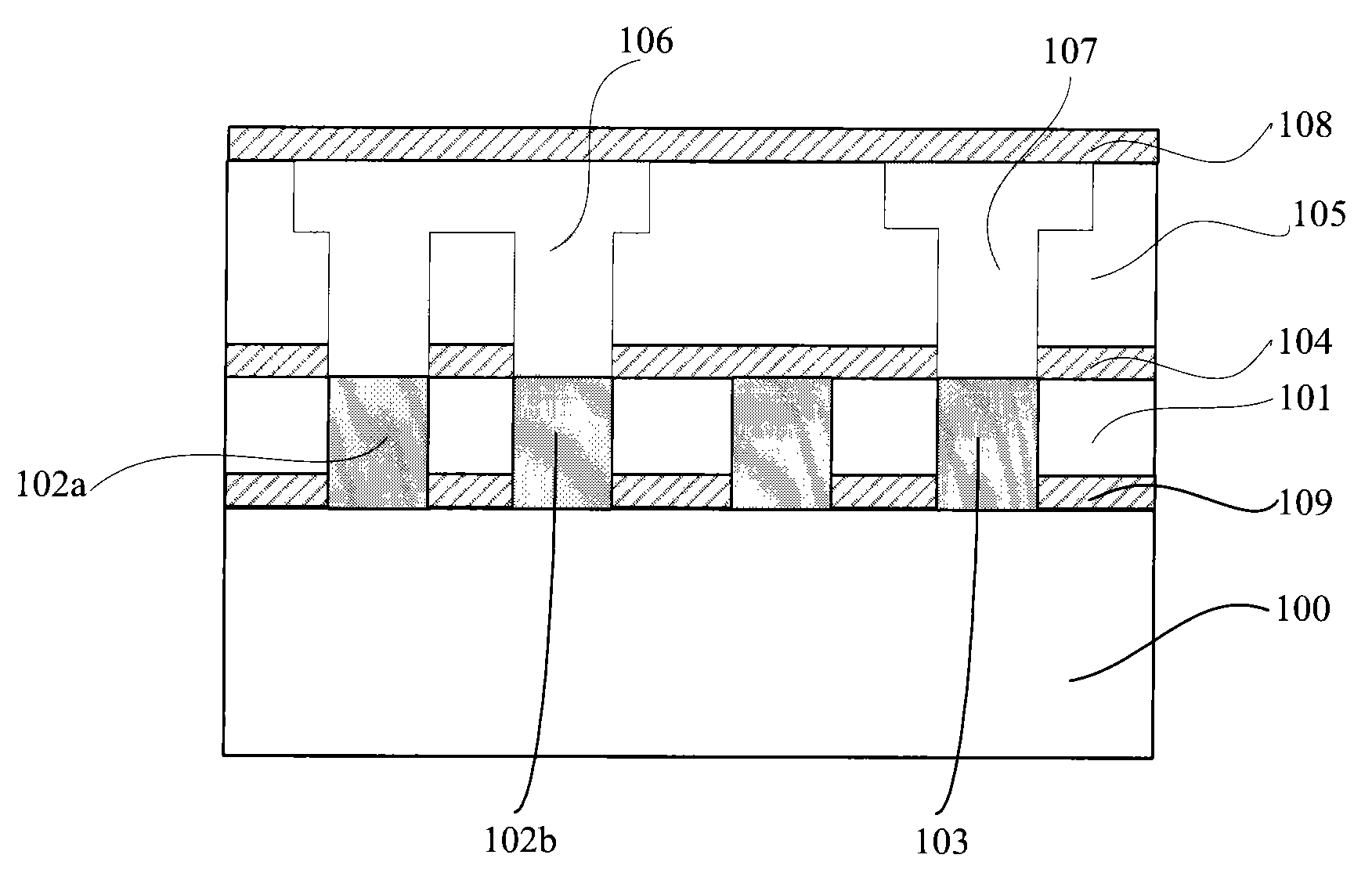

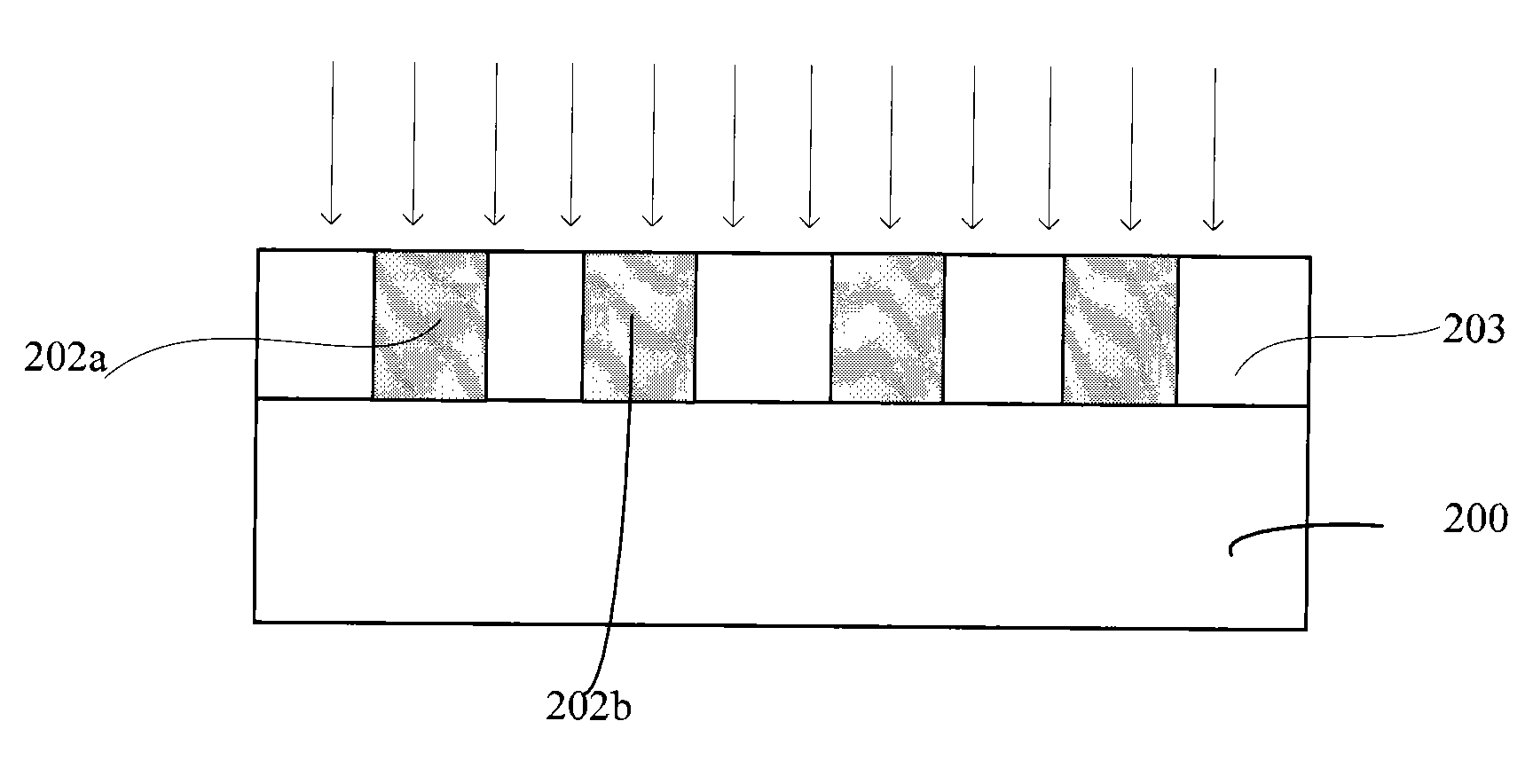

Power semiconductor device and manufacturing method thereof

ActiveCN104377241AImprove electric field distributionImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEngineering

Owner:GPOWER SEMICON

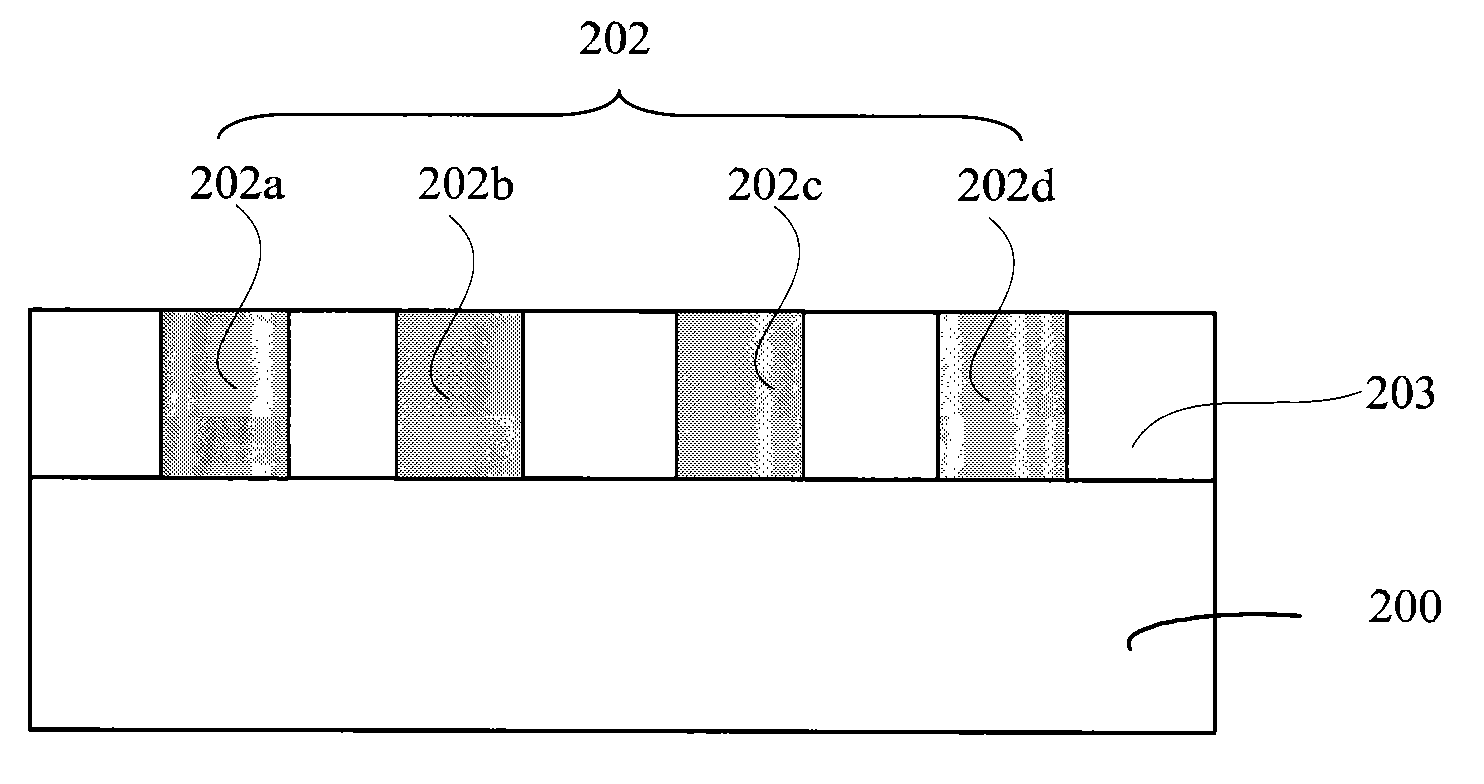

Method of forming an ESD protection device

InactiveUS20010010954A1Lower breakdown voltageLower junction capacitanceTransistorThyristorCapacitanceGate dielectric

The invention discloses a method of forming an ESD protection device without adding the extra mask layers into the traditional CMOS process. At first, P-wells, N-wells, and isolations are formed in a semiconductor substrate. Next, an NMOS transistor with a gate dielectric layer, a gate electrode, source / drain regions, lightly doped source / drain regions, and insulator spacers is formed on the substrate. Particularly, N-wells are also formed in a part of the source / drain regions of the NMOS transistor. Thereafter, ESD protection regions are formed under the source / drain regions by performing P+ ESD protection implantation. Such ESD protection device has a low junction breakdown voltage, quick response speed, and a small junction capacitance.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

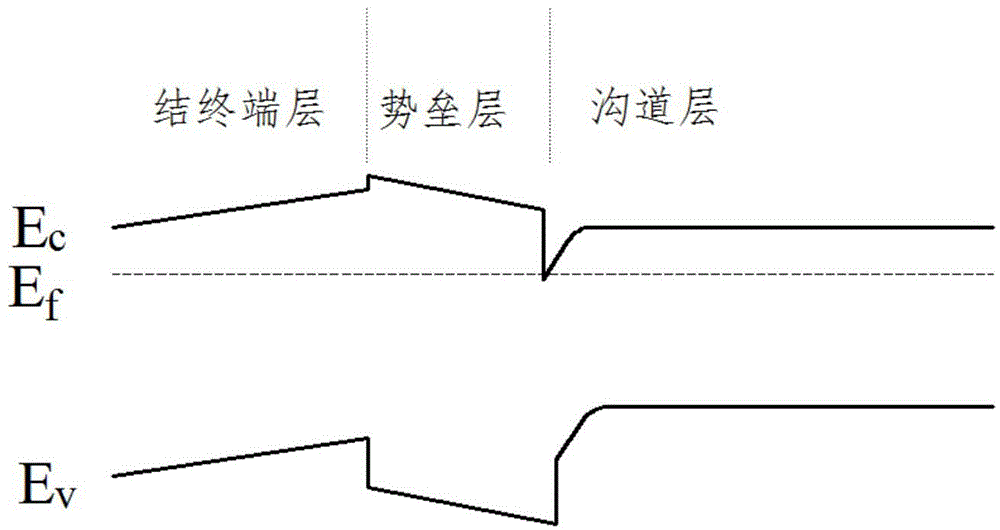

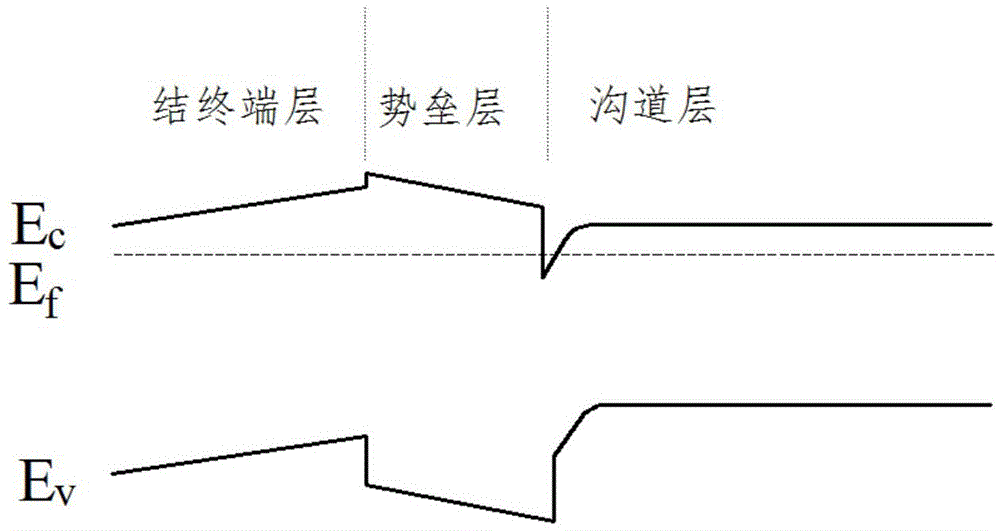

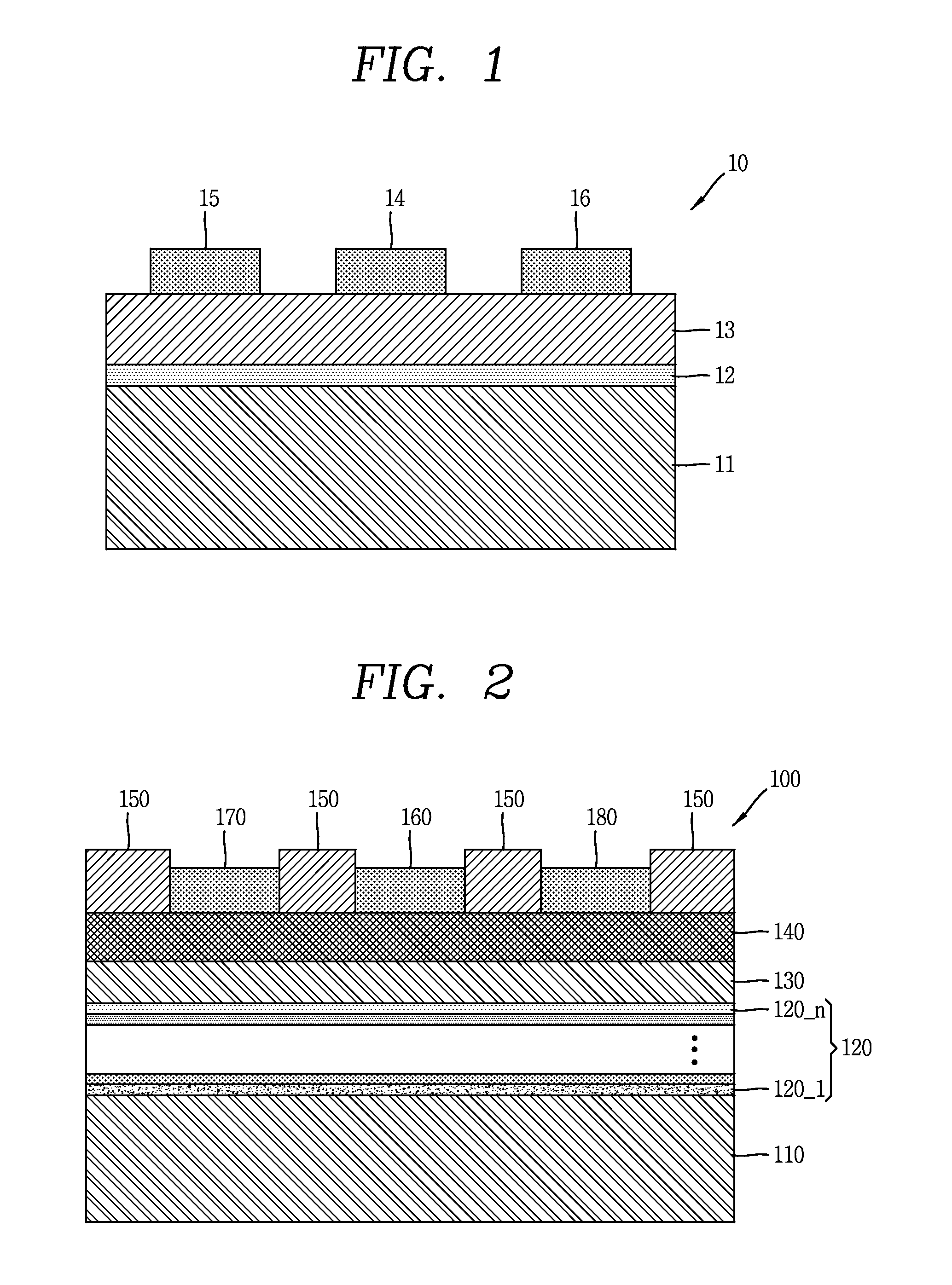

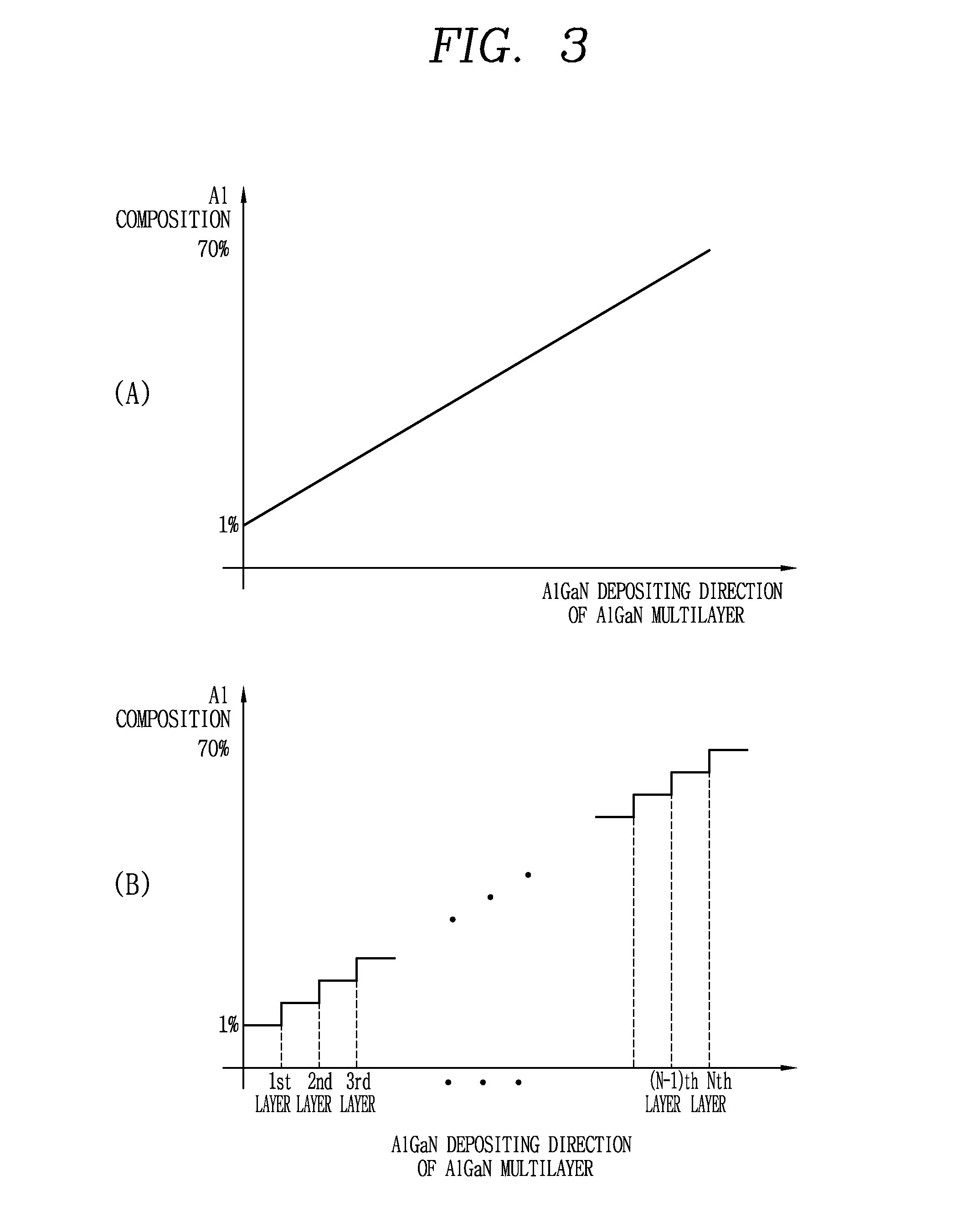

Nitride semiconductor device and fabricating method thereof

ActiveUS20150200257A1Minimized increaseLower breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionDevice material

Owner:LG ELECTRONICS INC

Production method of metal wiring structure

InactiveCN101593722AAvoid it happening againImprove bindingSemiconductor/solid-state device manufacturingBinding forceDielectric layer

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap