Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

7 results about "Gate dielectric" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A gate dielectric is a dielectric used between the gate and substrate of a field-effect transistor. The capacitance and thickness constraints are almost directly opposed to each other. For silicon-substrate FETs, the gate dielectric is almost always silicon dioxide (called "gate oxide"), since thermal oxide has a very clean interface. However, the semiconductor industry is interested in finding alternative materials with higher dielectric constants, which would allow higher capacitance with the same thickness.

Method of forming an ESD protection device

InactiveUS20010010954A1Lower breakdown voltageLower junction capacitanceTransistorThyristorCapacitanceGate dielectric

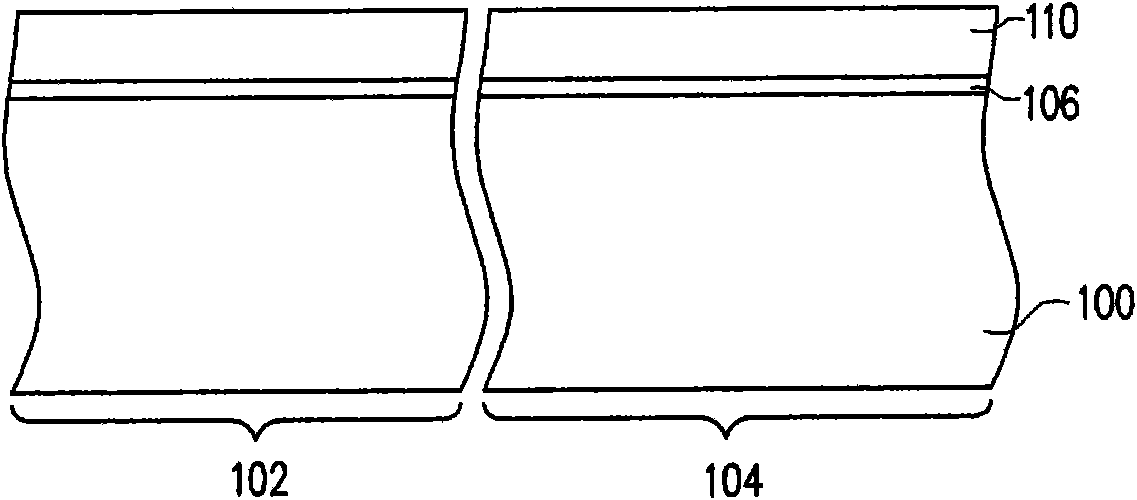

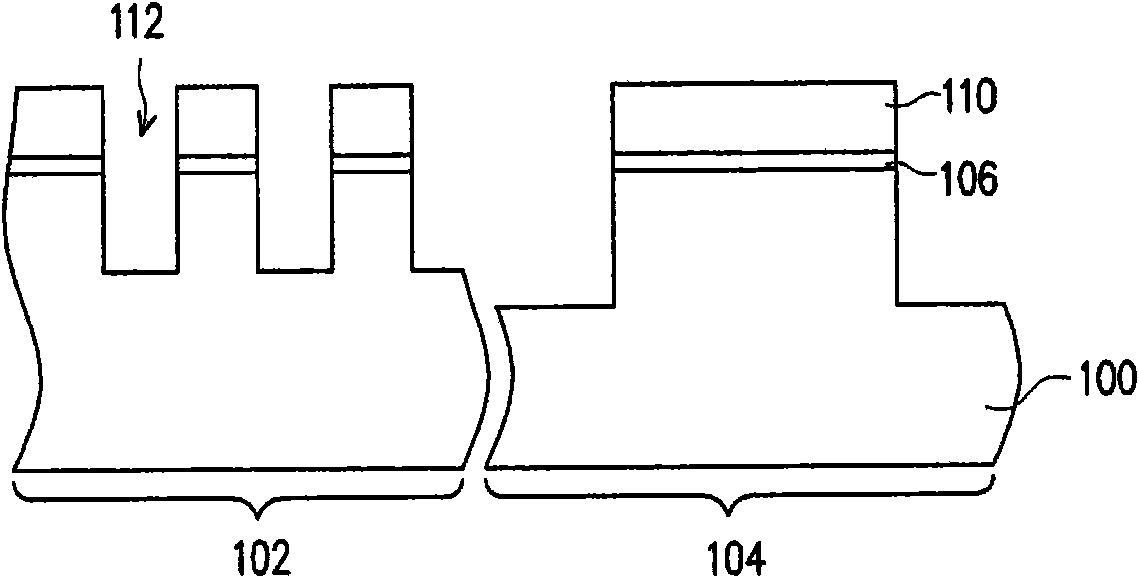

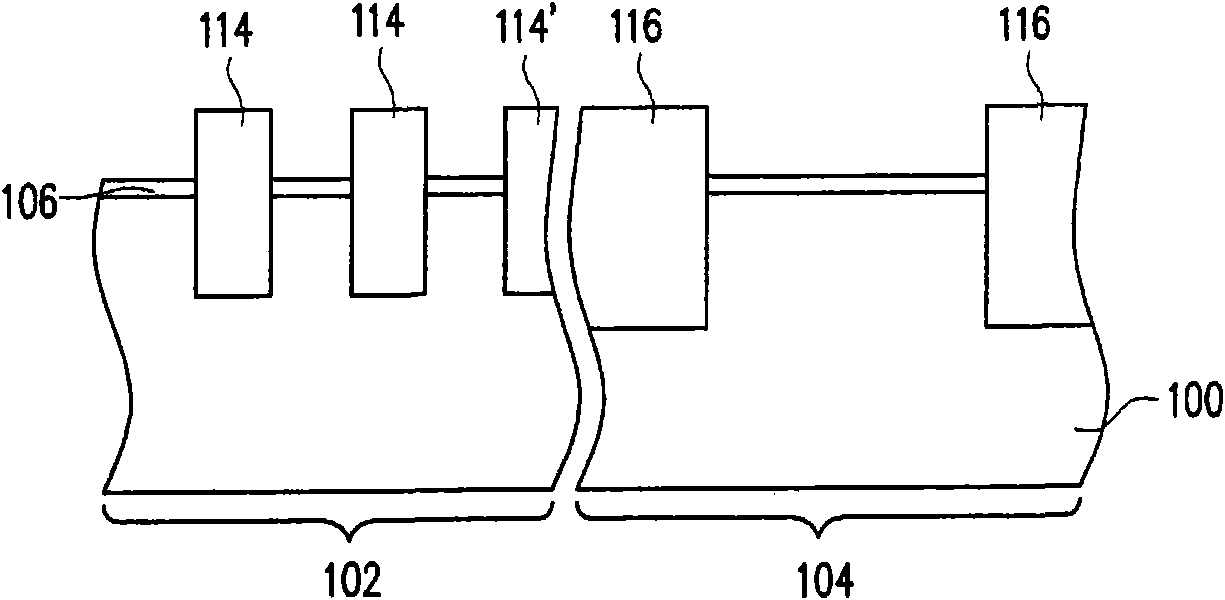

The invention discloses a method of forming an ESD protection device without adding the extra mask layers into the traditional CMOS process. At first, P-wells, N-wells, and isolations are formed in a semiconductor substrate. Next, an NMOS transistor with a gate dielectric layer, a gate electrode, source / drain regions, lightly doped source / drain regions, and insulator spacers is formed on the substrate. Particularly, N-wells are also formed in a part of the source / drain regions of the NMOS transistor. Thereafter, ESD protection regions are formed under the source / drain regions by performing P+ ESD protection implantation. Such ESD protection device has a low junction breakdown voltage, quick response speed, and a small junction capacitance.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

Method for manufacturing flash memory

ActiveCN101924078AImprove gate coupling ratioImprove electrical performanceSemiconductor/solid-state device manufacturingElectrical conductorGate dielectric

Owner:WINBOND ELECTRONICS CORP

Universal CMOS device leakage characterization system

ActiveUS20070252613A1Marginal circuit testingIndividual semiconductor device testingCMOSGate dielectric

The invention provides a universal leakage monitoring system (ULMS) to measure a plurality of leakage macros during the development of a manufacturing process or a normal operation period. The ULMS characterizes the leakage of both n-type and p-type CMOS devices on the gate dielectric leakage, the sub-threshold leakage, and the reverse biased junction leakage, and the like. Testing is performed sequentially from the first test macro up to the last test macro using an on-chip algorithm. When the last test macro is tested, it scans the leakage data out.

Owner:MARVELL ASIA PTE LTD

Vertical power mosfet and methods of forming the same

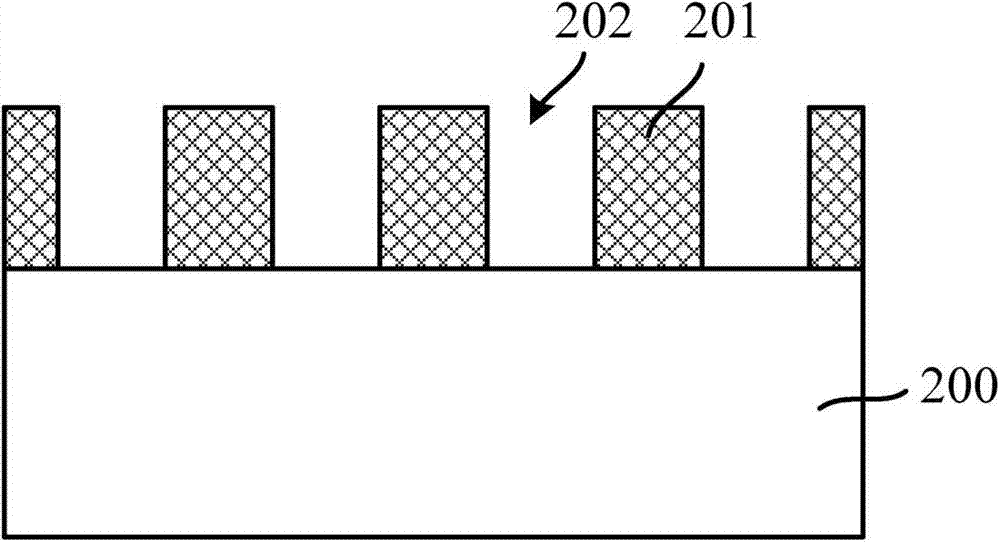

ActiveCN103456790ASemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricPower MOSFET

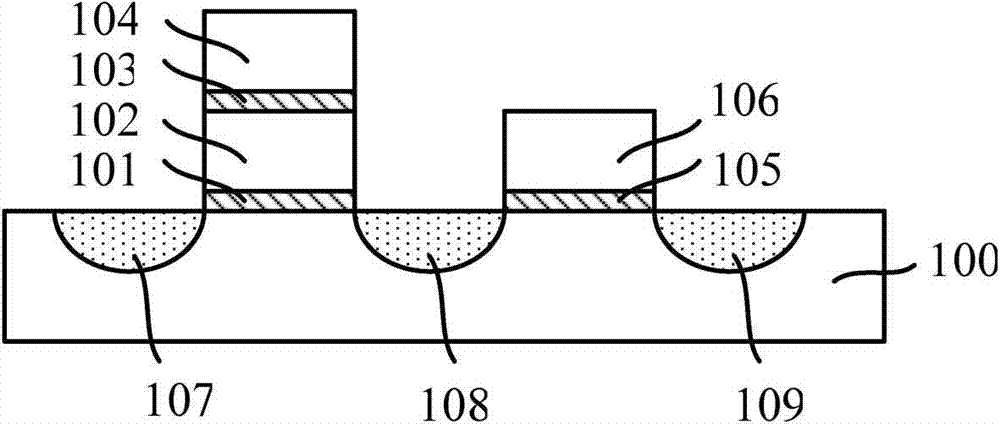

A device includes a semiconductor layer of a first conductivity type, and a first and a second body region over the semiconductor layer, wherein the first and the second body regions are of a second conductivity type opposite the first conductivity type. A doped semiconductor region of the first conductivity type is disposed between and contacting the first and the second body regions. A gate dielectric layer is disposed over the first and the second body regions and the doped semiconductor region. A first and a second gate electrode are disposed over the gate dielectric layer, and overlapping the first and the second body regions, respectively. The first and the second gate electrodes are physically separated from each other by a space, and are electrically interconnected. The space between the first and the second gate electrodes overlaps the doped semiconductor region.

Owner:TAIWAN SEMICON MFG CO LTD

Flash memory device and formation method thereof

ActiveCN104752358AImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricEngineering

Owner:SEMICON MFG NORTH CHINA (BEIJING) CORP +1

FinFET and manufacturing method thereof

ActiveCN103855026AReduce adverse effectsReduce usageSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate dielectric

The invention discloses a FinFET and a manufacturing method thereof. The manufacturing method of the FinFET comprises the steps of forming a semiconductor fin with a trapezoidal cross section, forming one of a source region and a drain region, forming a sacrifice side wall, using the sacrifice side wall as a mask, forming the other one of the source region and the drain region, removing the sacrifice side wall, and using a gate stack for replacing the sacrifice side wall, wherein the gate stack comprises a gate conductor and gate dielectric media, and the gate dielectric media partition the gate conductor and the semiconductor fin.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

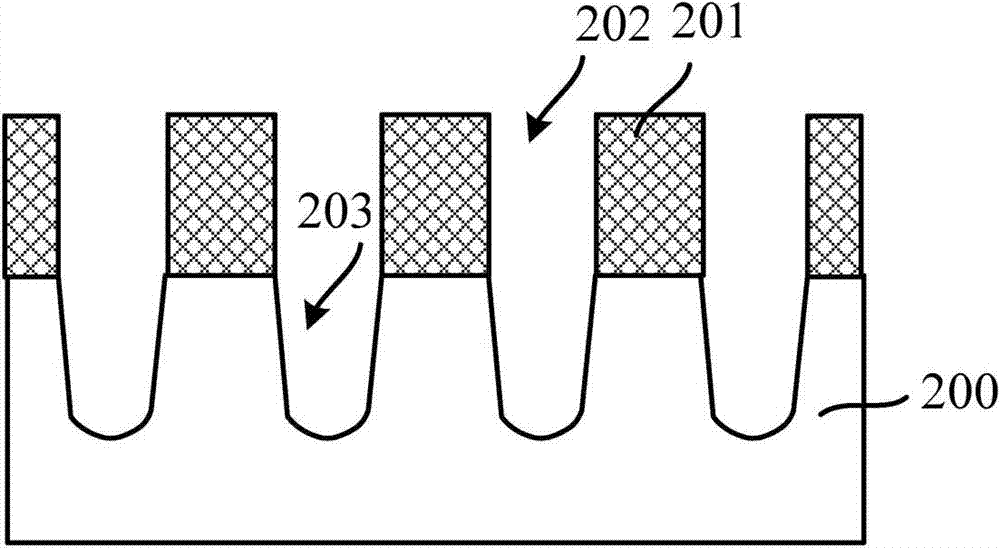

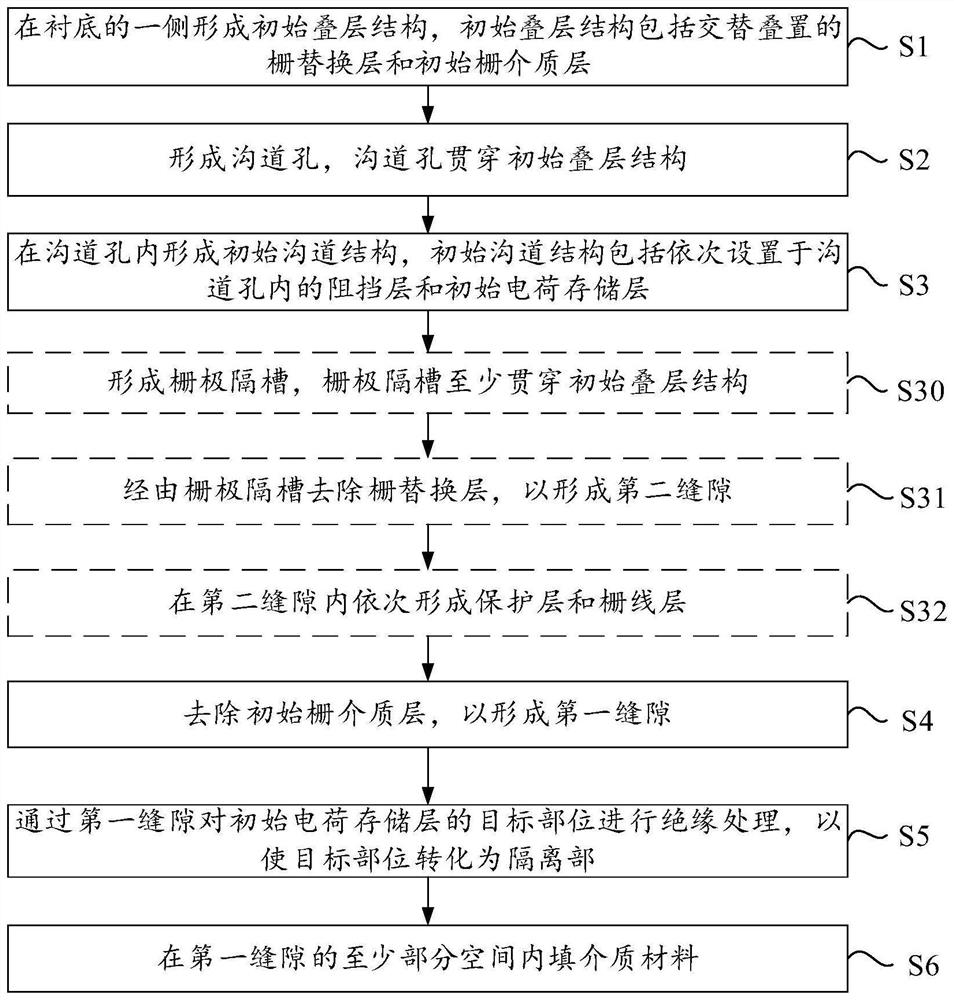

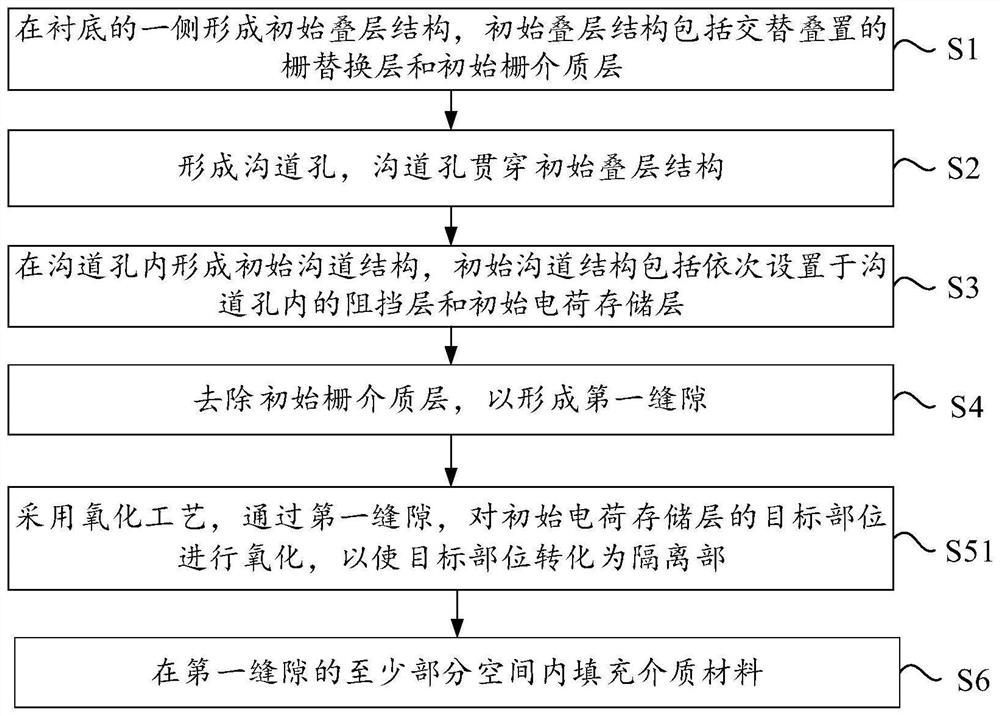

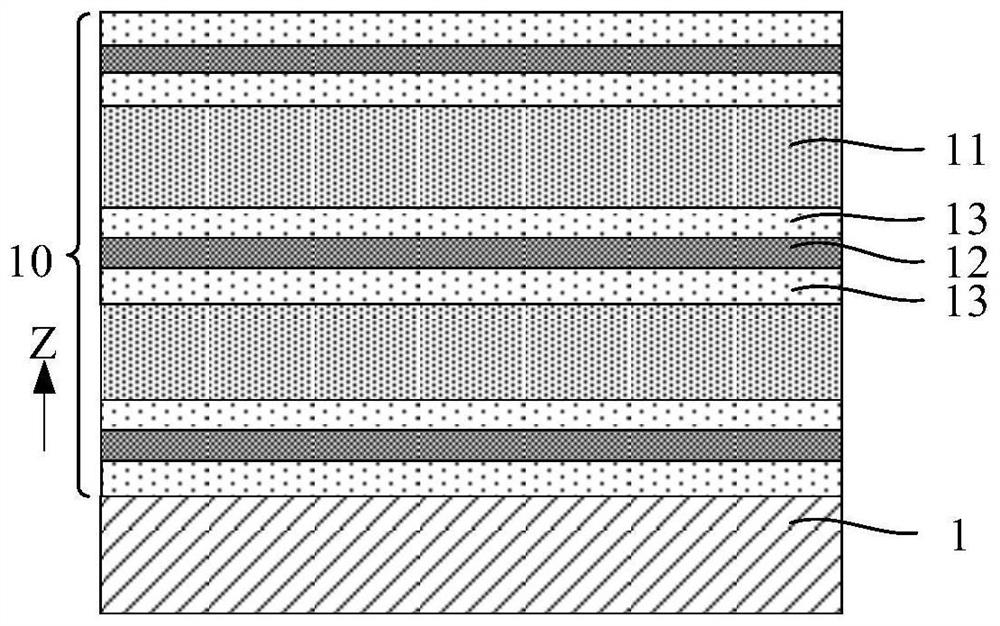

Semiconductor structure and preparation method thereof, three-dimensional memory and storage system

PendingCN114551457AInhibit migrationImprove stabilitySolid-state devicesRead-only memoriesGate dielectricSemiconductor structure

Owner:YANGTZE MEMORY TECH CO LTD

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap