Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3 results about "Junction leakage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

If a potential is applied from collector to emitter, then one junction is reverse-biased, so a tiny leakage will occur. The other junction is forward-biased, so will have a low resistance.

Universal CMOS device leakage characterization system

ActiveUS20070252613A1Marginal circuit testingIndividual semiconductor device testingCMOSGate dielectric

The invention provides a universal leakage monitoring system (ULMS) to measure a plurality of leakage macros during the development of a manufacturing process or a normal operation period. The ULMS characterizes the leakage of both n-type and p-type CMOS devices on the gate dielectric leakage, the sub-threshold leakage, and the reverse biased junction leakage, and the like. Testing is performed sequentially from the first test macro up to the last test macro using an on-chip algorithm. When the last test macro is tested, it scans the leakage data out.

Owner:MARVELL ASIA PTE LTD

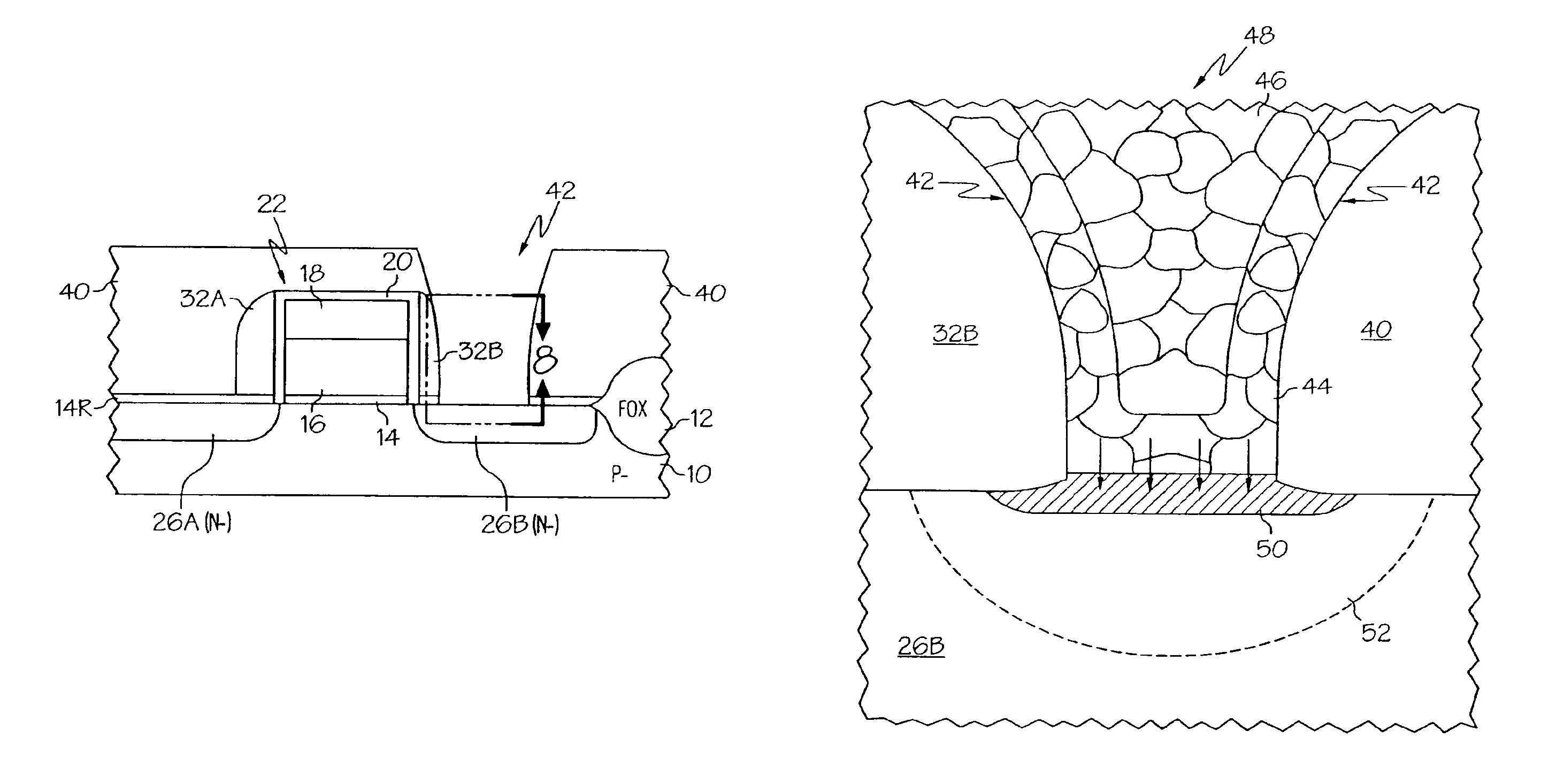

Method of manufacturing a multilayered doped conductor for a contact in an integrated circuit device

InactiveUS6858534B2Increase the doping concentrationLess susceptibleTransistorSemiconductor/solid-state device detailsDopantRefresh cycle

Owner:MICRON TECH INC

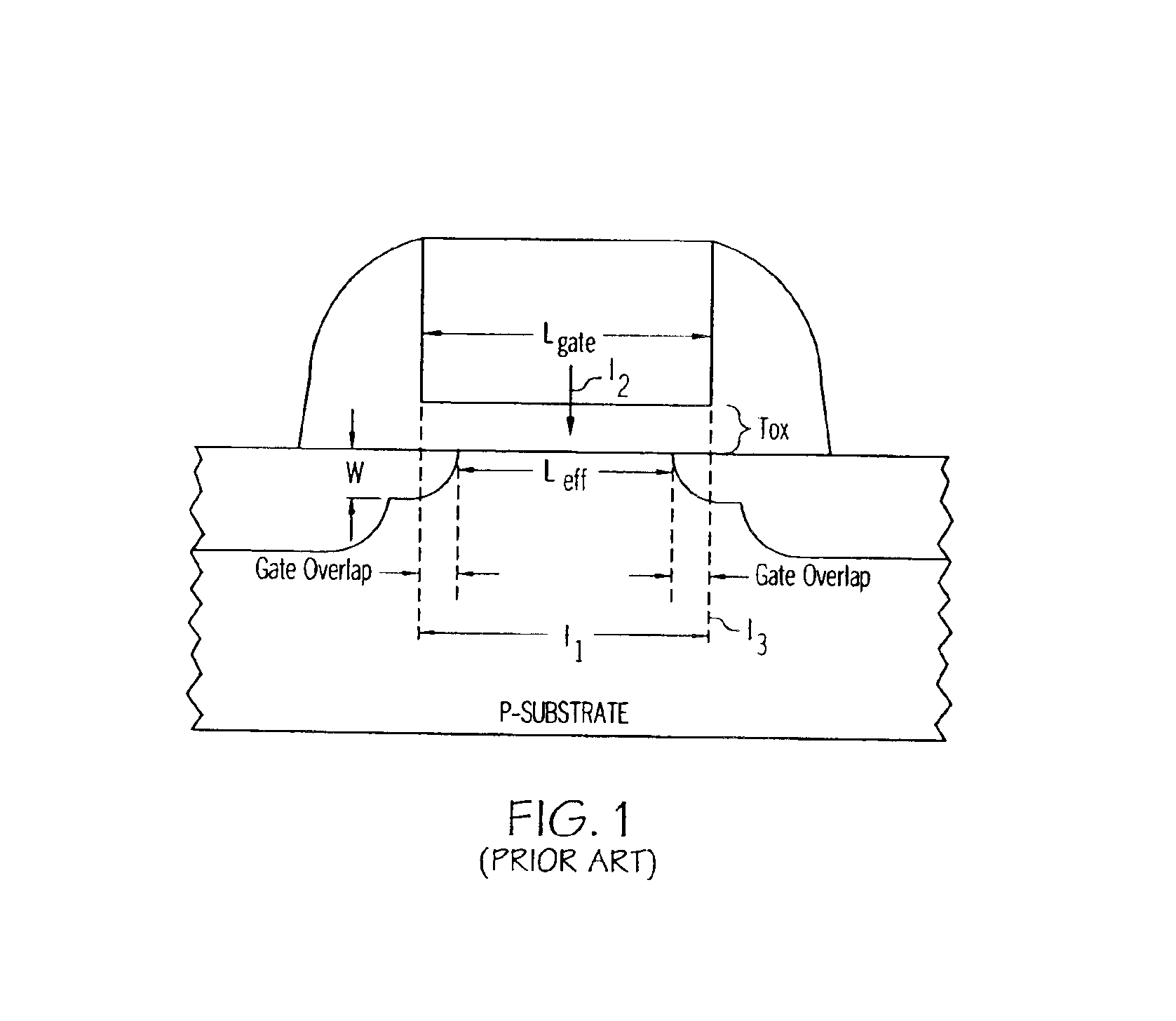

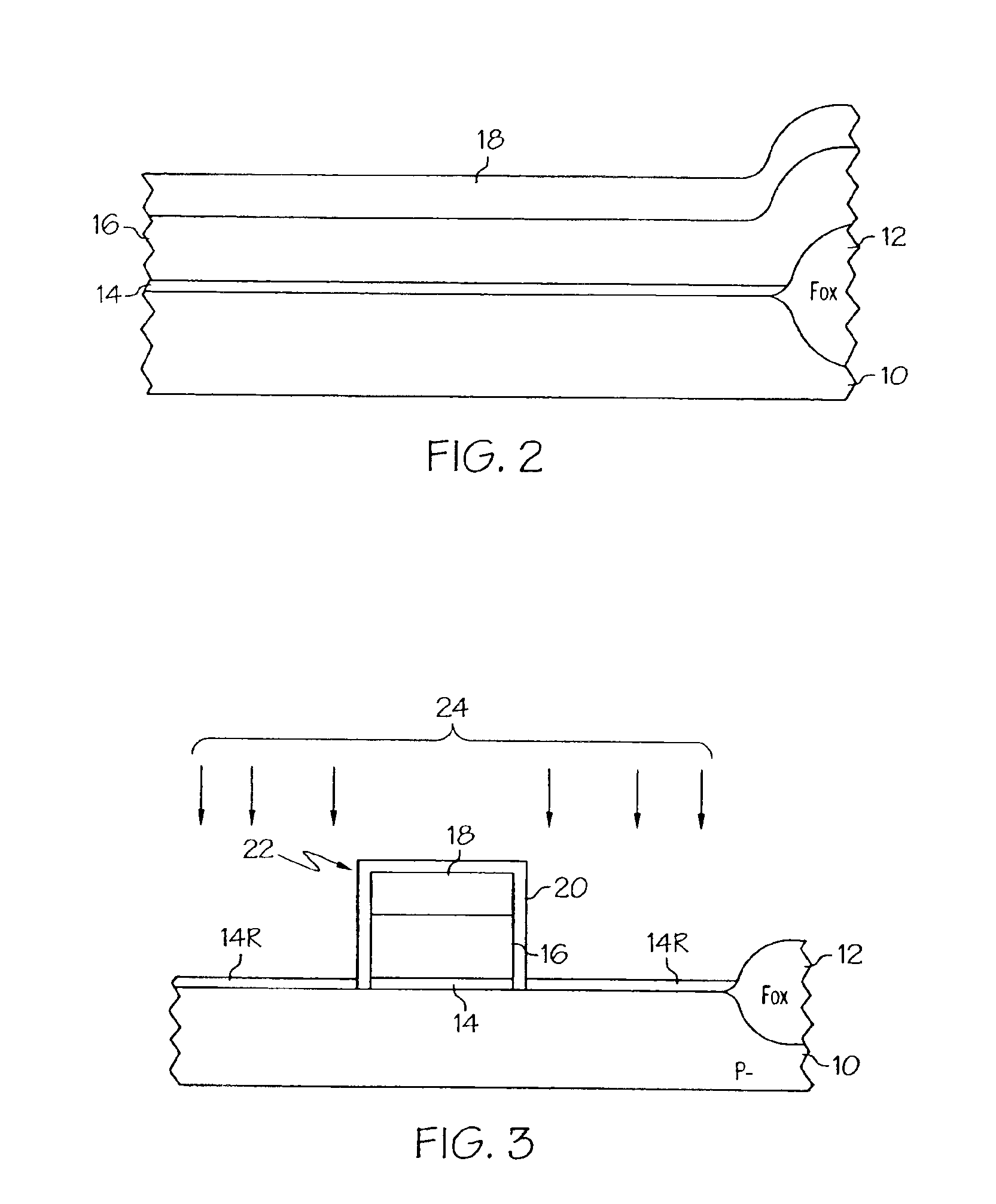

Semiconductor device and producing method thereof

InactiveCN1531110APrevent Residual DefectsReduces the chance of junction leakageTransistorSemiconductor/solid-state device manufacturingInsulation layerJunction leakage

To reduce a leakage current by suppressing the generation of a junction leakage. [Means to Solve the Problem]A semiconductor device comprises: a semiconductor region 103, in which an impurity of one conductivity type is doped; a gate insulation layer 105, formed on the semiconductor region 103; a gate electrode 106, formed on the gate insulation layer 105; a lightly doped layer 109a, formed in a region from the principal surface of the semiconductor region 103 to a first depth, in which a first impurity of the other conductivity type is implanted into the semiconductor region 103 with a first dose amount; and a heavily doped layer 109b, formed in a region from the principal surface of the semiconductor region 103 to a second depth, which is shallower than the first depth, in which a second impurity of the other conductivity type is implanted into the semiconductor region 103 with a second dose amount in a range of the first dose amount or more to 1x10E15 / cm<2 >or less.

Owner:SEIKO EPSON CORP

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap