Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3 results about "Chip stacking" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor wafer processing method

ActiveUS20120322231A1Without causing damageReduce risk of damageSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor wafer has a device area where a plurality of semiconductor devices are respectively formed in a plurality of regions partitioned by a plurality of crossing division lines formed on the front side of the semiconductor wafer and a peripheral area surrounding the device area. The back side of the semiconductor wafer corresponding to the device area is ground to thereby form a circular recess and an annular projection surrounding the circular recess. In a chip stacked wafer forming step, a plurality of semiconductor device chips are provided on the bottom surface of the circular recess of the semiconductor wafer at the positions respectively corresponding to the semiconductor devices of the semiconductor wafer. The chip stacked wafer is ground to reduce the thickness of each semiconductor device chip to a finished thickness, and a through electrode is formed in each semiconductor device of the semiconductor wafer.

Owner:DISCO CORP

Multi-layer multi-chip fan-out structure and manufacturing method

ActiveCN103594451ALow costPackage Size OptimizationSemiconductor/solid-state device detailsSolid-state devicesSolder maskInterconnection

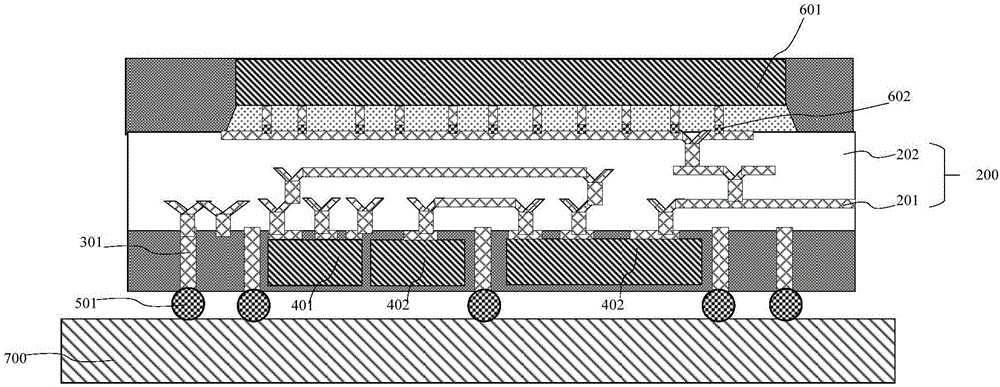

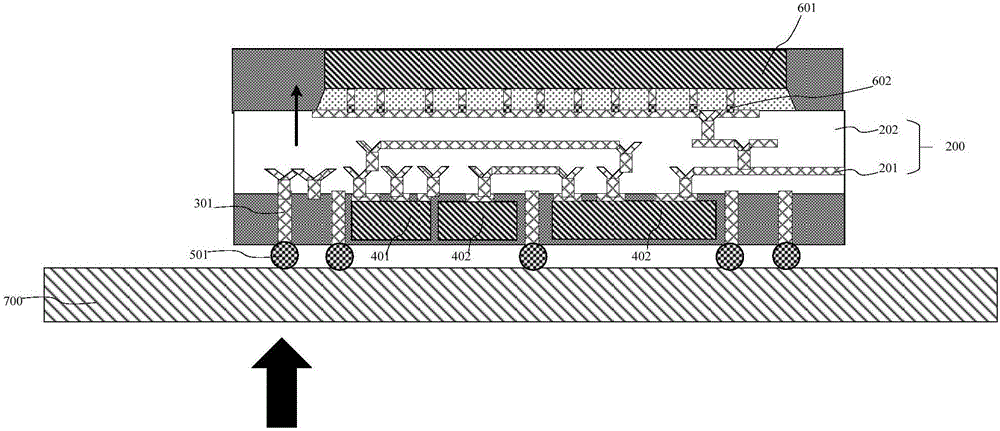

The invention provides a multi-layer multi-chip fan-out structure. The multi-layer multi-chip fan-out structure comprises a bearing plate, and a plurality of packaging sub bodies which are stacked are arranged on the bearing plate; at least one die is packaged into each packaging sub body; in each packaging sub body, the die is coated by a dielectric material of a dielectric layer, and the die is attached to a metal cushion block with the front face faces upwards; an RDL layer is arranged on the dielectric layer of each packaging sub body; a bonding pad of the front face of each die is electrically connected with the RDL layer of the corresponding packaging sub body where the die exists; insulating layers are arranged between adjacent packaging sub bodies, and the RDL layers of the adjacent packaging sub bodies are electrically connected through second interconnection holes between the layers. The metal cushion blocks in the bottom packaging sub bodies are pressed on the surface of the bearing plate, and the metal cushion blocks in the middle or top packaging sub bodies are pressed on the insulating layers of the packaging sub bodies; the surface of each top packaging sub body is provided with a solder mask layer in a distributed mode. According to the multi-layer multi-chip fan-out structure, three-dimensional multi-chip stacking can be easily achieved.

Owner:JIANGSU CAS MICROELECTRONICS INTEGRATION TECH CO LTD

Packager piece of integrated power supply system and package method

PendingCN106531710AEliminate parasitic resistanceSolve processing problemsSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionElectricity delivery

Owner:SJ SEMICON JIANGYIN CORP

Popular searches

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap