Equalizer architecture

a technology of equalizers and components, applied in equalizers, transmission, transmitter/receiver shaping networks, etc., can solve the problems of increasing the probability that the receiver will fail to determine correctly, increasing the probability of bit errors, and placing a so as to achieve high data rates and high computational burden on the components

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

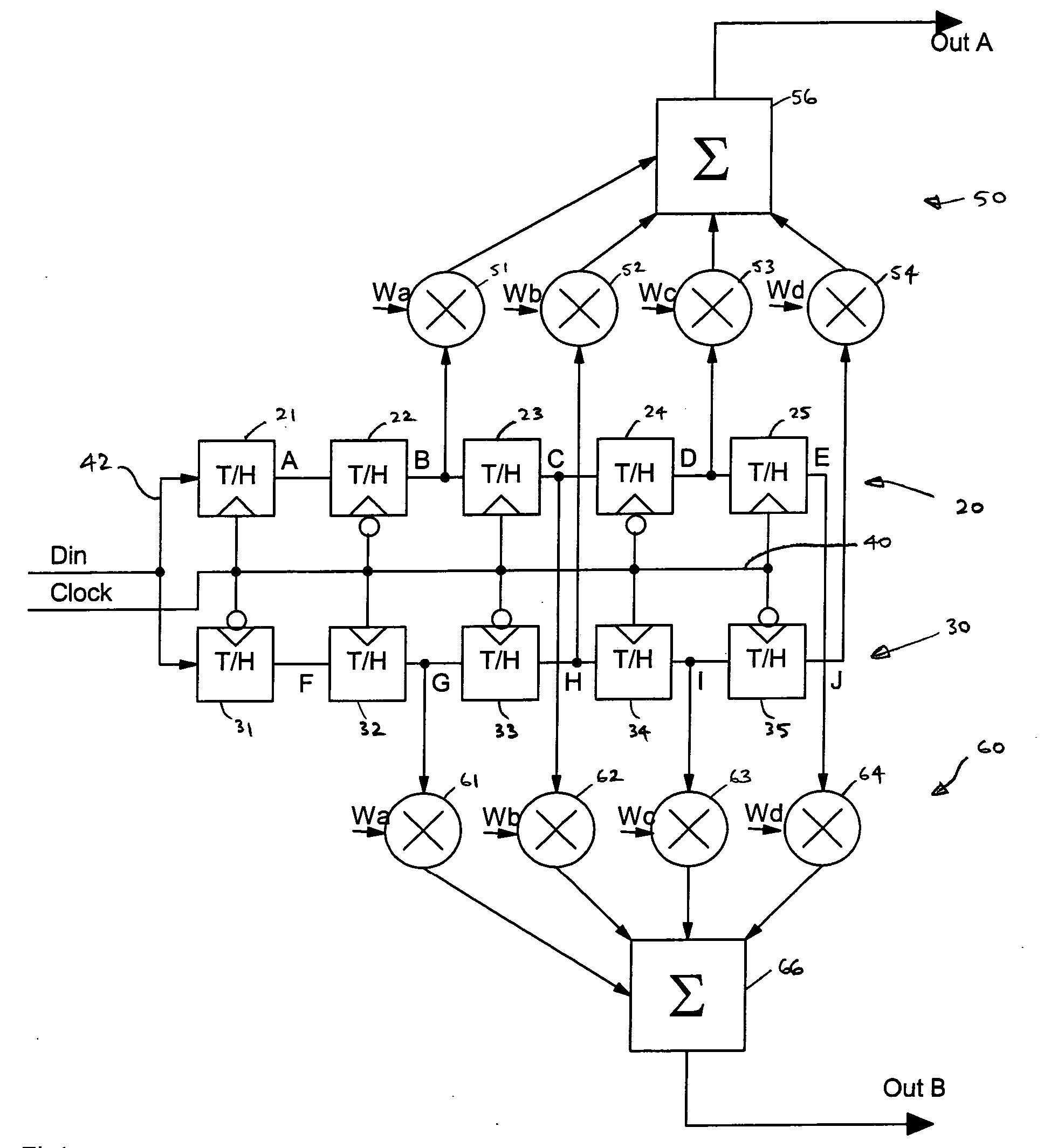

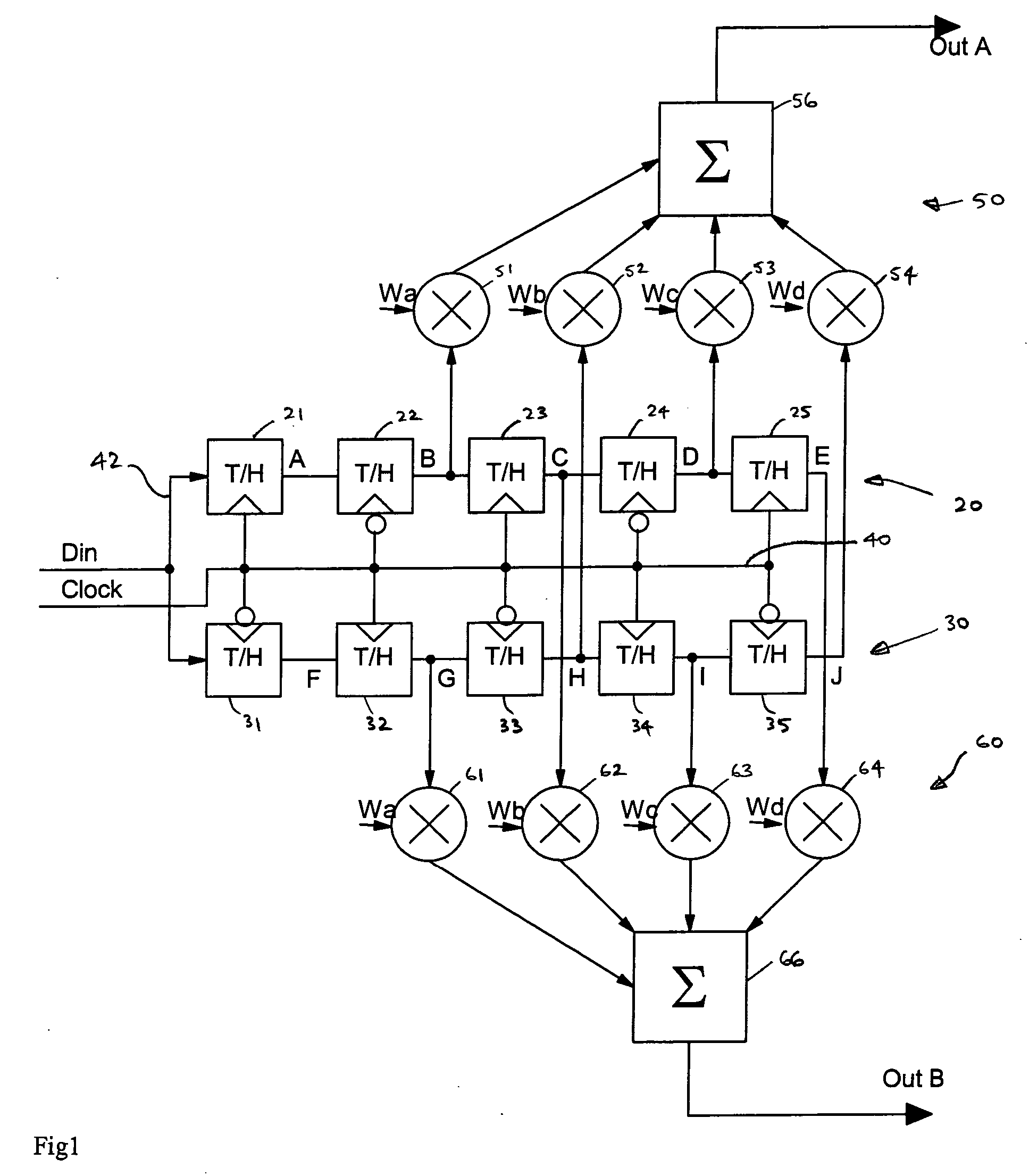

[0019]FIG. 1 is a block schematic diagram of an equalizer in accordance with the present invention, implemented in the form of a finite impulse response filter, divided into two parallel paths.

[0020] Thus, compared with a conventional finite impulse response filter implementation, which includes a tapped delay line, the equalizer of FIG. 1 includes a first tapped delay line 20 and a second tapped delay line 30. In this illustrated embodiment of the invention, the first tapped delay line 20 is made up of five track and hold circuits 21-25, while the second tapped delay line 30 is made up of five track and hold circuits 31-35. However, it will be appreciated that the tapped delay lines may be of any convenient length, depending on the extent to which transmitted bits are spread over multiple bit periods by the time they reach the receiver.

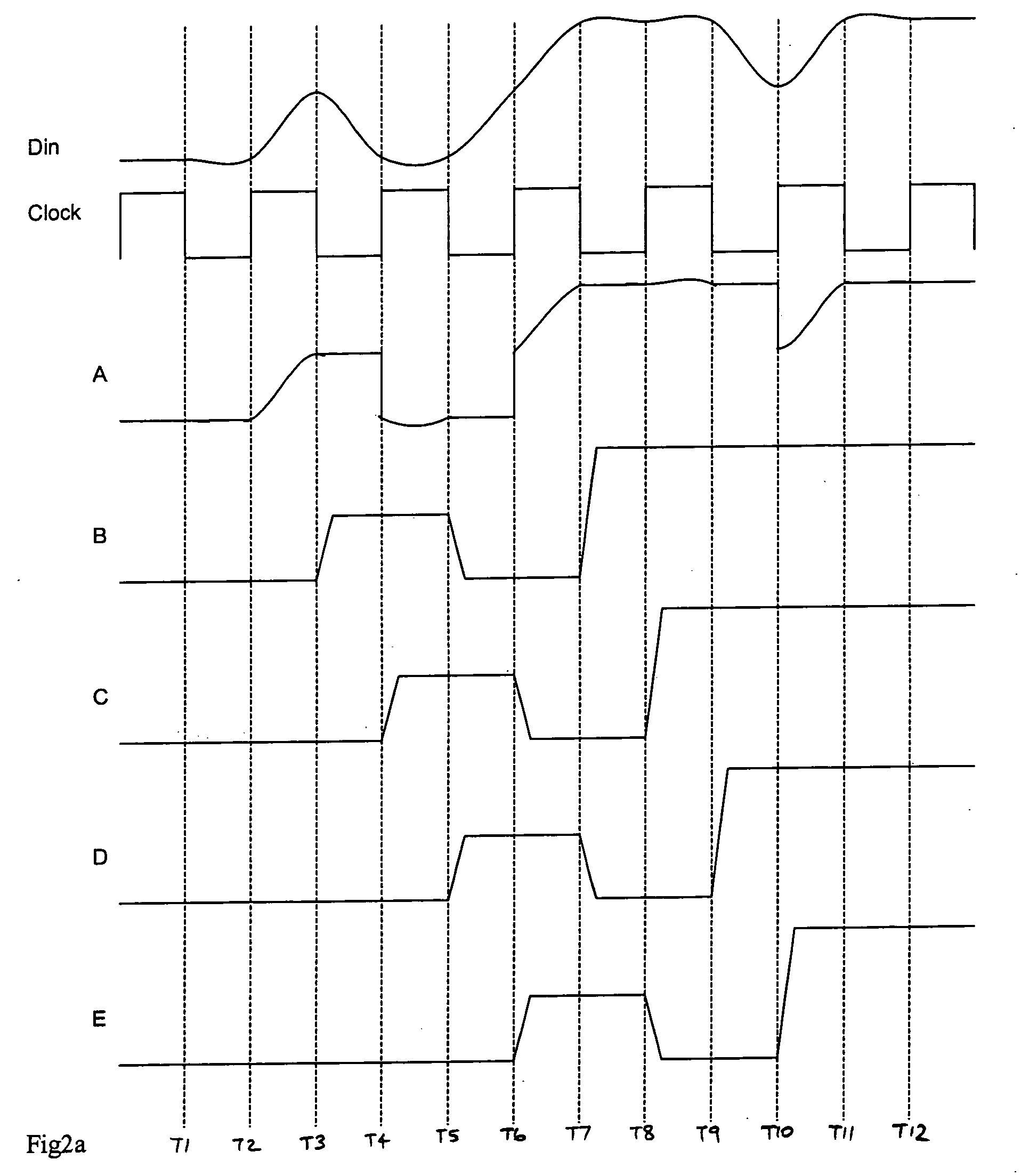

[0021] In this illustrated embodiment of the invention, each of the track and hold circuits 21-25, 31-35 is of a type which is transparent when its c

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap