Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1 results about "Burn-in" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Burn-in is the process by which components of a system are exercised prior to being placed in service (and often, prior to the system being completely assembled from those components). This testing process will force certain failures to occur under supervised conditions so an understanding of load capacity of the product can be established.

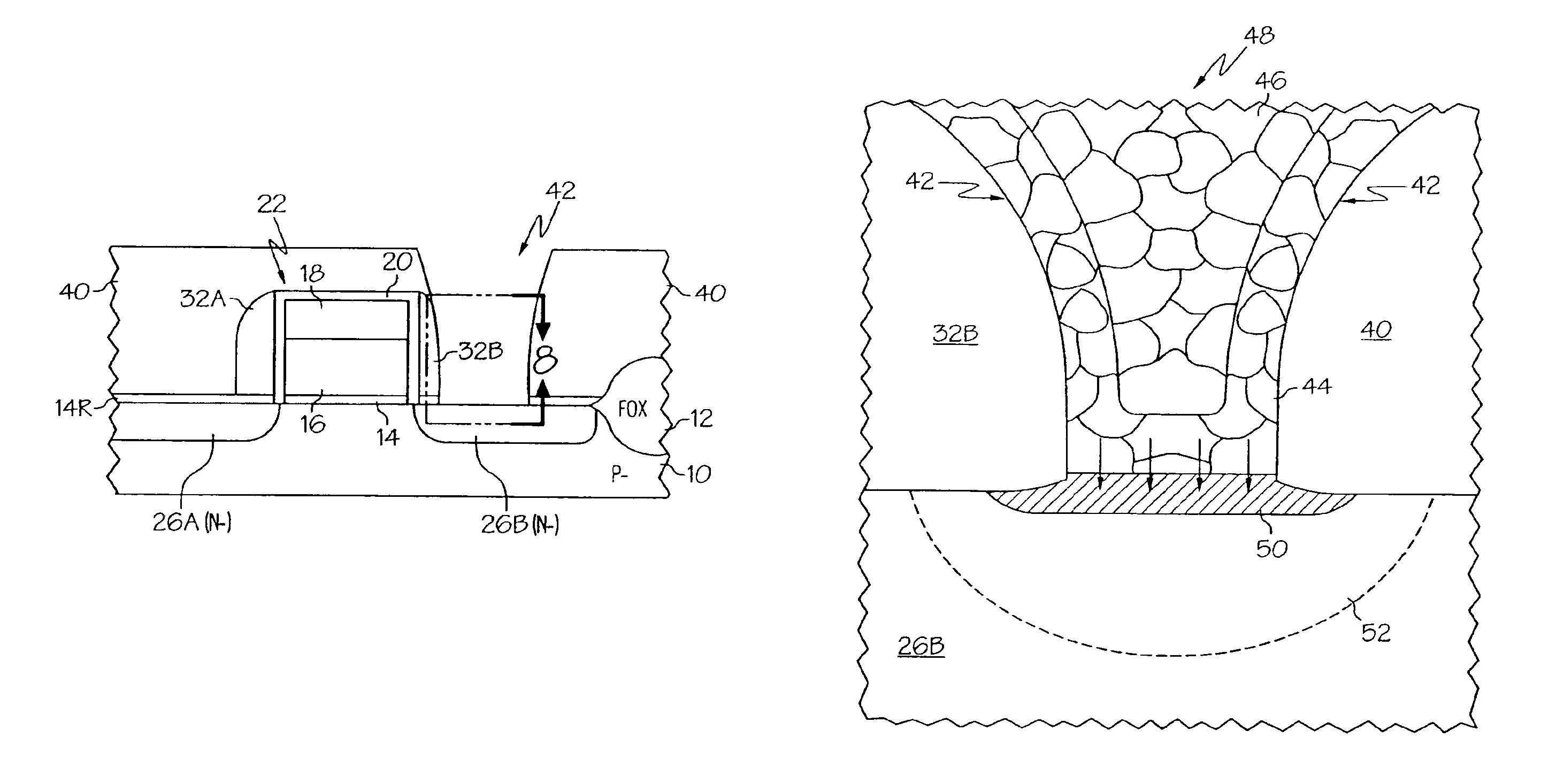

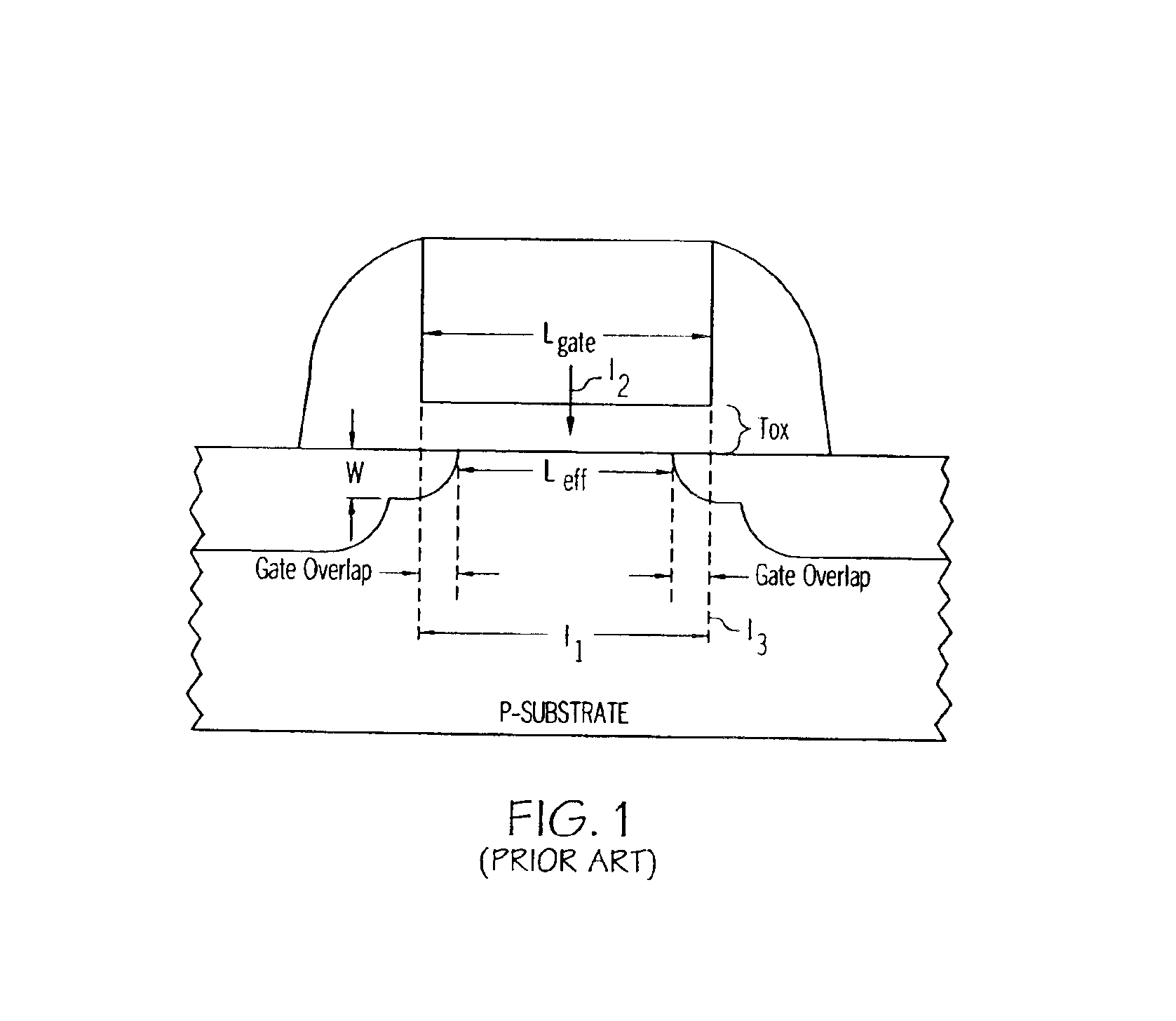

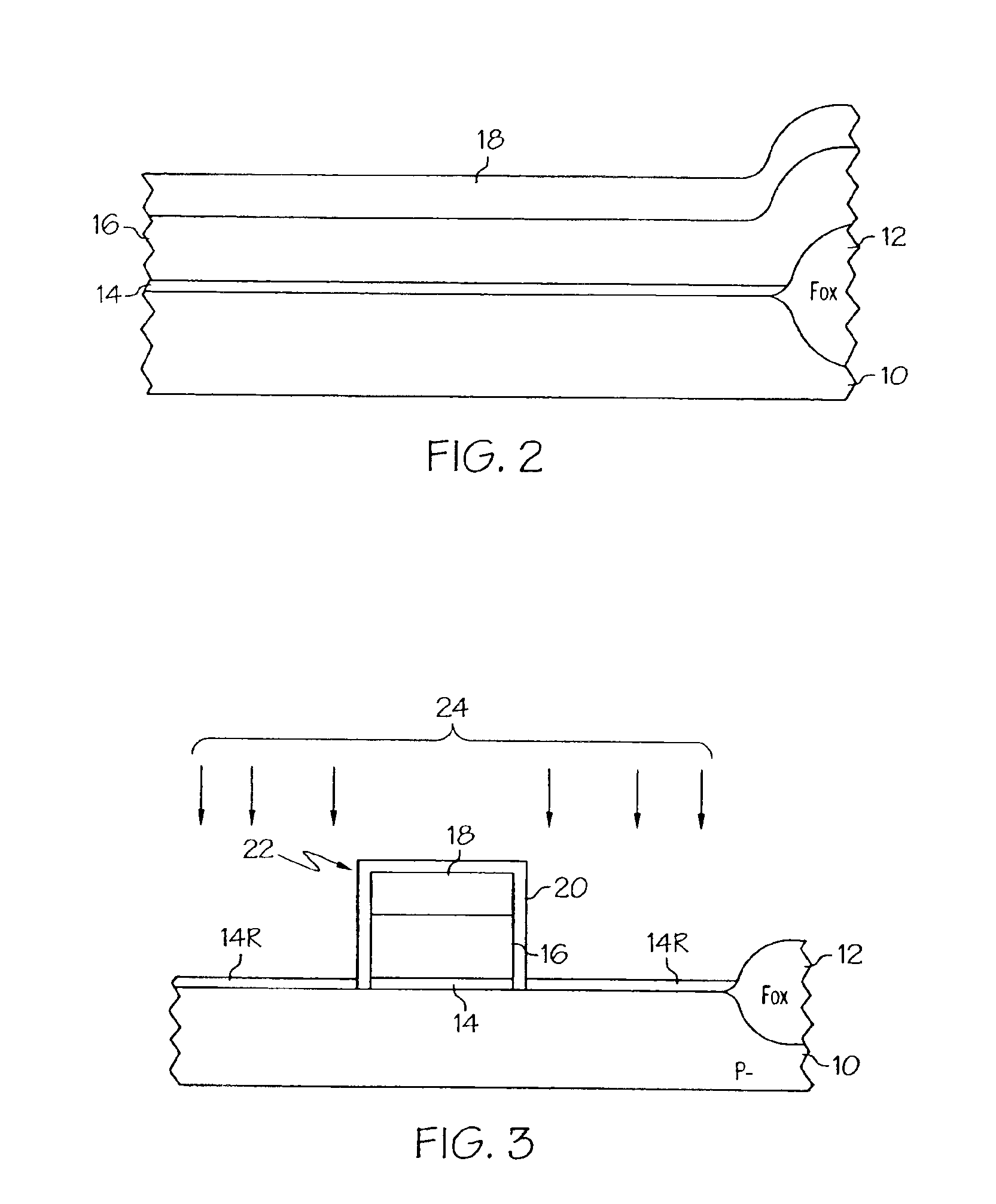

Method of manufacturing a multilayered doped conductor for a contact in an integrated circuit device

InactiveUS6858534B2Increase the doping concentrationLess susceptibleTransistorSemiconductor/solid-state device detailsDopantRefresh cycle

Owner:MICRON TECH INC

Popular searches

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap