Verification method for connection sequence of signal line and power line

A verification method and signal line technology, applied in electrical digital data processing, instruments, calculations, etc., can solve the problems of easy missed detection and low efficiency, and achieve the effect of improving accuracy and efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to make the purpose, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the embodiments and the accompanying drawings. as a limitation of the present invention.

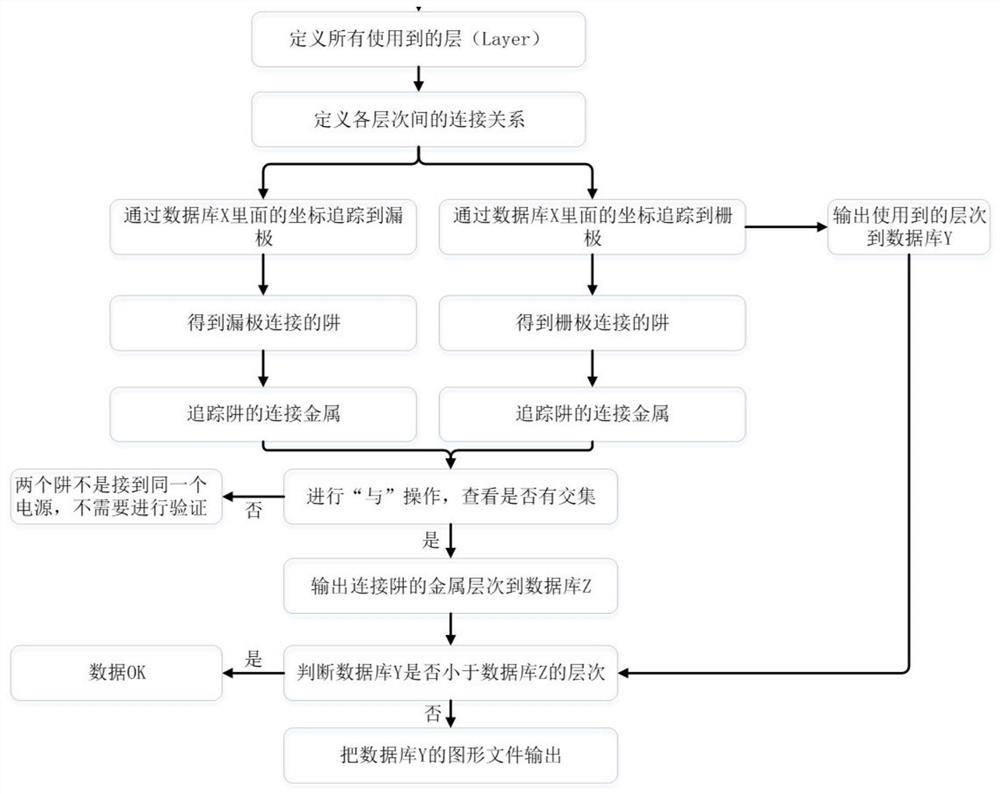

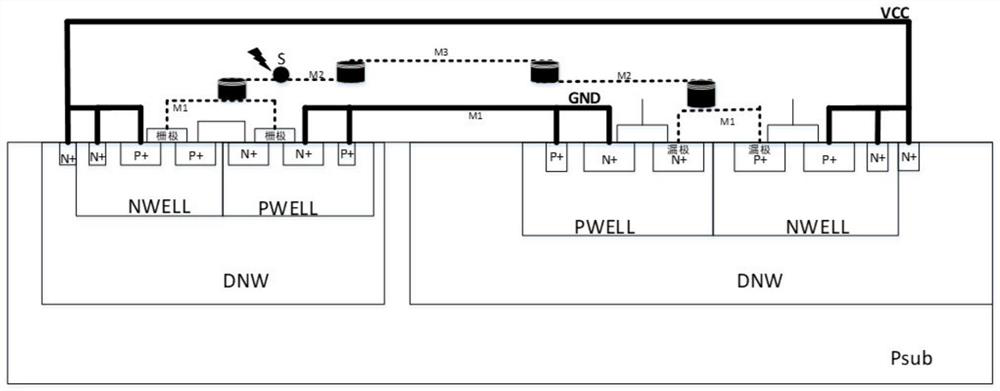

[0033] The improvement of the present invention over the prior art lies in that, in the design of a large-scale integrated circuit, an automatic check is realized for the verification that the signal line is connected before the power line.

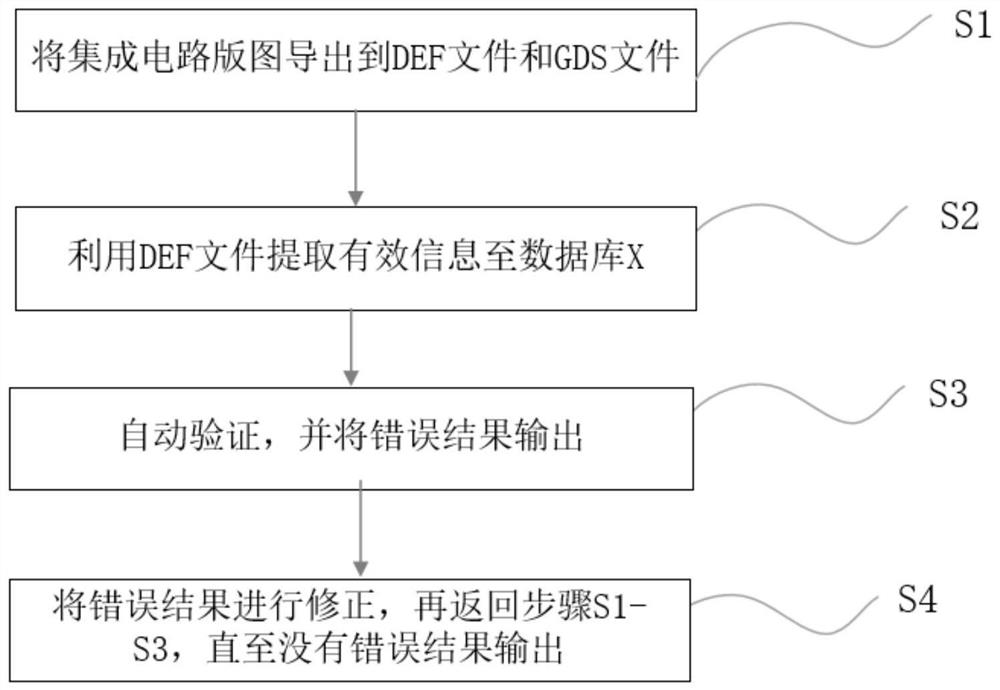

[0034] An embodiment of the present invention provides a method for verifying the connection sequence of a signal line and a power line, including the following steps:

[0035] S1. Export the IC layout to DEF files and GDS files;

[0036] The DEF file is a text file that records layout information, including the coordinates and names of modules, lines, etc.;

[0037] GDS file is a graphic file that records layout information, including coordinates and names of modul

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap