Circuit measuring operating speed and related semiconductor memory device

a technology of operating speed and semiconductor memory chip, which is applied in the direction of instruments, nuclear elements, nuclear engineering, etc., can solve the problems of inability to conduct direct operating speed measurements, inability to generate test signals at a sufficiently high frequency, and inability of test devices to accurately measure the operating speed of constituent semiconductor memory chips. , to achieve the effect of accurately measuring the operating speed of the constituent semiconductor memory chip

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022]Embodiments of the invention will now be described more fully with reference to the accompanying drawings. The invention may, however, be embodied in different forms and should not be construed as limited to only the illustrated embodiments. Rather, these embodiments are presented as teaching examples. In the drawings, certain geometric relationships may be exaggerated for clarity. Throughout the drawings and written description like reference numbers and legends refer to like or similar elements.

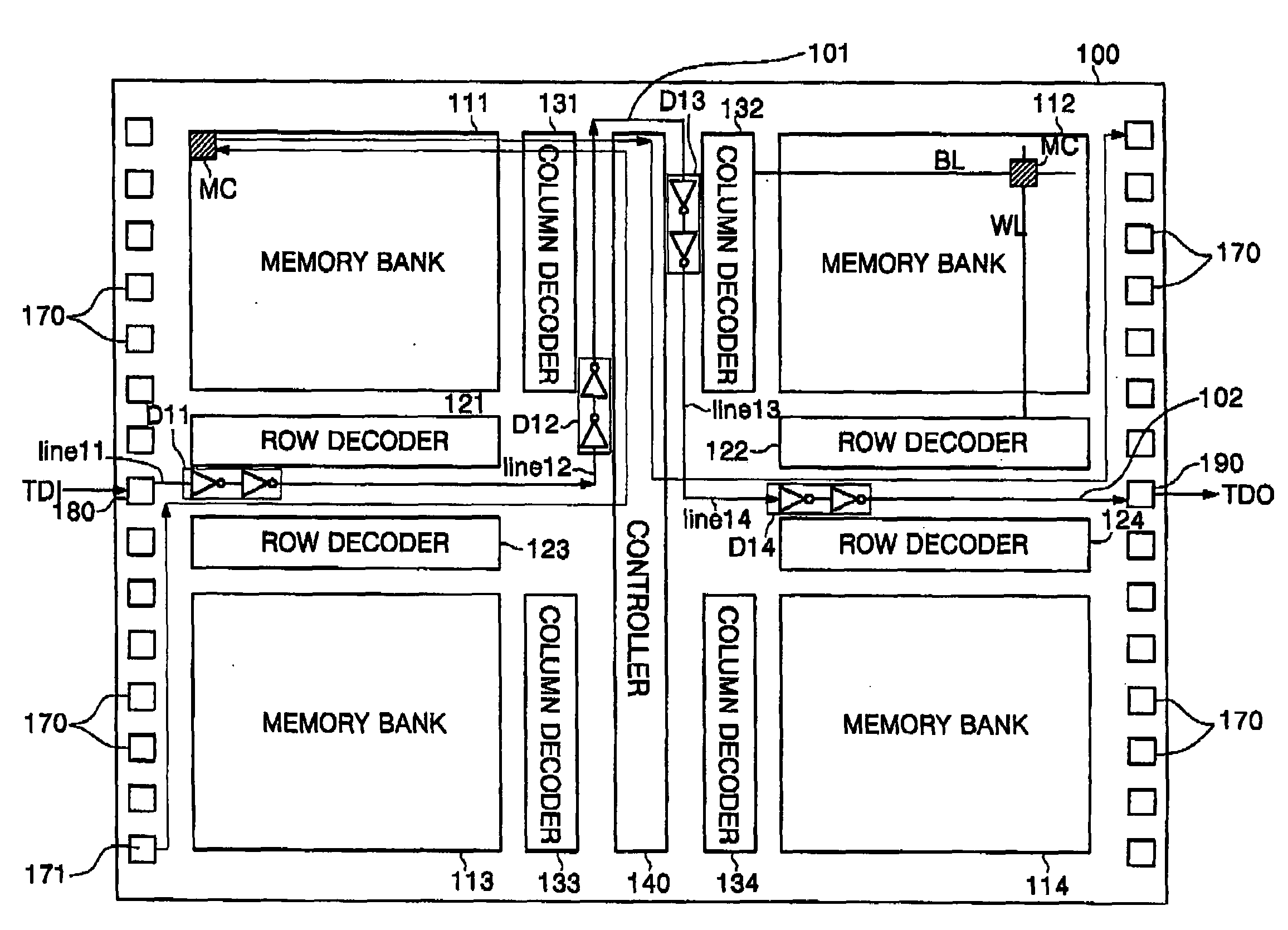

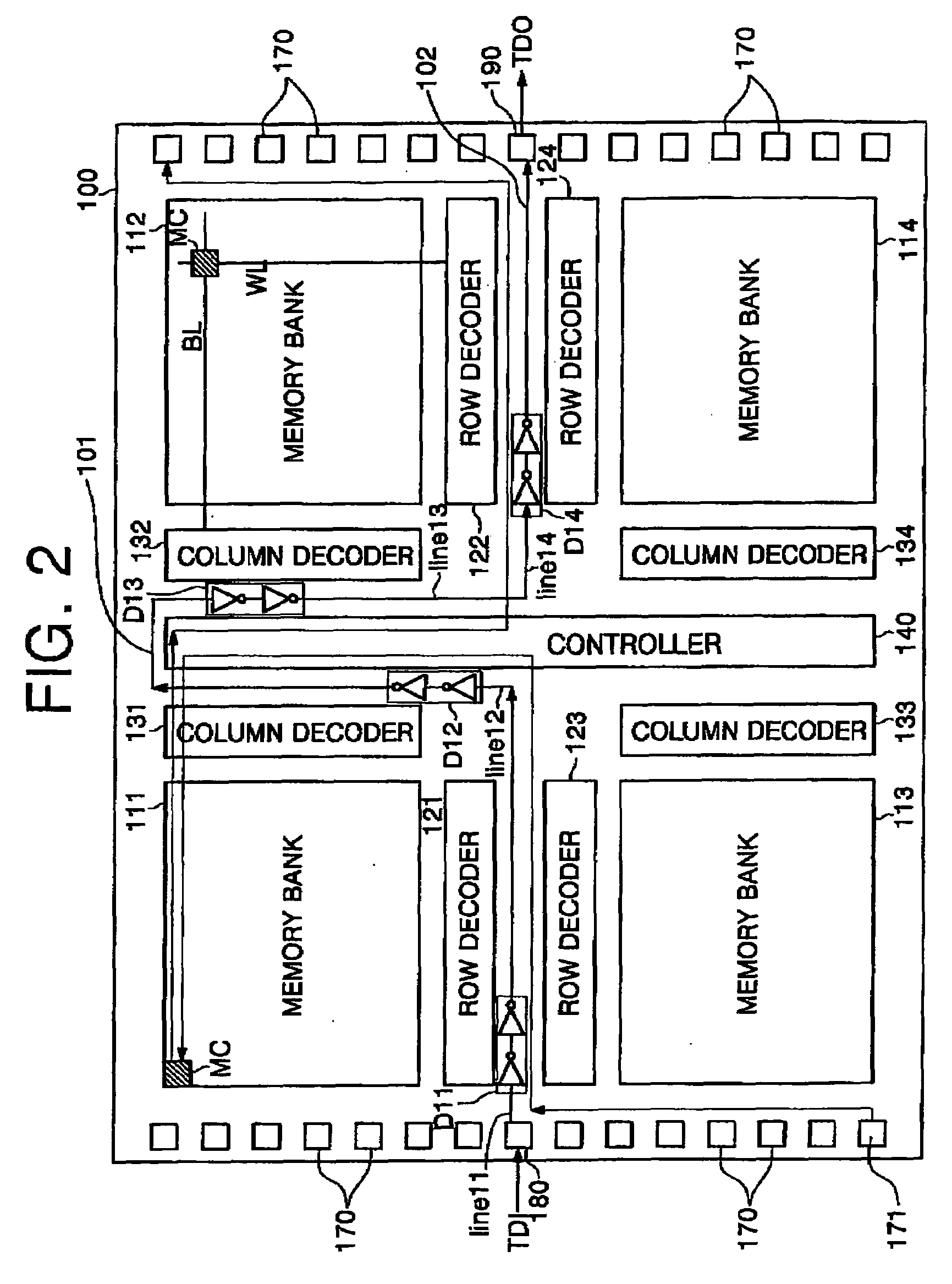

[0023]FIG. 2 is a schematic diagram illustrating a semiconductor memory chip incorporating a measuring circuit according to an embodiment of the invention. The term “chip” is used to denote a wafer level arrangement of circuits functionally enabling at least the read / write operations of the ultimately formed semiconductor memory device. Thus, a semiconductor memory chip is a wafer level fabrication of a wafer portion capable of being testing for operating speed and subsequently removed

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap