An integrated circuit chip pin performance analysis method, device and equipment and a medium

A technology of integrated circuits and analysis methods, applied in the field of computer-aided engineering, can solve the problems of time-consuming and laborious, increase R&D cost and R&D cycle, and achieve the effect of saving time, improving R&D efficiency, and shortening R&D cycle.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

[0038] Next, the technical solutions in the embodiments of the present invention will be apparent from the embodiment of the present invention, and it is clearly described, and it is understood that the described embodiments are merely embodiments of the present invention, not all of the embodiments. Based on the embodiments of the present invention, there are all other embodiments obtained without making creative labor without making creative labor premises.

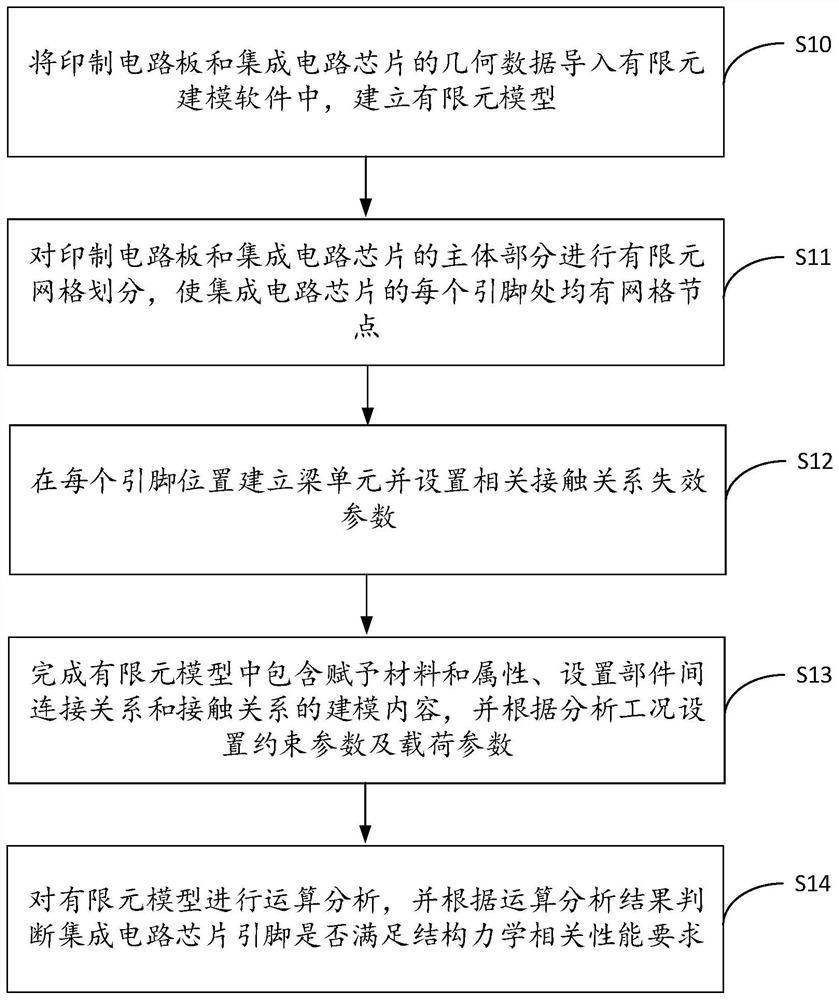

[0039] The present invention provides a performance analysis method of an integrated circuit chip pin, such as figure 1 As shown, including the following steps:

[0040] S10, introducing the geometric data of the printed circuit board and integrated circuit chip into finite element modeling software, establish finite element model;

[0041] In practical applications, the printed circuit board is an electronically connected provider of electronic components, while the integrated circuit chip includes a silicon substrate, at lea

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap