Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4 results about "Coincidence" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A coincidence is a remarkable concurrence of events or circumstances that have no apparent causal connection with one another. The perception of remarkable coincidences may lead to supernatural, occult, or paranormal claims. Or it may lead to belief in fatalism, which is a doctrine that events will happen in the exact manner of a predetermined plan.

Method for planning code word in sector of TD-SCDMA system

InactiveCN1728622AReduce the impact of interferenceImprove anti-interference abilityCode division multiplexRadio transmission for post communicationParallel computingSynchronization code division multiple access

The method includes steps: (1) calculating and storing degree of interference between each scrambling code group in all scrambling code groups and other each scrambling code group; the degree of interference indicates degree of crosscorrelation between two scrambling code groups; (2) finding out assignment of sector scrambling code group with minimal total degree of interference in TD-SCDMA system; (3) based on coincidence relation between scrambling code group and down going pilot frequency code, through assigned scrambling code group for each sector, determining down going pilot frequency code for own sector, and selecting a scrambling code for own sector. Considering disturbed condition caused from relativity between composite codes, the invention raises interference killing feature of system and lowers influence on capacity of TD-SCDMA system from interference between codes in same frequency in network.

Owner:CHINA ACAD OF TELECOMM TECH

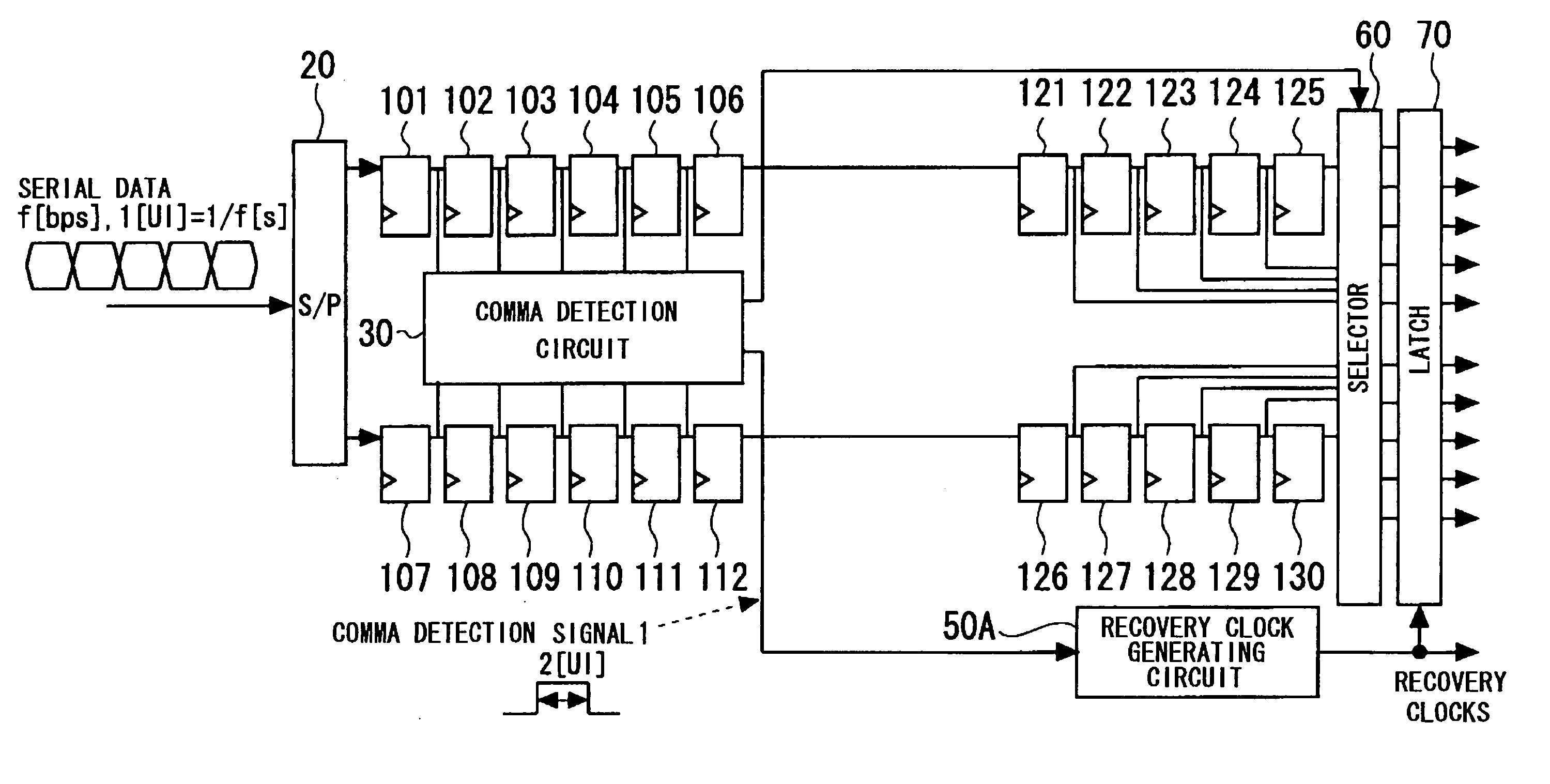

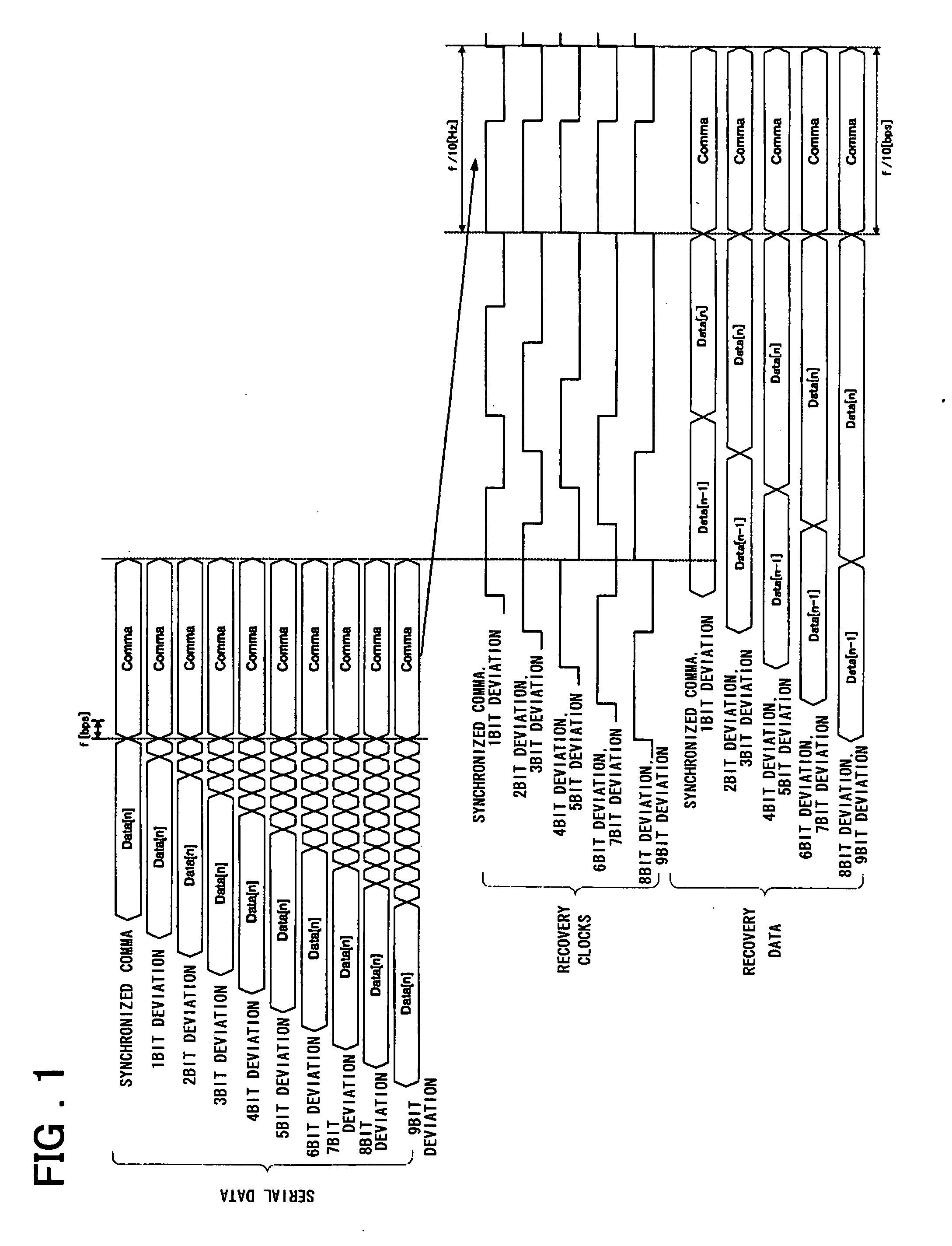

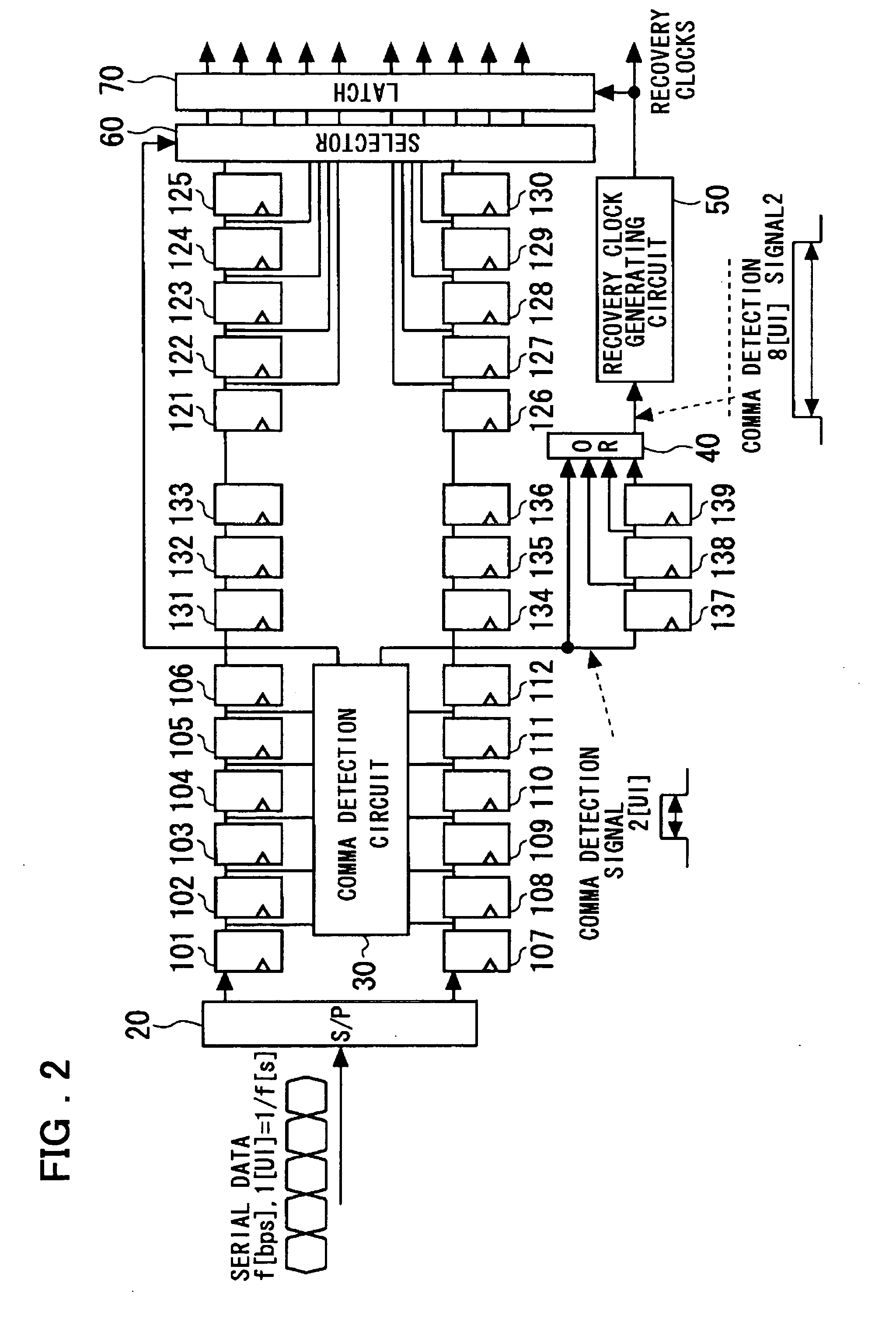

Demultiplexer circuit

InactiveUS20050220089A1Improve data transfer rateMultiplex system selection arrangementsParallel/series conversionShift registerSignal on

Owner:RENESAS ELECTRONICS CORP

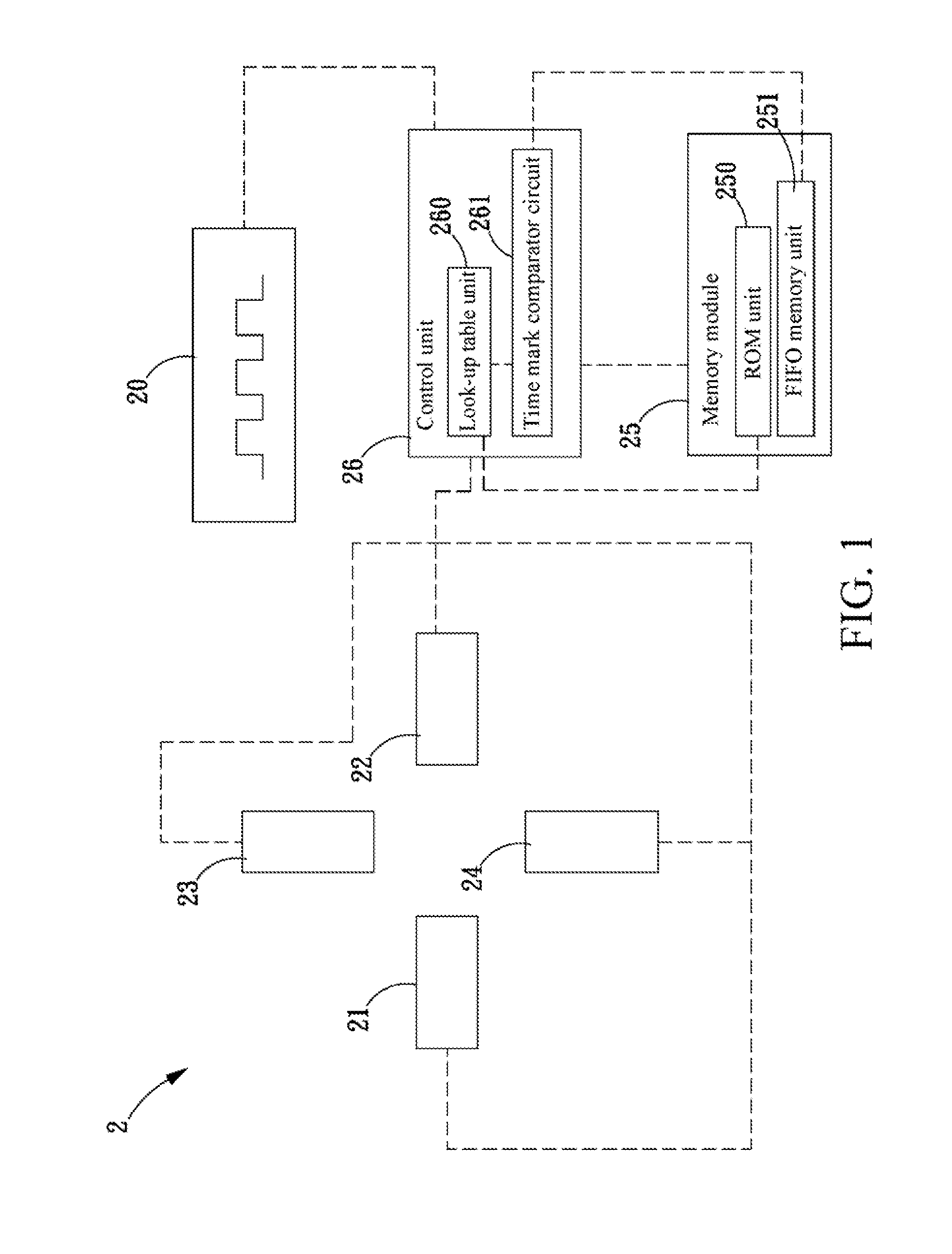

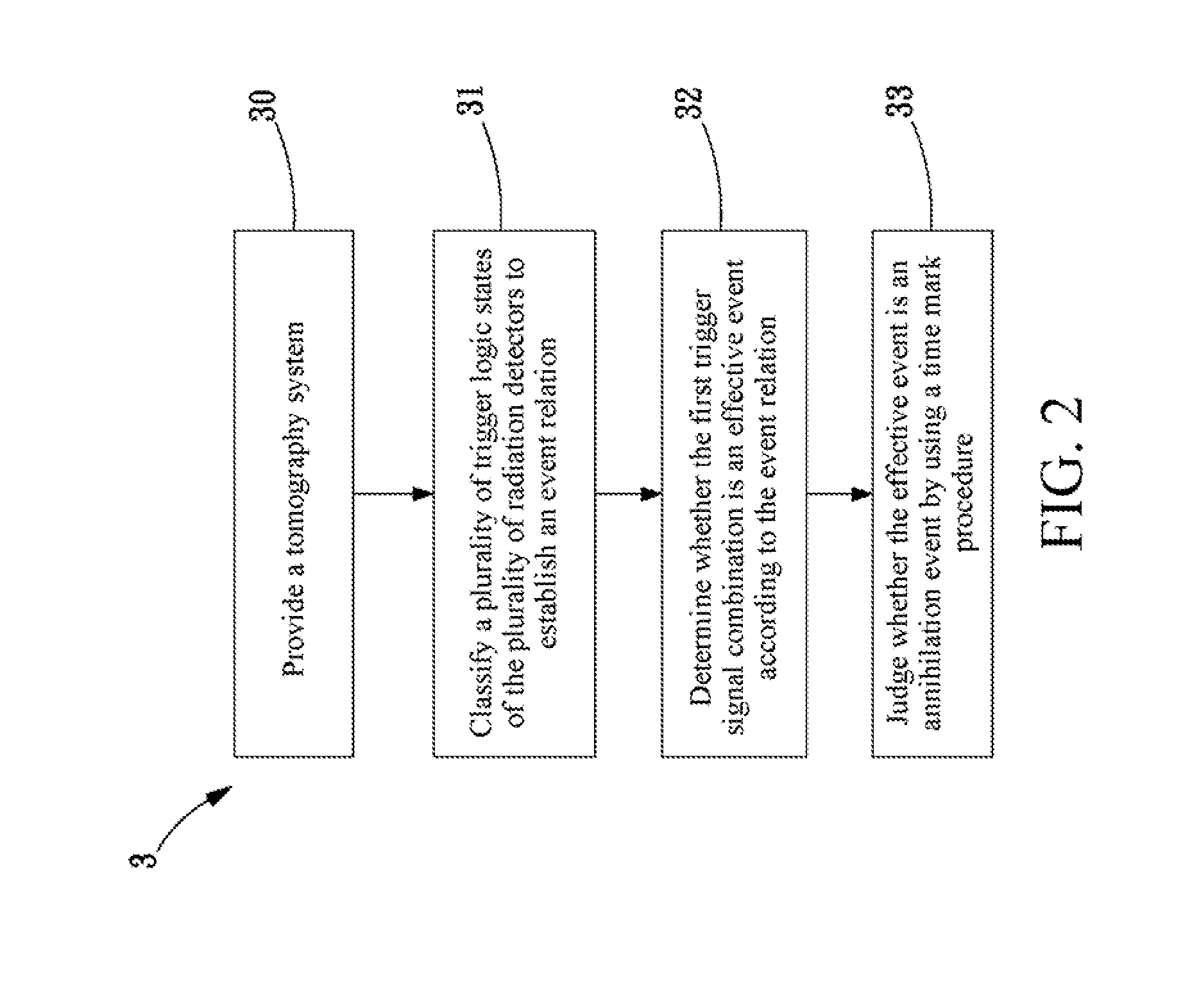

Method of coincidence detection and tomography system using the same

InactiveUS20120025091A1Material analysis by optical meansPhotometry using electric radiation detectorsTomographyCoincidence

Owner:INST NUCLEAR ENERGY RES ROCAEC

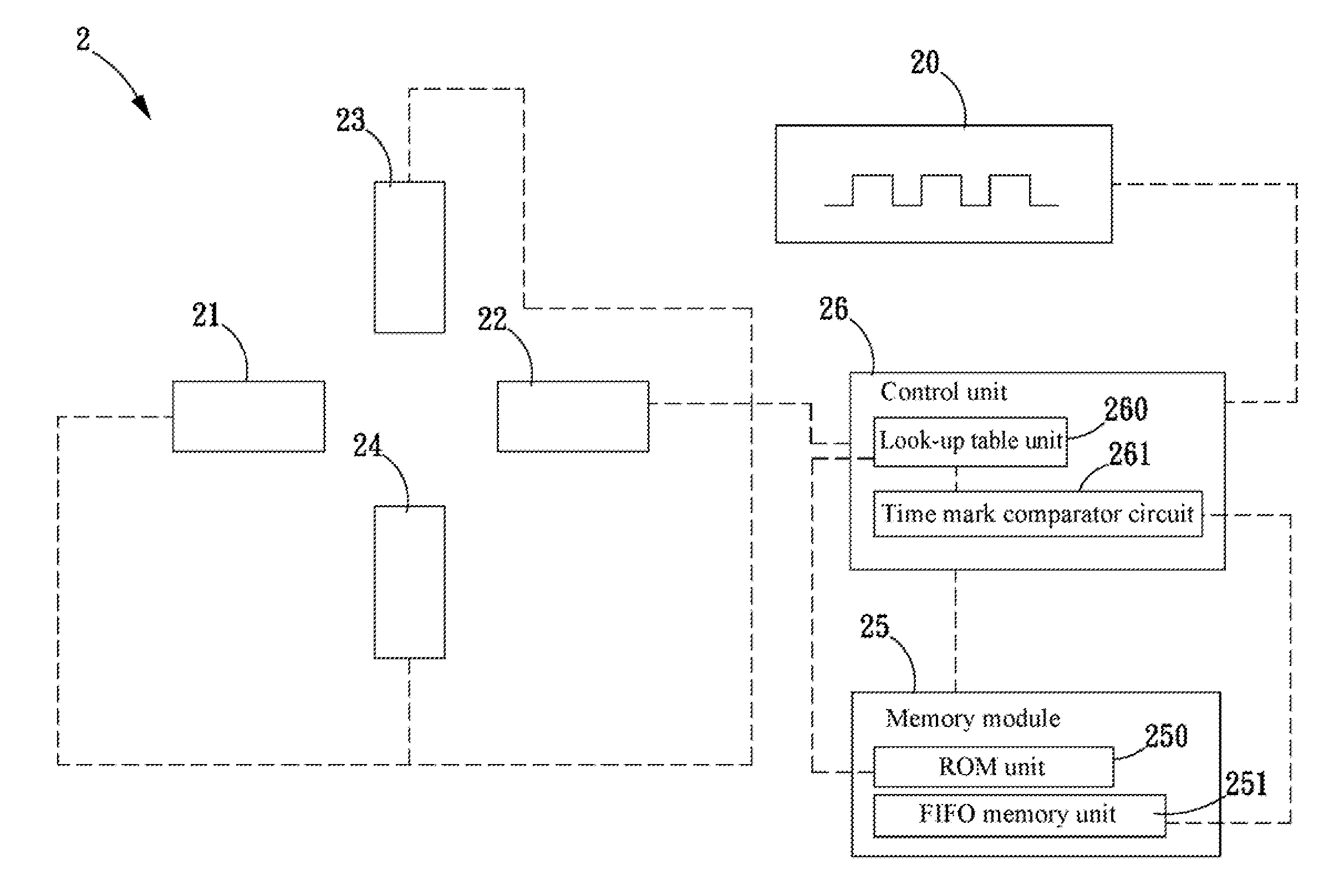

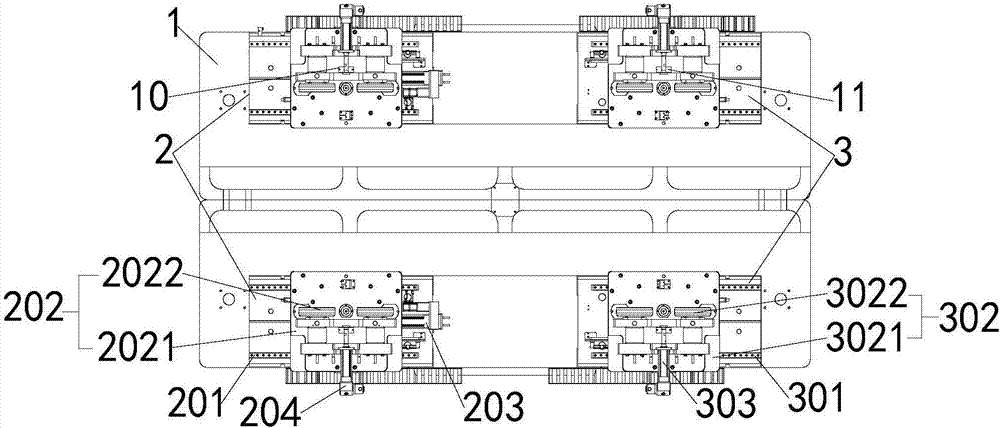

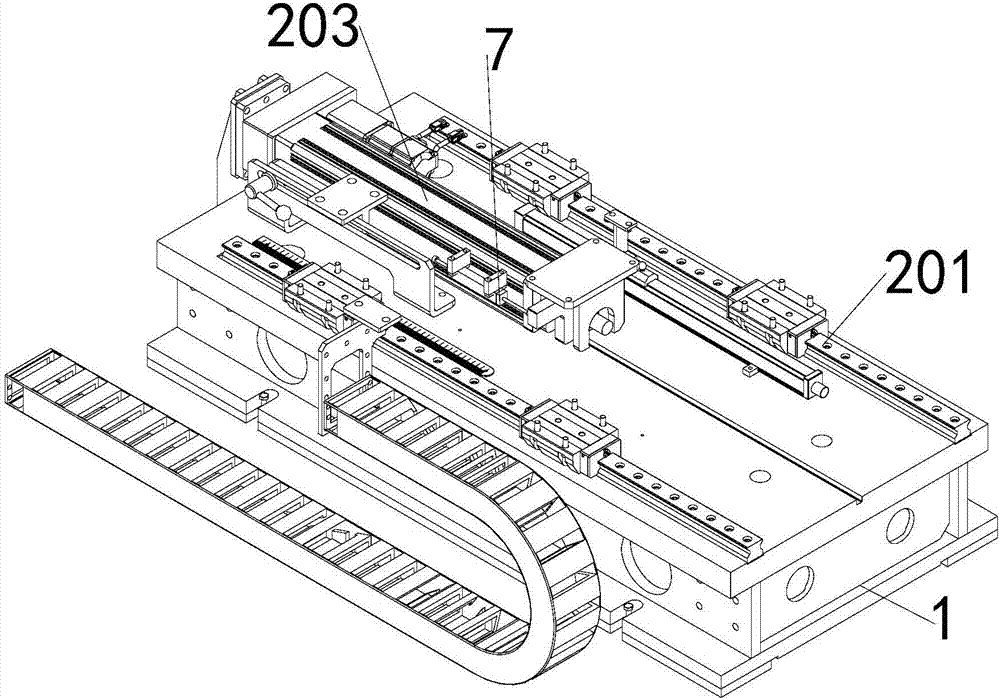

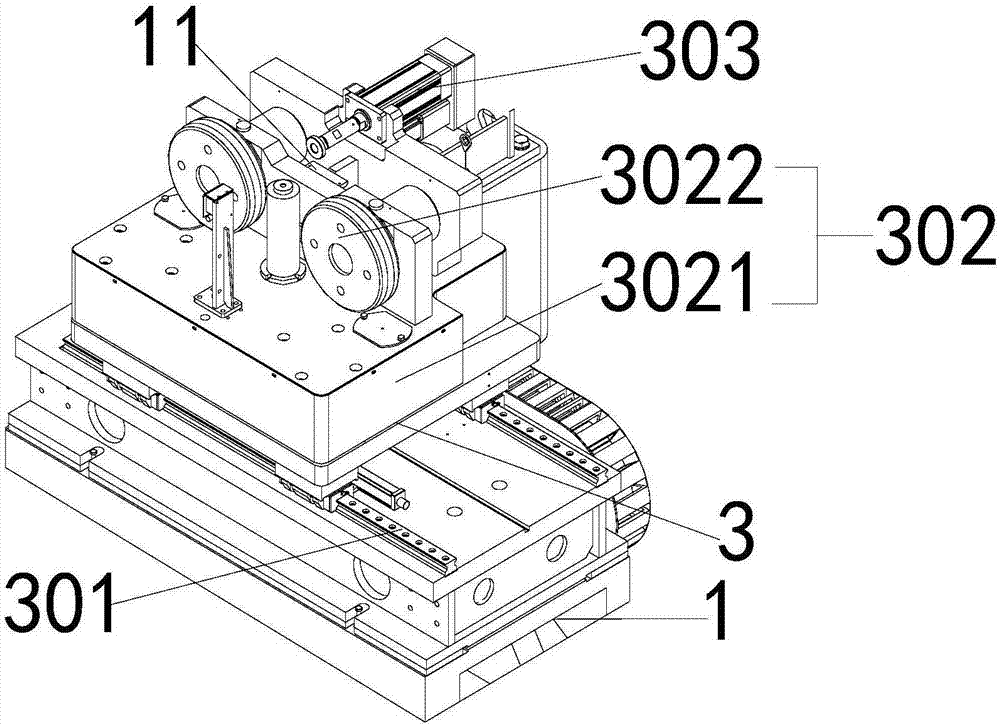

Weighing test device and bogie test system

InactiveCN107132062ARealize automatic reclosingRealize automatic adjustmentRailway vehicle testingSpecial purpose weighing apparatusBogieEngineering

Owner:CRRC QINGDAO SIFANG ROLLING STOCK RES INST +1

Popular searches

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap