Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3 results about "Control delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

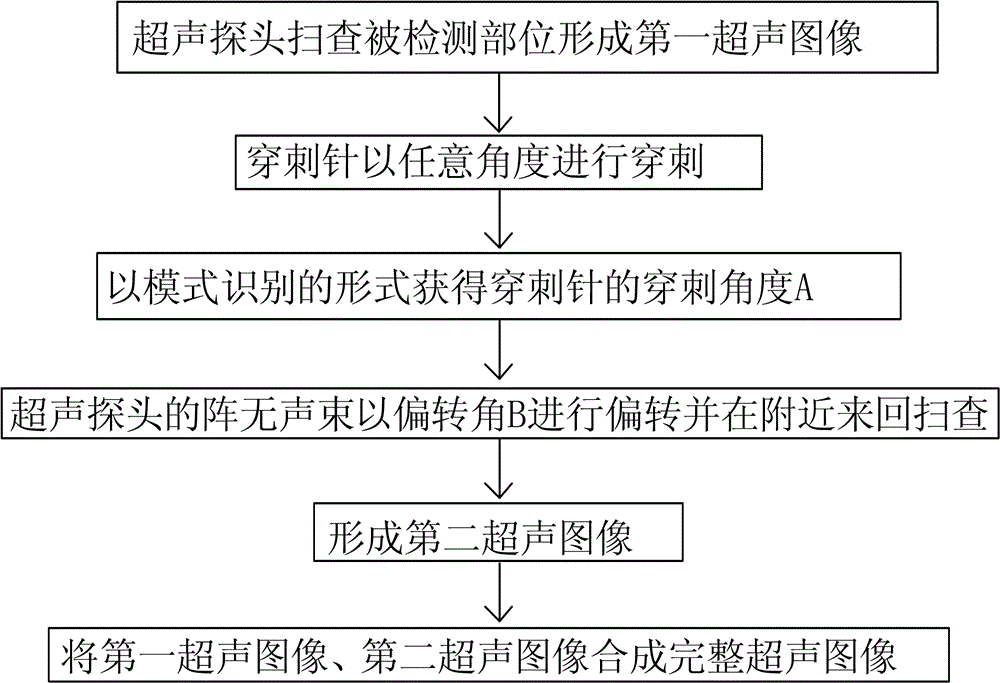

Full-automatic puncture needle developing enhancing method based on pattern recognition

InactiveCN105596030AEcho signal enhancementPuncture work without any restrictionsSurgical navigation systemsInfrasonic diagnosticsMedicineRadiology

Owner:SHANTOU INST OF UITRASONIC INSTR CO LTD

Pulse Signal transforming delay regulating circuit

InactiveCN1388648AEliminate delaysEliminate coupling noiseSingle output arrangementsPulse shapingPhase detectorEngineering

A delay circuit has an input node receiveing an input pulsed signal. A buffer transfers the input signal to a floating node. A detector outputs to an output node an output voltage that has a first level, if the voltage at the floating node is below a threshold, and a second level otherwise. Two similar branches are used, one for controlling delays in the rising transitions and one for controlling delays in the falling transitions. For each branch, a reference terminal carries a reference voltage for biasing the floating node. A capacitor and a switch are coupled between the reference terminal and the floating node. The switch opens and closes responsive to the output voltage. When it opens, it shorts out the capacitor. An optional phase detector and delay code generator may be in a feedback arrangement, for continuously adjusting the reference voltages.

Owner:SAMSUNG ELECTRONICS CO LTD

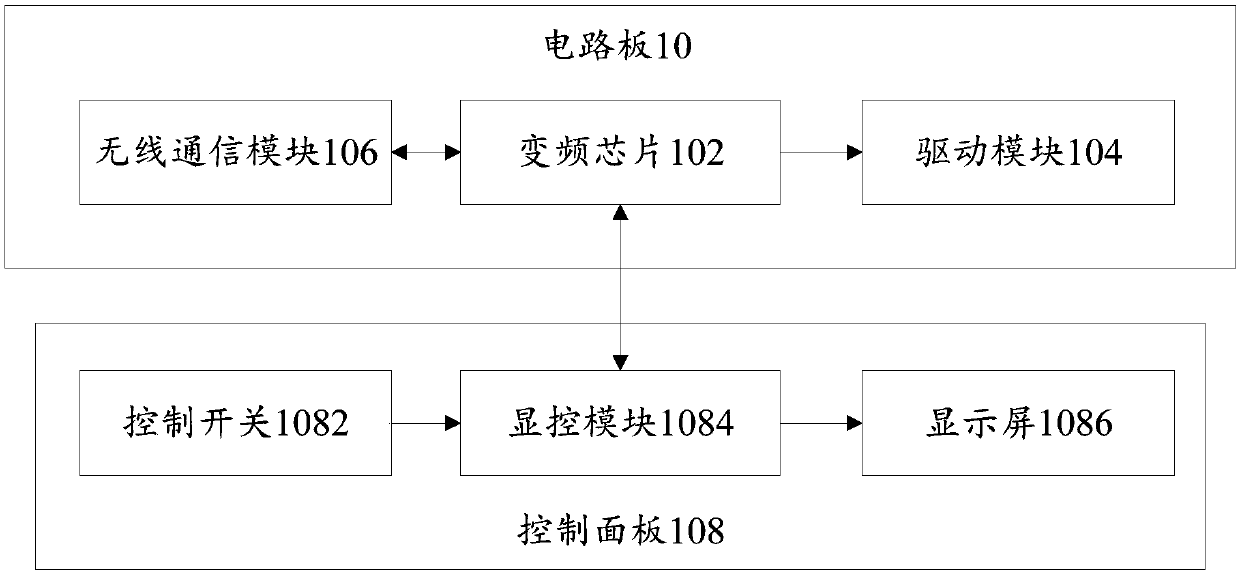

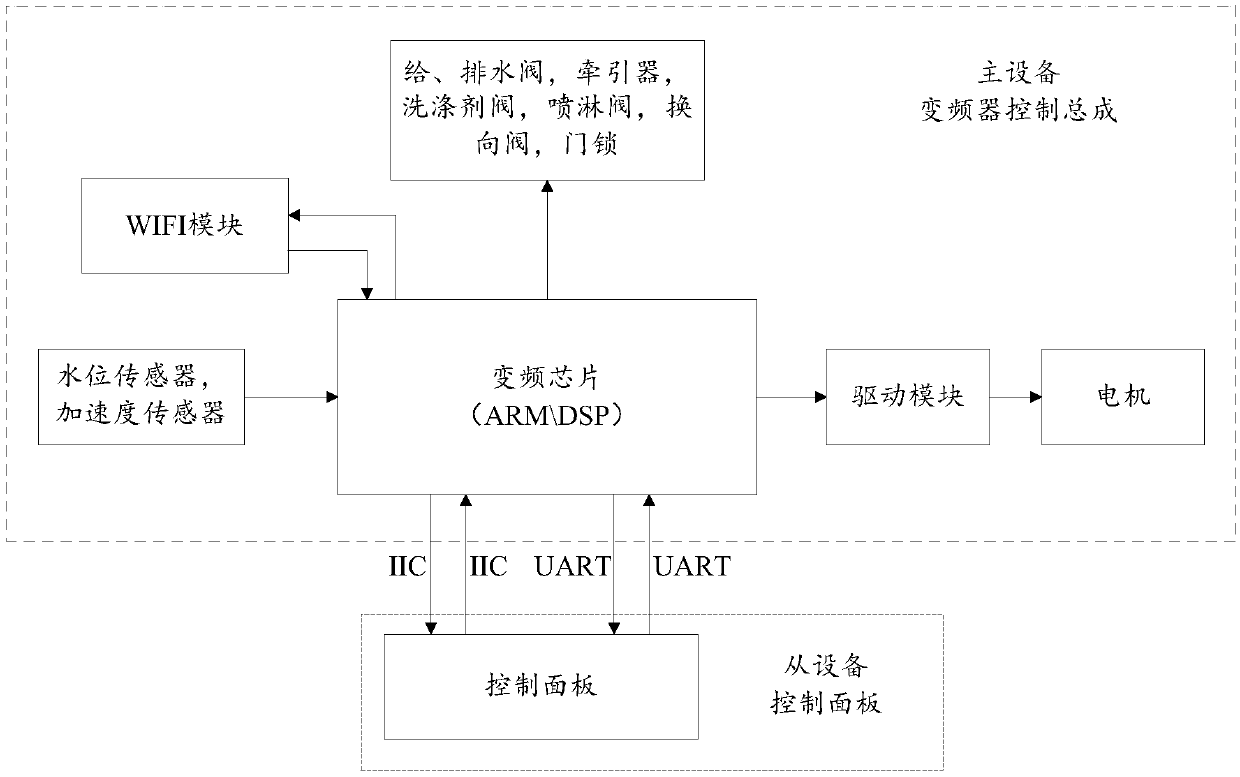

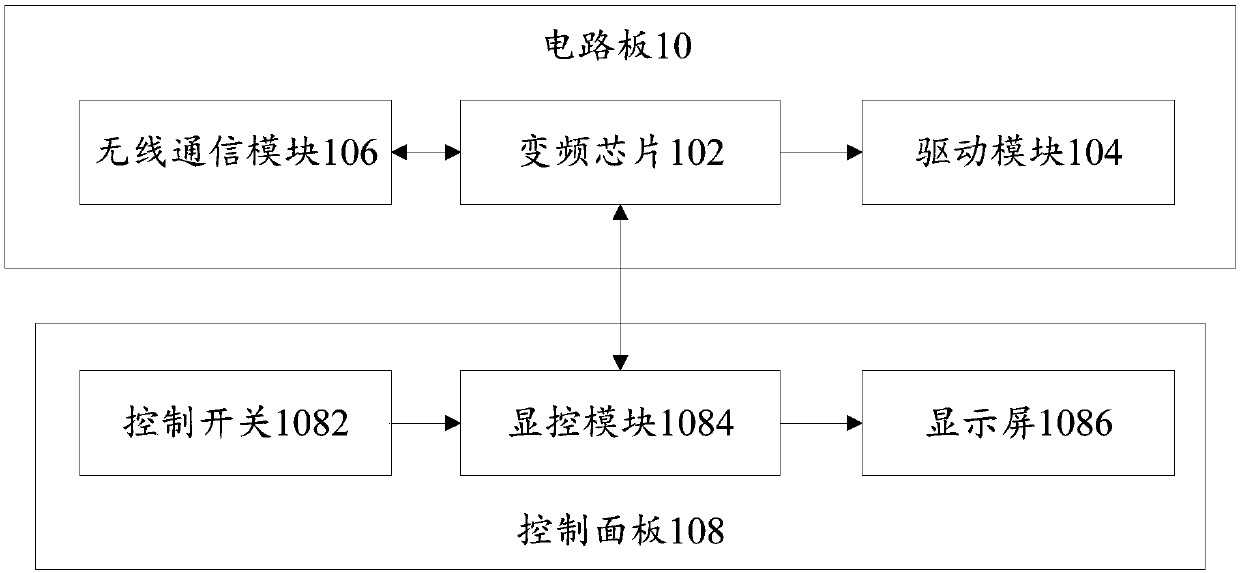

Control device and washing machine

PendingCN111118822AOther washing machinesControl devices for washing apparatusLaundry washing machineFrequency conversion

Owner:WUXI FILIN ELECTRONICS CO LTD

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap