Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

6 results about "Phase detector" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A phase detector or phase comparator is a frequency mixer, analog multiplier or logic circuit that generates a voltage signal which represents the difference in phase between two signal inputs. It is an essential element of the phase-locked loop (PLL).

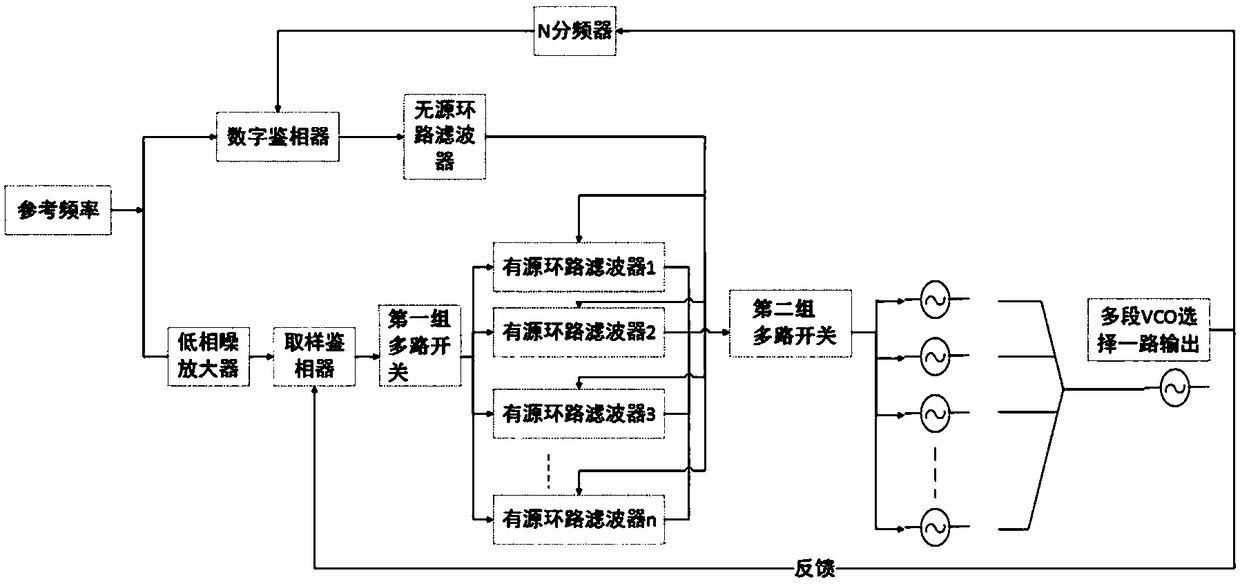

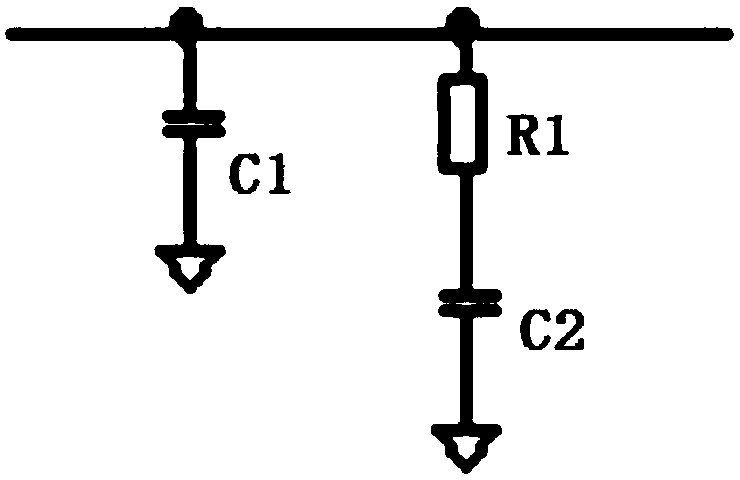

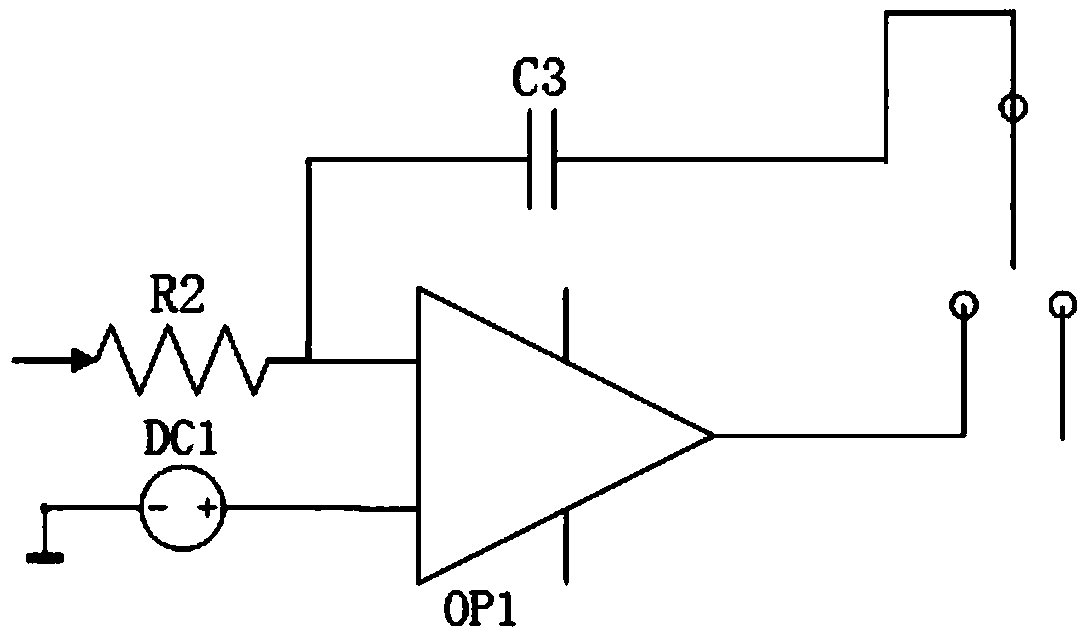

A low phase noise broadband microwave frequency source circuit

ActiveCN109088634AReduce phase noiseAchieve the effect of low phase noisePulse automatic controlLoop filterPhase detector

Owner:SOUTHEAST UNIV

Pulse Signal transforming delay regulating circuit

InactiveCN1388648AEliminate delaysEliminate coupling noiseSingle output arrangementsPulse shapingPhase detectorEngineering

A delay circuit has an input node receiveing an input pulsed signal. A buffer transfers the input signal to a floating node. A detector outputs to an output node an output voltage that has a first level, if the voltage at the floating node is below a threshold, and a second level otherwise. Two similar branches are used, one for controlling delays in the rising transitions and one for controlling delays in the falling transitions. For each branch, a reference terminal carries a reference voltage for biasing the floating node. A capacitor and a switch are coupled between the reference terminal and the floating node. The switch opens and closes responsive to the output voltage. When it opens, it shorts out the capacitor. An optional phase detector and delay code generator may be in a feedback arrangement, for continuously adjusting the reference voltages.

Owner:SAMSUNG ELECTRONICS CO LTD

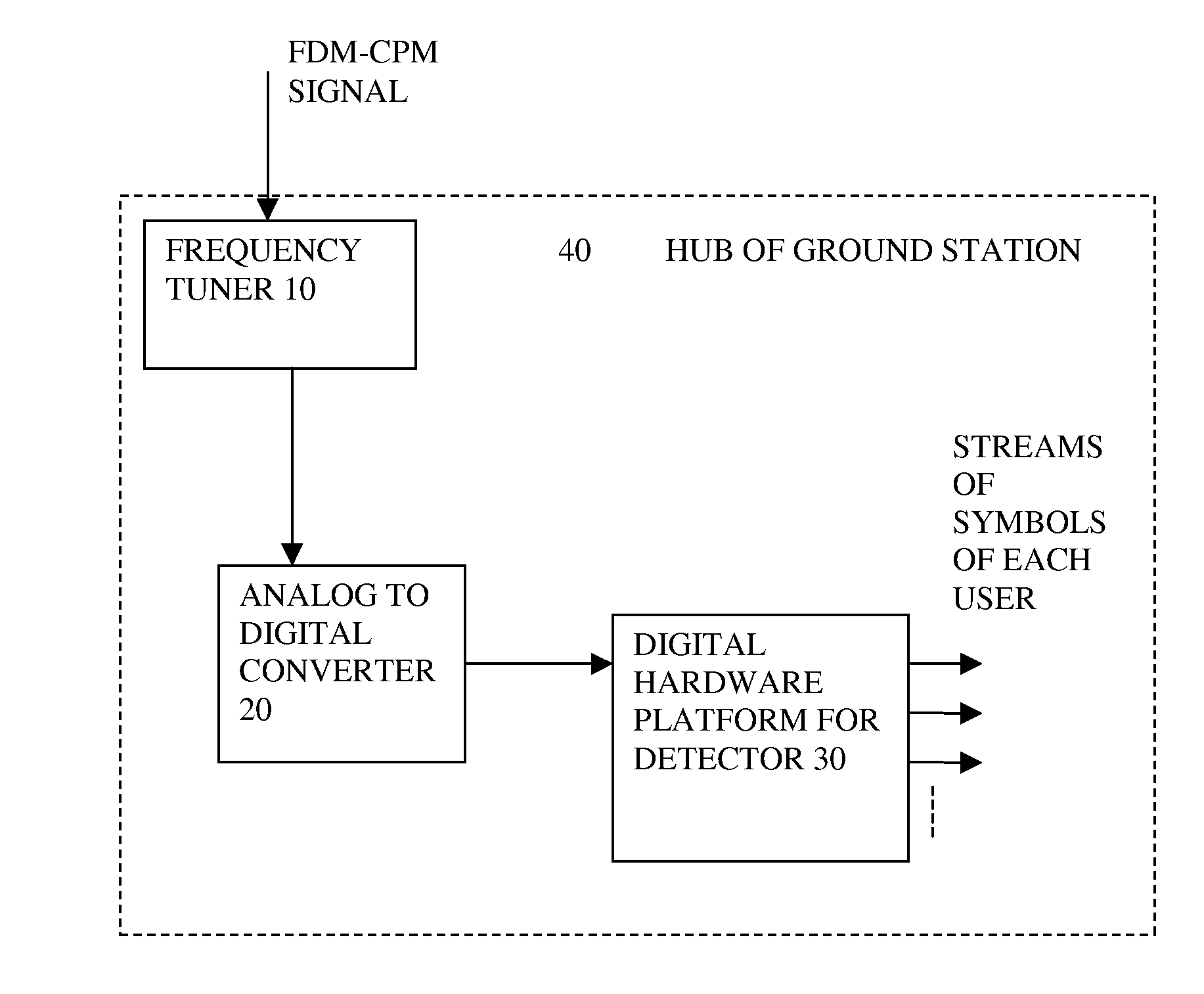

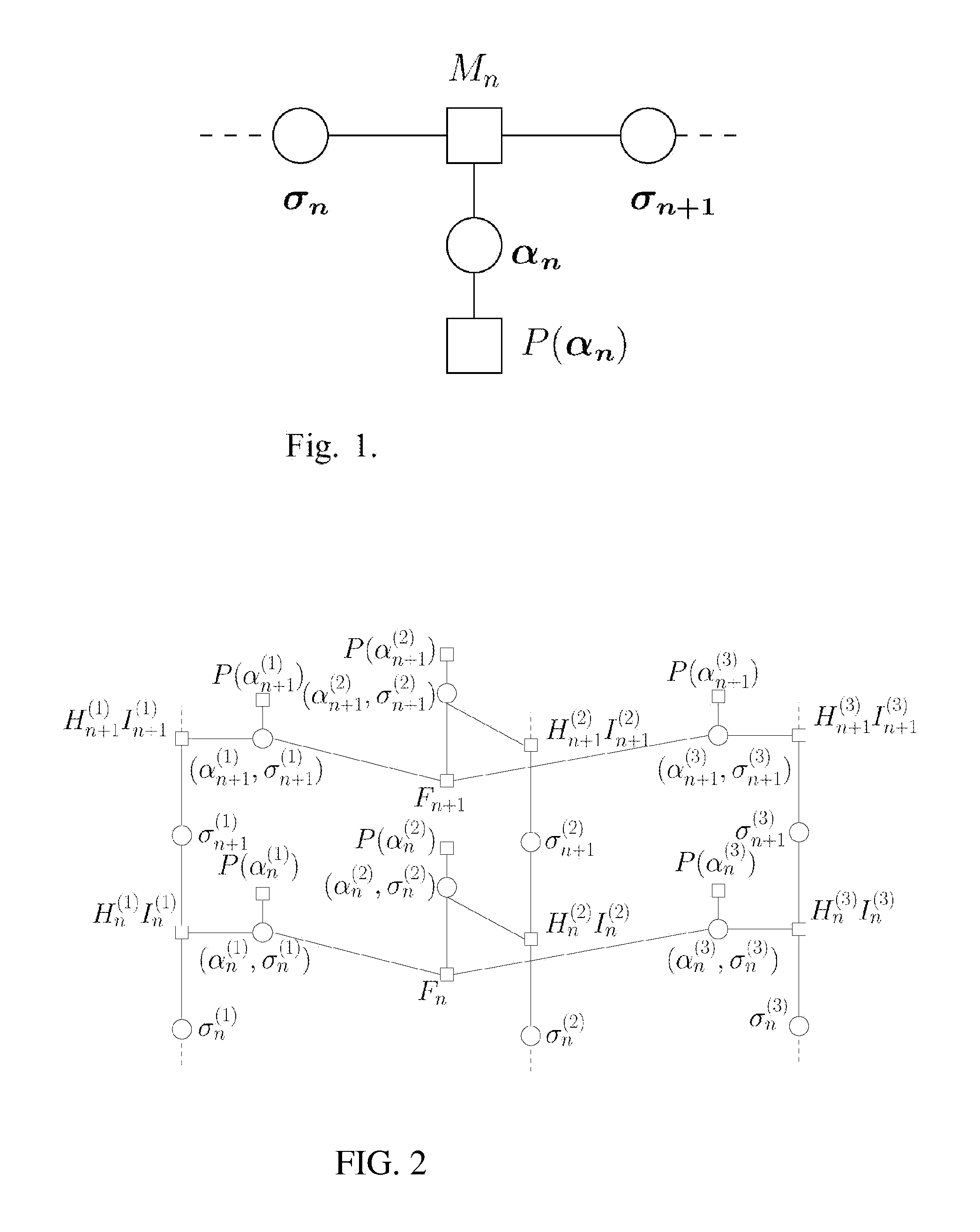

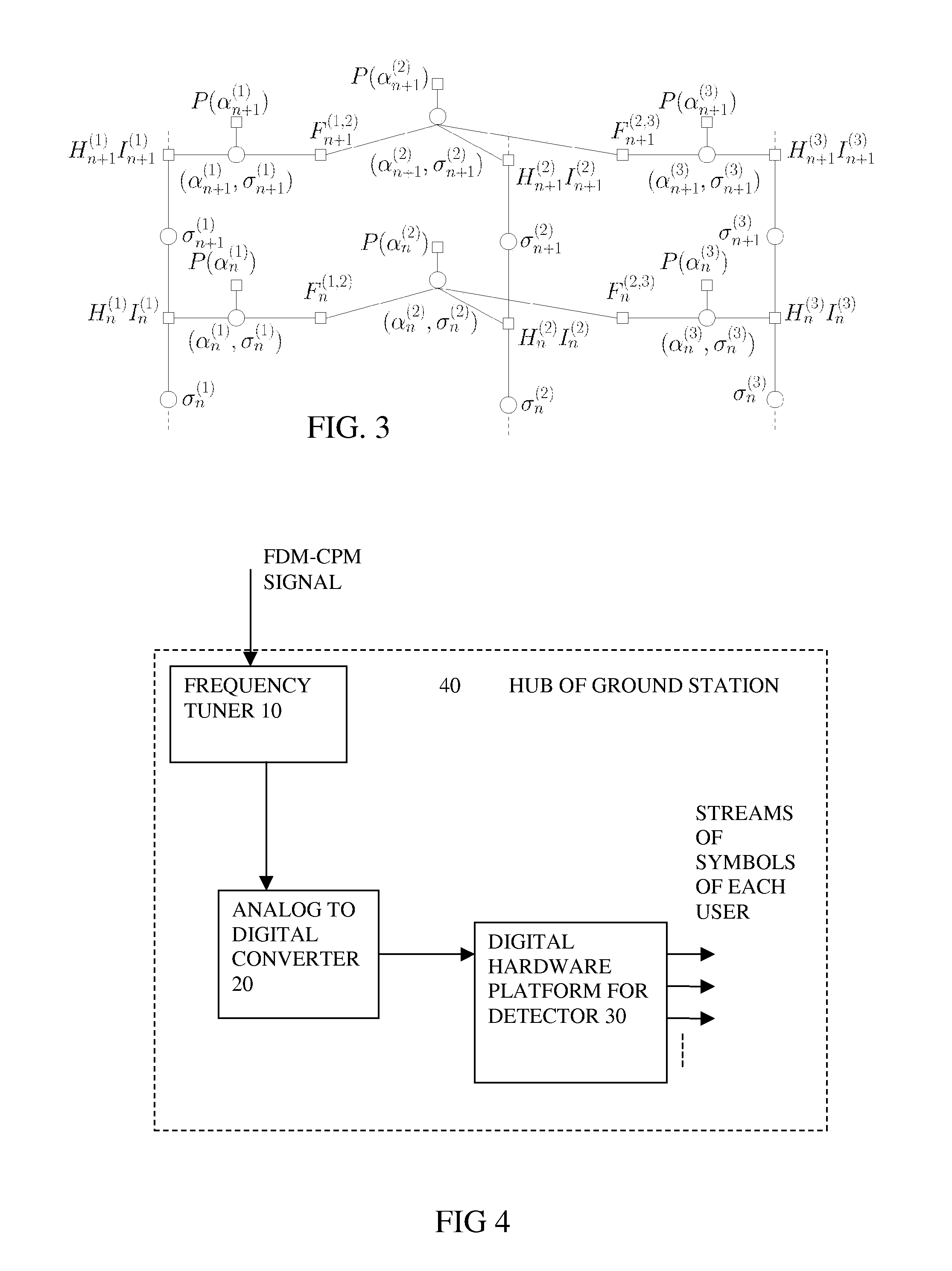

Reduced complexity fdm-cpm dectector with multiple access interference cancellation

InactiveUS20120098612A1Reduce complexityReduce degradationModulated-carrier systemsAngle modulationPhase detectorExponential complexity

Owner:NEWTEC CY

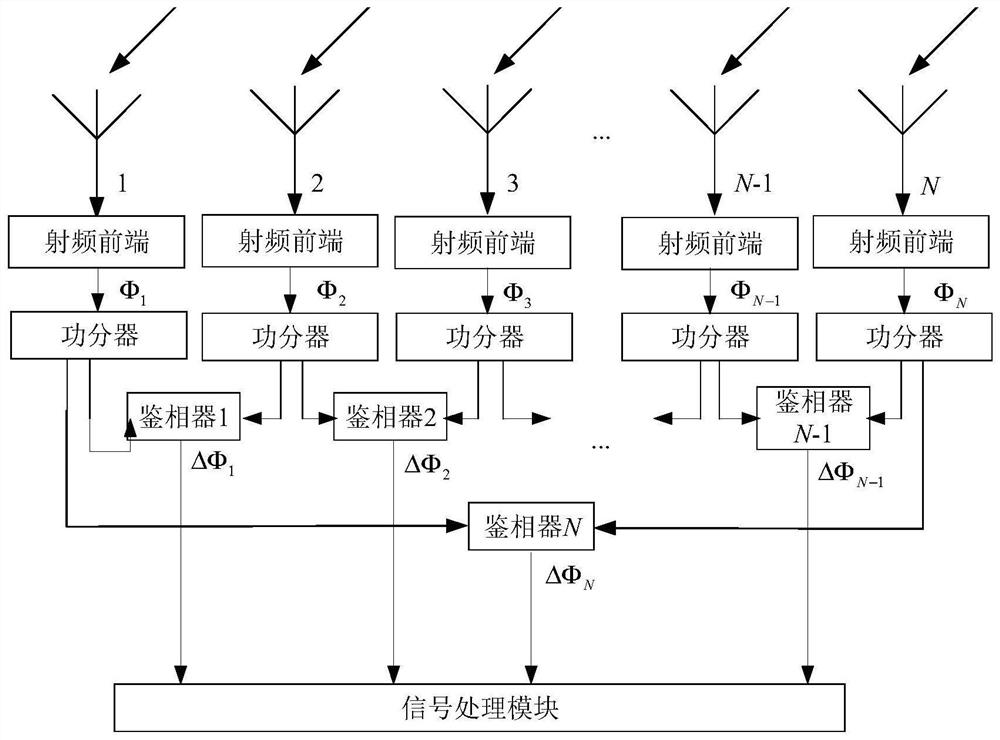

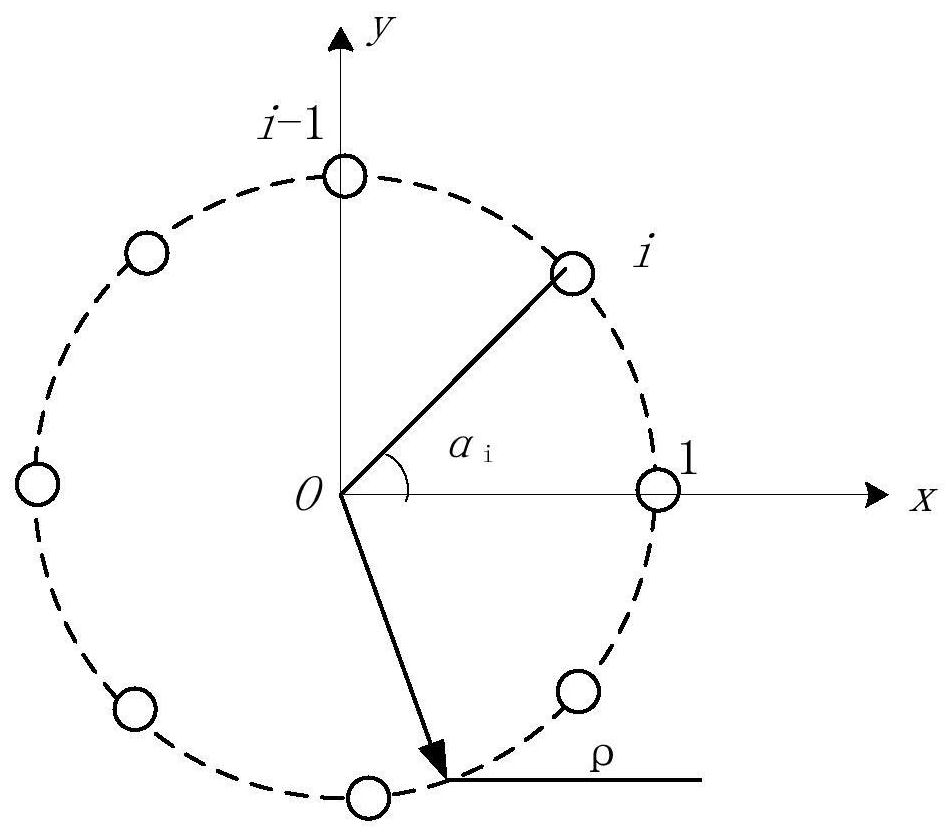

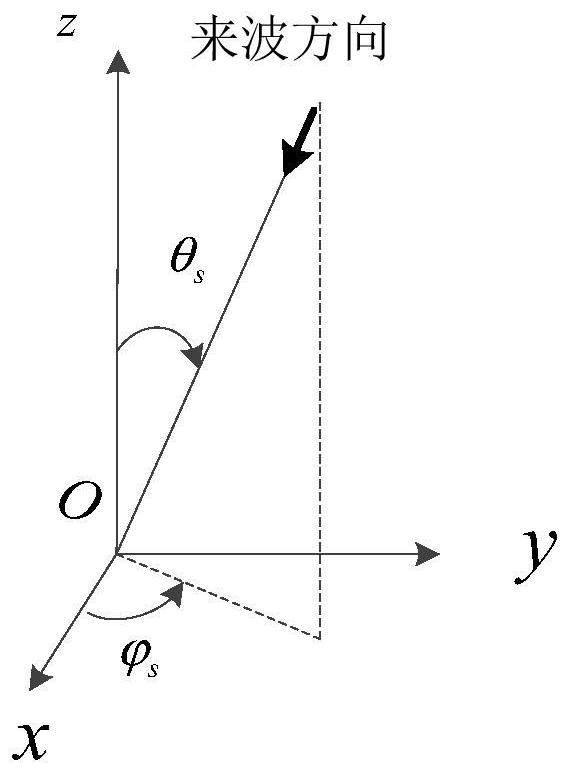

Direction finding method and system based on radio frequency analog receiving system

ActiveCN111693936AAvoid the problem of unbalanced input signal amplitudeSolving Phase Blur ProblemsRadio wave finder detailsPhase detectorEngineering

Owner:SOUTHWEST CHINA RES INST OF ELECTRONICS EQUIP

Phase locked loop with dual input reference and dynamic bandwidth control

Systems and methods for improved performance of phase-locked loop-based clock generators, particularly in the context of wireless audio, are disclosed herein. The PLL clock generator includes: a PLL core configured to receive a module reference clock provided by the communication module and generate a subsystem data clock corresponding to a module data clock of the communication module; and a data clock tracker module configured to receive the module data and the subsystem data clock and determine a corresponding data clock correction factor. In this way, the bandwidth of the PLL core can be dynamically changed, thereby achieving fast and very precise stabilization. The PLL core may use a low jitter frequency reference for the phase detector while using a synchronized and easily jitter audio sampling clock to ensure that the average frequency of the PLL core tracks the audio sampling clock.

Owner:SYNAPTICS INC

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap