Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3 results about "Clock correction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

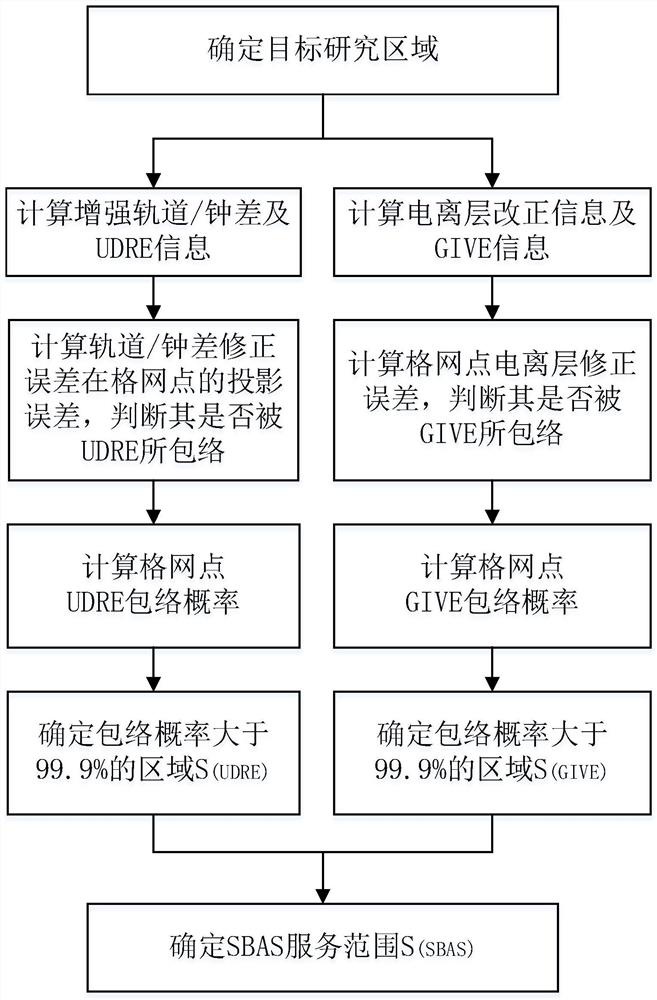

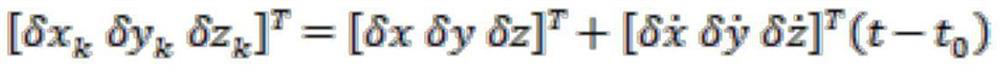

Method for determining service range of satellite-based augmentation system

PendingCN114152962AReasonable handlingImprove processing efficiencySatellite radio beaconingClock correctionIonosphere

Owner:NO 20 RES INST OF CHINA ELECTRONICS TECH GRP

Phase locked loop with dual input reference and dynamic bandwidth control

Systems and methods for improved performance of phase-locked loop-based clock generators, particularly in the context of wireless audio, are disclosed herein. The PLL clock generator includes: a PLL core configured to receive a module reference clock provided by the communication module and generate a subsystem data clock corresponding to a module data clock of the communication module; and a data clock tracker module configured to receive the module data and the subsystem data clock and determine a corresponding data clock correction factor. In this way, the bandwidth of the PLL core can be dynamically changed, thereby achieving fast and very precise stabilization. The PLL core may use a low jitter frequency reference for the phase detector while using a synchronized and easily jitter audio sampling clock to ensure that the average frequency of the PLL core tracks the audio sampling clock.

Owner:SYNAPTICS INC

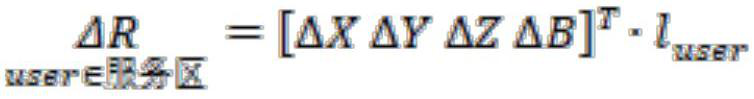

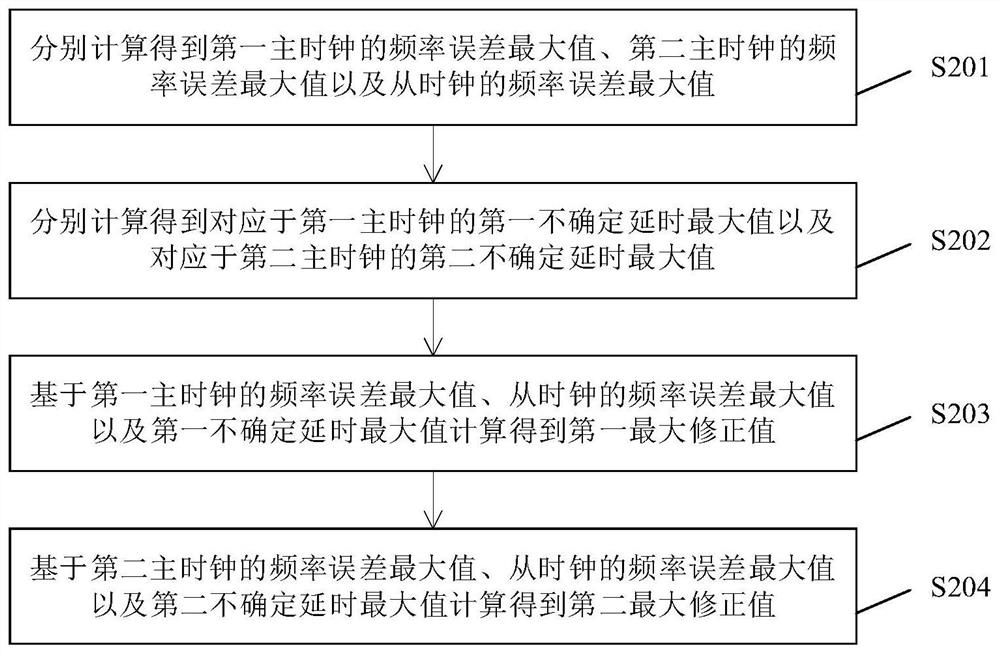

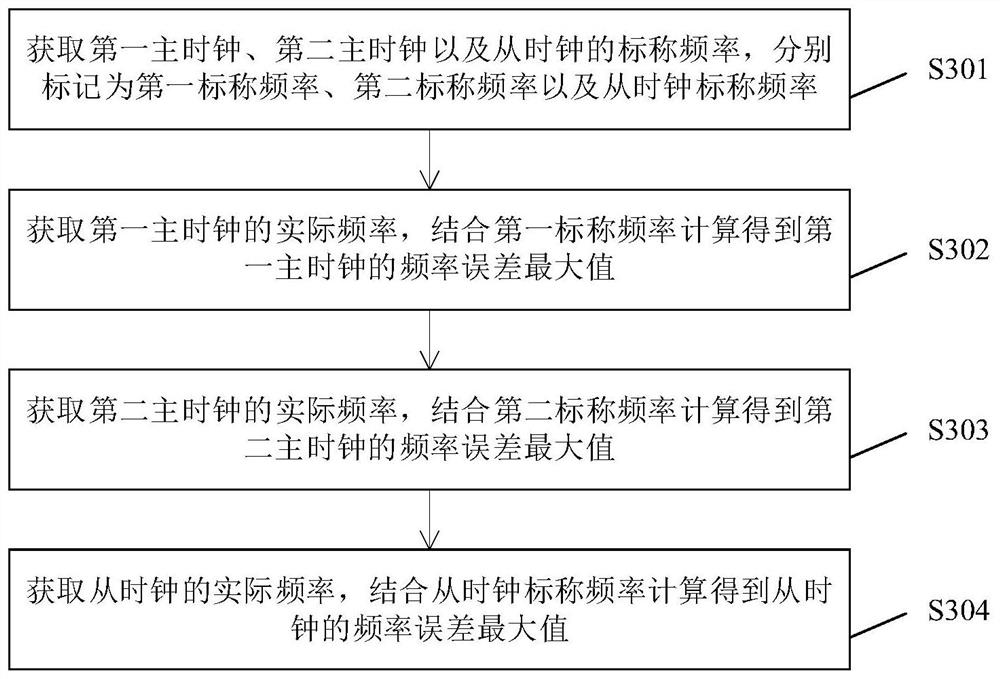

Clock synchronization and fault feedback method and device

Owner:CSR ZHUZHOU ELECTRIC LOCOMOTIVE RES INST

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap