Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4 results about "Gate control" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Non-key gate control system

InactiveCN101343961AExtended service lifeImprove securityElectric permutation locksMicrocontrollerSystem controller

The invention relates to a keyless gate controlling system. The keyless gate controlling system comprises a keyless system controller utilizing the cipher mode of mutual identification verification, a carrying card, and a receiving and transmitting antenna, the keyless system controller positioned at a car body end comprises a low frequency transmitting circuit connected with a singlechip and a high frequency receiving circuit; the carrying card adopts an identification verification card which comprises a low frequency receiving circuit connected with a microprocessor and a high frequency transmitting circuit; by adopting the keyless gate controlling system, the problem that the great inconvenience brought to users due to the car door opening mode through directly using a key or a remote controller is solved.

Owner:SHANGHAI SICAR VEHICLE TECH DEV

Timing controller, display device including the same, and method of driving the same

ActiveUS20170345375A1Reduce oneInternal logic is simplifiedCathode-ray tube indicatorsData controlControl signal

A timing controller includes an input signal processor that receives a data enable signal and a frame frequency information signal, generates one of a first internal data enable signal having a first frame frequency and a second internal data enable signal having a second frame frequency, the first and second frame frequencies being selected based on the frame frequency information signal. A gate control signal output unit generates and outputs a first gate control signal based on the first internal data enable signal or a second gate control signal based on the second internal data enable signal. A data control signal output unit generates and outputs a first data control signal based on the first internal data enable signal or a second data control signal based on the second internal data enable signal. The pulse widths of the first and second internal data enable signals are the same.

Owner:LG DISPLAY CO LTD

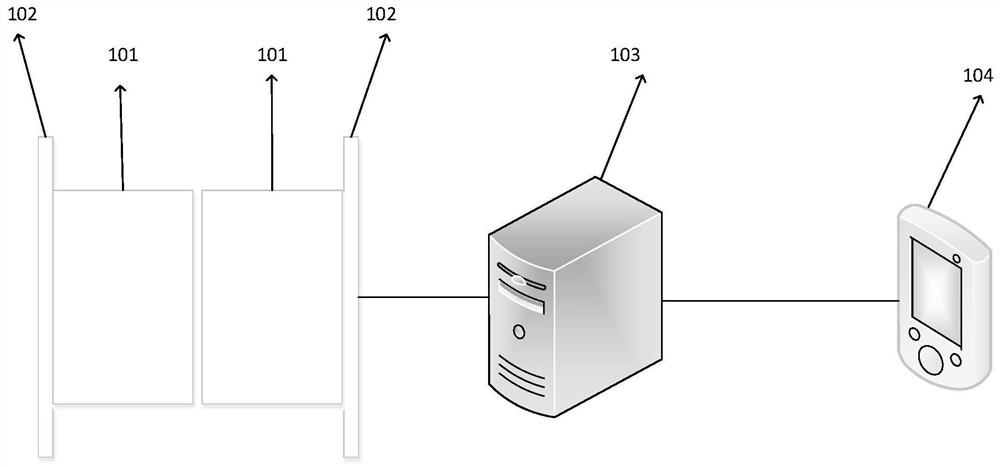

Gate control system

PendingCN113450483AEffective controlEasy to controlIndividual entry/exit registersTraffic restrictionsControl systemEngineering

Owner:广州欧轩网络科技有限公司

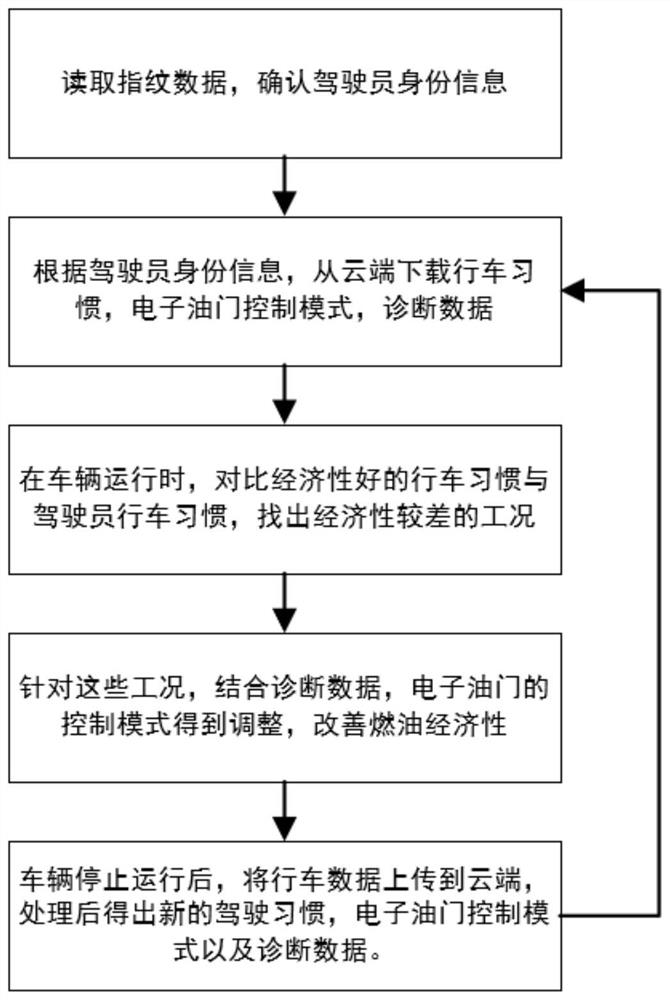

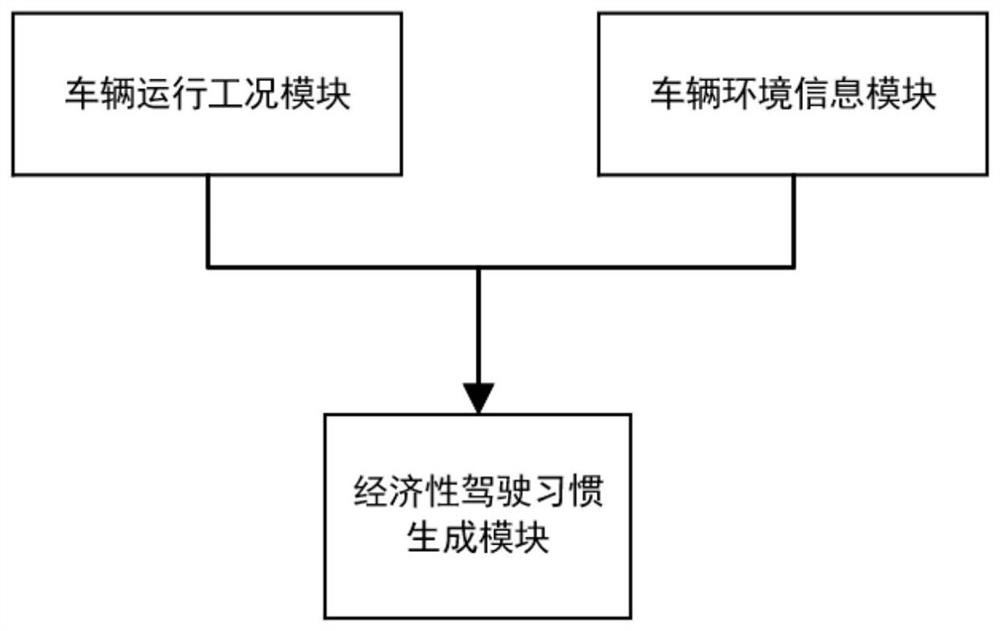

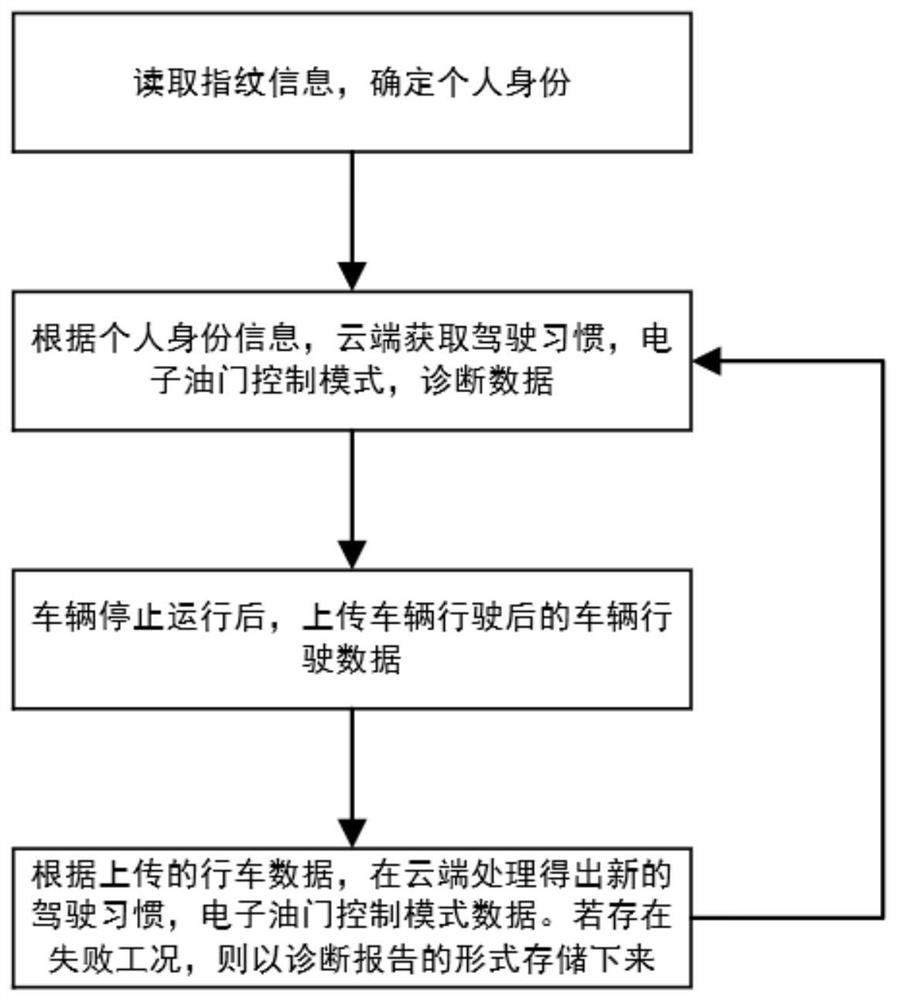

Electronic throttle control mode adjusting method based on driving habits of driver

InactiveCN112319487AImprove economyDoes not change the driving experienceData processing managementControl devicesDriver/operatorElectronic throttle control

Owner:江苏紫琅汽车集团股份有限公司

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap