Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3 results about "Logical address" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

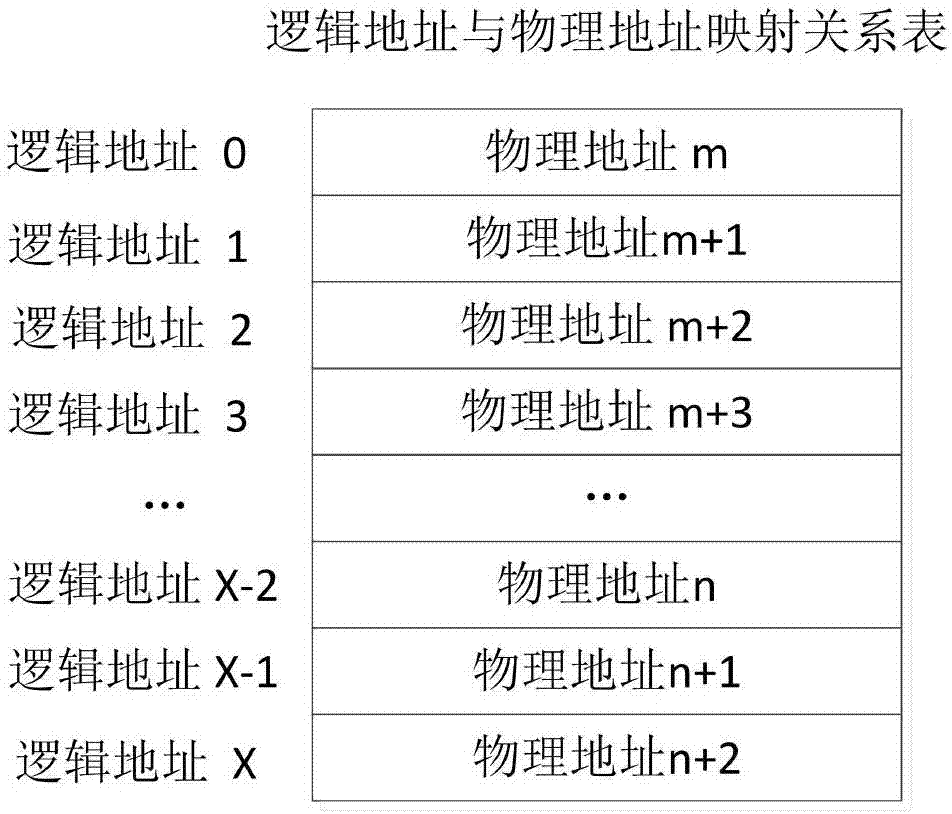

In computing, a logical address is the address at which an item (memory cell, storage element, network host) appears to reside from the perspective of an executing application program. A logical address may be different from the physical address due to the operation of an address translator or mapping function. Such mapping functions may be, in the case of a computer memory architecture, a memory management unit (MMU) between the CPU and the memory bus.

Flash memory management method and flash memory device

ActiveCN102841851AIncrease write speedIncrease profitMemory adressing/allocation/relocationLogical addressCopy move

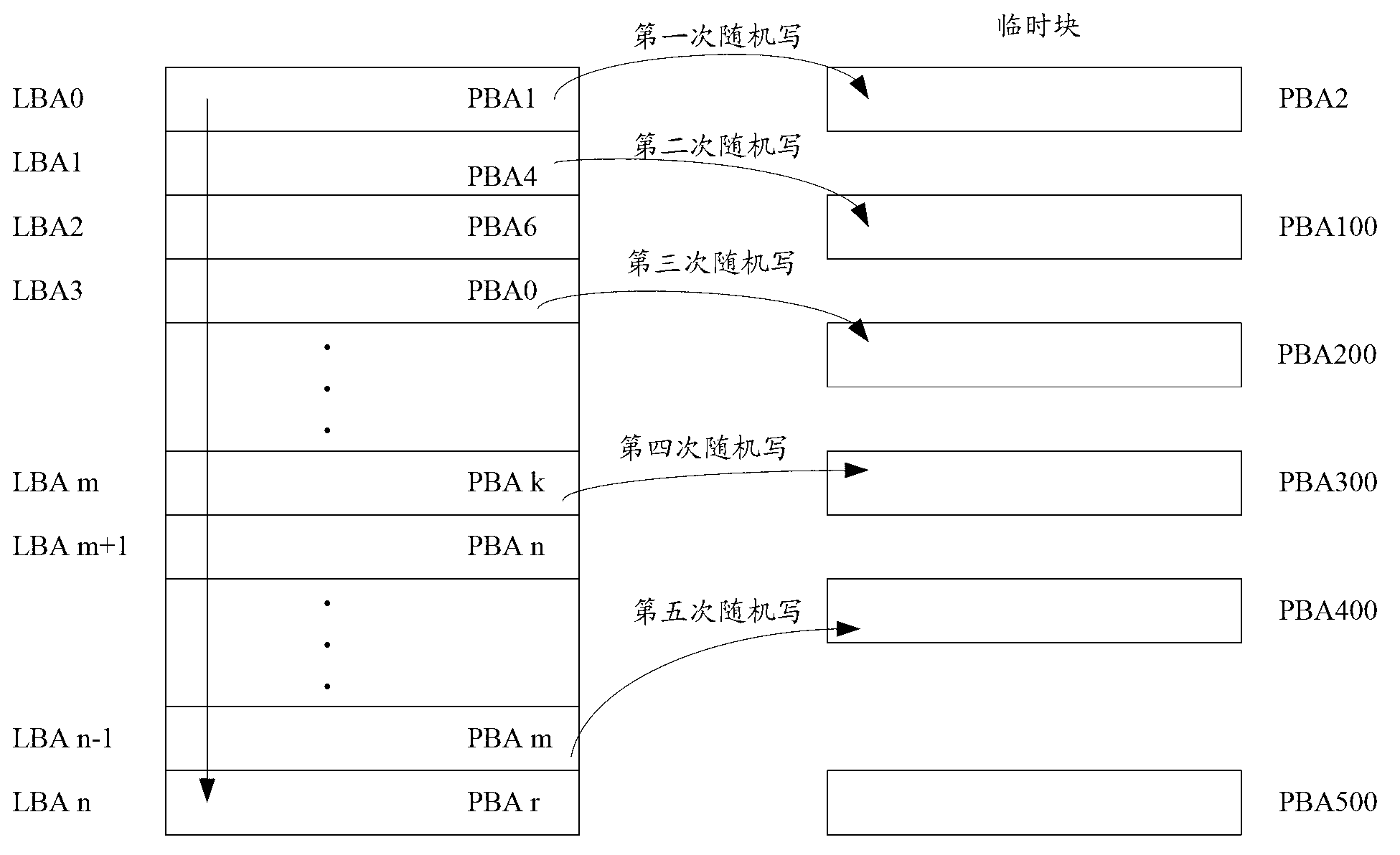

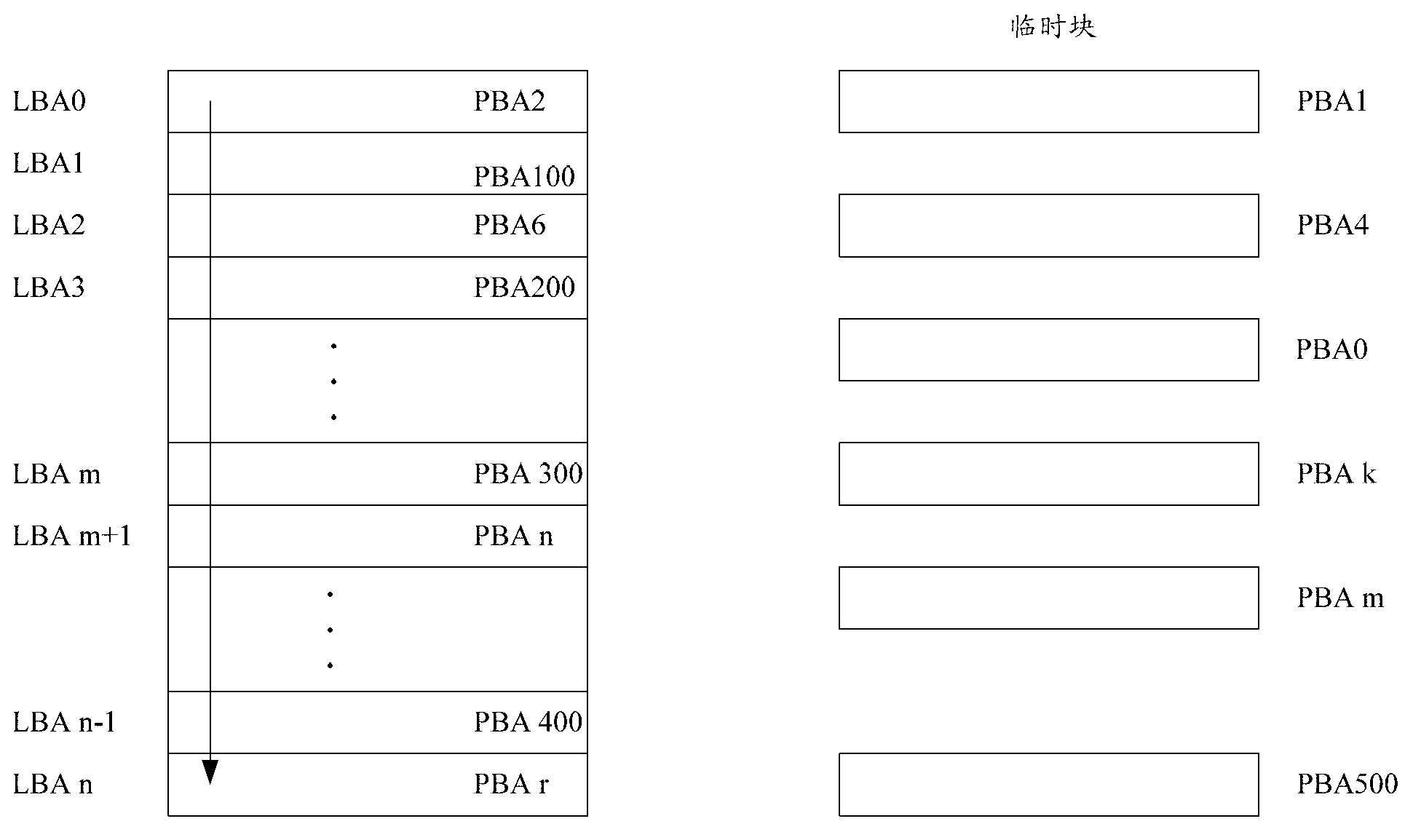

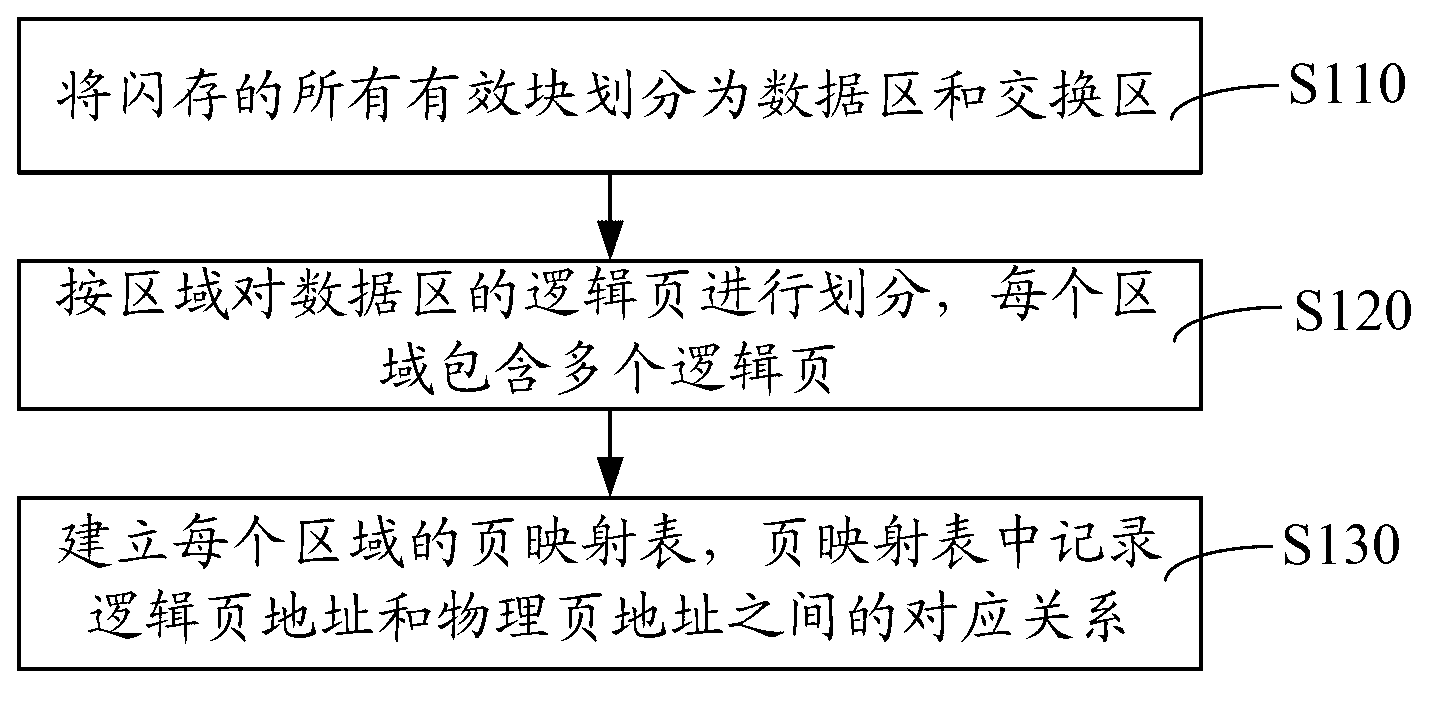

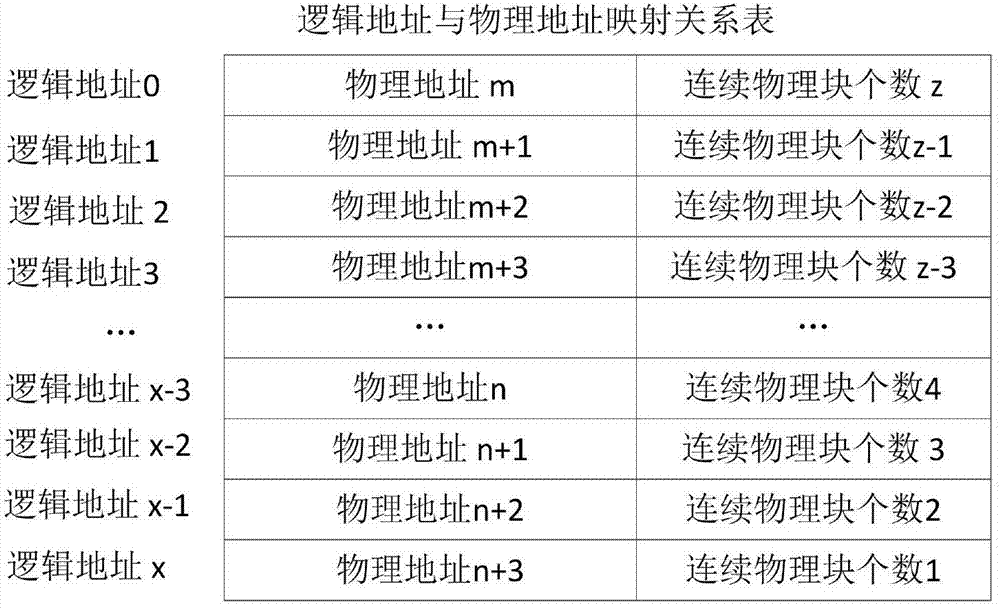

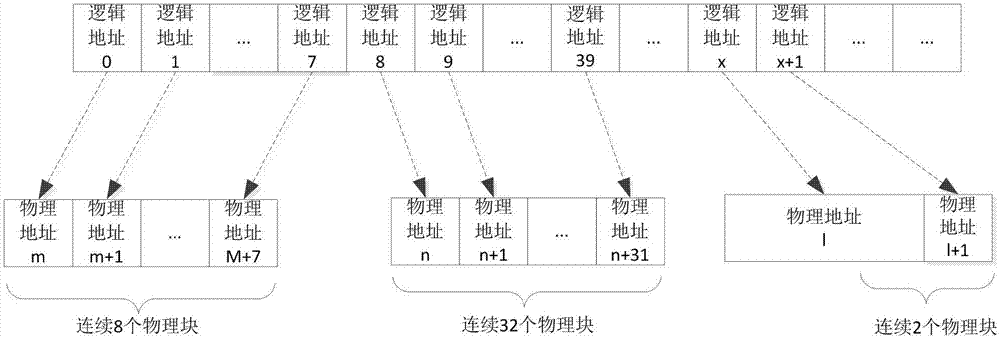

The invention relates to a flash memory management method and a flash memory device. The flash memory management method comprises following steps of dividing all active blocks of a flash memory into a data area and a switching area; dividing a logical page of the data area according to the area, wherein each area comprises a plurality of logical pages; and establishing a page mapping table of each area, and recording a correspondence relation of a logical page address and a physical page address in the page mapping table. According to the flash memory management method and the flash memory device, the data area of the flash memory is divided into different areas, the page mapping table of each area is established, the correspondence relation of the logical page address and the physical page address is recorded in the page mapping table, the flash memory is managed by adopting the page as a unit, when data is written in the flash memory, the data can be written into the flash memory according to the page sequence, after multiple pages of one block are fulfilled, the data is written into a next empty block, the utilization rate of the block is improved, the copy moving operation and erasing operation of the data can be reduced, the writing-in speed of the flash memory is improved, and the occupation of an internal memory can be reduced by establishing the page mapping table according to the areas.

Owner:SHENZHEN NETCOM ELECTRONICS CO LTD

Data reading method and device

InactiveCN107329904AImprove performanceReduce the number of visits to FTLMemory adressing/allocation/relocationGranularityComputer engineering

Owner:HUNAN GOKE MICROELECTRONICS

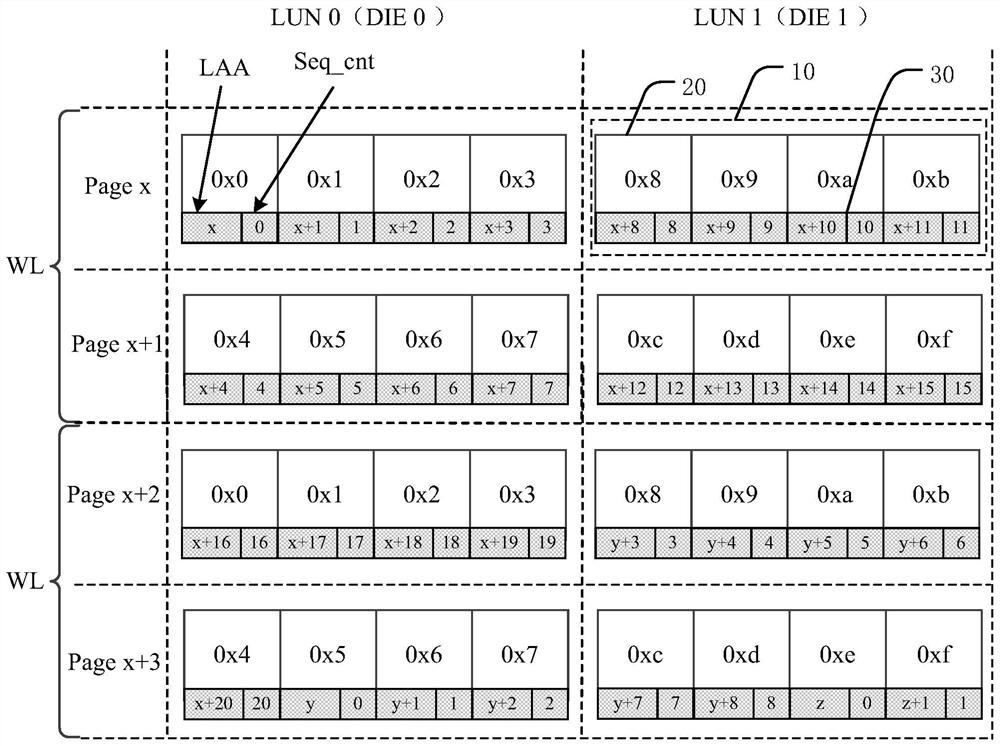

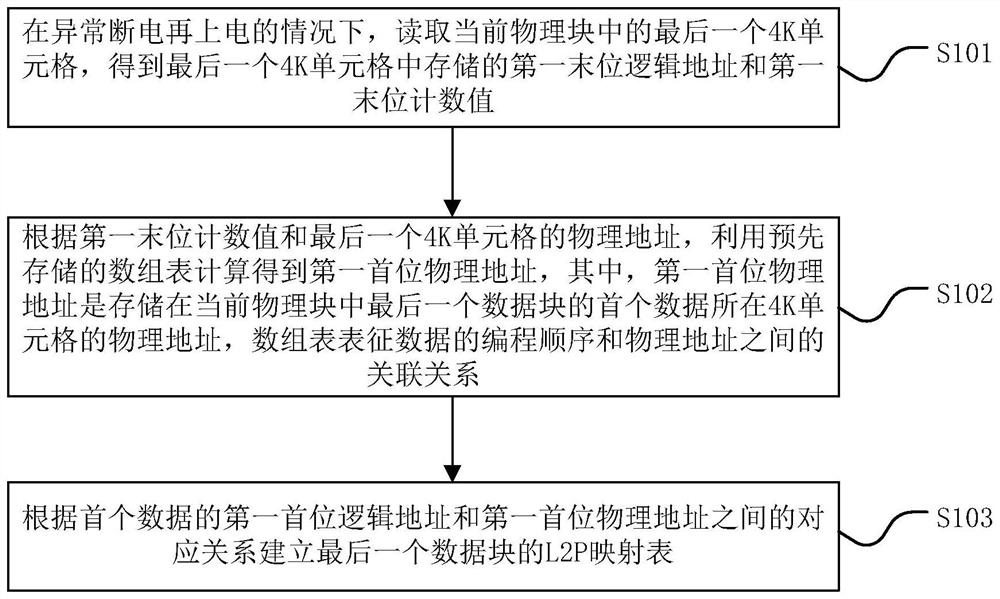

L2P mapping table reconstruction method and solid state disk

ActiveCN114415942AShorten the timeReduce the number of timesInput/output to record carriersEnergy efficient computingAlgorithmReconstruction method

Owner:MAXIO TECH (HANGZHOU) CO LTD

Popular searches

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap