Semiconductor memory device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Example

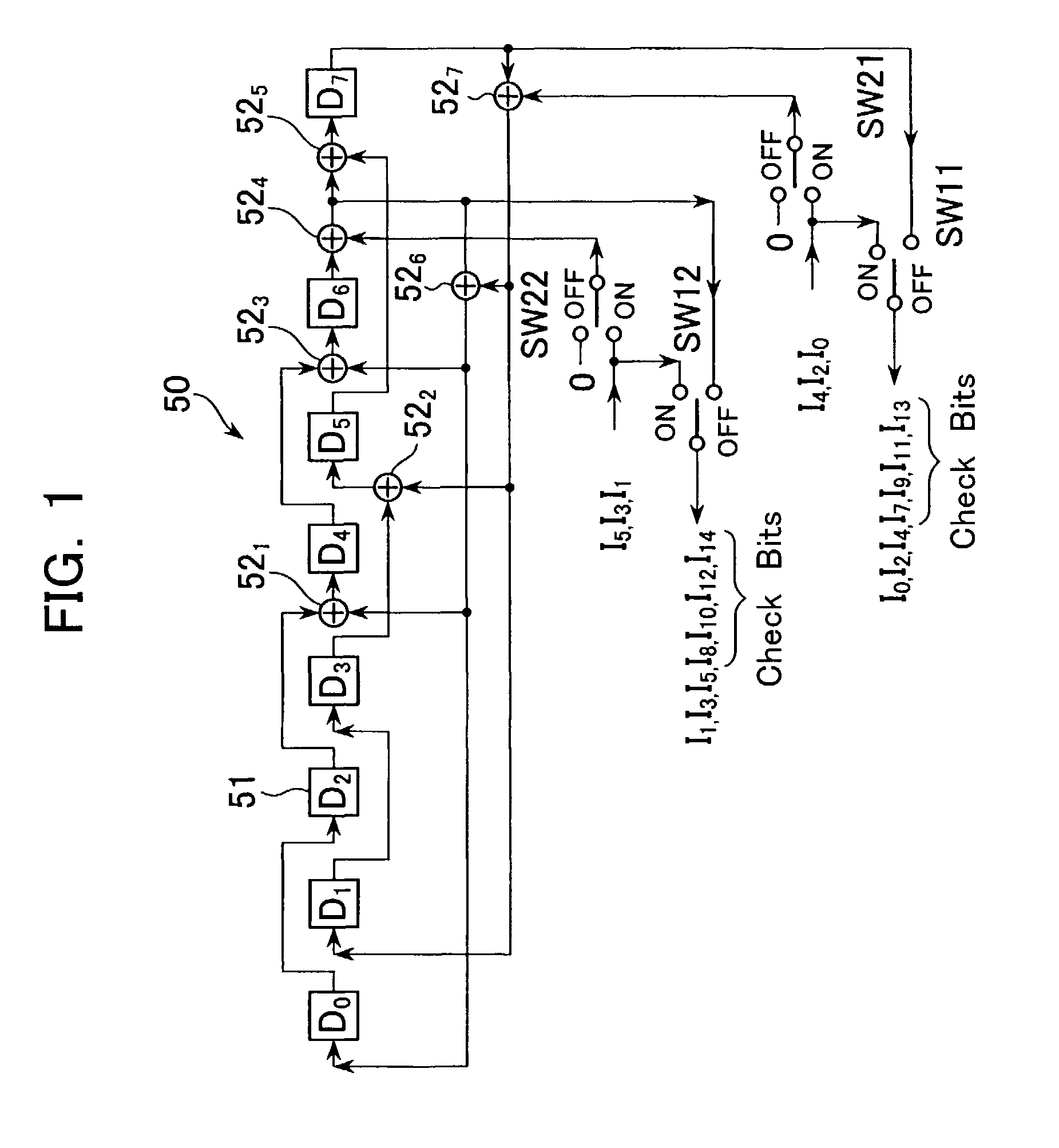

(1) First Embodiment

[0055]In order to provide an understanding of the present invention, 2-bit error correction is exemplified as a first embodiment with the number of information bits, k=7, a code length, n=15, and the number of correction bits, t=2.

(1-1) Coder

[0056]When input data I0 enters the conventional coder 11 shown in FIG. 22, the input data I0 is added at the XOR circuit 124 to the term of X7 in the coder, then multiplied by X. Each register 11 in the coder 10 in the initial state has a value of 0, which is referred to as (0). Accordingly:

(0+I0X7)X (17)

When next input data I1 enters the coder 10, the input data I1 is added to the term of X7 in the coder 10, then multiplied by X to yield:

((0+I0X7)X+I1X7)X (18)

[0057]When next input data I2 enters the coder 10, the input data I2 is added to the term of X7 in the coder 10, then multiplied by X to yield:

(((0+I0X7)X+I1X7)X+I2X7)X (19)

[0058]Similarly, after input data, up to I6, enters the coder 10, the following is given:

((((

Example

(2) Second Embodiment

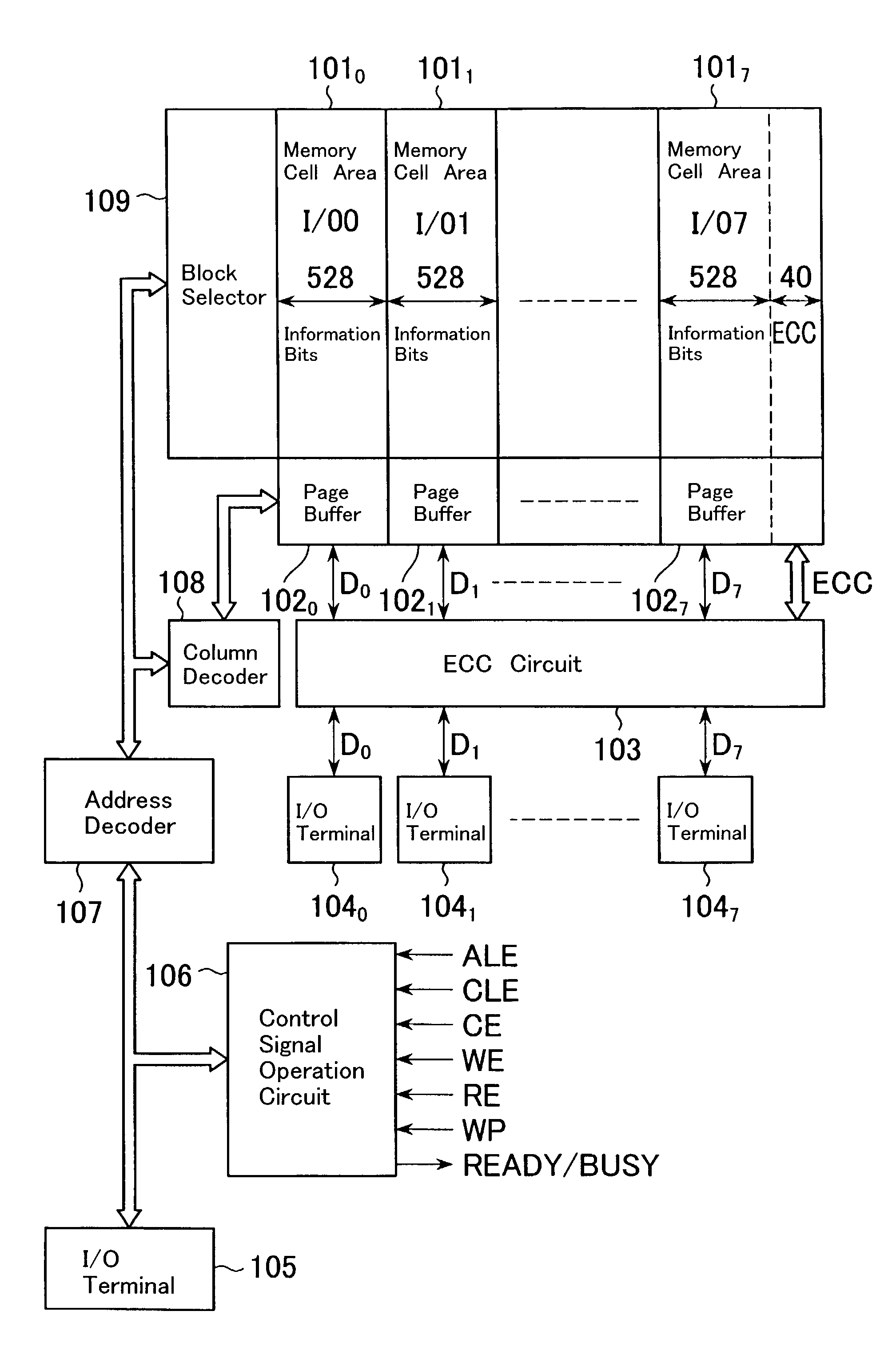

[0084]FIG. 7 is a block diagram showing a NAND-type flash memory according to a second embodiment, which mounts an ECC circuit on a chip.

[0085]The memory comprises eight memory cell areas 1010, 1011, 1012, . . . , 1017. Eight page buffers 1020, 1021, 1022, . . . , 1027 are provided corresponding to the memory cell areas 1010, 1011, 1012, . . . , 1017 to temporarily store data to be written in and read out of the memory cell areas 1010, 1011, 1012, . . . , 1017. Between the page buffers 1020–1027 and I / 0 terminals 1040, 1041, . . . , 1047, an ECC circuit 103 is provided to generate check bits, ECC, for correcting errors in the write data and to correct errors in the read data using the check bits (ECC). Different from the conventional type, for error detection and correction, the ECC circuit 103 adds 40 check bits commonly to information bits consisting of 528 bits ×8 I / O=4224 bits data (M=528, N=8) that can be read out of and written into all memory cell areas

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap