Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3 results about "Transmission gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A transmission gate (TG) is an analog gate similar to a relay that can conduct in both directions or block by a control signal with almost any voltage potential. It is a CMOS-based switch, in which PMOS passes a strong 1 but poor 0, and NMOS passes strong 0 but poor 1. Both PMOS and NMOS work simultaneously.

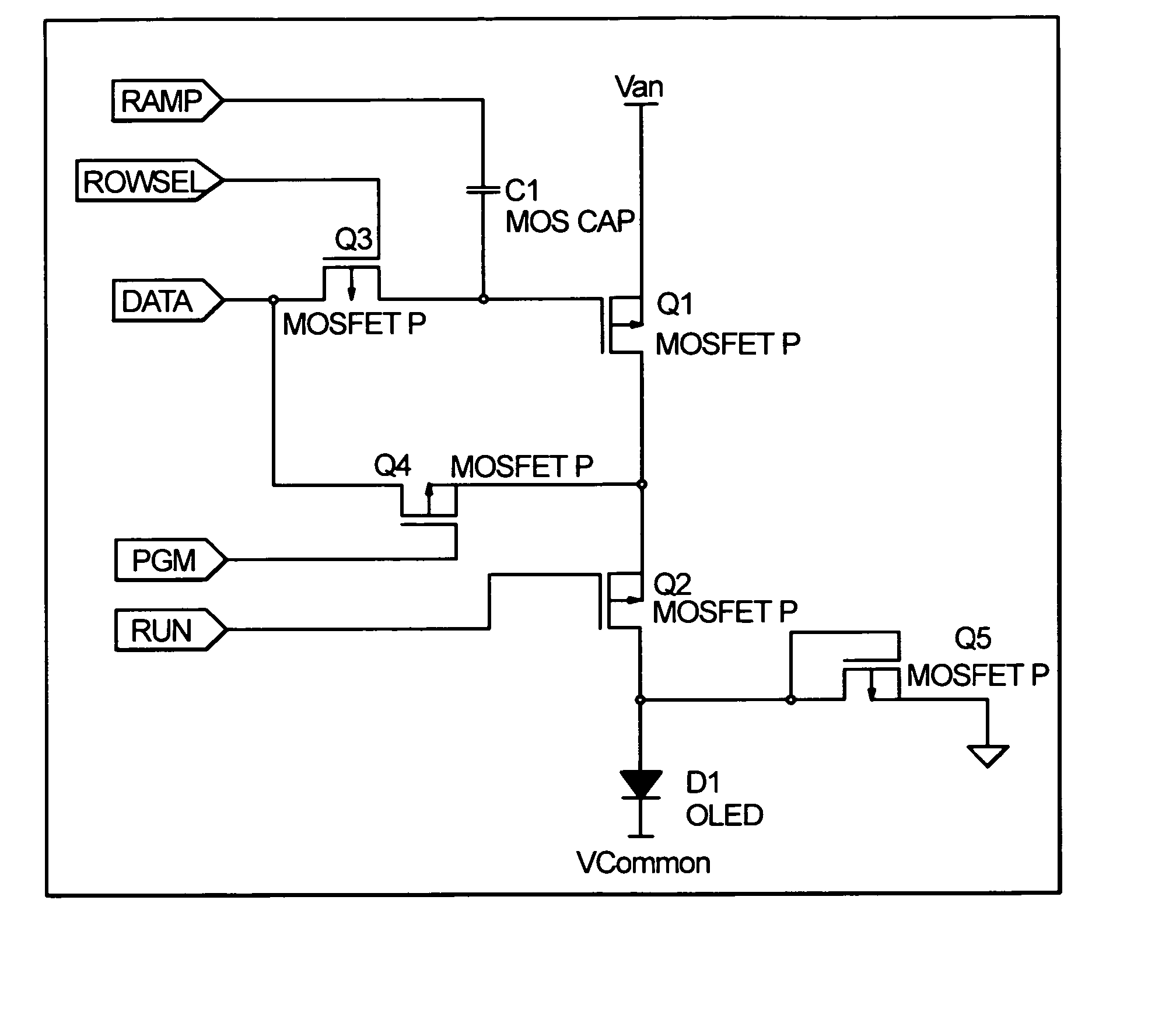

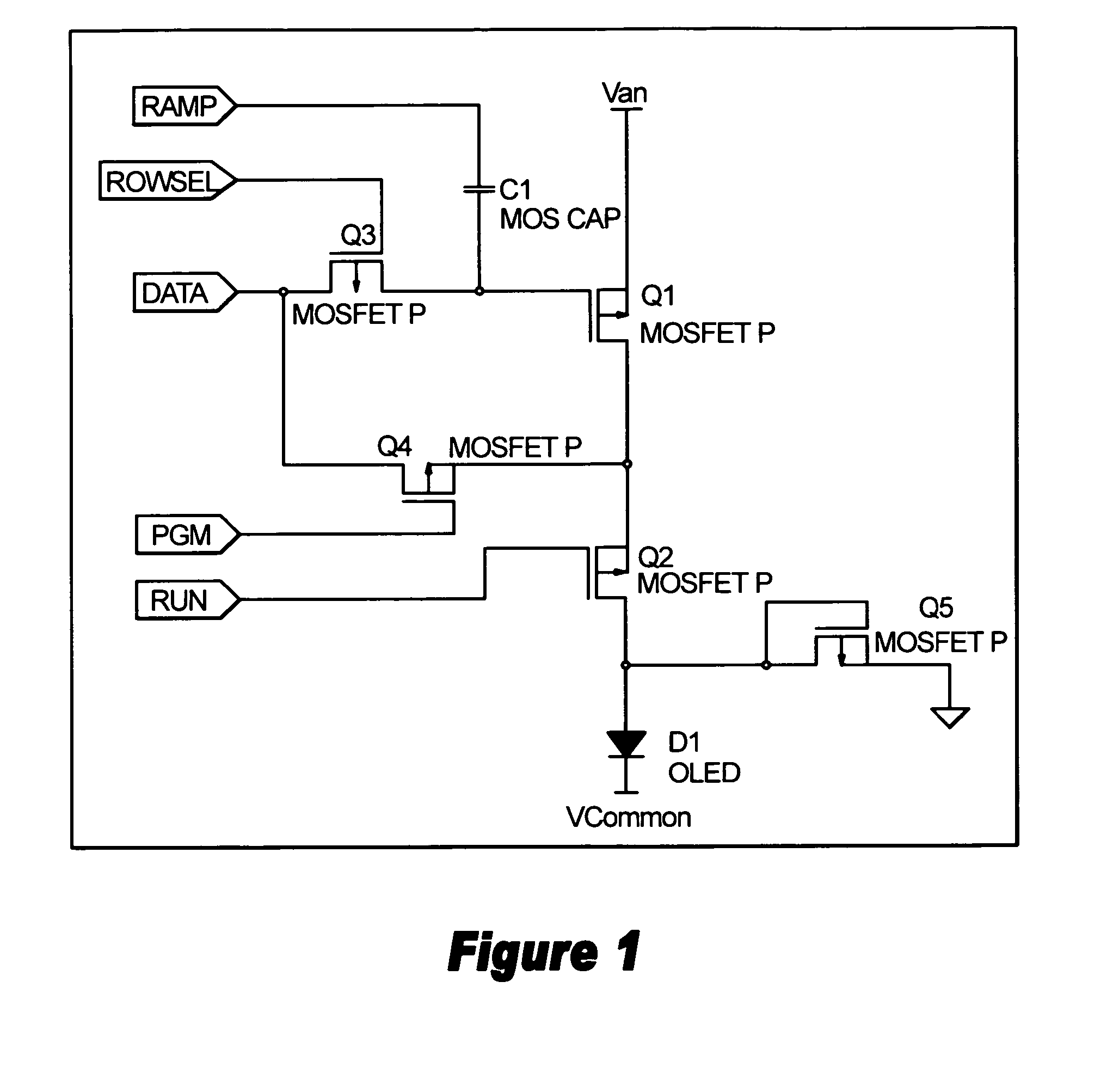

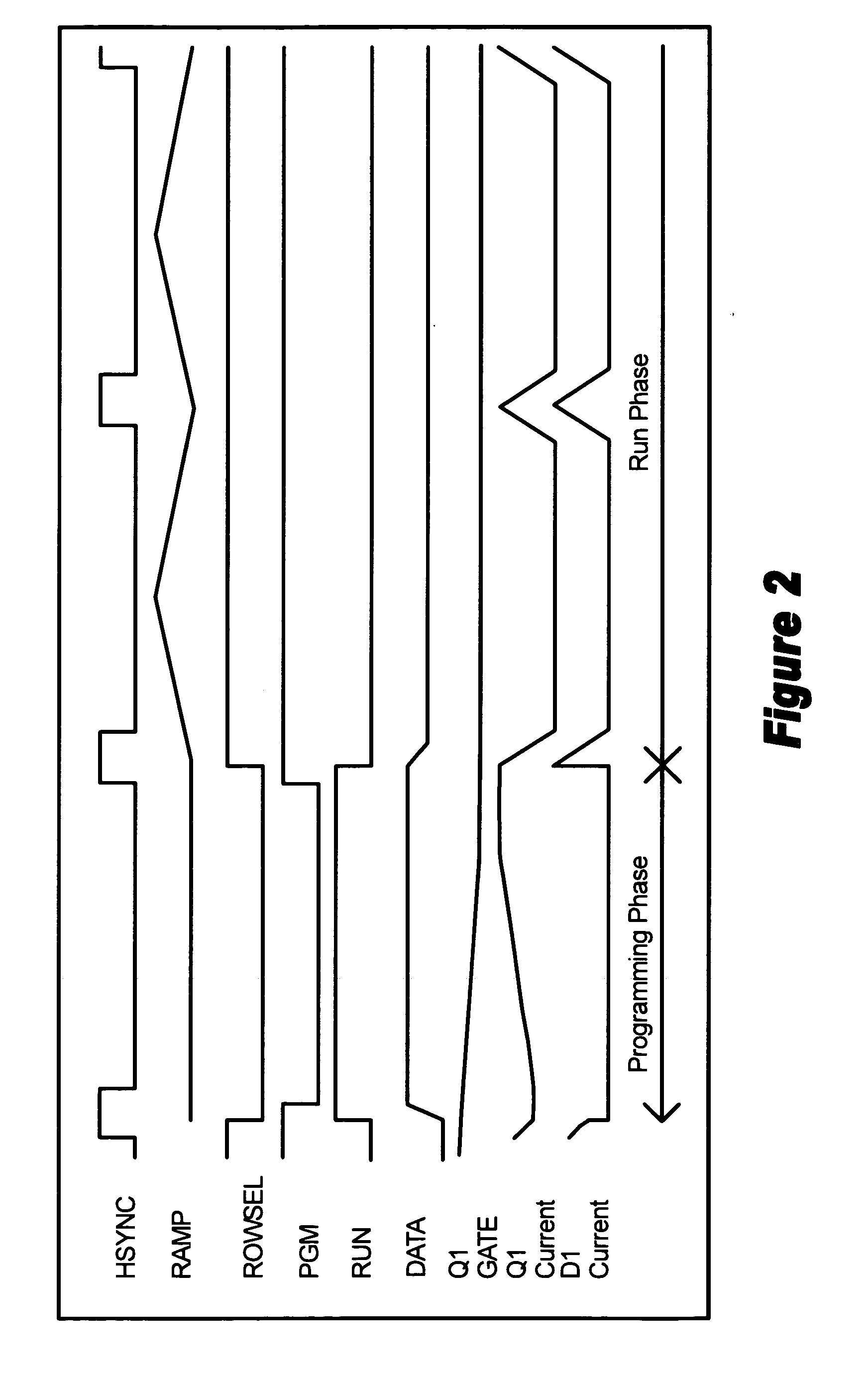

OLED active matrix cell designed for optimal uniformity

Owner:EMAGIN CORP

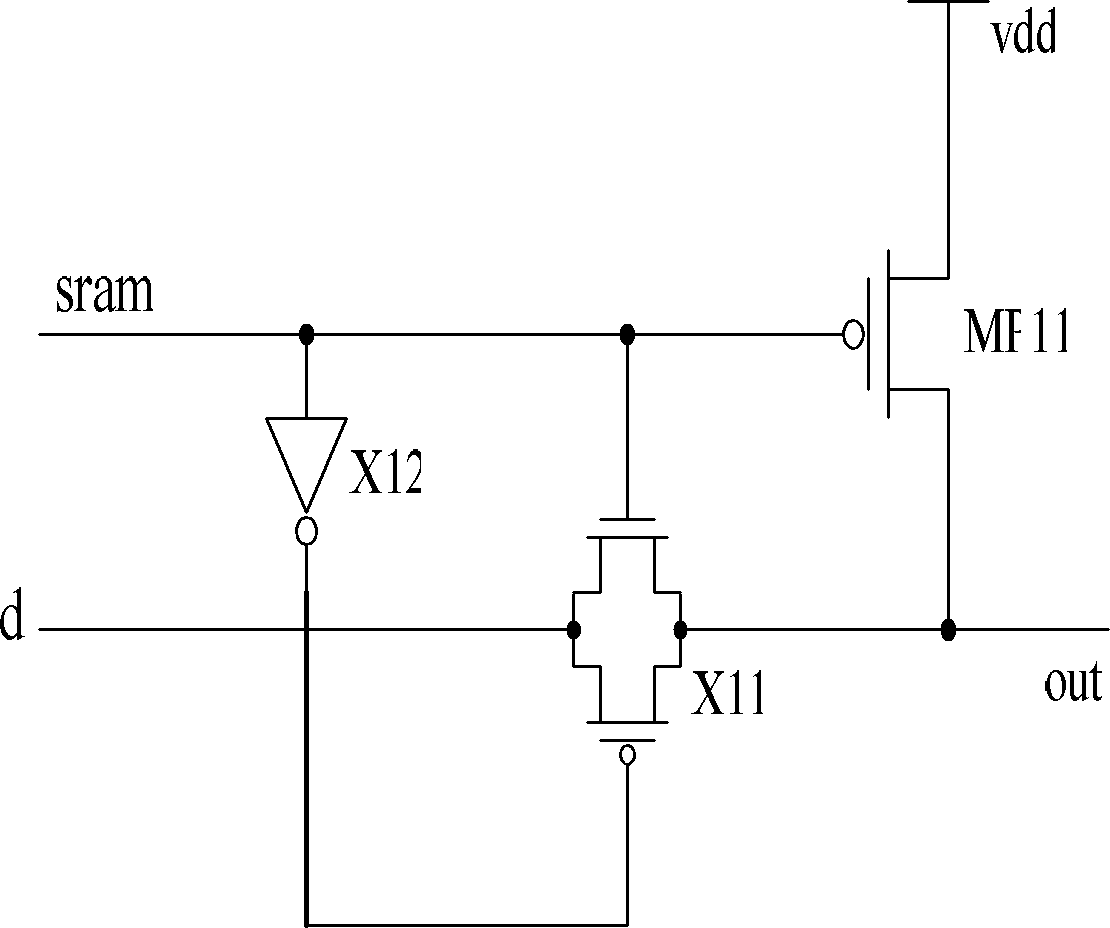

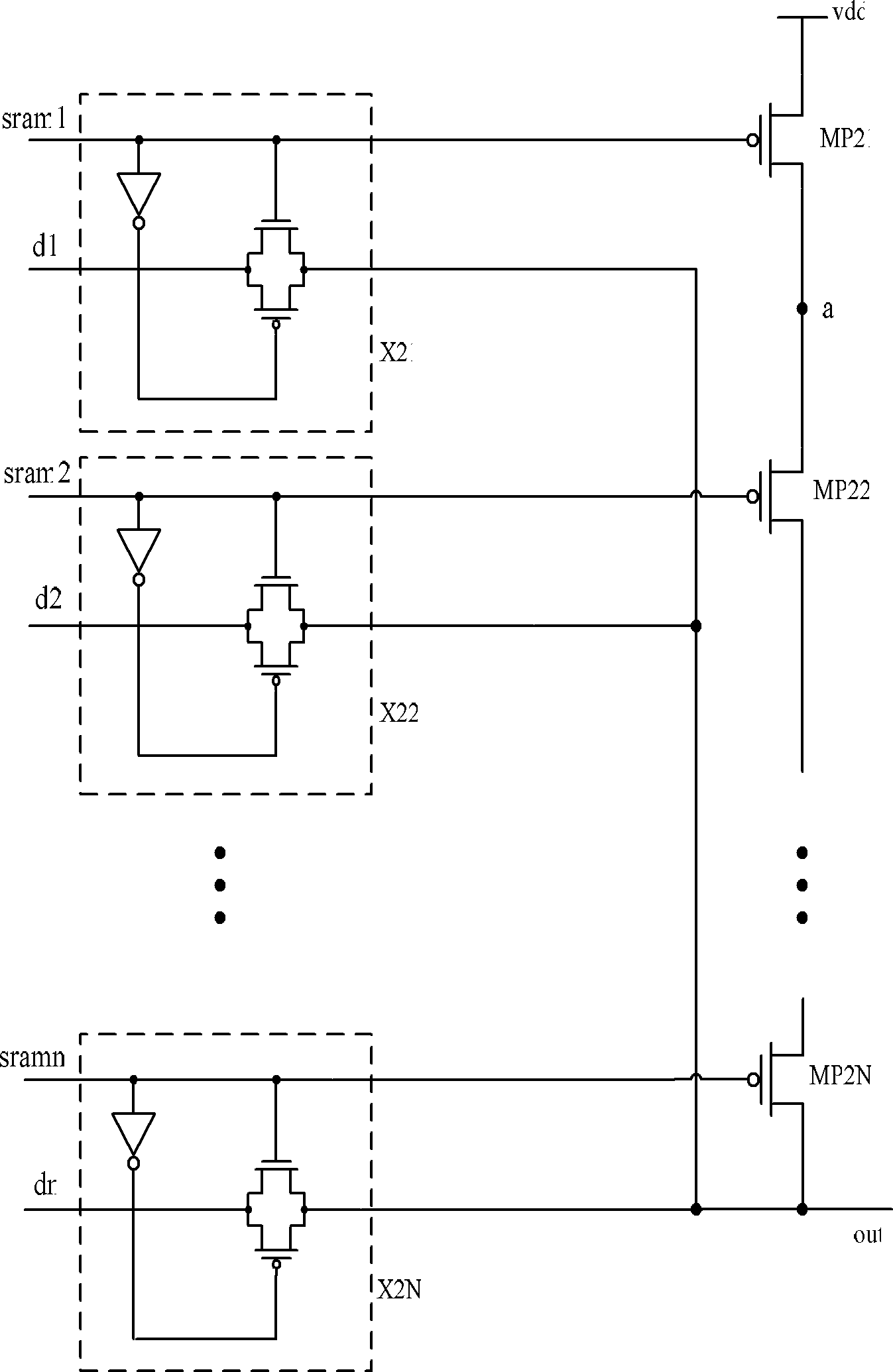

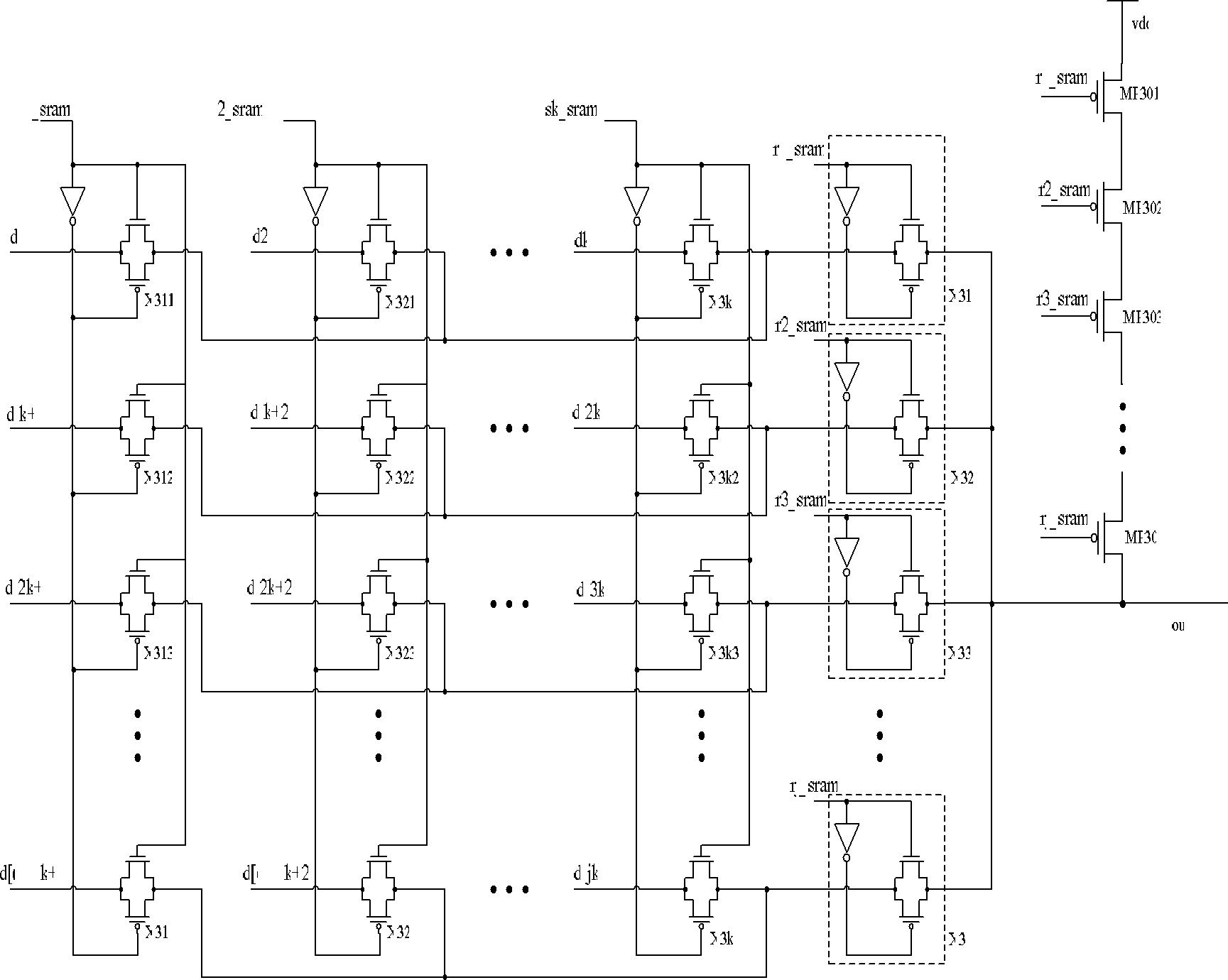

Selector circuit with fixed output state

ActiveCN102761325AGuaranteed to workGuaranteed driving abilityElectronic switchingTransmission gateEngineering

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

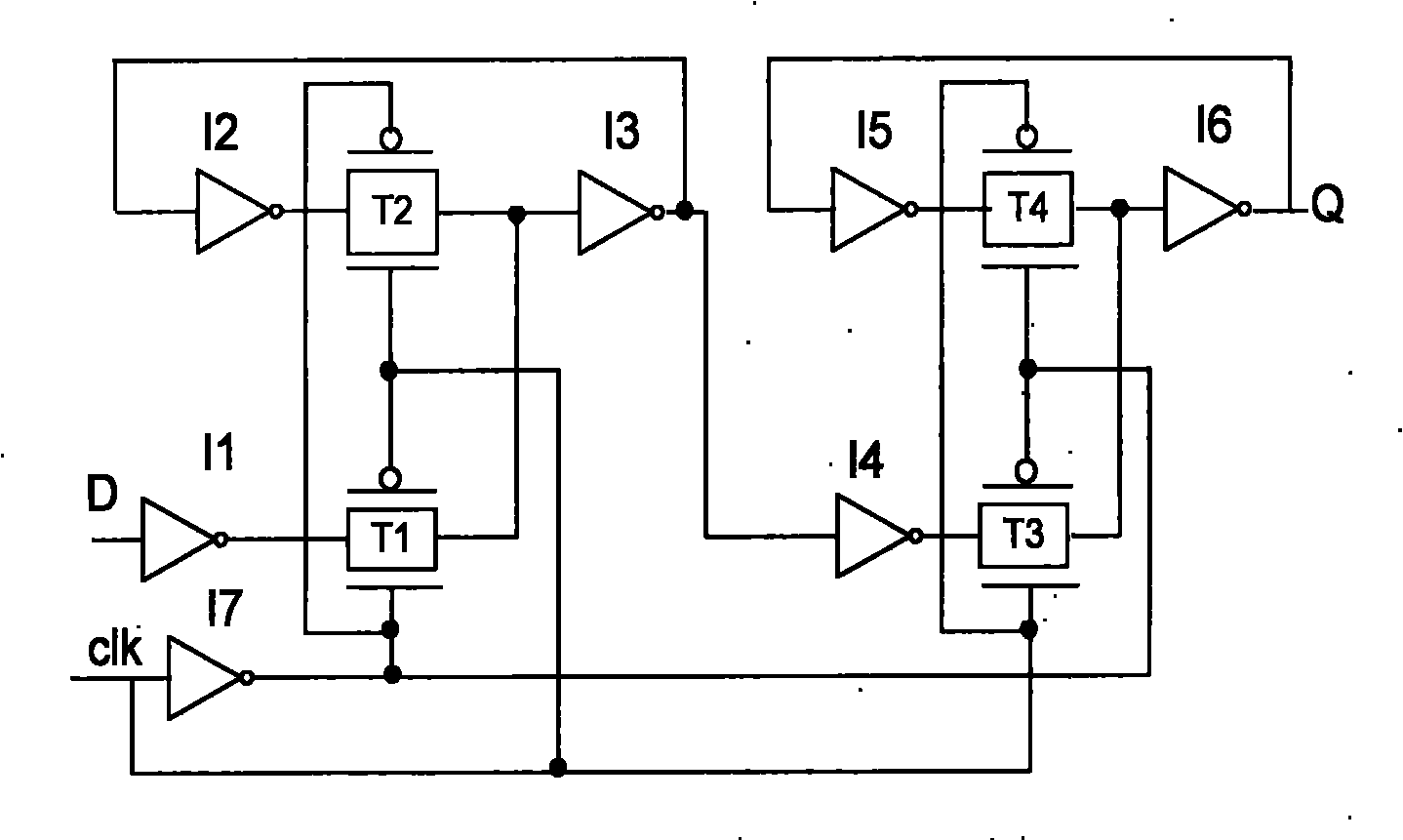

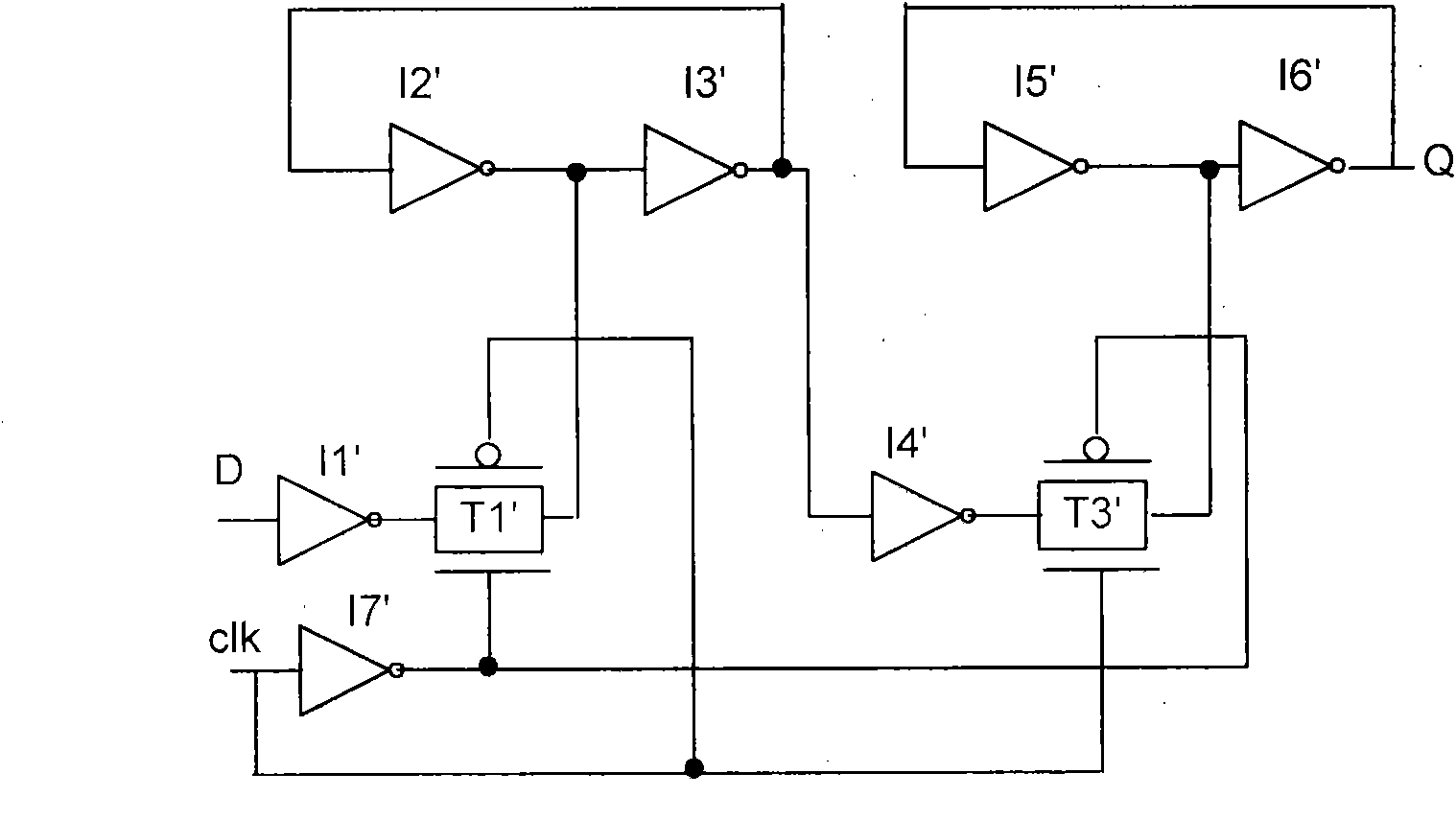

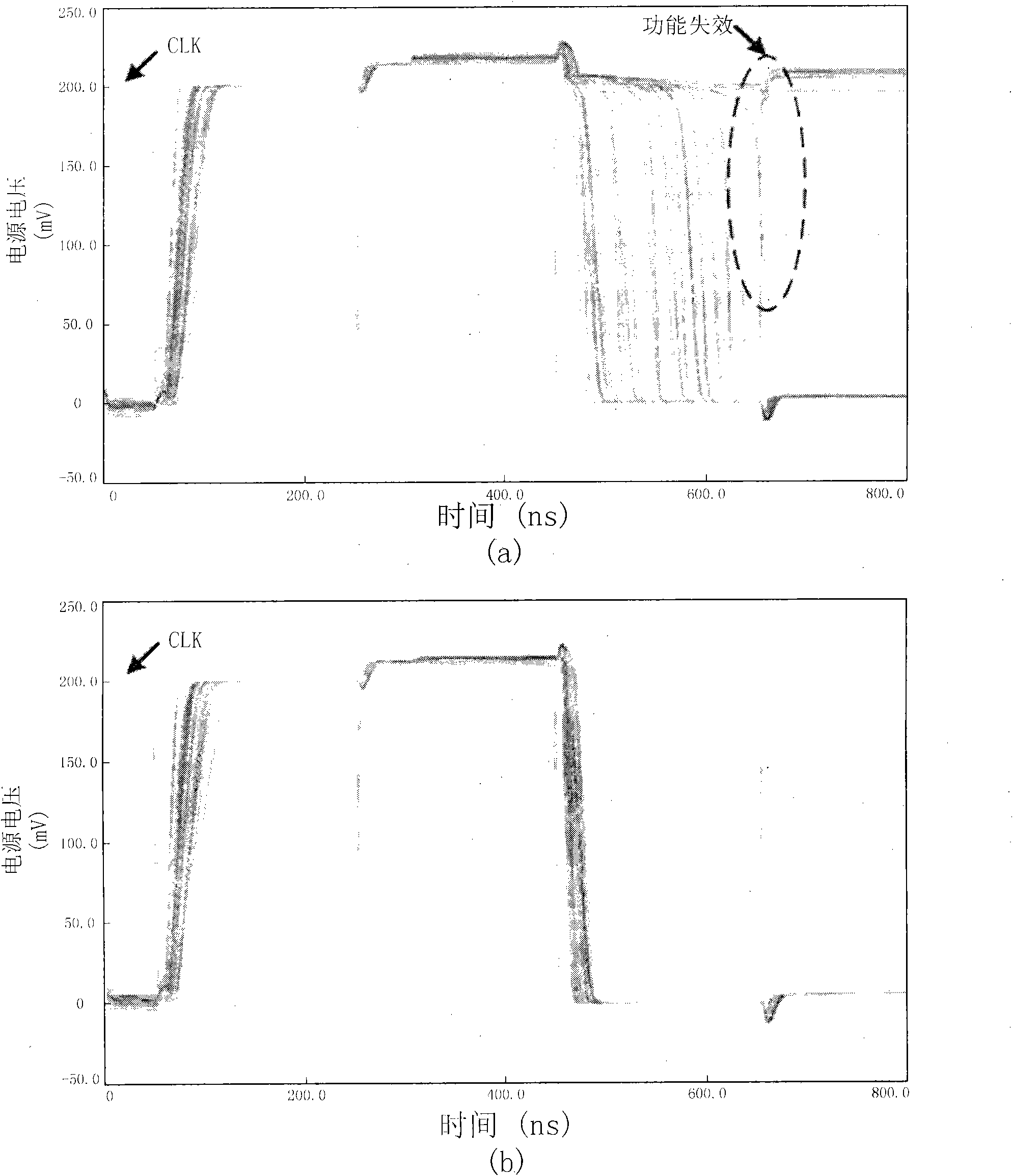

Subthreshold latch

InactiveCN102075179AAvoid the problem of not saving data normallyGuaranteed to workLogic circuitsCMOSTransmission gate

Owner:SOUTHEAST UNIV

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap