Multi-core microcontroller having comparator for checking processing result

a multi-core microcontroller and processing result technology, applied in the field of microcontrollers, can solve the problems of deteriorating system stability, both cpus cannot execute the same processing at the complete same time, etc., and achieve normal comparison operation results, high-performance processing, and normal processing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

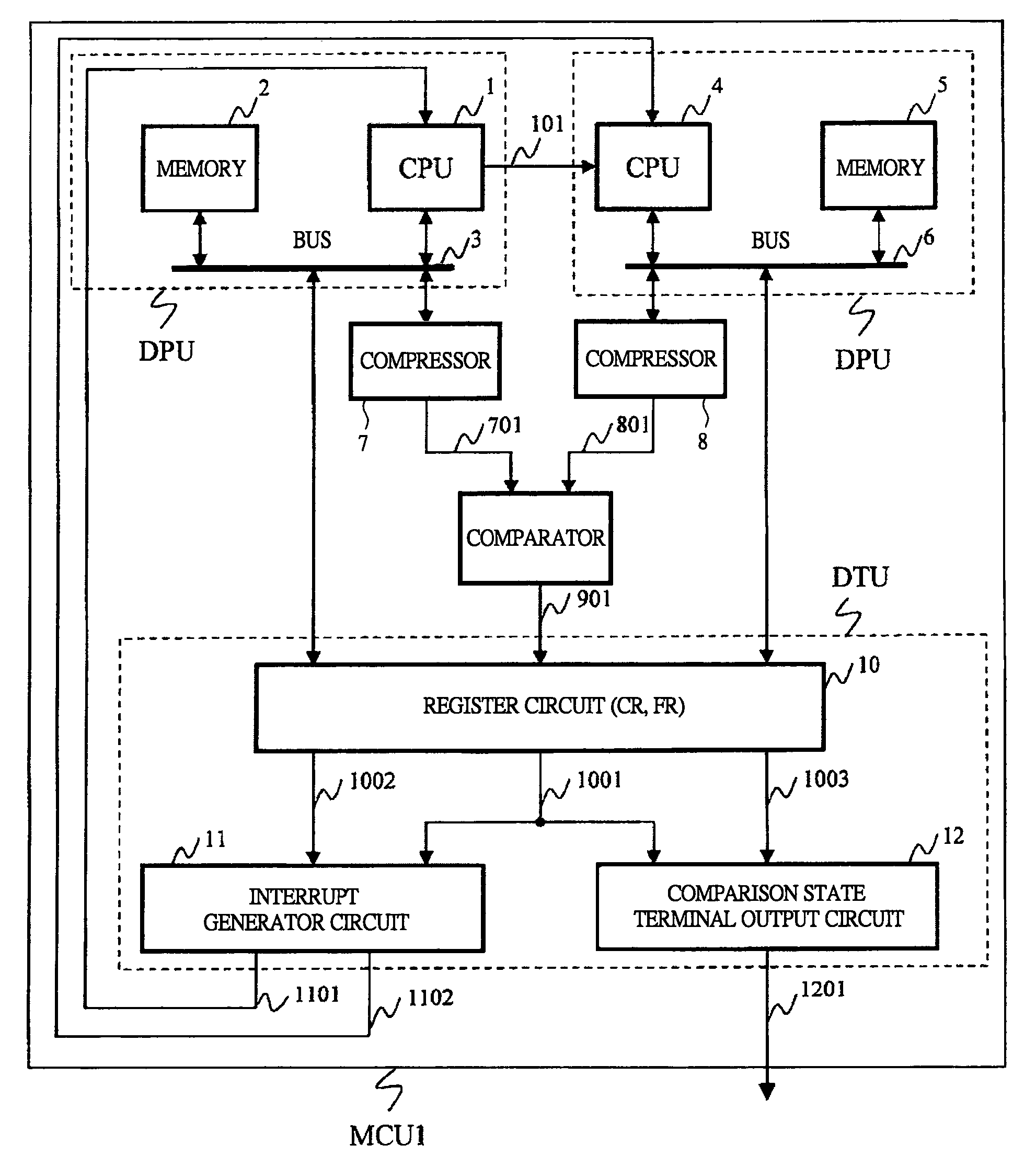

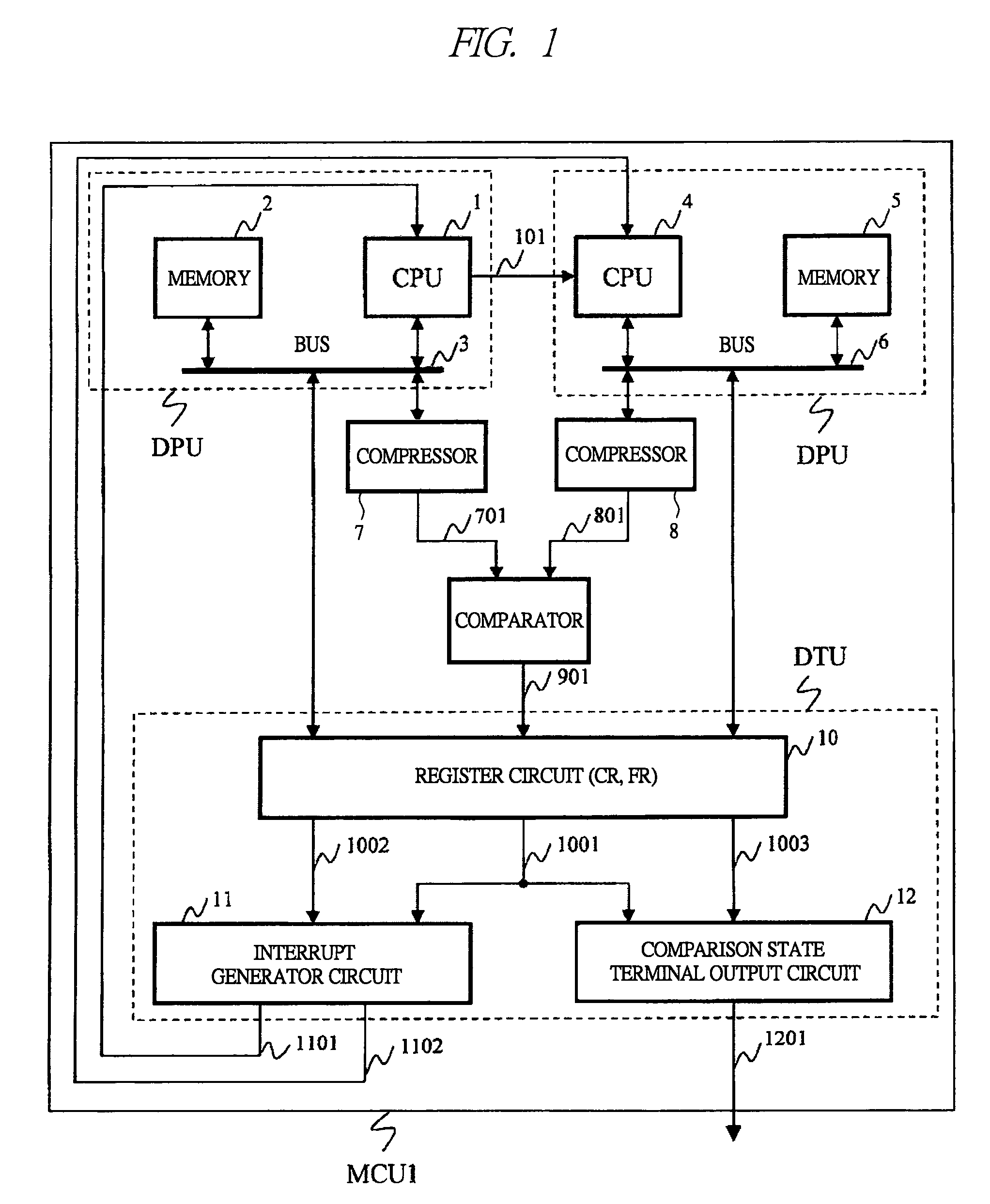

[0061]FIG. 1 exemplarily illustrates a configuration of a microcontroller to which the present invention is applied. The microcontroller MCU1 illustrated herein is constituted as a dual-core microcontroller having two CPUs, and the drawing mainly illustrates the configuration in which the same application for which safety is required can be asynchronously executed by the CPUs, and results thereof to be output at different timings can be checked.

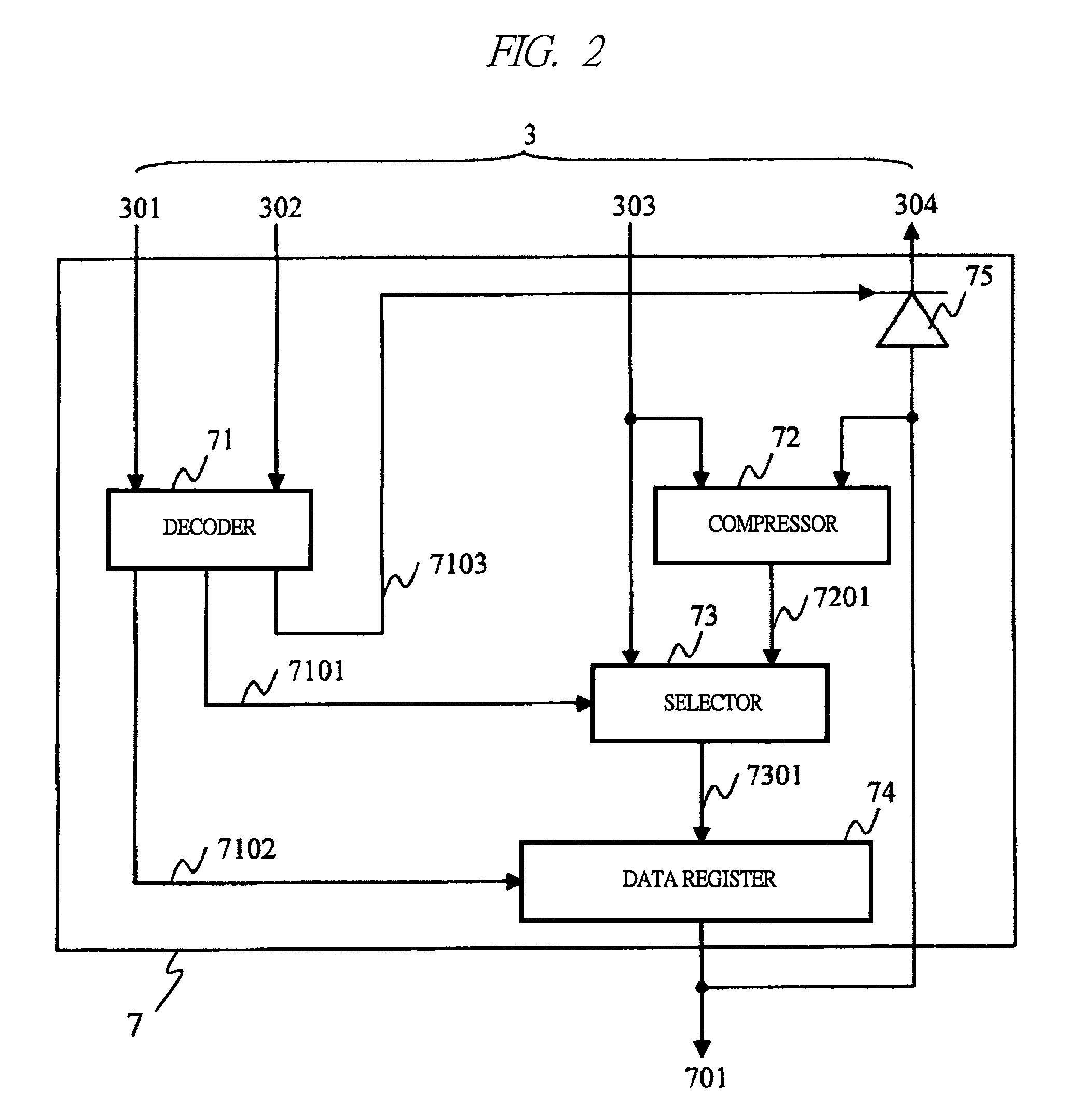

[0062]The CPU which executes commands and carries out processing such as calculations and data transfer is denoted by 1. A memory which stores the commands executed by and the data processed by the CPU 1 is denoted by 2. A bus by which the CPU 1 accesses devices such as the memory 2 is denoted by 3. The CPU which executes commands and carries out processing such as calculations and data transfer is denoted by 4. A memory which stores the commands executed by and the data processed by the CPU 4 is denoted by 5. A bus by which the CPU 4 accesses

second embodiment

[0076]FIG. 7 exemplarily illustrates a microcontroller MCU2 according to the present invention. The microcontroller MCU2 is constituted as a multi-core microcontroller having three CPUs. Differences from the dual-core microcontroller of FIG. 1 will be explained. A CPU which executes commands and carries out processing such as calculations and data transfer is denoted by 14. A memory which stores the commands executed by the CPU 14 and the data processed by the CPU 14 is denoted by 15. A bus by which the CPU 14 accesses devices such as the memory 15 is denoted by 16. A compressor which compresses and stores the data output from the CPU 14 is denoted by 17. The comparator which compares the output signal 701 of the compressor 7, the output signal 801 of the compressor 8, and an output signal 1701 of the compressor 17 with one another and outputs a result signal 901 is denoted by 9. In the comparison register CR which the register circuit 10 has, the CPU 1, the CPU 4, and the CPU 14 carry

third embodiment

[0079]FIG. 9 exemplarily illustrates a microcontroller MCU3 according to the present invention. The microcontroller MCU3 is constituted as a dual-core microcontroller having two CPUs. Differences from the dual-core microcontroller MCU1 of FIG. 1 will be explained. The compressor 7, the compressor 8, and the comparator 9 of FIG. 1 are replaced by FIFO 21, FIFO 22, and a comparator 23 in FIG. 9.

[0080]The FIFO 21 stores the data output from the CPU 1 into a FIFO register including a plurality of stages of registers of the first-in first-out method without compressing the data. Similarly, the FIFO 22 stores the data output from the CPU 2 into a FIFO register without compressing the data. The FIFO 21 outputs the oldest data of the FIFO register to a FIFO output signal 2101. Also, the FIFO 21 outputs a FIFO output valid signal 2102 which indicates that the FIFO output signal is valid. Similarly, the FIFO 22 outputs a FIFO output signal 2201 and a FIFO output valid signal 2202.

[0081]When both

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap