Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

5 results about "Digital down converter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In digital signal processing, a digital down-converter (DDC) converts a digitized, band limited signal to a lower frequency signal at a lower sampling rate in order to simplify the subsequent radio stages. The process preserves all the information in the original signal less that which is lost to rounding errors in the mathematical processes. The input and output signals can be real or complex samples. Often the DDC converts from the raw radio frequency or intermediate frequency down to a complex baseband signal.

Pipelined analog-digital converter

InactiveCN101552609AReduce power consumptionAnalogue-digital convertersDigital down converterAudio power amplifier

The present invention relates to a pipelined analog-digital converter, including a plurality of sub pipelined stages for implementing analog-to-digital conversion and allowance amplification to input analog signals; a time-delay synchronization register for implementing time-delay alignment to output digital codes from each pipelined stage; a digital correction module for receiving output digital codes from the synchronization register, and implementing bit shift addition to the output digital codes to obtain digital output codes of the analog-digital converter; a dynamic bias circuit for adjusting the bias level of the operational amplifier of each sub pipelined stage according to the frequency of sampling clocks to each sub pipelines stage; and a built-in band-gap reference source circuit for generating a reference voltage source of the dynamic bias circuit, thus the ''excess'' of the operational amplifier quantity for meeting the built-up time of a highest sampling frequency may be avoided, and an amplifying power will be reduced accordingly relative to a lower sampling frequency, thereby the power consumption of the analog-digital converter will be saved integrally.

Owner:SUZHOU TONGCHUANG WEIXIN CO LTD

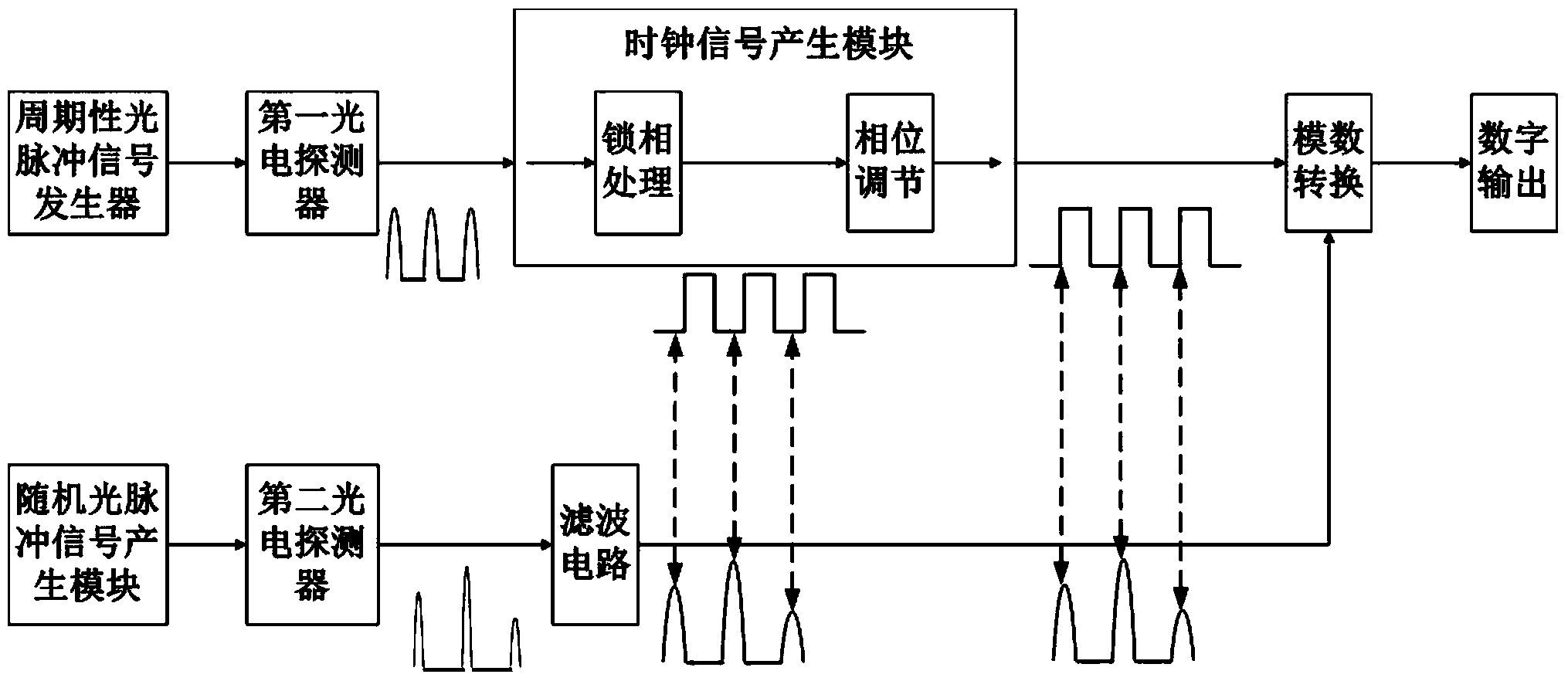

Digital interface radio frequency chip and implementation method thereof

ActiveCN103209070ALow costReduce power consumptionTransmitter/receiver shaping networksSynchronising arrangementMultiplexingDigital down converter

The invention discloses a digital interface radio frequency chip and an implementation method thereof. The digital interface radio frequency chip comprises a receiving antenna, a radio frequency analog front-end subsystem and an analog baseband subsystem, wherein the analog baseband subsystem comprises an oversampling analog-to-digital converter, an internal clock generating module, a digital signal processor and a multiplexing parallel module, an output end of the receiving antenna is connected with an input end of the multiplexing parallel module through the radio frequency analog front-end subsystem, the oversampling analog-to-digital converter and the digital signal processor sequentially, and an output end of the internal clock generating module is connected with a clock input end of the oversampling analog-to-digital converter and a clock input end of the multiplexing parallel module respectively. According to the digital interface radio frequency chip, clocks generated inside the radio frequency chip serve as reference clocks, so that the correctness of the baseband chip data collection can be guaranteed; and no complex first-in first-out (FIFO) structure is required, the structure is simple, the integration is easy, and the cost and the power consumption are reduced. The digital interface radio frequency chip and the implementation method thereof are widely applied in the technical field of communications.

Owner:TOLL MICROELECTRONIC CO LTD

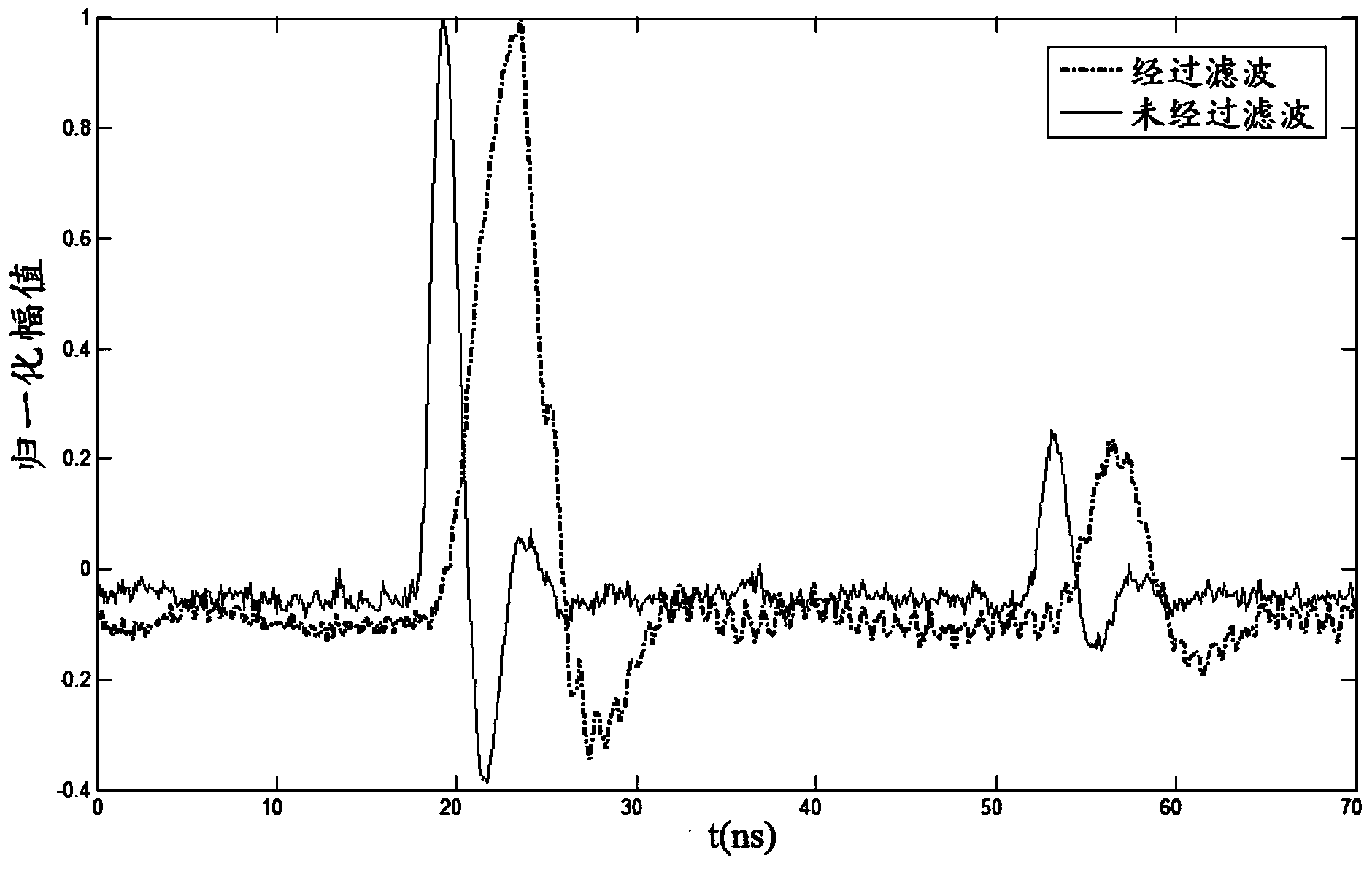

Nanosecond level pulse peak value detection method

InactiveCN103901262ALow costAccurate samplingMeasurement using digital techniquesDigital down converterLow-pass filter

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

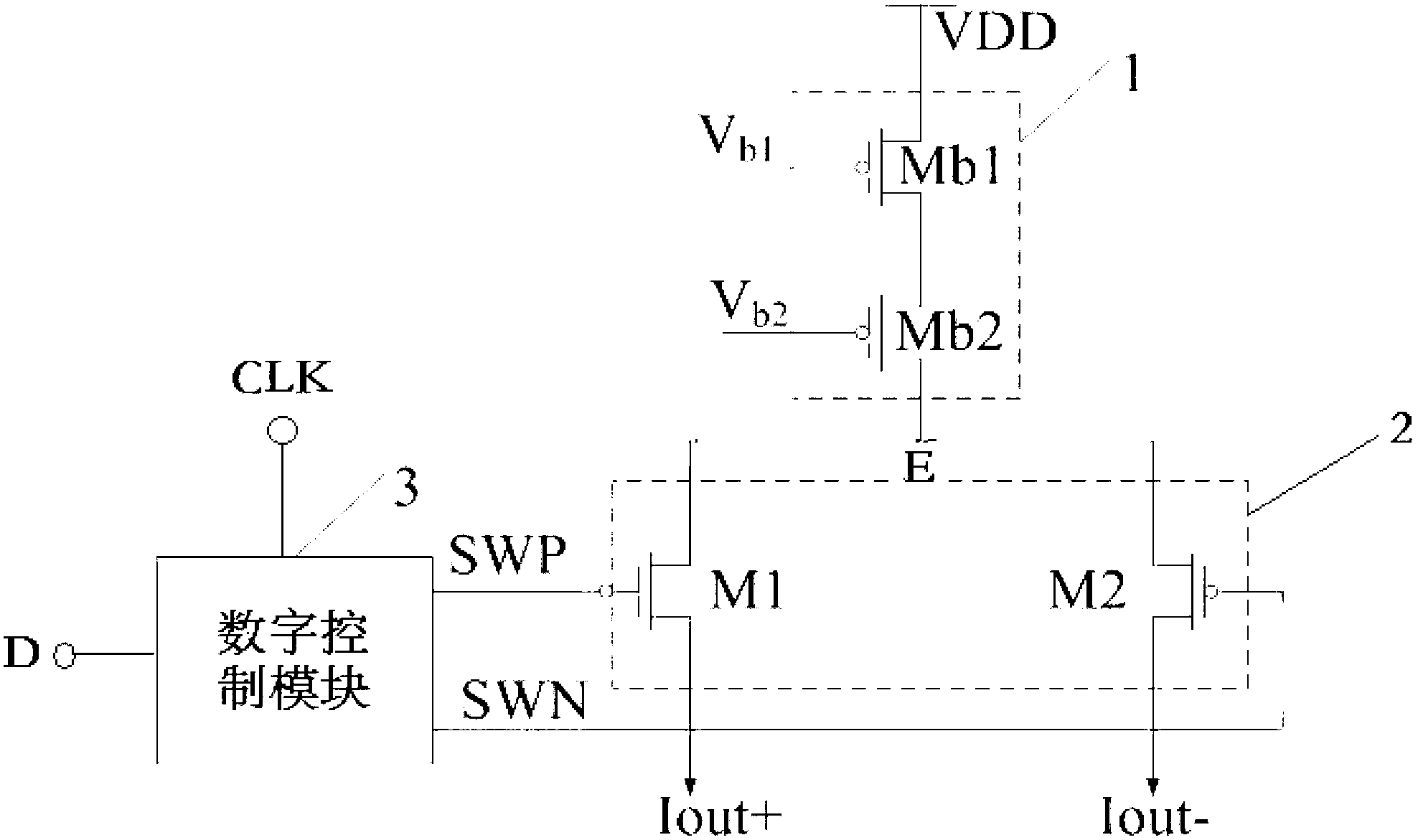

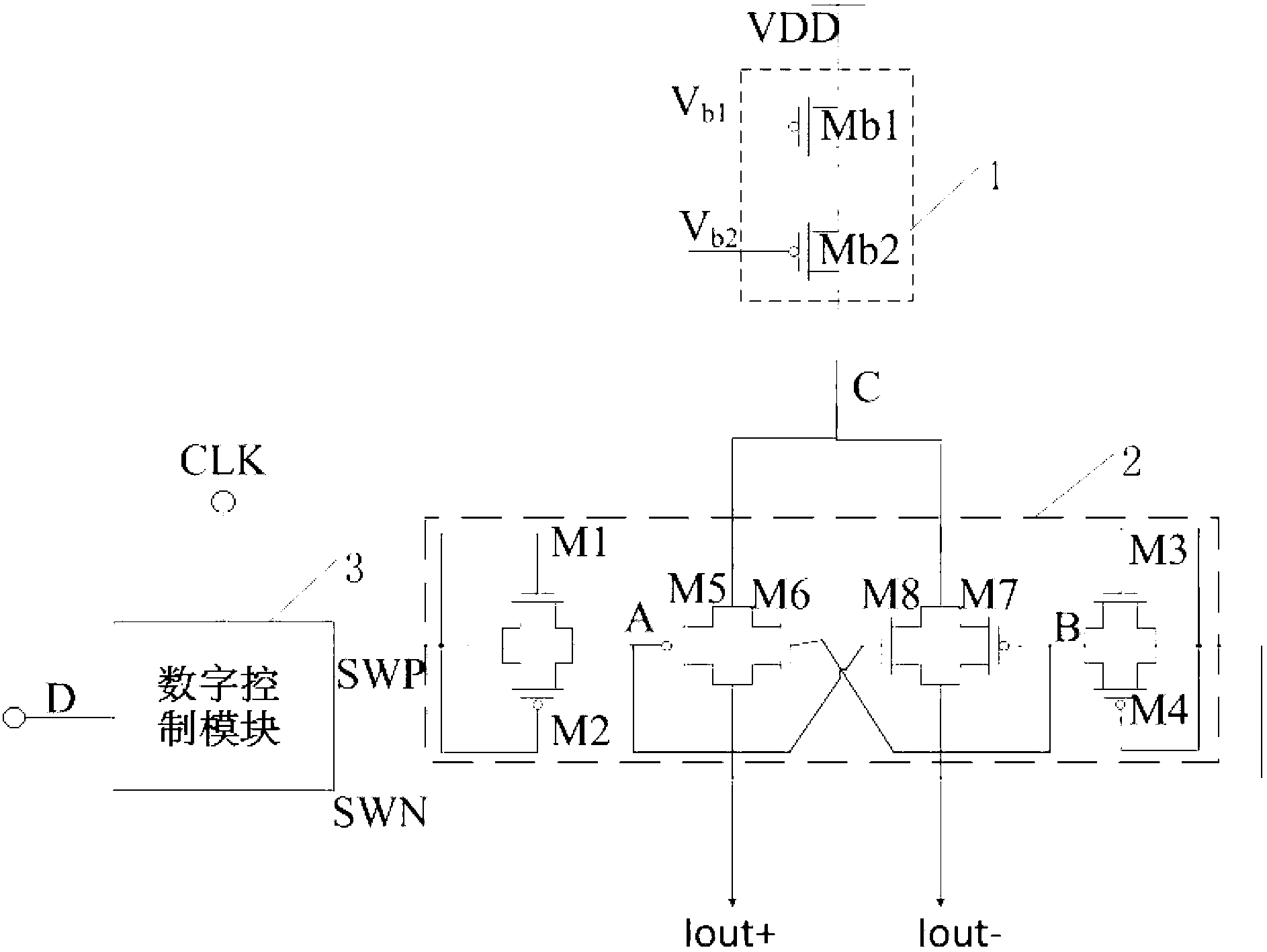

Current source unit circuit of current-steering digital analog converter

InactiveCN103023508AReduce output signalEasy to implementDigital-analogue convertorsDigital down converterControl signal

Owner:NORTH CHINA UNIVERSITY OF TECHNOLOGY

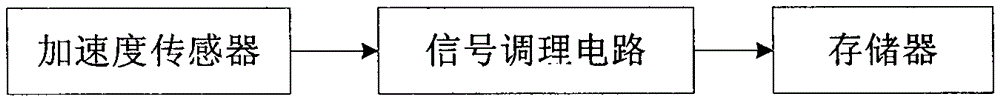

Acceleration sensor acquisition system

InactiveCN105021845AHigh precisionEasy to handleAcceleration measurement using interia forcesSpeed/acceleration/shock instrument detailsSignal conditioning circuitsDigital down converter

Owner:刘佳

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap