DBC board layout method for reducing parasitic inductance of GaN HEMT power module packaging

A parasitic inductance and power module technology, applied in the field of DBC board layout to reduce the parasitic inductance of GaN HEMT power module packaging, can solve the problems of unreasonable thermal stress design, insufficient compatibility, troublesome heat dissipation, etc., to reduce chip performance degradation, The effect of avoiding mutual interference and reducing design cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

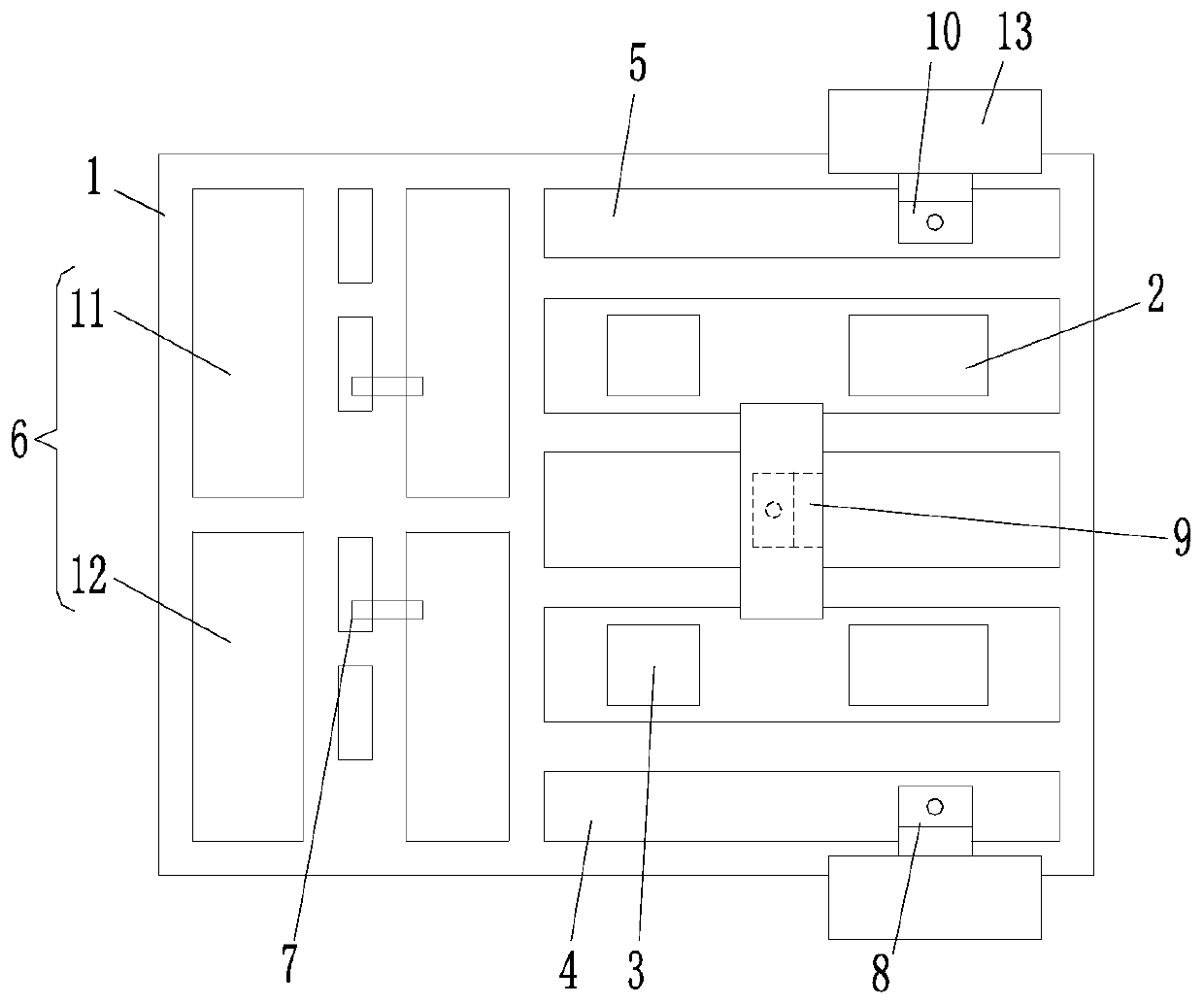

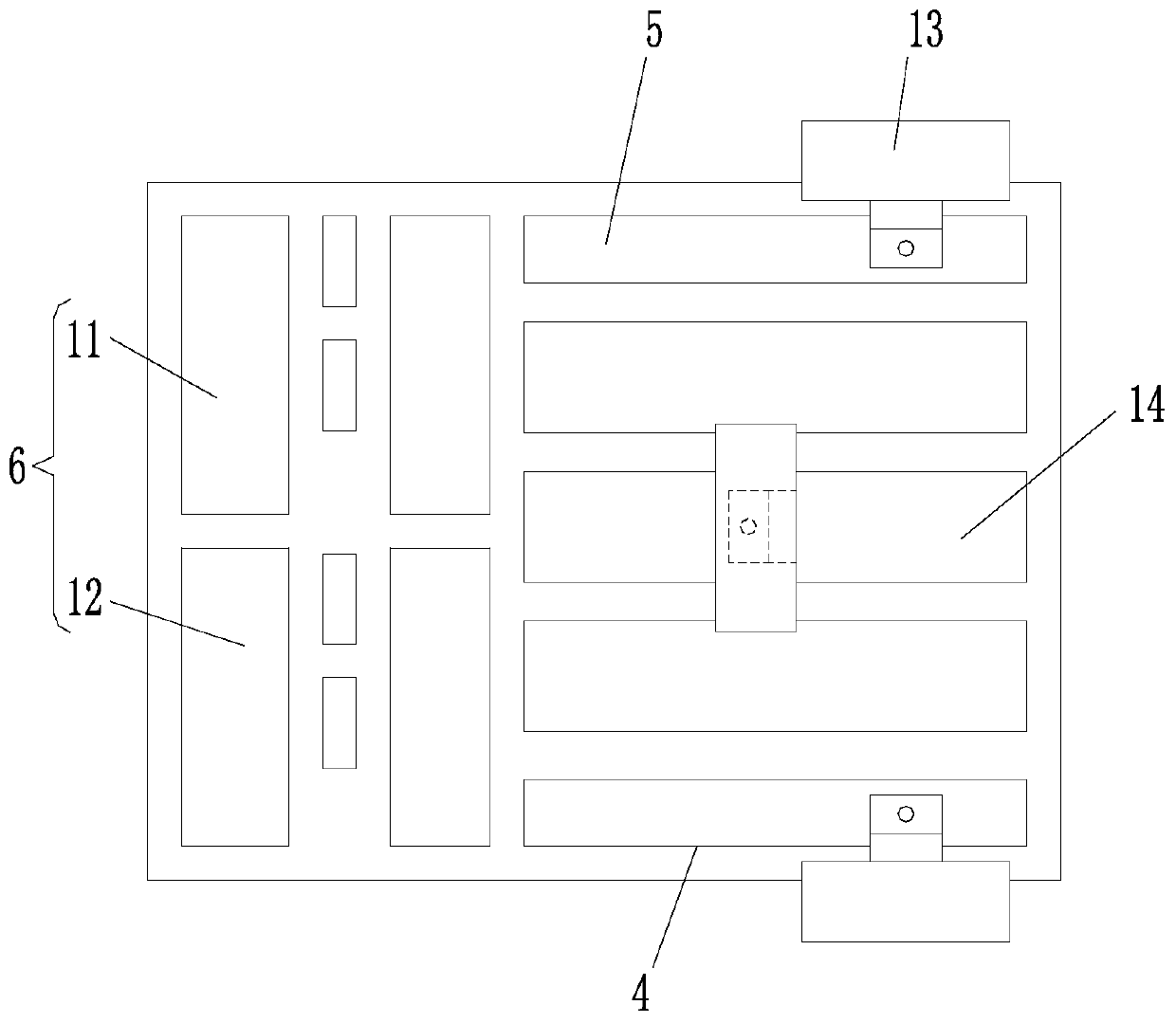

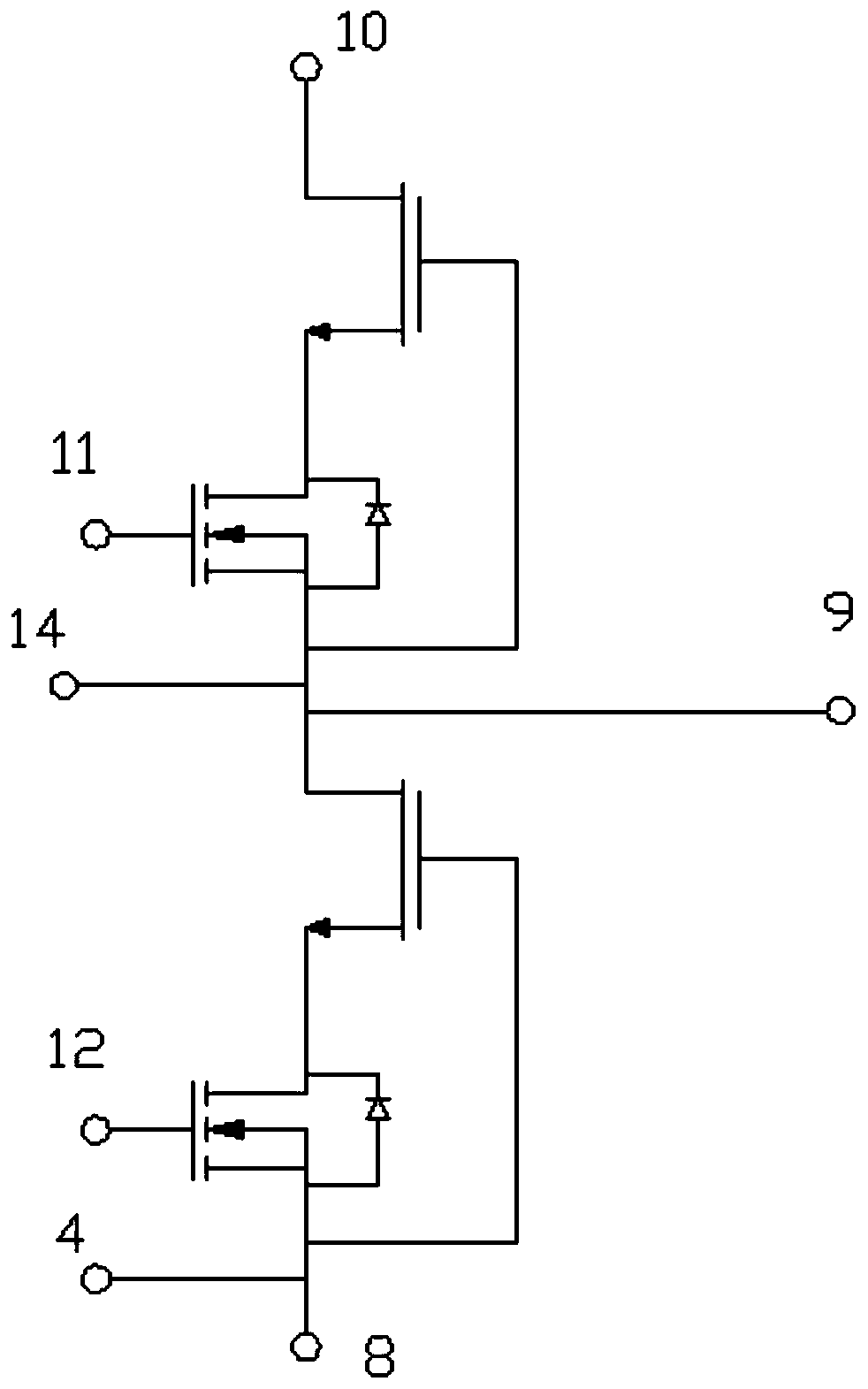

[0016] The invention relates to a DBC board layout method for reducing the parasitic inductance of GaN HEMT power module packaging, wherein the DBC board 1 is pasted with circuit design and layout components, and the components include a GaN chip 2, a MOS chip 3, a gate Resistor 7 and power terminal 13, said DBC board 1 includes source region 5, drain region 4, gate region 6, the key is that said GaN chip 2, MOS chip 3, gate resistor 7 and DBC The boards 1 are soldered by solder paste reflow, and the idle space left between the GaN chip 2 , the MOS chip 3 , the gate resistor 7 and the power terminal 13 is the copper clad on the DBC board 1 .

[0017] The present invention will be further described below with reference to the accompanying drawings and specific embodiments.

[0018] Specific examples, such as Figure 1-3 As shown, the gate region 6 is located at the side area of the DBC board 1, the gate region 6 is distributed with a gate resistor 7, the GaN chip 2 and the MOS

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap