Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

5 results about "Clock generator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A clock generator is an electronic oscillator (circuit) that produces a timing signal (known as a clock signal and behaves as such) for use in synchronizing a circuit's operation. The signal can range from a simple symmetrical square wave to more complex arrangements. The basic parts that all clock generators share are a resonant circuit and an amplifier.

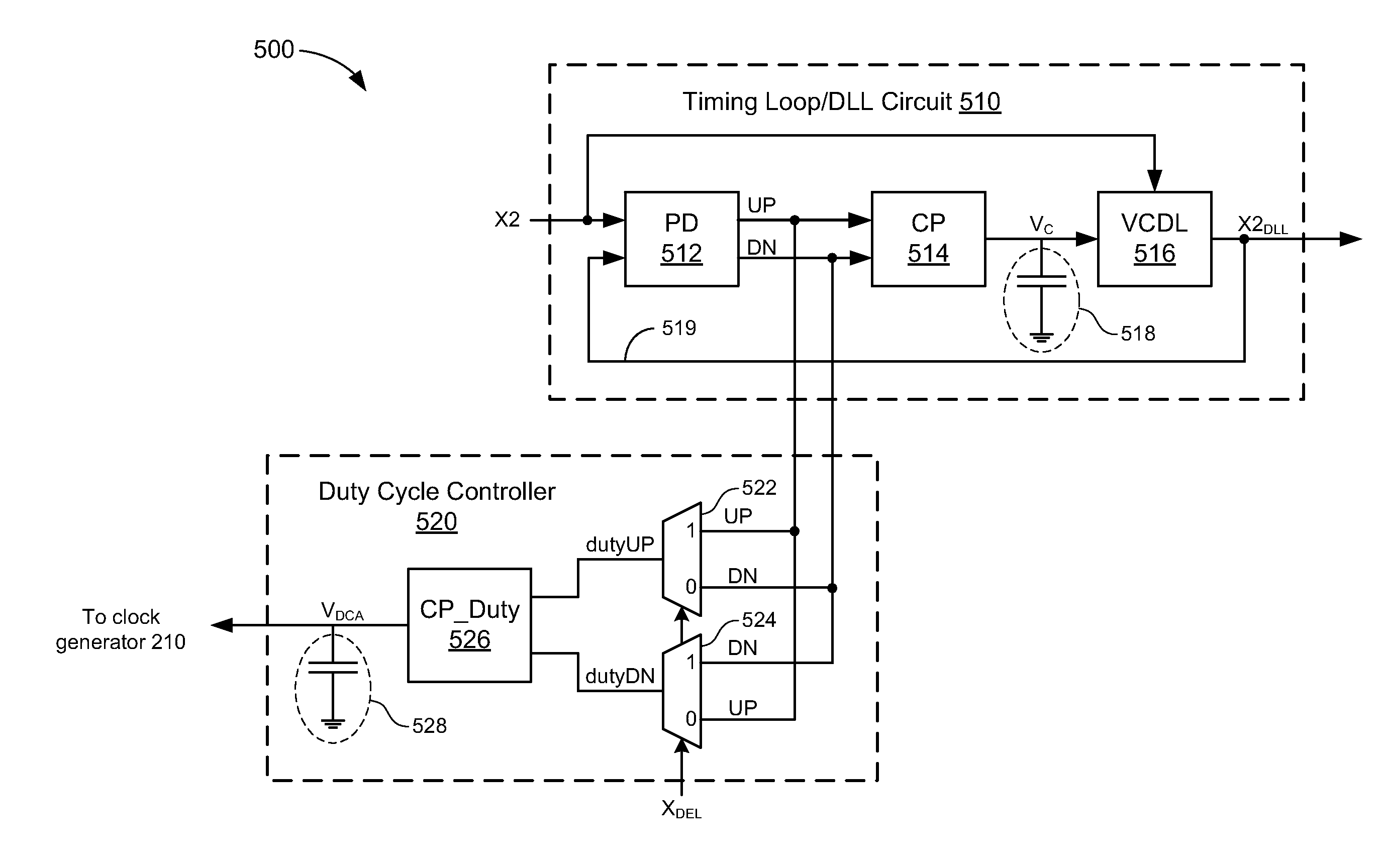

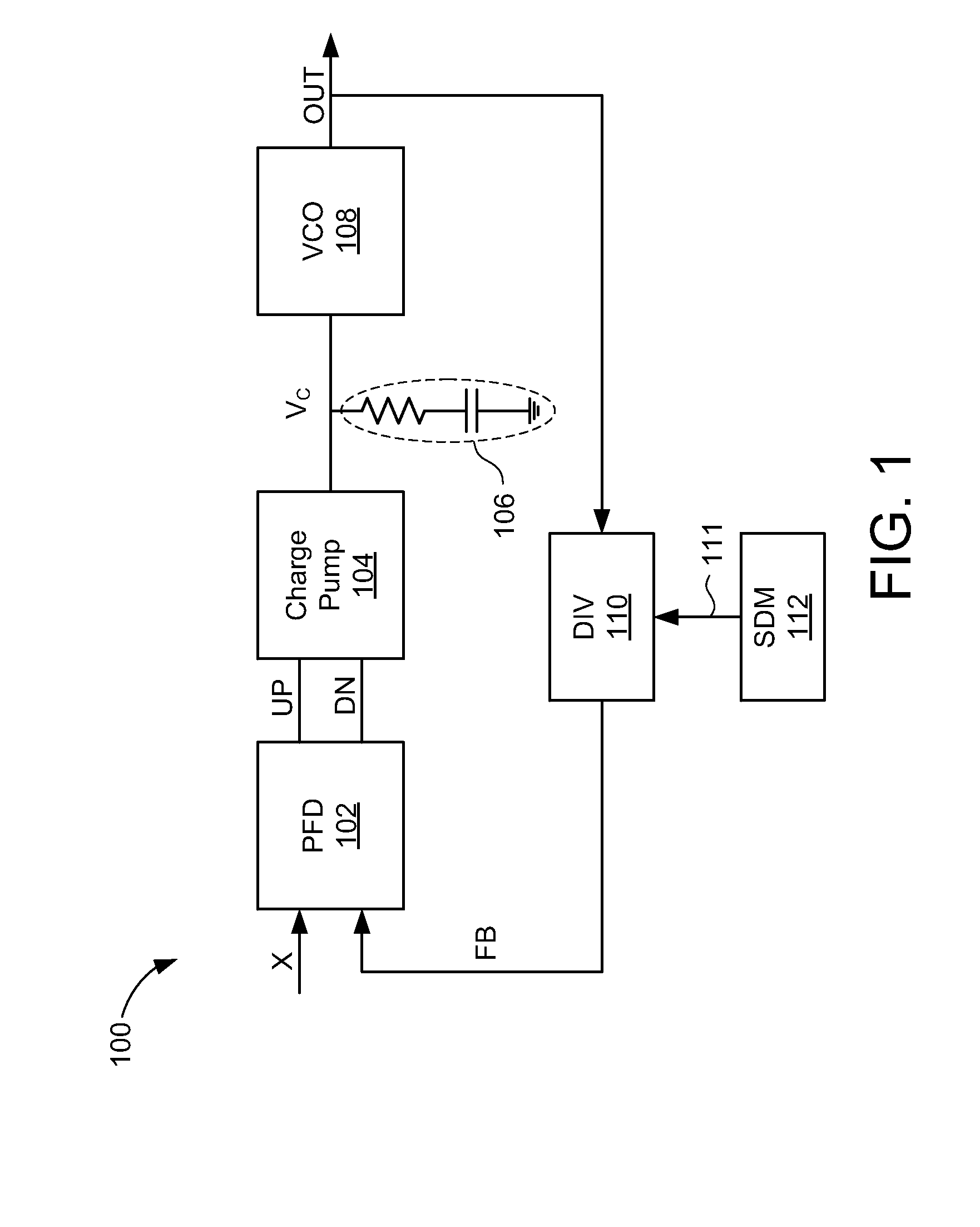

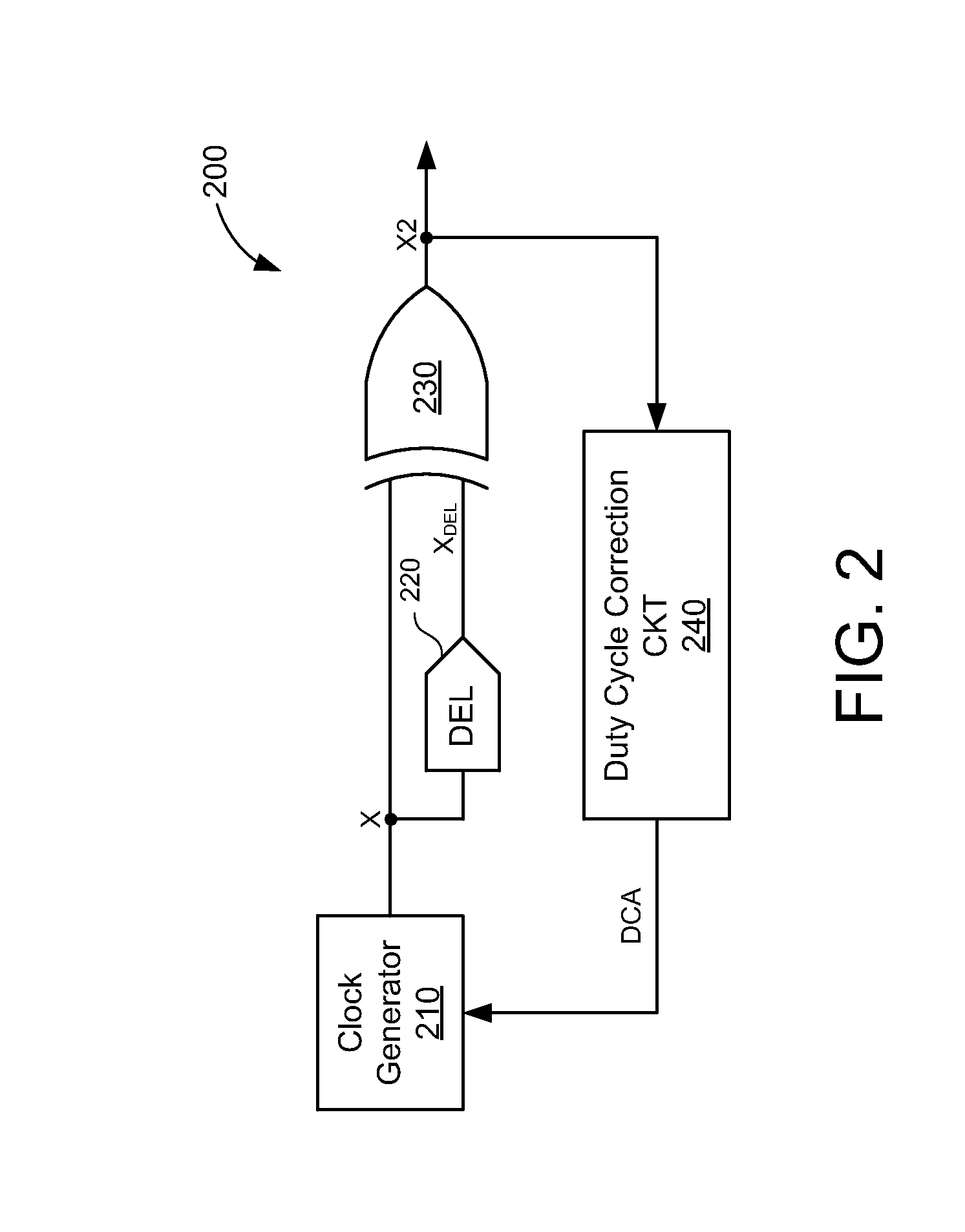

Method and apparatus for generating a reference signal for a fractional-n frequency synthesizer

ActiveUS20140340132A1Synthesizer output phase noiseSettling fastPulse automatic controlFrequency multiplierClock generator

Owner:QUALCOMM INC

System and method for measuring a high speed signal

ActiveUS20050013355A1Transmitters monitoringElectric signal transmission systemsVoltage generatorFall time

An apparatus is provided for measuring an output of a high-speed data transmission circuit. The apparatus includes a programmable reference voltage generator operable to generate a reference voltage that is variable between a plurality of levels. The apparatus also includes a quantizer to quantize an output of the high-speed data transmission circuit relative to the reference voltage level input thereto. Also included is a clock generator operable to generate a clock having a transitioning time (rise-time, fall-time or both) that is less than one quarter of a minimum switching period of the output of the circuit. Finally, the apparatus includes a sampler operable to sample the quantized output with the clock to produce a plurality of samples which measure the output of the circuit.

Owner:MARVELL ASIA PTE LTD

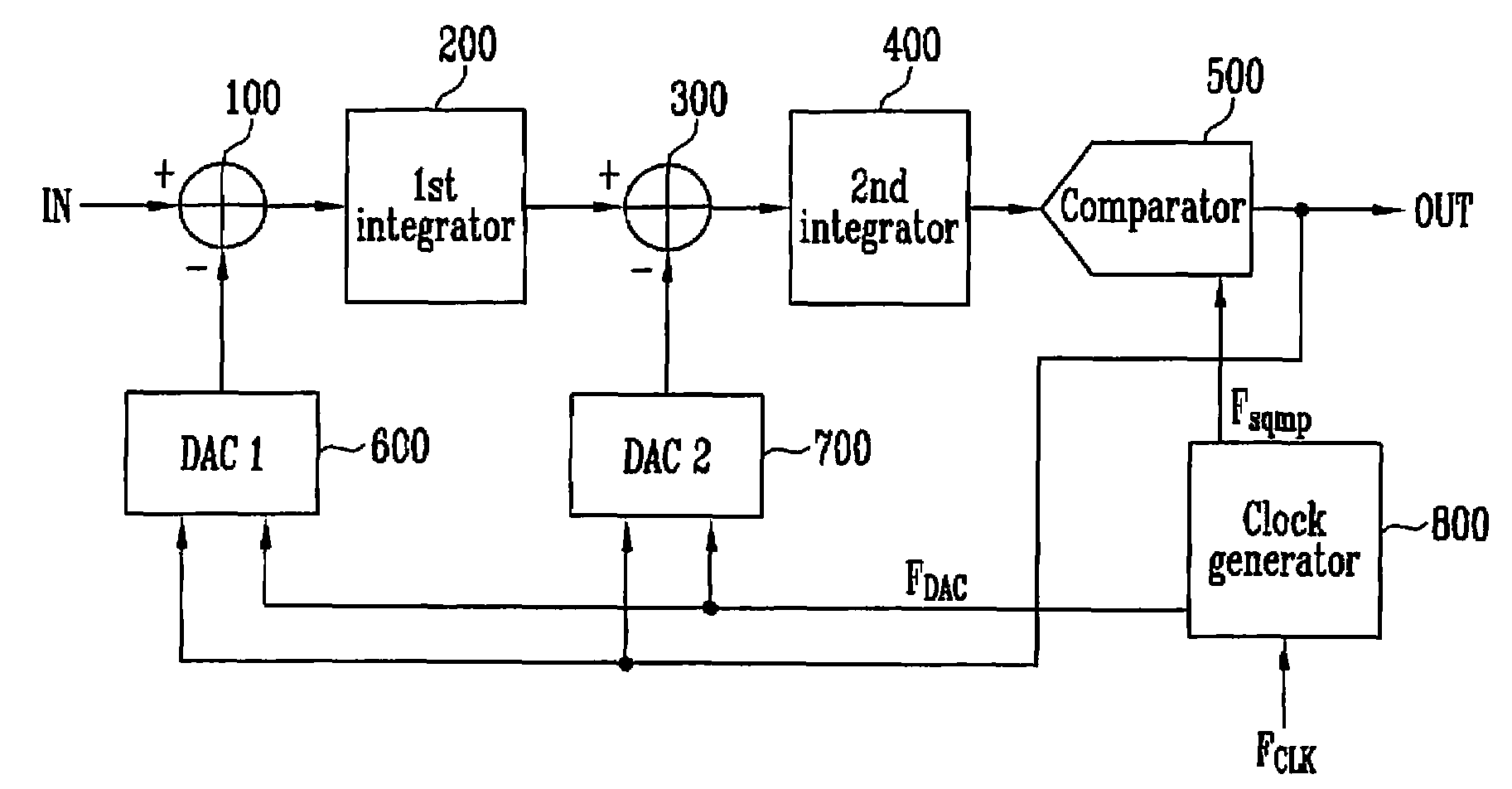

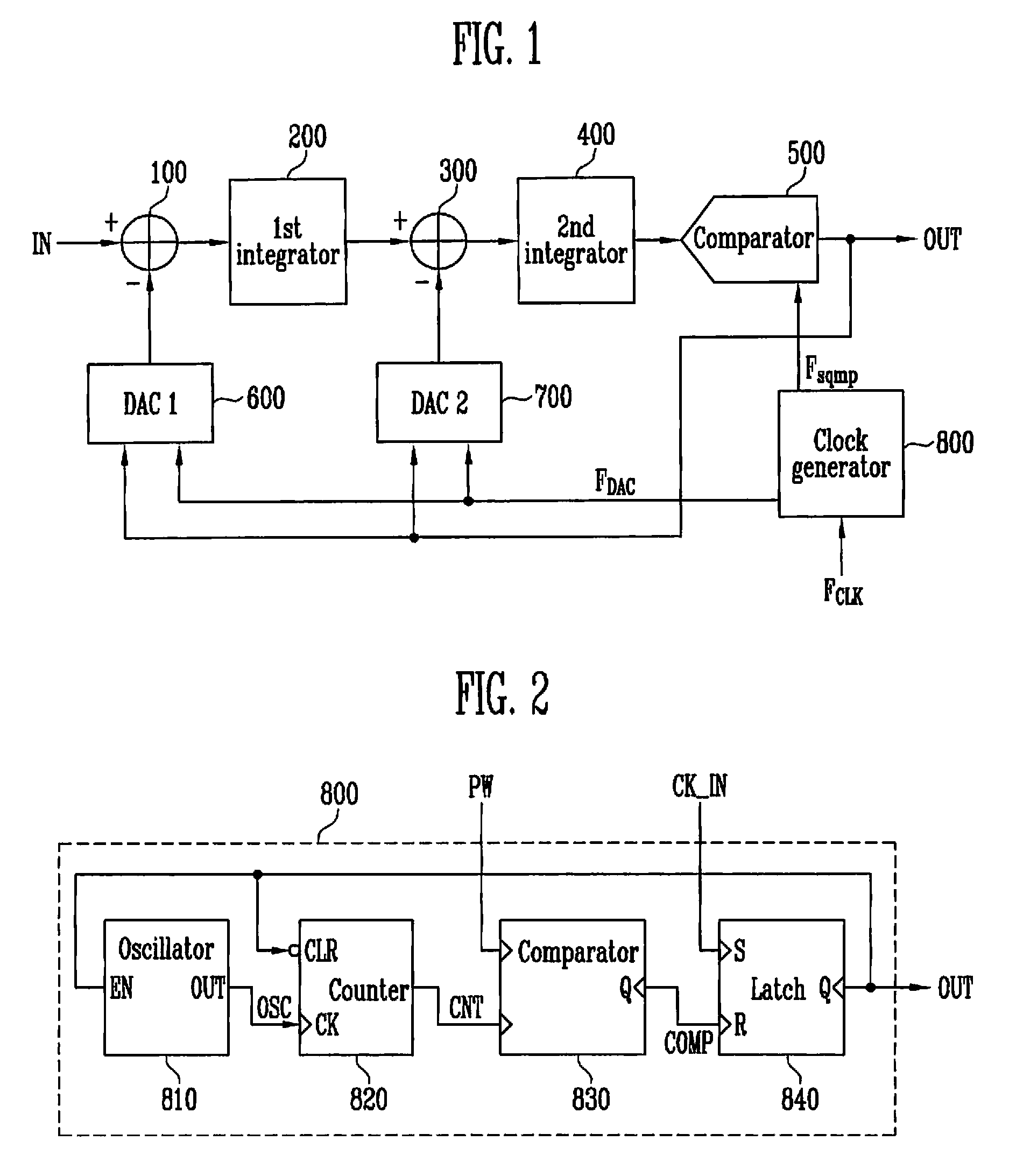

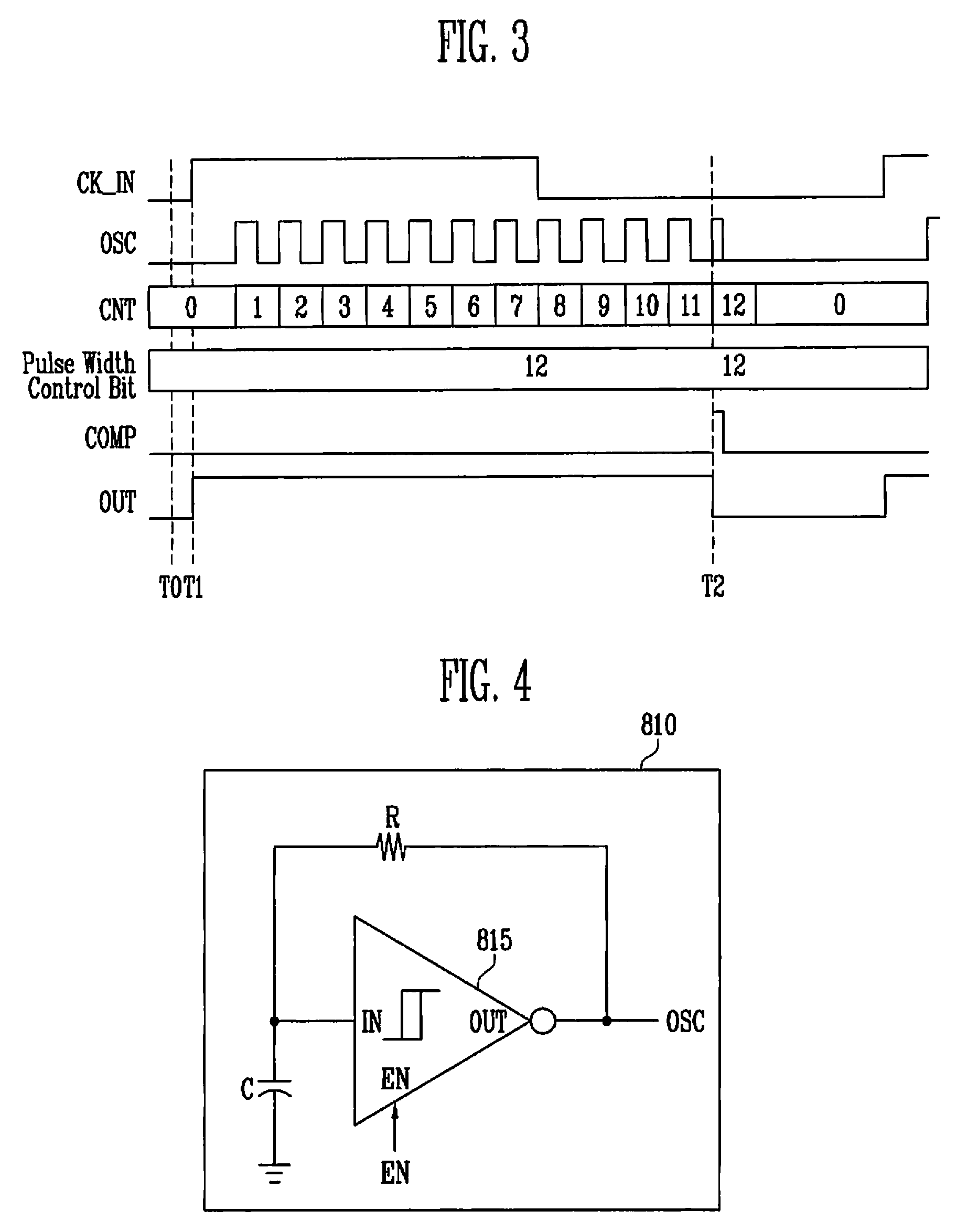

Pulse generator and continuous-time sigma-delta modulator

ActiveUS20100156686A1Avoid SNR DegradationAnalogue/digital conversionElectric signal transmission systemsSignal-to-noise ratio (imaging)Signal-to-quantization-noise ratio

Owner:ELECTRONICS & TELECOMM RES INST

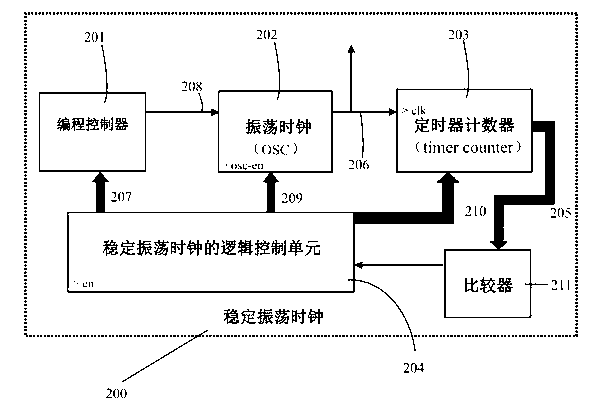

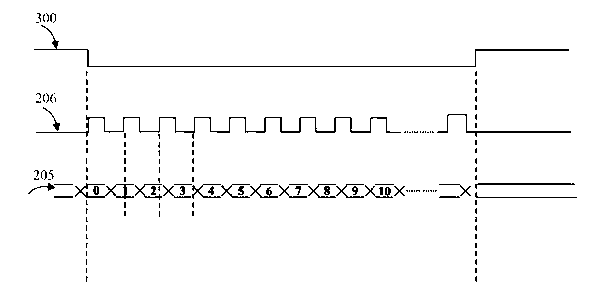

Oscillation clock capable of automatically adjusting frequency and generated inside chip and designing method thereof

InactiveCN103023432AOscillations generatorsClock generatorComparator

Owner:WUXI ADVANCE SUNRISE

Phase locked loop with dual input reference and dynamic bandwidth control

Systems and methods for improved performance of phase-locked loop-based clock generators, particularly in the context of wireless audio, are disclosed herein. The PLL clock generator includes: a PLL core configured to receive a module reference clock provided by the communication module and generate a subsystem data clock corresponding to a module data clock of the communication module; and a data clock tracker module configured to receive the module data and the subsystem data clock and determine a corresponding data clock correction factor. In this way, the bandwidth of the PLL core can be dynamically changed, thereby achieving fast and very precise stabilization. The PLL core may use a low jitter frequency reference for the phase detector while using a synchronized and easily jitter audio sampling clock to ensure that the average frequency of the PLL core tracks the audio sampling clock.

Owner:SYNAPTICS INC

Popular searches

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap