Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3 results about "Shallow trench isolation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

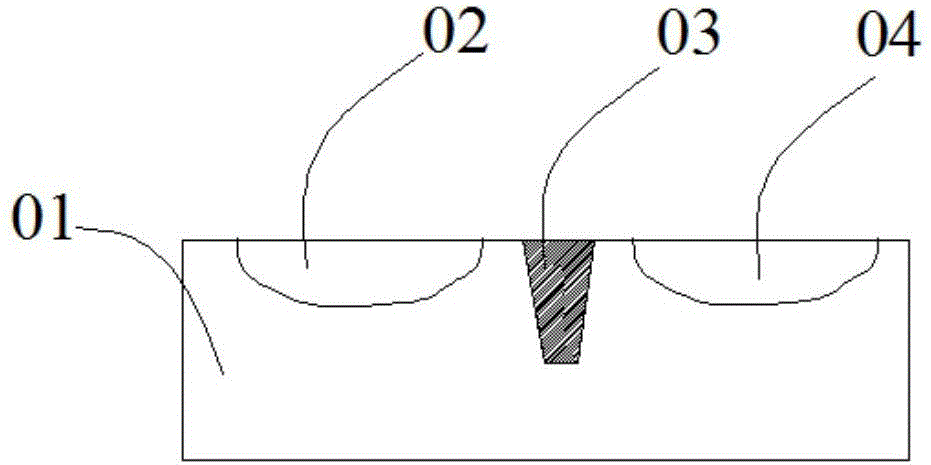

Shallow trench isolation (STI), also known as box isolation technique, is an integrated circuit feature which prevents electric current leakage between adjacent semiconductor device components. STI is generally used on CMOS process technology nodes of 250 nanometers and smaller. Older CMOS technologies and non-MOS technologies commonly use isolation based on LOCOS.

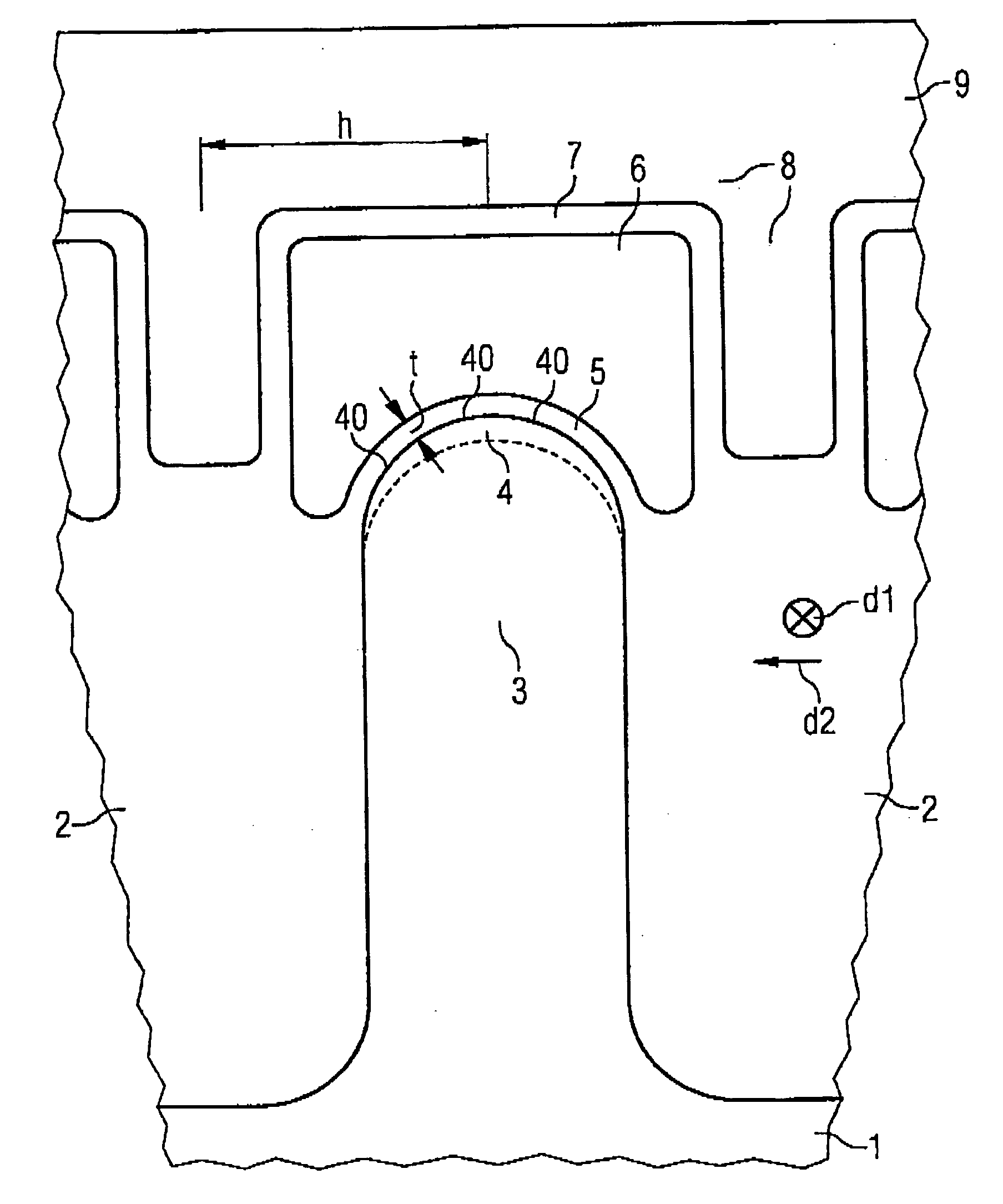

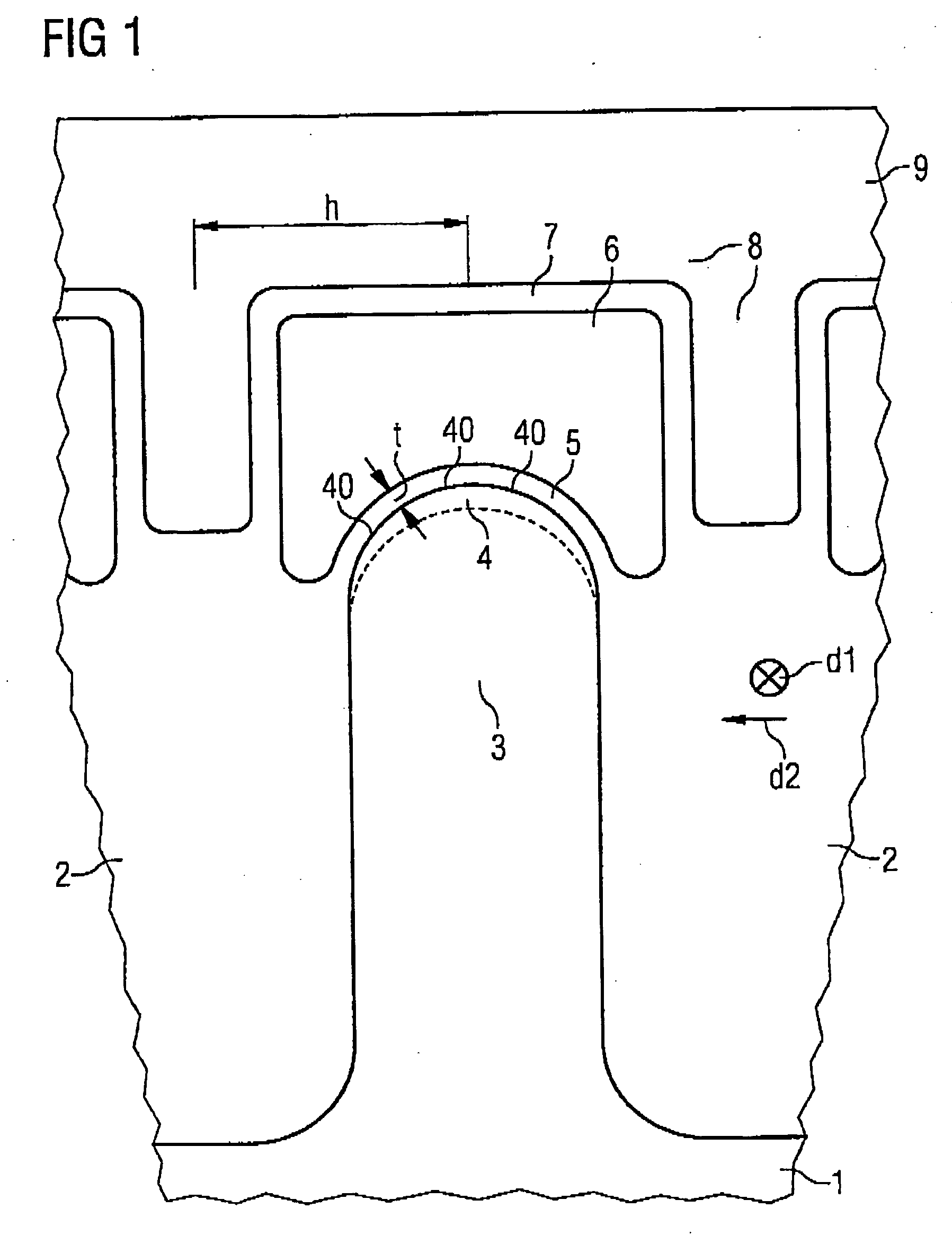

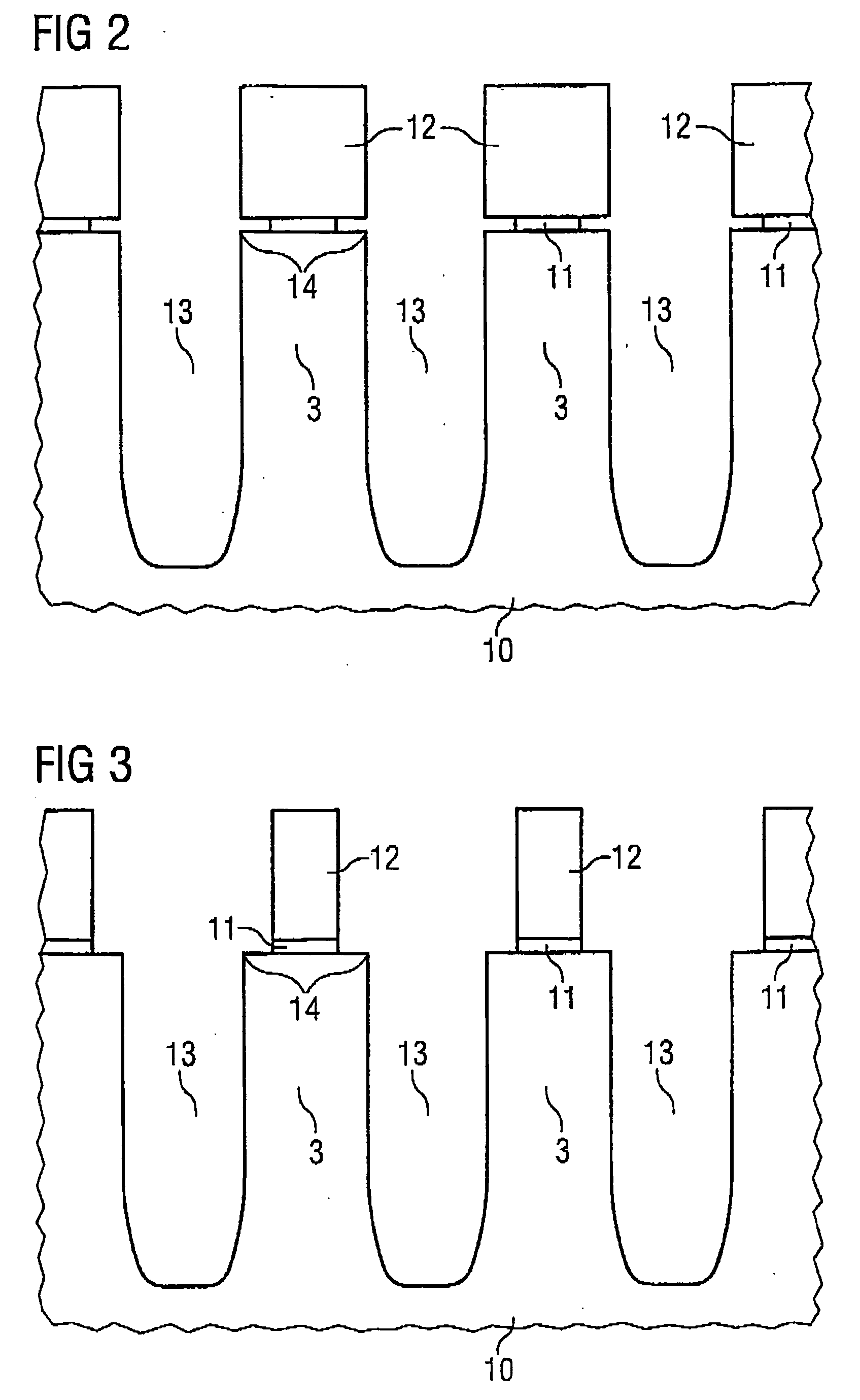

Semiconductor memory device comprising memory cells with floating gate electrode and method of production

InactiveUS20060038220A1Improve compatibilityLower Level RequirementsTransistorSolid-state devicesDielectricSemiconductor materials

Owner:POLARIS INNOVATIONS

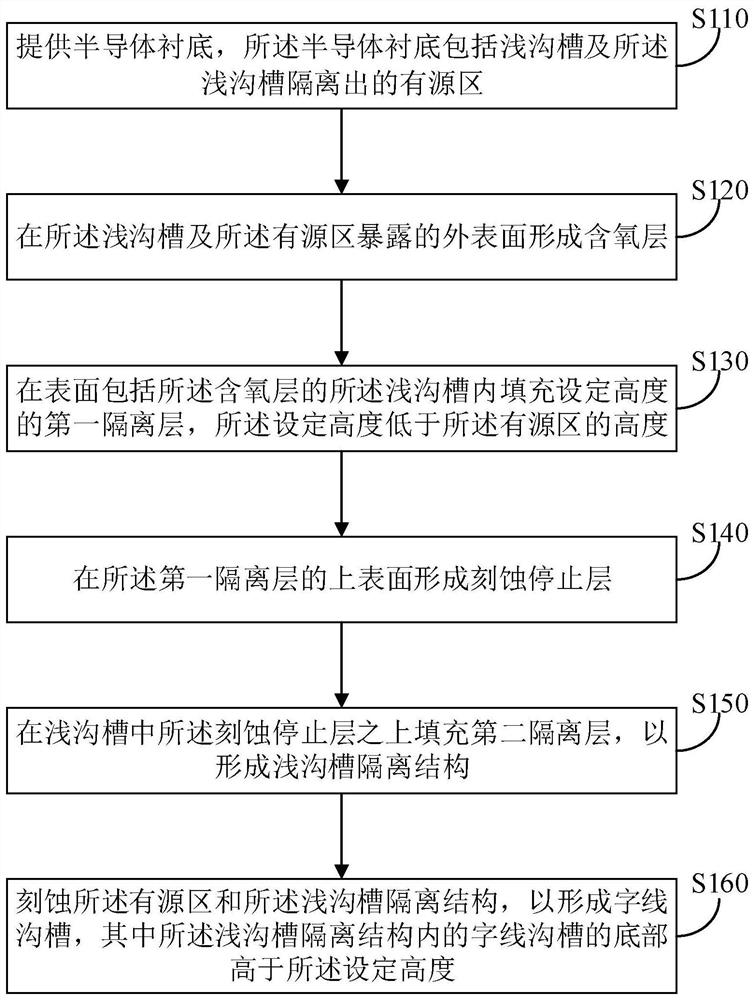

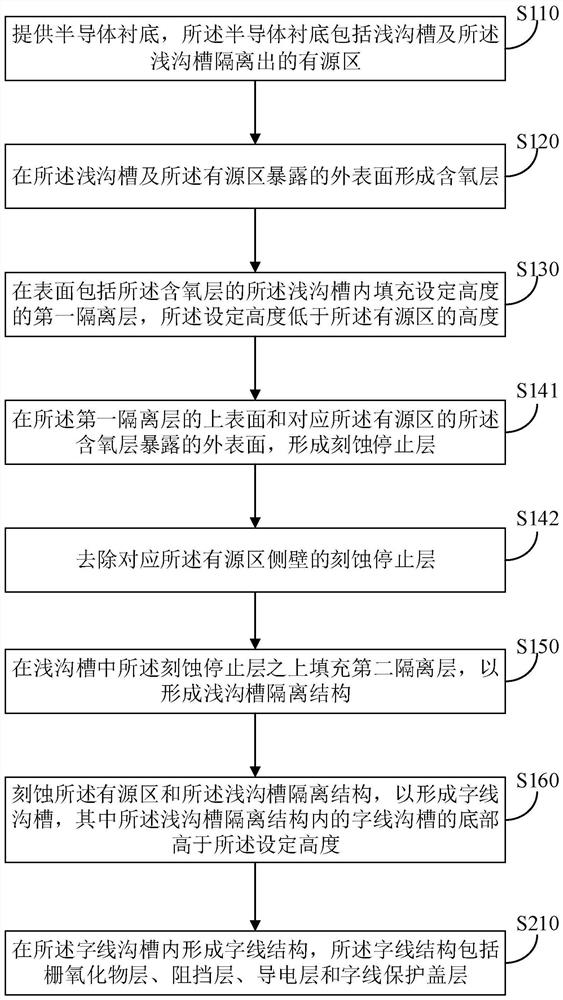

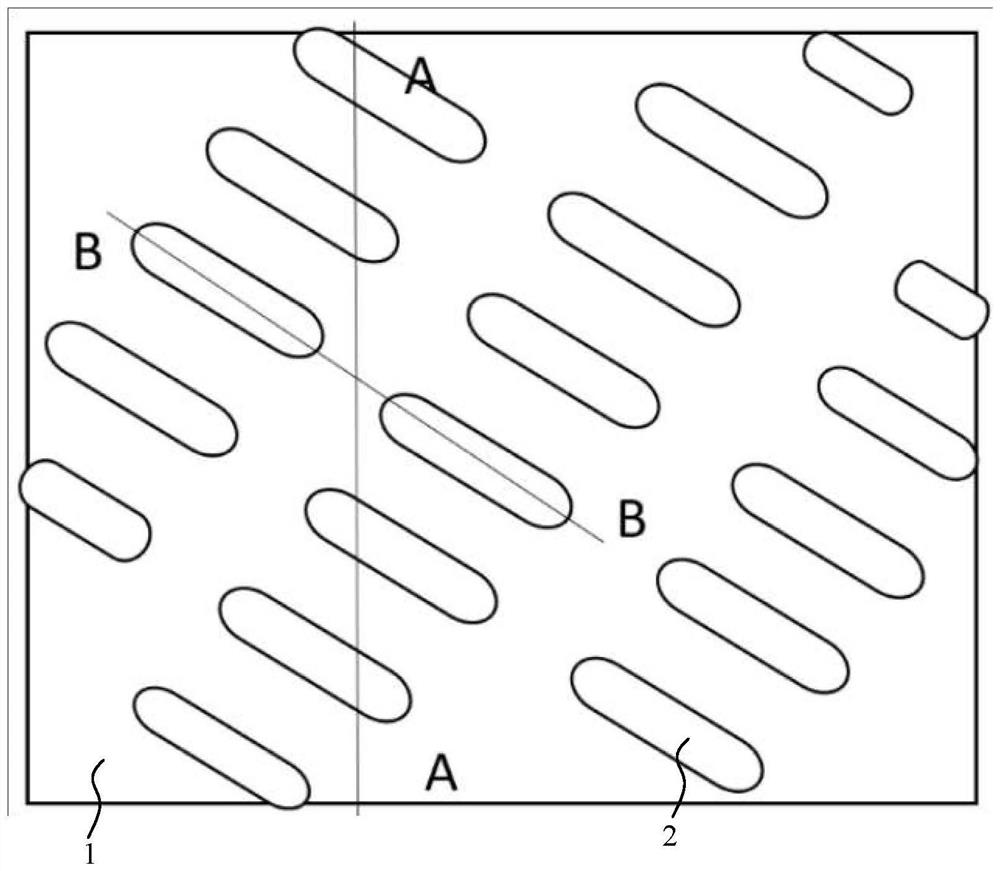

Preparation method of semiconductor device and semiconductor device

ActiveCN113990799AShorten the lengthIncrease parasitic capacitanceTransistorSemiconductor/solid-state device manufacturingDevice materialIsolation layer

Owner:CHANGXIN MEMORY TECH INC

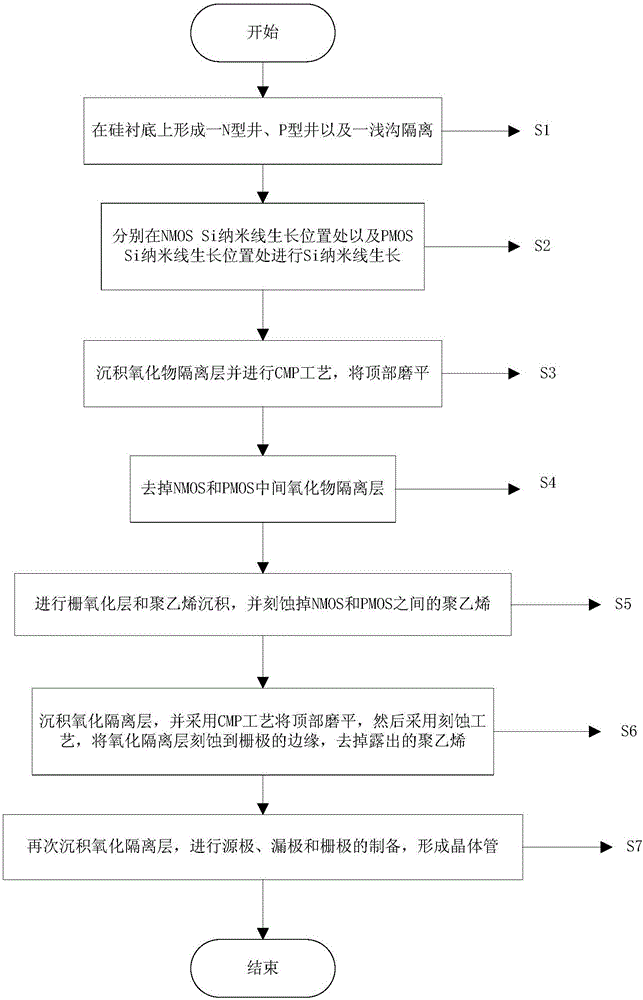

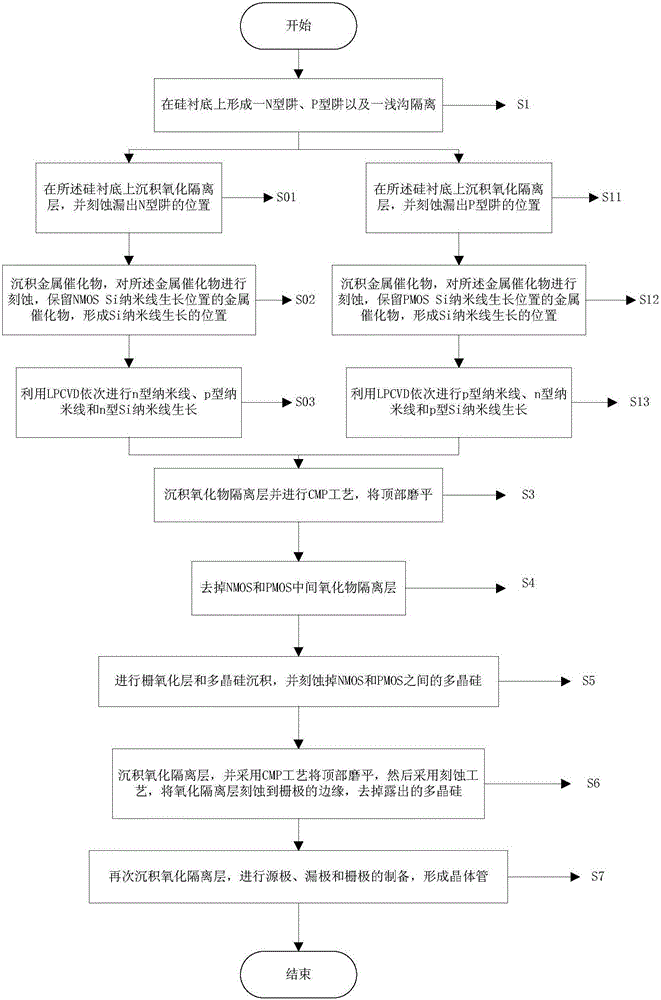

Preparation method of 3D peripheral grid MOS tube

InactiveCN105870192AImprove controlImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon nanowiresIsolation layer

Owner:WUHAN XINXIN SEMICON MFG CO LTD

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap