Method for improving reliability of gate oxide layer in SiC field effect transistor

A technology of field effect transistors and gate oxide layers, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of low reliability of middle gate oxide layers and poor performance of SiC field effect transistors, and achieve compactness Effects of enhancement, interface quality optimization, and reliability improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

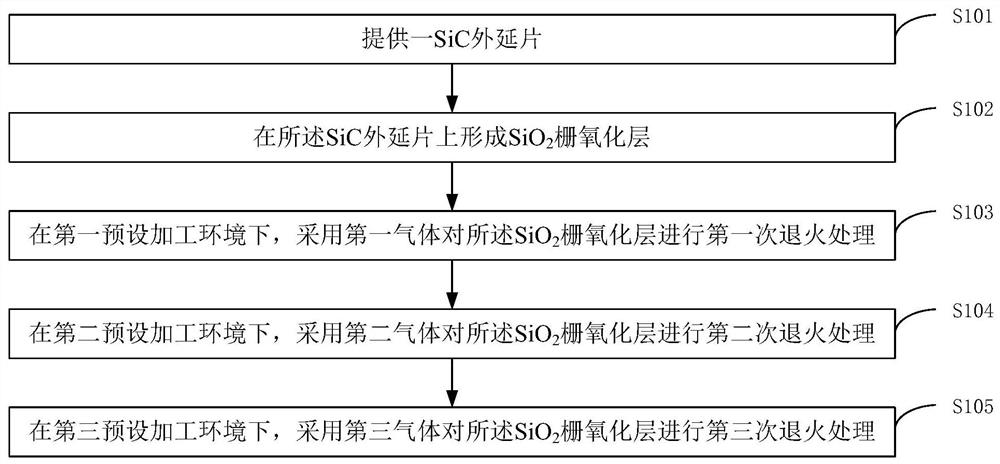

[0038] The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only a part of the embodiments of the present invention, but not all of the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art without creative efforts shall fall within the protection scope of the present invention.

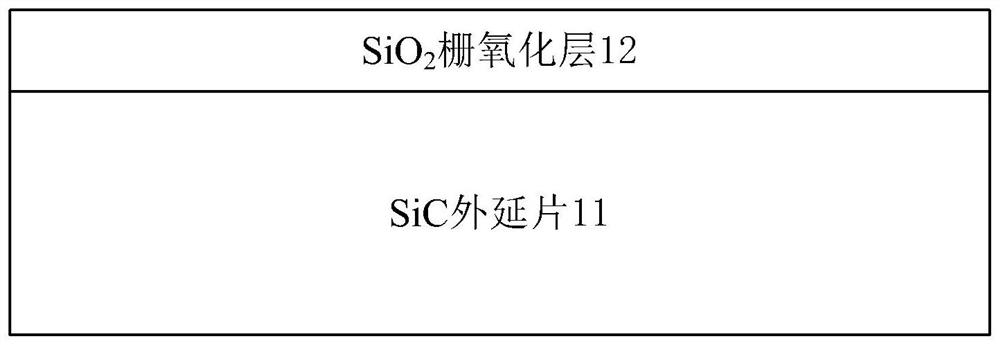

[0039] During the invention and creation process of the present invention, the inventor found that in the SiC field effect transistor, due to the SiO2 in the growth process 2 And the problem of lattice mismatch of SiC material, in SiO 2 SiO for gate oxide 2 A large number of trapped charges such as dangling bonds, carbon clusters and oxygen vacancies will be generated in the interface and the SiC interface of the SiC epitaxial layer, wh

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap