High-voltage-withstanding semiconductor device and fabrication method thereof

a high-voltage-resistance semiconductor and fabrication method technology, applied in semiconductor devices, semiconductor device details, electrical apparatus, etc., can solve the problems of not paying attention to the need to avoid plasma damage in a high-voltage-resistance semiconductor device, the semiconductor device's insulation film is susceptible to plasma damage, and the need to resist plasma damage, etc., to suppress the dispersion of vt fluctuation, avoid operation failure, and suppress the effect of vt fluctuation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029]One exemplary embodiment of a high-voltage-withstanding semiconductor device of the invention and its fabrication method will be explained below with reference to the drawings.

[NOMS Transistor]

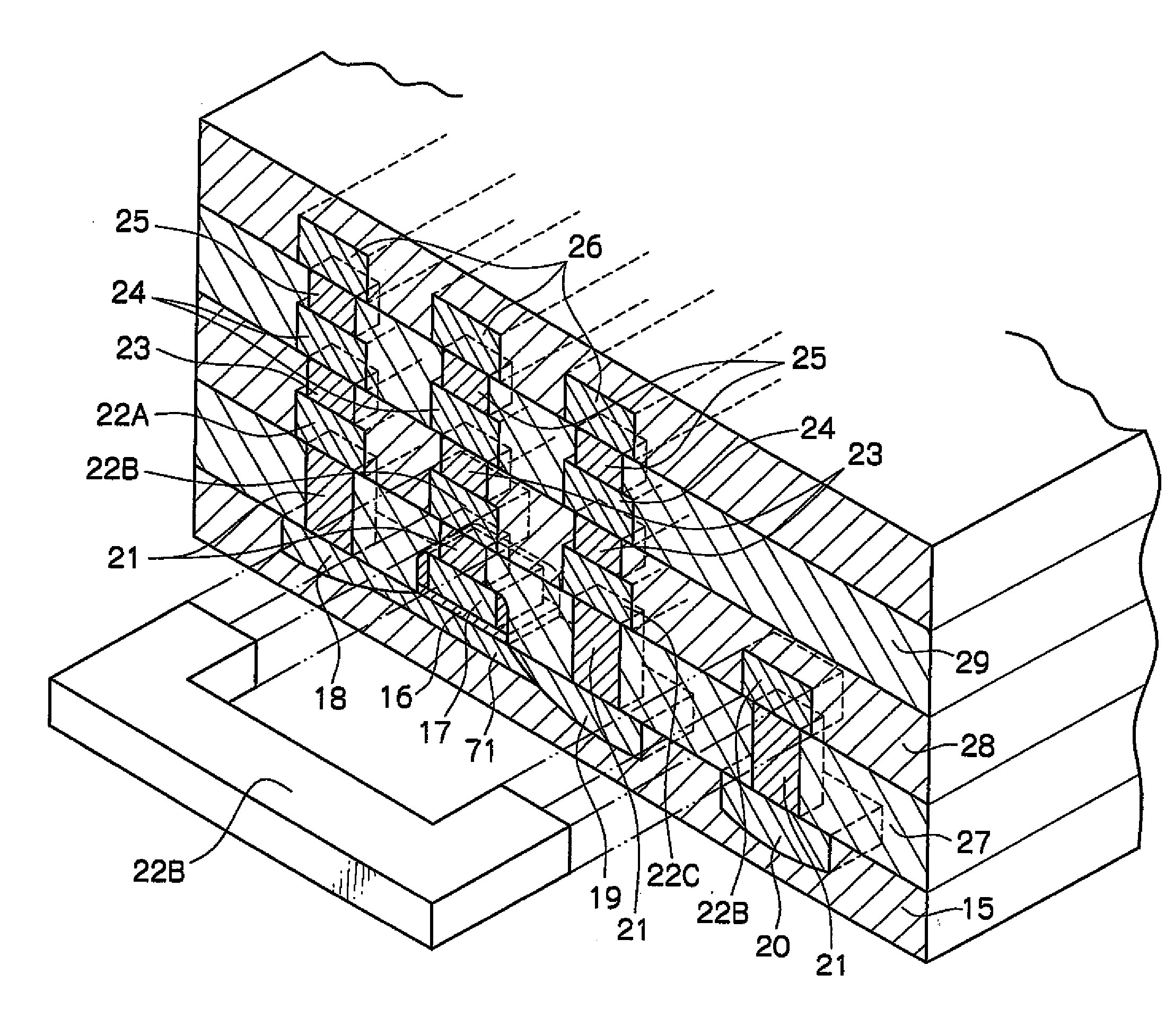

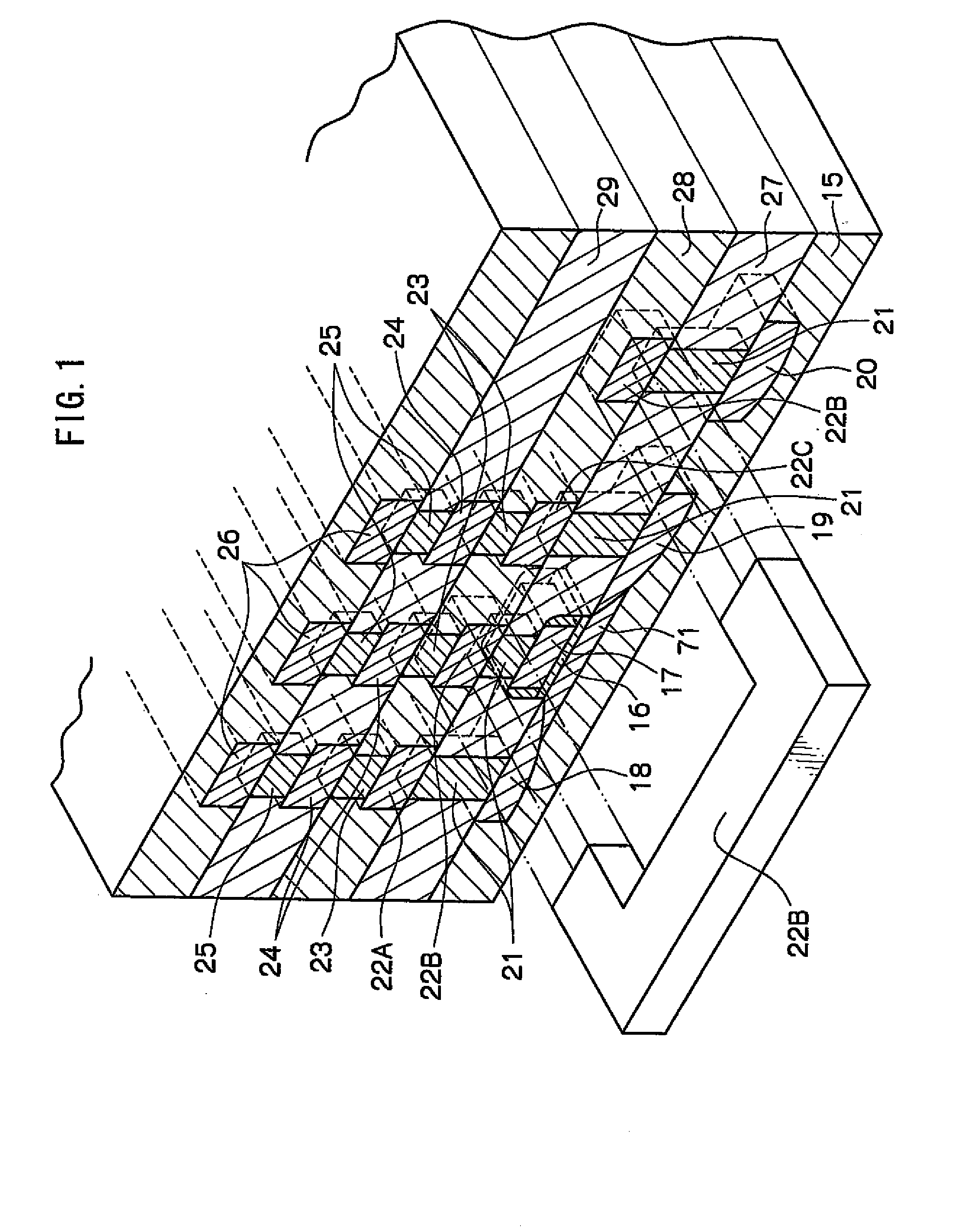

[0030]FIG. 1 is a schematic diagram of a high-voltage-withstanding semiconductor device using a NMOS transistor of the invention.

[0031]The high-voltage-withstanding semiconductor device is fabricated through the following processing steps.

[0032]A semiconductor substrate having a first conductive transistor forming region and a first conductive diode forming region in a surface layer region thereof is prepared.

[0033]Here, the first conductive transistor forming region is formed at a region different from the first conductive diode-forming region. A distance between the transistor forming region and the diode forming region is not specifically defined as long as they are apart from each other by a degree of exhibiting functions of transistor and diode, respectively.

[0034]The transistor is for

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap