Method and apparatus for buried word line formation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

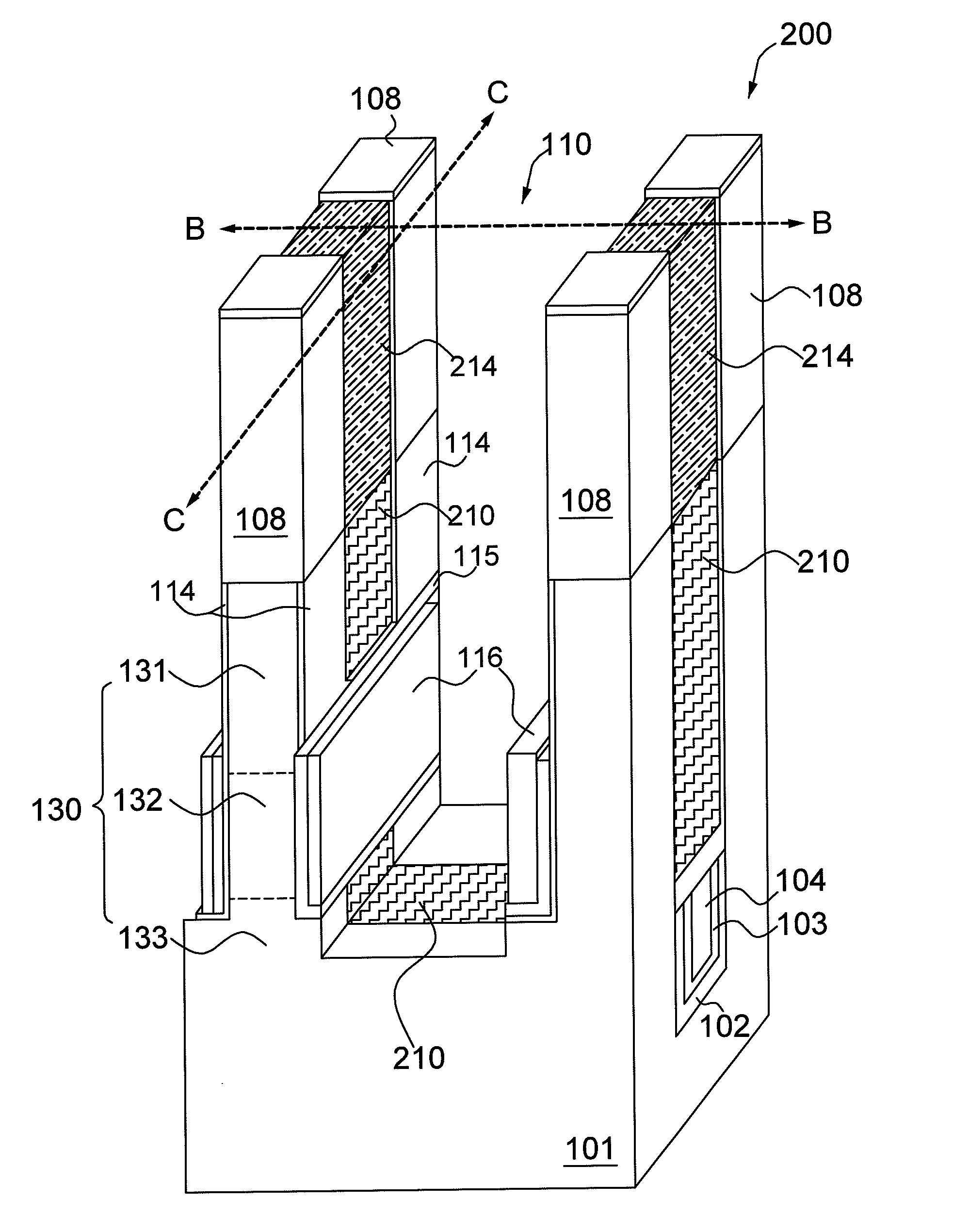

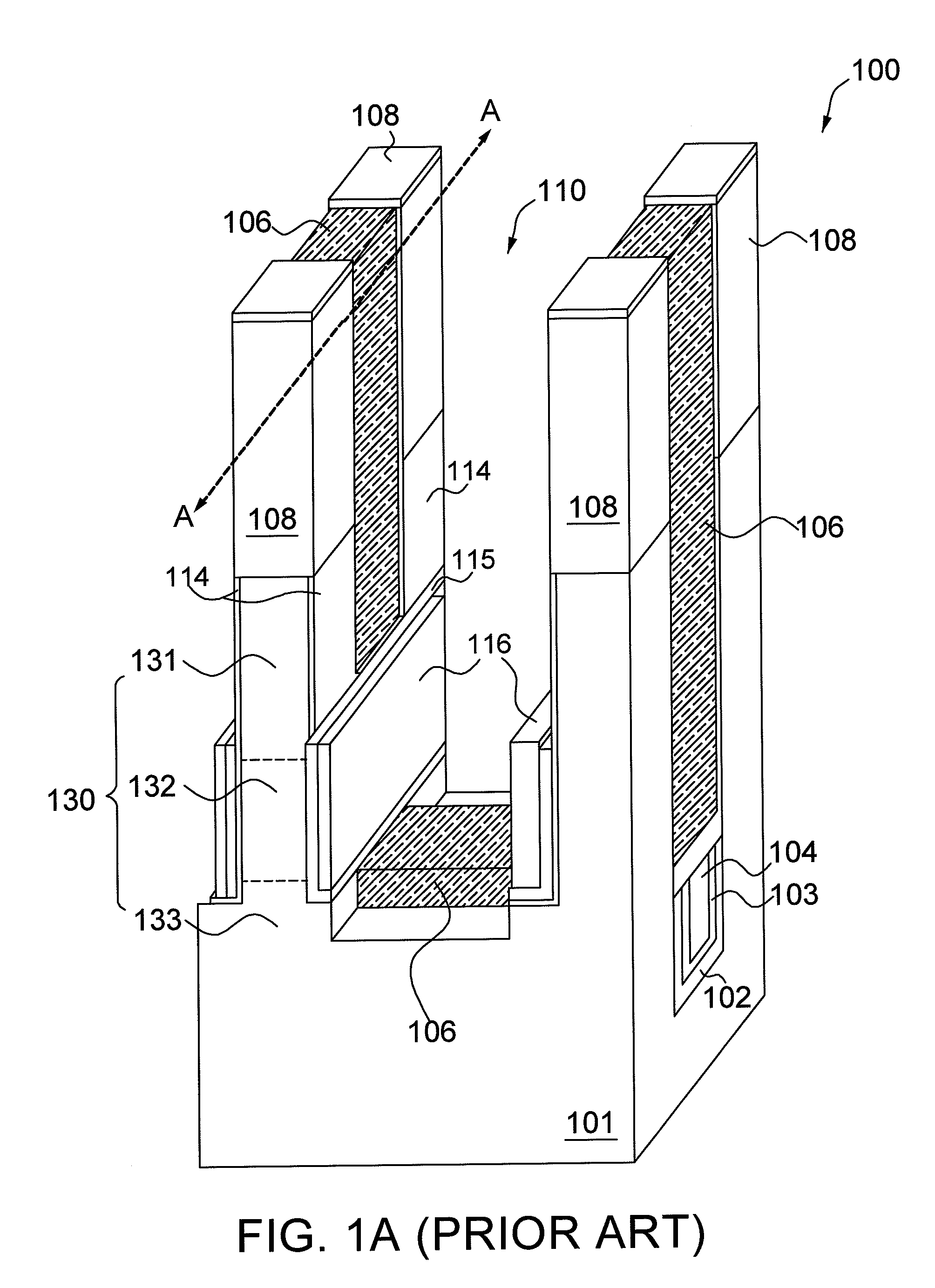

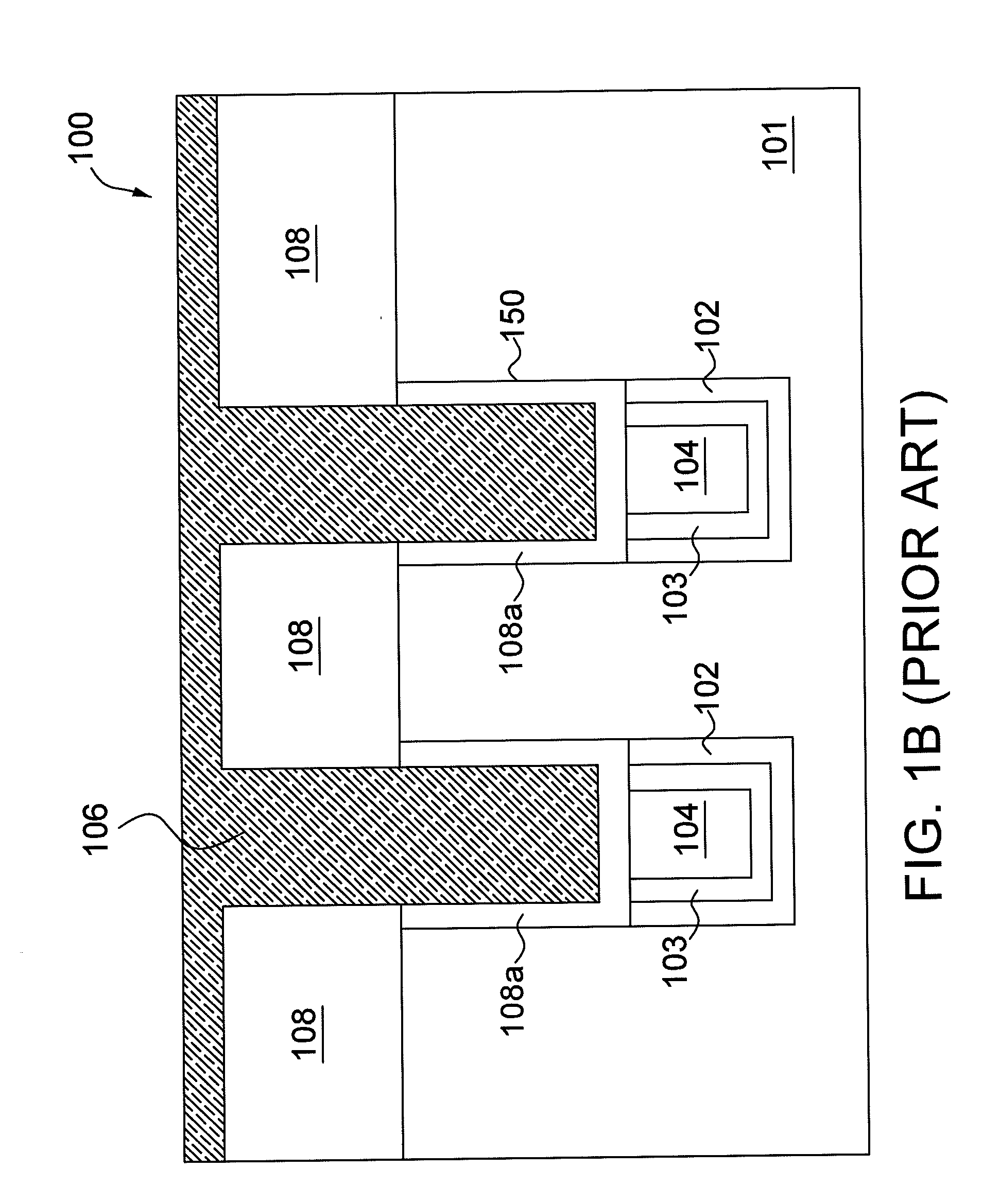

[0024]FIG. 2A is a perspective view of a memory cell having a generally smooth word line trench according to an embodiment of the invention. Referring to FIG. 2A, a memory cell 200 includes buried bit and word lines 104, 116 coupled to a vertical access transistor 130 disposed in a semiconductor substrate 101. The memory cell 200 can be any type of memory cell employing buried bit and word lines 104, 116, such as a DRAM cell, a MRAM cell, a FLASH cell, etc. For ease of description, the memory cell 200 is described herein as a DRAM cell. However, those skilled in the art will appreciate that the embodiments described herein are readily applicable to other types of memory cells having buried bit and word lines 104, 116.

[0025]In this specification, common reference numerals have been employed where common elements have the same function as in all drawings and embodiments described herein.

[0026]FIG. 2B is a cross-section view taken along the cut line B-B of FIG. 2A. Two adjacent word lines

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap