Manufacturing method of high-linearity and high-power CMOS structure

a manufacturing method and high-power technology, applied in the direction of basic electric elements, electrical apparatus, semiconductor devices, etc., can solve the problems of increasing the dc power consumption of the cmos component, and achieve the effect of reducing leakage current and dc power consumption, increasing linearity and output power, and increasing output power

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024]Now, the present invention will be described more specifically with reference to the following embodiments. It is to be noted that the following descriptions of preferred embodiments of this invention are, presented herein for purpose of illustration and description only; it is not intended to be exhaustive or to be limited to the precise form disclosed.

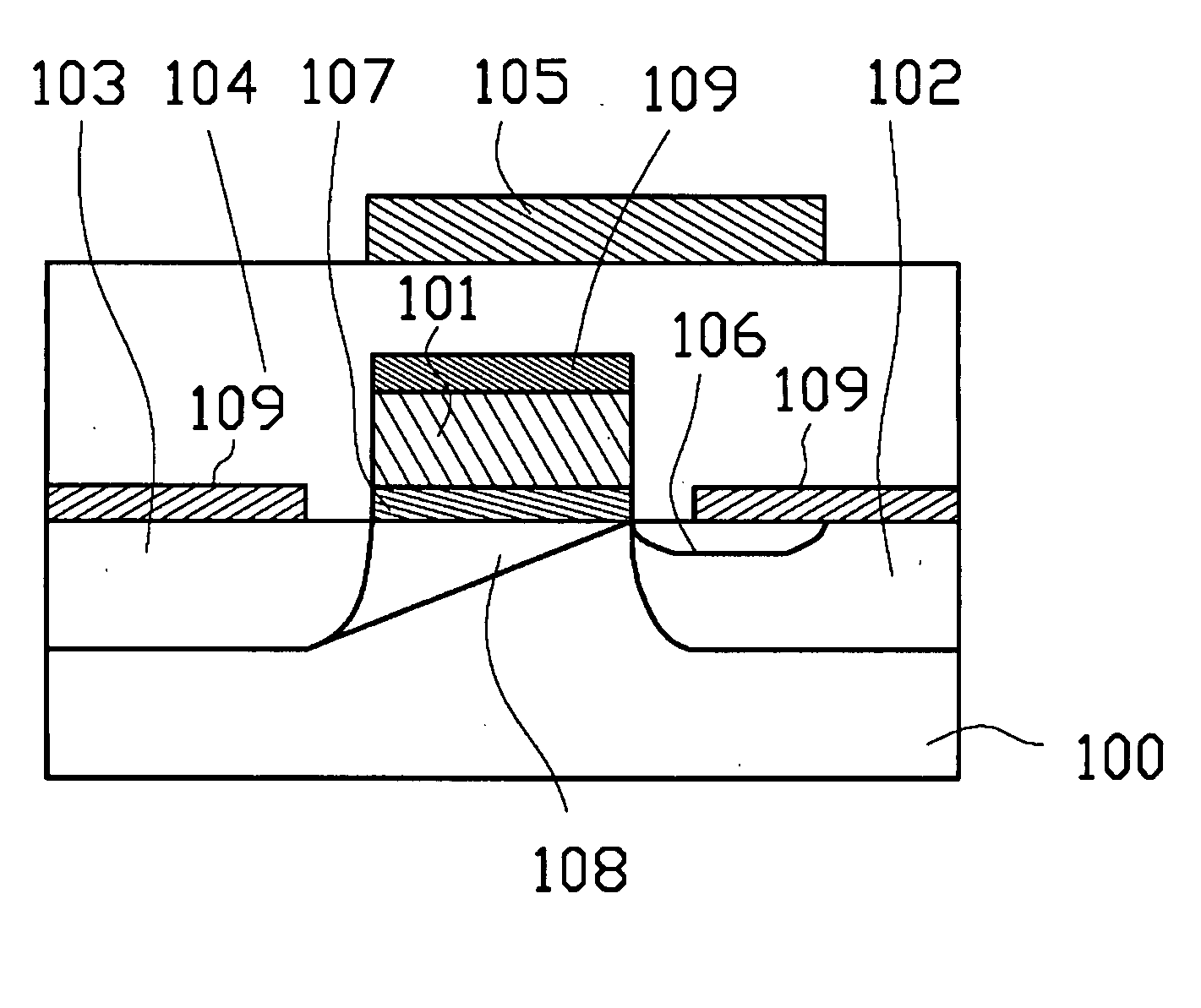

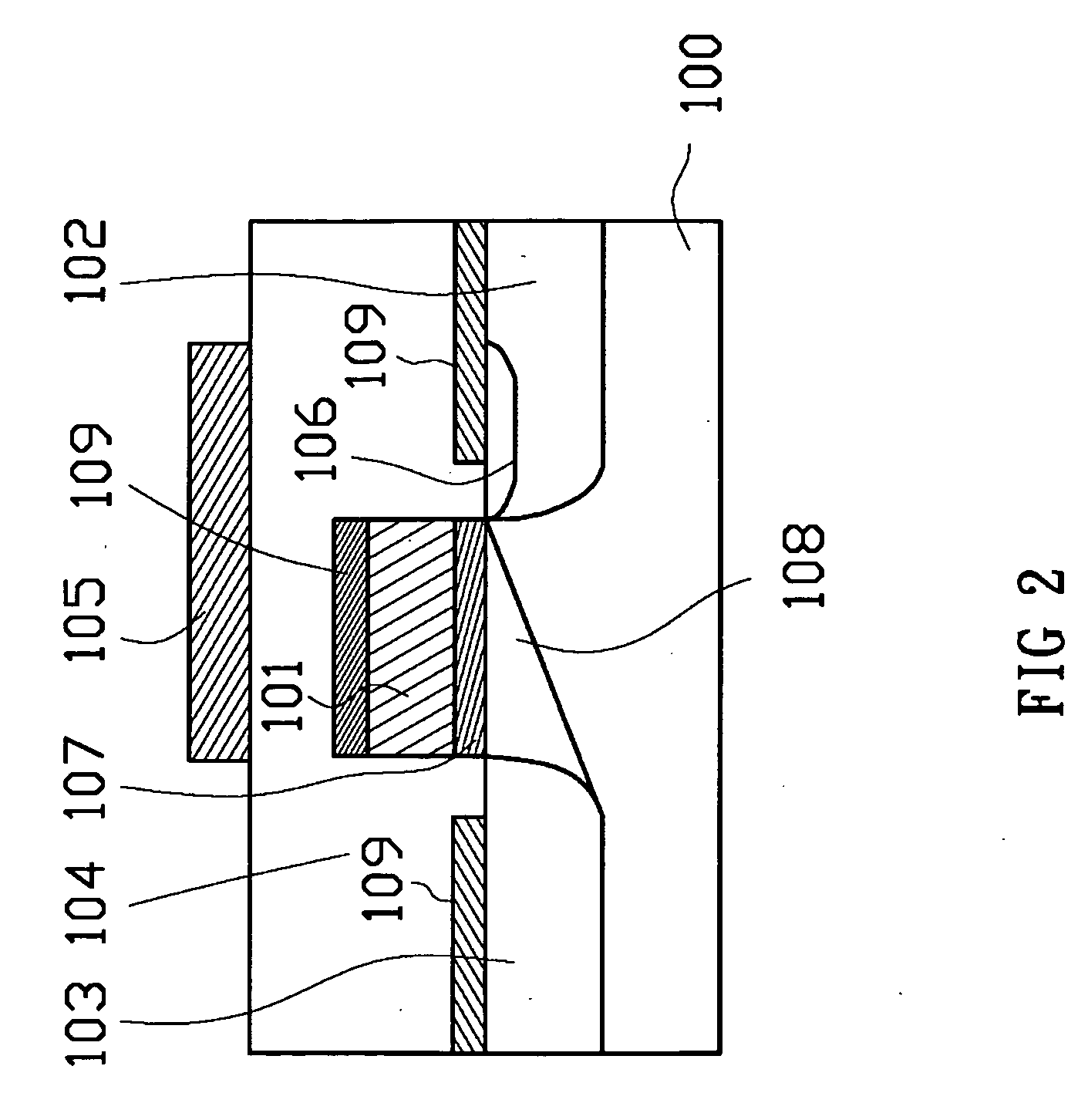

[0025]In an embodiment of this invention, a field plate technology is applied to a NMOS component in a standard TSMC 0.13 um CMOS process, in which, as shown in FIG. 2, the CMOS component is structured with a Si bulk as a base 100, comprising a gate 101 on a base 100, in which, a source 103 and a drain 102 are arranged in the base 100 between the two sides of the gate 101. Besides, a gate dielectric layer 107 is arranged between the gate 101 and the base 100, and may be made of silica and serve as an insulation layer that provides the CMOS component with an extremely high input resistance.

[0026]Further, metallic silicide layers 10

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap