Verification method for chip reset test scene

A technology for testing scenarios and verification methods, which is applied in the fields of instruments, computing, electrical and digital data processing, etc., and can solve the problems of easy-to-miss reset scenario testing, increased difficulty in code management and maintenance, and difficulty in debugging when problems occur.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] The following will be combined with the attachment to describe the preferred embodiments of the present invention in detail to further explain the present invention.

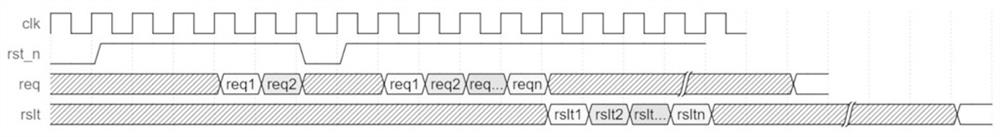

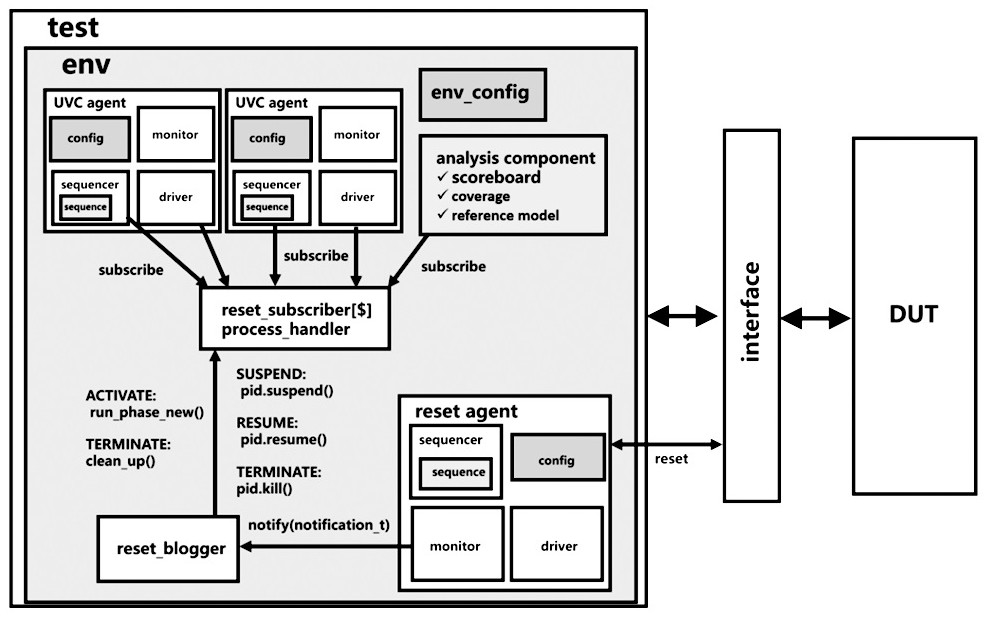

[0057] First, it will be combined Figure 2 ~ 3 The 5 ~ 6 description is based on the verification method of the chip reset testing scenario based on the examples of the present invention. It is used for chip verification and use, and its application scenarios are wide.

[0058] like image 3 It shows that the verification method of the embodiment of the present invention has the following steps:

[0059] In S1, such as image 3 Show, the processing processor process_handler, resetner Reset_Subscriber, and resetter Reset_blogger. Provide the Apply method to the processing processor to operate the current simulation operation according to the type of reset notification message. The reset notification information type Reset_blogger_notification_t is an enumeration variable that operates the process process, includ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap